# **mXT336UD-MAUHA1 1.0**

# maXTouch 336-node Touchscreen Controller

### **Functional Safety**

- IEC/UL 60730 Class B support

- Self diagnostics at power-on and as periodic tests during operation

- · Heartbeat (alive) signal output to host

# maXTouch® Adaptive Sensing Touchscreen Technology

- Up to 14 X (transmit) lines and 24 Y (receive) lines for use by a touchscreen (see Section 3.2.1 "Permitted Configurations")

- A maximum of 336 nodes can be allocated to the touch sensor

- Touchscreen size of 7.11 inches (16:9 aspect ratio), assuming a sensor electrode pitch of 6.5 mm. Other sizes are possible with different electrode pitches and appropriate sensor material

- Multiple touch support with up to 10 concurrent touches tracked in real time

#### **Touch Sensor Technology**

- Discrete/out-cell support including glass and PET filmbased sensors

- On-cell/touch-on display support including TFT, IPS and OLED

- Synchronization with display refresh timing capability

- Support for standard (for example, Diamond) and proprietary sensor patterns (review of designs by Microchip or a Microchip-qualified touch sensor module partner is recommended)

#### **Front Panel Material**

- Works with PET or glass, including curved profiles (configuration and stack-up to be approved by Microchip or a Microchip-qualified touch sensor module partner)

- 10 mm glass (or 5 mm PMMA) with bare finger (dependent on screen size, touch size, configuration and stack-up)

- 6 mm glass (or 3 mm PMMA) with multi-finger 5 mm glove (2.7 mm PMMA equivalent) (dependent on screen size, touch size, configuration and stack-up)

#### **Touch Performance**

- · Moisture/Water Compensation

- No false touch with condensation or water drop up to 22 mm diameter

- One-finger tracking with condensation or water drop up to 22 mm diameter

- Mutual capacitance and self capacitance measurements supported for robust touch detection

- P2P mutual capacitance measurements supported for extra sensitive multi-touch sensing

- Noise suppression technology to combat ambient, charger, and power-line noise

- Up to 240  $V_{PP}$  between 1 Hz and 1 kHz sinusoidal waveform

- Up to 20 V<sub>PP</sub> between 1 kHz and 1 MHz sinusoidal waveform

- Burst Frequency

- Controlled Tx burst frequency drift over process and temperature range

- Scan Speed

- Configurable to allow for power and speed optimization

- · Touch panel failure detection

- Automatic touch sensor diagnostics during run time to support the implementation of safety critical features

- Diagnostics reported using dedicated output pin or by standard Object Protocol messages

- Configurable test limits

#### **Enhanced Algorithms**

- · Lens bending algorithms to remove display noise

- Touch suppression algorithms to remove unintentional large touches, such as palm

- Palm Recovery Algorithm for quick restoration to normal state

#### **Power Saving**

- Programmable timeout for automatic transition from Active to Idle state

- Pipelined analog sensing detection and digital processing to optimize system power efficiency

#### **Application Interfaces**

I<sup>2</sup>C slave with support for Standard mode (up to 100 kHz), Fast mode (up to 400 kHz)

# **mXT336UD-MAUHA1 1.0**

- Interrupt to indicate when a message is available

- Additional SPI Debug Interface to read the raw data for tuning and debugging purposes

### **Power Supply**

- Digital (Vdd) 3.3V nominal

- Digital I/O (VddIO) 3.3V nominal

- Analog (AVdd) 3.3V nominal

- High voltage internal X line drive (XVdd) 6.6 V with internal voltage pump (XVdd connected to Vdd if voltage pump not used)

### **Package**

• 56-pin XQFN 6 x 6 x 0.4 mm, 0.35 mm pitch

### **Operating Temperature**

• -40°C to +85°C

#### **Design Services**

- · Review of device configuration, stack-up and sensor patterns

- · Custom firmware versions can be considered

- Contact your Microchip representative for more information

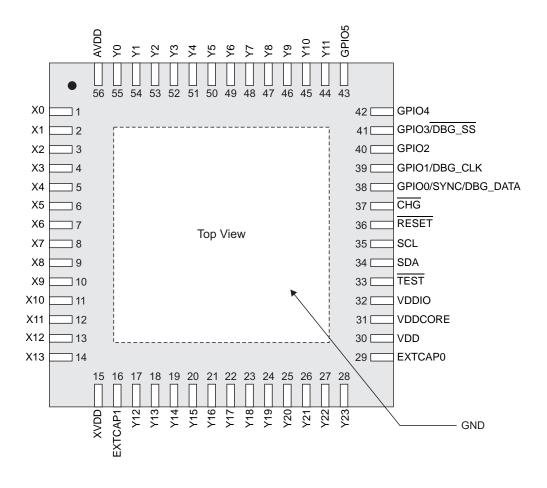

### **PIN CONFIGURATION**

# Pin Configuration - 56-pin XQFN

TABLE 1: PIN LISTING - 56-PIN XQFN

| IADLE | I: PIN LIST | 110 50 | <del></del> | Ş1 IV                                                                                                                           |                  |

|-------|-------------|--------|-------------|---------------------------------------------------------------------------------------------------------------------------------|------------------|

| Pin   | Name        | Туре   | Supply      | Description                                                                                                                     | If Unused        |

| 1     | X0          | S      | XVdd        | X line connection                                                                                                               | Leave open       |

| 2     | X1          | S      | XVdd        | X line connection                                                                                                               | Leave open       |

| 3     | X2          | S      | XVdd        | X line connection                                                                                                               | Leave open       |

| 4     | Х3          | S      | XVdd        | X line connection                                                                                                               | Leave open       |

| 5     | X4          | S      | XVdd        | X line connection                                                                                                               | Leave open       |

| 6     | X5          | S      | XVdd        | X line connection                                                                                                               | Leave open       |

| 7     | X6          | S      | XVdd        | X line connection                                                                                                               | Leave open       |

| 8     | X7          | S      | XVdd        | X line connection                                                                                                               | Leave open       |

| 9     | X8          | S      | XVdd        | X line connection                                                                                                               | Leave open       |

| 10    | Х9          | S      | XVdd        | X line connection                                                                                                               | Leave open       |

| 11    | X10         | S      | XVdd        | X line connection                                                                                                               | Leave open       |

| 12    | X11         | S      | XVdd        | X line connection                                                                                                               | Leave open       |

| 13    | X12         | S      | XVdd        | X line connection                                                                                                               | Leave open       |

| 14    | X13         | S      | XVdd        | X line connection                                                                                                               | Leave open       |

| 15    | XVDD        | Р      | _           | X line drive power                                                                                                              | _                |

| 16    | EXTCAP1     | Р      | _           | Voltage doubler – connect to EXTCAP0 via capacitor; see Section 2.2.5 "XVdd"                                                    | Leave open       |

| 17    | Y12         | S      | AVdd        | Y line connection                                                                                                               | Leave open       |

| 18    | Y13         | S      | AVdd        | Y line connection                                                                                                               | Leave open       |

| 19    | Y14         | S      | AVdd        | Y line connection                                                                                                               | Leave open       |

| 20    | Y15         | S      | AVdd        | Y line connection                                                                                                               | Leave open       |

| 21    | Y16         | S      | AVdd        | Y line connection                                                                                                               | Leave open       |

| 22    | Y17         | S      | AVdd        | Y line connection                                                                                                               | Leave open       |

| 23    | Y18         | S      | AVdd        | Y line connection                                                                                                               | Leave open       |

| 24    | Y19         | S      | AVdd        | Y line connection                                                                                                               | Leave open       |

| 25    | Y20         | S      | AVdd        | Y line connection                                                                                                               | Leave open       |

| 26    | Y21         | S      | AVdd        | Y line connection                                                                                                               | Leave open       |

| 27    | Y22         | S      | AVdd        | Y line connection                                                                                                               | Leave open       |

| 28    | Y23         | S      | AVdd        | Y line connection                                                                                                               | Leave open       |

| 29    | EXTCAP0     | Р      | -           | Voltage doubler – connect to EXTCAP1 via capacitor; see Section 2.2.5 "XVdd"                                                    | Leave open       |

| 30    | VDD         | Р      | _           | Digital power                                                                                                                   | _                |

| 31    | VDDCORE     | Р      | -           | Digital core power                                                                                                              |                  |

| 32    | VDDIO       | Р      | _           | Digital IO interface power                                                                                                      | _                |

| 33    | TEST        | _      | VddIO       | Reserved for factory use; pull up to VddlO                                                                                      | _                |

| 34    | SDA         | OD     | VddIO       | I <sup>2</sup> C Serial Data                                                                                                    |                  |

| 35    | SCL         | OD     | VddIO       | I <sup>2</sup> C Serial Clock –                                                                                                 |                  |

| 36    | RESET       | I      | VddIO       | Reset low. Pull up to VddIO. Connection to host system is recommended                                                           | Pull up to VddIO |

| 37    | CHG         | OD     | VddIO       | State change interrupt. Pull up to VddIO  Note: Briefly set (~100 ms) as an input after power-up/ reset for diagnostic purposes | -                |

TABLE 1: PIN LISTING – 56-PIN XQFN (CONTINUED)

| Pin | Name     | Туре | Supply | Description                                           | If Unused                                   |

|-----|----------|------|--------|-------------------------------------------------------|---------------------------------------------|

|     | GPIO0    | I/O  |        | General purpose IO; see Section 2.2.9 "GPIO Pins" (1) | Connect to test point                       |

| 38  | SYNC     | I    | VddIO  | External synchronization: (VSync or HSync)            | Input: Connect to GND                       |

|     | DBG_DATA | 0    |        | Debug Data                                            | Output: Leave open                          |

|     | GPIO1    | I/O  |        | General purpose IO; see Section 2.2.9 "GPIO Pins" (1) | Connect to test point                       |

| 39  | DBG_CLK  | 0    | VddIO  | Debug Clock                                           | Input: Connect to GND Output: Leave open    |

| 40  | GPIO2    | I/O  | Vdd    | General purpose IO; see Section 2.2.9 "GPIO Pins" (1) | Input: Connect to GND<br>Output: Leave open |

|     | GPIO3    | I/O  |        | General purpose IO; see Section 2.2.9 "GPIO Pins" (1) | Connect to test point                       |

| 41  | DBG_SS   | 0    | Vdd    | Debug SS line                                         | Input: Connect to GND Output: Leave open    |

| 42  | GPIO4    | I/O  | Vdd    | General purpose IO; see Section 2.2.9 "GPIO Pins" (1) | Input: Connect to GND<br>Output: Leave open |

| 43  | GPIO5    | I/O  | Vdd    | General purpose IO; see Section 2.2.9 "GPIO Pins" (1) | Input: Connect to GND<br>Output: Leave open |

| 44  | Y11      | S    | AVdd   | Y line connection                                     | Leave open                                  |

| 45  | Y10      | S    | AVdd   | Y line connection                                     | Leave open                                  |

| 46  | Y9       | S    | AVdd   | Y line connection                                     | Leave open                                  |

| 47  | Y8       | S    | AVdd   | Y line connection                                     | Leave open                                  |

| 48  | Y7       | S    | AVdd   | Y line connection                                     | Leave open                                  |

| 49  | Y6       | S    | AVdd   | Y line connection                                     | Leave open                                  |

| 50  | Y5       | S    | AVdd   | Y line connection                                     | Leave open                                  |

| 51  | Y4       | S    | AVdd   | Y line connection                                     | Leave open                                  |

| 52  | Y3       | S    | AVdd   | Y line connection                                     | Leave open                                  |

| 53  | Y2       | S    | AVdd   | Y line connection                                     | Leave open                                  |

| 54  | Y1       | S    | AVdd   | Y line connection                                     | Leave open                                  |

| 55  | Y0       | S    | AVdd   | Y line connection                                     | Leave open                                  |

| 56  | AVDD     | Р    | _      | Analog power                                          | -                                           |

| Pad | GND      | Р    | -      | Exposed pad must be connected to GND                  |                                             |

Note 1: Use of the GPIO pin not supported for functional safety purposes under IEC/UL 60730 Class B.

Key:

#### 1.0 OVERVIEW OF MXT336UD-MAUHA1

The Microchip maXTouch family of touch controllers brings industry-leading capacitive touch performance to customer applications. The mXT336UD-MAUHA1 features the latest generation of Microchip adaptive sensing technology that utilizes a hybrid mutual and self capacitive sensing system in order to deliver unparalleled touch features and a robust user experience.

- Patented capacitive sensing method The mXT336UD-MAUHA1 uses a unique charge-transfer acquisition engine to implement Microchip's patented capacitive sensing method. Coupled with a state-of-the-art CPU, the entire touchscreen sensing solution can measure, classify and track a number of individual finger touches with a high degree of accuracy in the shortest response time.

- Capacitive Touch Engine (CTE) The mXT336UD-MAUHA1 features an acquisition engine that uses an optimal

measurement approach to ensure almost complete immunity from parasitic capacitance on the receiver input

lines. The engine includes sufficient dynamic range to cope with anticipated touchscreen self and mutual

capacitances, which allows great flexibility for use with the Microchip proprietary sensor pattern designs. One- and

two-layer ITO sensors are possible using glass or PET substrates.

- Touch detection The mXT336UD-MAUHA1 allows for both mutual and self capacitance measurements, with the self capacitance measurements being used to augment the mutual capacitance measurements to produce reliable touch information.

When self capacitance measurements are enabled, touch classification is achieved using both mutual and self capacitance touch data. This has the advantage that both types of measurement systems can work together to detect touches under a wide variety of circumstances.

The system may be configured for different types of default measurements in both idle and active modes. For example, the device may be configured for Mutual Capacitance Touch as the default in active mode and Self Capacitance Touch as the default in idle mode. Note that other types of scans (such as P2P mutual capacitance scans and other types of self capacitance scans) may also be made depending on configuration.

Mutual capacitance touch data is used wherever possible to classify touches as this has a greater resolution than self capacitance measurements and provides positional information on touches. For this reason, multiple touches can only be determined by mutual capacitance touch data. In Self Capacitance Touch Default mode, if the self capacitance touch processing detects multiple touches, touchscreen processing is skipped until mutual capacitance touch data is available.

Self capacitance and P2P mutual capacitance measurements allow for the detection of touches in extreme scenarios, such as thick glove touches, when mutual capacitance touch detection alone may miss touches.

- **Display Noise Cancellation** A combination of analog circuitry, hardware noise processing, and firmware combats display noise without requiring additional listening channels or synchronization to display timing. This enables the use of shieldless touch sensor stacks, including touch-on-lens.

- Noise filtering Hardware noise processing in the capacitive touch engine provides enhanced autonomous

filtering and allows a broad range of noise profiles to be handled. The result is good performance in the presence

of LCD noise.

- **Processing power** The main CPU has two companion microsequencer coprocessors under its control consuming low power. This system allows the signal acquisition, preprocessing and postprocessing to be partitioned in an efficient and flexible way.

- Interpreting user intention The Microchip hybrid mutual and self capacitance method provides unambiguous

multitouch performance. Algorithms in the mXT336UD-MAUHA1 provide optimized touchscreen position filtering

for the smooth tracking of touches, responding to a user's intended touches while preventing false touches

triggered by ambient noise, conductive material on the sensor surface, such as moisture, or unintentional touches

from the user's resting palm or fingers.

- Functional Safety The device is designed with functional safety applications in mind (for example, for the home appliance market). Specifically, the device complies with the IEC/UL 60730 standard for Class B safety specification:

- Self diagnostics at power-on and Periodic testing during operation to detect faults for immediate action by the host system (see Table 1-1)

- Heartbeat (alive) signal output to host

- Enhanced I<sup>2</sup>C communications for error detection and reporting

TABLE 1-1: FUNCTIONAL SAFETY TESTS

| Tests                                  | Power-on Test (POST) | Periodic Runtime Test (BIST) |

|----------------------------------------|----------------------|------------------------------|

| CPU register tests                     | Yes                  | Yes                          |

| Missing and unexpected interrupt tests | Yes                  | Yes                          |

| Internal clock tests                   | Yes                  | Yes                          |

| Flash memory tests                     | Yes                  | Yes                          |

| RAM tests                              | Yes                  | Yes                          |

| Factory data                           | Yes                  | Yes                          |

| Software related tests (1)             | Yes                  | Yes                          |

| Brown-out detection (BOD) tests        | Yes                  | -                            |

| Analog and digital front-end tests (2) | -                    | Yes                          |

| Signal Limit and Pin Fault tests (2)   | _                    | Yes                          |

Note 1: Includes flow execution tests (specifically, all safety-related modules are executed).

<sup>2:</sup> Several tests detect both internal and external defects, including a number of touch sensor faults.

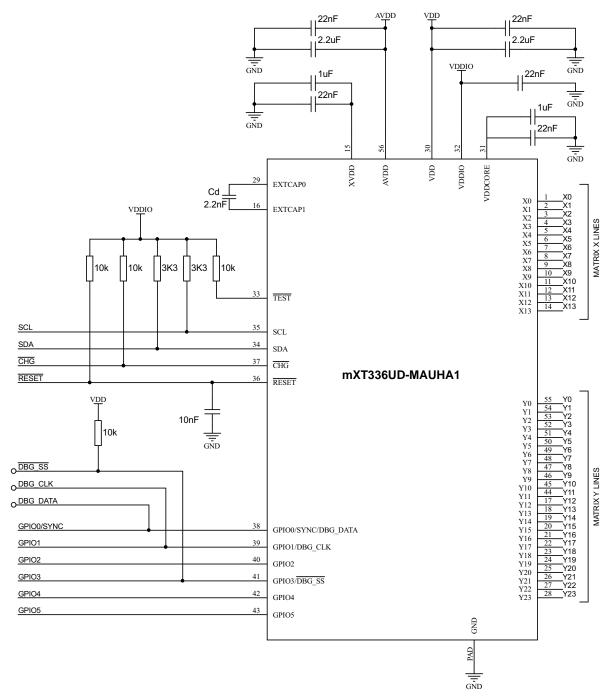

### 2.0 SCHEMATIC

### 2.1 56-pin XQFN

#### Notes:

- The schematic shown assumes that the voltage doubler is used. If low voltage operation is required, capacitor Cd must be omitted (see Section 2.2.5 "XVdd")

- 2. See "Pin configuration" for information on I/O pin supply

- 3. See Section 2.2 "Schematic Notes"

#### 2.2 Schematic Notes

#### 2.2.1 POWER SUPPLY

The sense and I/O pins are supplied by the power rails on the device as listed in Table 2-1. This information is also indicated in "Pin configuration".

TABLE 2-1: POWER SUPPLY FOR SENSE AND I/O PINS

| Power Supply | Pins                                                             |

|--------------|------------------------------------------------------------------|

| XVdd         | X sense pins                                                     |

| AVdd         | Y sense pins                                                     |

| Vdd          | GPIO2, GPIO3/DBG_SS, GPIO4, GPIO5                                |

| VddIO        | RESET, TEST, CHG<br>SCL, SDA, GPIO0/SYNC/DBG_DATA, GPIO1/DBG_CLK |

#### 2.2.2 DECOUPLING CAPACITORS

All decoupling capacitors must be X7R or X5R and placed less than 5 mm away from the pins for which they act as bypass capacitors. Pins of the same type can share a capacitor provided no pin is more than 10 mm from the capacitor.

The schematics on the previous pages show the capacitors required. The parallel combination of capacitors is recommended to give high and low frequency filtering, which is beneficial if the voltage regulators are likely to be some distance from the device (for example, If an active tail design is used). Note that this requires that the voltage regulator supplies for AVdd, Vdd and VddIO are clean and noise free. It also assumes that the track length between the capacitors and on-board power supplies is less than 50 mm.

The number of base capacitors can be reduced if the pinout configuration means that sharing a bypass capacitor is possible (subject to the distance between the pins satisfying the conditions above and there being no routing difficulties).

#### 2.2.3 PULL-UP RESISTORS

The pull-up resistors shown in the schematic are suggested typical values and may be modified to meet the requirements of an individual customer design.

This applies, in particular, to the pull-up resistors on the I<sup>2</sup>C SDA and SCL lines (shown on the schematic), as the values of these resistors depend on the speed of the I<sup>2</sup>C interface. See Section 7.6 "I2C Specification" for details.

Note that if a VddIO supply at the low end of the allowable range is used, the I<sup>2</sup>C pull-up resistor values may need to be reduced.

#### 2.2.4 VDDCORE

VddCore is internally generated from the Vdd power supply. To guarantee stability of the internal voltage regulator, one or more external decoupling capacitors are required.

#### 2.2.5 XVDD

XVdd power can be supplied either as high voltage (using an internal voltage pump) or as low voltage (connected directly to the Vdd supply). The operating mode should be chosen according to the final application.

The voltage pump requires one external capacitor:

- EXTCAP0 must be connected to EXTCAP1 via a capacitor (Cd). The capacitor must be placed as close as possible to the EXTCAP*n* pins.

- The capacitor on XVDD should be rated at least 10 V if the voltage doubler is used.

Capacitor Cd should provide a capacitance of 2.2 nF.

If low voltage XVdd is required (that is, the XVdd voltage doubler is not required):

- Capacitor Cd must be omitted and EXTCAP0 and EXTCAP1 left unconnected.

- · XVDD must be connected directly to the Vdd supply.

**CAUTION!** The device may be permanently damaged if the XVDD supply pin is shorted to Ground or high current is drawn from it.

### **mXT336UD-MAUHA1 1.0**

#### 2.2.6 AVDD

A diode from AVDD to VDD is present in the device. If AVDD and VDD are driven from different supplies, the Vdd supply must be powered up earlier than AVdd.

#### 2.2.7 MULTIPLE FUNCTION PINS

Some pins may have multiple functions. In this case, only one function can be chosen and the circuit should be designed accordingly.

#### 2.2.8 SYNC PIN

The mXT336UD-MAUHA1 has a single SYNC pin that can be used for either frame synchronization or pulse synchronization, but not both.

IMPORTANT! Use of the SYNC pin is not covered for functional safety purposes under IEC/UL 60730 Class B.

#### 2.2.9 GPIO PINS

The mXT336UD-MAUHA1 has 6 GPIO pins. The pins can be set to be either an input or an output, as required, using the GPIO Configuration T19 object.

**IMPORTANT!** Use of the GPIO pins is not covered for functional safety purposes under IEC/UL 60730 Class B.

If a GPIO pin is unused, it can be left unconnected externally as long as it is given a defined state by the GPIO Configuration T19 object.

By default the GPIO pins are set to be inputs so if a pin is not used, and is left configured as an input, it should be connected to GND through a resistor or else the internal resistor should be pulled up using the GPIO Configuration T19 object. Note that this does not apply if the GPIO pin is shared with a debug line; see Section 2.2.10 "SPI Debug Interface" for advice on how to treat an unused GPIO pin in this case.

Alternatively, the GPIO pin can be set as an output low using the GPIO Configuration T19 object and left open. This second option avoids any problems should the pin accidentally be configured as output high at a later date.

If the GPIO Configuration T19 object is not enabled for use, the GPIO pins cannot be used for GPIO purposes, although any alternative function can still be used.

Some GPIO pins have alternative functions. If an alternative function is used then this takes precedence over the GPIO function and the pin cannot be used as a GPIO pin. In particular:

- · GPIO0 cannot be used if the SYNC function is in use.

- The SPI Debug Interface functionality is shared with some of the GPIO pins. See Section 2.2.10 "SPI Debug Interface" for more details on the SPI Debug Interface and how to handle these pins if they are totally unused.

### 2.2.10 SPI DEBUG INTERFACE

**IMPORTANT!** Use of the SPI Debug Interface is not covered for functional safety purposes under IEC/UL 60730 Class B.

The DBG\_CLK, DBG\_DATA and DBG\_SS lines form the SPI Debug Interface. These pins should be routed to test points on all designs, such that they can be connected to external hardware during system development and for debug purposes. See also Section 6.1 "SPI Debug Interface".

The debug lines may share pins with other functionality. If the circuit is designed to use the SPI Debug Interface, then any alternative functionality cannot be used. Specifically:

- The DBG\_CLK line shares functionality with GPIO1; therefore GPIO1 cannot be used if the SPI Debug Interface is

in use.

- The DBG\_DATA line shares functionality with GPIO0; therefore GPIO0 cannot be used if the SPI Debug Interface

is in use.

- The DBG\_SS line shares functionality with GPIO3, so GPIO3 cannot be used.

- The pull-up resistor for DBG\_SS in the schematics is optional and should be present only if the line is used as DBG\_SS.

# **mXT336UD-MAUHA1 1.0**

The DBG\_CLK, DBG\_DATA and  $\overline{DBG_SS}$  lines should not be connected to power or GND. For this reason, where these pins are shared with GPIO pins and they are totally unused (that is, they are not being used as debug or GPIO pins), they should be set as outputs using the GPIO Configuration T19 object.

#### 3.0 SENSOR LAYOUT

| NOTE | The specific electrode designs used in Microchip touchscreens may be the subject of various patents and |

|------|---------------------------------------------------------------------------------------------------------|

|      | patent applications. Further information is available on request.                                       |

| IMPORTANT | The device is currently under development. Functionality described here may be subject to change or is not yet implemented. |

|-----------|-----------------------------------------------------------------------------------------------------------------------------|

|           | You are advised to consult Microchip concerning any designs based on the information below                                  |

#### 3.1 Electrodes

The device supports various configurations of touch electrodes as summarized below:

• Touchscreen: 1 touchscreen panel occupies a rectangular matrix of up to 14 X x 24 Y lines maximum (subject to other configurations).

### 3.2 Sensor Matrix Layout

When designing the physical layout of the touch panel, the following rules must be obeyed:

- · General layout rules:

- The Multiple Touch Touchscreen T100 object should be a regular rectangular shape in terms of the lines it uses.

- Additional layout rules for Multiple Touch Touchscreen T100:

- The Multiple Touch Touchscreen T100 object *must* start at (X0, Y0).

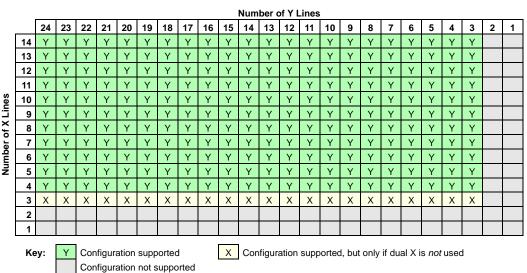

- For mutual capacitance measurements (see Table 3-1):

The touchscreen must contain a minimum of 3 X lines. If Dual X Drive is enabled for use in the Noise Suppression T72 object, the minimum is 4 X lines.

The touchscreen must contain a minimum of 3 Y lines.

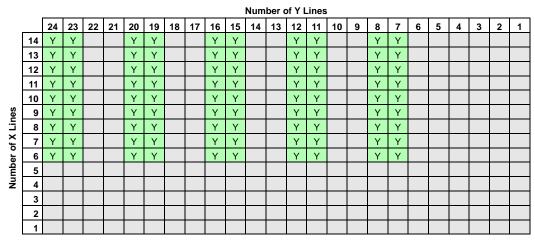

- For self capacitance measurements (see Table 3-2):

The touchscreen must contain a minimum of 6 X lines.

The number of Y lines must be one of 24, 23, 20, 19, 16, 15, 12, 11, 8 or 7.

#### 3.2.1 PERMITTED CONFIGURATIONS

The permitted X/Y configurations are shown in Table 3-1 and Table 3-2.

TABLE 3-1: PERMITTED TOUCHSCREEN CONFIGURATIONS – MUTUAL CAPACITANCE SENSING

Advance Information – Under NDA

TABLE 3-2: PERMITTED TOUCHSCREEN CONFIGURATIONS – SELF CAPACITANCE SENSING

Key: Y Configuration supported

Configuration not supported

### 3.3 Screen Size

Table 3-3 lists some typical screen size and electrode pitch combinations to achieve various aspect ratios.

TABLE 3-3: TYPICAL SCREEN SIZES

|              |                |            | Screen Diagonal (Inches) |              |              |  |  |

|--------------|----------------|------------|--------------------------|--------------|--------------|--|--|

| Aspect Ratio | Matrix Size    | Node Count | 4.5 mm Pitch             | 5.5 mm Pitch | 6.5 mm Pitch |  |  |

| 16:10        | X = 14, Y = 23 | 322        | 4.77                     | 5.83         | 6.89         |  |  |

| 16:9         | X = 14, Y = 24 | 336        | 4.92                     | 6.02         | 7.11         |  |  |

| 4:3          | X = 14, Y = 20 | 280        | 4.18                     | 5.11         | 6.04         |  |  |

| 2:1          | X = 12, Y = 24 | 288        | 4.75                     | 5.81         | 6.87         |  |  |

**Note** 1: The figures given in the table are for a Touchscreen and show the largest node count possible to achieve the desired aspect ratio.

#### 4.0 POWER-UP / RESET REQUIREMENTS

#### 4.1 Power-on Reset

There is an internal Power-on Reset (POR) in the device.

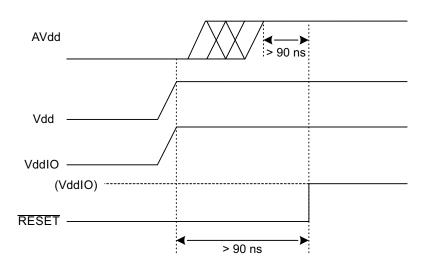

If an external reset is to be used the device must be held in RESET (active low) while the digital (Vdd), analog (AVdd) and digital I/O (VddIO) power supplies are powering up. The supplies must have reached their nominal values before the RESET signal is deasserted (that is, goes high). This is shown in Figure 4-1. See Section 7.2 "Recommended Operating Conditions" for nominal values for the power supplies to the device.

A diode from AVDD to VDD is present in the device. If AVDD and VDD are driven from different supplies, the Vdd supply must be powered up earlier than AVdd.

FIGURE 4-1: POWER SEQUENCING ON THE MXT336UD-MAUHA1

Note: When using external RESET at power-up, VddIO must not be enabled after Vdd

It is recommended that customer designs include the capability for the host to control all the maXTouch power supplies and pull the RESET line low.

After power-up, the device typically takes TBD ms before it is ready to start communications.

**NOTE** Device initialization will not complete until after all the power supplies are present. If any power supply is not present, internal initialization stalls and the device will not communicate with the host.

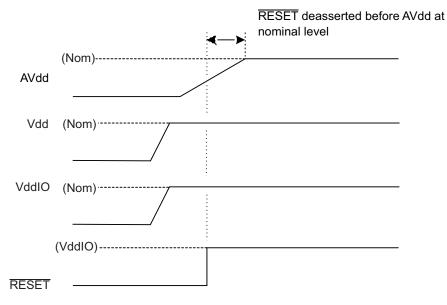

If the RESET line is released before the AVdd supply has reached its nominal voltage (see Figure 4-2), then some additional operations need to be carried out by the host. There are two options open to the host controller:

- Start the part in Deep Sleep mode and then send the command sequence to set the cycle time to wake the part and allow it to run normally. Note that in this case a calibration command is also needed.

- Send a RESET command.

### FIGURE 4-2: POWER SEQUENCING ON THE MXT336UD-MAUHA1 – LATE RISE ON AVDD

The RESET pin can be used to reset the device whenever necessary. The RESET pin must be asserted low for at least 90 ns to cause a reset. After the host has released the RESET pin, the device typically takes TBD ms before it is ready to start communications. It is recommended to connect the RESET pin to a host controller to allow the host to initiate a full hardware reset without requiring the mXT336UD-MAUHA1 to be powered down.

WARNING

The device should be reset only by using the RESET line. If an attempt is made to reset by removing the power from the device without also sending the signal lines low, power will be drawn from the communication and I/O lines and the device will not reset correctly.

Make sure that any lines connected to the device are below or equal to Vdd during power-up and power-down. For example, if RESET is supplied from a different power domain to the VDDIO pin, make sure that it is held low when Vdd is off. If this is not done, the RESET signal could parasitically couple power via the RESET pin into the Vdd supply.

NOTE The voltage level on the RESET pin of the device must never exceed VddIO (digital supply voltage).

A software RESET command (using the Command Processor T6 object) can be used to reset the chip. A software reset typically takes TBD ms. After the chip has finished it asserts the CHG line to signal to the host that a message is available. The reset flag is set in the Command Processor T6 object message data to indicate to the host that it has just completed a reset cycle. This bit can be used by the host to detect any unexpected brownout events. This allows the host to take any necessary corrective actions, such as reconfiguration.

**NOTE**

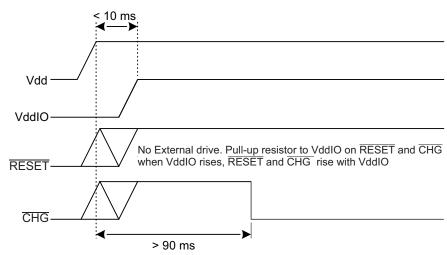

The  $\overline{\text{CHG}}$  line is briefly set (~100 ms) as an input during power-up or reset. It is therefore particularly important that the line should be allowed to float high via the  $\overline{\text{CHG}}$  line pull-up resistor during this period. It should never be driven by the host.

At power-on, the device performs a self-test routine (using the Self Test T25 object) to check for shorts that might cause damage to the device.

#### 4.2 Power-up and Reset Sequence – VddIO Enabled after Vdd

The power-up sequence that can be used in applications where VddIO must be powered up after Vdd, is shown in Figure 4-3.

In this case the communication interface to the maXTouch device is not driven by the host system. The RESET and CHG pins are connected to VddIO using suitable pull-up resistors. Vdd is powered up, followed by VddIO, no more than 10 ms after Vdd. Due to the pull-up resistors, RESET and CHG will rise with VddIO. The internal POR system ensures reliable boot up of the device and the CHG line will go low approximately TBD ms after Vdd to notify the host that the device is ready to start communication.

FIGURE 4-3: POWER-UP SEQUENCE

#### 5.0 PCB DESIGN CONSIDERATIONS

#### 5.1 Introduction

The following sections give the design considerations that should be adhered to when designing a PCB layout for use with the mXT336UD-MAUHA1. Of these, power supply and ground tracking considerations are the most critical.

By observing the following design rules, and with careful preparation for the PCB layout exercise, designers will be assured of a far better chance of success and a correctly functioning product.

#### 5.2 Printed Circuit Board

Microchip recommends the use of a four-layer printed circuit board for mXT336UD-MAUHA1 applications. This, together with careful layout, will ensure that the board meets relevant EMC requirements for both noise radiation and susceptibility, as laid down by the various national and international standards agencies.

#### 5.2.1 PCB CLEANLINESS

Modern no-clean-flux is generally compatible with capacitive sensing circuits.

CAUTION

If a PCB is reworked to correct soldering faults relating to any device, or to any associated traces or components, be sure that you fully understand the nature of the flux used during the rework process. Leakage currents from hygroscopic ionic residues can stop capacitive sensors from functioning. If you have any doubts, a thorough cleaning after rework may be the only safe option.

### 5.3 Power Supply

#### 5.3.1 SUPPLY QUALITY

While the device has good Power Supply Rejection Ratio properties, poorly regulated and/or noisy power supplies can significantly reduce performance.

Particular care should be taken of the AVdd supply, as it supplies the sensitive analog stages in the device.

#### 5.3.2 SUPPLY RAILS AND GROUND TRACKING

Power supply and clock distribution are the most critical parts of any board layout. Because of this, it is advisable that these be completed before any other tracking is undertaken. After these, supply decoupling, and analog and high speed digital signals should be addressed. Track widths for all signals, especially power rails should be kept as wide as possible in order to reduce inductance.

The Power and Ground planes themselves can form a useful capacitor. Flood filling for either or both of these supply rails, therefore, should be used where possible. It is important to ensure that there are no floating copper areas remaining on the board: all such areas should be connected to the ground plane. The flood filling should be done on the outside layers of the board.

### 5.3.3 POWER SUPPLY DECOUPLING

Decoupling capacitors should be fitted as specified in Section 2.2 "Schematic Notes".

The decoupling capacitors must be placed as close as possible to the pin being decoupled. The traces from these capacitors to the respective device pins should be wide and take a straight route. They should be routed over a ground plane as much as possible. The capacitor ground pins should also be connected directly to a ground plane.

Surface mounting capacitors are preferred over wire-leaded types due to their lower ESR and ESL. It is often possible to fit these decoupling capacitors underneath and on the opposite side of the PCB to the digital ICs. This will provide the shortest tracking, and most effective decoupling possible.

#### 5.3.4 VOLTAGE PUMP

The traces for the voltage pump capacitor between EXTCAP0 and EXTCAP1 (Cd on the schematic in Section 2.0 "Schematic") should be kept as short and as wide as possible for best pump performance. They should also be routed as parallel and as close as possible to each other in order to reduce emissions, and ideally the traces should be the same length.

#### 5.3.5 VOLTAGE REGULATORS

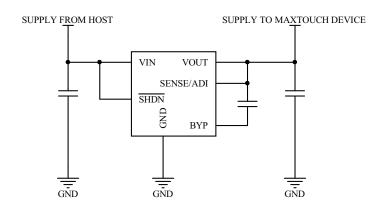

Each supply rail requires a Low Drop-Out (LDO) voltage regulator, although an LDO can be shared where supply rails share the same voltage level.

Figure 5-1 shows an example circuit for an LDO.

FIGURE 5-1: EXAMPLE LDO CIRCUIT

An LDO regulator should be chosen that provides adequate output capability, low noise, good load regulation and step response. The voltage regulators listed in Table 5-1 have been tested and found to work well with maXTouch devices. If it is desired to use an alternative LDO, however, certain performance criteria should be verified before using the device. These are:

- Stable with high value multi-layer ceramic capacitors on the output

- Low output noise ideally less than 100  $\mu V_{RMS}$  over the range 10 Hz to 1 MHz

- Good load transient response this should be less than 35 mV peak when a load step change of 100 mA is applied at the device output terminal

- No-load stable Some LDOs become unstable if the output current falls below a certain minimum. If this is the

case, then this minimum must be lower than the minimum current consumed by the mXT336UD-MAUHA1 (for

example, in deep sleep).

TABLE 5-1: SUITABLE LDO REGULATORS

| Manufacturer              | Device   | Current Rating (mA) |

|---------------------------|----------|---------------------|

| Microchip Technology Inc. | MCP1824  | 300                 |

| Microchip Technology Inc. | MCP1824S | 300                 |

| Microchip Technology Inc. | MAQ5300  | 300                 |

| Microchip Technology Inc. | MCP5504  | 300                 |

| Microchip Technology Inc. | MCP1725  | 500                 |

| Microchip Technology Inc. | MIC5514  | 300                 |

| Microchip Technology Inc. | MIC5323  | 300                 |

Note:

Some manufacturers claim that minimal or no capacitance is required for correct regulator operation. However, in all cases, a minimum of a 1.0  $\mu$ F ceramic, low ESR capacitor at the input and output of these devices should be used. The manufacturer's datasheets should always be referred to when selecting capacitors for these devices and the typical recommended values, types and dielectrics adhered to.

#### 5.3.6 SINGLE SUPPLY OPERATION

When designing a PCB for an application using a single LDO, extra care should be taken to ensure short, low inductance traces between the supply and the touch controller supply input pins. Ideally, tracking for the individual supplies should be arranged in a star configuration, with the LDO at the junction of the star. This will ensure that supply current variations or noise in one supply rail will have minimum effect on the other supplies. In applications where a ground plane is not practical, this same star layout should also apply to the power supply ground returns.

Only regulators with a 300 mA or greater rating can be used in a single-supply design.

Refer to the following application note for more information:

Application Note: MXTAN0208 – Design Guide for PCB Layouts for maXTouch Touch Controllers

#### 5.3.7 MULTIPLE VOLTAGE REGULATOR SUPPLY

The AVdd supply stability is critical for the device because this supply interacts directly with the analog front end. If noise problems exist when using a single LDO regulator, Microchip recommends that AVdd is supplied by a regulator that is separate from the digital supply. This reduces the amount of noise injected into the sensitive, low signal level parts of the design.

#### 5.4 Guard Track

A guard track (Ground) should be routed between the X and Y tracks, as well as between the X/Y tracks and Ground. It should be fairly wide to avoid X-to-Y coupling in mutual capacitance operation.

A guard track is also needed between any self capacitance X/Y lines and mutual capacitance only X/Y lines.

### 5.5 ESD Ground Routing

To avoid damage due to ESD strikes, the outermost track on the sensor should be an ESD ground. This should completely surround the sensor but with an overlap at the top rather than forming a complete loop.

The ESD ground traces should be connected to a dedicated ground trace in the PCB, and routed such that ESD strike currents do not flow under or close to the touch controller or the connecting wiring between it and the touchscreen array. The ESD ground should be connected in to the main system ground at a star point at the main GND connection to the PCB.

See also:

MXTAN0208 – Design guide for PCB Layouts for maXTouch Touch Controllers

### 5.6 Analog I/O

In general, tracking for the analog I/O signals from the device should be kept as short as possible. These normally go to a connector which interfaces directly to the touchscreen.

Ensure that adequate ground-planes are used. An analog ground plane should be used in addition to a digital one. Care should be taken to ensure that both ground planes are kept separate and are connected together only at the point of entry for the power to the PCB. This is usually at the input connector.

#### 5.7 Component Placement and Tracking

It is important to orient all devices so that the tracking for important signals (such as power and clocks) are kept as short as possible.

#### 5.7.1 DIGITAL SIGNALS

In general, when tracking digital signals, it is advisable to avoid sharp directional changes on sensitive signal tracks (such as analog I/O) and any clock or crystal tracking.

A good ground return path for all signals should be provided, where possible, to ensure that there are no discontinuities.

#### 5.7.2 QFN PACKAGE RESTRICTIONS

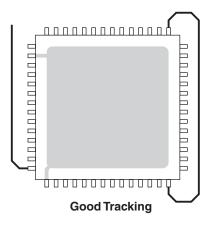

The central pad on the underside of the QFN device should be connected to ground. Do not run any tracks underneath the body of the device on the top layer of the PCB, only ground. Figure 5-2 shows examples of good and bad tracking.

#### FIGURE 5-2: EXAMPLES OF GOOD AND BAD TRACKING

Note: The number of pins and their functions is shown for example purposes only and may not reflect the actual number or function on the device.

#### 5.8 EMC and Other Observations

The following recommendations are not mandatory, but may help in situations where particularly difficult EMC or other problems are present:

- Try to keep as many signals as possible on the inside layers of the board. If suitable ground flood fills are used on

the top and bottom layers, these will provide a good level of screening for noisy signals, both into and out of the

PCB.

- Ensure that the on-board regulators have sufficient tracking around and underneath the devices to act as a heatsink. This heatsink will normally be connected to the 0 V or ground supply pin. Increasing the width of the copper tracking to any of the device pins will aid in removing heat. There should be no solder mask over the copper track underneath the body of the regulators.

- Ensure that the decoupling capacitors, especially high capacity ceramic type, have the requisite low ESR, ESL and good stability/temperature properties. Refer to the regulator manufacturer's datasheet for more information.

#### 6.0 DEBUGGING AND TUNING

### 6.1 SPI Debug Interface

The SPI Debug Interface is used for tuning and debugging when running the system and allows the development engineer to use Microchip maXTouch Studio to read the real-time raw data. This uses the low-level debug port.

The SPI Debug Interface consists of the DBG\_SS, DBG\_CLK, and DBG\_DATA lines. These lines should be routed to test points on all designs such that they can be connected to external hardware during system development. These lines should not be connected to power or GND. See Section 2.2.10 "SPI Debug Interface" for more details.

The SPI Debug Interface is enabled by the Command Processor T6 object and by default will be off.

NOTE The touch controller will take care of the pin configuration. When the DBG\_SS, DBG\_CLK, and DBG\_DATA lines are in use for debugging, any alternative function for the pins cannot be used.

#### 6.2 Object-based Protocol

The device provides a mechanism for obtaining debug data for development and testing purposes by reading data from the Diagnostic Debug T37 object.

NOTE The Diagnostic Debug T37 object is of most use for simple tuning purposes. When debugging a design, it is preferable to use the SPI Debug Interface, as this will have a much higher bandwidth and can provide real-time data.

#### 6.3 Self Test

There is a Self Test T25 object that runs self-test routines in the device to find hardware faults on the sense lines and the electrodes. This object also performs an initial pin fault test on power-up to ensure that there is no pin short (X to Y, or X lines to power or GND) before the high-voltage supply is enabled inside the chip. A high-voltage short on the sense lines could damage the device.

In addition to one-off hardware tests, the Self Test T25 object can also provide continuous monitoring of the health of the device while it is in operation. A periodic test can be run at a user-specified interval and reports pass and/or fail messages (as determined by the device configuration). Reporting is achieved either by standard Self Test T25 object protocol messages or by a dedicated hardware GPIO pin, configured using the GPIO Configuration T19 object.

**IMPORTANT!** For compliance with IEC/UL 60730 Class B safety specification, reporting should be achieved using Self Test T25 object protocol messages and not by a hardware GPIO pin.

### 7.0 SPECIFICATIONS

### 7.1 Absolute Maximum Specifications

| Vdd                                                     | 3.6V                                   |

|---------------------------------------------------------|----------------------------------------|

| VddIO                                                   | 3.6V                                   |

| AVdd                                                    | 3.6V                                   |

| Maximum continuous combined pin current, all GPIOn pins | 40 mA                                  |

| Voltage forced onto any pin                             | -0.3 V to (Vdd, VddIO or AVdd) + 0.3 V |

| Configuration parameters maximum writes                 | 10,000                                 |

| Maximum junction temperature                            | 125°C                                  |

### CAUTION!

Stresses beyond those listed under *Absolute Maximum Specifications* may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum specification conditions for extended periods may affect device reliability.

# 7.2 Recommended Operating Conditions

| Operating temperature                                         | -40°C to +85°C   |

|---------------------------------------------------------------|------------------|

| Storage temperature                                           | −60°C to +150°C  |

| Vdd                                                           | 3.3 V            |

| VddIO                                                         | 1.8 V to 3.3 V   |

| AVdd                                                          | 3.3 V            |

| XVdd with internal voltage doubler                            | 2 × Vdd          |

| XVdd low voltage operation (without internal voltage doubler) | Connected to Vdd |

| Temperature slew rate                                         | 10°C/min         |

#### 7.2.1 DC CHARACTERISTICS

### 7.2.1.1 Analog Voltage Supply – AVdd

| Parameter        | Min | Тур | Max   | Units | Notes                                                                             |

|------------------|-----|-----|-------|-------|-----------------------------------------------------------------------------------|

| AVdd             |     |     |       |       |                                                                                   |

| Operating limits | 3.0 | 3.3 | 3.47  | V     |                                                                                   |

| Supply Rise Rate | -   | _   | 0.036 | V/µs  | For example, for a 3.3 V rail, the voltage should take a minimum of 92 µs to rise |

### 7.2.1.2 Digital Voltage Supply – VddIO, Vdd

| Parameter        | Min      | Тур | Max   | Units | Notes                                                                             |

|------------------|----------|-----|-------|-------|-----------------------------------------------------------------------------------|

| VddIO            |          |     |       |       |                                                                                   |

| Operating limits | 1.71     | 3.3 | 3.47  | V     |                                                                                   |

| Supply Rise Rate | -        | -   | 0.036 | V/µs  | For example, for a 3.3 V rail, the voltage should take a minimum of 92 µs to rise |

| Vdd              | <u>.</u> | •   |       |       |                                                                                   |

| Operating limits | 2.7      | 3.3 | 3.47  | V     |                                                                                   |

| Supply Rise Rate | -        | _   | 0.036 | V/µs  | For example, for a 3.3 V rail, the voltage should take a minimum of 92 µs to rise |

| Supply Fall Rate | -        | -   | 0.05  | V/µs  | For example, for a 3.3 V rail, the voltage should take a minimum of 66 µs to fall |

### 7.2.1.3 XVdd Voltage Supply – XVdd

| Parameter                                   | Min | Тур     | Max | Units | Notes |

|---------------------------------------------|-----|---------|-----|-------|-------|

| XVdd                                        |     |         |     |       |       |

| Operating limits – voltage doubler enabled  |     | 2 × Vdd | -   | V     |       |

| Operating limits – voltage doubler disabled | _   | Vdd     | -   | V     |       |

### 7.2.2 POWER SUPPLY RIPPLE AND NOISE

| Parameter | Min | Тур | Max | Units | Notes                                                                      |

|-----------|-----|-----|-----|-------|----------------------------------------------------------------------------|

| Vdd       | _   | -   | ±50 | mV    | Across frequency range 1 Hz to 1 MHz                                       |

| AVdd      | -   | _   | ±40 | mV    | Across frequency range<br>1 Hz to 1 MHz, with Noise<br>Suppression enabled |

### 7.3 Timing Specifications

### 7.3.1 BURST FREQUENCY TOLERANCE

The burst frequency is directly correlated to the system clock. The burst frequency tolerance depends on the tolerance of the system's oscillator (see Table 7-1).

### TABLE 7-1: OSCILLATOR TOLERANCE

| Min Drift | Nominal             | Max Drift | Notes                                                                                           |

|-----------|---------------------|-----------|-------------------------------------------------------------------------------------------------|

| -5%       | 40 MHz (calibrated) | +5%       | Minimum/Maximum drift over temperature is specified as percentage below/above nominal frequency |

### 7.4 Touchscreen Sensor Characteristics

| Parameter | Description                           | Value                                                                    |  |  |

|-----------|---------------------------------------|--------------------------------------------------------------------------|--|--|

| Cm        | Mutual capacitance                    | Typical value is between 0.15 pF and 10 pF on a single node. Single node |  |  |

| Срх       | Mutual capacitance load to X          | Microchip recommends a maximum load of 300 pF on each X or Y line. (1)   |  |  |

|           | With Internal Voltage Pump            | Maximum recommended load on each X line: (2)                             |  |  |

|           |                                       | Cpx + (num_Y x Cm) < 240 pF                                              |  |  |

|           | With Internal Voltage Pump and Dual X | Maximum recommended load on each X line: (2)                             |  |  |

|           |                                       | $Cpx + (2 \times num_Y \times Cm) < 120 pF$                              |  |  |

| Сру       | Mutual capacitance load to Y          | Microchip recommends a maximum load of 300 pF on each X or Y line. (1)   |  |  |

| Срх       | Self capacitance load to X            | Microchip recommends a maximum load of 130 pF on each X or Y             |  |  |

| Сру       | Self capacitance load to Y            | line. (1)                                                                |  |  |

| ∆Срх      | Self capacitance imbalance on X       | Nominal value is 14.8 pF. Value increases by 1 pF for every 45 pF        |  |  |

| ∆Сру      | Self capacitance imbalance on Y       | reduction in Cpx/Cpy (based on 100 pF load)                              |  |  |

Note 1: Please contact your Microchip representative for advice if you intend to use higher values.

# 7.5 Input/Output Characteristics

| Parameter      | Description                         | Min            | Тур | Max            | Units | Notes                                    |

|----------------|-------------------------------------|----------------|-----|----------------|-------|------------------------------------------|

| Input (All inp | ut pins connected to the VddIO po   | ower rail)     |     |                |       |                                          |

| Vil            | Low input logic level               | -0.3           | -   | 0.3 ×<br>VddIO | V     | VddIO = 1.8 V to Vdd                     |

| Vih            | High input logic level              | 0.7 x<br>VddIO | -   | VddIO          | V     | VddIO = 1.8 V to Vdd                     |

| lil            | Input leakage current               | -              | _   | 1              | μΑ    |                                          |

| RESET          | Internal pull-up resistor           | 9              | 10  | 16             | kΩ    |                                          |

| GPIOs          | Internal pull-up/pull-down resistor |                |     |                |       |                                          |

| Input (All inp | ut pins connected to the Vdd pow    | er rail)       |     |                |       |                                          |

| Vil            | Low input logic level               | -0.3           | -   | 0.3 × Vdd      | V     |                                          |

| Vih            | High input logic level              | 0.7 × Vdd      | -   | Vdd            | V     |                                          |

| lil            | Input leakage current               | -              | -   | 1              | μΑ    | Pull-up resistors disabled               |

| Output (All o  | utput pins connected to the VddlC   | ) power rail   | )   | •              |       | •                                        |

| Vol            | Low output voltage                  | 0              | -   | 0.2 ×<br>VddIO | V     | VddIO = 1.8 V to Vdd<br>IoI = max 0.4 mA |

| Voh            | High output voltage                 | 0.8 x<br>VddIO | -   | VddIO          | V     | VddIO = 1.8 V to Vdd<br>Ioh = 0.4 mA     |

| Output (All o  | utput pins connected to the Vdd p   | ower rail)     |     |                |       | ·                                        |

| Vol            | Low output voltage                  | 0              | -   | 0.2 × Vdd      | V     | IoI = max 0.4 mA                         |

| Voh            | High output voltage                 | 0.8 × Vdd      | _   | Vdd            | V     | Ioh = 0.4 mA                             |

<sup>2:</sup> num\_Y = Number of active Y lines defined by Multiple Touch Touchscreen T100.

### 7.6 I<sup>2</sup>C Specification

| Parameter                                     | Value        |

|-----------------------------------------------|--------------|

| Address                                       | 0x4A         |

| I <sup>2</sup> C specification <sup>(1)</sup> | Revision 6.0 |

| Maximum bus speed (SCL) (2)                   | 400 kHz      |

| Standard Mode (3)                             | 100 kHz      |

| Fast Mode (3)                                 | 400 kHz      |

Note 1: More detailed information on I<sup>2</sup>C operation is available from www.nxp.com/documents/user\_manual/UM10204.pdf.

- 2: In systems with heavily laden I<sup>2</sup>C lines, even with minimum pull-up resistor values, bus speed may be limited by capacitive loading to less than the theoretical maximum.

- 3: The values of pull-up resistors should be chosen to ensure SCL and SDA rise and fall times meet the I<sup>2</sup>C specification. The value required will depend on the amount of capacitance loading on the lines.

### 7.7 Thermal Packaging

#### 7.7.1 THERMAL DATA

| Parameter         | Description                            | Тур  | Unit | Condition | Package                    |

|-------------------|----------------------------------------|------|------|-----------|----------------------------|

| $\theta_{JA}$     | Junction to ambient thermal resistance | 33.7 | °C/W | Still air | 56-pin XQFN 6 × 6 × 0.4 mm |

| $\theta_{\sf JC}$ | Junction to case thermal resistance    | 10.1 | °C/W |           | 56-pin XQFN 6 × 6 × 0.4 mm |

#### 7.7.2 JUNCTION TEMPERATURE

The maximum junction temperature allowed on this device is 125°C.

The average junction temperature in °C (T<sub>J</sub>) for this device can be obtained from the following:

$$T_J = T_A + (P_D \times \theta_{JA})$$

If a cooling device is required, use this equation:

$$T_J = T_A + (P_D \times (\theta_{HEATSINK} + \theta_{JC}))$$

where:

- $\theta_{JA}$ = package thermal resistance, Junction to ambient (°C/W) (see Section 7.7.1 "Thermal Data")

- θ<sub>JC</sub> = package thermal resistance, Junction to case thermal resistance (°C/W) (see Section 7.7.1 "Thermal Data")

- θ<sub>HEATSINK</sub> = cooling device thermal resistance (°C/W), provided in the cooling device datasheet

- P<sub>D</sub> = device power consumption (W)

- T<sub>A</sub> is the ambient temperature (°C)

#### 7.8 ESD Information

| Parameter                 | Value   | Reference Standard |

|---------------------------|---------|--------------------|

| Human Body Model (HBM)    | ±2000 V | JEDEC JS-001       |

| Charge Device Model (CDM) | ±250 V  | JEDEC JS-001       |

# **mXT336UD-MAUHA1 1.0**

# 7.9 Soldering Profile

| Profile Feature                            | Green Package |

|--------------------------------------------|---------------|

| Average Ramp-up Rate (217°C to Peak)       | 3°C/s max     |

| Preheat Temperature 175°C ±25°C            | 150 – 200°C   |

| Time Maintained Above 217°C                | 60 – 150 s    |

| Time within 5°C of Actual Peak Temperature | 30 s          |

| Peak Temperature Range                     | 260°C         |

| Ramp down Rate                             | 6°C/s max     |

| Time 25°C to Peak Temperature              | 8 minutes max |

# 7.10 Moisture Sensitivity Level (MSL)

| MSL Rating | Package Type(s) | Peak Body Temperature | Specifications      |

|------------|-----------------|-----------------------|---------------------|

| MSL3       | QFN             | 260°C                 | IPC/JEDEC J-STD-020 |

### 8.0 PACKAGING INFORMATION

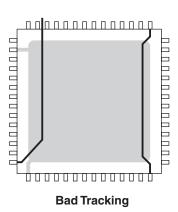

### 8.1 Package Marking Information

#### 8.1.1 56-PIN XQFN

#### 8.1.2 ORDERABLE PART NUMBERS

The product identification system for maXTouch devices is described in "Product Identification System". That section also lists example part numbers for the device.

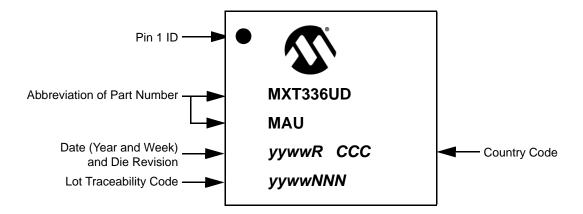

### 8.2 Package Details

### 8.2.1 56-PIN XQFN 6 × 6 × 0.4 MM

# **APPENDIX A: REVISION HISTORY**

# Revision A (January 2020)

Initial edition for firmware revision 0.2 – Advance Information

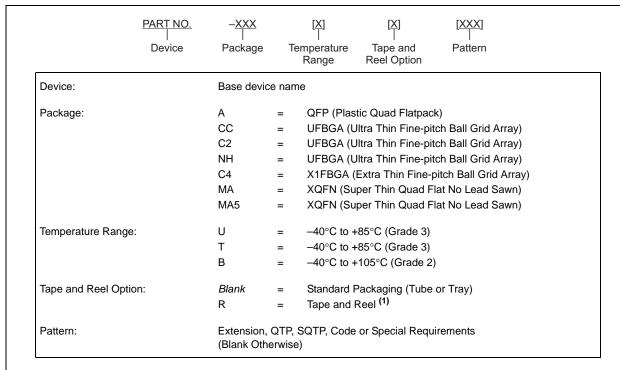

#### PRODUCT IDENTIFICATION SYSTEM

The table below gives details on the product identification system for maXTouch devices. See "Orderable Part Numbers" below for example part numbers for the mXT336UD-MAUHA1.

To order or obtain information, for example on pricing or delivery, refer to the factory or the listed sales office.

Note 1: Tape and Reel identifier only appears in the catalog part number description. This identifier is used for ordering purposes and is not printed on the device package. See "Orderable Part Numbers" below or check with your Microchip Sales Office for package availability with the Tape and Reel option.

#### **Orderable Part Numbers**

| Orderable Part Number                          | Firmware Revision | Description                                                                                               |

|------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------|

| ATMXT336UD-MAUHA1<br>(Supplied in trays)       | 0.2               | 56-pin XQFN 6 × 6 × 0.4 mm, RoHS compliant Industrial grade; not suitable for automotive characterization |

| ATMXT336UD-MAURHA1 (Supplied in tape and reel) |                   |                                                                                                           |

#### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at <a href="www.microchip.com">www.microchip.com</a>. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

#### CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at <a href="www.microchip.com">www.microchip.com</a>. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

#### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- · Field Application Engineer (FAE)

- · Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

# **mXT336UD-MAUHA1 1.0**

NOTES:

Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### Trademarks

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TempTrackr, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, Vite, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, INICnet, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2019 - 2020, Microchip Technology Incorporated, All Rights Reserved.

ISBN: 978-1-5224-5408-3

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

# **Worldwide Sales and Service**

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd.

Chandler, AZ 85224-6199

Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/

support

Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX

Tel: 512-257-3370

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Dallas

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi. MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN

Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

**Raleigh, NC** Tel: 919-844-7510

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

**Australia - Sydney** Tel: 61-2-9868-6733

China - Beijing Tel: 86-10-8569-7000

China - Chengdu Tel: 86-28-8665-5511

**China - Chongqing** Tel: 86-23-8980-9588

China - Dongguan

Tel: 86-769-8702-9880

**China - Guangzhou** Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

**China - Nanjing** Tel: 86-25-8473-2460

**China - Qingdao** Tel: 86-532-8502-7355

China - Shanghai Tel: 86-21-3326-8000

China - Shenyang Tel: 86-24-2334-2829

China - Shenzhen

Tel: 86-755-8864-2200 China - Suzhou

Tel: 86-186-6233-1526

**China - Wuhan** Tel: 86-27-5980-5300

**China - Xian** Tel: 86-29-8833-7252

**China - Xiamen** Tel: 86-592-2388138

**China - Zhuhai** Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631

India - Pune

Tel: 91-20-4121-0141

**Japan - Osaka** Tel: 81-6-6152-7160

**Japan - Tokyo** Tel: 81-3-6880- 3770

Korea - Daegu Tel: 82-53-744-4301

Korea - Seoul Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

**Singapore** Tel: 65-6334-8870

**Taiwan - Hsin Chu** Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

**Vietnam - Ho Chi Minh** Tel: 84-28-5448-2100

#### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

Finland - Espoo

Tel: 358-9-4520-820 France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Garching** Tel: 49-8931-9700

**Germany - Haan** Tel: 49-2129-3766400

**Germany - Heilbronn** Tel: 49-7131-72400

**Germany - Karlsruhe** Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Germany - Rosenheim** Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Padova Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7288-4388

**Poland - Warsaw** Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**Sweden - Gothenberg** Tel: 46-31-704-60-40

**Sweden - Stockholm** Tel: 46-8-5090-4654