#### **QP82S100 - PLS100**

October 9, 2007

# QP82S100 – PLS100 Field Programmable Logic Array (16 x 48 x 8)

#### **General Description**

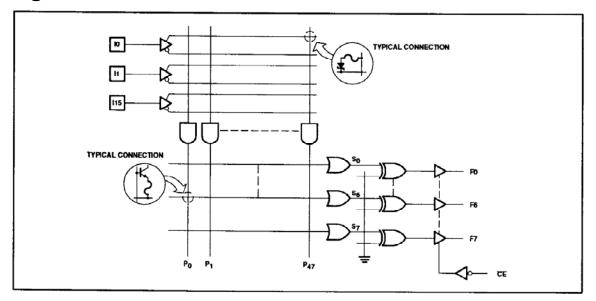

The QP82S100 – PLS100 PLA is a tri-state output bi-polar programmable logic array with field programmable metal fuse technology (NiChrome). The device utilizes the standard AND/OR/NOT (invert) architecture to directly implement custom sum of product logic equations.

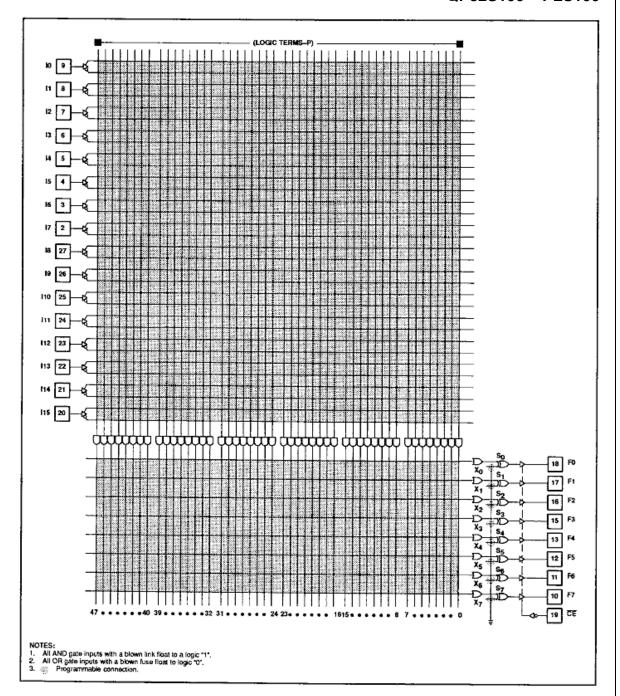

Each Device consists of 16 dedicated inputs and 8 dedicated outputs. Each output is capable of being actively controlled by any or all of the 48 product terms. The True, Complement, or Don't Care condition of each of the 16 inputs can be ANDed together to comprise one P-Term. All 48 P-Terms can be selectively Ored to each output.

The device is fully TTL compatible, and chip enable control for expansion of input variables and output inhibit. The device features Tri-State outputs for ease of expansion terms and application in bus-organized systems.

The QP82S100 - PLS100 features:

- Field-Programmable (Ni-Cr link)

- Output Functions: 8

- I/O propagation delay: 50ns

- Input loading: -100uA

- Tri-State Output

Applications:

- CRT Display Systems

Code Conversion

Peripheral Controllers

Function Generators

Look-up and Decision Tables

Microprogramming

Address Mapping

- Input Variables: 16

Product Terms: 48

Power Dissipation: 600mW (typ.)

- Chip Enable Input

Output Disable Function: High-Z

Character Generators

Data Security Encoders

Fault Detectors

- Frequency Synthesizers

- 16-bit to 8-bit Bus Interface

Random Logic Replacement

The device/family is constructed using Bipolar/NiChrome processing.

Programming supported by Data I/O under QP Semi/Qualified Parts Lab 82S100

QP Semiconductor products are not authorized for use in any space applications. The inclusion of QP Semiconductor products in space applications implies that the space application manufacturer assumes all risk of such use and in doing so indemnifies QP Semiconductor against all charges.

# **Functional Diagram**

QP82S100 **PLS100**

#### **QP82S100 - PLS100**

# Logic Diagram

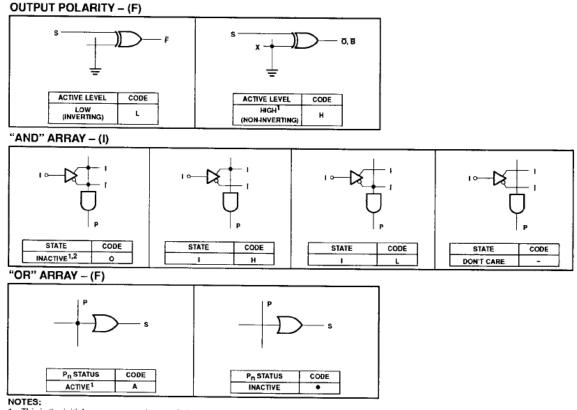

### **Fuse Function**

- This is the initial unprogrammed state of all links. It is normally associated with all unused (inactive) AND gates P<sub>n</sub>.

- Any gate P<sub>n</sub> will be unconditionally inhibited if any one of its (I) link pairs is left intact.

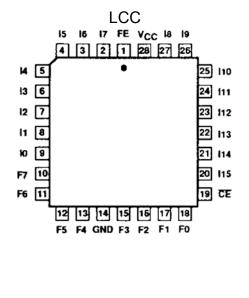

## **Connection Diagrams**

QP82S100 - PLS100

Fuse Enable Pin: It is recommended that this pin be left open or connected to ground during normal operation.

Absolute Maximum Ratings

Stresses above the AMR may cause permanent damage; extended operation at AMR may degrade performance and affect reliability

| Condition                                |              | Units    | Notes |

|------------------------------------------|--------------|----------|-------|

|                                          |              |          |       |

| Power Supply and Input Voltage           | -0.5 to +7.0 | Volts DC |       |

| Output Current                           | +100         | mA       |       |

| Input Clamp Current                      | -30 to +30   | mA       |       |

| No Terminal may exceed VCC               | >0.5         | Volts    | /1    |

| Storage Temperature Range                | -65 to +150  | °C       |       |

| Lead Temperature (soldering, 10 seconds) | +300         | °C       |       |

| Junction Temperature (T <sub>J</sub> )   | +150         | °C       |       |

|                                          |              |          |       |

**Recommended Operating Conditions**

| Condition                                                                                                                            |                   | Units    | Notes |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------|-------|--|--|

|                                                                                                                                      |                   |          |       |  |  |

| Supply Voltage Range (V <sub>CC</sub> )                                                                                              | 4.5 to 5.5        | Volts DC |       |  |  |

| Input or Output Voltage Range                                                                                                        | $0.0$ to $V_{CC}$ | Volts DC | /1    |  |  |

| Minimum High-Level Input Voltage (V <sub>IH</sub> )                                                                                  | 2.0               | Volts DC |       |  |  |

| Maximum Low-Level Input Voltage (V <sub>IL</sub> )                                                                                   | 0.8               | Volts DC |       |  |  |

| Case Operating Range (T <sub>c</sub> )                                                                                               | -55C to +125      | °C       | /2    |  |  |

| /1 – For VCC≥6.5V, the upper limit on the range is limited to 7.0V<br>/2 – Maximum PD, Maximum T <sub>J</sub> Are Not to Be Exceeded |                   |          |       |  |  |

| 12 - Maximum PD, Maximum 1, Are Not to                                                                                               | be exceeded       |          |       |  |  |

| Test                     | Symbol           | Conditions<br>-55°C ≤TA≤+125°C<br>Unless Otherwise Specified                                                               | Min   | Max    | Unit |

|--------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------|-------|--------|------|

| Input High Voltage       | V <sub>IH</sub>  | V <sub>CC</sub> = 5.5V                                                                                                     | 2.0   |        | V    |

| Input Low Voltage        | V <sub>IL</sub>  | V <sub>CC</sub> = 4.5V                                                                                                     |       | 0.8    | V    |

| Input High Current       | I <sub>IH</sub>  | V <sub>CC</sub> =5.5V, V <sub>IN</sub> =5.5V                                                                               |       | 50     | uA   |

| Input Low Current        | I <sub>IL</sub>  | V <sub>CC</sub> =5.5V, V <sub>IN</sub> =0.45V                                                                              | -1.0  | -250   | uA   |

| Input Clamp              | Vic              | V <sub>CC</sub> = 4.5V, I <sub>IN</sub> =-18mA                                                                             |       | 1.2    | V    |

| Output High Voltage      | $V_{OH}$         | $V_{CC} = 4.5V, I_{OH} = -2mA$                                                                                             | 2.4   |        | V    |

| Output Low Voltage       | V <sub>OL</sub>  | $V_{CC} = 5.5V, I_{OH} = 9.6mA$                                                                                            |       | 0.5    | V    |

| Tri-State Output Current | I <sub>OZL</sub> | $V_{CC}$ = 5.5V, $V_{OUT}$ = 0.45V, $CE_{BAR}$ =High                                                                       | -60.0 |        | uA   |

| (High Impedance State)   | I <sub>OZH</sub> | $V_{CC} = 5.5V, V_{OUT} = 5.5V, CE_{BAR} = High$                                                                           |       | +100.0 | uA   |

| Short Circuit Current    | I <sub>OS</sub>  | V <sub>CC</sub> = 5.5V,V <sub>OUT</sub> = 0V, CE <sub>BAR</sub> =Low Duration not to exceed 1 second, one output at a time | -15   | -85    | mA   |

| Power Supply Current     | I <sub>CC</sub>  | V <sub>CC</sub> = 5.5V                                                                                                     |       | 180    | mA   |

#### **QP82S100 - PLS100**

| TABLE I – ELECTRICAL PERFORMANCE CHARACTERISTICS |                 |                                                              |     |     |      |

|--------------------------------------------------|-----------------|--------------------------------------------------------------|-----|-----|------|

| Test                                             | Symbol          | Conditions<br>-55°C ≤TA≤+125°C<br>Unless Otherwise Specified | Min | Max | Unit |

| Input to Output Propagation Delay                | t <sub>PD</sub> | V <sub>CC</sub> = 4.5 - 5.5V                                 |     | 80  | ns   |

| Chip Enable Delay ENABLE to OUTPUT               | t <sub>CE</sub> | V <sub>CC</sub> = 4.5 - 5.5V                                 |     | 50  | ns   |

| Chip Disable Delay ENABLE to OUTPUT              | t <sub>CD</sub> | $V_{CC} = 4.5 - 5.5V$                                        |     | 50  | ns   |

**Ordering Information**

| Part Number      | Package (Mil-Std-1835)         | Generic         |

|------------------|--------------------------------|-----------------|

| QP82S100/B3A-MIL | CQCC1-N28 (LCC)                | 82S100 - PLS100 |

| QP82S100/BXA-MIL | GDIP1-T28 CDIP2-T28 (DIP)      | 82S100 - PLS100 |

| QP82S100/BYA-MIL | GDFP2-F28 CDFP3-F28 (FLATPACK) | 82S100 – PLS100 |

QP Semiconductor supports Source Control Drawing (SCD), and custom package development for this product family.

#### Notes:

Package outline information and specifications are defined by Mil-Std-1835 package dimension requirements.

"-MIL" products manufactured by QP Semiconductor are compliant to the assembly, burn-in, test and quality conformance requirements of Test Methods 5004 & 5005 of Mil-Std-883 for Class B devices. This datasheet defines the electrical test requirements for the device(s).

The listed drawings, Mil-PRF-38535, Mil-Std-883 and Mil-Std-1835 are available online at <a href="http://www.dscc.dla.mil/">http://www.dscc.dla.mil/</a>

Additional information is available at our website <a href="http://www.qpsemi.com">http://www.qpsemi.com</a>