# Le87611

# **PLC Single Channel Class AB Line Driver**

Data Sheet

#### **FEATURES**

- 16-pin, 4x4 mm QFN Package

- · Very low power dissipation

- Class AB operation

- · 4 programmable states

- · No external gain resistors required

- · RoHS compliant

#### **APPLICATIONS**

- Power Line Communications

- Home Networking

- HPNA

- G.HN

#### DESCRIPTION

The Le87611 is a single channel differential amplifier designed to work in Home Plug Alliance HPAV2 systems with very low power dissipation.

The Le87611 contains a pair of wideband amplifiers designed with Microsemi's HV15 Bipolar SOI process for low power consumption.

The line driver gain is fixed internally. The amplifiers are powered from a single supply.

The device can be programmed to one-of-three preset Bias levels or to a Disable state. The control pins respond to input levels that can be generated with a standard tri-state GPIO.

The Le87611 is available in a 16-pin (4 mm x 4 mm) QFN package with exposed pad for enhanced thermal conductivity.

#### Version 4.0

**Document Code**

PD-000286416

Sept 2019

#### ORDERING INFORMATION

Le87611NQC 16-pin QFN Green Package Tray

Le87611NQCT 16-pin QFN Green Package Tape and Reel

The green package meets RoHS 2 Directive 2011/65/EU of the European Council to minimize the environmental impact of electrical equipment.

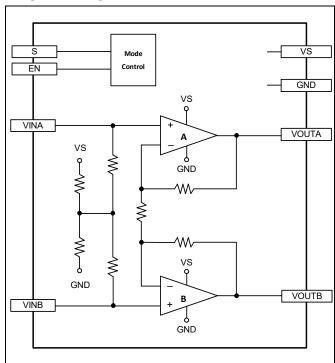

#### **BLOCK DIAGRAM**

Data Sheet

# TABLE OF CONTENTS

| <u>Features</u>              | 1  |

|------------------------------|----|

|                              |    |

| <u>Description</u>           |    |

| Ordering Information.        | 1  |

| Block Diagram                | 1  |

| Connection Diagram           | 3  |

| Pin Descriptions             | 4  |

| Absolute Maximum Ratings     | 5  |

| Thermal Resistance           | 5  |

| Package Assembly             | 5  |

| Operating Ranges             | 5  |

| <u>Device Specifications</u> | 6  |

| State Control                | 7  |

| <u>Applications</u>          | 3  |

| Physical Dimensions          | 9  |

| <u>16-Pin QFN</u>            | 9  |

| Revision History             | 10 |

| Version 2.0 to Version 3.0.  | 10 |

| Version 3.0 to Version 3.1   | 10 |

| Version 3.1 to Version 4.0.  | 10 |

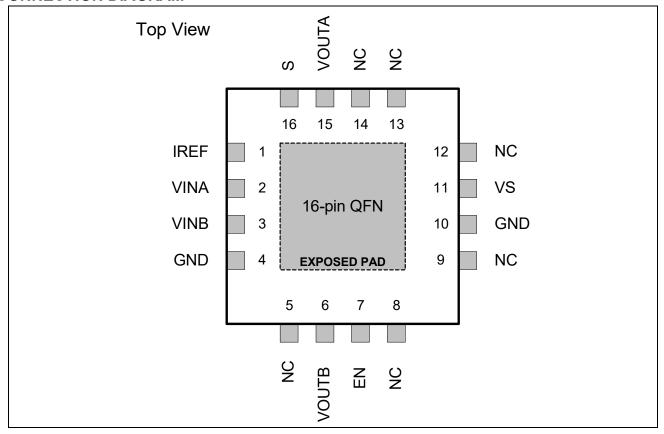

# **CONNECTION DIAGRAM**

#### Note:

- 1. Pin 1 is marked for orientation.

- 2. The Le87611 device incorporates an exposed die pad on the underside of its package. The pad acts as a heat sink and must be connected to a copper plane through thermal vias, for proper heat dissipation. It is electrically isolated and maybe connected to GND.

# PIN DESCRIPTIONS

| Pin Number | Pin Name    | Type   | Description                                                                       |  |

|------------|-------------|--------|-----------------------------------------------------------------------------------|--|

| 1          | IREF        | Input  | Device internal reference current. Connect a resistor (R <sub>REF</sub> ) to GND. |  |

| 2          | VINA        | Input  | Non-inverting input of amplifier A                                                |  |

| 3          | VINB        | Input  | Non-inverting input of amplifier B                                                |  |

| 4          | GND         | Ground | Reference ground                                                                  |  |

| 5          | NC          |        | No internal connection                                                            |  |

| 6          | VOUTB       | Output | Amplifier B output                                                                |  |

| 7          | EN          | Input  | Enable transmission                                                               |  |

| 8          | NC          |        | No internal connection                                                            |  |

| 9          | NC          |        | - No litternal confinection                                                       |  |

| 10         | GND         | Ground | Reference ground                                                                  |  |

| 11         | VS          | Power  | Power Supply, +12 V                                                               |  |

| 12         | NC          |        |                                                                                   |  |

| 13         | NC          |        | No internal connection                                                            |  |

| 14         | NC          |        |                                                                                   |  |

| 15         | VOUTA       | Output | Amplifier A output                                                                |  |

| 16         | S           | Input  | State control                                                                     |  |

|            | Exposed pad |        | Electrically isolated thermal conduction pad, can be grounded                     |  |

### **ABSOLUTE MAXIMUM RATINGS**

Stresses above the values listed under *Absolute Maximum Ratings* can cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods can affect device reliability.

| Storage Temperature                                                                                                      | -65 ≤ T <sub>A</sub> ≤ +150 °C |  |  |

|--------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|--|

| Operating Junction Temperature <sup>(1)</sup>                                                                            | -40 ≤ T <sub>j</sub> ≤ +150 °C |  |  |

| VS with respect to GND                                                                                                   | -0.3 V to +16 V                |  |  |

| Control inputs with respect to GND                                                                                       | -0.3 V to 4 V                  |  |  |

| Continuous Driver Output Current                                                                                         | 100 mA                         |  |  |

| Maximum device power dissipation, continuous <sup>(2)</sup> - T <sub>A</sub> = 85°C, P <sub>D</sub>                      | 1.0 W                          |  |  |

| Junction to ambient thermal resistance $^{(2,3)}$ , $\theta_{JA}$                                                        | 52.0 °C/W                      |  |  |

| Junction to board thermal resistance $^{(2)}$ , $\theta_{JB}$                                                            | 26.0 °C/W                      |  |  |

| Junction to case bottom (exposed pad) thermal resistance, $\theta_{\mbox{\scriptsize JC}}_{\mbox{\scriptsize (BOTTOM)}}$ | 14.6 °C/W                      |  |  |

| Junction-to-top characterization parameter $^{(2)}$ , $\psi_{JT}$                                                        | 3.1 °C/W                       |  |  |

| ESD Immunity (Human Body Model)                                                                                          | JESD22 Class 2 compliant       |  |  |

| ESD Immunity (Charge Device Model)                                                                                       | JESD22 Class IV compliant      |  |  |

#### Notes:

- 1. Continuous operation above 145°C junction temperature may degrade device reliability.

- 2. See Thermal Resistance.

- 3. No air flow.

#### Thermal Resistance

The thermal performance of a thermally enhanced package is assured through optimized printed circuit board layout. Specified performance requires that the exposed thermal pad be soldered to an equally sized exposed copper surface, which, in turn, conducts heat through multiple vias to larger internal copper planes.

## **Package Assembly**

The green package devices are assembled with enhanced, environmental compatible lead-free, halogen-free, and antimony-free materials. The leads possess a matte-tin plating which is compatible with conventional board assembly processes or newer lead-free board assembly processes.

Refer to IPC/JEDEC J-Std-020 Table 4 for recommended peak soldering temperature and Table 5-2 for the recommended solder reflow temperature profile.

#### **OPERATING RANGES**

Microsemi guarantees the performance of this device over the -40°C to 85°C temperature range by conducting electrical characterization over each range and by conducting a production test with single insertion coupled with periodic sampling. These characterization and test procedures comply with the Telcordia GR-357-CORE Generic Requirements for Assuring the Reliability of Components Used in Telecommunications Equipment.

| Ambient temperature | T <sub>A</sub>         | -40°C to +85°C |

|---------------------|------------------------|----------------|

| Power Supply        | VS with respect to GND | +12 V ± 5%     |

# **DEVICE SPECIFICATIONS**

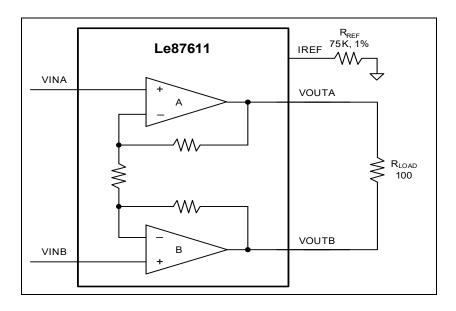

*Typical Conditions:* As shown in the basic test circuit (<u>Figure 1</u>) with VS = +12 V,  $R_{REF}$  = 75 k $\Omega$ , and  $T_A$  = 25°C. *Min/Max Parameters:*  $T_A$  = -40 to +85°C.

Table 1. Electrical Specifications

| Symbol             | Parameter Description           | Condition                       | Min     | Тур      | Max      | Unit    | Notes |

|--------------------|---------------------------------|---------------------------------|---------|----------|----------|---------|-------|

| Supply Cu          | rrent Characteristics           |                                 |         |          | ·        |         |       |

| I <sub>VS</sub>    | Supply Current                  | Full Power State                | 17      | 23       | 29       | mA      |       |

|                    |                                 | Medium Power State              | 11<br>5 | 19<br>10 | 23<br>15 |         |       |

|                    |                                 | Low Power State                 |         |          |          |         |       |

|                    |                                 | Disable State                   |         | 0.8      | 1.5      |         |       |

| Control Inp        | out (S, EN) Specification       | s                               | •       |          |          | •       |       |

| V <sub>IH</sub>    | Input High Voltage              |                                 | 2.0     |          |          | V       |       |

| V <sub>IM</sub>    | Input Middle Voltage            |                                 |         | 1.5      |          | V       |       |

| V <sub>IL</sub>    | Input Low Voltage               |                                 |         |          | 0.8      | V       |       |

|                    | Enable Time                     |                                 |         | 500      |          | ns      | 1     |

| Amplifier C        | Characteristics                 |                                 | -       |          | 1        |         |       |

|                    | Differential Gain               | Full Power State, VOUT/VIN      | 8.2     | 8.7      | 9.0      | V/V     |       |

| Bandwidth, -3      |                                 | Full Power State                |         | 200      |          |         | 1     |

|                    | Bandwidth, -3 dB                | Medium Power State              |         | 200      |          | MHz     | 1     |

|                    |                                 | Low Power State                 |         | 115      |          |         | 1     |

| V <sub>O</sub>     | Output Voltage                  |                                 |         | 10       |          | V       |       |

| Io                 | Output Current                  |                                 | 150     |          |          | mA      | 1     |

| Z <sub>l</sub>     | Input Impedance                 | Differential                    | 13      | 15       | 18       | kΩ      |       |

| Amplifier D        | ynamic Characteristics          |                                 |         | 1        |          | 1       |       |

| Noise              | Input Referred Noise            | 2 – 106 MHz                     |         | 9        | 15       | nV/ √Hz | 1     |

| TSD                | Thermal Shutdown<br>Temperature |                                 |         | 170      |          | °C      | 1     |

| Notes: 1. Not test | red in production. Guaranteed   | by characterization and design. | •       |          | •        | •       |       |

Figure 1. Basic Test Circuit

### STATE CONTROL

S and EN pins are used as combinatorial logic inputs to control the line driver operating states. <u>Table 2</u> shows the programmable states.

S is a tri-state input that accepts three operating levels. This pin has an internal resistor tied to +1.5 V which forces a middle logic input level when the control to this pin is tri-stated.

**Table 2. Control Matrix**

| S    | EN | State              |

|------|----|--------------------|

| Х    | 0  | Disable            |

| 0    | 1  | Enable Low Bias    |

| Open | 1  | Enable Medium Bias |

| 1    | 1  | Enable Full Bias   |

**Disable State:** Amplifier bias current removed. This is the lowest power state. Amplifier output is high impedance. Gain-setting feedback resistors are still connected across amplifier output pins, creating 1300 ohm differential impedance at pins.

**Bias States:** Line Driver is active for transmission. States are different only in the amount of bias current to the amplifiers, and therefore power consumption. There is a trade-off between bias current and bandwidth.

#### **APPLICATIONS**

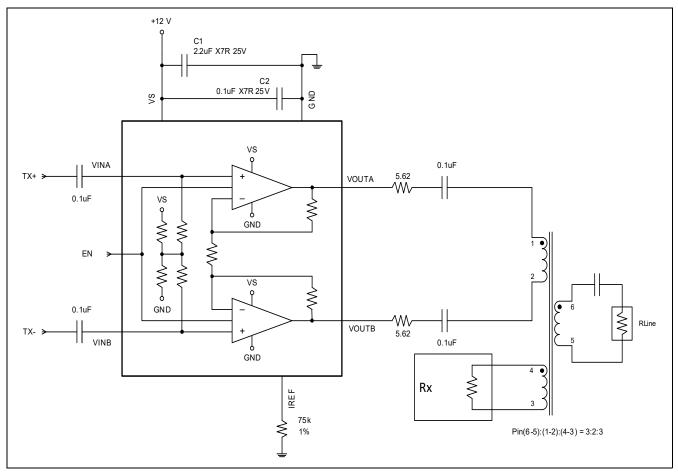

The Le87611 integrates a set of high-power line driver amplifiers designed for low distortion for signals up to 106 MHz.

Figure 2 shows an application circuit with amplifiers A and B in transmission.

Figure 2. Typical Application Circuit

#### **Input Considerations**

The driving source impedance should be less than 100 nH to avoid any ringing or oscillation.

#### **Output Driving Considerations**

The internal metallization is designed to carry up to about 100 mA of steady DC current and there is no current limit mechanism. The device does feature integrated thermal shutdown protection however with hysteresis. Driving lines with no series resistor is not recommended.

#### **Power Supplies and Component Placement**

The power supplies should be well bypassed close to the Le87611 device. A 2.2  $\mu$ F tantalum capacitor and a 0.1  $\mu$ F ceramic capacitor for the VS supply is recommended.

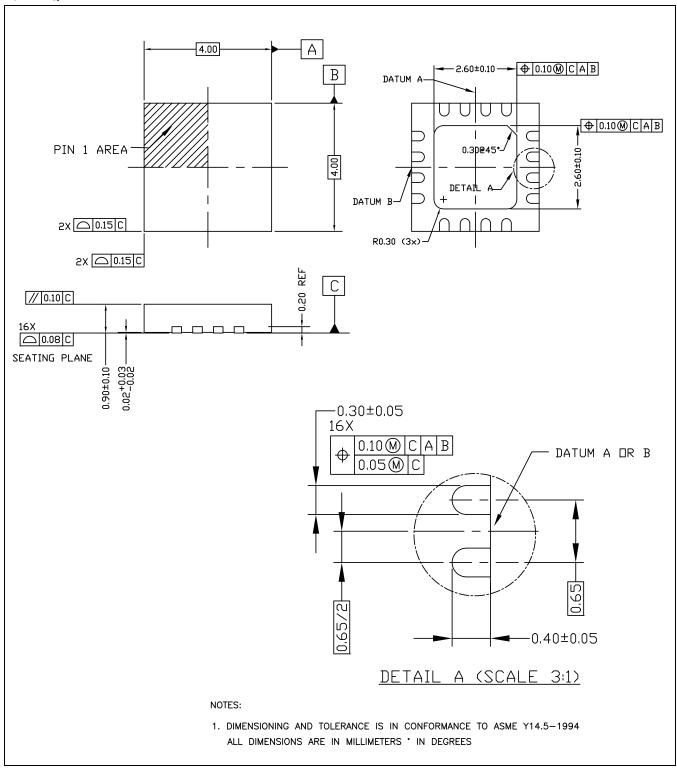

## PHYSICAL DIMENSIONS

#### 16-Pin QFN

#### Note:

Packages may have mold tooling markings on the surface. These markings have no impact on the form, fit or function of the device. Markings will vary with the mold tool used in manufacturing.

# **REVISION HISTORY**

## Version 2.0 to Version 3.0

• Updated Operating Ranges about Ambient temperature, T<sub>A</sub>, on page 5 and page 6, from 0°C to +85°C to -40°C to +85°C.

# Version 3.0 to Version 3.1

Minor format update on page 1.

### Version 3.1 to Version 4.0

- · Data sheet status updated by removing "Preliminary".

- Updated Table 1, "Electrical Specifications," on page 6

Information relating to products and services furnished herein by Microsemi Corporation or its subsidiaries (collectively "Microsemi") is believed to be reliable. However, Microsemi assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Microsemi or licensed from third parties by Microsemi, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Microsemi, or non-Microsemi furnished goods or services may infringe patents or other intellectual property rights owned by Microsemi.

This publication is issued to provide information only and (unless agreed by Microsemi in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Microsemi without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical and other products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Microsemi's conditions of sale which are available on request.

For more information about all Microsemi products visit our website at www.microsemi.com

TECHNICAL DOCUMENTATION - NOT FOR RESALE

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor solutions for: aerospace, defense and security; enterprise and communications; and industrial and alternative energy markets. Products include mixed-signal ICs, SoCs, and ASICs; programmable logic solutions; power management products; timing and voice processing devices; RF solutions; discrete components; and systems. Microsemi is headquartered in Aliso Viejo, Calif. Learn more at www.microsemi.com.

© 2019 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.