Buy

SLWS237A-NOVEMBER 2012-REVISED NOVEMBER 2014

## DRV11873 12-V, 3-Phase, Sensorless BLDC Motor Driver

#### Features 1

Texas

INSTRUMENTS

- Input Voltage Range: 5 to 16 V

- Six Integrated MOSFETs With 1.5-A Continuous **Output Current**

- Total Driver H + L R<sub>DSON</sub> 450 mΩ

- Sensorless Proprietary BMEF Control Scheme

- 150° Commutation

- Synchronous Rectification PWM Operation

- FG and RD Open-Drain Output

- 5-V LDO for External Use up to 20 mA

- PWM<sub>IN</sub> Input from 7 to 100 kHz

- **Overcurrent Protection With Adjustable Limit** Through External Resistor

- Lock Detection

- Voltage Surge Protection

- UVLO

- Thermal Shutdown

#### Applications 2

- **Appliance Cooling Fan**

- **Desktop Cooling Fan**

- Server Cooling Fan

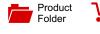

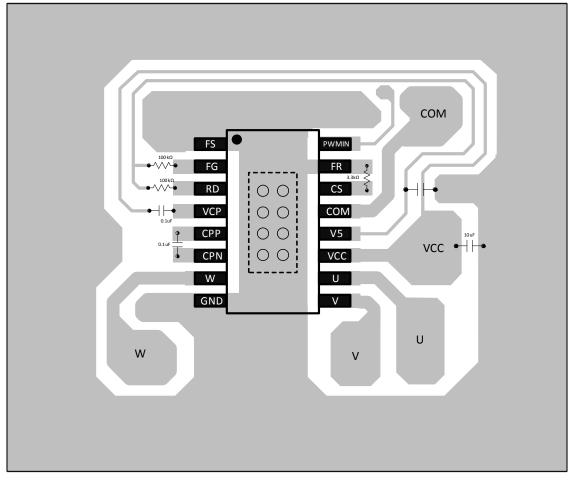

### Simplified Schematic

#### 3 Description

DRV11873 is a three-phase, sensorless motor driver with integrated power MOSFETs with drive current capability up to 1.5-A continuous and 2-A peak. DRV11873 is specifically designed for fan motor drive applications with low noise and low external component count. DRV11873 has built-in overcurrent protection with no external current sense resistor needed. The synchronous rectification mode of operation achieves increased efficiency for motor driver applications. DRV11873 outputs FG and RD to indicate motor status with open-drain output. A 150° sensorless BEMF control scheme is implemented for a three-phase motor. DRV11873 is available in the thermally-efficient 16-pin TSSOP package. The operation temperature is specified from -40°C to 125°C.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE     | BODY SIZE (NOM)   |  |  |

|-------------|-------------|-------------------|--|--|

| DRV11873    | HTSSOP (16) | 4.40 mm × 5.00 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

TEXAS INSTRUMENTS

www.ti.com

## **Table of Contents**

| 1 | Feat               | tures                            | 1   |  |  |  |  |

|---|--------------------|----------------------------------|-----|--|--|--|--|

| 2 | Арр                | lications                        | 1   |  |  |  |  |

| 3 | Des                | cription                         | 1   |  |  |  |  |

| 4 | Sim                | plified Schematic                | 1   |  |  |  |  |

| 5 | Revision History 2 |                                  |     |  |  |  |  |

| 6 | Pin                | Configuration and Functions      | 3   |  |  |  |  |

| 7 | Spe                | cifications                      | 4   |  |  |  |  |

|   | 7.1                | Absolute Maximum Ratings         | . 4 |  |  |  |  |

|   | 7.2                | Handling Ratings                 | . 4 |  |  |  |  |

|   | 7.3                | Recommended Operating Conditions | . 4 |  |  |  |  |

|   | 7.4                | Thermal Information              | 5   |  |  |  |  |

|   | 7.5                | Electrical Characteristics       | 6   |  |  |  |  |

|   | 7.6                | Typical Characteristics          | . 7 |  |  |  |  |

| 8 | Deta               | ailed Description                | 9   |  |  |  |  |

|   | 8.1                | Overview                         | 9   |  |  |  |  |

|   |                    |                                  |     |  |  |  |  |

|    | 8.3  | Feature Description                         | 10 |

|----|------|---------------------------------------------|----|

|    | 8.4  | Device Functional Modes                     | 11 |

| 9  | App  | lication and Implementation                 | 13 |

|    | 9.1  | Application Information                     | 13 |

|    | 9.2  | Typical Application                         | 13 |

| 10 | Pow  | er Supply Recommendations                   | 15 |

| 11 | Lay  | out                                         | 15 |

|    | 11.1 | Layout Guidelines                           | 15 |

|    | 11.2 | Layout Example                              | 15 |

| 12 | Dev  | ice and Documentation Support               | 16 |

|    | 12.1 | Trademarks                                  | 16 |

|    | 12.2 | Electrostatic Discharge Caution             | 16 |

|    | 12.3 | Glossary                                    | 16 |

| 13 |      | hanical, Packaging, and Orderable<br>mation | 16 |

### 5 Revision History

## Changes from Original (November 2012) to Revision A

#### Page

| • | Added Handling Ratings table, Feature Description section, Device Functional Modes, Application and    |     |

|---|--------------------------------------------------------------------------------------------------------|-----|

|   | Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation |     |

|   | Support section, and Mechanical, Packaging, and Orderable Information section                          | . 1 |

| • | Changed $f_{\text{PWM}}$ minimum value                                                                 | 6   |

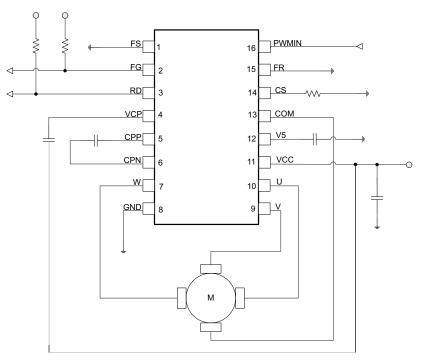

## 6 Pin Configuration and Functions

#### **Pin Functions**

| PIN   |     | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|-------|-----|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME  | NO. | 1/0 ( /            | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| FS    | 1   | I                  | Motor parameter adjustment pin. Pull low for lower-speed motor and pull high for high-speed motor.                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| FG    | 2   | 0                  | Frequency generator output. The output period is equal to 6 electrical states (FG).                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| RD    | 3   | 0                  | In the lock condition, RD output is high through a pullup resistor to $V_{CC}$ or 5 V.                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| VCP   | 4   | 0                  | Charge pump output                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| CPP   | 5   | 0                  | Charge pump conversion terminal                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| CPN   | 6   | 0                  | Charge pump conversion terminal                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| W     | 7   | 0                  | Phase W output                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| GND   | 8   | _                  | Ground pin                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| V     | 9   | 0                  | Phase V output                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| U     | 10  | 0                  | Phase U output                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| VCC   | 11  | I                  | Input voltage for motor and chip supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| V5    | 12  | 0                  | 5-V regulator output                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| СОМ   | 13  | I                  | Motor common terminal input. If the motor does not have a common wire, see <i>Application and Implementation</i> for more details.                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| cs    | 14  | I                  | Overcurrent threshold set-up pin. A resistor set-up current limit is connected between this pin and ground. The voltage across the resistor compares with the voltage converted from the bottom MOSFETs' current. If MOSFETs' current is high, the part goes into the overcurrent protection mode by turning off the top PWM MOSFET and keeping the bottom MOSFET on. $I_{limit}(A) = 6600 / R_{CS} (\Omega)$ ; Equation valid range: 500 mA < $I_{limit} < 2000$ mA |  |  |  |  |

| FR    | 15  | Ι                  | Set high for reverse rotation. Set low or floating for forward rotation.                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| PWMIN | 16  | Ι                  | PWM input pin. The PWM input signal is converted to a fixed switching frequency on the MOSFET driver.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

(1) I = input, O = output, N/A = not available

### 7 Specifications

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature (unless otherwise noted)

|                               |                                | MIN  | MAX | UNIT |

|-------------------------------|--------------------------------|------|-----|------|

| Input voltage <sup>(1)</sup>  | VCC                            | -0.3 | 20  |      |

|                               | CS                             | -0.3 | 3.6 |      |

|                               | PWMIN, FS, FR                  | -0.3 | 6   | V    |

|                               | GND                            | -0.3 | 0.3 |      |

|                               | СОМ                            | -1   | 20  |      |

|                               | U, V, W                        | -1   | 20  |      |

|                               | FG, RD                         | -0.3 | 20  |      |

| Output voltage <sup>(1)</sup> | VCP                            | -0.3 | 25  | V    |

| Output voltage                | CPN                            | -0.3 | 20  | v    |

|                               | СРР                            | -0.3 | 25  |      |

|                               | V5                             | -0.3 | 6   |      |

| TJ                            | Operating junction temperature | -40  | 125 | °C   |

(1) Voltage values are with respect to the network ground terminal unless otherwise noted.

#### 7.2 Handling Ratings

|                    |                            |                                                                                          | MIN   | MAX  | UNIT |

|--------------------|----------------------------|------------------------------------------------------------------------------------------|-------|------|------|

| T <sub>stg</sub>   | Storage tempe              | -55                                                                                      | 150   | °C   |      |

|                    |                            | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | -4000 | 4000 |      |

| V <sub>(ESD)</sub> | Electrostatic<br>discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | -1000 | 1000 | V    |

|                    |                            | Machine model (MM)                                                                       | -200  | 200  |      |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. (1)

(2)

### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                                | MIN  | MAX | UNIT |

|----------------|--------------------------------|------|-----|------|

| Supply voltage | VCC                            | 5    | 16  | V    |

|                | U, V, W                        | -0.7 | 17  |      |

|                | СОМ                            | -0.1 | 17  |      |

|                | FG, RD                         | -0.1 | 16  |      |

|                | PGND, GND                      | -0.1 | 0.1 |      |

| Voltage range  | VCP                            | -0.1 | 22  | V    |

|                | СРР                            | -0.1 | 22  |      |

|                | CPN                            | -0.1 | 16  |      |

|                | V5                             | -0.1 | 5.5 |      |

|                | PWMIN, FR, FS                  | -0.1 | 5.5 |      |

| TJ             | Operating junction temperature | -40  | 125 | V    |

### 7.4 Thermal Information

|                       |                                              | DRV11873 |         |

|-----------------------|----------------------------------------------|----------|---------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PWP      | UNIT    |

|                       |                                              | 16 PINS  |         |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 39.4     |         |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 30.3     |         |

| $R_{	heta JB}$        | Junction-to-board thermal resistance         | 25.6     | °C 1.1/ |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.5      | °C/W    |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 10.2     |         |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 3.6      |         |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

SLWS237A-NOVEMBER 2012-REVISED NOVEMBER 2014

www.ti.com

#### 7.5 Electrical Characteristics

over recommended operating free-air temperature (unless otherwise noted)

|                          | PARAMETER                            | TEST CONDITIONS                                                                        | MIN   | TYP   | MAX   | UNIT |

|--------------------------|--------------------------------------|----------------------------------------------------------------------------------------|-------|-------|-------|------|

| SUPPLY CU                | IRRENT                               |                                                                                        |       |       |       |      |

| I <sub>VCC</sub>         | Supply current                       | T <sub>A</sub> = 25°C; PWM = V <sub>CC</sub> ; V <sub>CC</sub> = 12 V                  |       | 2.7   | 5     | mA   |

| UVLO                     |                                      |                                                                                        |       |       |       |      |

| V <sub>VUVLO-th_</sub> r | UVLO threshold voltage               | Rise threshold, $T_A = 25^{\circ}C$                                                    |       | 4.3   | 4.6   | V    |

| V <sub>UVLO-th_f</sub>   | UVLO threshold voltage               | Fall threshold, $T_A = 25^{\circ}C$                                                    | 3.9   | 4.1   |       | V    |

| V <sub>UVLO-thhys</sub>  | UVLO threshold voltage<br>hysteresis | T <sub>A</sub> = 25°C                                                                  | 100   | 200   | 300   | mV   |

| INTEGRATE                | D MOSFET                             | •                                                                                      | •     |       | ,     |      |

| R <sub>DSON</sub>        | Series resistance (H + L)            | T <sub>A</sub> = 25°C; V <sub>CC</sub> = 12 V; VCP = 19 V;<br>I <sub>OUT</sub> = 1.5 A |       | 0.45  | 0.6   | Ω    |

| PWM                      |                                      |                                                                                        |       |       | 1     |      |

| V <sub>PWM-IH</sub>      | High-level input voltage             | $V_{CC} \ge 4.5 V$                                                                     | 2.7   |       |       | V    |

| V <sub>PWM-IL</sub>      | Low-level input voltage              | V <sub>CC</sub> ≥ 4.5 V                                                                |       |       | 0.8   | V    |

| <i>f</i> <sub>PWM</sub>  | PWM input frequency                  |                                                                                        | 7     |       | 100   | kHz  |

| I <sub>PWM-SOURCE</sub>  | PWM source current                   |                                                                                        | 35    | 50    | 65    | μA   |

| FG                       |                                      |                                                                                        |       |       |       |      |

| I <sub>FG-SINK</sub>     | FG pin sink current                  | V <sub>FG</sub> = 0.3 V                                                                | 5     |       |       | mA   |

| I <sub>FG-short</sub>    | FG pin short current limit           | V <sub>FG</sub> = 12 V                                                                 |       | 20    | 25    | mA   |

| RD                       |                                      |                                                                                        |       |       |       |      |

| I <sub>RD-SINK</sub>     | RD pin sink current                  | V <sub>RD</sub> = 0.3 V                                                                | 5     |       |       | mA   |

| I <sub>RD-short</sub>    | RD pin short current limit           | $V_{RD} = 12 V$                                                                        |       | 20    | 25    | mA   |

| FR and FS                |                                      |                                                                                        |       |       |       |      |

| V <sub>FR-IH</sub>       | High-level input voltage             | $V_{CC} \ge 4.5 V$                                                                     | 2.3   |       |       | V    |

| V <sub>FR-IL</sub>       | Low-level input voltage              | $V_{CC} \ge 4.5 V$                                                                     |       |       | 0.8   | V    |

| V <sub>FS-th</sub>       | FS set threshold voltage             | $V_{CC} \ge 4.5 V$                                                                     | 2.3   |       | 0.8   | V    |

| V5                       |                                      |                                                                                        |       |       |       |      |

| V5                       | 5-V LDO voltage                      | $V_{CC} = 12 V$                                                                        | 4.75  | 5     | 5.25  | V    |

| $I_{V5}$                 | 5-V LDO load current                 | $V_{CC} = 12 V$                                                                        |       | 20    |       | mA   |

| LOCK PROT                | FECTION                              |                                                                                        |       |       |       |      |

| t                        | Lock dotoct time                     | FS = 0                                                                                 | 0.875 | 1.25  | 1.625 | 0    |

| tLOCK-ON                 | Lock detect time                     | FS = 1                                                                                 | 0.437 | 0.625 | 0.812 | S    |

| t                        | Lock release time                    | FS = 0                                                                                 | 4.375 | 6.25  | 8.125 | · ·  |

| tLOCK-OFF                |                                      | FS = 1                                                                                 | 2.187 | 3.125 | 4.06  | S    |

| CURRENT L                | IMIT                                 |                                                                                        |       |       |       |      |

|                          | Current limit                        | CS pin to GND resistor = 3.3 k $\Omega$                                                | 1.7   | 2     | 2.3   | А    |

| THERMAL S                | SHUTDOWN                             |                                                                                        | r     |       |       |      |

| Tanu                     | Shutdown temperature threshold       | Shutdown temperature                                                                   |       | 160   |       | °C   |

| T <sub>SDN</sub>         | Chaldown temperature threshold       | Hysteresis                                                                             |       | 10    |       | U    |

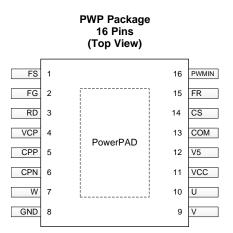

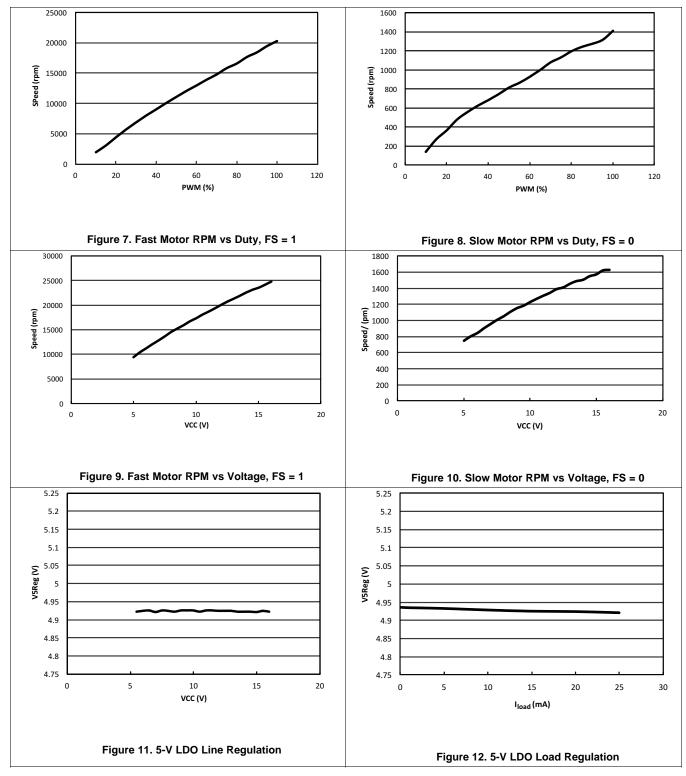

### 7.6 Typical Characteristics

SLWS237A-NOVEMBER 2012-REVISED NOVEMBER 2014

www.ti.com

#### **Typical Characteristics (continued)**

### 8 Detailed Description

#### 8.1 Overview

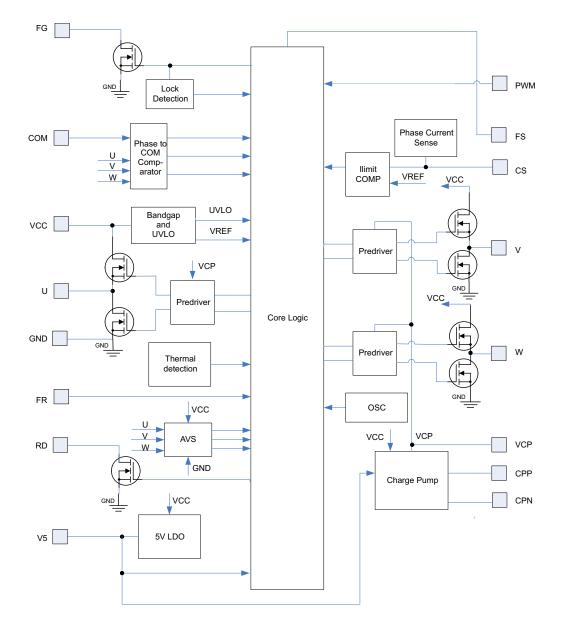

DRV11873 is a three-phase, sensorless motor driver with integrated power MOSFETs with drive current capability up to 1.5-A continuous and 2-A peak. It is specifically designed for fan motor drive applications with low noise and low external component count. DRV11873 has built-in overcurrent protection with no external current sense resistor needed. The synchronous rectification mode of operation achieves increased efficiency for motor driver applications. A 5-V LDO is available to provide up to 20 mA to an external load. DRV11873 outputs FG and RD to indicate motor status with open-drain output. A 150° sensorless BEMF control scheme was implemented for a three-phase motor. DRV11873 can fit a wide range of fan motors with the FS pin selection function. Motor speed can be controlled by adjusting  $V_{CC}$  or providing a PWM input. Voltage surge protection scheme prevents the input  $V_{CC}$  capacitor from overcharge during motor braking mode. DRV11873 has multiple built-in protection blocks including UVLO, overcurrent protection, lock protection, and thermal shutdown protection.

#### 8.2 Functional Block Diagram

Copyright © 2012–2014, Texas Instruments Incorporated

#### 8.3 Feature Description

#### 8.3.1 Speed Control

DRV11873 can control motor speed through either the PWM<sub>IN</sub> or V<sub>CC</sub> pin. Motor speed increases with higher PWM<sub>IN</sub> duty cycle or V<sub>CC</sub> input voltage. The curve of motor speed (RPM) vs PWM<sub>IN</sub> duty cycle or V<sub>CC</sub> input voltage is close to linear in most cases. However, motor characteristics affect the linearity of this speed curve. DRV11873 can operate at low V<sub>CC</sub> input voltage  $\geq$  4.1 V. The PWM<sub>IN</sub> pin is pulled up to V5 internally and the frequency range can vary from 7 to 100 kHz. The motor driver MOSFETs operate at a constant switching frequency of 125 kHz when the FS pin is pulled high and 62.5 kHz when the FS pin is pulled low. With this high switching frequency, DRV11873 can eliminate audible noise and reduce the ripple of V<sub>CC</sub> input voltage and current.

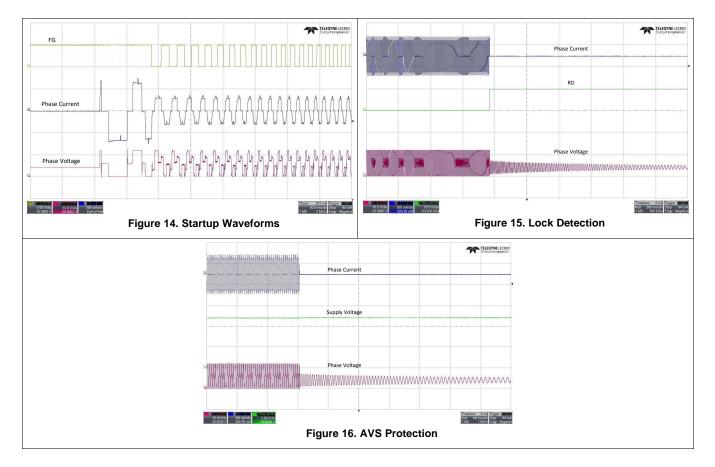

#### 8.3.2 Frequency Generator

The FG output is a 50% duty square wave output in the normal operation condition. Its frequency represents the motor speed and phase information. The FG pin is an open-drain output. An external pullup resistor is needed to connect any external system. During the start up, the FG output remains at high impedance until the motor speed reaches a certain level and BEMF is detected. If FG is not used, this pin can be left floating. The FG pin can be tied to either V5 or V<sub>CC</sub> through a pullup resistor. Normally, the pullup resistor value can be 100 k $\Omega$  or higher. During lock protection, the FG output remains high until the lockout protection is dismissed and restart is completed. A current limit function is built in for the FG pin which prevents the open-drain MOSFET from damage if V<sub>CC</sub> or V5 is accidentally connected to the FG pin. To calculate RPM based on FG frequency, refer to Equation 1.

$$\mathsf{RPM} = \frac{(\mathsf{FG} \times 60)}{\mathsf{pole pairs}}$$

where

• FG is in hertz (Hz)

(1)

#### 8.3.3 FS Setting

DRV11873 can fit a wide range of fan motors by setting the FS pin. For high speed fan motors with low motor winding resistance and low inductance, the FS pin should be pulled high. For low speed fan motors with high motor winding resistance and high inductance, the FS pin should be pulled low. Through FS pin selection, DRV11873 can be used for wide applications from low-speed refrigerator cooling fans to high-speed server cooling fans. FS status can only be set during device power up.

#### 8.3.4 Lock Protection and RD Output

If the motor is blocked or stopped by an external force, the lock protection will be triggered after detection time. During lock detection time, the circuit monitors the FG signal. If the FG output does not change state during the lock detection time, the lock protection will stop driving the motor. After lock release time, DRV11873 resumes driving the motor. If the lock condition is still present, DRV11873 proceeds with the next lock protection cycle until the lock condition is removed. With this lock protection, the motor and device do not get overheated or damaged. A different FS setting determines a different lock detection and lock release time. See the *Electrical Characteristics* for the different lock detection and release times.

The RD pin is an open-drain output which can be tied to either V5 or  $V_{CC}$  through a pullup resistor. Normally, the pullup resistor value can be 100 k $\Omega$  or higher. During the lock protection condition, the RD output remains high until the lock protection is dismissed and restart is completed. A current limit function is built in for the RD pin which prevents the open-drain MOSFET from damage if  $V_{CC}$  or V5 is accidentally connected to the RD pin.

#### 8.3.5 Reverse Spin Control FR

DRV11873 has an FR pin to set the motor for forward or reverse spin. During DRV11873 power up, FR status is set. During normal operation, the spin direction of the motor does not change if the FR status is changed. The FR status can be reset if the PWM<sub>IN</sub> is pulled low; if FS is high, PWM must be pulled low for 300  $\mu$ s, and if FS is low, PWM must be low for 600  $\mu$ s. After being pulled down for the appropriate time, the FR status resets upon the PWM rising edge.

#### Feature Description (continued)

#### 8.3.6 5-V LDO

DRV11873 has a built-in 5-V LDO which can output a 20-mA load current. It can provide 5-V bias voltage for external use. TI recommends a 2.2-µF ceramic capacitor to connect closely on the PCB layout between the V5 pin and ground.

#### 8.3.7 Overcurrent Protection

DRV11873 can adjust overcurrent through the external resistor connected to the CS pin and ground. Without using an external current sense resistor, DRV11873 senses the current through the power MOSFET. Therefore, no power loss occurs during the current sensing. This current sense architecture improves the system efficiency. Shorting the CS pin to ground disables overcurrent protection. During overcurrent protection, DRV11873 only limits the current to the motor and it does not shut down the operation. The overcurrent threshold can be set by the value of the external resistor through Equation 2.

$$I(A) = \frac{6600}{R_{cs}(\Omega)}$$

(2)

During motor start up, the overcurrent level is increased to 1.5 times the value set by R<sub>CS</sub>. If the overcurrent protection is triggered during the start up sequence, the motor will fail to start.

#### 8.3.8 UVLO

DRV11873 has a built-in UVLO function block. The hysteresis of the UVLO threshold is 200 mV. The device is locked out when  $V_{CC}$  reaches 4.1 V and woken up at 4.3 V.

#### 8.3.9 Thermal Shutdown

DRV11873 has a built-in thermal shutdown function, which shuts down the device when the junction temperature is over 160°C and resumes operating when the junction temperature drops back to 150°C.

#### 8.3.10 Anti-Voltage Surge (AVS)

The DRV11873 has a protection feature to prevent any energy from returning to the power supply when the motor is braked. This feature, AVS, protects the device as well as any other device from allowing  $V_{CC}$  from increasing. AVS works when the motor is braked to a lower speed and when the motor is stopped.

#### 8.4 Device Functional Modes

#### 8.4.1 Startup

At startup, commutation logic starts to drive the motor with one phase high, one phase low, and the third shut off. If a zero-cross is detected on the shut off phase, commutation logic advances to the next step; the same phase high, the shut off phase goes low, and the low phase is shut off. Initially, the BEMF is not strong enough to detect the zero crossings, at this very initial stage the commutation switches automatically until the BEMF is large enough to read. In startup mode, 100% duty cycle is applied regardless of PWM input. After the commutation logic receives 4 continuous successful zero-crossings, it switches to normal operation.

In certain cases, the motor may have initial speed when the device attempts to startup the motor again. When this occurs, the commutation logic jumps over the startup process and goes to normal operation directly.

#### 8.4.2 Closed Loop Control

After the motor is started successfully, the start up control switches to steady state operation. In steady state control, the motor is commutated 150°. This is an advanced trapezoidal method that allows the device to drive the phases gradually to the maximum current and gradually to 0 at commutation.

#### **Device Functional Modes (continued)**

#### 8.4.3 AVS Protection

When the device is commanded to decelerate or stop the motor, in order to protect the IC and the system, the DRV11873 has AVS protection. This function keeps the voltage supply,  $V_{CC}$ , from surging above the nominal value. To do this, the device monitors the current flow in the MOSFETs and is able to sense when the surging starts to occur. The AVS function controls the current, not allowing it to charge back to  $V_{CC}$  so that there is no voltage surging.

#### 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

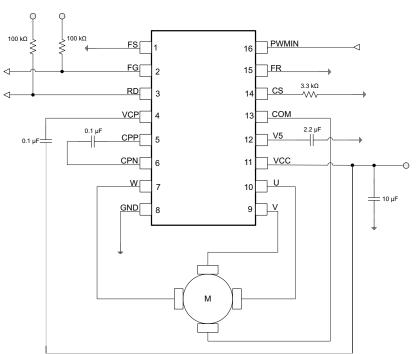

#### 9.1 Application Information

DRV11873 only requires five external components. The device needs a 10- $\mu$ F or higher ceramic capacitor connected to V<sub>CC</sub> and ground for decoupling. During layout, the strategy of ground copper pour is very important to enhance the thermal performance. For two or more layers, use eight thermal vias. Refer to *Layout Example* for an example of the PCB layout. For high current motors, place three Schottky diodes between phases U, V, W, and ground. Each diode anode terminal must be connected to ground and the cathode terminal must be connected to either U, V, or W. If there is no COM pin on the motor, one can be simulated. Use three resistors connected in a wye formation, one connected to U, one to V, and one to W. Connect the resistor ends opposite of the phases together. This center point is COM. To find the proper resistor value, start with a value of 10 kΩ and continue to decrease by 1 kΩ until the motor runs properly.

#### 9.2 Typical Application

Figure 13. Typical Application Schematic

#### 9.2.1 Design Requirements

#### **Table 1. Design Parameters**

|                      |                                           | MIN | TYP | MAX | UNIT |

|----------------------|-------------------------------------------|-----|-----|-----|------|

| Motor voltage        |                                           | 5   |     | 16  | V    |

| VCC capacitor        | Place as close to the pin as possible     |     | 10  |     | μF   |

| Operating current    | Running with normal load at rated speed   |     |     | 1.5 | А    |

| Absolute max current | During startup and locked motor condition |     |     | 2   | А    |

Copyright © 2012–2014, Texas Instruments Incorporated

DRV11873

SLWS237A-NOVEMBER 2012-REVISED NOVEMBER 2014

#### 9.2.2 Detailed Design Procedure

- 1. Refer to the *Design Requirements* and ensure the system meets the recommended application range.

- Ensure the  $V_{CC}$  level is in between 5 and 16 V

- Verify the motor needs no more than 1.5 A during runtime

- 2. Follow the application and *Power Supply Recommendations* when constructing the schematic.

- If the motor is high current/ high speed, use three Schottky diodes between the phases and ground.

- Make sure there is adequate capacitance on VCC, V5, VCP, CPP, and CPN.

- Size the resistor on CS according to the details given in feature description.

- Use a pull-up on FG and RD.

- If the motor doesn't have a common pin, create one using the method listed in Application Information.

- 3. Build the hardware according to the *Layout Guidelines*.

- Place the supply capacitors as close to the pins as possible.

- Route the U, V, W, and VCC traces to handle the allowed current.

- Ensure GND connections are made with the pin and thermal PAD.

- Use vias on the thermal pad to dissipate heat away from the IC.

- 4. Test the system with the application's motor to verify proper operation.

#### 9.2.3 Application Curves

#### **10 Power Supply Recommendations**

The DRV11873 is designed to operate from an input voltage supply,  $V_{CC}$ , range between 5 and 16 V. The user must place a 10-µF ceramic capacitor rated for VCC as close as possible to the VCC and GND pin. If the power supply ripple is more than 200 mV, in addition to the local decoupling capacitors, a bulk capacitance is required and must be sized according to the application requirements. If the bulk capacitance is implemented in the application, the user can reduce the value of the local ceramic capacitor to 1 µF.

### 11 Layout

#### 11.1 Layout Guidelines

- Place VCC, GND, U, V, and W pins with thick traces because high current passes through these traces.

- Place the 10-µF capacitor between VCC and GND, and as close to the VCC and GND pins as possible.

- Place the capacitor between CPP and CPN, and as close to the CPP and CPN pins as possible.

- Place the capacitor between V5 and GND as close to the V5 pin as possible.

- Connect the GND under the thermal pad.

- Keep the thermal pad connection as large as possible, both on the bottom side and top side. It should be one piece of copper without any gaps.

### 11.2 Layout Example

### **12 Device and Documentation Support**

#### 12.1 Trademarks

All trademarks are the property of their respective owners.

#### **12.2 Electrostatic Discharge Caution**

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### 12.3 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

### 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

#### **PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type (2) | Package   Pins    | Package qty   Carrier | <b>RoHS</b><br>(3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|---------------|-------------------|-------------------|-----------------------|--------------------|-------------------------------|----------------------------|--------------|------------------|

|                       |               |                   |                   |                       |                    | (4)                           | (5)                        |              |                  |

| DRV11873PWPR          | Active        | Production        | HTSSOP (PWP)   16 | 2000   LARGE T&R      | Yes                | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | 11873            |

| DRV11873PWPR.A        | Active        | Production        | HTSSOP (PWP)   16 | 2000   LARGE T&R      | Yes                | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | 11873            |

<sup>(1)</sup> **Status:** For more details on status, see our product life cycle.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

Texas

NSTRUMENTS

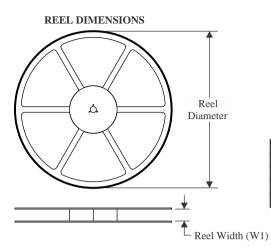

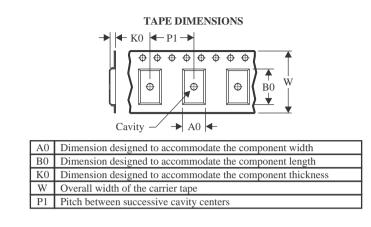

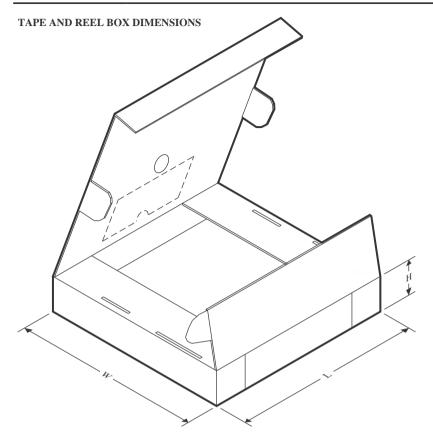

#### TAPE AND REEL INFORMATION

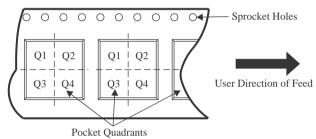

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions a | re nominal |

|-------------------|------------|

|-------------------|------------|

| Device       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| DRV11873PWPR | HTSSOP          | PWP                | 16 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

## PACKAGE MATERIALS INFORMATION

5-Dec-2023

\*All dimensions are nominal

| Γ | Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

|   | DRV11873PWPR | HTSSOP       | PWP             | 16   | 2000 | 350.0       | 350.0      | 43.0        |

## **GENERIC PACKAGE VIEW**

## PWP 16

# PowerPAD<sup>™</sup> TSSOP - 1.2 mm max height

PLASTIC SMALL OUTLINE

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

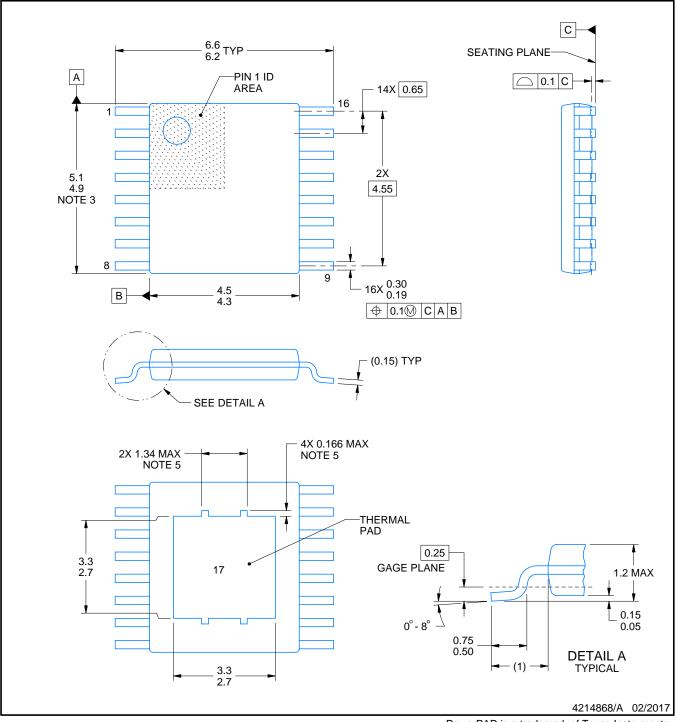

## **PWP0016A**

## **PACKAGE OUTLINE**

## PowerPAD<sup>™</sup> HTSSOP - 1.2 mm max height

PLASTIC SMALL OUTLINE

NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side. 4. Reference JEDEC registration MO-153.

- 5. Features may not be present.

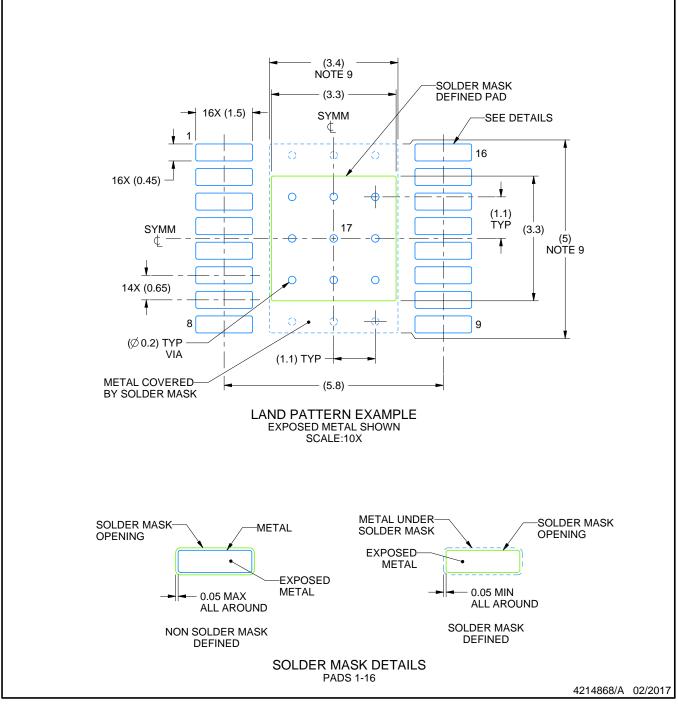

## **PWP0016A**

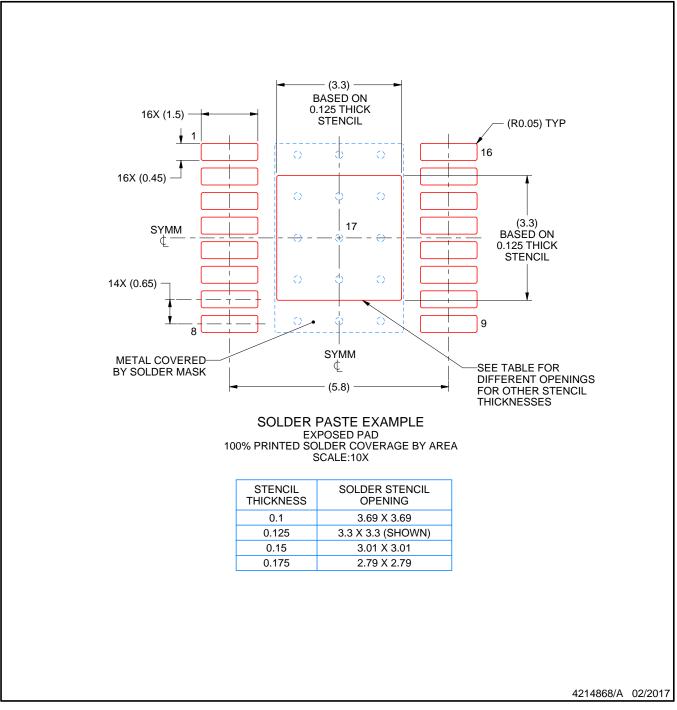

# **EXAMPLE BOARD LAYOUT**

# PowerPAD<sup>™</sup> HTSSOP - 1.2 mm max height

PLASTIC SMALL OUTLINE

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- 8. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 (www.ti.com/lit/slma002) and SLMA004 (www.ti.com/lit/slma004).

- 9. Size of metal pad may vary due to creepage requirement.

## **PWP0016A**

## **EXAMPLE STENCIL DESIGN**

## PowerPAD<sup>™</sup> HTSSOP - 1.2 mm max height

PLASTIC SMALL OUTLINE

NOTES: (continued)

- 10. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 11. Board assembly site may have different recommendations for stencil design.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated