# **PCF8563**

# Real-time clock/calendar Rev. 7 — 23 July 2010

**Product data sheet**

#### **General description** 1.

The PCF8563 is a CMOS<sup>1</sup> Real-Time Clock (RTC) and calendar optimized for low power consumption. A programmable clock output, interrupt output, and voltage-low detector are also provided. All addresses and data are transferred serially via a two-line bidirectional I<sup>2</sup>C-bus. Maximum bus speed is 400 kbit/s. The register address is incremented automatically after each written or read data byte.

#### **Features and benefits** 2.

- Provides year, month, day, weekday, hours, minutes, and seconds based on a 32.768 kHz quartz crystal

- Century flag

- Clock operating voltage: 1.0 V to 5.5 V at room temperature

- Low backup current; typical 0.25  $\mu$ A at  $V_{DD} = 3.0 \text{ V}$  and  $T_{amb} = 25 \text{ °C}$

- 400 kHz two-wire I<sup>2</sup>C-bus interface (at V<sub>DD</sub> = 1.8 V to 5.5 V)

- Programmable clock output for peripheral devices (32.768 kHz, 1.024 kHz, 32 Hz, and 1 Hz)

- Alarm and timer functions

- Integrated oscillator capacitor

- Internal Power-On Reset (POR)

- I<sup>2</sup>C-bus slave address: read A3h and write A2h

- Open-drain interrupt pin

# **Applications**

- Mobile telephones

- Portable instruments

- Electronic metering

- Battery powered products

The definition of the abbreviations and acronyms used in this data sheet can be found in Section 18.

#### Real-time clock/calendar

# 4. Ordering information

Table 1. Ordering information

| Type number | Package |                                                                                                                       |          |  |  |  |  |

|-------------|---------|-----------------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|

|             | Name    | Description                                                                                                           | Version  |  |  |  |  |

| PCF8563P    | DIP8    | plastic dual in-line package; 8 leads (300 mil)                                                                       | SOT97-1  |  |  |  |  |

| PCF8563T    | SO8     | plastic small outline package; 8 leads;<br>body width 3.9 mm                                                          | SOT96-1  |  |  |  |  |

| PCF8563TS   | TSSOP8  | plastic thin shrink small outline package; 8 leads; body width 3 mm                                                   | SOT505-1 |  |  |  |  |

| PCF8563BS   | HVSON10 | plastic thermal enhanced very thin small outline package; no leads; 10 terminals; body $3\times3\times0.85~\text{mm}$ | SOT650-1 |  |  |  |  |

# 5. Marking

Table 2. Marking codes

| Type number | Marking code |

|-------------|--------------|

| PCF8563P    | PCF8563P     |

| PCF8563T    | 8563T        |

| PCF8563TS   | 8563         |

| PCF8563BS   | 8563S        |

Real-time clock/calendar

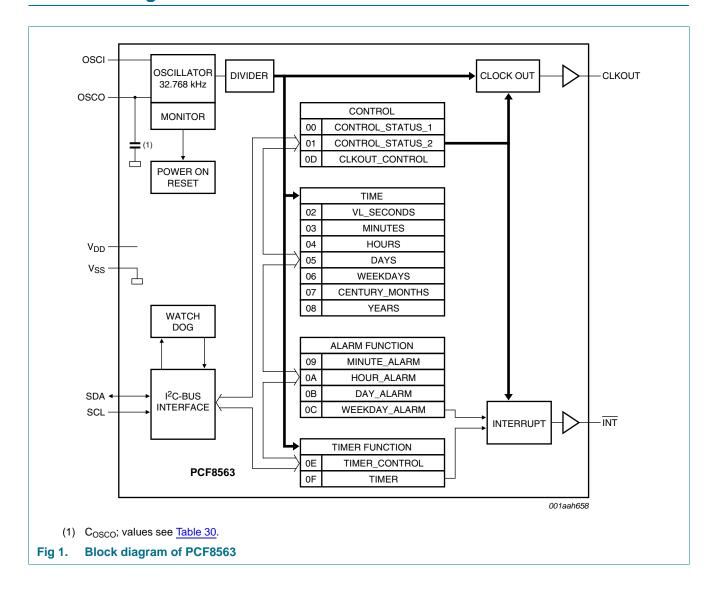

# 6. Block diagram

Real-time clock/calendar

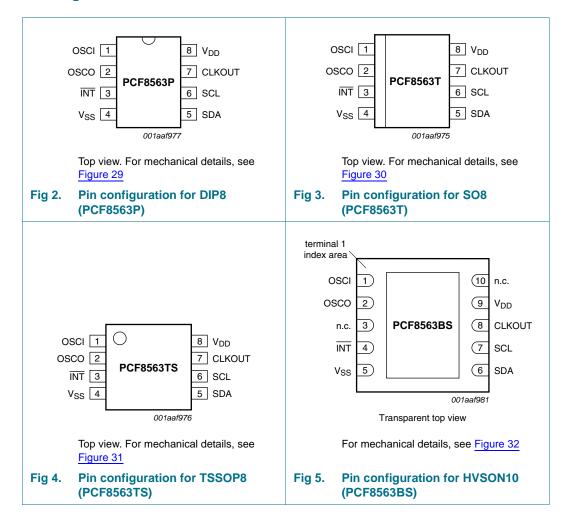

# 7. Pinning information

### 7.1 Pinning

#### Real-time clock/calendar

#### 7.2 Pin description

Table 3. Pin description

| Symbol   | Pin               |              | Description                                                  |  |

|----------|-------------------|--------------|--------------------------------------------------------------|--|

|          | DIP8, SO8, TSSOP8 | HVSON10      | _                                                            |  |

| OSCI     | 1                 | 1            | oscillator input                                             |  |

| OSCO     | 2                 | 2            | oscillator output                                            |  |

| ĪNT      | 3                 | 4            | interrupt output (open-drain; active LOW)                    |  |

| $V_{SS}$ | 4                 | 5 <u>[1]</u> | ground                                                       |  |

| SDA      | 5                 | 6            | serial data input and output                                 |  |

| SCL      | 6                 | 7            | serial clock input                                           |  |

| CLKOUT   | 7                 | 8            | clock output, open-drain                                     |  |

| $V_{DD}$ | 8                 | 9            | supply voltage                                               |  |

| n.c.     | -                 | 3, 10        | not connected; do not connect and do not use as feed through |  |

<sup>[1]</sup> The die paddle (exposed pad) is wired to V<sub>SS</sub> but should not be electrically connected.

# 8. Functional description

The PCF8563 contains sixteen 8-bit registers with an auto-incrementing register address, an on-chip 32.768 kHz oscillator with one integrated capacitor, a frequency divider which provides the source clock for the Real-Time Clock (RTC) and calender, a programmable clock output, a timer, an alarm, a voltage-low detector, and a 400 kHz I<sup>2</sup>C-bus interface.

All 16 registers are designed as addressable 8-bit parallel registers although not all bits are implemented. The first two registers (memory address 00h and 01h) are used as control and/or status registers. The memory addresses 02h through 08h are used as counters for the clock function (seconds up to years counters). Address locations 09h through 0Ch contain alarm registers which define the conditions for an alarm. Address 0Dh controls the CLKOUT output frequency. 0Eh and 0Fh are the Timer\_control and Timer registers, respectively.

The Seconds, Minutes, Hours, Days, Months, Years as well as the Minute\_alarm, Hour\_alarm, and Day\_alarm registers are all coded in Binary Coded Decimal (BCD) format.

When one of the RTC registers is written or read, the contents of all time counters are frozen. Therefore, faulty writing or reading of the clock and calendar during a carry condition is prevented.

### 8.1 CLKOUT output

A programmable square wave is available at the CLKOUT pin. Operation is controlled by the register CLKOUT\_control at address 0Dh. Frequencies of 32.768 kHz (default), 1.024 kHz, 32 Hz, and 1 Hz can be generated for use as a system clock, microcontroller clock, input to a charge pump, or for calibration of the oscillator. CLKOUT is an open-drain output and enabled at power-on. If disabled it becomes high-impedance.

Real-time clock/calendar

# 8.2 Register organization

#### Table 4. Formatted registers overview

Bit positions labelled as x are not relevant. Bit positions labelled with N should always be written with logic 0; if read they could be either logic 0 or logic 1. After reset, all registers are set according to <u>Table 27</u>.

| Address   | Register name       | Bit       | Bit               |                  |             |           |         |            |            |  |

|-----------|---------------------|-----------|-------------------|------------------|-------------|-----------|---------|------------|------------|--|

|           |                     | 7         | 6                 | 5                | 4           | 3         | 2       | 1          | 0          |  |

| Control a | nd status registers |           | '                 |                  | '           | '         | '       | '          | '          |  |

| 00h       | Control_status_1    | TEST1     | N                 | STOP             | N           | TESTC     | N       | N          | N          |  |

| 01h       | Control_status_2    | N         | N                 | N                | TI_TP       | AF        | TF      | AIE        | TIE        |  |

| Time and  | date registers      |           |                   |                  |             |           |         |            |            |  |

| 02h       | 2h VL_seconds \     |           | SECONDS (0 to 59) |                  |             |           |         |            |            |  |

| 03h       | Minutes             | x         | MINUTES (0 to 59) |                  |             |           |         |            |            |  |

| 04h       | Hours               | x         | x HOURS (0 to 23) |                  |             |           |         |            |            |  |

| 05h       | Days                | х         | х                 | x DAYS (1 to 31) |             |           |         |            |            |  |

| 06h       | Weekdays            | х         | х                 | x                | х           | х         | WEEKDA' | YS (0 to 6 | )          |  |

| 07h       | Century_months      | С         | х                 | х                | MONTHS      | (1 to 12) |         |            |            |  |

| 08h       | Years               | YEARS (0  | to 99)            |                  |             |           |         |            |            |  |

| Alarm reg | jisters             |           |                   |                  |             |           |         |            |            |  |

| 09h       | Minute_alarm        | AE_M      | MINUTE_/          | ALARM (0 to      | o 59)       |           |         |            |            |  |

| 0Ah       | Hour_alarm          | AE_H      | х                 | HOUR_AL          | ARM (0 to 2 | 23)       |         |            |            |  |

| 0Bh       | Day_alarm           | AE_D      | х                 | DAY_ALAI         | RM (1 to 31 | )         |         |            |            |  |

| 0Ch       | Weekday_alarm       | AE_W      | х                 | х                | х           | х         | WEEKDA' | Y_ALARM    | 1 (0 to 6) |  |

| CLKOUT    | control register    |           |                   |                  |             |           |         |            |            |  |

| 0Dh       | CLKOUT_control      | FE        | х                 | х                | х           | х         | х       | FD[1:0]    |            |  |

| Timer reg | isters              |           |                   |                  |             |           |         |            |            |  |

| 0Eh       | Timer_control       | TE        | х                 | х                | х           | х         | х       | TD[1:0]    |            |  |

| 0Fh       | Timer               | TIMER[7:0 | 0]                |                  |             |           |         |            |            |  |

#### Real-time clock/calendar

# 8.3 Control registers

# 8.3.1 Register Control\_status\_1

Table 5. Control\_status\_1 - control and status register 1 (address 00h) bit description

| Bit    | Symbol | Value  | Description                                                                                                                            | Reference      |

|--------|--------|--------|----------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 7      | TEST1  | 0[1]   | normal mode                                                                                                                            | Section 8.9    |

|        |        |        | must be set to logic 0 during normal operations                                                                                        |                |

|        |        | 1      | EXT_CLK test mode                                                                                                                      |                |

| 6      | N      | 0[2]   | unused                                                                                                                                 |                |

| 5      | STOP   | 0[1]   | RTC source clock runs                                                                                                                  | Section 8.10   |

|        |        | 1      | all RTC divider chain flip-flops are asynchronously set to logic 0; the RTC clock is stopped (CLKOUT at 32.768 kHz is still available) |                |

| 4      | N      | 0[2]   | unused                                                                                                                                 |                |

| 3      | TESTC  | 0      | Power-On Reset (POR) override facility is disabled; set to logic 0 for normal operation                                                | Section 8.11.1 |

|        |        | 1[1]   | Power-On Reset (POR) override may be enabled                                                                                           |                |

| 2 to 0 | N      | 000[2] | unused                                                                                                                                 |                |

<sup>[1]</sup> Default value.

# 8.3.2 Register Control\_status\_2

Table 6. Control\_status\_2 - control and status register 2 (address 01h) bit description

| Bit    | Symbol | Value  | Description                                                                                               | Reference       |  |  |

|--------|--------|--------|-----------------------------------------------------------------------------------------------------------|-----------------|--|--|

| 7 to 5 | N      | 000[1] | unused                                                                                                    |                 |  |  |

| 4      | TI_TP  | 0[2]   | INT is active when TF is active (subject to the status of TIE)                                            | Section 8.3.2.1 |  |  |

|        |        | 1      | INT pulses active according to <u>Table 7</u> (subject to the status of TIE);                             | and             |  |  |

|        |        |        | <b>Remark:</b> note that if AF and AIE are active then $\overline{\text{INT}}$ will be permanently active | Section 8.8     |  |  |

| 3      | AF     | 0[2]   | read: alarm flag inactive                                                                                 | Section 8.3.2.1 |  |  |

|        |        |        | write: alarm flag is cleared                                                                              |                 |  |  |

|        |        | 1      | read: alarm flag active                                                                                   |                 |  |  |

|        |        |        | write: alarm flag remains unchanged                                                                       |                 |  |  |

| 2      | TF     | 0[2]   | read: timer flag inactive                                                                                 |                 |  |  |

|        |        |        | write: timer flag is cleared                                                                              |                 |  |  |

|        |        | 1      | read: timer flag active                                                                                   |                 |  |  |

|        |        |        | write: timer flag remains unchanged                                                                       |                 |  |  |

| 1      | AIE    | 0[2]   | alarm interrupt disabled                                                                                  |                 |  |  |

|        |        | 1      | alarm interrupt enabled                                                                                   |                 |  |  |

| 0      | TIE    | 0[2]   | timer interrupt disabled                                                                                  |                 |  |  |

|        |        | 1      | timer interrupt enabled                                                                                   |                 |  |  |

<sup>[1]</sup> Bits labeled as N should always be written with logic 0.

All information provided in this document is subject to legal disclaimers.

<sup>[2]</sup> Bits labeled as N should always be written with logic 0.

<sup>[2]</sup> Default value.

Real-time clock/calendar

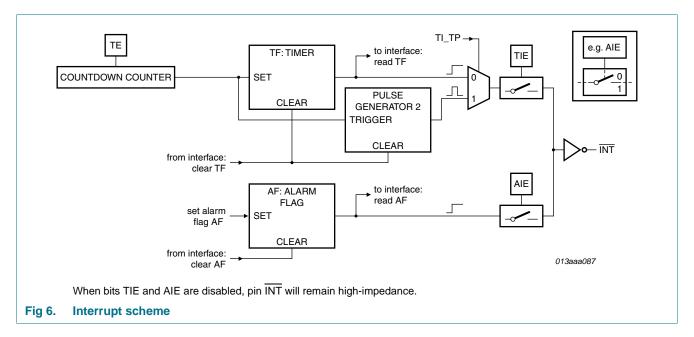

#### 8.3.2.1 Interrupt output

**Bits TF and AF:** When an alarm occurs, AF is set to logic 1. Similarly, at the end of a timer countdown, TF is set to logic 1. These bits maintain their value until overwritten using the interface. If both timer and alarm interrupts are required in the application, the source of the interrupt can be determined by reading these bits. To prevent one flag being overwritten while clearing another, a logic AND is performed during a write access.

**Bits TIE and AIE:** These bits activate or deactivate the generation of an interrupt when TF or AF is asserted, respectively. The interrupt is the logical OR of these two conditions when both AIE and TIE are set.

**Countdown timer interrupts:** The pulse generator for the countdown timer interrupt uses an internal clock and is dependent on the selected source clock for the countdown timer and on the countdown value n. As a consequence, the width of the interrupt pulse varies (see Table 7).

Table 7.  $\overline{INT}$  operation (bit  $TI_TP = 1)$

| Source clock (Hz) | INT period (s)     |          |  |  |  |

|-------------------|--------------------|----------|--|--|--|

|                   | n = 1[2]           | n > 1[2] |  |  |  |

| 4096              | <sup>1</sup> /8192 | 1/4096   |  |  |  |

| 64                | 1/128              | 1/64     |  |  |  |

| 1                 | 1/64               | 1/64     |  |  |  |

| 1/60              | 1/64               | 1/64     |  |  |  |

<sup>[1]</sup> TF and  $\overline{\text{INT}}$  become active simultaneously.

[2] n = loaded countdown value. Timer stops when n = 0.

#### Real-time clock/calendar

### 8.4 Time and date registers

The majority of the registers are coded in the BCD format to simplify application use.

#### 8.4.1 Register VL\_seconds

Table 8. VL\_seconds - seconds and clock integrity status register (address 02h) bit description

| Bit    | Symbol  | Value  | Place value | Description                                            |

|--------|---------|--------|-------------|--------------------------------------------------------|

| 7      | VL      | 0      | -           | clock integrity is guaranteed                          |

|        |         | 1[1]   | -           | integrity of the clock information is not guaranteed   |

| 6 to 4 | SECONDS | 0 to 5 | ten's place | actual seconds coded in BCD format, see <u>Table 9</u> |

| 3 to 0 |         | 0 to 9 | unit place  |                                                        |

<sup>[1]</sup> Start-up value.

Table 9. Seconds coded in BCD format

| Seconds value | Upper-c | Jpper-digit (ten's place) |       | Digit (u | Digit (unit place) |       |       |

|---------------|---------|---------------------------|-------|----------|--------------------|-------|-------|

| (decimal)     | Bit 6   | Bit 5                     | Bit 4 | Bit 3    | Bit 2              | Bit 1 | Bit 0 |

| 00            | 0       | 0                         | 0     | 0        | 0                  | 0     | 0     |

| 01            | 0       | 0                         | 0     | 0        | 0                  | 0     | 1     |

| 02            | 0       | 0                         | 0     | 0        | 0                  | 1     | 0     |

| :             | :       | :                         | :     | :        | :                  | :     | :     |

| 09            | 0       | 0                         | 0     | 1        | 0                  | 0     | 1     |

| 10            | 0       | 0                         | 1     | 0        | 0                  | 0     | 0     |

| :             | :       | :                         | :     | :        | :                  | :     | :     |

| 58            | 1       | 0                         | 1     | 1        | 0                  | 0     | 0     |

| 59            | 1       | 0                         | 1     | 1        | 0                  | 0     | 1     |

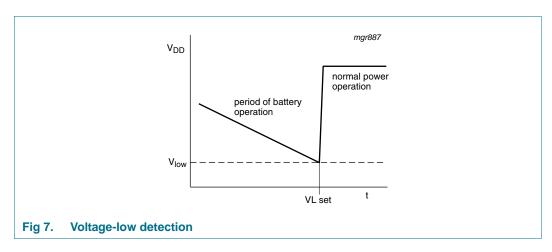

#### 8.4.1.1 Voltage-low detector and clock monitor

The PCF8563 has an on-chip voltage-low detector (see Figure 7). When  $V_{DD}$  drops below  $V_{low}$ , bit VL in the VL\_seconds register is set to indicate that the integrity of the clock information is no longer guaranteed. The VL flag can only be cleared by using the interface.

PCF8563

All information provided in this document is subject to legal disclaimers.

#### Real-time clock/calendar

The VL flag is intended to detect the situation when  $V_{DD}$  is decreasing slowly, for example under battery operation. Should the oscillator stop or  $V_{DD}$  reach  $V_{low}$  before power is re-asserted, then the VL flag is set. This will indicate that the time may be corrupted.

#### 8.4.2 Register Minutes

Table 10. Minutes - minutes register (address 03h) bit description

| Bit    | Symbol  | Value  | Place value | Description                        |

|--------|---------|--------|-------------|------------------------------------|

| 7      | -       | -      | -           | unused                             |

| 6 to 4 | MINUTES | 0 to 5 | ten's place | actual minutes coded in BCD format |

| 3 to 0 |         | 0 to 9 | unit place  |                                    |

#### 8.4.3 Register Hours

Table 11. Hours - hours register (address 04h) bit description

| Bit    | Symbol | Value  | Place value | Description                      |

|--------|--------|--------|-------------|----------------------------------|

| 7 to 6 | -      | -      | -           | unused                           |

| 5 to 4 | HOURS  | 0 to 2 | ten's place | actual hours coded in BCD format |

| 3 to 0 |        | 0 to 9 | unit place  |                                  |

#### 8.4.4 Register Days

Table 12. Days - days register (address 05h) bit description

| Bit    | Symbol  | Value  | Place value | Description                    |

|--------|---------|--------|-------------|--------------------------------|

| 7 to 6 | -       | -      | -           | unused                         |

| 5 to 4 | DAYS[1] | 0 to 3 | ten's place | actual day coded in BCD format |

| 3 to 0 |         | 0 to 9 | unit place  |                                |

<sup>[1]</sup> The PCF8563 compensates for leap years by adding a 29th day to February if the year counter contains a value which is exactly divisible by 4, including the year 00.

#### 8.4.5 Register Weekdays

Table 13. Weekdays - weekdays register (address 06h) bit description

| Bit    | Symbol   | Value  | Description                         |

|--------|----------|--------|-------------------------------------|

| 7 to 3 | -        | -      | unused                              |

| 2 to 0 | WEEKDAYS | 0 to 6 | actual weekday values, see Table 14 |

#### Real-time clock/calendar

Table 14. Weekday assignments

| Day[1]    | Bit |   |   |  |  |

|-----------|-----|---|---|--|--|

|           | 2   | 1 | 0 |  |  |

| Sunday    | 0   | 0 | 0 |  |  |

| Monday    | 0   | 0 | 1 |  |  |

| Tuesday   | 0   | 1 | 0 |  |  |

| Wednesday | 0   | 1 | 1 |  |  |

| Thursday  | 1   | 0 | 0 |  |  |

| Friday    | 1   | 0 | 1 |  |  |

| Saturday  | 1   | 1 | 0 |  |  |

<sup>[1]</sup> Definition may be re-assigned by the user.

### 8.4.6 Register Century\_months

Table 15. Century\_months - century flag and months register (address 07h) bit description

| Bit    | Symbol | Value  | Place value | Description                                    |

|--------|--------|--------|-------------|------------------------------------------------|

| 7      | C[1]   | 0[2]   | -           | indicates the century is x                     |

|        |        | 1      | -           | indicates the century is x + 1                 |

| 6 to 5 | -      | -      | -           | unused                                         |

| 4      | MONTHS | 0 to 1 | ten's place | actual month coded in BCD format, see Table 16 |

| 3 to 0 |        | 0 to 9 | unit place  |                                                |

<sup>[1]</sup> This bit may be re-assigned by the user.

Table 16. Month assignments in BCD format

| Month     | Upper-digit (ten's place) | Digit (unit place) |       |       |       |  |

|-----------|---------------------------|--------------------|-------|-------|-------|--|

|           | Bit 4                     | Bit 3              | Bit 2 | Bit 1 | Bit 0 |  |

| January   | 0                         | 0                  | 0     | 0     | 1     |  |

| February  | 0                         | 0                  | 0     | 1     | 0     |  |

| March     | 0                         | 0                  | 0     | 1     | 1     |  |

| April     | 0                         | 0                  | 1     | 0     | 0     |  |

| May       | 0                         | 0                  | 1     | 0     | 1     |  |

| June      | 0                         | 0                  | 1     | 1     | 0     |  |

| July      | 0                         | 0                  | 1     | 1     | 1     |  |

| August    | 0                         | 1                  | 0     | 0     | 0     |  |

| September | 0                         | 1                  | 0     | 0     | 1     |  |

| October   | 1                         | 0                  | 0     | 0     | 0     |  |

| November  | 1                         | 0                  | 0     | 0     | 1     |  |

| December  | 1                         | 0                  | 0     | 1     | 0     |  |

**Product data sheet**

<sup>[2]</sup> This bit is toggled when the register Years overflows from 99 to 00.

#### Real-time clock/calendar

#### 8.4.7 Register Years

Table 17. Years - years register (08h) bit description

| Bit    | Symbol | Value  | Place value | Description                        |

|--------|--------|--------|-------------|------------------------------------|

| 7 to 4 | YEARS  | 0 to 9 | ten's place | actual year coded in BCD format[1] |

| 3 to 0 |        | 0 to 9 | unit place  |                                    |

<sup>[1]</sup> When the register Years overflows from 99 to 00, the century bit C in the register Century\_months is toggled.

### 8.5 Setting and reading the time

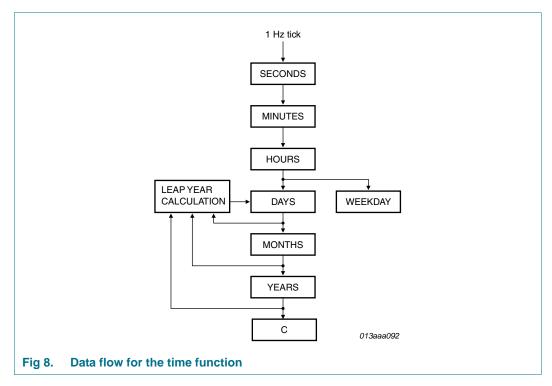

Figure 8 shows the data flow and data dependencies starting from the 1 Hz clock tick.

During read/write operations, the time counting circuits (memory locations 02h through 08h) are blocked.

#### This prevents

- Faulty reading of the clock and calendar during a carry condition

- Incrementing the time registers, during the read cycle

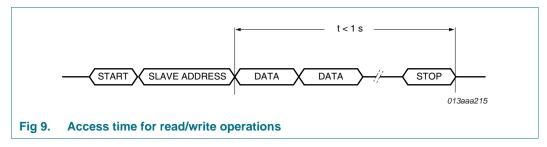

After this read/write access is completed, the time circuit is released again and any pending request to increment the time counters that occurred during the read access is serviced. A maximum of 1 request can be stored; therefore, all accesses must be completed within 1 second (see Figure 9).

#### Real-time clock/calendar

As a consequence of this method, it is very important to make a read or write access in one go, that is, setting or reading seconds through to years should be made in one single access. Failing to comply with this method could result in the time becoming corrupted.

As an example, if the time (seconds through to hours) is set in one access and then in a second access the date is set, it is possible that the time may increment between the two accesses. A similar problem exists when reading. A roll over may occur between reads thus giving the minutes from one moment and the hours from the next.

Recommended method for reading the time:

- 1. Send a START condition and the slave address for write (A2h).

- 2. Set the address pointer to 2 (VL\_seconds) by sending 02h.

- 3. Send a RESTART condition or STOP followed by START.

- 4. Send the slave address for read (A3h).

- 5. Read VL\_seconds.

- 6. Read Minutes.

- 7. Read Hours.

- 8. Read Days.

- 9. Read Weekdays.

- 10. Read Century\_months.

- 11. Read Years.

- 12. Send a STOP condition.

#### Real-time clock/calendar

# 8.6 Alarm registers

#### 8.6.1 Register Minute\_alarm

Table 18. Minute\_alarm - minute alarm register (address 09h) bit description

| Bit    | Symbol       | Value  | Place value | Description                           |

|--------|--------------|--------|-------------|---------------------------------------|

| 7      | AE_M         | 0      | -           | minute alarm is enabled               |

|        |              | 1[1]   | -           | minute alarm is disabled              |

| 6 to 4 | MINUTE_ALARM | 0 to 5 | ten's place | minute alarm information coded in BCD |

| 3 to 0 |              | 0 to 9 | unit place  | format                                |

<sup>[1]</sup> Default value.

#### 8.6.2 Register Hour\_alarm

Table 19. Hour\_alarm - hour alarm register (address 0Ah) bit description

| Bit    | Symbol     | Value  | Place value | Description                         |

|--------|------------|--------|-------------|-------------------------------------|

| 7      | AE_H       | 0      | -           | hour alarm is enabled               |

|        |            | 1[1]   | -           | hour alarm is disabled              |

| 6      | -          | -      | -           | unused                              |

| 5 to 4 | HOUR_ALARM | 0 to 2 | ten's place | hour alarm information coded in BCD |

| 3 to 0 |            | 0 to 9 | unit place  | format                              |

<sup>[1]</sup> Default value.

#### 8.6.3 Register Day\_alarm

Table 20. Day\_alarm - day alarm register (address 0Bh) bit description

| Bit              | Symbol | Value       | Place value                        | Description           |

|------------------|--------|-------------|------------------------------------|-----------------------|

| 7                | AE_D   | 0           | -                                  | day alarm is enabled  |

|                  |        | 1[1]        | -                                  | day alarm is disabled |

| 6                | -      | -           | -                                  | unused                |

| 5 to 4 DAY_ALARM | 0 to 3 | ten's place | day alarm information coded in BCD |                       |

| 3 to 0           |        | 0 to 9      | unit place                         | format                |

<sup>[1]</sup> Default value.

#### 8.6.4 Register Weekday\_alarm

Table 21. Weekday\_alarm - weekday alarm register (address 0Ch) bit description

| Bit    | Symbol        | Value        | Description               |

|--------|---------------|--------------|---------------------------|

| 7      | AE_W          | 0            | weekday alarm is enabled  |

|        |               | 1 <u>[1]</u> | weekday alarm is disabled |

| 6 to 3 | -             | -            | unused                    |

| 2 to 0 | WEEKDAY_ALARM | 0 to 6       | weekday alarm information |

|        |               |              |                           |

<sup>[1]</sup> Default value.

Real-time clock/calendar

#### 8.6.5 Alarm flag

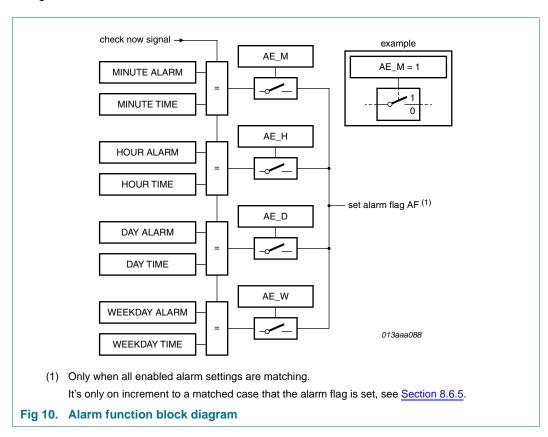

By clearing the alarm enable bit (AE\_x) of one or more of the alarm registers, the corresponding alarm condition(s) are active. When an alarm occurs, AF is set to logic 1. The asserted AF can be used to generate an interrupt (INT). The AF is cleared using the interface.

The registers at addresses 09h through 0Ch contain alarm information. When one or more of these registers is loaded with minute, hour, day or weekday, and its corresponding AE\_x is logic 0, then that information is compared with the current minute, hour, day, and weekday. When all enabled comparisons first match, the alarm flag (AF in register Control\_2) is set to logic 1.

The generation of interrupts from the alarm function is controlled via bit AIE. If bit AIE is enabled, the INT pin follows the condition of bit AF. AF will remain set until cleared by the interface. Once AF has been cleared, it will only be set again when the time increments to match the alarm condition once more. Alarm registers which have their AE\_x bit at logic 1 are ignored.

# 8.7 Register CLKOUT\_control and clock output

Frequencies of 32.768 kHz (default), 1.024 kHz, 32 Hz, and 1 Hz can be generated for use as a system clock, microcontroller clock, input to a charge pump, or for calibration of the oscillator.

**Product data sheet**

#### Real-time clock/calendar

Table 22. CLKOUT\_control - CLKOUT control register (address 0Dh) bit description

| Bit    | Symbol  | Value | Description                                                        |

|--------|---------|-------|--------------------------------------------------------------------|

| 7      | FE      | 0     | the CLKOUT output is inhibited and CLKOUT output is set to logic 0 |

|        |         | 1[1]  | the CLKOUT output is activated                                     |

| 6 to 2 | -       | -     | unused                                                             |

| 1 to 0 | FD[1:0] |       | frequency output at pin CLKOUT                                     |

|        |         | 00[1] | 32.768 kHz                                                         |

|        |         | 01    | 1.024 kHz                                                          |

|        |         | 10    | 32 Hz                                                              |

|        |         | 11    | 1 Hz                                                               |

<sup>[1]</sup> Default value.

#### 8.8 Timer function

The 8-bit countdown timer at address 0Fh is controlled by the Timer\_control register at address 0Eh. The Timer\_control register determines one of 4 source clock frequencies for the timer (4096 Hz, 64 Hz, 1 Hz, or  $\frac{1}{60}$  Hz), and enables or disables the timer. The timer counts down from a software-loaded 8-bit binary value. At the end of every countdown, the timer sets the timer flag TF. The TF may only be cleared by using the interface. The asserted TF can be used to generate an interrupt on pin INT. The interrupt may be generated as a pulsed signal every countdown period or as a permanently active signal which follows the state of TF. Bit TI\_TP is used to control this mode selection. When reading the timer, the current countdown value is returned.

#### 8.8.1 Register Timer\_control

Table 23. Timer\_control - timer control register (address 0Eh) bit description

| Bit            | Symbol   | Value        | Description                            |

|----------------|----------|--------------|----------------------------------------|

| 7              | TE       | 0 <u>[1]</u> | timer is disabled                      |

|                |          | 1            | timer is enabled                       |

| 6 to 2         | <u> </u> | -            | unused                                 |

| 1 to 0 TD[1:0] |          |              | timer source clock frequency select[2] |

|                |          | 00           | 4.096 kHz                              |

|                |          | 01           | 64 Hz                                  |

|                |          | 10           | 1 Hz                                   |

|                |          | 11[2]        | ¹⁄ <sub>60</sub> Hz                    |

<sup>[1]</sup> Default value.

<sup>[2]</sup> These bits determine the source clock for the countdown timer; when not in use, TD[1:0] should be set to  $^{1}/_{60}$  Hz for power saving.

Real-time clock/calendar

#### 8.8.2 Register Timer

Table 24. Timer - timer value register (address 0Fh) bit description

| Bit    | Symbol     | Value      | Description                                        |

|--------|------------|------------|----------------------------------------------------|

| 7 to 0 | TIMER[7:0] | 00h to FFh | countdown period in seconds:                       |

|        |            |            | $CountdownPeriod = \frac{n}{SourceClockFrequency}$ |

|        |            |            | where n is the countdown value                     |

Table 25. Timer register bits value range

| Bit |    |    |    |   |   |   |   |

|-----|----|----|----|---|---|---|---|

| 7   | 6  | 5  | 4  | 3 | 2 | 1 | 0 |

| 128 | 64 | 32 | 16 | 8 | 4 | 2 | 1 |

The register Timer is an 8-bit binary countdown timer. It is enabled and disabled via the Timer\_control register bit TE. The source clock for the timer is also selected by the Timer\_control register. Other timer properties such as interrupt generation are controlled via the register Control\_status\_2.

For accurate read back of the count down value, it is recommended to read the register twice and check for consistent results, since it is not possible to freeze the countdown timer counter during read back.

#### 8.9 EXT CLK test mode

A test mode is available which allows for on-board testing. In such a mode it is possible to set up test conditions and control the operation of the RTC.

The test mode is entered by setting bit TEST1 in register Control\_status\_1. Then pin CLKOUT becomes an input. The test mode replaces the internal 64 Hz signal with the signal applied to pin CLKOUT. Every 64 positive edges applied to pin CLKOUT will then generate an increment of one second.

The signal applied to pin CLKOUT should have a minimum pulse width of 300 ns and a maximum period of 1000 ns. The internal 64 Hz clock, now sourced from CLKOUT, is divided down to 1 Hz by a 2<sup>6</sup> divide chain called a prescaler. The prescaler can be set into a known state by using bit STOP. When bit STOP is set, the prescaler is reset to 0 (STOP must be cleared before the prescaler can operate again).

From a STOP condition, the first 1 second increment will take place after 32 positive edges on CLKOUT. Thereafter, every 64 positive edges will cause a one-second increment.

**Remark:** Entry into EXT\_CLK test mode is not synchronized to the internal 64 Hz clock. When entering the test mode, no assumption as to the state of the prescaler can be made.

#### 8.9.1 Operation example:

- 1. Set EXT CLK test mode (Control status 1, bit TEST1 = 1).

- 2. Set STOP (Control status 1, bit STOP = 1).

- 3. Clear STOP (Control status 1, bit STOP = 0).

- 4. Set time registers to desired value.

All information provided in this document is subject to legal disclaimers.

Real-time clock/calendar

- 5. Apply 32 clock pulses to CLKOUT.

- 6. Read time registers to see the first change.

- 7. Apply 64 clock pulses to CLKOUT.

- 8. Read time registers to see the second change.

Repeat steps 7 and 8 for additional increments.

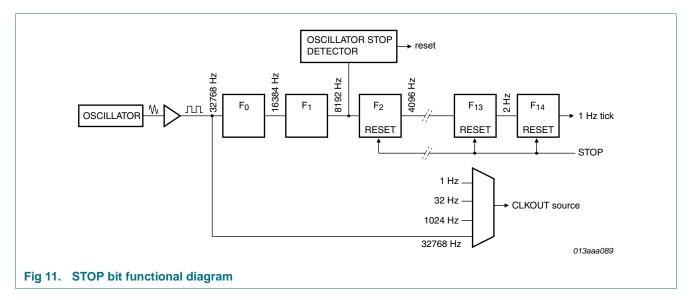

#### 8.10 STOP bit function

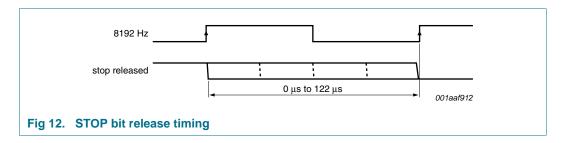

The function of the STOP bit is to allow for accurate starting of the time circuits. The STOP bit function will cause the upper part of the prescaler ( $F_2$  to  $F_{14}$ ) to be held in reset and thus no 1 Hz ticks will be generated (see <u>Figure 11</u>). The time circuits can then be set and will not increment until the STOP bit is released (see <u>Figure 12</u> and <u>Table 26</u>).

The STOP bit function will not affect the output of 32.768 kHz on CLKOUT, but will stop the generation of 1.024 kHz, 32 Hz, and 1 Hz.

The lower two stages of the prescaler ( $F_0$  and  $F_1$ ) are not reset; and because the  $I^2$ C-bus is asynchronous to the crystal oscillator, the accuracy of re-starting the time circuits will be between zero and one 8.192 kHz cycle (see Figure 12).

PCF8563

#### Real-time clock/calendar

Table 26. First increment of time circuits after STOP bit release

| Bit      | Prescaler bits                                                   | [1]                             | 1 Hz tick    | Time            | Comment                                                           |

|----------|------------------------------------------------------------------|---------------------------------|--------------|-----------------|-------------------------------------------------------------------|

| STOP     | F <sub>0</sub> F <sub>1</sub> -F <sub>2</sub> to F <sub>14</sub> |                                 |              | hh:mm:ss        |                                                                   |

| Clock is | running normally                                                 |                                 |              |                 |                                                                   |

| 0        | 01-0 0001 1101 0100                                              |                                 |              | 12:45:12        | prescaler counting normally                                       |

| STOP bi  | t is activated by user.                                          | F <sub>0</sub> F <sub>1</sub> a | are not rese | t and values ca | nnot be predicted externally                                      |

| 1        | XX-0 0000 0000 0000                                              |                                 |              | 12:45:12        | prescaler is reset; time circuits are frozen                      |

| New time | e is set by user                                                 |                                 |              |                 |                                                                   |

| 1        | XX-0 0000 0000 0000                                              |                                 |              | 08:00:00        | prescaler is reset; time circuits are frozen                      |

| STOP bi  | t is released by user                                            |                                 |              |                 |                                                                   |

| 0        | XX-0 0000 0000 0000                                              |                                 | • I          | 08:00:00        | prescaler is now running                                          |

|          | XX-1 0000 0000 0000                                              |                                 |              | 08:00:00        | -                                                                 |

|          | XX-0 1000 0000 0000                                              | 507                             |              | 08:00:00        | -                                                                 |

|          | XX-1 1000 0000 0000                                              |                                 |              | 08:00:00        | -                                                                 |

|          | :                                                                | 784,                            |              | :               | :                                                                 |

|          | 11-1 1111 1111 1110                                              | 7                               | 3            | 08:00:00        | -                                                                 |

|          | 00-0 0000 0000 0001                                              |                                 |              | 08:00:01        | 0 to 1 transition of $F_{14}$ increments the time circuits        |

|          | 10-0 0000 0000 0001                                              |                                 |              | 08:00:01        | -                                                                 |

|          | :                                                                | _                               | n ]          | :               | :                                                                 |

|          | 11-1 1111 1111 1111                                              |                                 |              | 08:00:01        | -                                                                 |

|          | 00-0 0000 0000 0000                                              |                                 | 000          | 08:00:01        | -                                                                 |

|          | 10-0 0000 0000 0000                                              |                                 |              | 08:00:01        | -                                                                 |

|          | :                                                                |                                 |              | :               | :                                                                 |

|          | 11-1 1111 1111 1110                                              |                                 |              | 08:00:01        | -                                                                 |

|          | 00-0 0000 0000 0001                                              |                                 |              | 08:00:02        | 0 to 1 transition of F <sub>14</sub> increments the time circuits |

#### [1] $F_0$ is clocked at 32.768 kHz.

The first increment of the time circuits is between 0.507813 s and 0.507935 s after STOP bit is released. The uncertainty is caused by the prescaler bits  $F_0$  and  $F_1$  not being reset (see <u>Table 26</u>) and the unknown state of the 32 kHz clock.

#### **8.11 Reset**

The PCF8563 includes an internal reset circuit which is active whenever the oscillator is stopped. In the reset state the I<sup>2</sup>C-bus logic is initialized including the address pointer and all registers are set according to <u>Table 27</u>. I<sup>2</sup>C-bus communication is not possible during reset.

#### Real-time clock/calendar

Table 27. Register reset value[1]

| Address | Register name    | Bit |   |   |   |   |   |   |   |

|---------|------------------|-----|---|---|---|---|---|---|---|

|         |                  | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 00h     | Control_status_1 | 0   | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 01h     | Control_status_2 | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 02h     | VL_seconds       | 1   | Х | Χ | Х | Х | Χ | X | X |

| 03h     | Minutes          | Χ   | Х | Χ | Х | Х | Χ | X | X |

| 04h     | Hours            | Χ   | Х | Χ | Х | Х | Χ | X | х |

| 05h     | Days             | Χ   | Х | Χ | Х | Х | Χ | X | х |

| 06h     | Weekdays         | Х   | Χ | Х | Х | X | X | Χ | Х |

| 07h     | Century_months   | Χ   | X | Χ | Χ | Χ | Χ | Χ | X |

| 08h     | Years            | Χ   | X | Χ | Χ | Χ | Χ | Χ | X |

| 09h     | Minute_alarm     | 1   | X | Χ | Χ | Χ | Χ | Χ | X |

| 0Ah     | Hour_alarm       | 1   | X | Χ | Χ | Χ | Χ | Χ | X |

| 0Bh     | Day_alarm        | 1   | X | Χ | Χ | Χ | Χ | Χ | X |

| 0Ch     | Weekday_alarm    | 1   | X | Χ | Χ | Χ | Χ | Χ | X |

| 0Dh     | CLKOUT_control   | 1   | Χ | Х | Х | X | X | 0 | 0 |

| 0Eh     | Timer_control    | 0   | Χ | Х | Х | X | X | 1 | 1 |

| 0Fh     | Timer            | Х   | Х | Х | Х | Х | X | Х | Х |

<sup>[1]</sup> Registers marked x are undefined at power-up and unchanged by subsequent resets.

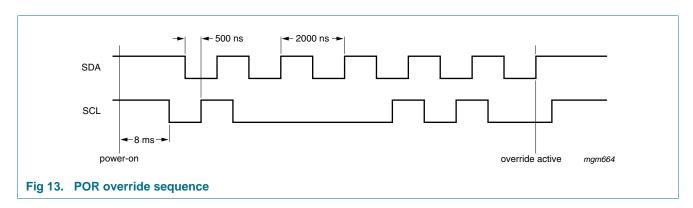

# 8.11.1 Power-On Reset (POR) override

The POR duration is directly related to the crystal oscillator start-up time. Due to the long start-up times experienced by these types of circuits, a mechanism has been built in to disable the POR and hence speed up on-board test of the device. The setting of this mode requires that the I<sup>2</sup>C-bus pins, SDA and SCL, are toggled in a specific order as shown in Figure 13. All timings are required minimums.

Once the override mode has been entered, the device immediately stops, being reset, and normal operation may commence i.e. entry into the EXT\_CLK test mode via I<sup>2</sup>C-bus access. The override mode may be cleared by writing logic 0 to TESTC. TESTC must be set to logic 1 before re-entry into the override mode is possible. Setting TESTC to logic 0 during normal operation has no effect except to prevent entry into the POR override mode.

PCF8563

All information provided in this document is subject to legal disclaimers.

Real-time clock/calendar

# 9. Characteristics of the I<sup>2</sup>C-bus

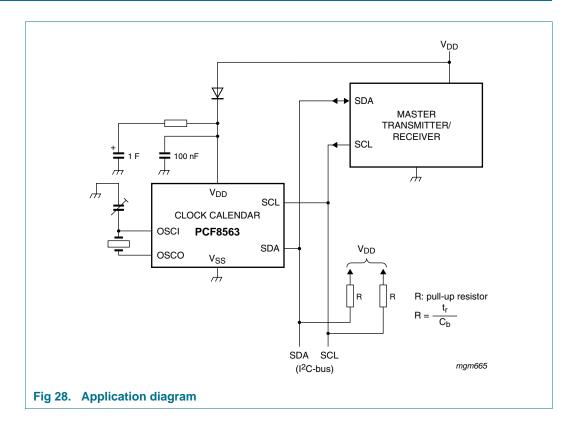

The I<sup>2</sup>C-bus is for bidirectional, two-line communication between different ICs or modules. The two lines are a Serial DAta line (SDA) and a Serial Clock Line (SCL). Both lines must be connected to a positive supply via a pull-up resistor. Data transfer may be initiated only when the bus is not busy.

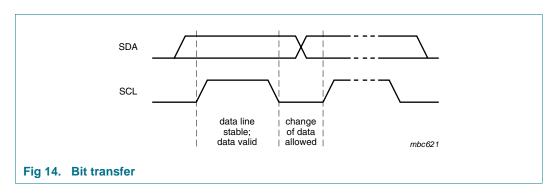

#### 9.1 Bit transfer

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the HIGH period of the clock pulse as changes in the data line at this time will be interpreted as a control signal (see Figure 14).

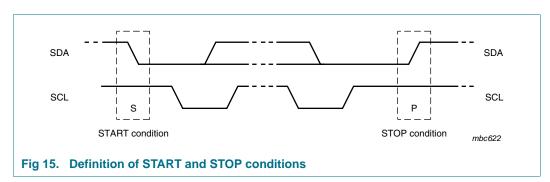

#### 9.2 START and STOP conditions

Both data and clock lines remain HIGH when the bus is not busy.

A HIGH-to-LOW transition of the data line while the clock is HIGH is defined as the START condition - S.

A LOW-to-HIGH transition of the data line while the clock is HIGH is defined as the STOP condition - P (see Figure 15).

#### 9.3 System configuration

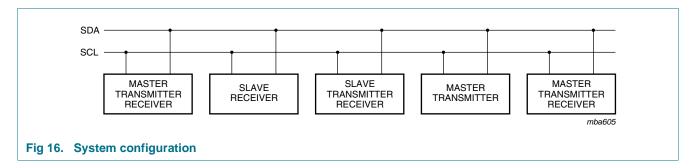

A device generating a message is a transmitter; a device receiving a message is a receiver. The device that controls the message is the master; and the devices which are controlled by the master are the slaves (see Figure 16).

Real-time clock/calendar

#### 9.4 Acknowledge

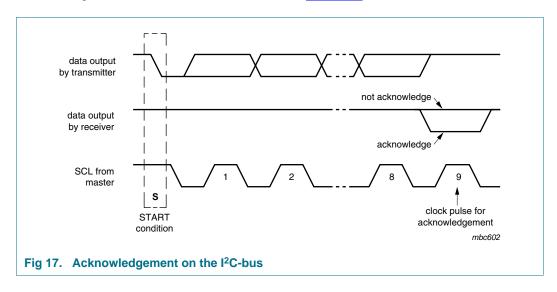

The number of data bytes transferred between the START and STOP conditions from transmitter to receiver is unlimited. Each byte of eight bits is followed by an acknowledge cycle.

- A slave receiver, which is addressed, must generate an acknowledge after the reception of each byte.

- Also a master receiver must generate an acknowledge after the reception of each byte that has been clocked out of the slave transmitter.

- The device that acknowledges must pull-down the SDA line during the acknowledge clock pulse, so that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse (set-up and hold times must be taken into consideration).

- A master receiver must signal an end of data to the transmitter by not generating an acknowledge on the last byte that has been clocked out of the slave. In this event, the transmitter must leave the data line HIGH to enable the master to generate a STOP condition.

Acknowledgement on the I<sup>2</sup>C-bus is illustrated in Figure 17.

Real-time clock/calendar

# 9.5 I<sup>2</sup>C-bus protocol

## 9.5.1 Addressing

Before any data is transmitted on the  $I^2C$ -bus, the device which should respond is addressed first. The addressing is always carried out with the first byte transmitted after the start procedure.

The PCF8563 acts as a slave receiver or slave transmitter. Therefore the clock signal SCL is only an input signal, but the data signal SDA is a bidirectional line.

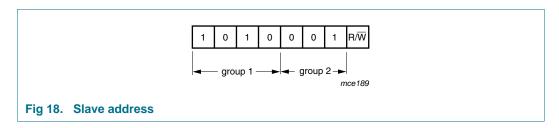

Two slave addresses are reserved for the PCF8563:

Read: A3h (10100011) Write: A2h (10100010)

The PCF8563 slave address is illustrated in Figure 18.

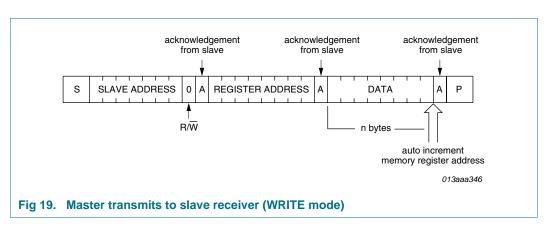

#### 9.5.2 Clock and calendar READ or WRITE cycles

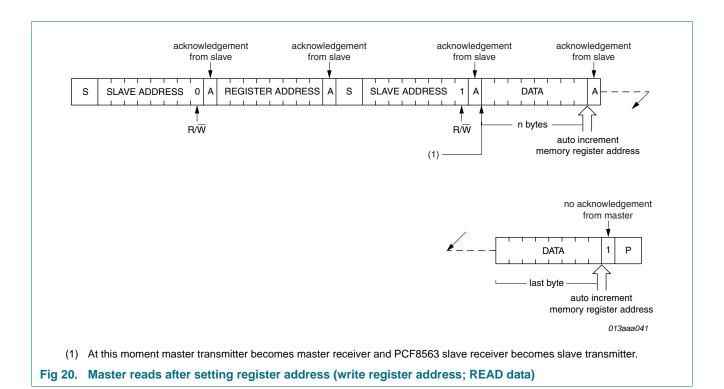

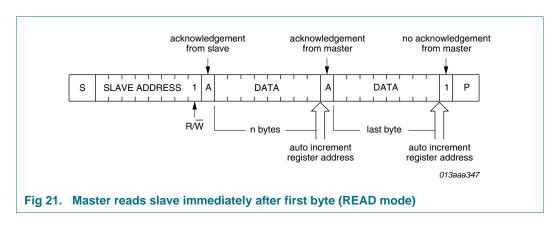

The I<sup>2</sup>C-bus configuration for the different PCF8563 READ and WRITE cycles is shown in Figure 19, Figure 20 and Figure 21. The register address is a 4-bit value that defines which register is to be accessed next. The upper four bits of the register address are not used.

PCF8563

#### Real-time clock/calendar

**PCF8563 NXP Semiconductors**

Real-time clock/calendar

# 10. Internal circuitry

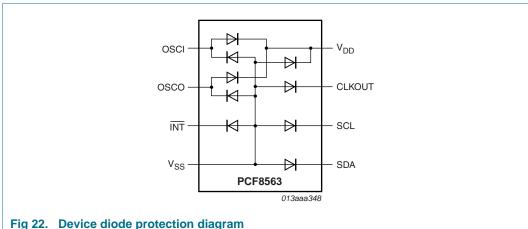

Fig 22. Device diode protection diagram

Real-time clock/calendar

# 11. Limiting values

Table 28. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol           | Parameter               | Conditions                 |     | Min  | Max   | Unit |

|------------------|-------------------------|----------------------------|-----|------|-------|------|

| $V_{DD}$         | supply voltage          |                            |     | -0.5 | +6.5  | V    |

| $I_{DD}$         | supply current          |                            |     | -50  | +50   | mΑ   |

| VI               | input voltage           | on pins SCL, SDA, and OSCI |     | -0.5 | +6.5  | V    |

| Vo               | output voltage          | on pins CLKOUT and INT     |     | -0.5 | +6.5  | V    |

| I <sub>I</sub>   | input current           | at any input               |     | -10  | +10   | mΑ   |

| Io               | output current          | at any output              |     | -10  | +10   | mΑ   |

| P <sub>tot</sub> | total power dissipation |                            |     | -    | 300   | mW   |

| $V_{ESD}$        | electrostatic discharge | HBM                        | [1] | -    | ±3500 | V    |

|                  | voltage                 | MM                         | [2] | -    | ±200  | V    |

|                  |                         | CDM                        |     |      |       |      |

|                  |                         | SO8 (PCF8563T)             | [3] | -    | ±1000 | V    |

|                  |                         | TSSOP8 (PCF8563TS)         | [3] | -    | ±1500 | V    |

|                  |                         | DIP8 (PCF8563P)            | [3] | -    | ±500  | V    |

|                  |                         | HVSON10 (PCF8563BS)        | [3] | -    | ±2000 | V    |

| I <sub>lu</sub>  | latch-up current        |                            | [4] | -    | 200   | mA   |

| T <sub>stg</sub> | storage temperature     |                            | [5] | -65  | +150  | °C   |

| T <sub>amb</sub> | ambient temperature     | operating device           |     | -40  | +85   | °C   |

<sup>[1]</sup> Pass level; Human Body Model (HBM), according to Ref. 5 "JESD22-A114".

<sup>[2]</sup> Pass level; Machine Model (MM), according to Ref. 6 "JESD22-A115".

<sup>[3]</sup> Pass level; Charged-Device Model (CDM), according to Ref. 7 "JESD22-C101".

<sup>[4]</sup> Pass level; latch-up testing according to Ref. 8 "JESD78" at maximum ambient temperature (T<sub>amb(max)</sub>).

<sup>[5]</sup> According to the NXP store and transport requirements (see Ref. 10 "NX3-00092") the devices have to be stored at a temperature of +8 °C to +45 °C and a humidity of 25 % to 75 %. For long term storage products deviant conditions are described in that document.

Real-time clock/calendar

# 12. Static characteristics

Table 29. Static characteristics

$V_{DD} = 1.8 \text{ V to } 5.5 \text{ V}; V_{SS} = 0 \text{ V}; T_{amb} = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}; f_{osc} = 32.768 \text{ kHz}; quartz R_s = 40 \text{ k}\Omega; C_L = 8 \text{ pF}; unless otherwise specified.}$

| Symbol          | Parameter                | Conditions                                                                                                                            | Min                | Тур | Max         | Uni |

|-----------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------------|-----|

| Supplies        |                          |                                                                                                                                       |                    |     |             |     |

| / <sub>DD</sub> | supply voltage           | interface inactive;<br>$f_{SCL} = 0 \text{ Hz};$<br>$T_{amb} = 25 ^{\circ}\text{C}$                                                   | 1.0                | -   | 5.5         | V   |

|                 |                          | interface active;<br>f <sub>SCL</sub> = 400 kHz                                                                                       | <u>11</u> 1.8      | -   | 5.5         | V   |

|                 |                          | clock data integrity;<br>T <sub>amb</sub> = 25 °C                                                                                     | $V_{low}$          | -   | 5.5         | V   |

| DD              | supply current           | interface active                                                                                                                      |                    |     |             |     |

|                 |                          | f <sub>SCL</sub> = 400 kHz                                                                                                            | -                  | -   | 800         | μΑ  |

|                 |                          | f <sub>SCL</sub> = 100 kHz                                                                                                            | -                  | -   | 200         | μΑ  |

|                 |                          | interface inactive ( $f_{SCL} = 0 \text{ Hz}$ ); CLKOUT disabled; $T_{amb} = 25 ^{\circ}\text{C}$                                     | <u>[2]</u>         |     |             |     |

|                 |                          | V <sub>DD</sub> = 5.0 V                                                                                                               | -                  | 275 | 550         | nΑ  |

|                 |                          | $V_{DD} = 3.0 \text{ V}$                                                                                                              | -                  | 250 | 500         | nΑ  |

|                 |                          | $V_{DD} = 2.0 \text{ V}$                                                                                                              | -                  | 225 | 450         | nΑ  |

|                 |                          | interface inactive ( $f_{SCL} = 0 \text{ Hz}$ ); CLKOUT disabled; $T_{amb} = -40 ^{\circ}\text{C}$ to +85 $^{\circ}\text{C}$          | [2]                |     |             |     |

|                 |                          | V <sub>DD</sub> = 5.0 V                                                                                                               | -                  | 500 | 750         | nΑ  |

|                 |                          | V <sub>DD</sub> = 3.0 V                                                                                                               | -                  | 400 | 650         | nΑ  |

|                 |                          | V <sub>DD</sub> = 2.0 V                                                                                                               | -                  | 400 | 600         | nΑ  |

|                 |                          | interface inactive ( $f_{SCL} = 0 \text{ Hz}$ ); CLKOUT enabled at 32 kHz; $T_{amb} = 25 ^{\circ}\text{C}$                            | [2]                |     |             |     |

|                 |                          | V <sub>DD</sub> = 5.0 V                                                                                                               | -                  | 825 | 1600        | nΑ  |

|                 |                          | V <sub>DD</sub> = 3.0 V                                                                                                               | -                  | 550 | 1000        | nΑ  |

|                 |                          | V <sub>DD</sub> = 2.0 V                                                                                                               | -                  | 425 | 800         | nΑ  |

|                 |                          | interface inactive ( $f_{SCL} = 0 \text{ Hz}$ ); CLKOUT enabled at 32 kHz; $T_{amb} = -40 ^{\circ}\text{C}$ to +85 $^{\circ}\text{C}$ | [2]                |     |             |     |

|                 |                          | V <sub>DD</sub> = 5.0 V                                                                                                               | -                  | 950 | 1700        | nΑ  |

|                 |                          | $V_{DD} = 3.0 \text{ V}$                                                                                                              | -                  | 650 | 1100        | nA  |

|                 |                          | $V_{DD} = 2.0 \text{ V}$                                                                                                              | -                  | 500 | 900         | nΑ  |

| nputs           |                          |                                                                                                                                       |                    |     |             |     |

| / <sub>IL</sub> | LOW-level input voltage  |                                                                                                                                       | $V_{SS}$           | -   | $0.3V_{DD}$ | V   |

| ′ін             | HIGH-level input voltage |                                                                                                                                       | 0.7V <sub>DD</sub> | -   | $V_{DD}$    | V   |

| _I              | input leakage<br>current | $V_{I} = V_{DD}$ or $V_{SS}$                                                                                                          | -1                 | 0   | +1          | μΑ  |

| Ç <sub>i</sub>  | input<br>capacitance     |                                                                                                                                       | [3] _              | -   | 7           | pF  |

PCF8563

All information provided in this document is subject to legal disclaimers.

#### Real-time clock/calendar

Table 29. Static characteristics ... continued

$V_{DD} = 1.8 \text{ V to } 5.5 \text{ V; } V_{SS} = 0 \text{ V; } T_{amb} = -40 \text{ °C to } +85 \text{ °C; } f_{osc} = 32.768 \text{ kHz; quartz } R_s = 40 \text{ k}\Omega; C_L = 8 \text{ pF; unless otherwise specified.}$

| -1              |                          |                                                                        |           |     |     |      |

|-----------------|--------------------------|------------------------------------------------------------------------|-----------|-----|-----|------|

| Symbol          | Parameter                | Conditions                                                             | Min       | Тур | Max | Unit |

| Outputs         |                          |                                                                        |           |     |     |      |

| I <sub>OL</sub> | LOW-level output current | output sink current;<br>V <sub>OL</sub> = 0.4 V; V <sub>DD</sub> = 5 V |           |     |     |      |

|                 |                          | on pin SDA                                                             | 3         | -   | -   | mA   |

|                 |                          | on pin INT                                                             | 1         | -   | -   | mA   |

|                 |                          | on pin CLKOUT                                                          | 1         | -   | -   | mA   |

| I <sub>LO</sub> | output leakage current   | $V_O = V_{DD}$ or $V_{SS}$                                             | <b>–1</b> | 0   | +1  | μА   |

| Voltage de      | tector                   |                                                                        |           |     |     |      |

| $V_{low}$       | low voltage              | T <sub>amb</sub> = 25 °C; sets bit VL; see Figure 7                    | -         | 0.9 | 1.0 | V    |

|                 |                          |                                                                        |           |     |     |      |

<sup>[1]</sup> For reliable oscillator start-up at power-up:  $V_{DD(min)power-up} = V_{DD(min)} + 0.3 \text{ V}.$

<sup>[3]</sup> Tested on sample basis.

<sup>[2]</sup> Timer source clock =  $\frac{1}{60}$  Hz, level of pins SCL and SDA is  $V_{DD}$  or  $V_{SS}$ .

#### Real-time clock/calendar

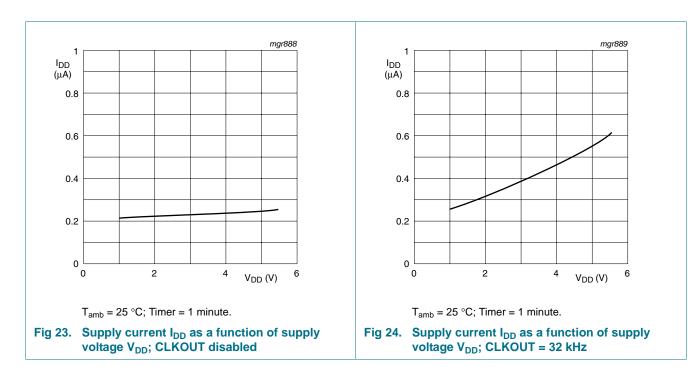

$V_{DD} = 3 \text{ V}$ ; Timer = 1 minute.

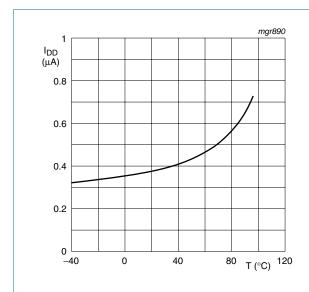

Fig 25. Supply current I<sub>DD</sub> as a function of temperature T; CLKOUT = 32 kHz

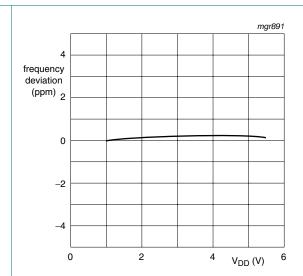

$T_{amb}$  = 25 °C; normalized to  $V_{DD}$  = 3 V.

Fig 26. Frequency deviation as a function of supply voltage  $V_{\text{DD}}$

Real-time clock/calendar

# 13. Dynamic characteristics

#### Table 30. Dynamic characteristics

$V_{DD}$  = 1.8 V to 5.5 V;  $V_{SS}$  = 0 V;  $T_{amb}$  = -40 °C to +85 °C;  $f_{osc}$  = 32.768 kHz; quartz  $R_s$  = 40 k $\Omega$ ;  $C_L$  = 8 pF; unless otherwise specified.

| Symbol                           | Parameter                                  | Conditions                                     |            | Min | Тур | Max  | Unit |

|----------------------------------|--------------------------------------------|------------------------------------------------|------------|-----|-----|------|------|

| Oscillator                       |                                            |                                                |            |     |     |      |      |

| Cosco                            | capacitance on pin OSCO                    |                                                |            | 15  | 25  | 35   | pF   |

| $\Delta f_{\rm osc}/f_{\rm osc}$ | relative oscillator frequency variation    | $\Delta V_{DD}$ = 200 mV;<br>$T_{amb}$ = 25 °C |            | -   | 0.2 | -    | ppm  |

| Quartz crys                      | tal parameters (f = 32.768 kHz)            |                                                |            |     |     |      |      |

| R <sub>s</sub>                   | series resistance                          |                                                |            | -   | -   | 100  | kΩ   |

| C <sub>L</sub>                   | load capacitance                           | parallel                                       | <u>[1]</u> | 7   | -   | 12.5 | pF   |

| $C_{trim}$                       | trimmer capacitance                        | external;<br>on pin OSCI                       |            | 5   | -   | 25   | pF   |

| CLKOUT or                        | ıtput                                      |                                                |            |     |     |      |      |

| $\delta_{\text{CLKOUT}}$         | duty cycle on pin CLKOUT                   |                                                | [2]        | -   | 50  | -    | %    |

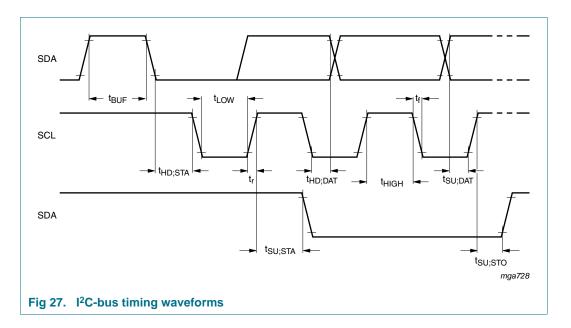

| I <sup>2</sup> C-bus tim         | ing characteristics (see Figure 27)[3][4]  |                                                |            |     |     |      |      |

| f <sub>SCL</sub>                 | SCL clock frequency                        |                                                | <u>[5]</u> | -   | -   | 400  | kHz  |

| t <sub>HD;STA</sub>              | hold time (repeated) START condition       |                                                |            | 0.6 | -   | -    | μS   |

| t <sub>SU;STA</sub>              | set-up time for a repeated START condition |                                                |            | 0.6 | -   | -    | μS   |

| $t_{LOW}$                        | LOW period of the SCL clock                |                                                |            | 1.3 | -   | -    | μS   |

| t <sub>HIGH</sub>                | HIGH period of the SCL clock               |                                                |            | 0.6 | -   | -    | μS   |

| t <sub>r</sub>                   | rise time of both SDA and SCL signals      |                                                |            | -   | -   | 0.3  | μS   |

| t <sub>f</sub>                   | fall time of both SDA and SCL signals      |                                                |            | -   | -   | 0.3  | μS   |

| C <sub>b</sub>                   | capacitive load for each bus line          |                                                |            | -   | -   | 400  | pF   |

| t <sub>SU;DAT</sub>              | data set-up time                           |                                                |            | 100 | -   | -    | ns   |

| t <sub>HD;DAT</sub>              | data hold time                             |                                                |            | 0   | -   | -    | ns   |

| t <sub>SU;STO</sub>              | set-up time for STOP condition             |                                                |            | 0.6 | -   | -    | μS   |

| t <sub>w(spike)</sub>            | spike pulse width                          | on bus                                         |            | -   | -   | 50   | ns   |

<sup>[1]</sup>  $C_L$  is a calculation of  $C_{trim}$  and  $C_{OSCO}$  in series:  $C_L = \frac{(C_{trim} \cdot C_{OSCO})}{(C_{trim} + C_{OSCO})}$ .

<sup>[2]</sup> Unspecified for f<sub>CLKOUT</sub> = 32.768 kHz.

<sup>[3]</sup> All timing values are valid within the operating supply voltage at ambient temperature and referenced to  $V_{IL}$  and  $V_{IH}$  with an input voltage swing of  $V_{SS}$  to  $V_{DD}$ .

<sup>[4]</sup> A detailed description of the I<sup>2</sup>C-bus specification is given in Ref. 12 "UM10204".

<sup>[5]</sup> I<sup>2</sup>C-bus access time between two STARTs or between a START and a STOP condition to this device must be less than one second.

#### Real-time clock/calendar

# 14. Application information

Real-time clock/calendar

# 14.1 Quartz frequency adjustment

### 14.1.1 Method 1: fixed OSCI capacitor

By evaluating the average capacitance necessary for the application layout, a fixed capacitor can be used. The frequency is best measured via the 32.768 kHz signal available after power-on at pin CLKOUT. The frequency tolerance depends on the quartz crystal tolerance, the capacitor tolerance and the device-to-device tolerance (on average  $\pm 5$  ppm). Average deviations of  $\pm 5$  minutes per year can be easily achieved.

#### 14.1.2 Method 2: OSCI trimmer

Using the 32.768 kHz signal available after power-on at pin CLKOUT, fast setting of a trimmer is possible.

## 14.1.3 Method 3: OSCO output

Direct measurement of OSCO out (accounting for test probe capacitance).

Downloaded from Arrow.com.

# 15. Package outline

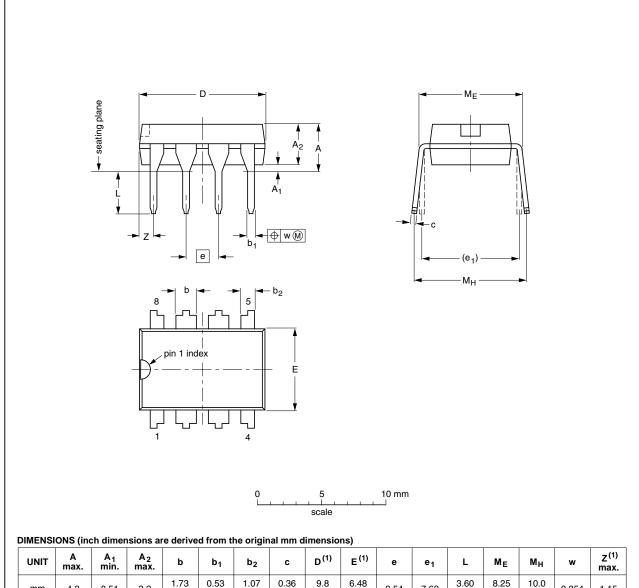

#### DIP8: plastic dual in-line package; 8 leads (300 mil)

SOT97-1

| UNIT   | A<br>max. | A <sub>1</sub><br>min. | A <sub>2</sub><br>max. | b              | b <sub>1</sub> | b <sub>2</sub> | С              | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | e <sub>1</sub> | L            | ME           | Мн           | w     | Z <sup>(1)</sup><br>max. |

|--------|-----------|------------------------|------------------------|----------------|----------------|----------------|----------------|------------------|------------------|------|----------------|--------------|--------------|--------------|-------|--------------------------|

| mm     | 4.2       | 0.51                   | 3.2                    | 1.73<br>1.14   | 0.53<br>0.38   | 1.07<br>0.89   | 0.36<br>0.23   | 9.8<br>9.2       | 6.48<br>6.20     | 2.54 | 7.62           | 3.60<br>3.05 | 8.25<br>7.80 | 10.0<br>8.3  | 0.254 | 1.15                     |

| inches | 0.17      | 0.02                   | 0.13                   | 0.068<br>0.045 | 0.021<br>0.015 | 0.042<br>0.035 | 0.014<br>0.009 | 0.39<br>0.36     | 0.26<br>0.24     | 0.1  | 0.3            | 0.14<br>0.12 | 0.32<br>0.31 | 0.39<br>0.33 | 0.01  | 0.045                    |

#### Note

1. Plastic or metal protrusions of 0.25 mm (0.01 inch) maximum per side are not included.

| OUTLINE |        | REFER  | ENCES    | EUROPEAN | ISSUE DATE |                                 |

|---------|--------|--------|----------|----------|------------|---------------------------------|

| VERSION | IEC    | JEDEC  | JEITA    |          | PROJECTION | ISSUE DATE                      |

| SOT97-1 | 050G01 | MO-001 | SC-504-8 |          |            | <del>99-12-27</del><br>03-02-13 |

|         |        |        |          |          |            |                                 |

Fig 29. Package outline SOT97-1 (DIP8) of PCF8563P

CF8563 All information provided in this document is subject to legal disclaimers.

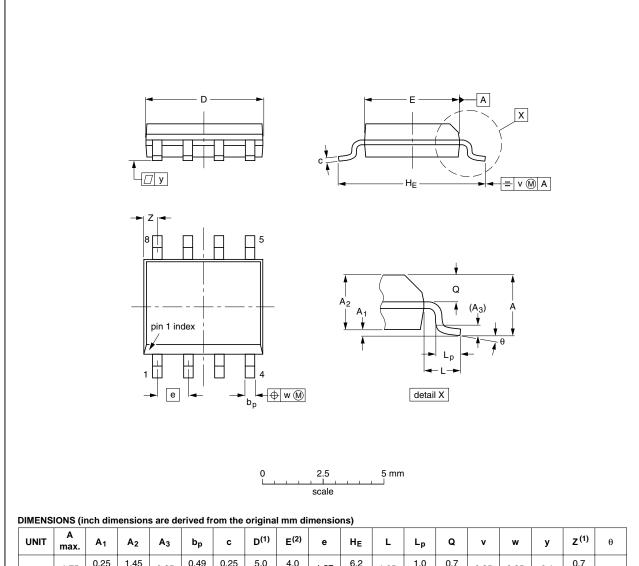

#### SO8: plastic small outline package; 8 leads; body width 3.9 mm

SOT96-1

| UNIT   | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | А3   | bp           | С                | D <sup>(1)</sup> | E <sup>(2)</sup> | е    | HE             | L     | Lp             | Q              | ٧    | w    | у     | z <sup>(1)</sup> | θ  |

|--------|-----------|----------------|----------------|------|--------------|------------------|------------------|------------------|------|----------------|-------|----------------|----------------|------|------|-------|------------------|----|

| mm     | 1.75      | 0.25<br>0.10   | 1.45<br>1.25   | 0.25 | 0.49<br>0.36 | 0.25<br>0.19     | 5.0<br>4.8       | 4.0<br>3.8       | 1.27 | 6.2<br>5.8     | 1.05  | 1.0<br>0.4     | 0.7<br>0.6     | 0.25 | 0.25 | 0.1   | 0.7<br>0.3       | 8° |

| inches | 0.069     | 0.010<br>0.004 | 0.057<br>0.049 | 0.01 |              | 0.0100<br>0.0075 | 0.20<br>0.19     | 0.16<br>0.15     | 0.05 | 0.244<br>0.228 | 0.041 | 0.039<br>0.016 | 0.028<br>0.024 | 0.01 | 0.01 | 0.004 | 0.028<br>0.012   | 0° |

#### Notes

- 1. Plastic or metal protrusions of 0.15 mm (0.006 inch) maximum per side are not included.

- 2. Plastic or metal protrusions of 0.25 mm (0.01 inch) maximum per side are not included.

| OUTLINE |        | EUROPEAN | ISSUE DATE |            |                                 |

|---------|--------|----------|------------|------------|---------------------------------|

| VERSION | IEC    | JEDEC    | JEITA      | PROJECTION | ISSUE DATE                      |

| SOT96-1 | 076E03 | MS-012   |            |            | <del>99-12-27</del><br>03-02-18 |

Fig 30. Package outline SOT96-1 (SO8) of PCF8563T

F8563 All information provided in this document is subject to legal disclaimers.

**PCF8563 NXP Semiconductors**

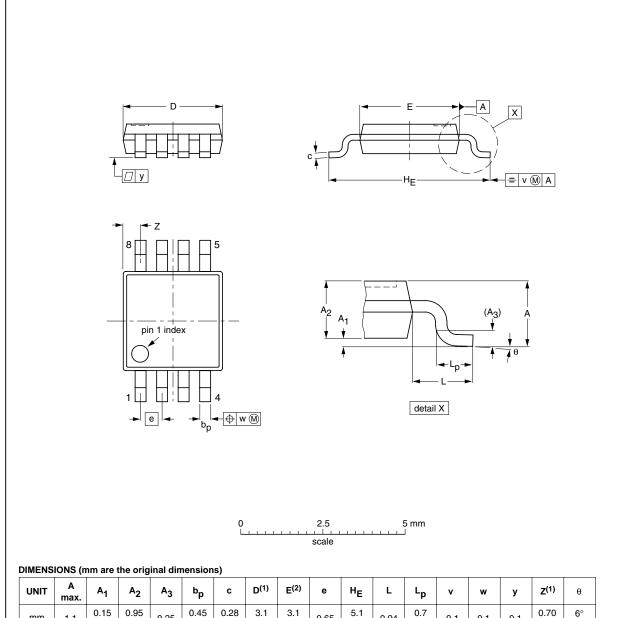

#### TSSOP8: plastic thin shrink small outline package; 8 leads; body width 3 mm

SOT505-1

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | bр           | С            | D <sup>(1)</sup> | E <sup>(2)</sup> | е    | HE         | L    | Lp         | ٧   | w   | у   | Z <sup>(1)</sup> | θ        |

|------|-----------|----------------|----------------|----------------|--------------|--------------|------------------|------------------|------|------------|------|------------|-----|-----|-----|------------------|----------|

| mm   | 1.1       | 0.15<br>0.05   | 0.95<br>0.80   | 0.25           | 0.45<br>0.25 | 0.28<br>0.15 | 3.1<br>2.9       | 3.1<br>2.9       | 0.65 | 5.1<br>4.7 | 0.94 | 0.7<br>0.4 | 0.1 | 0.1 | 0.1 | 0.70<br>0.35     | 6°<br>0° |

#### Notes

- 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

- 2. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

|   | OUTLINE  |     | REFER | RENCES | EUROPEAN   | ISSUE DATE                      |

|---|----------|-----|-------|--------|------------|---------------------------------|

|   | VERSION  | IEC | JEDEC | JEITA  | PROJECTION | ISSUE DATE                      |

|   | SOT505-1 |     |       |        |            | <del>99-04-09</del><br>03-02-18 |

| L |          |     |       |        | )          | 03-02-18                        |

Fig 31. Package outline SOT505-1 (TSSOP8) of PCF8563TS

All information provided in this document is subject to legal disclaimers.

Real-time clock/calendar

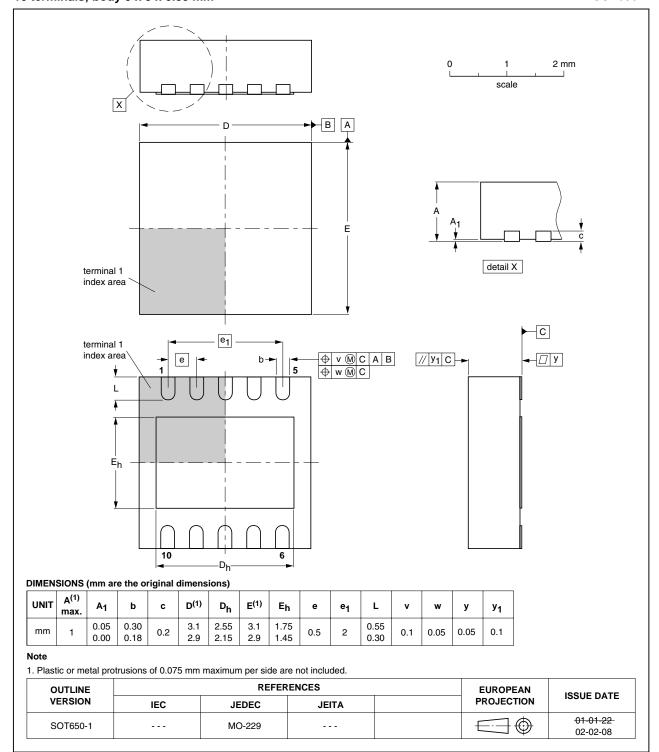

# HVSON10: plastic thermal enhanced very thin small outline package; no leads; 10 terminals; body $3 \times 3 \times 0.85 \text{ mm}$

SOT650-1

Fig 32. Package outline SOT650-1 (HVSON10) of PCF8563BS

CF8563 All information provided in this document is subject to legal disclaimers.

Real-time clock/calendar

# 16. Handling information

All input and output pins are protected against ElectroStatic Discharge (ESD) under normal handling. When handling Metal-Oxide Semiconductor (MOS) devices ensure that all normal precautions are taken as described in *JESD625-A*, *IEC 61340-5* or equivalent standards.

# 17. Soldering of SMD packages

This text provides a very brief insight into a complex technology. A more in-depth account of soldering ICs can be found in Application Note *AN10365* "Surface mount reflow soldering description".

# 17.1 Introduction to soldering