### **FEATURES AND BENEFITS**

- Low R<sub>DS(ON)</sub> outputs

- Automatic current decay mode detection/selection

- Mixed and Slow current decay modes

- Synchronous rectification for low power dissipation

- Internal UVLO

- Crossover-current protection

- 3.3 and 5 V compatible logic supply

- Thin profile QFN and TSSOP packages

- Thermal shutdown circuitry

- Short-to-ground protection

- Shorted load protection

- Low current Sleep mode, < 10 μA</li>

- No smoke no fire (NSNF) compliance (ET package)

### **PACKAGES:**

24-contact QFN with exposed thermal pad 4 mm × 4 mm × 0.75 mm (ES package)

32-contact QFN with exposed thermal pad 5 mm × 5 mm × 0.90 mm (ET package)

24-pin TSSOP with exposed thermal pad (LP Package)

#### DESCRIPTION

The A4984 is a complete microstepping motor driver with built-in translator for easy operation. It is designed to operate bipolar stepper motors in full-, half-, quarter-, and eighth-step modes. Step modes are selectable by MSx logic inputs. It has an output drive capacity of up to 35 V and  $\pm 2 \text{ A}$ . The A4984 includes a fixed off-time current regulator which has the ability to operate in Slow or Mixed decay modes.

The ET package meets customer requirements for no smoke no fire (NSNF) designs by adding no-connect pins between critical output, sense, and supply pins. So, in the case of a pin-to-adjacent-pin short, the device does not cause smoke or fire. Additionally, the device does not cause smoke or fire when any pin is shorted to ground or left open.

The translator is the key to the easy implementation of the A4984. Simply inputting one pulse on the STEP input drives the motor one microstep. There are no phase sequence tables, high frequency control lines, or complex interfaces to program. The A4984 interface is an ideal fit for applications where a complex microprocessor is unavailable or is overburdened.

During stepping operation, the chopping control in the A4984 automatically selects the current decay mode, Slow or Mixed.

Continued on the next page...

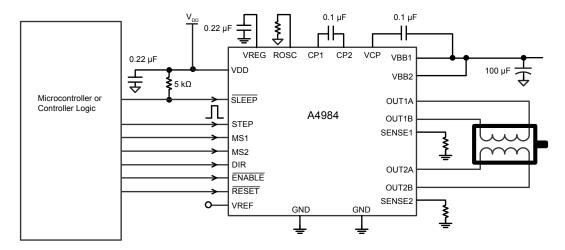

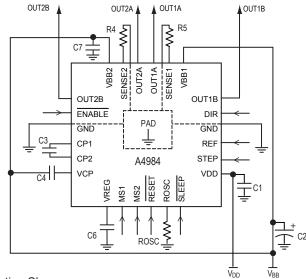

### **Typical Application Diagram**

### A4984

## DMOS Microstepping Driver with Translator and Overcurrent Protection

### **DESCRIPTION** (continued)

In Mixed decay mode, the device is set initially to a fast decay for a proportion of the fixed off-time, then to a slow decay for the remainder of the off-time. Mixed decay current control results in reduced audible motor noise, increased step accuracy, and reduced power dissipation.

Internal synchronous rectification control circuitry is provided to improve power dissipation during PWM operation. Internal circuit protection includes thermal shutdown with hysteresis, undervoltage lockout (UVLO), and crossover-current protection. Special power-on sequencing is not required.

The A4984 is supplied in three surface mount packages: two QFN packages, the 4 mm  $\times$  4 mm, 0.75 mm nominal overall height ES package, and the 5 mm  $\times$  5 mm  $\times$  0.90 mm ET package. The LP package is a 24-pin TSSOP. All three packages have exposed pads for enhanced thermal dissipation and are lead (Pb) free (suffix -T), with 100% matte tin plated leadframes.

#### **Selection Guide**

| Part Number  | Package                               | Packing                     |

|--------------|---------------------------------------|-----------------------------|

| A4984SESTR-T | 24-pin QFN with exposed thermal pad   | 1500 pieces per 7-in. reel  |

| A4984SETTR-T | 32-pin QFN with exposed thermal pad   | 1500 pieces per 7-in. reel  |

| A4984SLPTR-T | 24-pin TSSOP with exposed thermal pad | 4000 pieces per 13-in. reel |

#### **Absolute Maximum Ratings**

| Characteristic                | Symbol               | Notes   | Rating      | Units |

|-------------------------------|----------------------|---------|-------------|-------|

| Load Supply Voltage           | $V_{BB}$             |         | 35          | V     |

| Output Current                | I <sub>OUT</sub>     |         | ±2          | Α     |

| Logic Input Voltage           | V <sub>IN</sub>      |         | -0.3 to 5.5 | V     |

| Logic Supply Voltage          | V <sub>DD</sub>      |         | -0.3 to 5.5 | V     |

| Motor Outputs Voltage         |                      |         | -2.0 to 37  | V     |

| Sense Voltage                 | V <sub>SENSE</sub>   |         | -0.5 to 0.5 | V     |

| Reference Voltage             | $V_{REF}$            |         | 5.5         | V     |

| Operating Ambient Temperature | T <sub>A</sub>       | Range S | -20 to 85   | °C    |

| Maximum Junction              | T <sub>J</sub> (max) |         | 150         | °C    |

| Storage Temperature           | T <sub>stg</sub>     |         | -55 to 150  | °C    |

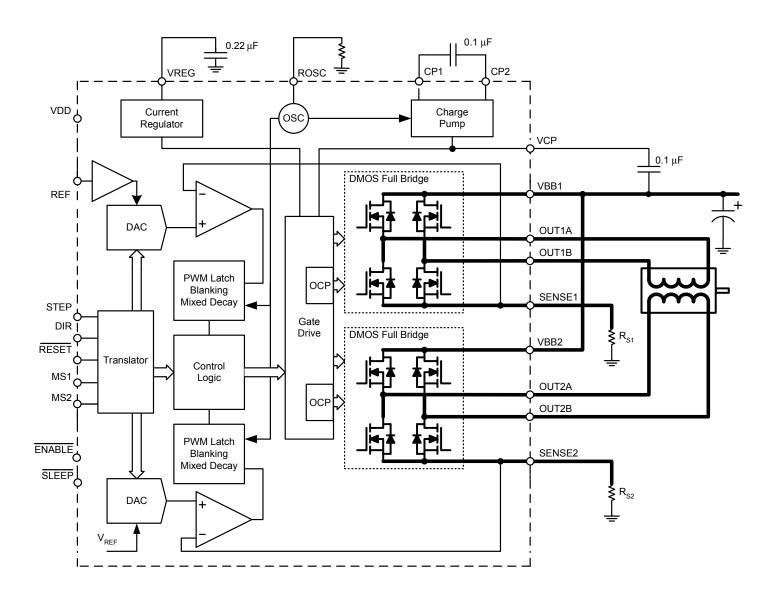

### **Functional Block Diagram**

### A4984

## DMOS Microstepping Driver with Translator and Overcurrent Protection

### **ELECTRICAL CHARACTERISTICS**<sup>1</sup> at T<sub>A</sub> = 25°C, V<sub>BB</sub> = 35 V (unless otherwise noted)

| Characteristics                               | Symbol                 | Test Conditions                                         | Min.                 | Typ. <sup>2</sup> | Max.                 | Units |

|-----------------------------------------------|------------------------|---------------------------------------------------------|----------------------|-------------------|----------------------|-------|

| Output Drivers                                | 1                      | 1                                                       | '                    |                   |                      |       |

| Load Cumply Voltage Dange                     |                        | Operating                                               | 8                    | _                 | 35                   | V     |

| Load Supply Voltage Range                     | V <sub>BB</sub>        | During Sleep Mode                                       | 0                    | _                 | 35                   | V     |

| Logic Supply Voltage Range                    | V <sub>DD</sub>        | Operating                                               | 3.0                  | _                 | 5.5                  | V     |

| Output On Resistance                          | В                      | Source Driver, I <sub>OUT</sub> = -1.5 A                | _                    | 320               | 430                  | mΩ    |

| Output On Resistance                          | R <sub>DSON</sub>      | Sink Driver, I <sub>OUT</sub> = 1.5 A                   | _                    | 320               | 430                  | mΩ    |

| Body Diode Forward Voltage                    | \/                     | Source Diode, I <sub>F</sub> = -1.5 A                   | _                    | _                 | 1.3                  | V     |

| Body Diode Forward Voltage                    | V <sub>F</sub>         | Sink Diode, I <sub>F</sub> = 1.5 A                      | _                    | _                 | 1.3                  | V     |

|                                               |                        | f <sub>PWM</sub> < 50 kHz                               | _                    | _                 | 4                    | mA    |

| Motor Supply Current                          | I <sub>BB</sub>        | Operating, outputs disabled                             | _                    | _                 | 2                    | mA    |

|                                               |                        | Sleep Mode                                              | _                    | _                 | 10                   | μA    |

|                                               |                        | f <sub>PWM</sub> < 50 kHz                               | _                    | _                 | 8                    | mA    |

| Logic Supply Current                          | I <sub>DD</sub>        | Outputs off                                             | _                    | _                 | 5                    | mA    |

|                                               |                        | Sleep Mode                                              | _                    | _                 | 10                   | μΑ    |

| Control Logic                                 |                        |                                                         |                      |                   |                      |       |

| Lagis Input Valtage                           | V <sub>IN(1)</sub>     |                                                         | V <sub>DD</sub> ×0.7 | -                 | _                    | V     |

| Logic Input Voltage                           | V <sub>IN(0)</sub>     |                                                         | _                    | -                 | V <sub>DD</sub> ×0.3 | V     |

| Logic Input Current                           | I <sub>IN(1)</sub>     | $V_{IN} = V_{DD} \times 0.7$                            | -20                  | <1.0              | 20                   | μΑ    |

| Logic Input Current                           | I <sub>IN(0)</sub>     | $V_{IN} = V_{DD} \times 0.3$                            | -20                  | <1.0              | 20                   | μΑ    |

| N                                             | R <sub>MS1</sub>       | MS1 pin                                                 | _                    | 100               | _                    | kΩ    |

| Microstep Select                              | R <sub>MS2</sub>       | MS2 pin                                                 | _                    | 50                | _                    | kΩ    |

| Logic Input Hysteresis                        | V <sub>HYS(IN)</sub>   | As a % of V <sub>DD</sub>                               | 5                    | 11                | 19                   | %     |

| Blank Time                                    | t <sub>BLANK</sub>     |                                                         | 0.7                  | 1                 | 1.3                  | μs    |

| Fixed Off Time                                |                        | OSC = VDD or GND                                        | 20                   | 30                | 40                   | μs    |

| Fixed Off-Time                                | t <sub>OFF</sub>       | $R_{OSC} = 25 \text{ k}\Omega$                          | 23                   | 30                | 37                   | μs    |

| Reference Input Voltage Range                 | V <sub>REF</sub>       |                                                         | 0                    | _                 | 4                    | V     |

| Reference Input Current                       | I <sub>REF</sub>       |                                                         | -3                   | 0                 | 3                    | μA    |

|                                               |                        | V <sub>REF</sub> = 2 V, %I <sub>TripMAX</sub> = 38.27%  | _                    | _                 | ±15                  | %     |

| Current Trip-Level Error <sup>3</sup>         | err <sub>l</sub>       | V <sub>REF</sub> = 2 V, %I <sub>TripMAX</sub> = 70.71%  | _                    | _                 | ±5                   | %     |

|                                               |                        | V <sub>REF</sub> = 2 V, %I <sub>TripMAX</sub> = 100.00% | _                    | _                 | ±5                   | %     |

| Crossover Dead Time                           | t <sub>DT</sub>        | ·                                                       | 100                  | 475               | 800                  | ns    |

| Protection                                    | 1                      | 1                                                       | 1                    |                   |                      |       |

| Overcurrent Protection Threshold <sup>4</sup> | I <sub>OCPST</sub>     |                                                         | 2.1                  | _                 | _                    | Α     |

| Thermal Shutdown Temperature                  | T <sub>TSD</sub>       |                                                         | _                    | 165               | _                    | °C    |

| Thermal Shutdown Hysteresis                   | T <sub>TSDHYS</sub>    |                                                         | _                    | 15                | _                    | °C    |

| VDD Undervoltage Lockout                      | V <sub>DDUVLO</sub>    | V <sub>DD</sub> rising                                  | 2.7                  | 2.8               | 2.9                  | V     |

| VDD Undervoltage Hysteresis                   | V <sub>DDUVLOHYS</sub> |                                                         | _                    | 90                | _                    | mV    |

<sup>&</sup>lt;sup>1</sup>For input and output current specifications, negative current is defined as coming out of (sourcing) the specified device pin.

<sup>&</sup>lt;sup>2</sup>Typical data are for initial design estimations only and assume optimum manufacturing and application conditions. Performance may vary for individual units, within the specified maximum and minimum limits.

$<sup>^{3}</sup>V_{ERR} = [(V_{REF}/8) - V_{SENSE}] / (V_{REF}/8).$

<sup>&</sup>lt;sup>4</sup>Overcurrent protection (OCP) is tested at T<sub>A</sub> = 25°C in a restricted range and guaranteed by characterization.

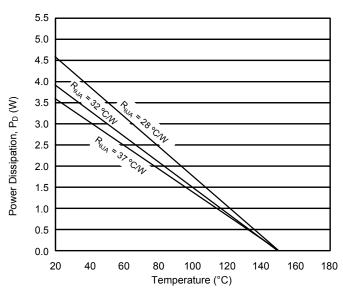

#### THERMAL CHARACTERISTICS: May require derating at maximum conditions

| The tank to the trade indo individual do a trade individual do indication |                 |                                                                |       |      |  |  |  |

|---------------------------------------------------------------------------|-----------------|----------------------------------------------------------------|-------|------|--|--|--|

| Characteristic                                                            | Symbol          | Value                                                          | Units |      |  |  |  |

|                                                                           |                 | ES package; estimated, on 4-layer PCB, based on JEDEC standard | 37    | °C/W |  |  |  |

| Package Thermal Resistance                                                | $R_{\theta JA}$ | ET package; estimated, on 4-layer PCB, based on JEDEC standard | 32    | °C/W |  |  |  |

|                                                                           |                 | LP package; on 4-layer PCB, based on JEDEC standard            | 28    | °C/W |  |  |  |

<sup>\*</sup>In still air. Additional thermal information available on Allegro website.

### Maximum Power Dissipation, P<sub>D</sub>(max)

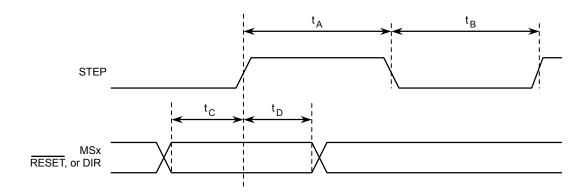

| Time Duration                    | Symbol         | Тур. | Unit |

|----------------------------------|----------------|------|------|

| STEP minimum, HIGH pulse width   | t <sub>A</sub> | 1    | μs   |

| STEP minimum, LOW pulse width    | t <sub>B</sub> | 1    | μs   |

| Setup time, input change to STEP | t <sub>C</sub> | 200  | ns   |

| Hold time, input change to STEP  | t <sub>D</sub> | 200  | ns   |

Figure 1: Logic Interface Timing Diagram

Table 1: Microstep Resolution Truth Table

| MS1 | MS2 | Microstep Resolution | Excitation Mode |

|-----|-----|----------------------|-----------------|

| L   | L   | Full Step            | 2 Phase         |

| Н   | L   | Half Step            | 1-2 Phase       |

| L   | Н   | Quarter Step         | W1-2 Phase      |

| Н   | Н   | Eighth Step          | 2W1-2 Phase     |

### **Functional Description**

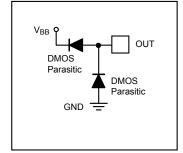

**Device Operation.** The A4984 is a complete microstepping motor driver with a built-in translator for easy operation with minimal control lines. It is designed to operate bipolar stepper motors in full-, half-, quarter-, and eighth-step modes. The currents in each of the two output full-bridges and all of the N-channel DMOS FETs are regulated with fixed off-time PWM (pulse width modulated) control circuitry. At each step, the current for each full-bridge is set by the value of its external current-sense resistor ( $R_{S1}$  and  $R_{S2}$ ), a reference voltage ( $V_{REF}$ ), and the output voltage of its DAC (which in turn is controlled by the output of the translator).

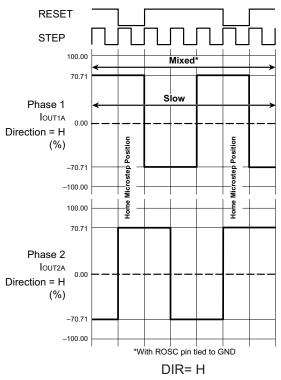

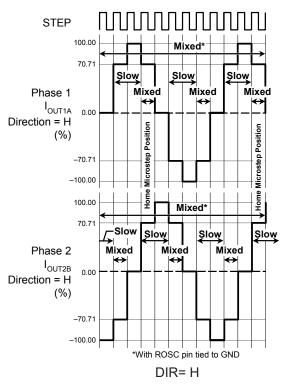

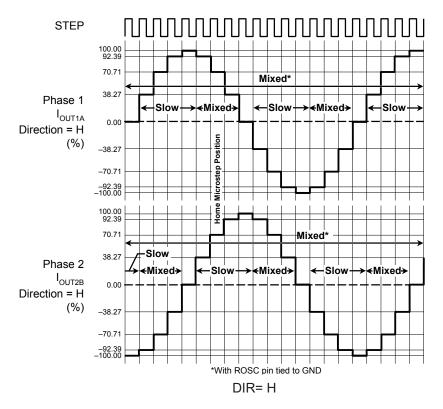

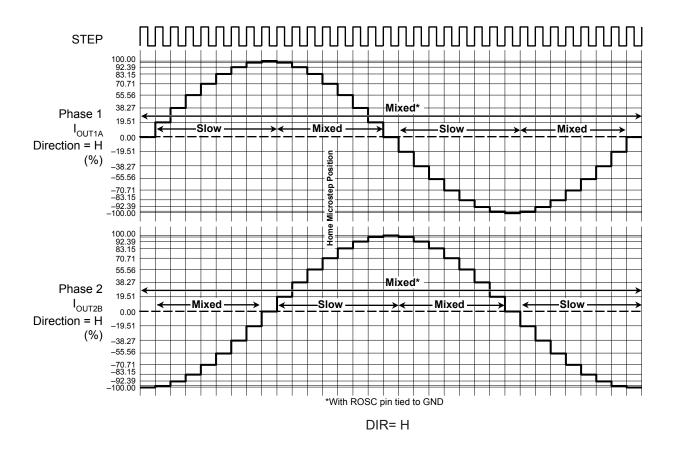

At power-on or reset, the translator sets the DACs and the phase current polarity to the initial Home state (shown in Figures 8 through 11), and the current regulator to Mixed Decay Mode for both phases. When a step command signal occurs on the STEP input, the translator automatically sequences the DACs to the next level and current polarity. (See Table 2 for the current-level sequence.) The microstep resolution is set by the combined effect of the MSx inputs, as shown in Table 1.

When stepping, if the new output levels of the DACs are lower than their previous output levels, then the decay mode for the active full-bridge is set to Mixed. If the new output levels of the DACs are higher than or equal to their previous levels, then the decay mode for the active full-bridge is set to Slow. This automatic current decay selection improves microstepping performance by reducing the distortion of the current waveform that results from the back EMF of the motor.

**Microstep Select (MSx).** The microstep resolution is set by the voltage on logic inputs MSx, as shown in Table 1. The MS1 pin has a  $100 \text{ k}\Omega$  pull-down resistance, and the MS2 pin has a  $50 \text{ k}\Omega$  pull-down resistance. When changing the step mode, the change does not take effect until the next STEP rising edge.

If the step mode is changed without a translator reset, and absolute position must be maintained, it is important to change the step mode at a step position that is common to both step modes in order to avoid missing steps. When the device is powered down or reset due to TSD or an over current event the translator is set to the home position which is by default common to all step modes.

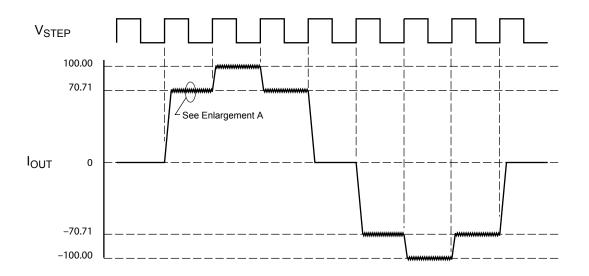

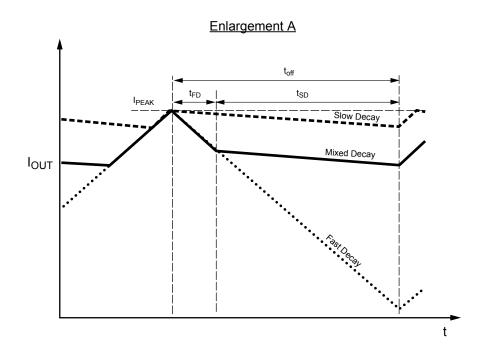

**Mixed Decay Operation.** The bridge operates in Mixed decay mode, at power-on and reset, and during normal running

according to the ROSC configuration and the step sequence, as shown in Figures 8 through 11. During Mixed decay, when the trip point is reached, the A4984 initially goes into a fast decay mode for 31.25% of the off-time,  $t_{OFF}$ . After that, it switches to Slow decay mode for the remainder of  $t_{OFF}$ . A timing diagram for this feature appears on the next page.

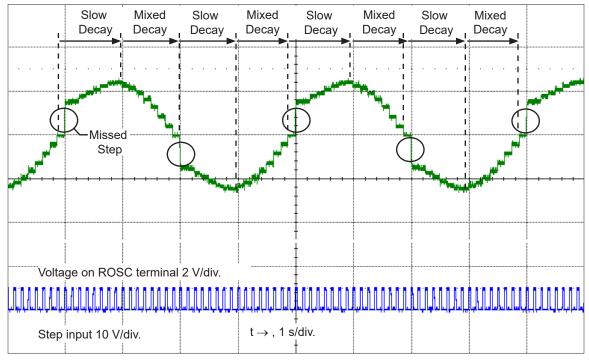

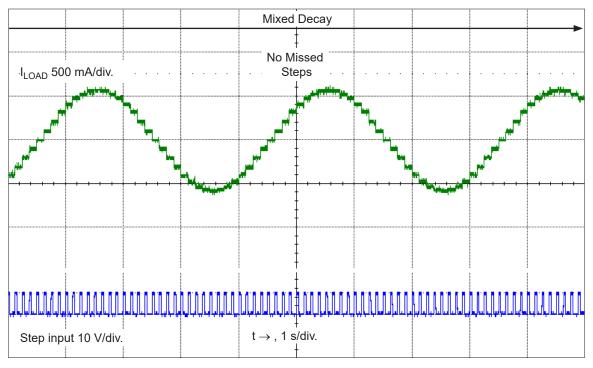

Typically, mixed decay is only necessary when the current in the winding is going from a higher value to a lower value as determined by the state of the translator. For most loads automatically selected mixed decay is convenient because it minimizes ripple when the current is rising and prevents missed steps when the current is falling. For some applications where microstepping at very low speeds is necessary, the lack of back EMF in the winding causes the current to increase in the load quickly, resulting in missed steps. This is shown in Figure 2. By pulling the ROSC pin to ground, mixed decay is set to be active 100% of the time, for both rising and falling currents, and prevents missed steps as shown in Figure 3. If this is not an issue, it is recommended that automatically selected mixed decay be used, because it will produce reduced ripple currents. Refer to the Fixed Off-Time section for details.

**Low Current Microstepping.** Intended for applications where the minimum on-time prevents the output current from regulating to the programmed current level at low current steps. To prevent this, the device can be set to operate in Mixed decay mode on both rising and falling portions of the current waveform. This feature is implemented by shorting the ROSC pin to ground. In this state, the off-time is internally set to 30 μs.

**Reset Input (RESET).** The  $\overline{\text{RESET}}$  input sets the translator to a predefined Home state (shown in Figures 8 through 11) and turns off all of the FET outputs. All STEP inputs are ignored until the  $\overline{\text{RESET}}$  input is set to high.

**Step Input (STEP).** A low-to-high transition on the STEP input sequences the translator and advances the motor one increment. The translator controls the input to the DACs and the direction of current flow in each winding. The size of the increment is determined by the combined state of the MSx inputs.

Figure 2: Missed Steps in Low-Speed Microstepping

Figure 3: Continuous Stepping Using Automatically Selected Mixed Stepping (ROSC pin grounded)

**Direction Input (DIR).** This determines the direction of rotation of the motor. Changes to this input do not take effect until the next STEP rising edge.

**Internal PWM Current Control.** Each full-bridge is controlled by a fixed off-time PWM current control circuit that limits the load current to a desired value,  $I_{TRIP}$ . Initially, a diagonal pair of source and sink FET outputs are enabled and current flows through the motor winding and the current sense resistor,  $R_{Sx}$ . When the voltage across  $R_{Sx}$  equals the DAC output voltage, the current sense comparator resets the PWM latch. The latch then turns off either the source FET (when in Slow decay mode) or the sink and source FETs (when in Mixed decay mode).

The maximum value of current limiting is set by the selection of  $R_{Sx}$  and the voltage at the VREF pin. The transconductance function is approximated by the maximum value of current limiting,  $I_{TripMAX}$  (A), which is set by

$$I_{TripMAX} = V_{REF}/(8 \times R_S)$$

where  $R_S$  is the resistance of the sense resistor ( $\Omega$ ) and  $V_{REF}$  is the input voltage on the REF pin (V).

The DAC output reduces the  $V_{REF}$  output to the current sense comparator in precise steps, such that

$$I_{trip} = (\%I_{TripMAX}/100) \times I_{TripMAX}$$

(See Table 2 for %I<sub>TripMAX</sub> at each step.)

It is critical that the maximum rating (0.5 V) on the SENSE1 and SENSE2 pins is not exceeded.

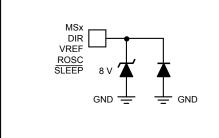

**Fixed Off-Time.** The internal PWM current control circuitry uses a one-shot circuit to control the duration of time that the DMOS FETs remain off. The off-time, t<sub>OFF</sub>, is determined by the ROSC terminal. The ROSC terminal has three settings:

- ROSC tied to VDD off-time internally set to 30 μs, decay mode is automatic Mixed decay except when in full step where decay mode is set to Slow decay

- ROSC tied directly to ground off-time internally set to 30 μs, current decay is set to Mixed decay for both increasing and decreasing currents for all step modes.

- ROSC through a resistor to ground off-time is determined by the following formula; the decay mode is automatic Mixed decay for all step modes except full step which is set to slow decay.

$$t_{OFF} \approx R_{OSC} / 825$$

Where  $t_{OFF}$  is in  $\mu s$ .

**Blanking.** This function blanks the output of the current sense comparators when the outputs are switched by the internal current

control circuitry. The comparator outputs are blanked to prevent false overcurrent detection due to reverse recovery currents of the clamp diodes, and switching transients related to the capacitance of the load. The blank time,  $t_{\rm BLANK}$  ( $\mu s$ ), is approximately

$$t_{BLANK} \approx 1 \ \mu s$$

#### Shorted-Load and Short-to-Ground Protection.

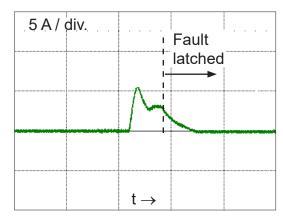

If the motor leads are shorted together, or if one of the leads is shorted to ground, the driver will protect itself by sensing the overcurrent event and disabling the driver that is shorted, protecting the device from damage. In the case of a short-to-ground, the device will remain disabled (latched) until the SLEEP input goes high or VDD power is removed. A short-to-ground overcurrent event is shown in Figure 4.

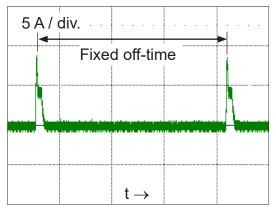

When the two outputs are shorted together, the current path is through the sense resistor. After the blanking time ( $\approx 1~\mu s$ ) expires, the sense resistor voltage is exceeding its trip value, due to the overcurrent condition that exists. This causes the driver to go into a fixed off-time cycle. After the fixed off-time expires the driver turns on again and the process repeats. In this condition the driver is completely protected against overcurrent events, but the short is repetitive with a period equal to the fixed off-time of the driver. This condition is shown in Figure 5.

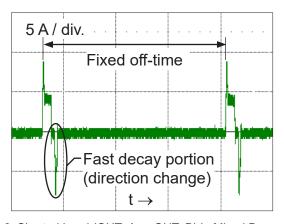

If the driver is operating in Mixed decay mode, it is normal for the positive current to spike, due to the bridge going in the forward direction and then in the negative direction, as a result of the direction change implemented by the Mixed decay feature. This is shown in Figure 6. In both instances the overcurrent circuitry is protecting the driver and prevents damage to the device.

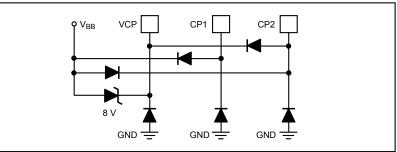

**Charge Pump (CP1 and CP2).** The charge pump is used to generate a gate supply greater than that of VBB for driving the source-side FET gates. A 0.1  $\mu$ F ceramic capacitor, should be connected between CP1 and CP2. In addition, a 0.1  $\mu$ F ceramic capacitor is required between VCP and VBB, to act as a reservoir for operating the high-side FET gates.

Capacitor values should be Class 2 dielectric  $\pm 15\%$  maximum, or tolerance R, according to EIA (Electronic Industries Alliance) specifications.

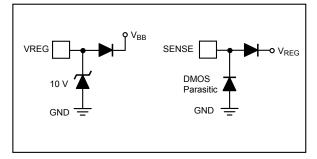

$V_{REG}$  (VREG). This internally generated voltage is used to operate the sink-side FET outputs. The nominal output voltage of the VREG terminal is 7 V. The VREG pin must be decoupled with a 0.22 μF ceramic capacitor to ground.  $V_{REG}$  is internally monitored. In the case of a fault condition, the FET outputs of the A4984 are disabled.

Capacitor values should be Class 2 dielectric  $\pm 15\%$  maximum, or tolerance R, according to EIA (Electronic Industries Alliance) specifications.

**Enable Input** (ENABLE). This input turns on or off all of the FET outputs. When set to a logic high, the outputs are disabled. When set to a logic low, the internal control enables the outputs as required. The translator inputs STEP, DIR, and MSx, as well as the internal sequencing logic, all remain active, independent of the ENABLE input state.

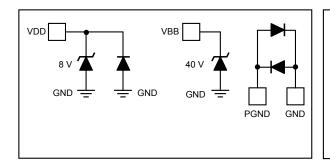

**Shutdown.** In the event of a fault, overtemperature (excess  $T_J$ ) or an undervoltage (on VCP), the FET outputs of the A4984 are disabled until the fault condition is removed. At power-on, the UVLO (undervoltage lockout) circuit disables the FET outputs and resets the translator to the Home state.

**Sleep Mode** (SLEEP). To minimize power consumption when the motor is not in use, this input disables much of the internal circuitry including the output FETs, current regulator, and charge pump. A logic low on the SLEEP pin puts the A4984 into Sleep mode. A logic high allows normal operation, as well as start-up (at which time the A4984 drives the motor to the Home microstep position). When emerging from Sleep mode, in order to allow the charge pump to stabilize, provide a delay of 1 ms before issuing a Step command.

**Mixed Decay Operation.** The bridge can operate in Mixed Decay mode, depending on the step sequence, as shown in Figures 8 through 11. As the trip point is reached, the A4984 initially goes into a fast decay mode for 31.25% of the off-time,  $t_{OFF}$ . After that, it switches to Slow Decay mode for the remainder of  $t_{OFF}$ . A timing diagram for this feature appears in Figure 7.

**Synchronous Rectification.** When a PWM-off cycle is triggered by an internal fixed-off time cycle, load current recirculates according to the decay mode selected by the control logic. This synchronous rectification feature turns on the appropriate FETs during current decay, and effectively shorts out the body diodes with the low FET  $R_{\rm DS(ON)}$ . This reduces power dissipation significantly and can eliminate the need for external Schottky diodes in many applications. Synchronous rectification turns off when the load current approaches zero (0 A), preventing reversal of the load current.

Figure 4: Short-to-Ground Event

Figure 5: Shorted Load (OUTxA  $\rightarrow$  OUTxB) in Slow Decay Mode

Figure 6: Shorted Load (OUTxA  $\rightarrow$  OUTxB) in Mixed Decay Mode

| Symbol            | Characteristic         |  |  |  |

|-------------------|------------------------|--|--|--|

| t <sub>off</sub>  | Device fixed off-time  |  |  |  |

| I <sub>PEAK</sub> | Maximum output current |  |  |  |

| t <sub>SD</sub>   | Slow decay interval    |  |  |  |

| t <sub>FD</sub>   | Fast decay interval    |  |  |  |

| I <sub>OUT</sub>  | Device output current  |  |  |  |

Figure 7: Current Decay Modes Timing Chart

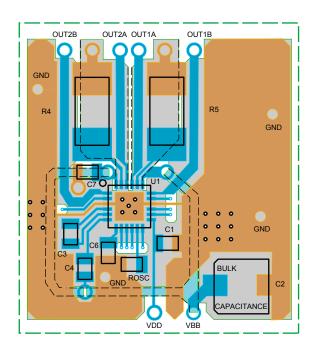

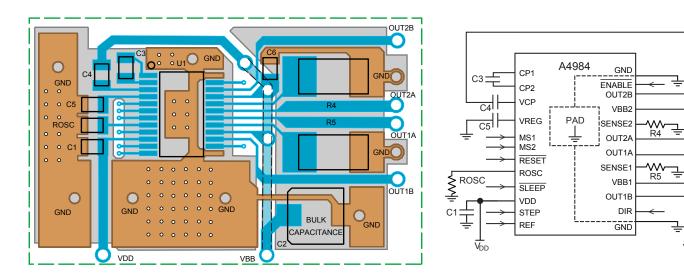

### **Application Layout**

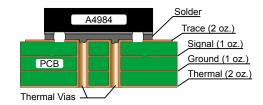

**Layout**. The printed circuit board should use a heavy ground-plane. For optimum electrical and thermal performance, the A4984 must be soldered directly onto the board. On the underside of the A4984 package is an exposed pad, which provides a path for enhanced thermal dissipation. The thermal pad should be soldered directly to an exposed surface on the PCB. Thermal vias are used to transfer heat to other layers of the PCB.

In order to minimize the effects of ground bounce and offset issues, it is important to have a low impedance single-point ground, known as a *star ground*, located very close to the device. By making the connection between the pad and the ground plane directly under the A4984, that area becomes an ideal location for a star ground point. A low impedance ground will prevent ground bounce during high current operation and ensure that the supply voltage remains stable at the input terminal.

The two input capacitors should be placed in parallel, and as close to the device supply pins as possible. The ceramic capacitor (C7) should be closer to the pins than the bulk capacitor (C2). This is necessary because the ceramic capacitor will be responsible for delivering the high frequency current components. The sense resistors, RSx, should have a very low impedance path to ground, because they must carry a large current while supporting very accurate voltage measurements by the current sense comparators. Long ground traces will cause additional voltage drops, adversely affecting the ability of the comparators to accurately measure the current in the windings. The SENSEx pins have very short traces to the RSx resistors and very thick, low impedance traces directly to the star ground underneath the device. If possible, there should be no other components on the sense circuits.

ES Package Configuration Shown

LP Package Typical Application and Circuit Layout

± C6

### Pin Circuit Diagrams

Figure 8: Decay Mode for Full-Step Increments

Figure 9: Decay Modes for Half-Step Increments

Figure 10. Decay Modes for Quarter-Step Increments

Figure 11: Decay Modes for Eighth-Step Increments

Table 2: Step Sequencing Settings

Home microstep position at Step Angle 45°; DIR = H

| Full<br>Step<br># | Half<br>Step<br># | 1/4<br>Step<br># | 1/8<br>Step<br># | Phase 1<br>Current<br>[%   <sub>tripMax</sub> ]<br>(%) | Phase 2<br>Current<br>[% ltripMax]<br>(%) | Step<br>Angle<br>(°) | Full<br>Step<br># | Half<br>Step<br># | 1/4<br>Step<br># | 1/8<br>Step<br># | Phase 1<br>Current<br>[% I <sub>tripMax</sub> ]<br>(%) | Phase 2<br>Current<br>[%  tripMax]<br>(%) | Step<br>Angle<br>(°) |

|-------------------|-------------------|------------------|------------------|--------------------------------------------------------|-------------------------------------------|----------------------|-------------------|-------------------|------------------|------------------|--------------------------------------------------------|-------------------------------------------|----------------------|

|                   | 1                 | 1                | 1                | 100.00                                                 | 0.00                                      | 0.0                  |                   | 5                 | 9                | 17               | -100.00                                                | 0.00                                      | 180.0                |

|                   |                   |                  |                  | 99.52                                                  | 9.80                                      | 5.6                  |                   |                   |                  |                  | -99.52                                                 | -9.80                                     | 185.6                |

|                   |                   |                  | 2                | 98.08                                                  | 19.51                                     | 11.3                 |                   |                   |                  | 18               | -98.08                                                 | -19.51                                    | 191.3                |

|                   |                   |                  |                  | 95.69                                                  | 29.03                                     | 16.9                 |                   |                   |                  |                  | -95.69                                                 | -29.03                                    | 196.9                |

|                   |                   | 2                | 3                | 92.39                                                  | 38.27                                     | 22.5                 |                   |                   | 10               | 19               | -92.39                                                 | -38.27                                    | 202.5                |

|                   |                   |                  |                  | 88.19                                                  | 47.14                                     | 28.1                 |                   |                   |                  |                  | -88.19                                                 | -47.14                                    | 208.1                |

|                   |                   |                  | 4                | 83.15                                                  | 55.56                                     | 33.8                 |                   |                   |                  | 20               | -83.15                                                 | -55.56                                    | 213.8                |

|                   |                   |                  |                  | 77.30                                                  | 63.44                                     | 39.4                 |                   |                   |                  |                  | -77.30                                                 | -63.44                                    | 219.4                |

| 1                 | 2                 | 3                | 5                | 70.71                                                  | 70.71                                     | 45.0                 | 3                 | 6                 | 11               | 21               | -70.71                                                 | -70.71                                    | 225.0                |

|                   |                   |                  |                  | 63.44                                                  | 77.30                                     | 50.6                 |                   |                   |                  |                  | -63.44                                                 | -77.30                                    | 230.6                |

|                   |                   |                  | 6                | 55.56                                                  | 83.15                                     | 56.3                 |                   |                   |                  | 22               | -55.56                                                 | -83.15                                    | 236.3                |

|                   |                   |                  |                  | 47.14                                                  | 88.19                                     | 61.9                 |                   |                   |                  |                  | -47.14                                                 | -88.19                                    | 241.9                |

|                   |                   | 4                | 7                | 38.27                                                  | 92.39                                     | 67.5                 |                   |                   | 12               | 23               | -38.27                                                 | -92.39                                    | 247.5                |

|                   |                   |                  |                  | 29.03                                                  | 95.69                                     | 73.1                 |                   |                   |                  |                  | -29.03                                                 | -95.69                                    | 253.1                |

|                   |                   |                  | 8                | 19.51                                                  | 98.08                                     | 78.8                 |                   |                   |                  | 24               | -19.51                                                 | -98.08                                    | 258.8                |

|                   |                   |                  |                  | 9.80                                                   | 99.52                                     | 84.4                 |                   |                   |                  |                  | -9.80                                                  | -99.52                                    | 264.4                |

|                   | 3                 | 5                | 9                | 0.00                                                   | 100.00                                    | 90.0                 |                   | 7                 | 13               | 25               | 0.00                                                   | -100.00                                   | 270.0                |

|                   |                   |                  |                  | -9.80                                                  | 99.52                                     | 95.6                 |                   |                   |                  |                  | 9.80                                                   | -99.52                                    | 275.6                |

|                   |                   |                  | 10               | -19.51                                                 | 98.08                                     | 101.3                |                   |                   |                  | 26               | 19.51                                                  | -98.08                                    | 281.3                |

|                   |                   |                  |                  | -29.03                                                 | 95.69                                     | 106.9                |                   |                   |                  |                  | 29.03                                                  | -95.69                                    | 286.9                |

|                   |                   | 6                | 11               | -38.27                                                 | 92.39                                     | 112.5                |                   |                   | 14               | 27               | 38.27                                                  | -92.39                                    | 292.5                |

|                   |                   |                  |                  | -47.14                                                 | 88.19                                     | 118.1                |                   |                   |                  |                  | 47.14                                                  | -88.19                                    | 298.1                |

|                   |                   |                  | 12               | -55.56                                                 | 83.15                                     | 123.8                |                   |                   |                  | 28               | 55.56                                                  | -83.15                                    | 303.8                |

|                   |                   |                  |                  | -63.44                                                 | 77.30                                     | 129.4                |                   |                   |                  |                  | 63.44                                                  | -77.30                                    | 309.4                |

| 2                 | 4                 | 7                | 13               | -70.71                                                 | 70.71                                     | 135.0                | 4                 | 8                 | 15               | 29               | 70.71                                                  | -70.71                                    | 315.0                |

|                   |                   |                  |                  | -77.30                                                 | 63.44                                     | 140.6                |                   |                   |                  |                  | 77.30                                                  | -63.44                                    | 320.6                |

|                   |                   |                  | 14               | -83.15                                                 | 55.56                                     | 146.3                |                   |                   |                  | 30               | 83.15                                                  | -55.56                                    | 326.3                |

|                   |                   |                  |                  | -88.19                                                 | 47.14                                     | 151.9                |                   |                   |                  |                  | 88.19                                                  | -47.14                                    | 331.9                |

|                   |                   | 8                | 15               | -92.39                                                 | 38.27                                     | 157.5                |                   |                   | 16               | 31               | 92.39                                                  | -38.27                                    | 337.5                |

|                   |                   |                  |                  | -95.69                                                 | 29.03                                     | 163.1                |                   |                   |                  |                  | 95.69                                                  | -29.03                                    | 343.1                |

|                   |                   |                  | 16               | -98.08                                                 | 19.51                                     | 168.8                |                   |                   |                  | 32               | 98.08                                                  | -19.51                                    | 348.8                |

|                   |                   |                  |                  | -99.52                                                 | 9.80                                      | 174.4                |                   |                   |                  |                  | 99.52                                                  | -9.80                                     | 354.4                |

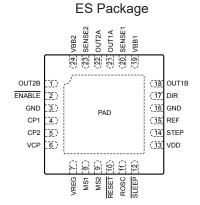

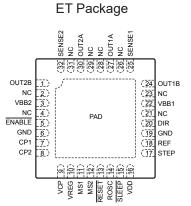

### Pin-out Diagrams

LP Package

#### Terminal List Table

| Number |       |                                 |        |                                               |

|--------|-------|---------------------------------|--------|-----------------------------------------------|

| Name   | ES    | ET*                             | LP     | Description                                   |

| CP1    | 4     | 7                               | 1      | Charge pump capacitor terminal                |

| CP2    | 5     | 8                               | 2      | Charge pump capacitor terminal                |

| DIR    | 17    | 20                              | 14     | Logic input                                   |

| ENABLE | 2     | 5                               | 23     | Logic input                                   |

| GND    | 3, 16 | 6, 19                           | 13, 24 | Ground                                        |

| MS1    | 8     | 11                              | 5      | Logic input                                   |

| MS2    | 9     | 12                              | 6      | Logic input                                   |

| NC     | -     | 2, 4, 21, 23,<br>26, 28, 29, 31 | -      | No connection                                 |

| OUT1A  | 21    | 27                              | 18     | DMOS Full Bridge 1 Output A                   |

| OUT1B  | 18    | 24                              | 15     | DMOS Full Bridge 1 Output B                   |

| OUT2A  | 22    | 30                              | 19     | DMOS Full Bridge 2 Output A                   |

| OUT2B  | 1     | 1                               | 22     | DMOS Full Bridge 2 Output B                   |

| REF    | 15    | 18                              | 12     | G <sub>m</sub> reference voltage input        |

| RESET  | 10    | 13                              | 7      | Logic input                                   |

| ROSC   | 11    | 14                              | 8      | Timing set                                    |

| SENSE1 | 20    | 25                              | 17     | Sense resistor terminal for Bridge 1          |

| SENSE2 | 23    | 32                              | 20     | Sense resistor terminal for Bridge 2          |

| SLEEP  | 12    | 15                              | 9      | Logic input                                   |

| STEP   | 14    | 17                              | 11     | Logic input                                   |

| VBB1   | 19    | 22                              | 16     | Load supply                                   |

| VBB2   | 24    | 3                               | 21     | Load supply                                   |

| VCP    | 6     | 9                               | 3      | Reservoir capacitor terminal                  |

| VDD    | 13    | 16                              | 10     | Logic supply                                  |

| VREG   | 7     | 10                              | 4      | Regulator decoupling terminal                 |

| PAD    | _     | _                               | _      | Exposed pad for enhanced thermal dissipation* |

<sup>\*</sup>The GND pins must be tied together externally by connecting to the PAD ground plane under the device.

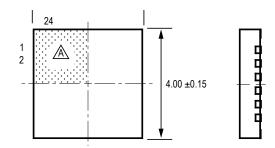

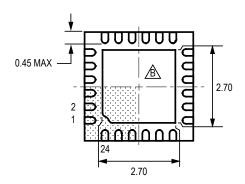

### ES Package, 24-Pin QFN with Exposed Thermal Pad

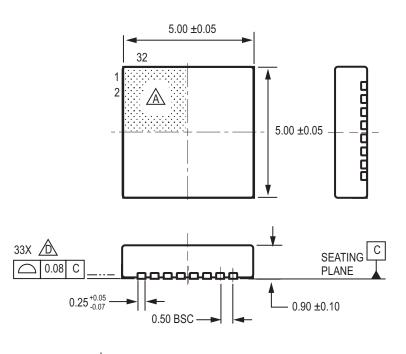

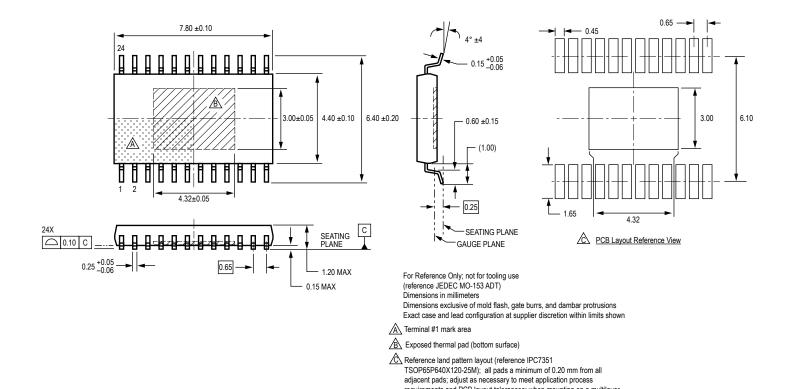

For Reference Only; not for tooling use (reference JEDEC MO-220WGGD) Dimensions in millimeters

Exact case and lead configuration at supplier discretion within limits shown

A Terminal #1 mark area

Exposed thermal pad (reference only, terminal #1 identifier appearance at supplier discretion)

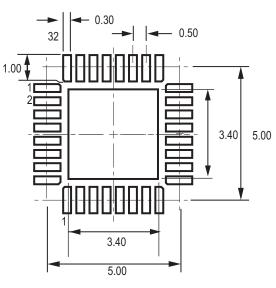

Reference land pattern layout (reference IPC7351 QFN50P400X400X80-25W6M)

All pads a minimum of 0.20 mm from all adjacent pads; adjust as necessary to meet application process requirements and PCB layout tolerances; when mounting on a multilayer PCB, thermal vias at the exposed thermal pad land can improve thermal dissipation (reference EIA/JEDEC Standard JESD51-5)

Coplanarity includes exposed thermal pad and terminals

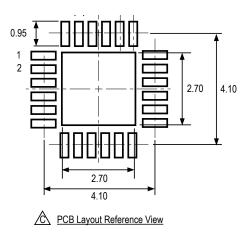

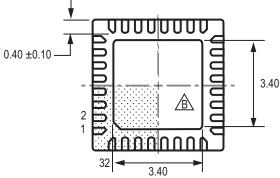

### ET Package, 32-Pin QFN with Exposed Thermal Pad

PCB Layout Reference View

For Reference Only; not for tooling use (reference JEDEC MO-220VHHD-5) Dimensions in millimeters

Exact case and lead configuration at supplier discretion within limits shown

A Terminal #1 mark area

Exposed thermal pad (reference only, terminal #1 identifier appearance at supplier discretion)

Reference land pattern layout (reference IPC7351 QFN50P500X500X100-33V6M);

All pads a minimum of 0.20 mm from all adjacent pads; adjust as necessary to meet application process requirements and PCB layout tolerances; when mounting on a multilayer PCB, thermal vias at the exposed thermal pad land can improve thermal dissipation (reference EIA/JEDEC Standard JESD51-5)

Coplanarity includes exposed thermal pad and terminals

requirements and PCB layout tolerances; when mounting on a multilayer PCB, thermal vias at the exposed thermal pad land can improve thermal dissipation (reference EIA/JEDEC Standard JESD51-5)

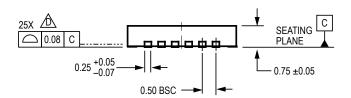

### LP Package, 24-Pin TSSOP with Exposed Thermal Pad

A4984

## DMOS Microstepping Driver with Translator and Overcurrent Protection

#### **Revision History**

| Number | Date              | Description                                                                      |

|--------|-------------------|----------------------------------------------------------------------------------|

| 4      | March 21, 2012    | Update example layout                                                            |

| 5      | February 24, 2014 | Revised Fixed Off-Time section, Figure 8, Table 2, and pkg. dims. for 32-pin QFN |

| 6      | April 2, 2020     | Minor editorial updates                                                          |

Copyright 2020, Allegro MicroSystems.

Allegro MicroSystems reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of Allegro's product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copies of this document are considered uncontrolled documents.

For the latest version of this document, visit our website: www.allegromicro.com