**AUR9717**

### **General Description**

The AUR9717 is a high efficiency step-down DC-DC voltage converter. The chip operation is optimized using constant frequency, peak-current mode architecture with built-in synchronous power MOSFET switchers and internal compensators to reduce external part counts. It is automatically switching between the normal PWM mode and LDO mode to offer improved system power efficiency covering a wide range of loading conditions.

The oscillator and timing capacitors are all built-in providing an internal switching frequency of 1.5MHz that allows the use of small surface mount inductors and capacitors for portable product implementations. Additional features including Soft Start (SS), Under Voltage Lock Out (UVLO), Input Over Voltage Protection (IOVP) and Thermal Shutdown Detection (TSD) are integrated to provide reliable product applications.

The device is available in adjustable output voltage versions ranging from 1V to 3.3V, and is able to deliver up to 1A.

The AUR9717 is available in WDFN-3×3-10 package.

### **Features**

- Dual Channel High Efficiency Buck Power Converter

- Low Quiescent Current

- Output Current: 1A

- Adjustable Output Voltage from 1V to 3.3V

- Wide Operating Voltage Range: 2.5V to 5.5V

- Built-in Power Switchers for Synchronous Rectification with High Efficiency

- Feedback Voltage: 600mV

- 1.5MHz Constant Frequency Operation

- Automatic PWM/LDO Mode Switching Control

- Thermal Shutdown Protection

- Low Drop-out Operation at 100% Duty Cycle

- No Schottky Diode Required

- Internal Input Over Voltage Protection

- For automotive applications requiring specific change control (i.e. parts qualified to AEC-Q100/101/200, PPAP capable, and manufactured in IATF 16949 certified facilities), please contact us or your local Diodes representative.

- https://www.diodes.com/quality/product-definitions/

# **Applications**

- Mobile Phone, Digital Camera and MP3 Player

- Headset, Radio and Other Hand-held Instruments

- Post DC-DC Voltage Regulation

- PDA and Notebook Computer

Figure 1. Package Type of AUR9717

AUR9717

Document number: DS42569 Rev. 1 - 3

© Diodes Incorporated

**AUR9717**

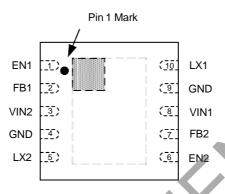

# **Pin Configuration**

D Package (WDFN-3×3-10)

Figure 2. Pin Configuration of AUR9717 (Top View)

# **Pin Description**

| Pin Number | Pin Name | Function                                                                                             |  |

|------------|----------|------------------------------------------------------------------------------------------------------|--|

| 1          | ENI      | Enable signal input of channel 1, active high                                                        |  |

| 2          | FB1      | Feedback voltage of channel 1                                                                        |  |

| 3          | VIN2     | Power supply input of channel 2                                                                      |  |

| 4,9        | GND      | This pin is the GND reference for the NMOSFET power stage. It must be connected to the system ground |  |

| 5          | LX2      | Connection from power MOSFET of channel 2 to inductor                                                |  |

| 6          | EN2      | Enable signal input of channel 2, active high                                                        |  |

| 7          | FB2      | Feedback voltage of channel 2                                                                        |  |

| 8          | VIN1     | Power supply input of channel 1                                                                      |  |

| 10         | LX1      | Connection from power MOSFET of channel 1 to inductor                                                |  |

AUR9<u>717</u>

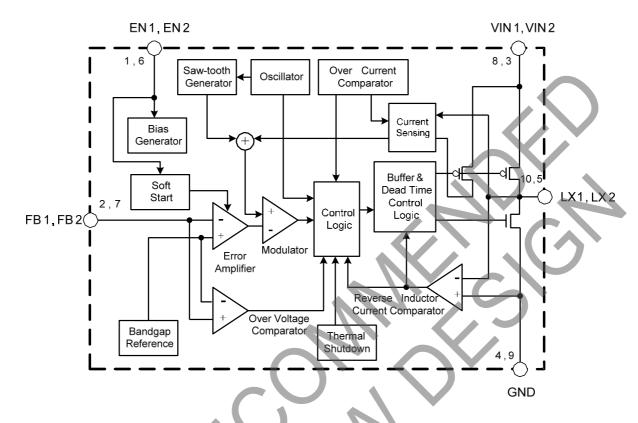

# **Functional Block Diagram**

Figure 3. Functional Block Diagram of AUR9717

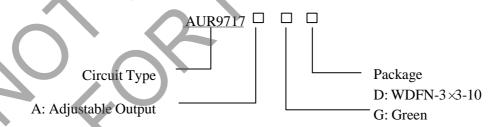

# **Ordering Information**

| Package     | Temperature<br>Range | Part Number | Marking ID | Packing Type |

|-------------|----------------------|-------------|------------|--------------|

| WDFN-3×3-10 | -40 to 80 ℃          | AUR9717AGD  | 9717A      | Tape & Reel  |

AUR9717

Document number: DS42569 Rev. 1 - 3

April 2020

© Diodes Incorporated

**AUR9717**

# **Absolute Maximum Ratings (Note 1)**

| Parameter                                            | Symbol                 | Value                              | Unit          |

|------------------------------------------------------|------------------------|------------------------------------|---------------|

| Supply Input Voltage                                 | $V_{IN1}$ , $V_{IN2}$  | 0 to 6.5                           | V             |

| Enable Input Voltage                                 | $V_{EN1}, V_{EN2}$     | -0.3 to                            | V             |

|                                                      |                        | $V_{IN1}(V_{IN2})+0.3$             |               |

| Switch Output Voltage                                | $V_{LX1}, V_{LX2}$     | -0.3  to<br>$V_{IN1}(V_{IN2})+0.3$ | V             |

| V <sub>IN1</sub> -V <sub>IN2</sub> Voltage (Note 2)  | $V_{\mathrm{DF}}$      | -0.3 to 0.3                        | V             |

| Power Dissipation (On PCB, T <sub>A</sub> =25 °C)    | $P_{D}$                | 2.22                               | W             |

| Thermal Resistance (Junction to Ambient, Simulation) | $\theta_{\mathrm{JA}}$ | 45.13                              | C/W           |

| Thermal Resistance (Junction to Case, Simulation)    | $\theta_{ m JC}$       | 6.97                               | C/W           |

| Operating Junction Temperature                       | $T_{J}$                | 160                                | $\mathbb{C}$  |

| Operating Temperature                                | $T_{\mathrm{OP}}$      | -40 to 85                          | $\mathcal{C}$ |

| Storage Temperature                                  | $T_{STG}$              | -55 to 150                         | $\mathcal C$  |

| ESD (Human Body Model)                               | $V_{\mathrm{HBM}}$     | 2000                               | V             |

| ESD (Machine Model)                                  | $V_{MM}$               | 200                                | V             |

Note 1: Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to "Absolute Maximum Ratings" for extended periods may affect device reliability.

Note 2: The absolute voltage difference between  $V_{\rm IN1}$  and  $V_{\rm IN2}$  can not exceed 0.3V.

# **Recommended Operating Conditions**

| Parameter                  | Symbol                | Min | Max | Unit          |

|----------------------------|-----------------------|-----|-----|---------------|

| Supply Input Voltage       | $V_{IN1}$ , $V_{IN2}$ | 2.5 | 5.5 | V             |

| Junction Temperature Range | $T_{J}$               | -20 | 125 | ${\mathbb C}$ |

| Ambient Temperature Range  | $T_{A}$               | -40 | 80  | ${\mathbb C}$ |

**AUR9717**

# **Electrical Characteristics**

$V_{IN} = V_{EN1} = V_{EN2} = 5V, \ V_{FB1} = V_{FB2} = 0.6V, \ L1 = L2 = 2.2 \mu H, \ C_{IN1} = C_{IN2} = 4.7 \mu F, \ C_{OUT1} = C_{OUT2} = 10 \mu F, \ T_A = 25 \ C, \ unless otherwise specified.$

| Parameter                            | Symbol                                                 | Conditions                                                                                                             | Min   | Тур  | Max   | Unit          |

|--------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------|------|-------|---------------|

| Input Voltage Range                  | $V_{IN}$                                               | $V_{IN}=V_{IN1}=V_{IN2}$                                                                                               | 2.5   |      | 5.5   | V             |

| Shutdown Current                     | $I_{\mathrm{OFF}}$                                     | $V_{ENI}=V_{EN2}=0V$                                                                                                   |       | 0.1  | 1     | μA            |

| Regulated Feedback<br>Voltage        | $V_{\mathrm{FB}}$                                      | For Adjustable Output Voltage                                                                                          | 0.585 | 0.6  | 0.615 | V             |

| Regulated Output<br>Voltage Accuracy | $\Delta V_{OUT1}/V_{OUT1},$ $\Delta V_{OUT2}/V_{OUT2}$ | $V_{IN}$ =2.5V to 5.5V,<br>$I_{OUT1}$ = $I_{OUT2}$ =0 to 1A                                                            | -3    |      | 3     | %             |

| Peak Inductor<br>Current             | $I_{PK}$                                               | V <sub>FB1</sub> =V <sub>FB2</sub> =0.5V                                                                               |       | 1.5  | -     | A             |

| Oscillator Frequency                 | $f_{ m OSC}$                                           |                                                                                                                        | 1.2   | 1.5  | 1.8   | MHz           |

| PMOSFET R <sub>ON</sub>              | $R_{ON(P)}$                                            | I <sub>OUT1</sub> =I <sub>OUT2</sub> =200mA                                                                            |       | 0.28 |       | Ω             |

| NMOSFET R <sub>ON</sub>              | $R_{ON(N)}$                                            | I <sub>OUT1</sub> =I <sub>OUT2</sub> =200mA                                                                            |       | 0.25 |       | Ω             |

| LX Leakage Current                   | ${ m I}_{ m LX}$                                       | $egin{array}{lll} V_{EN1}\!\!=\!\!V_{EN2}\!\!=\!\!0V, \\ V_{LX1}\!\!=\!\!V_{LX2}\!\!=\!\!0V \ { m or}\ 5V \end{array}$ |       | 0.01 | 0.1   | μA            |

| Feedback Current                     | $I_{\mathrm{FB1}}$ , $I_{\mathrm{FB2}}$                |                                                                                                                        | X     |      | 30    | nA            |

| Input Over Voltage<br>Protection     | V <sub>IOVP</sub>                                      |                                                                                                                        | ) `   | 6    |       | V             |

| EN Leakage Current                   | $I_{\text{EN1}}, I_{\text{EN2}}$                       |                                                                                                                        |       | 0.01 | 0.1   | μA            |

| EN High-level Input<br>Voltage       | $V_{\text{EN\_H1}}, V_{\text{EN\_H2}}$                 | V <sub>IN</sub> =2.5V to 5.5V                                                                                          | 1.5   |      |       | V             |

| EN Low-level Input<br>Voltage        | V <sub>EN_L</sub> , V <sub>EN_12</sub>                 | V <sub>IN</sub> =2.5V to 5.5V                                                                                          |       |      | 0.6   | V             |

| Under Voltage Lock<br>Out            | $V_{\rm UVLO}$                                         | Rising                                                                                                                 |       | 1.8  |       | V             |

| Hysteresis                           |                                                        | Hysteresis                                                                                                             |       | 0.1  |       | V             |

| Thermal Shutdown                     | $T_{SD}$                                               |                                                                                                                        |       | 160  |       | ${\mathbb C}$ |

**AUR9717**

# **Typical Performance Characteristics**

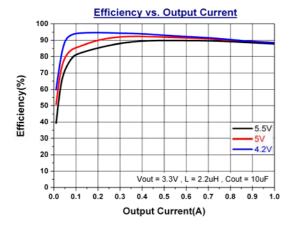

Figure 4. Efficiency vs. Output Current

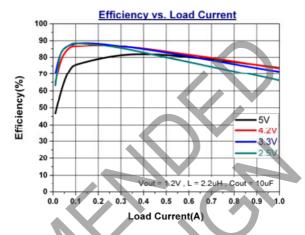

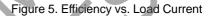

Figure 6. Efficiency vs. Load Current

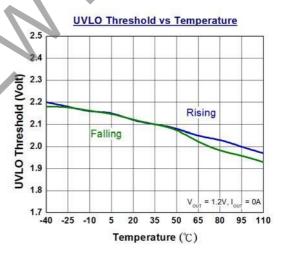

Figure 7. UVLO Threshold vs. Temperature

**AUR9717**

# **Typical Performance Characteristics (Continued)**

Output Current Limit vs Input Voltage

2.4

2.3

(dwy)

2.1

2.0

1.9

1.8

1.7

1.6

1.5

1.7

1.6

1.3

3.1

3.4

3.7

4.0

4.3

4.6

4.9

5.2

5.5

Input Voltage (Volt)

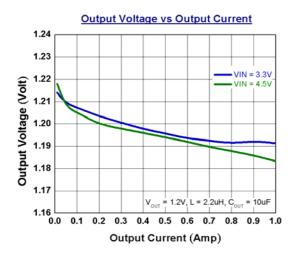

Figure 8. Output Voltage vs. Output Current

Figure 9. Output Current Limit vs. Input Voltage

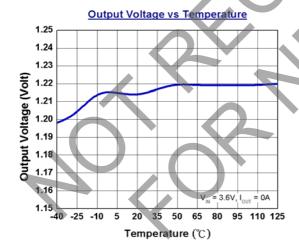

Figure 10. Output Voltage vs. Temperature

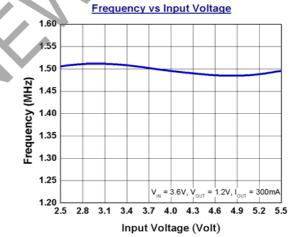

Figure 11. Frequency vs. Input Voltage

**AUR9717**

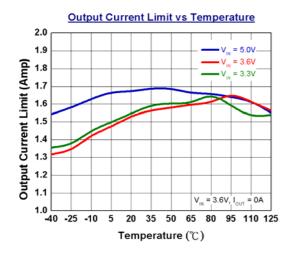

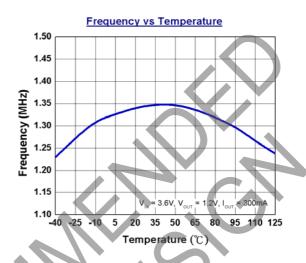

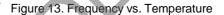

# **Typical Performance Characteristics (Continued)**

Figure 12. Output Current Limit vs. Temperature

Figure 14. Temperature vs. Load Current

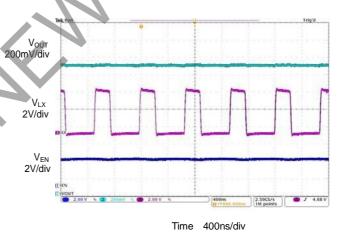

Figure 15. Waveform of  $V_{IN}$ =4.5V,  $V_{OUT}$ =1.5V, L=2.2 $\mu$ H

AUR9717 Document number: DS42569 Rev. 1 - 3 April 2020 © Diodes Incorporated

**AUR9717**

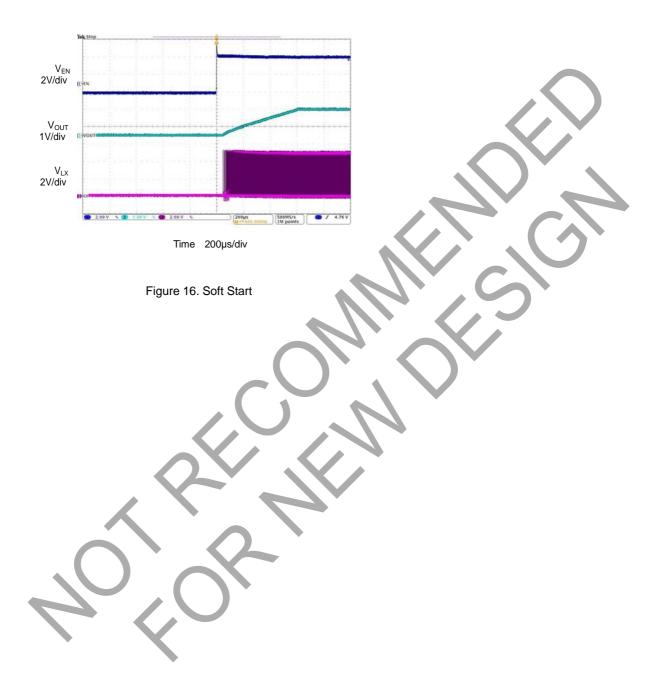

# **Typical Performance Characteristics (Continued)**

**AUR9717**

## **Application Information**

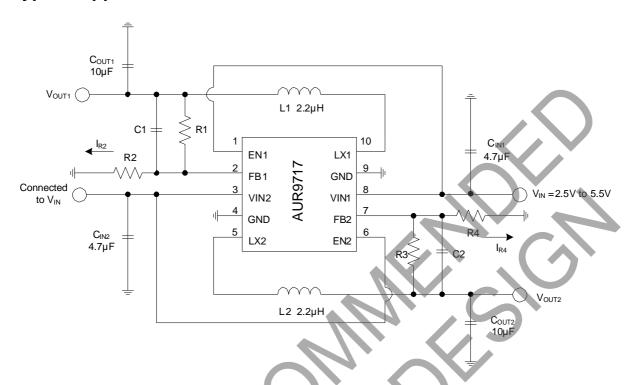

The basic AUR9717 application circuit is shown in Figure 18.

#### 1. Inductor Selection

For most applications, the value of inductor is chosen based on the required ripple current with the range of 2.2µH to 4.7µH.

$$\Delta I_L = \frac{1}{f \times L} V_{OUT} (1 - \frac{V_{OUT}}{V_{IN}})$$

The largest ripple current occurs at the highest input voltage. Having a small ripple current reduces the ESR loss in the output capacitor and improves the efficiency. The highest efficiency is realized at low operating frequency with small ripple current. However, larger value inductors will be required. A reasonable starting point for ripple current setting is  $\Delta I_L \! = \! 40\% I_{MAX}.$  For a maximum ripple current stays below a specified value, the inductor should be chosen according to the following equation:

$$L = [\frac{V_{OUT}}{f \times \Delta I_L(MAX)}][1 - \frac{V_{OUT}}{V_{IN}(MAX)}]$$

The DC current rating of the inductor should be at least equal to the maximum output current plus half the highest ripple current to prevent inductor core saturation. For better efficiency, a lower DC-resistance inductor should be selected.

### 2. Capacitor Selection

The input capacitance,  $C_{\rm IN}$ , is needed to filter the trapezoidal current at the source of the top MOSFET. To prevent large ripple voltage, a low ESR input capacitor sized for the maximum RMS current must be used. The maximum RMS capacitor current is given by:

$$I_{RMS} = I_{OMAX} \times \frac{\left[V_{OUT} \left(V_{IN} - V_{OUT}\right)\right]^{\frac{1}{2}}}{V_{IN}}$$

It indicates a maximum value at  $V_{IN}=2V_{OUT}$ , where  $I_{RMS}=I_{OUT}/2$ . This simple worse-case condition is commonly used for design because even significant

deviations do not much relieve. The selection of  $C_{OUT}$  is determined by the Effective Series Resistance (ESR) that is required to minimize output voltage ripple and load step transients, as well as the amount of bulk capacitor that is necessary to ensure that the control loop is stable. Loop stability can be also checked by viewing the load step transient response as described in the following section. The output ripple,  $\triangle V_{OUT}$ , is determined by:

$$\Delta V_{OUT} \le \Delta I_L [ESR + \frac{1}{8 \times f \times C_{OUT}}]$$

The output ripple is the highest at the maximum input voltage since  $\triangle I_L$  increases with input voltage.

#### 3. Load Transient

A switching regulator typically takes several cycles to respond to the load current step. When a load step occurs,  $V_{OUT}$  immediately shifts by an amount equal to  $\triangle I_{LOAD} \times ESR$ , where ESR is the effective series resistance of output capacitor.  $\triangle I_{LOAD}$  also begins to charge or discharge  $C_{OUT}$  generating a feedback error signal used by the regulator to return  $V_{OUT}$  to its steady-state value. During the recovery time,  $V_{OUT}$  can be monitored for overshoot or ringing that would

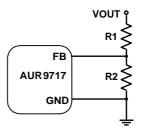

#### 4. Output Voltage Setting

The output voltage of AUR9717 can be adjusted by a resistive divider according to the following formula:

$$V_{OUT} = V_{FB} \times (1 + \frac{R_1}{R_2}) = 0.6V \times (1 + \frac{R_1}{R_2})$$

The resistive divider senses the fraction of the output voltage as shown in Figure 17.

Figure 17. Setting the Output Voltage

**AUR9717**

### **Application Information (Continued)**

### 5. Efficiency Considerations

The efficiency of switching regulator is equal to the output power divided by the input power times 100%. It is usually useful to analyze the individual losses to determine what is limiting efficiency and which change could produce the largest improvement. Efficiency can be expressed as:

Efficiency=100%-L1-L2-.....

Where L1, L2, etc. are the individual losses as a percentage of input power.

Although all dissipative elements in the regulator produce losses, two major sources usually account for most of the power losses: V<sub>IN</sub> quiescent current and I<sup>2</sup>R losses. The V<sub>IN</sub> quiescent current loss dominates the efficiency loss at very light load currents and the I<sup>2</sup>R loss dominates the efficiency loss at medium to heavy load currents.

5.1 The V<sub>IN</sub> quiescent current loss comprises two parts: the DC bias current as given in the electrical characteristics and the internal MOSFET switch gate charge currents. The gate charge current results from switching the gate capacitance of the internal power MOSFET switches. Each cycle the gate is switched from high to low, then to high again, and the packet of charge, dQ moves from  $V_{\rm IN}$  to ground. The resulting dQ/dt is the current out of  $V_{IN}$  that is typically larger than the internal DC bias current. In continuous mode,

$$I_{GATE} = f \times (Q_P + Q_N)$$

Downloaded from Arrow.com.

Where Q<sub>P</sub> and Q<sub>N</sub> are the gate charge of power PMOSFET and NMOSFET switches. Both the DC bias current and gate charge losses are proportional to the V<sub>IN</sub> and this effect will be more serious at higher input voltages.

**5.2** I<sup>2</sup>R losses are calculated from internal switch resistance, R<sub>SW</sub> and external inductor resistance R<sub>L</sub>. In continuous mode, the average output current flowing through the inductor is chopped between power PMOSFET switch and NMOSFET switch. Then, the series resistance looking into the LX pin is a function of both PMOSFET R<sub>DS(ON)P</sub> and

NMOSFET R<sub>DS(ON)N</sub> resistance and the duty cycle

$$R_{SW} = R_{DS(ON)P} \times D + R_{DS(ON)N} \times (1 - D)$$

Therefore, to obtain the I<sup>2</sup>R losses, simply add R<sub>SW</sub> to R<sub>L</sub> and multiply the result by the square of the average output current.

Other losses including C<sub>IN</sub> and C<sub>OUT</sub> ESR dissipative losses and inductor core losses generally account for less than 2% of total additional loss.

#### 6. Thermal Characteristics

In most applications, the part does not dissipate much heat due to its high efficiency. However, in some conditions when the part is operating in high ambient temperature with high R<sub>DS(ON)</sub> resistance and high duty cycles, such as in LDO mode, the heat dissipated may exceed the maximum junction temperature. To avoid the part from exceeding maximum junction temperature, the user should do some thermal analysis. The maximum power dissipation depends on the layout of PCB, the thermal resistance of IC package, the rate of surrounding airflow and the temperature difference between junction and ambient.

#### 7. PC Board layout considerations

When laying out the printed circuit board, the following checklist should be used to optimize the performance of AUR9717.

- 1. The power traces, including the GND trace, the LX trace and the VIN trace should be kept direct, short and

- 2. Put the input capacitor as close as possible to the VIN and GND pins.

- 3. The FB pin should be connected directly to the feedback resistor divider.

- 4. Keep the switching node LX away from the sensitive FB pin and the node should be kept small area.

AUR9717 April 2020 Document number: DS42569 Rev. 1 - 3 © Diodes Incorporated 11

**AUR9717**

# **Typical Application**

Note 3:

$$V_{OUT1} = V_{FB1} \times (1 + \frac{R_1}{R_2})$$

;  $V_{OUT2} = V_{FB2} \times (1 + \frac{R_3}{R_4})$

When R2 or R4=300k $\Omega$  to  $60k\Omega$ , the  $I_{R2}$  or  $I_{R4}$ =2 $\mu$ A to  $10\mu$ A, and R1 ×C1 or R3 ×C2 should be in the range between  $3 \times 10^{-6}$  and  $6 \times 10^{-6}$  for component selection.

Figure 18. Typical Application Circuit of AUR9717 (Note 3)

# Table 1. Component Guide

| $egin{array}{c} V_{OUT1} \ or \ V_{OUT2} \ (V) \end{array}$ | R1 or R3<br>(kΩ) | <b>R2 or R4</b> (kΩ) | C1 or C2<br>(pF) | L1 or L2<br>(µH) |

|-------------------------------------------------------------|------------------|----------------------|------------------|------------------|

| 3.3                                                         | 453              | 100                  | 13               | 2.2              |

| 2.5                                                         | 320              | 100                  | 18               | 2.2              |

| 1.8                                                         | 200              | 100                  | 30               | 2.2              |

| 1.2                                                         | 100              | 100                  | 56               | 2.2              |

| 1.0                                                         | 68               | 100                  | 82               | 2.2              |

AUR9717 April 2020 © Diodes Incorporated 12

Document number: DS42569 Rev. 1 - 3

**AUR9717**

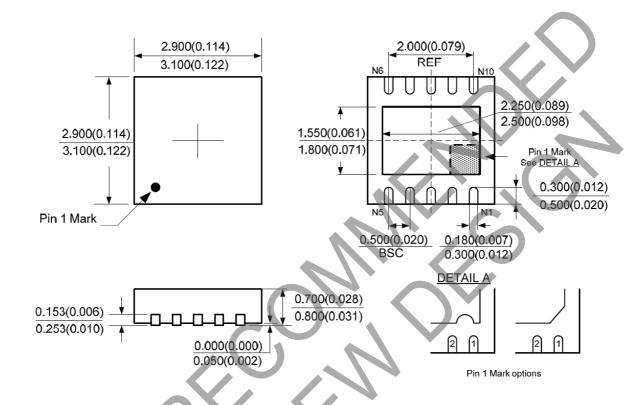

# **Mechanical Dimensions**

WDFN-3×3-10 Unit: mm(inch)

#### **IMPORTANT NOTICE**

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2020, Diodes Incorporated

www.diodes.com

AUR9717 April 2020 Document number: DS42569 Rev. 1 - 3 14