**CDCM6208**

SCAS931G -MAY 2012-REVISED JANUARY 2018

# CDCM6208 2:8 Clock Generator, Jitter Cleaner With Fractional Dividers

Check for Samples: CDCM6208

#### **Features**

- Superior Performance With Low Power:

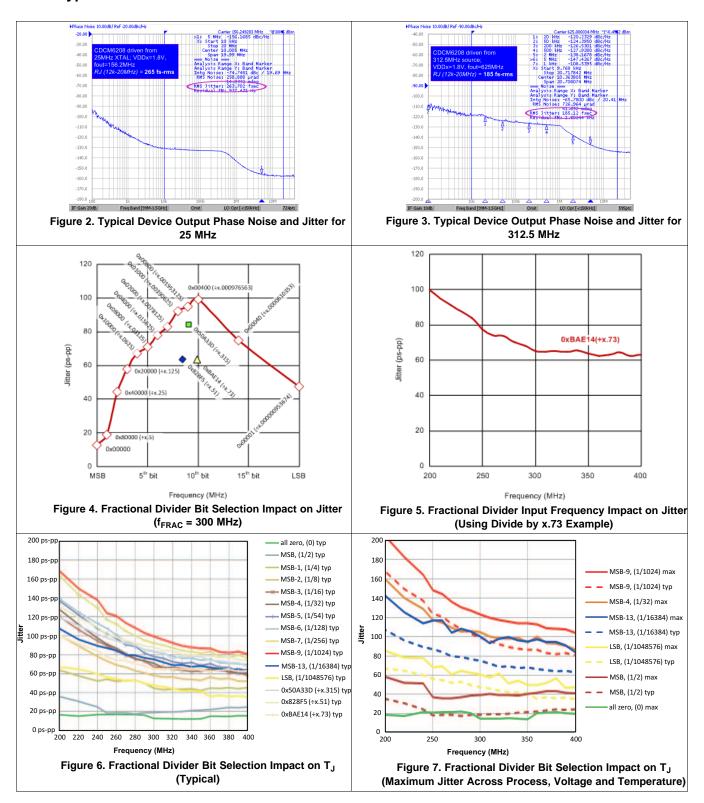

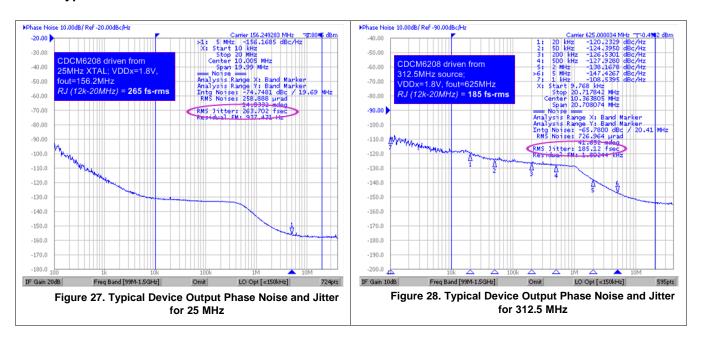

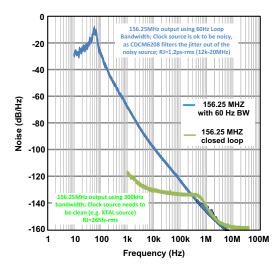

- Low Noise Synthesizer (265 fs-rms Typical Jitter) or Low Noise Jitter Cleaner (1.6 ps-rms Typical Jitter)

- 0.5-W Typical Power Consumption

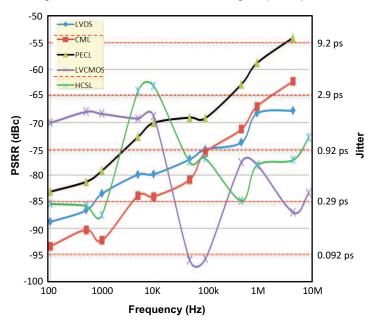

- High Channel-to-Channel Isolation and **Excellent PSRR**

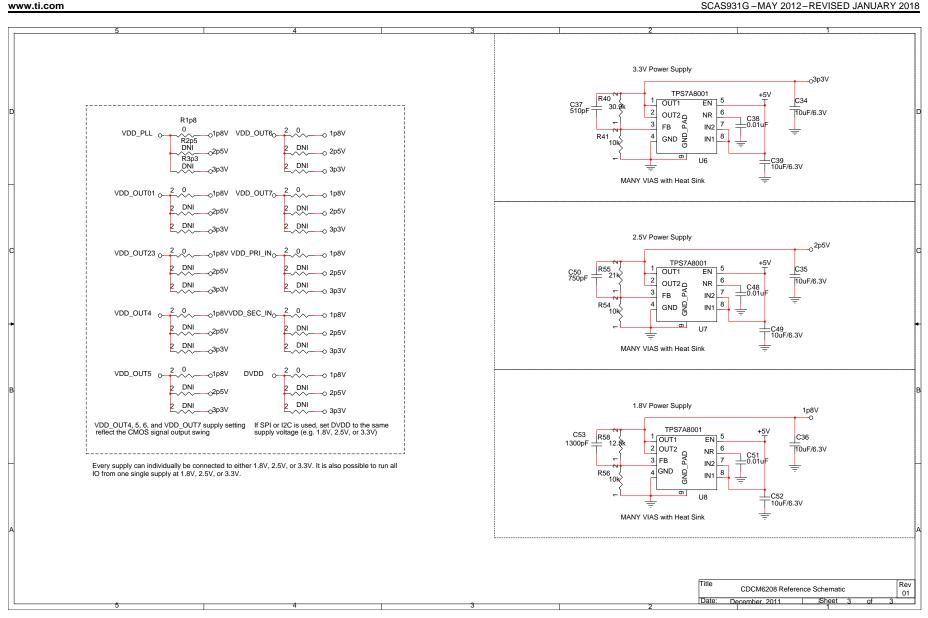

- Device Performance Customizable Through Flexible 1.8-V, 2.5-V and 3.3-V Power Supplies, Allowing Mixed Output Voltages

- Flexible Frequency Planning:

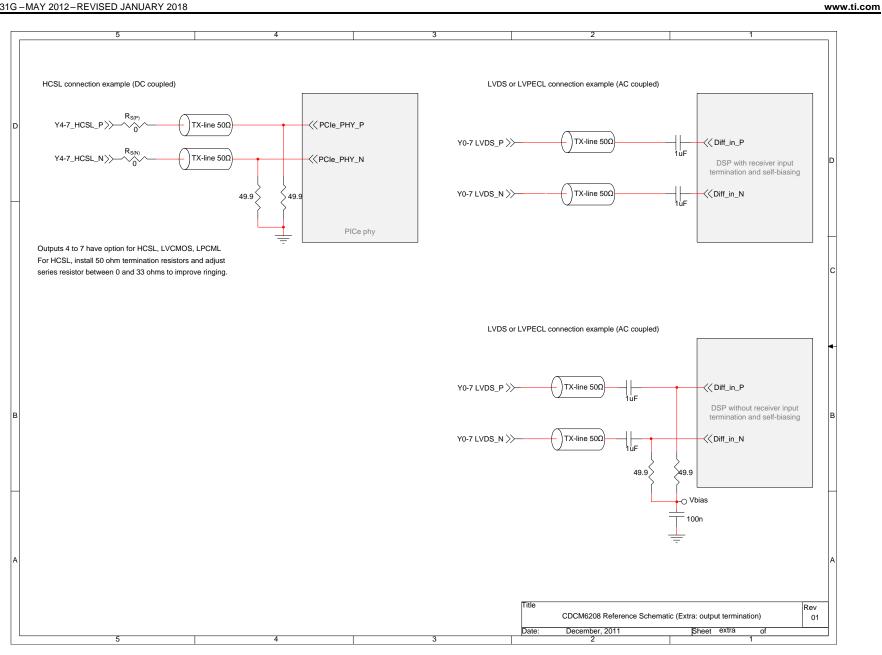

- 4x Integer Down-Divided Differential Clock Outputs Supporting LVPECL-Like, CML, or LVDS-Like Signaling

- 4x Fractional or Integer Divided Differential Clock Outputs Supporting HCSL, LVDS-Like Signaling, or Eight CMOS Outputs

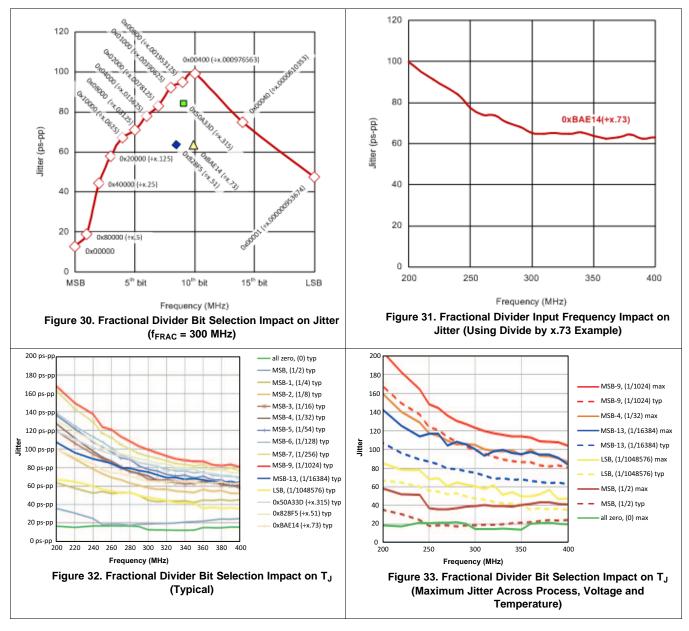

- Fractional Output Divider Achieve 0 ppm to < 1</li> ppm Frequency Error and Eliminates Need for Crystal Oscillators and Other Clock Generators

- Output Frequencies up to 800 MHz

- Two Differential Inputs, XTAL Support, Ability for **Smart Switching**

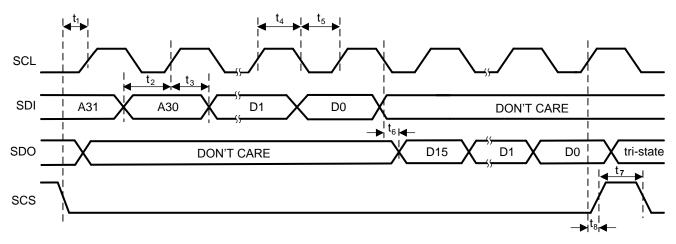

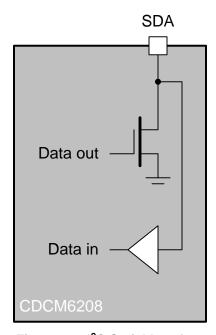

- SPI, I<sup>2</sup>C, and Pin Programmable

- Professional User GUI for Quick Design Turnaround

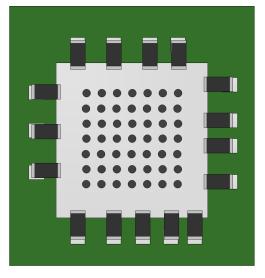

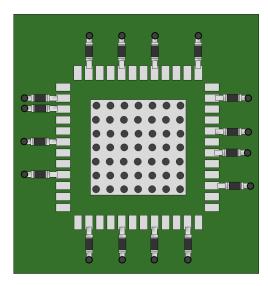

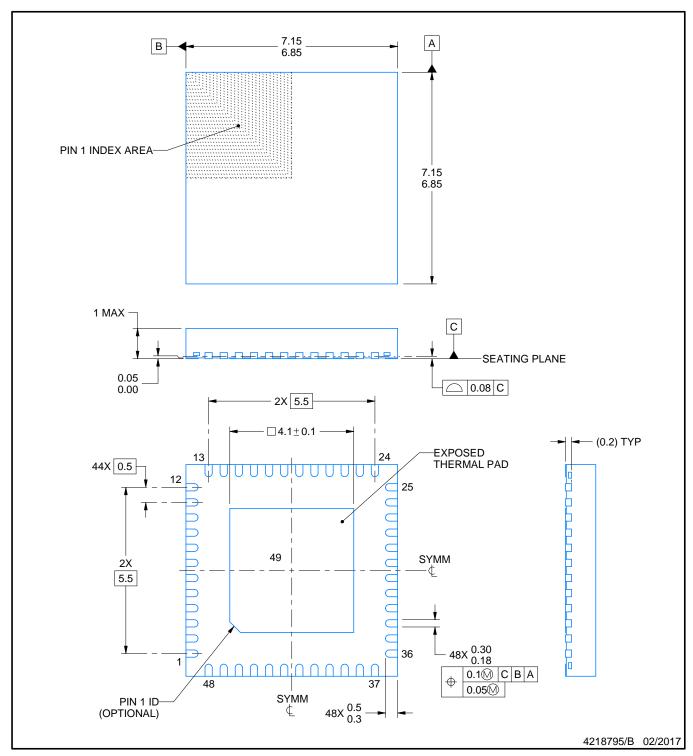

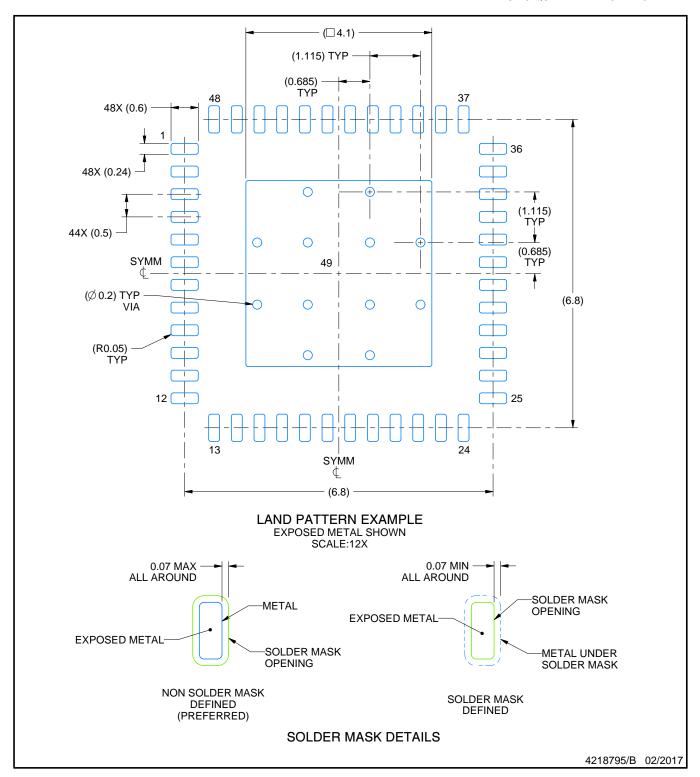

- 7 x 7 mm 48-VQFN package (RGZ)

- -40°C to 85°C Temperature Range

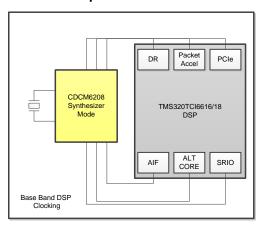

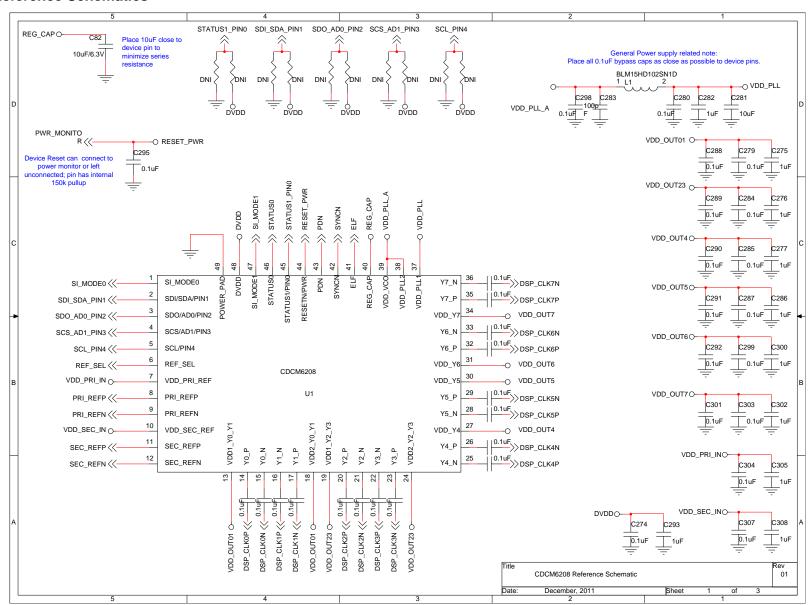

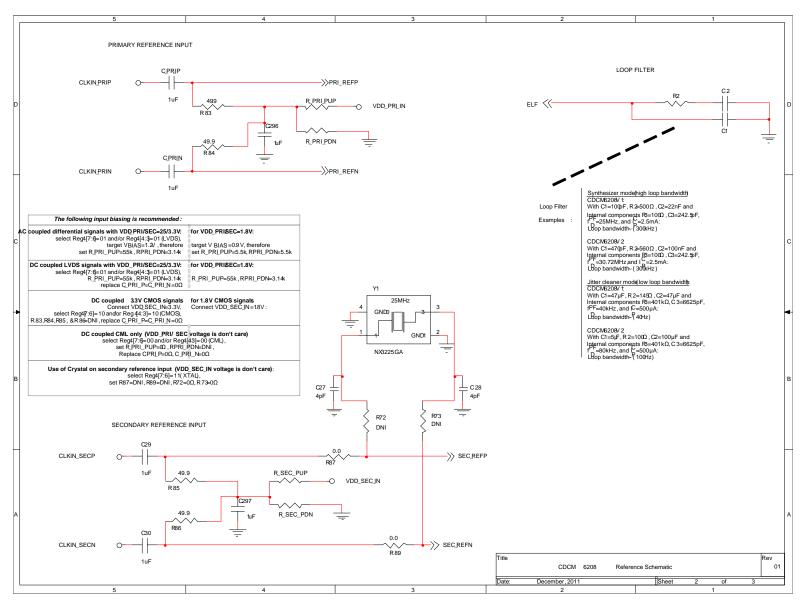

#### Simplified Schematic

## 2 Applications

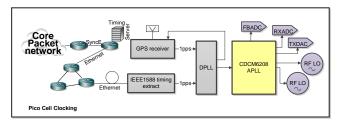

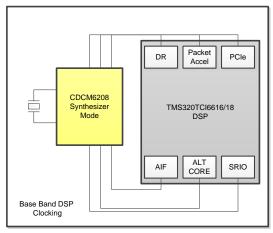

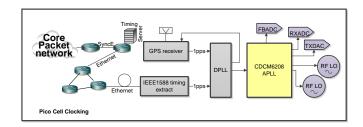

- Base Band Clocking (Wireless Infrastructure)

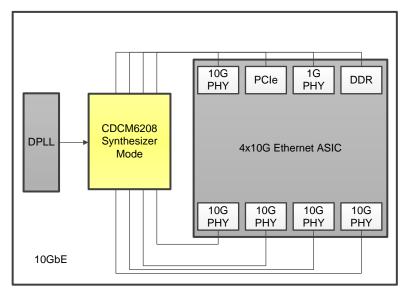

- **Networking and Data Communications**

- Micro and Pico Base Stations

- Keystone C66x Multicore DSP Clocking

- Storage Server, Portable Test Equipment

- Medical Imaging, High End A/V

#### Description 3

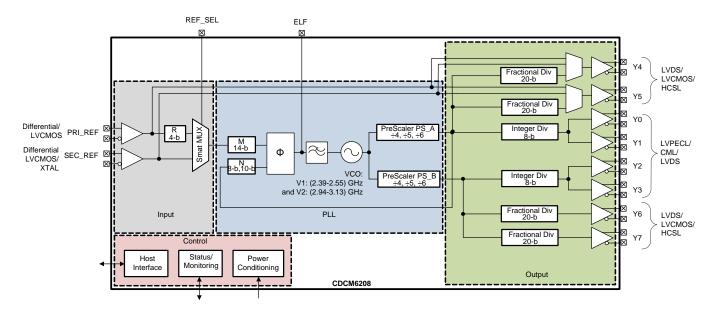

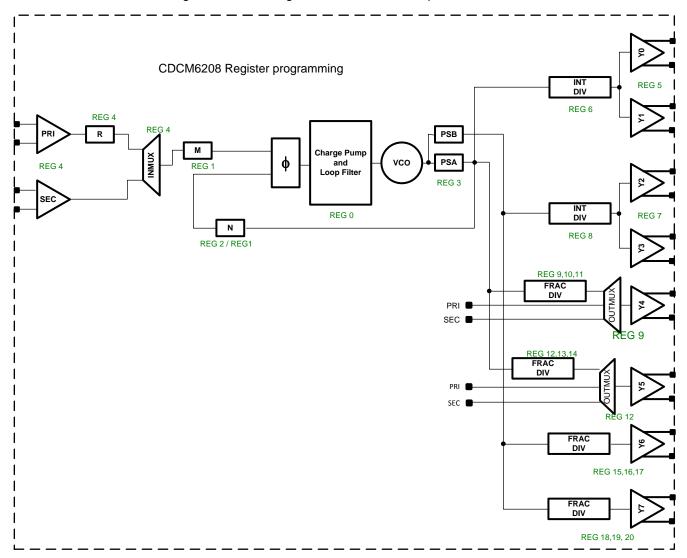

The CDCM6208 is a highly versatile, low jitter low power frequency synthesizer which can generate eight low jitter clock outputs, selectable between LVPECL-like high-swing CML, normal-swing CML, LVDS-like low-power CML, HCSL, or LVCMOS, from one of two inputs that can feature a low frequency crystal or CML, LVPECL, LVDS, or LVCMOS signals for a variety of wireless infrastructure baseband, Small Cells, wireline data communication, computing, low power medical imaging and portable test and measurement applications. The CDCM6208 also features an innovative fractional divider architecture for four of its outputs that can generate any frequency with better than 1ppm frequency accuracy. The CDCM6208 can be easily configured through I2C or SPI programming interface and in the absence of serial interface, pin mode is also available that can set the device in 1 of 32 distinct pre-programmed configurations using control pins.

#### **Device Information**

| DEVICE NAME | PACKAGE   | BODY SIZE         |

|-------------|-----------|-------------------|

| CDCM6208    | VQFN (48) | 7.00 mm × 7.00 mm |

#### Simplified Schematic

## **Table of Contents**

| 1 | Features 1                                                     | 6.21 Worst Case Current Consumption                                       | 1  |

|---|----------------------------------------------------------------|---------------------------------------------------------------------------|----|

| 2 | Applications 1                                                 | 6.22 Timing Requirements, I <sup>2</sup> C Timing                         | 17 |

| 3 | Description 1                                                  | 6.23 Typical Characteristics                                              | 19 |

| 4 | Revision History2                                              | 7 Parameter Measurement Information                                       | 2° |

| 5 | Pin Configuration and Functions 4                              | 8 Detailed Description                                                    | 26 |

| 6 | Specifications6                                                | 8.1 Overview                                                              | 26 |

|   | 6.1 Absolute Maximum Ratings                                   | 8.2 Functional Block Diagram                                              | 20 |

|   | 6.2 ESD Ratings                                                | 8.3 Feature Description                                                   | 26 |

|   | 6.3 Recommended Operating Conditions                           | 8.4 Device Functional Modes                                               | 3  |

|   | 6.4 Thermal Information, Airflow = 0 LFM                       | 8.5 Programming                                                           | 5  |

|   | 6.5 Thermal Information, Airflow = 150 LFM 8                   | 8.6 Register Maps                                                         | 52 |

|   | 6.6 Thermal Information, Airflow = 250 LFM 8                   | 9 Application and Implementation                                          | 6  |

|   | 6.7 Thermal Information, Airflow = 500 LFM 8                   | 9.1 Application Information                                               | 6  |

|   | 6.8 Single-Ended Input Characteristics (SI_MODE[1:0],          | 9.2 Typical Applications                                                  | 6  |

|   | SDI/SDA/PIN1, SCL/PIN4, SDO/ADD0/PIN2,                         | 10 Power Supply Recommendations                                           | 74 |

|   | SCS/ADD1/PIN3, STATUS1/PIN0, RESETN/PWR, PDN, SYNCN, REF_SEL)9 | 10.1 Power Rail Sequencing, Power Supply Ramp F and Mixing Supply Domains |    |

|   | 6.9 Single-Ended Input Characteristics (PRI_REF,               | 10.2 Device Power-Up Timing                                               | 7! |

|   | SEC_REF)                                                       | 10.3 Power Down                                                           | 78 |

|   | 6.10 Differential Input Characteristics (PRI_REF, SEC_REF) 10  | 10.4 Power Supply Ripple Rejection (PSRR) versus Ripple Frequency         |    |

|   | 6.11 Crystal Input Characteristics (SEC_REF) 10                |                                                                           |    |

|   | 6.12 Single-Ended Output Characteristics (STATUS1,             |                                                                           |    |

|   | STATUS0, SDO, SDA) 11                                          | 11.1 Layout Guidelines                                                    |    |

|   | 6.13 PLL Characteristics                                       |                                                                           |    |

|   | 6.14 LVCMOS Output Characteristics                             | 12 Device and Documentation Support                                       |    |

|   | 6.15 LVPECL (High-Swing CML) Output Characteristics            | 12.1 Documentation Support                                                |    |

|   |                                                                | 12.3 Community Resources                                                  |    |

|   | 6.16 CML Output Characteristics                                | 12.4 Trademarks                                                           |    |

|   | 6.18 HCSL Output Characteristics                               | 12.5 Electrostatic Discharge Caution                                      |    |

|   | 6.19 Output Skew and Sync to Output Propagation Delay          | 12.6 Glossary                                                             |    |

|   | Characteristics                                                | 13 Mechanical, Packaging, and Orderable                                   | 0. |

|   | 6.20 Device Individual Block Current Consumption 16            | Information                                                               | 8! |

|   | ·                                                              |                                                                           |    |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| С | Changes from Revision F (April 2014) to Revision G |      |  |

|---|----------------------------------------------------|------|--|

| • | Changed Handling Ratings table to ESD Ratings      | 6    |  |

| • | Added Table 7                                      | 38   |  |

| • | Added Table 10                                     | 43   |  |

| С | Changes from Revision E (March 2013) to Revision F | Page |  |

| Cł | hanges from Revision E (March 2013) to Revision F                                                                                                                                                                   | Page      |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| •  | Changed layout of data sheet to conform to new TI standards. Added the following sections: Handling Ratings, Thermal Information, Typical Characteristics, Programming, Register Maps, Layout and Layout Guidelines | 1         |

| •  | Changed from zero to one                                                                                                                                                                                            | <u>53</u> |

Submit Documentation Feedback

| Cŀ       | nanges from Revision D (March 2013) to Revision E                                                                                                                | Page       |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| •        | Changed the data sheet layout to the new TI standard                                                                                                             | 1          |

| •        | Added the Handling Ratings table                                                                                                                                 | 6          |

| •        | Changed Pullup and Pulldown value From: MIN = 40 To: 35 k $\Omega$ and MAX = 60 To: 65 k $\Omega$                                                                | 9          |

| •        | Changed the from Random Jitter, Maximum in Table 2 From: 10k - 20MHZ To: 12k - 20MHZ and From: 0.5 ps-rms (int div) To: 0.3 ps-rms (int div)                     | 27         |

| •        | Added new Note 1 to Table 2                                                                                                                                      | 27         |

| Ch       | nanges from Revision C (September 2012) to Revision D                                                                                                            | Page       |

| •        | Changed the Description of pin VDD_PRI_REF                                                                                                                       | 4          |

| •        | Changed the Description of pin VDD_SEC_REF                                                                                                                       | 4          |

| •        | Changed Figure 35                                                                                                                                                | 33         |

| •        | Changed Table 6 - Note 2 and row 10 - 0x1C, PinMode 29-V1, fout(Y7) From: 33.33 To: 44.44                                                                        | 36         |

| •        | Changed Table 8 - Note 2 and row 10 - 0x13, PinMode 20-V2, fout(Y7) From: 25 To: 12.5                                                                            | 40         |

| •        | Changed text in the PLL lock detect section From: "1/1000 <sup>th</sup> of the input reference frequency" To: "1/1000 <sup>th</sup> of the PFD update frequency" | 45         |

| •        | Changed text in the PLL lock detect section From: "approximately 1000 input clock cycles" To: "approximately 1000 PFD update clock cycles"                       | 45         |

| •        | Changed Figure 60, From: PDN held Low To: RESETN held low                                                                                                        | <b>7</b> 6 |

| •        | Changed Equation 4                                                                                                                                               | <b>7</b> 8 |

| •        | Changed Table 39, 2:0 DIE_REVISION Description                                                                                                                   |            |

| _        |                                                                                                                                                                  |            |

| Cr       | nanges from Revision A (June 2012) to Revision B                                                                                                                 | Page       |

| •        | Editorial changes made throughout the data sheet                                                                                                                 |            |

| •        | Changed the Description of pin VDD_PRI_REF                                                                                                                       |            |

| •        | Changed the Description of pin VDD_SEC_REF                                                                                                                       |            |

| •        | Added Table Note 1 to the description of pin 44.                                                                                                                 |            |

| •        | Added Note to the Preventing false output frequencies in SPI/I2C mode at startup: section                                                                        |            |

| •        | Changed the NOTE following Table 12                                                                                                                              |            |

| •        | Added Note to the I <sup>2</sup> C SERIAL INTERFACE section                                                                                                      |            |

| •        | Deleted text "All outputs PECL (Y4:0) and LVDS (Y7:4)." from the Conclusion statement                                                                            |            |

| •        | Changed the text in the OUTPUT MUX on Y4 and Y5 section                                                                                                          |            |

| •        | Changed the text in item 1 of the Staggered CLK output powerup for power sequencing of a DSP section                                                             |            |

| •        | Changed the first paragraph in the Power Down section                                                                                                            |            |

| <u>•</u> | Changed the first paragraph in the Power Supply Ripple Rejection (PSRR) versus Ripple Frequency section                                                          | 78         |

| Cr       | nanges from Original (May 2012) to Revision A                                                                                                                    | Page       |

| •        | Changed the device From: Product Preview To: Production                                                                                                          | 1          |

| •        | Section Header From: RESTN, PWR, SYNC To: RESETN, PWR, SYNCN, PDN, REF_SEL, SI_MODE[1:0]                                                                         | <u>9</u>   |

| •        | Changed the R <sub>PULLUP</sub> parametres From: R <sub>PULLUP</sub> - Input Pullup Resistor To: R - Input Pullup and Pulldown Resistor                          |            |

Product Folder Links: CDCM6208

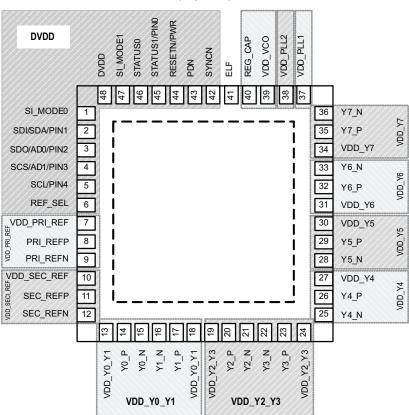

## 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN         |     | I/O TYPE |                             | DESCRIPTION                                                                                                                                                                                                                                                                                    |

|-------------|-----|----------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | NO. | I/O      | TYPE                        | DESCRIPTION                                                                                                                                                                                                                                                                                    |

| PRI_REFP    | 8   | Input    | Universal                   | Primary Reference Input +                                                                                                                                                                                                                                                                      |

| PRI_REFN    | 9   | Input    | Universal                   | Primary Reference Input –                                                                                                                                                                                                                                                                      |

| VDD_PRI_REF | 7   | PWR      | Analog                      | Supply pin for reference inputs to set between 1.8 V, 2.5 V, or 3.3 V, or connected to VDD_SEC_REF.                                                                                                                                                                                            |

| SEC_REFP    | 11  | Input    | Universal                   | Secondary Reference Input +                                                                                                                                                                                                                                                                    |

| SEC_REFN    | 12  | Input    | Universal                   | Secondary Reference Input –                                                                                                                                                                                                                                                                    |

| VDD_SEC_REF | 10  | PWR      | Analog                      | Supply pin for reference inputs to set between 1.8 V, 2.5 V, or 3.3 V, or connected to VDD_PRI_REF <sup>(1)</sup> .                                                                                                                                                                            |

| REF_SEL     | 6   | Input    | LVCMOS<br>with 50-kΩ pullup | Manual Reference Selection MUX for PLL. In SPI or $I^2C$ mode the reference selection is also controlled through Register 4 bit 12.REF_SEL = 0 ( $\leq$ V <sub>IL</sub> ): selects PRI_REFREF_SEL = 1 ( $\geq$ V <sub>IH</sub> ): selects SEC_REF (when Reg 4.12 = 1). See Table 5 for detail. |

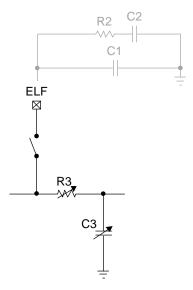

| ELF         | 41  | Output   | Analog                      | External loop filter pin for PLL                                                                                                                                                                                                                                                               |

| Y0_P        | 14  | Output   | Universal                   | Output 0 Positive Pin                                                                                                                                                                                                                                                                          |

| Y0_N        | 15  | Output   | Universal                   | Output 0 Negative Pin                                                                                                                                                                                                                                                                          |

| Y1_P        | 17  | Output   | Universal                   | Output 1 Positive Pin                                                                                                                                                                                                                                                                          |

| Y1_N        | 16  | Output   | Universal                   | Output 1 Negative Pin                                                                                                                                                                                                                                                                          |

(1) If Secondary input buffer is disabled (Register 4 Bit 5 = 0), it is possible to connect VDD\_SEC\_REF to GND.

4 Submit Documentation Feedback

Copyright © 2012–2018, Texas Instruments Incorporated

Product Folder Links: CDCM6208

# Pin Functions (continued)

| PIN                   |        |                  |                                                              |                                                                                                                                                                                                  |  |  |

|-----------------------|--------|------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME NO.              |        | I/O              | TYPE                                                         | DESCRIPTION                                                                                                                                                                                      |  |  |

| VDD_Y0_Y1<br>(2 pins) | 13, 18 | PWR              | Analog                                                       | Supply pin for outputs 0, 1 to set between 1.8 V, 2.5 V, or 3.3 V                                                                                                                                |  |  |

| Y2_P                  | 20     | Output           | Universal                                                    | Output 2 Positive Pin                                                                                                                                                                            |  |  |

| Y2_N                  | 21     | Output           | Universal                                                    | Output 2 Negative Pin                                                                                                                                                                            |  |  |

| Y3_P                  | 23     | Output           | Universal                                                    | Output 3 Positive Pin                                                                                                                                                                            |  |  |

| Y3_N                  | 22     | Output           | Universal                                                    | Output 3 Negative Pin                                                                                                                                                                            |  |  |

| VDD_Y2_Y3<br>(2 pins) | 19, 24 | PWR              | Analog                                                       | Supply pin for outputs 2, 3 to set between 1.8 V, 2.5 V, or 3.3 V                                                                                                                                |  |  |

| Y4_P                  | 26     | Output           | Universal                                                    | Output 4 Positive Pin                                                                                                                                                                            |  |  |

| Y4_N                  | 25     | Output           | Universal                                                    | Output 4 Negative Pin                                                                                                                                                                            |  |  |

| VDD_Y4                | 27     | PWR              | Analog                                                       | Supply pin for output 4 to set between 1.8 V, 2.5 V, or 3.3 V                                                                                                                                    |  |  |

| Y5_P                  | 29     | Output           | Universal                                                    | Output 5 Positive Pin                                                                                                                                                                            |  |  |

| Y5_N                  | 28     | Output           | Universal                                                    | Output 5 Negative Pin                                                                                                                                                                            |  |  |

| VDD_Y5                | 30     | PWR              | Analog                                                       | Supply pin for output 5 to set between 1.8 V, 2.5 V, or 3.3 V                                                                                                                                    |  |  |

| Y6_P                  | 32     | Output           | Universal                                                    | Output 6 Positive Pin                                                                                                                                                                            |  |  |

| Y6_N                  | 33     | Output           | Universal                                                    | Output 6 Negative Pin                                                                                                                                                                            |  |  |

| VDD_Y6                | 31     | PWR              | Analog                                                       | Supply pin for output 6 to set between 1.8 V, 2.5 V, or 3.3 V                                                                                                                                    |  |  |

| Y7_P                  | 35     | Output           | Universal                                                    | Output 7 Positive Pin                                                                                                                                                                            |  |  |

| Y7_N                  | 36     | Output           | Universal                                                    | Output 7 Negative Pin                                                                                                                                                                            |  |  |

| VDD_Y7                | 34     | PWR              | Analog                                                       | Supply pin for output 7 to set between 1.8 V, 2.5 V, or 3.3 V                                                                                                                                    |  |  |

| VDD_VCO               | 39     | PWR              | Analog                                                       | Analog power supply for PLL/VCO; This pin is sensitive to power supply noise; The supply of this pin and the VDD_PLL2 supply pin can be combined as they are both analog and sensitive supplies; |  |  |

| VDD_PLL1              | 37     | PWR              | Analog                                                       | Analog Power Supply Connections                                                                                                                                                                  |  |  |

| VDD_PLL2              | 38     | PWR              | Analog                                                       | Analog Power Supply Connections; This pin is sensitive to power supply noise; The supply of VDD_PLL2 and VDD_VCO can be combined as these pins are both power-sensitive, analog supply pins      |  |  |

| DVDD                  | 48     | PWR              | Analog                                                       | Digital Power Supply Connections; This is also the reference supply voltage for all control inputs and must match the expected input signal swing of control inputs.                             |  |  |

| GND                   | PAD    | PWR              | Analog                                                       | Power Supply Ground and Thermal Pad                                                                                                                                                              |  |  |

| STATUS0               | 46     | Output           | LVCMOS                                                       | Status pin 0 (see Table 12 for details)                                                                                                                                                          |  |  |

| STATUS1/PIN0          | 45     | Output and Input | LVCMOS<br>no pull resistor                                   | STATUS1: Status pin in SPI/I <sup>2</sup> C modes. For details, see Table 10 for pin modes and Table 12 for status mode. PIN0: Control pin 0 in pin mode.                                        |  |  |

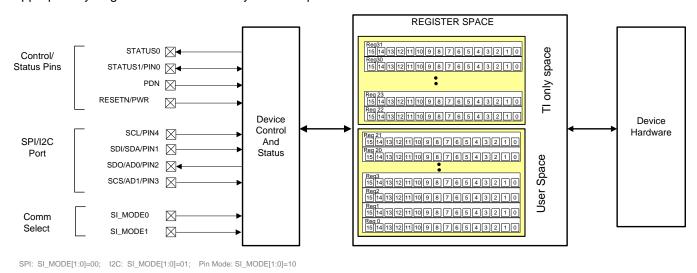

| SI_MODE1              | 47     | Input            | LVCMOS with 50-kΩ pullup                                     | Serial Interface Mode or Pin mode selection. SI_MODE[1:0]=00: SPI mode; SI_MODE[1:0]=01: I <sup>2</sup> C mode; SI_MODE[1:0]=10: Pin Mode (No serial programming); SI_MODE[1:0]=11: RESERVED     |  |  |

| SI_MODE0              | 1      |                  | LVCMOS with 50-k $\Omega$ pulldown                           |                                                                                                                                                                                                  |  |  |

| SDI/SDA/PIN1          | 2      | I/O              | LVCMOS in<br>Open drain out<br>LVCMOS in<br>no pull resistor | SDI: SPI Serial Data Input SDA: I <sup>2</sup> C Serial Data (Read/Write bidirectional), open-drain output; requires a pullup resistor in I <sup>2</sup> C mode; PIN1: Control pin 1 in pin mode |  |  |

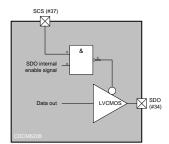

| SDO/AD0/PIN2          | 3      | Output/Input     | LVCMOS out<br>LVCMOS in<br>LVCMOS in<br>no pull resistor     | SDO: SPI Serial Data AD0: I <sup>2</sup> C Address Offset Bit 0 input; PIN2: Control pin 2 in pin mode                                                                                           |  |  |

| SCS/AD1/PIN 3         | 4      | Input            | LVCMOS no pull resistor                                      | SCS: SPI Latch EnableAD1: I <sup>2</sup> C Address Offset Bit 1 input; PIN3: Control pin 3 in pin mode                                                                                           |  |  |

| SCL/PIN4              | 5      | Input            | LVCMOS no pull resistor                                      | SCL: SPI/I <sup>2</sup> C ClockPIN4: Control pin 4 in pin mode                                                                                                                                   |  |  |

Product Folder Links: CDCM6208

#### Pin Functions (continued)

| PIN        |     | 1/0 <b>-</b> 1/0- |                                  | DECODIFICAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|------------|-----|-------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME       | NO. | I/O               | TYPE                             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

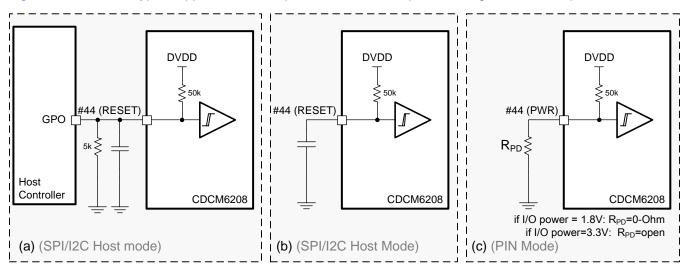

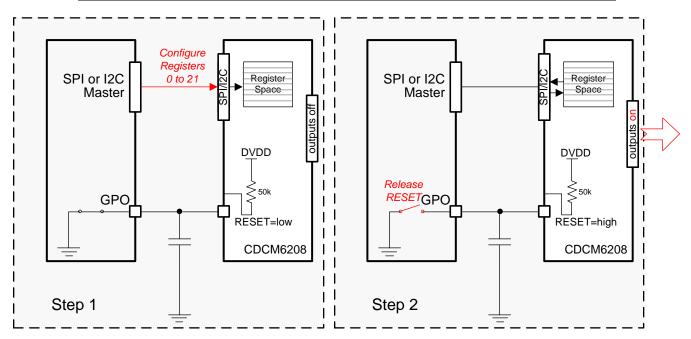

| RESETN/PWR | 44  | Input             | LVCMOS with 50-k $\Omega$ pullup | In SPI/I <sup>2</sup> C programming mode, external RESETN signal (active low). RESETN = V IL: device in reset (registers values are retained) RESETN = V IH: device active. The device can be programmed through SPI while RESETN is held low (this is useful to avoid any false output frequencies at power up). (2) In Pin mode this pin controls device core and I/O supply voltage setting. 0 = 1.8 V, 1 = 2.5/3.3 V for the device core and I/O power supply voltage. In pin mode, it is not possible to mix and match the supplies. All supplies should either be 1.8 V or 2.5/3.3 V. |  |  |

| REG_CAP    | 40  | Output            | Analog                           | Regulator Capacitor; connect a 10- $\mu$ F cap with ESR below 1 $\Omega$ to GND at frequencies above 100 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

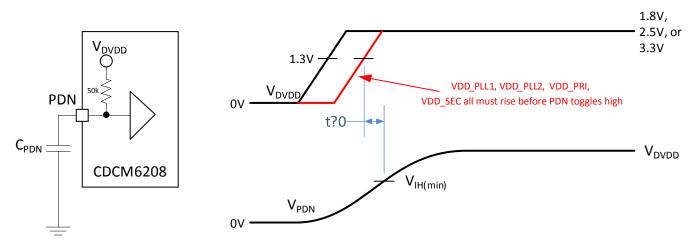

| PDN        | 43  | Input             | LVCMOS<br>with 50-kΩ pullup      | Power Down Active low. When PDN = $V_{IH}$ is normal operation. When PDN = $V_{IL}$ , the device is disabled and current consumption minimized. Exiting power down resets the entire device and defaults all registers. It is recommended to connect a capacitor to GND to hold the device in power-down until the digital and PLL related power supplies are stable. See section on power down in the application section.                                                                                                                                                                 |  |  |

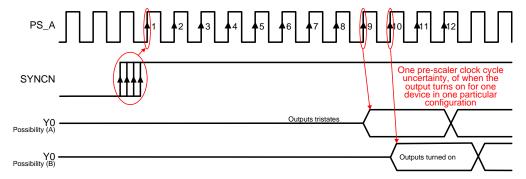

| SYNCN      | 42  | Input             | LVCMOS with 50-kΩ pullup         | Active low. Device outputs are synchronized on a low-to-high transition on the SYNCN pin. SYNCN held low disables all outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

<sup>(2)</sup> Note: the device cannot be programmed in I<sup>2</sup>C while RESETN is held low.

## 6 Specifications

# 6.1 Absolute Maximum Ratings<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                                                       |                                       | MIN  | MAX                                            | UNIT |

|-------------------------------------------------------|---------------------------------------|------|------------------------------------------------|------|

| VDD_PRI, VDD_SEC,<br>VDD_Yx_Yy,<br>VDD_PLL[2:1], DVDD | Supply voltage                        | -0.5 | 4.6                                            | V    |

| V <sub>IN</sub>                                       | Input voltage for CMOS control inputs | -0.5 | 4.6<br>AND<br>V <sub>DVDD</sub> + 0.5          | V    |

| ſ                                                     | Input voltage for PRI/SEC inputs      |      | 4.6<br>AND<br>V <sub>VDDPRI.SEC</sub> +<br>0.5 | V    |

| V <sub>OUT</sub>                                      | Output voltage                        | -0.5 | $V_{YxYy}$ + 0.5                               | V    |

| I <sub>IN</sub>                                       | Input current                         |      | 20                                             | mA   |

| I <sub>OUT</sub>                                      | Output current                        |      | 50                                             | mA   |

| T <sub>J</sub>                                        | Junction temperature                  |      | 125                                            | °C   |

| T <sub>stg</sub>                                      | Storage temperature                   | -65  | 150                                            | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.2 ESD Ratings

|                                 |                           |                                                   | VALUE | UNIT |

|---------------------------------|---------------------------|---------------------------------------------------|-------|------|

| v (1)                           | Electronic Configurations | Human Body Model (HBM) ESD Stress Voltage (2)     | ±2000 | V    |

| V <sub>ESD</sub> <sup>(1)</sup> | Electrostatic discharge   | Charged Device Model (CDM) ESD Stress Voltage (3) | ±500  | V    |

Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges in to the device.

Product Folder Links: CDCM6208

Submit Documentation Feedback

<sup>(2)</sup> Level listed above is the passing level per ANSI/ESDA/JEDEC JS-001. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(3)</sup> Level listed above is the passing level per EIA-JEDEC JESD22-C101. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                       |                                                                                                                  |             | MIN        | NOM         | MAX                   | UNIT |

|-----------------------|------------------------------------------------------------------------------------------------------------------|-------------|------------|-------------|-----------------------|------|

| VDD_Yx_Yy             | Output supply voltage                                                                                            |             | 1.71       | 1.8/2.5/3.3 | 3.465                 | V    |

| VDD_PLL1,<br>VDD_PLL2 | Core analog supply voltage                                                                                       |             | 1.71       | 1.8/2.5/3.3 | 3.465                 | V    |

| DVDD                  | Core digital supply voltage                                                                                      |             | 1.71       | 1.8/2.5/3.3 | 3.465                 | V    |

| VDD_PRI,<br>VDD_SEC   | Reference input supply voltage                                                                                   |             | 1.71       | 1.8/2.5/3.3 | 3.465                 | V    |

| ΔVDD/Δt               | VDD power-up ramp time (0 to 3.3 V) PDN left open, all VDD tight together PDN low-high is delayed <sup>(†)</sup> |             |            |             | 50 < t <sub>PDN</sub> | ms   |

| T <sub>A</sub>        | Ambient Temperature                                                                                              |             | -40        |             | 85                    | °C   |

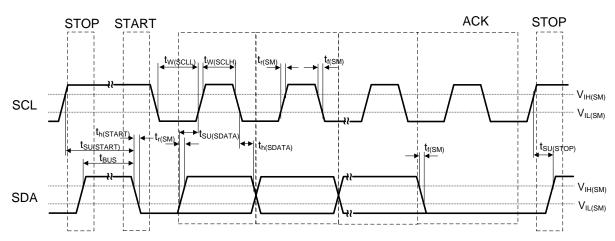

| SDA and SCL in        | $I^2$ C Mode (SI_MODE[1:0] = 01)                                                                                 |             |            |             |                       |      |

| V                     |                                                                                                                  | VDD = 1.8 V | -0.5       |             | 2.45                  | V    |

| $V_{I}$               | Input voltage                                                                                                    | VDD = 3.3 V | -0.5       |             | 3.965                 | V    |

| d <sub>R</sub>        | Data rate                                                                                                        |             |            | 100<br>400  |                       | kbps |

| V <sub>IH</sub>       | High-level input voltage                                                                                         |             | 0.7 × DVDD |             |                       | V    |

| V <sub>IL</sub>       | Low-level input voltage                                                                                          |             |            |             | 0.3 × DVDD            | V    |

| C <sub>BUS_I2C</sub>  | Total capacitive load for each bus lir                                                                           | ne          |            |             | 400                   | pF   |

<sup>(1)</sup> For fast power up ramps under 50 ms and when all supply pins are driven from the same power supply source, PDN can be left floating. For slower power-up ramps or if supply pins are sequenced with uncertain time delays, PDN needs to be held low until DVDD, VDD\_PLLx, and VDD\_PRI/SEC reach at least 1.45-V supply voltage. See application section on mixing power supplies and particularly Figure 59 for details.

# 6.4 Thermal Information, Airflow = $0 LFM^{(1)(2)(3)(4)}$

|                      |                                              | CDCM6208   |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RGZ (VQFN) | UNIT |

|                      |                                              | 48 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 30.27      | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 16.58      | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 6.83       | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.23       | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 6.8        | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 1.06       | °C/W |

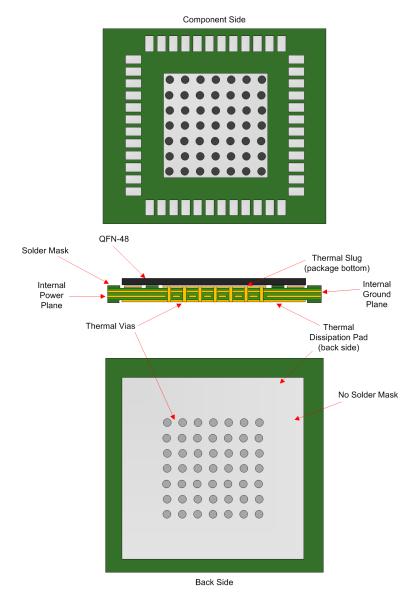

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report.

<sup>(2)</sup> The package thermal resistance is calculated in accordance with JESD 51 and JEDEC2S2P (high-k board).

<sup>(3)</sup> Connected to GND with 36 thermal vias (0.3-mm diameter).

<sup>(4)</sup> θ<sub>JB</sub> (junction to board) is used for the VQFN package, the main heat flow is from the junction to the GND pad of the VQFN.

# 6.5 Thermal Information, Airflow = 150 LFM $^{(1)(2)(3)(4)}$

|                        |                                              | CDCM6208   |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RGZ (VQFN) | UNIT |

|                        |                                              | 48 PINS    |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 21.8       | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | _          | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 6.61       | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.37       | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | _          | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 1.06       | °C/W |

- (1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report.

- (2) The package thermal resistance is calculated in accordance with JESD 51 and JEDEC2S2P (high-k board).

- (3) Connected to GND with 36 thermal vias (0.3-mm diameter).

- (4) θ<sub>JB</sub> (junction to board) is used for the VQFN package, the main heat flow is from the junction to the GND pad of the VQFN.

## 6.6 Thermal Information, Airflow = 250 LFM $^{(1)(2)(3)(4)}$

|                      |                                              | CDCM6208   |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RGZ (VQFN) | UNIT |

|                      |                                              | 48 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 19.5       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | _          | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 6.6        | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.45       | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | _          | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 1.06       | °C/W |

- (1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report.

- (2) The package thermal resistance is calculated in accordance with JESD 51 and JEDEC2S2P (high-k board).

- (3) Connected to GND with 36 thermal vias (0.3-mm diameter).

- (4) θ<sub>JB</sub> (junction to board) is used for the VQFN package, the main heat flow is from the junction to the GND pad of the VQFN.

## 6.7 Thermal Information, Airflow = 500 LFM $^{(1)(2)(3)(4)}$

|                      |                                              | CDCM6208   |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RGZ (VQFN) | UNIT |

|                      |                                              | 48 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 17.7       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | _          | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 6.58       | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.58       | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | _          | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 1.05       | °C/W |

Product Folder Links: CDCM6208

- (1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report.

- 2) The package thermal resistance is calculated in accordance with JESD 51 and JEDEC2S2P (high-k board).

- (3) Connected to GND with 36 thermal vias (0.3-mm diameter).

- (4) θ<sub>JB</sub> (junction to board) is used for the VQFN package, the main heat flow is from the junction to the GND pad of the VQFN.

Submit Documentation Feedback

# 6.8 Single-Ended Input Characteristics (SI\_MODE[1:0], SDI/SDA/PIN1, SCL/PIN4, SDO/ADD0/PIN2, SCS/ADD1/PIN3, STATUS1/PIN0, RESETN/PWR, PDN, SYNCN, REF\_SEL)

DVDD = 1.71 V to 1.89 V, 2.375 V to 2.625 V, 3.135 V to 3.465 V,  $T_A = -40^{\circ}$ C to 85°C

|                      | PARAMETER                                                   | TEST CONDITIONS                                                        | MIN                       | TYP  | MAX           | UNIT      |

|----------------------|-------------------------------------------------------------|------------------------------------------------------------------------|---------------------------|------|---------------|-----------|

| V <sub>IH</sub>      | Input high voltage                                          |                                                                        | 0.8 ×<br>DVDD             |      |               | V         |

| $V_{IL}$             | Input low voltage                                           |                                                                        |                           |      | 0.2 ×<br>DVDD | V         |

| I <sub>IH</sub>      | Input high current                                          | DVDD = 3.465V, V <sub>IH</sub> = 3.465 V<br>(pullup resistor excluded) |                           |      | 30            | μA        |

| I <sub>IL</sub>      | Input low current                                           | DVDD = 3.465V, V <sub>IL</sub> = 0 V                                   |                           |      | -30           | μA        |

| ΔV/ΔΤ                | PDN, RESETN, SYNCN, REF_SEL input edge rate                 | 20% – 80%                                                              | 0.75                      |      |               | V/ns      |

| minPulse             | PDN, RESETN, SYNCN low pulse to trigger proper device reset |                                                                        | 10                        |      |               | ns        |

| C IN                 | Input capacitance                                           |                                                                        |                           | 2.25 |               | pF        |

| RESETN,              | PWR, SYNCN, PDN, REF_SEL, SI_MC                             | DDE[1:0]                                                               |                           |      |               |           |

| R                    | Input pullup and pulldown resistor                          |                                                                        | 35                        | 50   | 65            | $k\Omega$ |

| SDA and S            | SCL in I $^2$ C Mode (SI_MODE[1:0]=01)                      | 1                                                                      |                           |      |               |           |

|                      |                                                             | DVDD = 1.8 V                                                           | 0.1 V <sub>DVDD</sub>     |      |               | V         |

| V <sub>HYS_I2C</sub> | Input hysteresis                                            | DVDD = 2.5/3.3 V                                                       | 0.05<br>V <sub>DVDD</sub> |      |               | V         |

| I <sub>H</sub>       | High-level input current                                    | $V_I = DVDD$                                                           | -5                        |      | 5             | μΑ        |

| V <sub>OL</sub>      | Output low voltage                                          | I <sub>OL</sub> = 3 mA                                                 |                           |      | 0.2 ×<br>DVDD | V         |

| C <sub>IN</sub>      | Input capacitance pin                                       |                                                                        |                           |      | 5             | pF        |

## 6.9 Single-Ended Input Characteristics (PRI\_REF, SEC\_REF)

VDD\_PRI, VDD\_SEC = 1.71 V to 1.89 V, 2.375 V to 2.625 V, 3.135 V to 3.465 V,  $T_A = -40^{\circ}$ C to 85°C

|                   | PARAMETER                  | TEST CONDITIONS                                      | MIN                          | TYP  | MAX                          | UNIT |

|-------------------|----------------------------|------------------------------------------------------|------------------------------|------|------------------------------|------|

| 4                 | Reference and bypass input | VDD_PRI/SEC = 1.8 V                                  | 0.008                        |      | 200                          | MHz  |

| f <sub>IN</sub>   | frequency                  | VDD_PRI/SEC = 3.3 V                                  | 0.008                        |      | 250                          | MHz  |

| $V_{IH}$          | Input high voltage         |                                                      | 0.8 x<br>VDD_PRI/<br>VDD_SEC |      |                              | V    |

| V <sub>IL</sub>   | Input low voltage          |                                                      |                              |      | 0.2 x<br>/DD_PRI/<br>/DD_SEC | V    |

| V <sub>HYST</sub> | Input hysteresis           |                                                      | 20                           | 65   | 150                          | mV   |

| I <sub>IH</sub>   | Input high current         | VDD_PRI/VDD_SEC = 3.465 V, V <sub>IH</sub> = 3.465 V |                              |      | 30                           | μΑ   |

| I <sub>IL</sub>   | Input low current          | VDD_PRI/VDD_SEC = 3.465 V, V <sub>IL</sub><br>= 0 V  |                              |      | -30                          | μΑ   |

| ΔV/ΔΤ             | Reference input edge rate  | 20% – 80%                                            | 0.75                         |      |                              | V/ns |

| IDC               | Deference input duty avale | f <sub>PRI</sub> ≤ 200 MHz                           | 40%                          |      | 60%                          |      |

| IDC <sub>SE</sub> | Reference input duty cycle | 200 ≤ f <sub>PRI</sub> ≤ 250 MHz                     | 43%                          |      | 60%                          |      |

| C <sub>IN</sub>   | Input capacitance          |                                                      |                              | 2.25 |                              | pF   |

Product Folder Links: CDCM6208

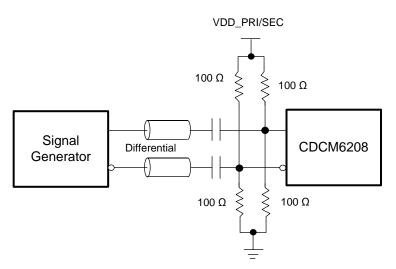

## Differential Input Characteristics (PRI\_REF, SEC\_REF)

VDD\_PRI, VDD\_SEC = 1.71 V to 1.89 V, 2.375 V to 2.625 V, 3.135 V to 3.465 V,  $T_A = -40^{\circ}$ C to 85°C

|                     | PARAMETER                            | TEST CONDITIONS                                                                    | MIN                         | TYP | MAX                         | UNIT      |

|---------------------|--------------------------------------|------------------------------------------------------------------------------------|-----------------------------|-----|-----------------------------|-----------|

| f <sub>IN</sub>     | Reference and bypass input frequency |                                                                                    | 0.008                       |     | 250                         | MHz       |

| \/                  | Differential input voltage swing,    | VDD_PRI/SEC = 2.5/3.3 V                                                            | 0.2                         |     | 1.6                         | $V_{PP}$  |

| VI                  | peak-to-peak                         | VDD_PRI/SEC = 1.8 V                                                                | 0.2                         |     | 1                           | $V_{PP}$  |

| V <sub>ICM</sub>    | Input common-mode voltage            | CML input signaling, R4[7:6] = 00                                                  | VDD_PRI/<br>VDD_SEC<br>-0.4 |     | /DD_PRI/<br>/DD_SEC<br>-0.1 | V         |

| V <sub>ICM</sub>    | Input common-mode voltage            | LVDS, VDD_PRI/SEC<br>= 1.8/2.5/3.3 V,<br>R4[7:6] = 01, R4.1 = d.c.,<br>R4.0 = d.c. | 0.8                         | 1.2 | 1.5                         | V         |

| V                   | Innut hyptoropia                     | LVDS (Q4[7:6,4:3] = 01)                                                            | 15                          |     | 65                          | $mV_{pp}$ |

| V <sub>HYST</sub>   | Input hysteresis                     | CML $(Q4[7:6,4:3] = 00)$                                                           | 20                          |     | 85                          | $mV_{pp}$ |

| I <sub>IH</sub>     | Input high current                   | VDD_PRI/SEC = 3.465 V,<br>V <sub>IH</sub> = 3.465 V                                |                             |     | 30                          | μΑ        |

| I <sub>IL</sub>     | Input low current                    | VDD_PRI/SEC = 3.465V, V <sub>IL</sub> = 0 V                                        |                             |     | -30                         | μΑ        |

| ΔV/ΔΤ               | Reference input edge rate            | 20% – 80%                                                                          | 0.75                        |     |                             | V/ns      |

| IDC <sub>DIFF</sub> | Reference input duty cycle           |                                                                                    | 30%                         |     | 70%                         |           |

| C <sub>IN</sub>     | Input capacitance                    |                                                                                    |                             | 2.7 |                             | pF        |

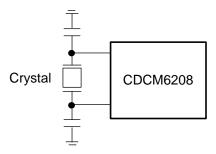

#### 6.11 **Crystal Input Characteristics (SEC\_REF)**

VDD\_SEC = 1.71 to 1.89 V, 2.375 V to 2.625 V, 3.135 V to 3.465 V,  $T_A = -40^{\circ}$ C to 85°C

| PARAMETER                          | TEST CONDITIONS         | MIN   | TYP       | MAX                | UNIT |

|------------------------------------|-------------------------|-------|-----------|--------------------|------|

| Mode of oscillation                |                         | Fur   | ndamental |                    |      |

| F                                  | See note (1)            | 10    |           | 30.72              | MHz  |

| Frequency                          | See note (2)            | 30.73 |           | 50                 | MHz  |

|                                    | 10 MHz                  |       |           | 150 <sup>(3)</sup> |      |

| Equivalent Series Resistance (ESR) | 25 MHz                  |       |           | 70 <sup>(4)</sup>  | Ω    |

|                                    | 50 MHz                  |       |           | 30 <sup>(5)</sup>  |      |

|                                    | 1.8-V / 3.3-V SEC_REFP  | 3.5   | 4.5       | 5.5                |      |

| On-chip load capacitance           | 1.8-V SEC_REFN          | 5.5   | 7.25      | 8.5                | pF   |

|                                    | 3.3-V SEC_REFN          | 6.5   | 7.34      | 8.5                |      |

| Drive level                        | See note <sup>(6)</sup> |       |           | 200                | μW   |

- (1) Verified with crystals specified for a load capacitance of  $C_L = 8$  pF, the PCB related capacitive load was estimated to be 2.3 pF, and completed with a load capacitors of 4 pF on each crystal pin connected to GND. XTALs tested: NX3225GA 10MHz EXS00A-CG02813 CRG, NX3225GA 19.44MHz EXS00A-CG02810 CRG, NX3225GA 25MHz EXS00A-CG02811 CRG, and NX3225GA 30.72MHz EXS00A-CG02812 CRG.

- For 30.73 MHz to 50 MHz, TI recommends to verify sufficient negative resistance and initial frequency accuracy with the crystal vendor. The 50-MHz use case was verified with a NX3225GA 50MHz EXS00A-CG02814 CRG. To meet a minimum frequency error, the best choice of the XTAL was one with  $C_L$  = 7 pF instead of  $C_L$  = 8 pF. With NX3225GA\_10M the measured remaining negative resistance on the EVM is 6430  $\Omega$  (43 x margin)

Product Folder Links: CDCM6208

- With NX3225GA\_25M the measured remaining negative resistance on the EVM is 1740  $\Omega$  (25 x margin)

- With NX3225GA\_50M the measured remaining negative resistance on the EVM is 350  $\Omega$  (11 x margin)

- Maximum drive level measured was 145  $\mu$ W; XTAL should at least tolerate 200  $\mu$ W

Submit Documentation Feedback

## 6.12 Single-Ended Output Characteristics (STATUS1, STATUS0, SDO, SDA)

VDD\_Yx\_Yy, VDD\_PRI, VDD\_SEC, VDD\_PLLx, DVDD, VDD\_VCO = 1.71 V to 1.89 V, 2.375 V to 2.625 V, 3.135 V to 3.465 V;  $T_A = -40^{\circ}$ C to 85°C (Output load capacitance 10 pF unless otherwise noted)

|                   | PARAMETER                            | TEST CONDITIONS                                                                                                                    | MIN           | TYP  | MAX           | UNIT               |

|-------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------|------|---------------|--------------------|

| V <sub>OH</sub>   | Output high voltage                  | Status 1, Status 0, and SDO only;<br>SDA is open drain and relies on<br>external pullup for high output; I <sub>OH</sub> =<br>1 mA | 0.8 ×<br>DVDD |      |               | V                  |

| V <sub>OL</sub>   | Output low voltage                   | I <sub>OL</sub> = 1 mA                                                                                                             |               |      | 0.2 ×<br>DVDD | V                  |

| V <sub>slew</sub> | Output slew rate                     | 30% – 70%                                                                                                                          | 0.5           |      |               | V/ns               |

| I <sub>OZH</sub>  | 3-state output high current          | DVDD = 3.465 V, V <sub>IH</sub> = 3.465 V                                                                                          |               |      | 5             | μΑ                 |

| I <sub>OZL</sub>  | 3-state output low current           | $DVDD = 3.465 \text{ V}, \text{ V}_{IL} = 0 \text{ V}$                                                                             |               |      | -5            | μΑ                 |

| t <sub>LOS</sub>  | Status loss of signal detection time | LOS_REFfvco                                                                                                                        |               | 1    | 2             | 1/f <sub>PFD</sub> |

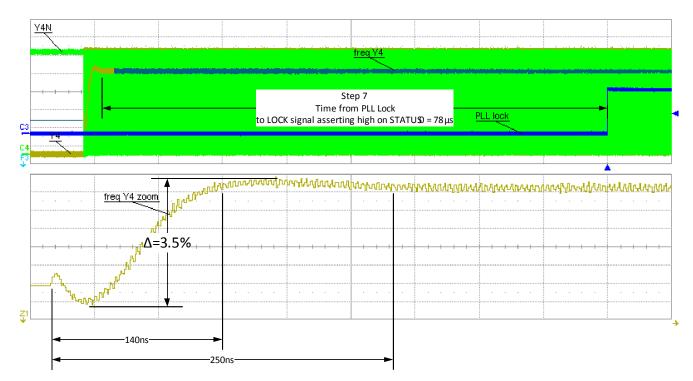

|                   | Status PLL lock detection time       | Detect lock                                                                                                                        |               | 2304 |               | 1 /f               |

| t <sub>LOCK</sub> | Status FLL lock detection time       | Detect unlock                                                                                                                      |               | 512  |               | 1/f <sub>PFD</sub> |

## 6.13 PLL Characteristics

VDD\_PLLx, VDD\_VCO = 1.71 V to 1.89 V, 2.375 V to 2.625 V, 3.135 V to 3.465 V,  $T_A = -40^{\circ}\text{C}$  to 85°C

|                      | PARAMETER                               | TEST CONDITIONS                                                                                                                                                                | MIN   | TYP   | MAX  | UNIT    |

|----------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|------|---------|

|                      | VCO fraguescu range                     | V1                                                                                                                                                                             | 2.39  |       | 2.55 | GHz     |

| f <sub>VCO</sub>     | VCO frequency range                     | V2                                                                                                                                                                             | 2.94  |       | 3.13 | GHZ     |

|                      |                                         | V1, 2.39 GHz                                                                                                                                                                   |       | 178   |      |         |

|                      |                                         | V1, 2.50 GHz                                                                                                                                                                   |       | 204   |      |         |

| V                    | VCO goin                                | V1, 2.55 GHz                                                                                                                                                                   |       | 213   |      | MHz/V   |

| K <sub>VCO</sub>     | VCO gain                                | V2, 2.94 GHz                                                                                                                                                                   |       | 236   |      | IVIПZ/V |

|                      |                                         | V2, 3.00 GHz                                                                                                                                                                   |       | 250   |      |         |

|                      |                                         | V2, 3.13 GHz                                                                                                                                                                   |       | 283   |      |         |

| f <sub>PFD</sub>     | PFD input frequency                     |                                                                                                                                                                                | 0.008 |       | 100  | MHz     |

| I <sub>CP-L</sub>    | High impedance mode charge pump leakage |                                                                                                                                                                                |       | ±700  |      | nA      |

| f <sub>FOM</sub>     | Estimated PLL figure of merit (FOM)     | Measured in-band phase noise at<br>the VCO output minus 20log(N-<br>divider) at the flat region                                                                                |       | -224  |      | dBc/Hz  |

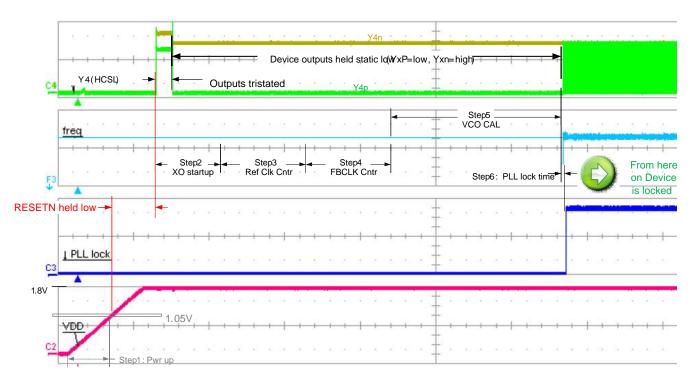

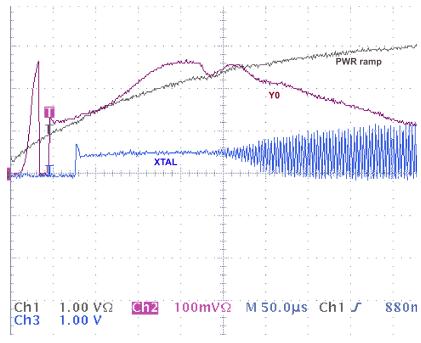

| t <sub>STARTUP</sub> | Start-up time (see Figure 60)           | Power supply ramp time of 1ms from 0 V to 1.7 V, final frequency accuracy of 10 ppm, f <sub>PFD</sub> = 25 MHz, CDCM6208 pin mode use case #2, C <sub>PDN_to_GND</sub> = 22 nF |       |       |      |         |

|                      |                                         |                                                                                                                                                                                | 12.8  |       | ms   |         |

|                      |                                         | with NDK 25 MHz crystal                                                                                                                                                        |       | 12.85 |      | ms      |

Product Folder Links: CDCM6208

Copyright © 2012–2018, Texas Instruments Incorporated

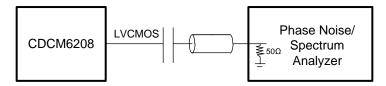

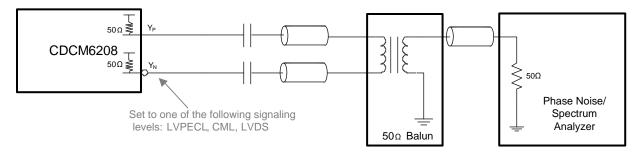

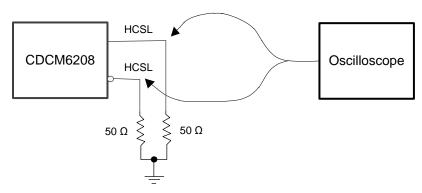

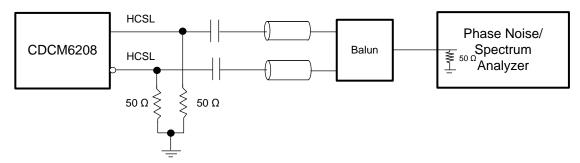

# 6.14 LVCMOS Output Characteristics

$VDD_{Yx_{Yy}} = 1.71 \text{ V to } 1.89 \text{ V}, 2.375 \text{ V to } 2.625 \text{ V}, 3.135 \text{ V to } 3.465 \text{ V}, T_A = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C}$

|                          | PARAMETER                                | TEST COND                                                | ITIONS                                  | MIN                    | TYP    | MAX                    | UNIT     |

|--------------------------|------------------------------------------|----------------------------------------------------------|-----------------------------------------|------------------------|--------|------------------------|----------|

|                          |                                          | Fract out divVDD_Yx_Yy = 2.                              | 5/3.3 V                                 | 0.78                   |        | 250                    |          |

| f <sub>OUT-F</sub>       | Output frequency                         | Integer out divVDD_Yx_Yy =                               | 2.5/3.3 V                               | 1.55                   |        | 250                    | MHz      |

|                          |                                          | Int or frac out divVDD_Yx_Yy                             | = 1.8 V                                 | 0.78/1.5               |        | 200                    |          |

| f <sub>ACC-F</sub>       | Output frequency error (1)               | Fractional output divider                                |                                         | -1                     |        | 1                      | ppm      |

| V <sub>OH</sub>          | Output high voltage (normal mode)        | $VDD\_Yx = min \text{ to max},$ $I_{OH} = -1 \text{ mA}$ |                                         | 0.8 x<br>VDD_Y<br>x_Yy |        |                        | V        |

| V <sub>OL</sub>          | Output low voltage (normal mode)         | VDD_Yx = min to max,<br>$I_{OL} = 100 \mu A$             |                                         |                        |        | 0.2 ×<br>VDD_Y<br>x_Yy | ٧        |

| V <sub>OH</sub>          | Output high voltage (slow mode)          | VDD_Yx = min to max,<br>$I_{OH}$ = -100 $\mu$ A          |                                         | 0.7 x<br>VDD_Y<br>x_Yy |        |                        | <b>V</b> |

| V <sub>OL</sub>          | Output low voltage (slow mode)           | VDD_Yx = min to max,<br>I <sub>OL</sub> = 100 μA         |                                         |                        |        | 0.3 ×<br>VDD_Y<br>x_Yy | V        |

|                          |                                          | $V_{OUT} = VDD_Yx_Yy/2$                                  |                                         |                        |        |                        |          |

| $I_{OH}$                 | Output high current                      | Normal mode                                              |                                         | -50                    |        | -8                     | mA       |

|                          |                                          | Slow mode                                                |                                         | -45                    |        | <b>–</b> 5             | mA       |

|                          |                                          | $V_{OUT} = VDD_Yx_Yy/2$                                  |                                         |                        |        |                        |          |

| $I_{OL}$                 | Output low current                       | Normal mode                                              |                                         | 10                     |        | 55                     | mA       |

|                          |                                          | Slow mode                                                |                                         | 5                      |        | 40                     | mA       |

| <b>t</b>                 | Output rise/fall slew rate (normal mode) | 20% to 80%, VDD_Yx_Yy = 2                                | $2.5/3.3 \text{ V}, C_L = 5 \text{ pF}$ |                        | 5.37   |                        | V/ns     |

| <sup>t</sup> SLEW-RATE-N | Output rise/fall slew rate (normal mode) | 20% to 80%, VDD_Yx_Yy = 1                                | 1.8 V, $C_L = 5 pF$                     |                        | 2.62   |                        | V/ns     |

|                          | Output rise/fall slew rate (slow mode)   | 20% to 80%, VDD_Yx_Yy = 2                                | $2.5/3.3 \text{ V}, C_L = 5 \text{ pF}$ |                        | 4.17   |                        | V/ns     |

| <sup>T</sup> SLEW-RATE-S | Output rise/fall slew rate (slow mode)   | 20% to 80%, VDD_Yx_Yy = 1                                | 1.8 V, C <sub>L</sub> = 5 pF            |                        | 1.46   |                        | V/ns     |

| PN-floor                 | Phase noise floor                        | f <sub>OUT</sub> = 122.88 MHz                            |                                         |                        | -159.5 | 154                    | dBc/Hz   |

| ODC                      | Output duty cycle                        | Not in bypass mode                                       |                                         | 45%                    |        | 55%                    |          |

| D                        | Output impedance                         | V <sub>OUT</sub> = VDD_Yx/2                              | Normal mode                             | 30                     | 50     | 90                     | Ω        |

| R <sub>OUT</sub>         | Output impedance                         | ν OUT = ν DD_1 χ/2                                       | Slow mode                               | 45                     | 74     | 130                    | 22       |

<sup>(1)</sup> The User's GUI calculates exact frequency error. It is a fixed, static offset. If the desired output target frequency is with the exact reach of a multiple 1 over 2<sup>20</sup>, the actual output frequency error is 0. Note: In LVCMOS Mode, positive and negative outputs are in phase.

Product Folder Links: CDCM6208

Submit Documentation Feedback

Copyright © 2012–2018, Texas Instruments Incorporated

12

## 6.15 LVPECL (High-Swing CML) Output Characteristics

$VDD\_Yx\_Yy = 1.71 \ V \ to \ 3.465 \ V, \ VDD\_PRI, \ VDD\_SEC, \ VDD\_PLLx, \ DVDD, \ VDD\_VCO = 1.71 \ V \ to \ 1.89 \ V, \ 2.375 \ V \ to \ 2.625 \ V, \ 3.135 \ V \ to \ 3.465 \ V, \ T_A = -40 ^{\circ}C \ to \ 85 ^{\circ}C$

|                                | PARAMETER                                    | TEST CONDI                                                 | TIONS                                                                | MIN   | TYP                            | MAX    | UNIT   |

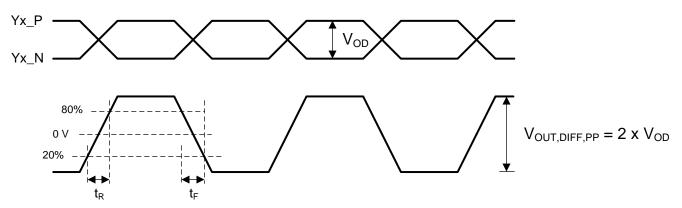

|--------------------------------|----------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------|-------|--------------------------------|--------|--------|