# **ALED7709**

Datasheet

# Automotive LED driver 4-channel 200 mA with a DC-DC controller

# **Features**

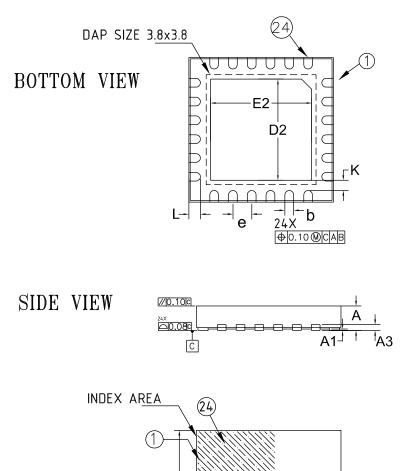

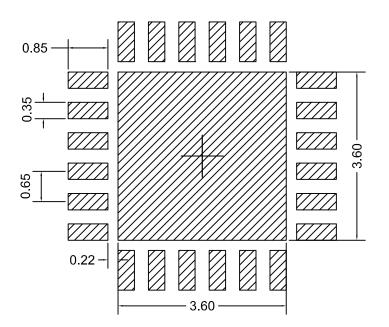

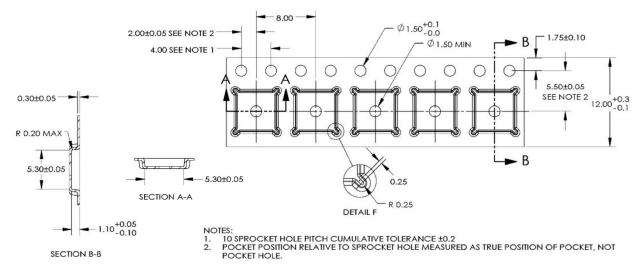

QFN24L (5x5 mm)

| Product status link |  |

|---------------------|--|

| AI ED7709           |  |

AEC-Q100 Grade1 gualified

- Operating temperature range -40 °C < T<sub>J</sub> < 150 °C</li>

- 4.5 V to 42 V operating input voltage range

- Up to 60 V tolerant for load dump @ 24 V battery

- Supports battery cranking events down to 4 V supply

- Simultaneous or exclusive control by PWMI and I<sup>2</sup>C interface

- Switching controller section

- Low shutdown current:  $I_{SHDN}$  < 15  $\mu$ A

- Fixed frequency peak current-mode controller

- Cycle-by-cycle power switch OCP

- Adjustable (250 kHz to 2.2 MHz) switching frequency with optional spread spectrum

- Synchronized boost and SEPIC topologies support

- Line switch control for standby power saving and inrush current protection

- Input overvoltage and output short-circuit protection

- LED strings control section

- 4 x 40 V rated constant current outputs

- Adjustable up to 200 mA per channel

- ±2 % typ. output current accuracy

- Mixed PWM and Analog dimming

- 100 Hz to 12.8 kHz dimming frequency

- Dimming ratio 10000:1 at 100 Hz

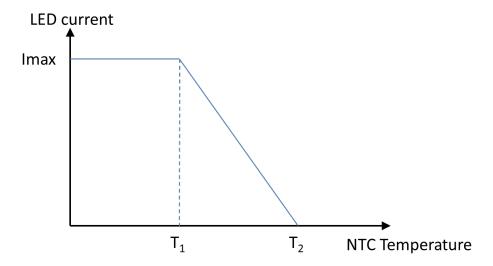

- LED temperature sensor (NTC) management

- Selectable channels phase-shifting and adjustable Rise/Fall time for reducing EMI

- Open channel, LED short-circuit detection

- Two versions available: ALED7709A and ALED7709B

# **Applications**

- Automotive lighting and backlighting for:

- Cluster / Infotainment display

- Head-Up Display (HUD)

- Instrument lighting system

- Ambient light

# Description

ALED7709x are automotive-grade (AEC-Q100 Grade1 qualified) LED drivers combining a boost/SEPIC controller and four low-side constant-current sinkers, designed to drive strings of high brightness LEDs. The switching converter section provides the supply rail for the LED strings, whose value is constantly optimized for maximum efficiency. The boost/SEPIC controller supports the external synchronization and spread spectrum. ALED7709x can work simultaneously or exclusively in standalone mode (SAM), controlled only by PWMI signal, and in bus driven mode (BDM) through an I<sup>2</sup>C serial interface. The brightness of the four LED strings can be controlled either in global or local mode. In global mode, the ALED7709x supports a mixed PWM and analog dimming to improve the brightness range capability. Only the BDM provides full access to ALED7709x advanced features. PWM dimming frequency can be programmed changing the setting of the internal 16-bit counter, while an internal oscillator avoids the use of an external clock source.

The ALED7709A is dedicated to BDM while ALED7709B is more suitable for SAM. ALED7709x implement basic protections (overvoltage, overcurrent, and thermal shutdown) as well as "Open and Short" LED fault detection, with optional channel auto-disconnect in case of fault.

The devices support an optional P-channel MOSFET in series to the input. It protects the system, LED strings and channels in case of some faulty conditions, output short-to-ground or excessive input voltage transients and it also reduces the power consumption when in standby.

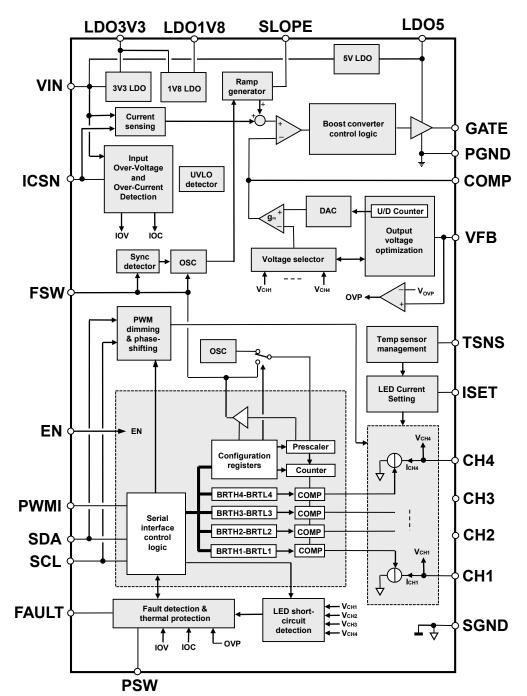

# 1 Diagram

57

Figure 1. Block diagram

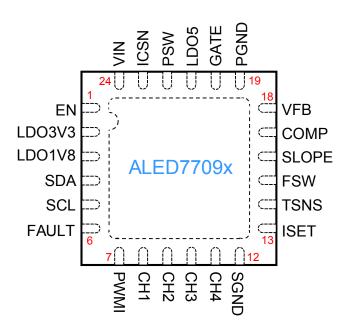

# 2 Pin configuration

The ALED7709x are in QFN24L (5x5 mm), 0.65 mm pitch small package with exposed pad.

### Figure 2. Pin connection (top view)

### Table 1. Pin description

| Pin # | Symbol | Function                                                                                                                                                                                                              |

|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | EN     | ENABLE the device and the internal DC-DC converter by using two different thresholds. An internal circuit clamps maximum voltage on the pin, allowing the use of high value pull-up resistor connected to input rail. |

| 2     | LDO3V3 | 3.3 V linear regulator output. Connect a 1 $\mu F$ bypass capacitor between this pin and SGND as close as possible to the device.                                                                                     |

| 3     | LDO1V8 | 1.8 V linear regulator output. Connect a 1 $\mu F$ bypass capacitor between this pin and SGND as close as possible to the device.                                                                                     |

| 4     | SDA    | DATA pin of the I <sup>2</sup> C interface                                                                                                                                                                            |

| 5     | SCL    | CLOCK pin of the I <sup>2</sup> C interface                                                                                                                                                                           |

| 6     | FAULT  | This pin is an open-drain and must be connected to SGND through a resistor. It is tied high to report a fault condition.                                                                                              |

| 7     | PWMI   | PWM/brightness dimming control input.                                                                                                                                                                                 |

| 8     | CH1    | Output pin to be connected to the negative terminal of the LED string.                                                                                                                                                |

| 9     | CH2    | Output pin to be connected to the negative terminal of the LED string.                                                                                                                                                |

| 10    | CH3    | Output pin to be connected to the negative terminal of the LED string.                                                                                                                                                |

| 11    | CH4    | Output pin to be connected to the negative terminal of the LED string.                                                                                                                                                |

| 12    | SGND   | Signal and channel ground. All external setting components must refer to this ground pin.                                                                                                                             |

| 13    | ISET   | LED current setting pin. Connect a resistor between this pin and SGND to set the full-scale output current.                                                                                                           |

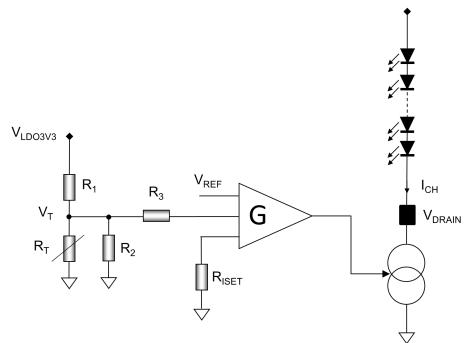

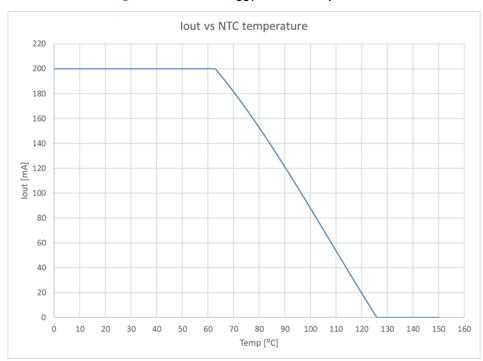

| 14    | TSNS   | External temperature sensor input. Connect to a remote NTC thermistor network to gradually reduce the LED current starting from a desired temperature level. Connect to LDO3V3 in case the function is not used.      |

| Pin # | Symbol | Function                                                                                                                                                                                                                                                                                                                                    |

|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15    | FSW    | Switching frequency setting. A resistor between this pin and SGND sets the desired switching frequency. This pin is also the synchronization input using a direct pulse signal.                                                                                                                                                             |

| 16    | SLOPE  | Control loop compensation slope setting. A resistor between this pin and SGND sets the proper amount of compensation slope for the control loop of the DC-DC converter.                                                                                                                                                                     |

| 17    | COMP   | DC-DC converter loop compensation. A proper RC filter must be connected between this pin and SGND for loop compensation.                                                                                                                                                                                                                    |

| 18    | VFB    | Output voltage feedback input by an external resistor ladder.                                                                                                                                                                                                                                                                               |

| 19    | PGND   | Power ground connection. External components of the DC-DC converter must refer to this ground pin.                                                                                                                                                                                                                                          |

| 20    | GATE   | External power NMOS switch gate driver output.                                                                                                                                                                                                                                                                                              |

|       |        | 5.1 V linear regulator supplies the external power NMOS switch gate driver.                                                                                                                                                                                                                                                                 |

| 21    | LDO5   | Connect a 1 $\mu F$ bypass capacitor between this pin and PGND as close as possible to the device.                                                                                                                                                                                                                                          |

| 22    | PSW    | Switch gate control pin for optional external PMOS for system input protection. Can be left floating or connected through a resistor to ICSN pin if unused.                                                                                                                                                                                 |

| 23    | ICSN   | Input and external power NMOS switch current sensing, negative terminal. Connect this pin to the negative terminal of the input current sensing resistor. The differential voltage between the VIN and ICSN pins is used to sense the current flowing in the DC-DC converter stage and to set the threshold for the overcurrent protection. |

| 24    | VIN    | Supply voltage input. Place a 1 $\mu\text{F}$ bypass capacitor to ground as close as possible to the device.                                                                                                                                                                                                                                |

| -     | TPAD   | Thermal pad. Connect to a suitable (JESD51-7) copper area (it could or not be electrically connected to ground) for power dissipation improvement.                                                                                                                                                                                          |

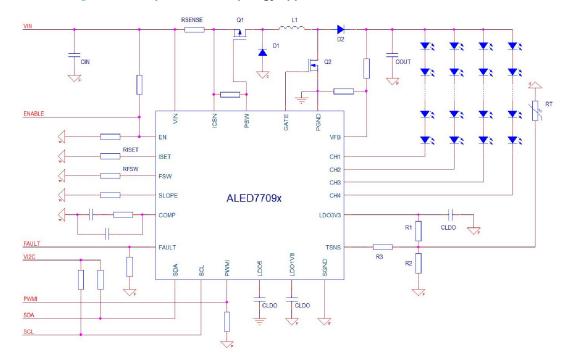

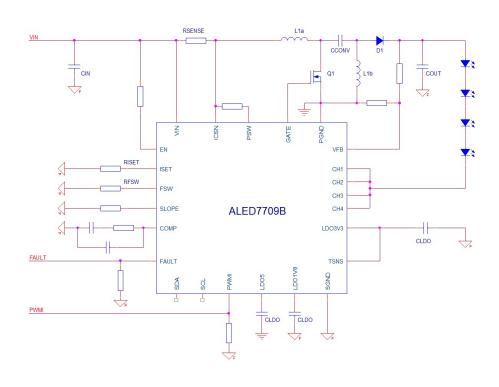

# 3 Typical application circuits

57

## Figure 3. Example of boost topology application with I<sup>2</sup>C and PWMI control

Table 2. Typical main components for boost application

| Symbol             | Value                 | Description                              | Note                      |

|--------------------|-----------------------|------------------------------------------|---------------------------|

| C <sub>IN</sub>    | 2 x 10 µF             | GCJ32EC71H106KA01L- Input<br>capacitor   | Murata                    |

| R <sub>SENSE</sub> | 0.039 Ω               | Input sense resistor                     | 2 W                       |

| Q <sub>1</sub>     | STD40P8F6AG           | PMOS                                     | ST                        |

| D <sub>1</sub>     | STPS1H100             | Diode                                    | ST                        |

| L <sub>1</sub>     | 15 µH                 | XGL1010-153 - inductor                   | Coilcraft                 |

| Q <sub>2</sub>     | STL8N10LF3            | NMOS                                     | ST                        |

| D <sub>2</sub>     | STPS2L60-Y            | Diode                                    | ST                        |

| C <sub>OUT</sub>   | 4 x 10 µF             | GRT31CR61H106KE01L - Output<br>capacitor | Murata                    |

| C <sub>LDO</sub>   | 1 µF                  | LDOs capacitor                           | One for each LDO pin      |

| R <sub>ISET</sub>  | 6.8 kΩ                | I <sub>OUT</sub> setting                 | 150 mA                    |

| R <sub>FSW</sub>   | 62 ΚΩ                 | Converter oscillator resistor            | 400 KHz                   |

| R <sub>T</sub>     | NCG18XH103F0SRB       | NTC resistor                             | Murata                    |

| R <sub>1</sub>     | 1.8 ΚΩ                |                                          |                           |

| R <sub>2</sub>     | 1.1 ΚΩ                | NTC working range setting                | T1 = 65 °C<br>T2 = 125 °C |

| R <sub>3</sub>     | 2.0 ΚΩ                |                                          | 12 = 123 G                |

| LED                | 4 x 10 x KW DPLS34.KD | LEDs                                     | OSRAM                     |

Figure 4. Example of simplified SAM application in SEPIC topology

Table 3. Typical main components for standalone SEPIC application

| Symbol             | Value               | Description                             | Note                 |

|--------------------|---------------------|-----------------------------------------|----------------------|

| C <sub>IN</sub>    | 10 µF               | GCM32EC7YA106KA03 – Input<br>capacitor  | Murata               |

| R <sub>SENSE</sub> | 0.082 Ω             | Input sense resistor                    | 1 W                  |

| L <sub>1a</sub>    | 15 µH               | MSD1260H-153ME – Coupled                | Coilcraft            |

| L <sub>1b</sub>    | 15 µH               | inductor                                | Colician             |

| C <sub>CONV</sub>  | 4.7 µF              | GRT32ER71H475KE01 - SEPIC<br>capacitor  | Murata               |

| Q <sub>1</sub>     | STS8N6LF6AG         | NMOS                                    | ST                   |

| D <sub>1</sub>     | STPS3L40-Y          | Diode                                   | ST                   |

| C <sub>OUT</sub>   | 2 x 10 µF           | GCM32EC71H106KA03 - Output<br>capacitor | Murata               |

| C <sub>LDO</sub>   | 1 uF                | LDOs capacitor                          | One for each LDO pin |

| R <sub>ISET</sub>  | 5.83 kΩ             | I <sub>OUT</sub> setting                | 175 mA               |

| R <sub>FSW</sub>   | 62 ΚΩ               | Converter oscillator resistor           | 400 KHz              |

| LED                | 4 x KW KW DMLS33.SG | LEDs                                    | OSRAM                |

# 4 Maximum ratings

| Table | 4. | Absolute    | maximum | ratings   |

|-------|----|-------------|---------|-----------|

| 10010 |    | / 100010100 |         | . a lingo |

| Symbol                                                  | Parameter                     | Value       | Unit |

|---------------------------------------------------------|-------------------------------|-------------|------|

| I <sub>EN</sub>                                         | Maximum pin supported current | 200         | uA   |

| VIN, EN, ICSN & PSW to SGND                             | Maximum pin voltage           | -0.3 to 60  | V    |

| CH1 through CH4 to SGND                                 |                               | -0.3 to 42  | V    |

| FSW, SDA, SCL & PWMI to<br>SGND                         |                               | -0.3 to 6   | V    |

| LDO3V3, VFB, FAULT, COMP,<br>SLOPE, ISET & TSNS to SGND |                               | -0.3 to 4   | V    |

| LDO5 & GATE to PGND                                     |                               | -0.3 to 6   | V    |

| LDO1V8 to SGND                                          |                               | -0.3 to 2.3 | V    |

| PGND to SGND                                            |                               | -0.3 to 0.3 | V    |

#### Note:

Stressing the device above the rating listed in this table may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

#### Table 5. ESD performance

| Symbol  | Parameter              | Test conditions     | Value | Unit |

|---------|------------------------|---------------------|-------|------|

| ESD ESC |                        | HBM                 | ± 2   | kV   |

|         | ESD protection voltage | CDM corner pins     | ± 750 | V    |

|         |                        | CDM non-corner pins | ± 500 | V    |

#### Table 6. Package thermal data

| Symbol           | Parameter                           | Value | Unit |

|------------------|-------------------------------------|-------|------|

| R <sub>θJA</sub> | Thermal resistance junction-ambient | 25.4  | °C/W |

| R <sub>θJC</sub> | Thermal resistance junction-case    | 2.2   | °C/W |

| R <sub>θJB</sub> | Thermal resistance junction-board   | 8.3   | °C/W |

| ΨJT              | Thermal parameter junction-top      | 0.2   | °C/W |

| Ψјв              | Thermal parameter junction-board    | 8.6   | °C/W |

Note:

Thermal value as defined in standard JESD51-7 on 2s2p board (with 4x4 PCB vias pitch 1 mm).

## Table 7. Thermal data, warning and shutdown

| Symbol           | Parameter                            | Min. | Тур. | Max. | Unit |

|------------------|--------------------------------------|------|------|------|------|

| T <sub>STG</sub> | Storage temperature range            | -55  |      | 150  | °C   |

| TJ               | Operating junction temperature range | -40  |      | 150  | °C   |

| Ta               | Operating ambient temperature        | -40  |      | 125  | °C   |

| T <sub>OTA</sub> | Overtemperature alert threshold      | 110  | 125  | 145  | °C   |

| IOIA             | Overtemperature alert hysteresis     |      | 20   |      | °C   |

| Symbol            | Parameter                   | Min. | Тур. | Max. | Unit |

|-------------------|-----------------------------|------|------|------|------|

| T <sub>SHDN</sub> | Thermal shutdown threshold  | 150  | 165  | 180  | °C   |

|                   | Thermal shutdown hysteresis |      | 20   |      | °C   |

# 5 Electrical characteristics

$V_{IN}$  = 12 V,  $V_{EN}$  = high,  $T_J$  = -40 °C to +125 °C unless otherwise specified.

| Symbol                | Parameter                                                                     | Test conditions                                                                                  | Min. | Тур.                | Max. | Unit     |

|-----------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------|---------------------|------|----------|

| M                     |                                                                               | LDO5 as output                                                                                   | 4.5  |                     | 42   | V        |

| V <sub>IN</sub>       | Operating input voltage                                                       | LDO5 as input (LDO5 shorted to VIN)                                                              | 4.5  |                     | 5.5  | V        |

| V <sub>UVLO,ON</sub>  | Undervoltage lockout upper threshold                                          | V <sub>IN</sub> rising                                                                           | 3.75 | 4.0                 | 4.2  |          |

| V <sub>UVLO,OFF</sub> | Undervoltage lockout lower threshold                                          | V <sub>IN</sub> falling                                                                          | 3.5  | 3.7                 | 3.9  | V        |

| V <sub>UVLO,HYS</sub> | Undervoltage lockout hysteresis                                               |                                                                                                  |      | 0.3                 |      |          |

| V <sub>LDO3V3</sub>   | 3V3 LDO output voltage                                                        |                                                                                                  | 3.2  | 3.33                | 3.45 | V        |

| V <sub>LDO1V8</sub>   | 1V8 LDO output voltage                                                        |                                                                                                  | 1.7  | 1.8                 | 1.87 | V        |

| V <sub>LDO5</sub>     | 5V LDO output voltage                                                         |                                                                                                  | 4.8  | 5.1                 | 5.35 | V        |

| I <sub>VIN,SHDN</sub> | Shutdown current                                                              | EN pin < V <sub>EN1</sub> (shutdown mode)                                                        |      | 7                   | 15   | μA       |

| I <sub>VIN,STBY</sub> | Standby current                                                               | EN pin > $V_{EN2}$ ; bit DEN = 0                                                                 |      | 1.5                 | 3    |          |

|                       | Operating current EN pin > V <sub>EN2</sub> ; bit DEN = 1;<br>CHs & Boost OFF |                                                                                                  |      | 2                   | 4    |          |

| I <sub>VIN,OP</sub>   |                                                                               |                                                                                                  |      | 3                   | 4    | mA       |

| I <sub>VIN,ON</sub>   | Full operating current (1)                                                    | Boost ON @1 MHz;                                                                                 |      | 15                  |      |          |

| ·VIN,ON               | All CHs ON @100 mA                                                            |                                                                                                  |      |                     |      |          |

| Enable                | 1                                                                             |                                                                                                  |      | 1                   | 1    |          |

| V <sub>EN1</sub>      | Device enable threshold                                                       |                                                                                                  | 0.3  |                     | 0.7  |          |

|                       |                                                                               | Rising                                                                                           | 1.12 | 1.22                | 1.32 | V        |

| V <sub>EN2</sub>      | Converter enable threshold                                                    | Falling                                                                                          | 0.97 | 1.07                | 1.17 |          |

|                       |                                                                               | Hysteresis                                                                                       |      | 0.15                |      |          |

| Converter co          |                                                                               |                                                                                                  | -    |                     |      |          |

| F <sub>SW_int</sub>   | Internal switching frequency                                                  | FSW[1:0] = 10                                                                                    | С    | LK <sub>INT</sub> / | 8    | Hz       |

| K <sub>FSW</sub>      | Switching frequency constant                                                  | R <sub>FSW</sub> = 24.9 kΩ                                                                       | 23   | 25                  | 27   | MHz * kΩ |

|                       | Adjustable switching frequency FSW[1:0] = 00                                  | $R_{FSW}$ = 100 k $\Omega$ => $K_{FSW}$ / $R_{FSW}$ = $F_{SW}$                                   |      | 250                 |      |          |

| F <sub>SW_adj</sub>   |                                                                               | $R_{FSW}$ = 12.4 k $\Omega$ => $K_{FSW}$ / $R_{FSW}$ = $F_{SW}$                                  |      | 2016                |      | kHz      |

| 011_00                | Synchronization signal frequency capture range                                | $t_{\rm CLK,H} = 200 \text{ ns}, V_{\rm CLK,L} < 0.3 \text{ V},$ $V_{\rm CLK,H} > 2.8 \text{ V}$ | 250  |                     | 2200 |          |

| F <sub>SWH</sub>      | FSW synchronization input high level                                          |                                                                                                  | 2.8  |                     |      |          |

| F <sub>SWL</sub>      | FSW synchronization input low level                                           |                                                                                                  |      |                     | 0.3  | V        |

| F <sub>SWPulse</sub>  | Synchronization input high level pulse width                                  |                                                                                                  | 200  |                     |      | ns       |

| V <sub>ICSN,PK</sub>  | Power switch max. peak detection threshold                                    | V <sub>IN</sub> - V <sub>ICSN</sub>                                                              | 180  | 200                 | 220  | mV       |

| DRVR_on_HS            | R_on of high-side driver (1)                                                  |                                                                                                  |      | 2.00                |      | Ω        |

| DRVR_on_LS            | R_on of low-side driver <sup>(1)</sup>                                        |                                                                                                  |      | 1.07                |      | Ω        |

| t <sub>SS,max</sub>   | -<br>Max. soft-start duration <sup>(1) (2)</sup>                              |                                                                                                  |      | 3.5                 |      | ms       |

### Table 8. Electrical characteristics

| Symbol                  | Parameter                                                                         | Test conditions                                                               | Min.  | Тур.                        | Max.     | Unit |

|-------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------|-----------------------------|----------|------|

| V <sub>VFB,max</sub>    |                                                                                   |                                                                               | 1.02  | 1.08                        | 1.14     |      |

| $V_{VFB,min}$           | Internal reference voltage for output regulation                                  |                                                                               | 0.75  | 5 0.795 0.84                |          | V    |

| V <sub>VFB,skip</sub>   | Internal reference voltage to force converter in pulse skip mode                  |                                                                               | 1.03  | 1.09                        | 1.15     |      |

| Current gene            | erators                                                                           |                                                                               |       | 1                           | · /      |      |

| V <sub>HRREF</sub>      | Minimum headroom voltage across reference channel                                 | R <sub>ISET</sub> = 5.11 kΩ                                                   | 0.83  | 1.1                         | 1.3      | V    |

| I <sub>CH_SETmin</sub>  | Output current <sup>(3)</sup>                                                     | R <sub>ISET</sub> = 40.7 KΩ<br>I <sub>CH_SET</sub> = 1022 / R <sub>ISET</sub> |       | 25.1                        |          | mA   |

| I <sub>CH_SETmax</sub>  | Output current                                                                    | $R_{ISET}$ = 5.11 KΩ<br>I <sub>CH_SET</sub> = 1022 / R <sub>ISET</sub>        |       | 200                         |          | IIIA |

| $\Delta I_{CHn}$        | Absolute channel accuracy (each channel to nominal value) $^{\left( 4\right) }$   | $R_{ISET}$ = 10 K $\Omega$<br>100% dimming and V <sub>HRCHx</sub> = 1.0 V     |       | ±2                          | ±4       | %    |

| ΔI <sub>CHx</sub>       | Channel to channel mismatch (each channel to device average value) <sup>(5)</sup> | $R_{ISET}$ = 10 K $\Omega$<br>100% dimming and V <sub>HRCHx</sub> = 1.0 V     |       | ±1                          | ±3       | %    |

| I <sub>CHoff</sub>      | Output current in OFF mode                                                        | EN = High; DEN = 0<br>V <sub>HRCHx</sub> = 35 V                               |       | 0.1                         | 0.5      | μA   |

| PWM dimmir              | ng control                                                                        |                                                                               |       |                             |          |      |

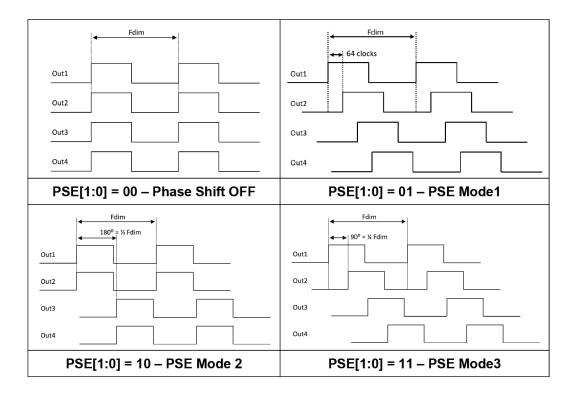

| CLK <sub>INT</sub>      | Internal dimming oscillator frequency                                             |                                                                               | 5.9   | 6.553                       | 7.34     | MHz  |

| CLK <sub>SS</sub>       | Spread spectrum of internal oscillator frequency                                  | DCLKMS[1:0] = 00                                                              | ±3.75 | ±4.75                       | ±5.0     | %    |

| F <sub>PWM</sub>        | Dimming frequency                                                                 | FDIM[2:0] = 110                                                               | CLK   | CLK <sub>INT</sub> / (2^10) |          |      |

| D <sub>PWM</sub>        | Dimming duty-cycle range                                                          |                                                                               | 0     |                             | 100      | %    |

| t <sub>PWM_ON</sub>     | Output pulse ON-time (1)                                                          | PWMx[0x0003]                                                                  |       | 0.46                        |          | μs   |

| F <sub>PWMI</sub>       | PWMI frequency                                                                    |                                                                               | 0.06  |                             | 14       | kHz  |

| t <sub>PWMImin</sub>    | PWMI minimum pulse transferred to output                                          | PWMI_DRCT = 1                                                                 |       | 0.5                         |          | μs   |

| V <sub>PWMIH</sub>      | PWMI high level                                                                   |                                                                               | 1.3   |                             |          |      |

| V <sub>PWMIL</sub>      | PWMI low level                                                                    |                                                                               |       |                             | 0.5      | V    |

| PMOS drivin             | g                                                                                 |                                                                               |       | 1                           | <u> </u> |      |

| I <sub>PSW,OFF</sub>    | PSW pin leakage current                                                           |                                                                               |       | 0.07                        | 1        |      |

| I <sub>PSW,ON</sub>     | PSW pin driving current                                                           |                                                                               | 80    | 105                         | 135      | μA   |

| Fault / protee          | ction management                                                                  |                                                                               |       |                             | II       |      |

| V <sub>IN,OVPT-UP</sub> | Input overvoltage protection upper threshold                                      | V <sub>IN</sub> rising                                                        | 36    | 40                          | 42       |      |

| V <sub>IN,OVPT-DW</sub> | Input overvoltage protection lower threshold                                      | V <sub>IN</sub> falling                                                       | 33    | 37.5                        | 40       | V    |

| V <sub>IN,OVPH</sub>    | Input overvoltage protection hysteresis                                           |                                                                               |       | 2.5                         |          |      |

| V <sub>ICSN,OCPT</sub>  | Input overcurrent protection threshold                                            | V <sub>IN</sub> – V <sub>ICSN</sub>                                           | 220   | 240                         | 260      | mV   |

| V <sub>VFB,OVPT</sub>   | Output overvoltage protection threshold                                           | Output voltage converter turning OFF threshold on $V_{FB}$                    | 1.1   | 1.18                        | 1.26     | V    |

| V <sub>CHx,FLT</sub>    | LED short-circuit detection threshold                                             |                                                                               | 4.6   | 4.9                         | 5.2      | V    |

| V <sub>FAULTH</sub>     | FAULT output high level                                                           | R <sub>FAULT</sub> = 3.3 KΩ                                                   | 2.9   |                             |          | V    |

| I <sub>FAULT</sub>      | FAULT leakage current                                                             |                                                                               |       |                             | 1        | μA   |

| Symbol                    | Parameter                           | Test conditions          | Min. | Тур. | Max. | Unit |  |

|---------------------------|-------------------------------------|--------------------------|------|------|------|------|--|

| I <sup>2</sup> C compatil | <sup>2</sup> C compatible interface |                          |      |      |      |      |  |

| VIH                       | High level input voltage            |                          | 1.3  |      |      |      |  |

| V <sub>IL</sub>           | Low level input voltage             |                          |      |      | 0.5  | V    |  |

| V <sub>OL</sub>           | Low level output voltage            | I <sub>TEST</sub> = 5 mA |      |      | 0.4  |      |  |

| C <sub>IO</sub>           | I/O pins capacitance (1)            |                          |      |      | 10   | pF   |  |

1. Not tested in production.

2. Overall soft-start duration depends on application.

3. The accuracy between the programmed  $I_{CH}$  and the output current is not guaranteed for:  $I_{CH} < I_{CH\_SETmin}$ .

4.

$$\Delta I_{CHn} = MAX \left( \frac{|I_{CHn} - I_{CHnom}|}{I_{CHnom}} \right) * 100$$

5.  $\Delta I_{CHx} = MAX \left( \frac{|I_{CHx} - I_{CHavg}|}{I_{CHavg}} \right) * 100; I_{CHavg} = \frac{\Sigma I_{CHn}}{4}$

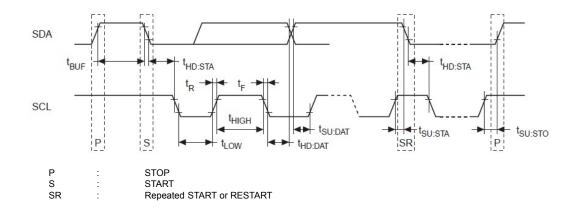

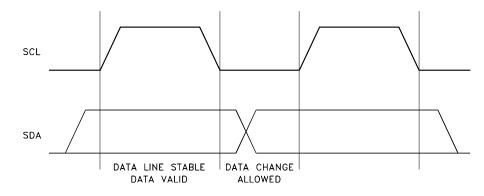

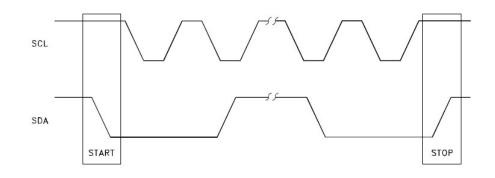

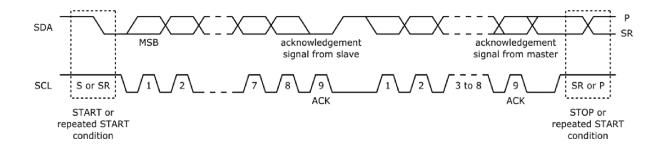

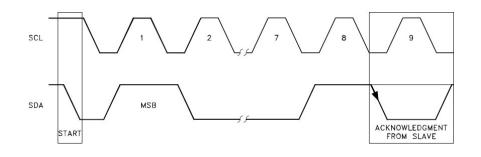

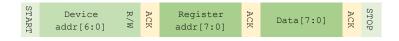

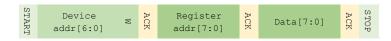

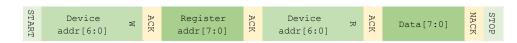

# 6 I<sup>2</sup>C switching characteristics

$V_{IN}$  = 12 V,  $V_{EN}$  = High,  $T_A$  = 25 °C unless otherwise specified.

| Symbol              | Parameter                        | Test conditions | Min. | Тур. | Max. | Unit |

|---------------------|----------------------------------|-----------------|------|------|------|------|

| f <sub>SCL</sub>    | SCL clock frequency              |                 |      |      | 400  | kHz  |

| t <sub>LOW</sub>    | Minimum clock low period         |                 | 1.3  |      |      | μs   |

| t <sub>HIGH</sub>   | Minimum clock high period        |                 | 600  |      |      | ns   |

| t <sub>F</sub>      | SDA and SCL fall time            |                 |      |      | 300  | ns   |

| t <sub>R</sub>      | SDA and SCL rise time            |                 |      |      | 300  | ns   |

| t <sub>HD:STA</sub> | Start condition hold time        |                 | 600  |      |      | ns   |

| t <sub>SU:STA</sub> | Start condition setup time       |                 | 600  |      |      | ns   |

| t <sub>SU:DAT</sub> | Data setup time                  |                 | 100  |      |      | ns   |

| t <sub>HD:DAT</sub> | Data hold time                   |                 | 0    |      |      | μs   |

| t <sub>SU:STO</sub> | Stop condition setup time        |                 | 600  |      |      | ns   |

| t <sub>BUF</sub>    | Minimum delay between operations |                 | 1.3  |      |      | μs   |

## Table 9. I<sup>2</sup>C fast-mode switching characteristics

## Figure 5. I<sup>2</sup>C timing reference

# 7 Functional description

## 7.1 Overview

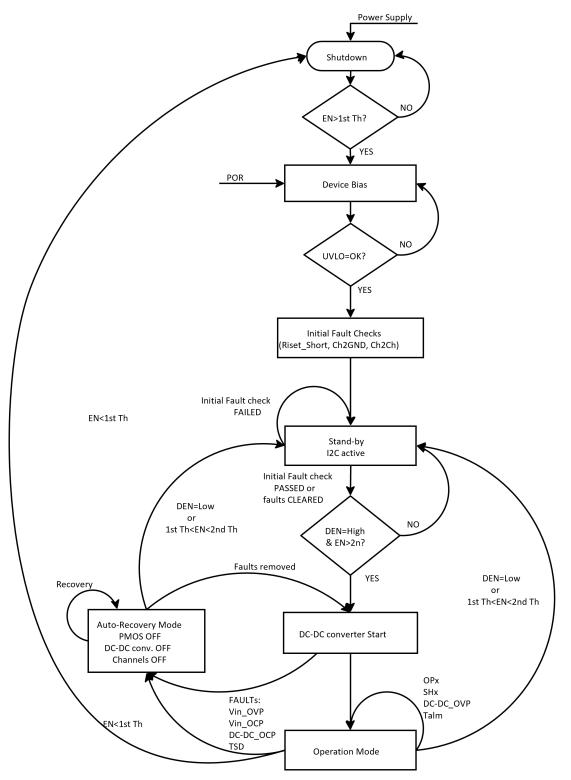

ALED7709x are LED drivers, which integrate a DC-DC converter controller and four high precision constantcurrent sinkers. They have been specifically designed to work controlled by an MCU through an I<sup>2</sup>C Bus and/or by a control signal applied on the PWMI pin. For both ALED7709A and ALED7709B, the two control methods are not mutually exclusive, either or both can be used.

ALED7709x can drive four strings of LEDs connected in series with high efficiency and flexible brightness control. The devices can support both boost and SEPIC topologies to cover most applications.

The DC-DC converter architecture is based on a constant peak current control; it has a specific adaptive output voltage regulation to reduce the internal power dissipation. An adaptive algorithm manages the DC-DC converter reference voltage looking at the CHs minimum voltage needed to guarantee the sinkers current regulation.

The brightness of the LED strings can be adjusted in two manners:

- 1. **Global**: all the outputs are driven to the same brightness level allowing mixed PWM and current dimming; this is also possible by driving the device through PWMI signal only.

- Local: the PWM and current adjustments are independent for each channel; this mode is possible through I<sup>2</sup>C register setting only.

Phase-shifting function (interleaved operation of the output channels) and edge control (rise and fall time adjustment), are useful to reduce EMI and audible noise.

# 7.2 Device supply

ALED7709x have a power tree composed by three different linear voltage regulators.

A 3V3 low-dropout linear regulator (LDO3V3), which supplies the analog circuitry of the chip; it is the master enabler of the device.

A 1V8 low-dropout linear regulator (LDO1V8), supplied by 3V3 LDO, powers the digital circuitry of the chip.

A 5.1 V low-dropout linear regulator (LDO5), supplied directly by  $V_{IN}$ , is dedicated to supply the gate driver of the external power MOS for the DC-DC converter.

All LDOs are protected against short circuit, nevertheless it is not suggested to use them for supplying external circuitry. LDO3V3 can be used for  $I^2C$  pull-ups and reference NTC resistor ladders.

An undervoltage lockout (UVLO) protection is connected on LDO5 output to control the complete power tree: in case the input voltage on  $V_{IN}$  pin is below the value to guarantee the proper power supply levels, the device is blocked and therefore disabled to work.

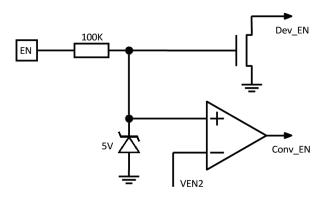

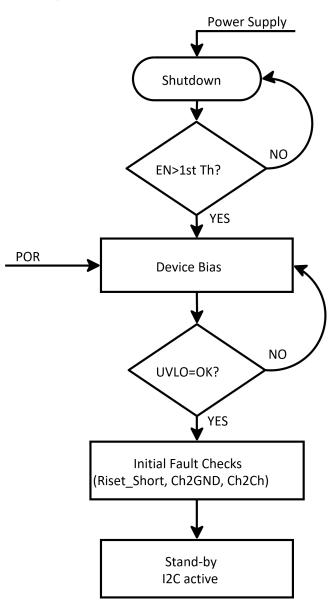

EN pin is the device enabler. It has a main threshold that brings the device in/out from shutdown.

Above this threshold LDO3V3 goes ON and activates the rest of the power tree; below it is turned OFF and, as consequence, the device enters in Shutdown setting at minimum the quiescent current; the volatile registers are not kept and I<sup>2</sup>C communication is disabled.

#### Figure 6. Enable pin circuit

57

The second threshold of EN pin enables the DC-DC converter stage and sinkers activity.

Properly setting a resistor divider connected to  $V_{IN}$ , it is possible to disable the DC-DC converter and channels when  $V_{IN}$  goes below a defined value. If the voltage on EN pin goes below the second threshold but stays above the main one, the rest of the device remains ON, keeping the content of volatile registers and I<sup>2</sup>C communication active, being ready to restart from the previously programmed condition as soon as EN pin rises above  $V_{EN2}$ .

When EN pin voltage is high, the device exits from shutdown and enters in standby; in this condition, the I<sup>2</sup>C communication is active, and the volatile register content is kept. To move from standby to operative mode, DEN bit must be set to high.

There is a 5 V clamp, for internal circuit protection, connected on EN pin through a 100 k $\Omega$  resistor, to avoid any unnecessary current flowing inside the pin it is suggested to keep V<sub>EN</sub> below 4.5 V. Anyway, it is possible to connect EN pin to a higher voltage but taking care to limit the max. current below 200  $\mu$ A.

As soon as the Power-on Reset (PoR) is released ALED7709x check the initial fault; after that ALED7709A enters in standby enabling also the I<sup>2</sup>C communication, while ALED7709B enters directly in operation mode.

Figure 7. Startup sequence for ALED7709A

## 7.3 Initial fault check

ALED7709x perform a specific fault verification each time the device exits from shutdown and before the first turn ON, to avoid any system malfunction if:

- R<sub>Iset</sub> resistance is short-to-ground,

- channels are short-to-ground,

- adjacent channels are short among them (ALED7709A only).

Such tests cannot be executed on demand and during operating mode are no longer active.

The user can overtake any condition of initial fault and force anyway the device to start, only acting on both CLRF and DEN bits through I<sup>2</sup>C communication (write 0x81 to register DEVEN).

Before performing this action, which could be potentially dangerous for the system, it is suggested to read the INITSTA register and decide whether the detected fault is manageable or not.

#### 7.3.1 R<sub>Iset</sub> short

5.11 K $\Omega$  is the minimum operative value of R<sub>Iset</sub> that corresponds to a maximum I<sub>CH</sub> current of 200 mA.

If R<sub>ISET</sub> is, for any reason, short-to-ground, ALED7709x enter a non-linear zone and drive an unknown current in the LED strings. A current that could be higher than the safe limit of LEDs.

To avoid such phenomena, each time the ALED7709x exit from shutdown, it checks the status of  $R_{lset}$ ; if it is found shorted-to-ground the devices stop in standby mode. ALED7709B does not reach the operational mode.

## 7.3.2 CH to GND

This function detects if one or more channels are shorted-to-ground.

This test is performed only during initial fault verification when all channels and DC-DC converter are OFF. This function prevents extra current from flowing into LED strings in case of accidental short-circuit from any channel to ground.

#### 7.3.3 CH to CH short (ALED7709A only)

This function detects if adjacent channels are shorted together and it is performed among: CH0-CH1, CH1-CH2 and CH2-CH3.

The validity of the output of this test relies on the fact that it is fulfilled at the beginning of the startup sequence when all channels and DC-DC converter are OFF, under this condition it is expected to have Vboost close to ground. If this is not the case, and the startup begins when Vboost still has a residual voltage, enough to allow a current flowing in the LED string, the test could give false result.

## 7.4 Fault detection

As soon as ALED7709x exit from standby, they execute various steps to reach operation mode; at each step, different fault detections are activated and kept running during operation mode as well.

## 7.4.1 V<sub>IN</sub>OVP by external PMOS

This circuit prevents damage to the output stage when input voltage rises above 40 V.

In boost configuration, to avoid a direct path from  $V_{\text{IN}}$  to the DC-DC converter out, a PMOS in series to the coil is needed.

If the fault is detected, the PMOS is immediately switched OFF to disconnect OUT from IN.

When the fault occurs, the device enters auto-recovery mode by trying to recover continuously from fault; if  $V_{IN}$  remains above the falling threshold, the device does not switch ON PMOS to keep the system safe. If the fault is removed/resolved, the device restarts from the soft-start procedure to return in operative mode.

In auto-recovery mode, the I<sup>2</sup>C communication is active, therefore internal registers can be read and written.

If the DEN bit is reset to 0, the device moves from recovery mode to standby mode.

This fault, when it occurs, is latched in the IOVP bit and externally signalized by the FAULT pin, if not masked.

## 7.4.2 V<sub>IN</sub>OCP and V<sub>OUT</sub>OCP by external PMOS

This circuit prevents input current from going higher than the limit imposed by the used external components. It also protects the system in case of overcurrent due to the DC-DC converter output short-to-ground. To protect the circuitry from the short, the PMOS turn-OFF is executed very quickly. When the fault occurs, the device enters auto-recovery mode; the fault is latched in the IOCP bit and externally signalized through the FAULT pin, if not masked.

#### 7.4.3 V<sub>IN</sub>\_UVLO

When  $V_{IN}$  is too low to have VLDO5 above the  $V_{UVLO, ON}$  threshold, the device is blocked and communication is disabled. Once running,  $V_{IN}$  must fall down enough to bring VLDO5 below  $V_{UVLO, OFF}$  to stop the operation.

#### 7.4.4 Thermal shutdown

This fault is detected when the device temperature is higher than  $T_{SHDN}$ .

When this fault is detected, the devices immediately turn OFF the DC-DC converter and then, after a delay that depends on PWM output frame duration, all the channels are also turned OFF.

The devices restart automatically when the temperature is reduced by the thermal hysteresis value. This fault, when it occurs, is latched in the THSD bit, and externally communicated through the FAULT pin, if not masked.

#### 7.4.4.1 Over temperature early alert indicator

This warning is issued when device temperature increases above T<sub>OTA</sub>.

When this event is detected the OTEA bit is latched and externally signalized by FAULT pin, if not masked. The devices do not move to shut down as consequence of this alert.

#### 7.4.5 V<sub>OUT</sub>OVP

This circuitry prevents DC-DC converter output voltage from rising over 42 V. As soon as OVP is detected the DC-DC converter section is switched OFF.

This function is obtained monitoring the VFB pin voltage; V<sub>OUT</sub>OVP is triggered when V<sub>FB</sub> reaches V<sub>VFB,OVPT</sub>.

The VFB pin is internally protected from any accidental low-side resistor disconnection. If this fault occurs, the OOVP bit is latched and signalized by the FAULT pin, if not masked.

#### 7.4.6 Channel fault detection

The ALED7709x implement both open and short LED detection.

Setting the auto-disconnection bits (OCAD for open LED and SCAD for short LED) the failing channel is properly disabled, clearing the respective CENx bit, only when the adaptive loop is active (OVRE bit to 1).

If the OCAD and SCAD bits are reset, the faulty channel is always signaled but it remains enabled and connected, potentially affecting the adaptive loop.

Channel fault detection is active if the channels are ON for a period longer than 32 main clocks (about 5 µs).

#### 7.4.6.1 Open LED

The detection of open LED fault is fulfilled by sensing the headroom voltage versus an internal reference. To confirm the fault, a specific algorithm has been implemented to identify real open LED fault from false detection due to some dynamic transitions.

When an open LED event is detected by the open LED comparator, it is not immediately reported as a fault. An LED open path forces the headroom voltage to fall, and the adaptive control provides the UP signal to allow  $V_{OUT}$  to rise. If the open LED information is confirmed when the DAC reaches the reference value, the FAULT is managed according to the device configuration.

If during the  $V_{OUT}$  rising the open LED information from the comparator disappears, the open LED fault interrupt is not generated and the  $V_{OUT}$  is frozen or moves down to the target value according to a new adaptive phase. If confirmed, the open LED fault is latched to the LEDF bit and the faulty channel is reported by the OPx bit, and the fault indication is exported to the FAULT pin, if not masked.

### 7.4.6.2 Short LED

In the case of LED short-circuit, the drop across the LED string is reduced and the voltage in excess remains on the output channel.

The ALED7709x compare the headroom voltage with the reference, and when it is higher the fault is immediately latched on the LEDF bit and on SHx to identify the faulty channel. The fault indication is also exported to the FAULT pin, if not masked.

# 7.5 Line switch P-MOS control

The ALED7709x have a line switch control circuit, which can drive an optional P-channel MOSFET placed in series to the input. In this manner the LED strings, channels, and DC-DC converter are protected in case of faulty conditions output short-circuit to ground or input voltage transient above 40 V. The switch control circuit is also helpful to reduce the power consumption in standby.

The line switch control senses the input voltage level on the  $V_{IN}$  pin and the current drawn from  $V_{IN}$  checking the voltage across the  $R_{SNS}$  on the ICSN pin.

PSW pin is the gate driver of the external PMOS, it provides a controlled current, which generates, across a resistor, an appropriate VGS to keep the PMOS active during the normal operation.

As soon as a critical fault is detected and auto-recovery mode is activated, the line switch circuit immediately sets the external PMOS OFF to protect the following circuits and a new startup sequence is activated. If the fault continues, the auto-recovery mode remains active repeating the PMOS OFF and new startup; as soon as the fault is solved, the startup goes to the end driving the device to normal operational mode.

In standby (bit DEN = 0) the PMOS is kept OFF to avoid any possible current leakage in boost and LED strings. Since the external PMOS is optional, the line switch control circuit can be disabled through the LSWE bit. Disabling this circuit, the Input OVP and OCPs are no longer active.

#### Figure 8. Complete working flow

## 7.6 Device shutdown and standby

The ALED7709x can be shut down by lowering the EN pin below the  $V_{EN1}$  threshold at any time.

However, when the device is controlled through the serial interface, there is also the possibility to act on DEN bit in the main configuration register (DEVCFG); this brings the device in standby preserving the content of the registers. This should be the simplest way to control the device unless further power consumption reduction is necessary.

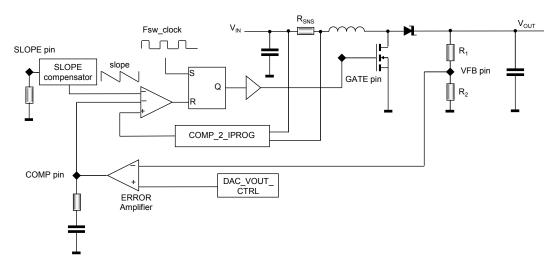

# 7.7 DC-DC converter controller section and output voltage optimization

The purpose of this macro-block is to convert the input voltage to the needed output voltage using the peakcurrent mode as control loop.

The output voltage is sensed by an external resistor voltage divider, whose output is connected to the VFB (feedback) pin; the target value is set providing to a transconductance amplifier (Error Amplifier) a reference voltage generated by a 7-bit DAC.

The current generated by this block is proportional to the output voltage error and it is sent to an external compensation network, mainly composed by an RC series, connected on the COMP pin.

The voltage of this pin is then used as a reference to set the peak current of the external inductor to control the "closed loop".

#### Figure 9. Converter stage circuitry

Each switching cycle starts with the FSW clock rising edge, which triggers the gate driver of the external NMOS; it starts a  $t_{ON,min}$  pulse during which the turning-off of the gate driver is not allowed.

This masking time has a double function:

- to avoid a too short ON pulse that is potentially dangerous for the circuits

- to avoid wrong current readings from current sensors due to the noise generated during transitions

The current flowing through the external inductor L is sensed by reading the voltage drop across the sense resistor R<sub>SNS</sub> connected in series with the inductor itself.

To avoid intrinsic instability present in the current loop of the current mode control, it's mandatory to add to the information coming from the current sensing (the voltage drop across external sense resistor) an extra ramp whose slope should be equal to that of current sensed during t<sub>OFF</sub>. Slope can be set by an external resistor on the SLOPE pin.

When the sum of the current sense voltage and the compensation ramp meets the threshold proportional to COMP pin voltage, the NMOS driver is turned OFF and the inductor current starts flowing through the external diode toward the load.

The overall DC-DC converter functions of the ALED7709x consist of:

- Fixed-frequency current-mode controller

- Output voltage optimization loop

- External MOSFET gate driver

- Related protection circuitry

### 7.7.1 Fixed-frequency current-mode controller main blocks

#### 7.7.1.1 DAC\_VOUT\_CTRL

This block is a 7-bit digital to analog converter whose main purpose is to provide the voltage reference to the converter block for optimizing  $V_{OUT}$ .

From this block are derived also three thresholds for specific actions:

- output overvoltage: if this threshold is reached on the VFB pin, a fault is generated and the converter is switched OFF (V<sub>VFB,OVPT</sub> = 1.18 V)

- skip mode: for VFB pin voltage slightly higher than V<sub>VFB,SKIP</sub> = 1.09 V, the converter enters in skip mode to avoid reaching the overvoltage protection threshold

- open fault: it is the value to be reached on VFB pin before getting an open channel fault recognition (V<sub>VFB,OD</sub> = 1.03 V)

In normal operational mode, the 7-bit addresses 128 voltage steps, the minimum voltage step is 2.244 mV granting a range of 285 mV between the  $V_{DAC,min}$  of 0.795 V to the  $V_{DAC,max}$  of 1.08 V.

#### Table 10. Converter reference voltages

| V <sub>DAC,max</sub> [V] | V <sub>DAC,min</sub> [V] | V <sub>VFB,OD</sub> [V] | V <sub>VFB,SKIP</sub> [V] | V <sub>VFB,OVPT</sub> [V] |

|--------------------------|--------------------------|-------------------------|---------------------------|---------------------------|

| 1.08                     | 0.795                    | 1.03                    | 1.09                      | 1.18                      |

### 7.7.1.2 Error amplifier and COMP pin

The error amplifier is a transconductance amplifier, with a typical Gain of 600  $\mu$ S, that generates a current proportional to the error between DC-DC converter voltage reference (V<sub>DAC</sub> output) and feedback voltage (V<sub>VFB</sub>) on the VFB pin.

If the error amplifier tries to drive the COMP pin below 0.725 V, a SKIP signal is asserted to stop switching activity preventing the output voltage to diverge.

To avoid the COMP pin voltage going above its maximum limit of 1.9 V, a sink current clamp is present.

The reference value of this clamp is gradually increased during the soft-start, allowing a progressive current control.

The stability of this block is granted only if a resistor in series to a compensation capacitor is connected on the COMP pin.

#### 7.7.1.3 COMP\_2\_IPROG and peak current comparator

This block is the core of the DC-DC converter control since it is responsible for controlling the peak current flowing into the coil and, as a consequence, controlling the output power.

The COMP\_2\_IPROG block manages the voltage  $V_{IN}$ - $V_{CSNS}$  =  $R_{SNS}$ \*I<sub>L</sub>.

The COMP pin voltage is buffered with a typical gain of 0.29167 and then it is modulated by SLOPE compensation and compared to the voltage drop on  $R_{SNS}$ , which is directly proportional to the coil current  $I_L$ .

The above-described voltages are the inputs of the peak current comparator that is the sub-block used to turn OFF the converter PWM cycle-by-cycle.

The peak current comparator is very fast and sensitive because input voltage could be of few tenths of mV. There are a couple of thresholds. 200 mV and 240 mV, to have a better circuit protection.

These two thresholds are used for cycle-by-cycle current limitation and for overcurrent protection, the latter causes a fault and then opening the external PMOS, if present.

#### 7.7.1.4 Slope compensator

The constant frequency, peak current-mode topology has the advantage of very easy loop compensation with output ceramic caps (reduced cost and size of the application), and fast transient response. In addition, the intrinsic peak current measurement simplifies the current limit protection, avoiding undesired saturation of the inductor. However, this topology has a drawback: there is inherent open loop instability when operating with a duty-cycle greater than 0.5. This phenomenon is known as "sub-harmonic instability" and can be avoided by adding an external ramp to the one coming from the sensed current. This compensating technique, based on the additional ramp, is called "slope compensation".

The slope compensator generates a correction ramp set by a resistor connected to the SLOPE pin; such ramp modulates the COMP pin voltage before to comparing it with the one present on the sensing resistor ( $R_{SNS}$ ).

To avoid sub-harmonic instability, the compensating slope should be greater than one-half of the slope of the inductor current during the OFF phase when the duty-cycle is greater than 50%. For an effective compensation, the value of  $R_{SLOPE}$  can be defined according to the following formula, for boost case:

$$R_{SLOPE} \le K_S \cdot K_{FS} \cdot \frac{L}{(V_{OUIT_{max}} - V_{IN_{min}}) \cdot R_{SNS}} \quad \Omega \tag{1}$$

and with the following formula for SEPIC case:

$$R_{SLOPE} \le K_S \cdot K_{FS} \cdot \frac{L}{K_{FS} \cdot V_{OUTmax} \cdot R_{SNS}} \quad \Omega \tag{2}$$

Where:  $V_{OUTmax}$  is the maximum output voltage set by resistor divider;  $V_{INmin}$  is the minimum voltage for which the converter is enabled to work;  $K_{FS}$  = 1.4 is an extra margin for a robust calculation;  $K_S$  = 5.833\*10<sup>9</sup> [ $\Omega$ \*V/s] is the SLOPE coefficient derived from the internal circuit implementation.

### 7.7.2 Device turning-on and soft-start sequence

As soon as the DEN bit is asserted, the ALED7709A executes the soft-start steps.

The ALED7709B executes the soft-start steps as soon as the EN pin is released since DEN is asserted at POR. For both devices, the soft-start sequence is the same.

If no critical faults have been detected, the DC-DC converter starts switching with a frequency 25% of the nominal value and current limit set at 20% of nominal level. Converter switching frequency and current limitation are increased according to specific steps until their nominal values.

This sequence is assumed to be concluded when the output voltage reaches the target level of skip mode; the switching frequency and the current limit are released to their respective nominal values and the channels are enabled according to their own enable setting.

Once the channels are enabled, the operating point (voltage and current) of all active channels is monitored and used as feedback to minimize the output voltage for maximum efficiency.

In practice, the internal DAC, in charge of providing the reference voltage to the control loop, starts rolling down as soon as a valid dimming is applied.

The output voltage optimization can only be performed when at least one channel is active, and all the active channels have an ON-time longer than 48 master clock cycles.

#### 7.7.3 DC-DC converter working frequency

The working frequency of DC-DC converter, F<sub>SW</sub>, can be selected either from local oscillator or from internal main clock.

The selection is done through FSW[1:0] bits in register BOOSTCFG (refer to Section 8.3.8).

When the local oscillator is chosen (FSW[1:0]=00, which is the POR value of ALED7709B), the value of  $F_{SW}$ , in MHz, is defined by the external resistor  $R_{FSW}$ , in K $\Omega$ , by the following formula:

#### $F_{SW}$ = 25 / $R_{FSW}$

Local oscillator has a dedicated spread spectrum capability; spread spectrum, which is active by default, can be disabled setting to 1 DFSW\_DIS bit.

The internal spread spectrum circuit changes the switching frequency in a range of ±5%.

$$\Delta F_{SW} = 5\% \cdot F_{SW} \tag{3}$$

The device updates the frequency every clock period by fixed steps:

- Ramps up in 63 steps from minimum to maximum F<sub>SW</sub>.

- Ramps down in 64 steps from maximum to minimum F<sub>SW</sub>

The modulation shape is almost triangular with a frequency of

$$Spr = \frac{F_{SW}}{127} \tag{4}$$

Local oscillator can be directly synchronized, within the working range, by an external signal

F

There is the possibility to use the DC-DC converter frequency  $F_{SW}$  derived from the main clock of ALED7709A, the value depends on the FSW[1:0] setting (refer to Section 8.3.8).

Under this configuration, the spread spectrum modulation of  $F_{SW}$  is a direct consequence of depth and speed applied to the main clock, configured by DCLKMS[1:0] bits and enabled/disabled by DCLK\_DIS bit available in BOOSTCFG register.

When  $F_{SW}$  is derived from main clock the synchronization is not possible; the resistor connected to FSW pin is not necessary, the pin could be left floating or, better, connected to LDO3V3 to inhibit the local oscillator.

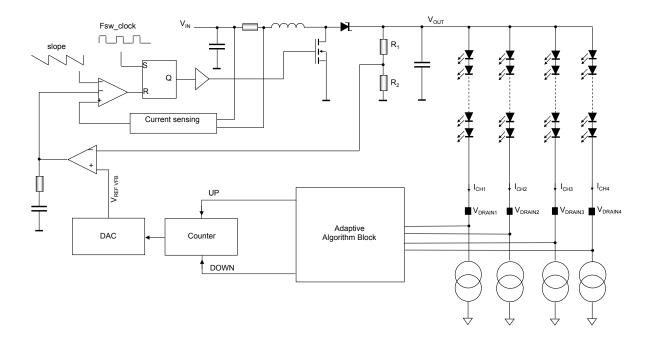

#### 7.7.4 Output voltage optimization and control

The output voltage of the DC-DC converter section, which is the supply rail for the LED strings, is regulated in an adaptive way to improve the overall system efficiency.

A dedicated Digital to Analog Converter (DAC) sets the reference voltage of the control loop; value is defined to set the output voltage enough to guarantee the required current but also to keep the power dissipation of the LED driving section to the minimum level.

This optimization is performed by keeping the voltage of the leading channel, the one with lower  $V_{DRAIN}$ , over the headroom reference voltage ( $V_{HRREF}$ ) which is an absolute value internally defined and dependent from  $I_{OUT,max}$  current set by  $R_{ISET}$ .

The  $V_{HRREF}$  includes an additional margin from the absolute minimum value that brings the  $I_{LED}$  current out of regulation, this to avoid any current variation in the channels due to the dynamic variation of  $V_{OUT}$ .

#### Figure 10. Simplified V<sub>OUT</sub> regulation circuitry

During normal operation, the status of all the channels is checked and the information is transferred to a proprietary algorithm, a mixed analog-digital solution, to optimize the  $V_{OUT}$ .

The ideal target is to have all the  $V_{DRAIN}$  between  $V_{HRREF}$  and  $V_{HRREF,H}$  (an hysteresis window of about 200 mV), but in reality it is the leading channel to take stronger control of the  $V_{OUT}$  adjustment to get itself inside the window.

- if a channel has a V<sub>DRAIN</sub> voltage higher than the reference V<sub>HRREF,H</sub> the algorithm records it; if during a PWM period all the active channels are in agreement, the system counts DOWN to reduce V<sub>OUT</sub>, until the leading channel V<sub>DRAIN</sub> crosses V<sub>HRREF,H</sub> and it is no longer in agreement with other channels:

- $V_{OUT}$  going DOWN up to CHx\_V<sub>DRAIN</sub> <  $V_{HRREF,H}$

- if the leading channel has the voltage drop lower than the reference V<sub>HRREF</sub>, the system immediately counts UP to increase V<sub>OUT</sub> until V<sub>DRAIN</sub> crosses V<sub>HRREF</sub>:

- V<sub>OUT</sub> going UP up to CHx\_V<sub>DRAIN</sub> > V<sub>HRREF</sub>

The DC-DC converter block is always active regardless of how many channels are active (that is, even if all channels are OFF) to improve the load transient dynamic response.

The output voltage regulation can be enabled/disabled (OVRE bit) allowing the user to perform the optimization continuously or on demand.

In real applications, the spread of the forward voltage of the LEDs may lead the channels to have different headroom voltages; in any case, the leading channel (that is, the channel requiring the highest voltage to drive its LED string) is the one that determines the V<sub>OUT</sub> for all the strings.

The adaptive algorithm works properly if all the channels have an ON-time longer than 10  $\mu$ s. If at least one channel is set with an ON-time shorter but longer than 5  $\mu$ s, the adaptive loop can only rise the voltage, while if all the channels have an ON-time shorter than 5  $\mu$ s, the ALED7709x keep the V<sub>OUT</sub> constant, like having set the OVRE bit to 0.

OFF channels are kept out from the control algorithm, so the algorithm stays active up to when at least one channel is ON while enters in freeze mode if all the channels are OFF.

The reference voltage, provided by the internal DAC driven by the UP/DOWN counter, spans between the minimum and maximum values; as a consequence, the output voltage can be adjusted by the device in the following range:

$$V_{OUT,min} = \left(\frac{R_1 + R_2}{R_2}\right)^* V_{DAC,min}$$

(5)

$$V_{OUT, max} = \left(\frac{R_1 + R_2}{R_2}\right)^* V_{DAC, max}$$

(6)

Where  $R_1$  and  $R_2$  are the high-side and low-side resistors of the divider connected to the output rail and  $V_{DAC}$  is the voltage expected at the VFB pin.

It must be ensured that V<sub>OUT,min</sub> and V<sub>OUT,max</sub> are below the minimum and above the maximum needed working output voltage to guarantee enough steering room for the optimization. In addition, the temperature of the LEDs significantly affects their forward voltage, which must be considered mainly when calculating the minimum expected output voltage.

The best way to proceed, when designing the external components, is to determine the output voltage range required by the LED strings, considering  $V_F$  spread and temperature variation:

$$V_{LED} = \max_{\substack{1 \le strings \le N}} \binom{m_{LEDS}}{\sum V_{F,j}}$$

(7)

calculate the output divider through the following equations:

$$\frac{V_{OUT, max}}{R_1 + R_2} \le 300 \,\mu A \tag{8}$$

The first is to choose the resistors to limit the current drawn from the output rail. Automotive applications could require a maximum resistance value (e.g., 100 k $\Omega$ ) for all setting resistors to avoid the risk of significant changes due to moisture. If for this reason, it is not possible to reach a current lower than 300  $\mu$ A, set R<sub>1</sub> to 100 k $\Omega$  and calculate R<sub>2</sub>:

$$R_2 = \frac{V_{DAC}}{V_{OUT} - V_{DAC}} \cdot R_1 \tag{9}$$

#### 7.7.4.1 Voltage optimization vs. PWM and phase shift

Adaptive control takes care of the information on each active channel  $V_{DRAIN}$ . Disabled channels or channels temporarily in the "OFF" phase, because of PWM control, must be excluded from the  $V_{DRAIN}$  MIN evaluation. The Phase Shift option further complicates the scenario for the final  $V_{DRAIN}$  MIN selection.

In practice, the  $V_{DRAIN}$  MIN selector algorithm before taking the decision to move DOWN must verify the status of all the channels, even if they are not active at the same time; otherwise, the risk is to generate oscillations on  $V_{OUT}$  adjustment.

While if an UP action is required by a channel, it is immediately executed to get out as quick as possible from any channel suffering condition, which could bring the  $I_{LED}$  current out of control.

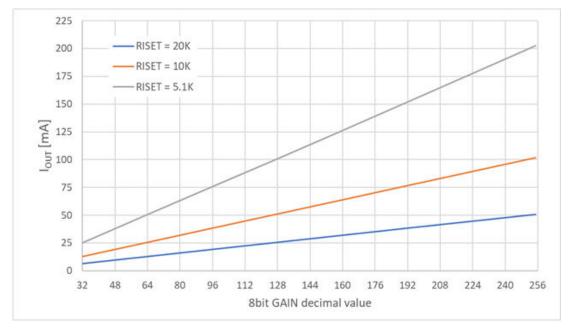

# 7.8 Current generators

The LED-driving section consists of four current generators connected to the internal control logic. The channels can sustain up to 40 V and sink up to 200 mA each.

The brightness of the LEDs connected to the ALED7709x is controlled by:

- PWM modulation, performed independently on each channel (local digital dimming) or on all channels as a group (global digital dimming).

- Current level regulated independently on each channel (local analog dimming) or on all channels as a group (global analog dimming).

The full-scale current level is set by the resistor connected between the I<sub>SET</sub> pin and ground.

$$I_{OUT, max} = \frac{V_{Iset}}{R_{Iset}} K_{GAIN}$$

(10)

Where  $V_{Iset} = 1 V$  and  $K_{GAIN} = 1022$  typ.

The current generators of the ALED7709x have been designed to be grouped (that is, connected in parallel) if required by the application. For stability reasons, the parallelization of the current generators should be done when the programmed current per channel is above 50% of  $I_{OUT}$  set by  $R_{lset}$ .

The current accuracy among different devices typically is better than ±2% at 100 mA.

To obtain better performances, it is suggested to work with I<sub>OUT</sub> current above 25 mA.

#### Figure 11. I<sub>OUT</sub> linearity with GAIN at different R<sub>ISET</sub>

Unused channels must be disabled through the internal CHSEL register to remove them from the adaptive algorithm.

During operation, a channel left floating and not disabled results in an open-channel faulty condition. This condition can be self-fixed by ALED7709x if the auto-disconnection on the open fault bit has been set.

While a channel connected to ground is recognized during the initial fault check procedure, once detected, and notified, the only way to proceed toward normal operation is to act on the CLRF bit and after setting the DEN bit to release the ALED7709x from standby. As described for a floating channel, if a grounded channel is not disabled it results in an open-channel faulty condition.

The POR configuration of the ALED7709B allows unused channels to be left floating; once in operation the floating channels are recognized as OPEN and auto-disconnected, removing them from the adaptive algorithm.

#### 7.8.1 Local dimming

In local dimming, each LED string is independently controlled by a dedicated PWM and current setting. The output current level of each channel can be adjusted through the "GAINx" register, while the "PWMx" register is used to define the digital dimming.

The PWM frequency and output control are set by the appropriate register value and are applied to all the channels.

Local dimming is fully adjustable only with I<sup>2</sup>C control and can be achieved in user mode only, where GAINx and PWMx registers are independently adjustable.

#### 7.8.2 Global dimming

In global dimming mode all the LED strings are driven at the same brightness value, by either PWMI or I<sup>2</sup>C registers, depending on the Reg-PWMI bit setting.

The PWM dimming frequency is achieved changing the configuration (number of active bits) of the internal 16-bit counter; with this method the PWM step resolution is not related to the selected PWM frequency but depends only on the used clock; for ALED7709x the step resolution is 152.6 ns, due to the internal clock set at a target value of 6.5536 MHz.

Controlling the device with PWMI signal, the frequency can either follow exactly the PWMI signal or readjust to a predefined frequency as explained later, depending on the PWMI\_direct bit setting.

Global dimming allows either user mode or mixed dimming mode.

In user mode the analog current and PWM values are unique for all the outputs; "GAIN1" and "PWM1" registers become the used reference and can be freely written by the user.

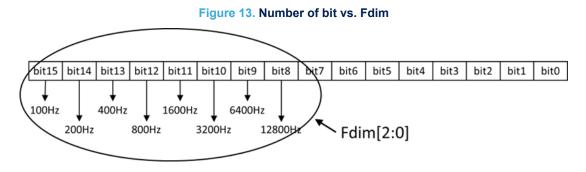

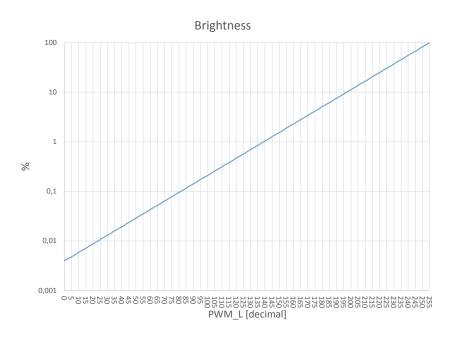

Mixed dimming mode combines both PWM and analog current control providing one optimal way to drive LEDs. At higher brightness the dimming is performed controlling only the constant-current; on the contrary, at lower brightness the dimming is performed acting on PWM duty-cycle.

This way to control the LED helps to improve the overall system efficiency (lower  $V_F$  requires also lower  $V_{OUT}$ ), increase the dimming ratio (respect to a single dimming mode) and reduce EMI (PWM works at lower current value).

Each time mixed dimming mode is active, the analog and PWM values are computed by ALED7709x starting from the brightness value coming from PWMI or the register. The result of such a calculation is readable by the user in the read only registers:  $PWM(H/L)_STS$  and  $GAIN_STS$ .

## 7.8.3 Output control setting

ALED7709x implement a couple of methods to control the LED current peak taken from V<sub>OUT</sub>.

One way is to control the speed of output switching ON/OFF; there is the possibility to select an appropriate rise/ fall time through the bits OCS[1:0] in register OUTCFG, which allows 4 different configurations:

| OCS[1:0] | Rise/fall time        |

|----------|-----------------------|

| 00       | Nominal (100 ns typ.) |

| 01       | 2xNom                 |

| 10       | 4xNom                 |

| 11       | 8xNom                 |

#### Table 11. Output control setting configuration

The second way to control the current peak is to avoid the switching ON of all the channels simultaneously. This also reduces the ripple on the  $V_{OUT}$  allowing a smaller value of the filter capacitor; a smaller ripple helps in avoiding audible noise coming from ceramic capacitors.

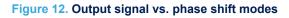

The phase shift can be selected through the bits PSE[1:0] in register OUTCFG and has four different working modes as reported in the following table:

#### Table 12. Phase shift mode configuration

| PSE[1:0] | Phase shift mode           |

|----------|----------------------------|

| 00       | OFF                        |

| 01       | 64 clock staggered delay   |

| 10       | 1&2 – 3&4 180° phase shift |

| 11       | 90° phase shift            |

## 7.9 Clock generation

The internal oscillator at 6.55 MHz is used for clocking all the internal digital blocks and to control internal timings also for analog parts.

A spread spectrum modulation can be enabled/disabled on main clock through DCLK\_DIS bit; the depth of the modulation can be adjusted by properly setting DCLKMS[1:0] in BOOSTCFG register, while the modulation speed is fixed to F<sub>CLK</sub>/127.