### SIDACtor<sup>®</sup> Protection Thyristors Broadband Optimized<sup>™</sup> Protection

## DSLP Series - SOT23-6

### **Agency Approvals**

| Agency    | Agency File Number |

|-----------|--------------------|

| <b>91</b> | E133083            |

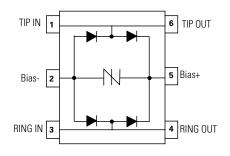

### **Pinout Designation & Schematic Symbol**

### Description

This new DSLP Series provides overvoltage protection for applications such as HD-SDI, HD-CVBS, ADSL, ADSL2, ADSL2+, VDSL2, Vplus (35b), and G.fast with minimal effect on data signals. This silicon design innovation results in a capacitive loading characteristic that is compatible with these high bandwidth applications.

These components adopt the patent granted EpiSCR silicon crowbar technology and industry popular cost competitive SOT23-6 package with flow-through lead frame design.

There are various  $V_{\text{DRM}}$  options available in this series. This technology provides a better surge capability than traditional clamping silicon technology. This reduces the possibility of field failures caused by A.C. power fault and multiple transient surges or lightning without compromising the signal integrity particularly at high data rate.

### Features & Benefits

- Compatible with ADSL, ADSL2+, VDSL2, VDSL2+ (35.328MHz, VDSL2 35b profile) and G.fast (both 106MHz & 212MHz)

- Balanced voltage protection

- Superior surge capability of of 30 A min, 35 A typ @ 8/20µs, 15 A typ @ 5/310 µs

- Fast response time

- Wide variety V<sub>DRM</sub> options for precise protection level needs

### Applicable Global Standards

• IEC 61000-4-5 2nd edition, 30 A min (tp = 8/20)

| <ul> <li>Ultra low capacitance</li> </ul> |

|-------------------------------------------|

| characteristic provides                   |

| low insertion loss and less               |

| distortion particularly in                |

| higher data rate signals                  |

RoHS W PO

- RoHS Compliant

- Flow-though pin assignment and layout ideal for high data rate

- Pb-free E3 means 2<sup>nd</sup> level interconnect is Pb-free and the terminal finish material is tin(Sn) (IPC/ JEDEC J-STD-609A.01)

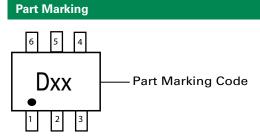

| Part Number      | Marking | V <sub>DRM</sub> @<br>I <sub>DRM</sub> =100nA | I <sub>r</sub><br>@V <sub>drm</sub> | V <sub>s</sub> @100V/µs | I <sub>H</sub> | I <sub>s</sub> | Capacita<br>f=1MHz | nce @<br>,2V bias |

|------------------|---------|-----------------------------------------------|-------------------------------------|-------------------------|----------------|----------------|--------------------|-------------------|

|                  |         | V min                                         | pA typ                              | V max                   | mA typ         | mA min         | pF typ             | pF max            |

| DSLP0080T023G6RP | D08     | 8                                             | 300                                 | 18                      | 40             | 10             | 1.3                | 2.5               |

| DSLP0120T023G6RP | D12     | 12                                            | 300                                 | 22                      | 40             | 10             | 1.3                | 2.5               |

| DSLP0180T023G6RP | D18     | 18                                            | 300                                 | 28                      | 40             | 10             | 1.3                | 2.5               |

| DSLP0240T023G6RP | D24     | 24                                            | 300                                 | 34                      | 40             | 10             | 1.3                | 2.5               |

| DSLP0360T023G6RP | D36     | 36                                            | 300                                 | 48                      | 40             | 10             | 1.3                | 2.5               |

### Electrical Characteristics between pin 1 and pin 3, Ta = 25°C

### **Surge Ratings**

|        | I <sub>PP</sub> |                                       |                                           |  |

|--------|-----------------|---------------------------------------|-------------------------------------------|--|

| Series |                 | /20 <sup>1</sup><br>2/50 <sup>2</sup> | 5/310 <sup>1</sup><br>10/700 <sup>2</sup> |  |

|        | A min           | A typ                                 | A typ                                     |  |

| G      | 30              | 35                                    | 15                                        |  |

#### Notes:

- 1 Current waveform in  $\mu s$

- 2 Voltage waveform in µs

- Peak pulse current ratio  $(I_{pp})$  is repetitive and guaranteed for the life of the product that remains in thermal equilibrium.

- The component must be in thermal equilibrium at 25°C.

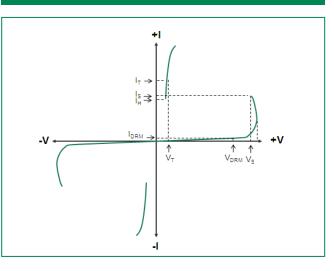

### **V-I: Characteristics**

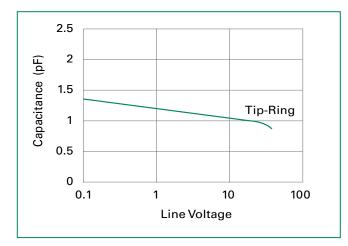

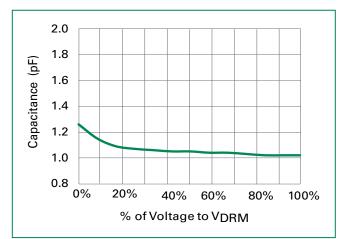

### Capacitance vs. Voltage

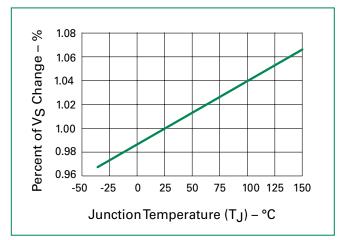

### Normalized V<sub>s</sub> Change vs. Junction Temperature

© 2016 Littelfuse, Inc. Specifications are subject to change without notice Revised: 02/16/18

# Typical capacitance against line voltage (without external bias)

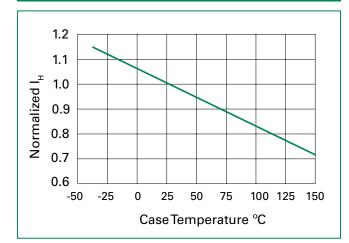

### Normalized Holding Current vs. Case Temperature

### Thermal Information

| Parameter                                | Value      | Unit |

|------------------------------------------|------------|------|

| Storage Temperature Range                | -55 to 150 | °C   |

| Maximum Junction Temperature             | 150        | °C   |

| Maximum Lead Temperature (Soldering 10s) | 260        | C°   |

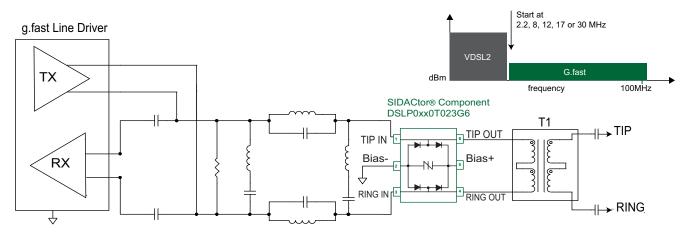

### Application example - G.fas Protection

G.fast has a targeted data rate of 1Gbps over 100 m of single twisted pair (24 AWG/0.5 mm) cable using DSL-like technology. This TDD (Time Division Duplex) signaling is a major difference from the existing FDD (Frequency Division Duplex) DSL signaling. G.fast bandwidth will extend up to 106 MHz (with the potential of going as high as 212 MHz) with the start frequency ranging from 2.2 MHz up to 30 MHz in an effort to avoid interference with existing xDSL services. G.fast may also employ "notching" where it suppresses carriers at specific individual frequencies to avoid clashing with local RF services.

### About G.fast

The G.fast amplitude is very low as compared to existing xDSL services and thus the varying voltage across the SIDACtor® component is very low. This results in imperceptible capacitance variance of the over voltage protection (OVP) component; therefore a bias voltage on pins 2 & 5 is not required in most applications, but pin 2 can be connected to the G.fast driver ground reference to provide longitudinal protection along with the differential protection mode. Rate and reach testing has shown an acceptable loss of less than 0.2dB with the DSLP0xx0T023G6RP component included at the tertiary position. Additionally, the flow-through layout of this component reduces the impedance mismatching "stub-effect" caused by non-"flow-through" PCB trace connections and provides for an easier PCB design. The small SOT23-6 footprint conserves valuable PCB real-estate space requriements.

Since this interface is capacitively coupled, no fusing is required for power fault protection, however; selection of appropriately voltage rated capacitors must be considered regarding lightning exposure risks. The coupling transformer should have an isolation rating of at least 1.5kV 50/60Hz and consideration of its lightning response characteristics must also be considered. The  $I_{pp}$  8/20 surge rating of this DSLP0xx0T023G6RP series is 30A minimally with a typical  $I_{pp}$  rating of 35A based on this waveshape. This should be sufficient for even the most severe exposure G.fast applications (including GR-1089 Issue 6 interbuilding requirements and ITU K20/21/45 Enhanced external line recommendations). The "Bias -" lead can be connected to the line driver ground with the "Bias +" lead left open so this solution provides both differential and common mode protection. Both "Bias -" and "Bias +" leads can be left floating for differential only protection and finally for capacitance variance sensitive applications, the "Bias -" and "Bias +" leads may have the appropriate polarity voltage (<  $V_{DRM}$ ) applied to further minimize any negative capacitance effects.

The higher  $V_{DRM}$  components in this DSLP series can be considered for ADSL, ADSL2, VDSL2, and VDSL2+ applications where the signal levels are much higher than the G.fast signals. The low off-state capacitance (>2pF max) and the flow-through compatible SOT23-6 footprint properties of this series is also beneficial for these other xDSL applications.

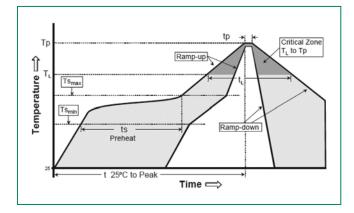

### **Soldering Parameters**

| Reflow Co                                  | Pb-Free assembly                                       |               |  |

|--------------------------------------------|--------------------------------------------------------|---------------|--|

|                                            | -Temperature Min (T <sub>s(min)</sub> )                | 150°C         |  |

| Pre Heat                                   | -Temperature Max (T <sub>s(max)</sub> )                | 200°C         |  |

|                                            | -Time (Min to Max) (t <sub>s</sub> )                   | 60-180 secs.  |  |

| Average ration to peak)                    | Average ramp up rate (Liquidus Temp ( $T_L$ ) to peak) |               |  |

| T <sub>S(max)</sub> to T <sub>I</sub>      | - Ramp-up Rate                                         | 3°C/sec. Max. |  |

| Deflect                                    | -Temperature (T <sub>L</sub> ) (Liquidus)              | +217°C        |  |

| Reflow                                     | -Temperature (t <sub>L</sub> )                         | 60-150 secs.  |  |

| PeakTemp                                   | 250(+0/-5)°C                                           |               |  |

| Time within 5°C of actual PeakTemp $(t_p)$ |                                                        | 20-40 secs.   |  |

| Ramp-down Rate                             |                                                        | 6°C/sec. Max. |  |

| Time 25°C                                  | 8 min. Max.                                            |               |  |

| Do not ex                                  | 260°C                                                  |               |  |

### **Physical Specifications**

| Lead Plating       | Matte Tin                                                 |  |

|--------------------|-----------------------------------------------------------|--|

| Lead Material      | Copper Alloy                                              |  |

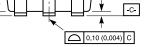

| Lead Coplanarity   | 0.0004 inches (0.102mm)                                   |  |

| Subsitute Material | Silicon                                                   |  |

| Body Material      | Molded Compound                                           |  |

| Flammability       | UL Recognized compound meeting<br>flammability rating V-0 |  |

| Notoo:             |                                                           |  |

1. All dimensions are in millimeters.

2. Dimensions include solder plating.

Dimension since solutive of mold flash & metal burr.

All specifications comply to JEDEC MO-178

Blo is facing up for mold and facing down for trim/form, i.e. reverse trim/form.

6. Package surface matte tine

| Packing Options |               |          |  |

|-----------------|---------------|----------|--|

| PackageType     | Description   | Quantity |  |

| SOT23-6         | Tape and Reel | 3000     |  |

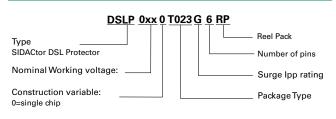

### **Part Numbering**

### **High Reliability Test Specification**

| Pre-condition<br>(HTRB/TC/ PCT/<br>H3TRB) | <ol> <li>Bake 24hrs @150°C</li> <li>168hrs @85% RH and 85°C</li> <li>I<sub>R</sub> reflow,3 reflows, peak temperature of 260°C</li> </ol> |  |  |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| HTRB                                      | JESD 22-108<br>V <sub>cc</sub> bias= 80%V <sub>DRM</sub> &T <sub>A</sub> =150°C, 1008hrs                                                  |  |  |

| Temperature Cycling                       | MIL-STD-883, Method 1010.8 Condition C<br>-65°C to150°C, 1000 cycles                                                                      |  |  |

| Pressure Cooker                           | JEDEC 22-A102<br>100%RH @121°C @15psi, 96hrs                                                                                              |  |  |

| Bias Humidity<br>(H3TRB)                  | JESD 22-A101<br>Vcc bias (pin1to pin3)=V <sub>DRM</sub> ,85%RH, 85°C , 1008<br>hours                                                      |  |  |

| RSH                                       | JESD 22-A111<br>260°C ,10 secs.                                                                                                           |  |  |

© 2016 Littelfuse, Inc. Specifications are subject to change without notice. . Revised: 02/16/18

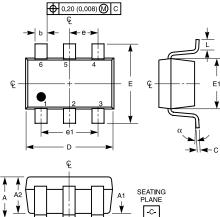

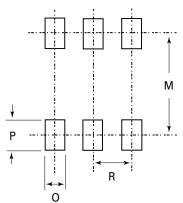

### **Dimensions - SOT23-6**

Recommended Solder Pad Layout

| Dimensions     | Inc   | hes   | Millin | neters |

|----------------|-------|-------|--------|--------|

| Dimensions     | Min   | Max   | Min    | Max    |

| А              | -     | 0.057 | -      | 1.450  |

| A1             | -     | 0.006 | -      | 0.150  |

| A2             | -     | 0.051 | -      | 1.300  |

| b              | 0.014 | 0.020 | 0.350  | 0.508  |

| С              | 0.004 | 0.008 | 0.090  | 0.200  |

| D              | 0.110 | 0.118 | 2.800  | 3.000  |

| E              | 0.102 | 0.118 | 2.600  | 3.000  |

| E1             | 0.057 | 0.069 | 1.450  | 1.750  |

| е              | -     | 0.037 | -      | 0.950  |

| e1             | -     | 0.075 | -      | 1.900  |

| L (note 4 & 5) | 0.004 | 0.023 | 0.100  | 0.600  |

| N (note 6)     | 6     | 3     | 6      |        |

| α              | 0°C   | 10°C  | 0°C    | 10°C   |

| Μ              | -     | 0.102 | -      | 2.590  |

| 0              | -     | 0.027 | -      | 0.690  |

| Р              | -     | 0.039 | -      | 0.990  |

| R              | -     | 0.038 | -      | 0.950  |

Notes:

1. Dimensioning and tolearances per ANSI 14.5M-1982.

2. Package conforms to EIAJ SC-74 (1992)

3. Dimensions D and E1 are exclusive of mold flash, protrusions, or gate burrs.

4. Foot lenth L measured at reference to seatng plane.

5. "L" is the length of flat foot surface for soldering to substrate.

6. "N" is the number of terminal positions.

7. Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily

#### **Embossed Carrier Tape & Reel Specification - SOT23-6** ▲ 4.0mm ▲ 2.0mm 14.4mm ACCESS HOLE 1.75mm DIA. HOLE Ç 🌢 13mm 60mm -GENERAL INFORMATION í ۵` 180mm 1. 3000 PIECES PER REEL. 2. ORDER IN MULTIPLES OF FULL REELS ONLY. 3. MEETS EIA-481 REVISION "A" SPECIFICATIONS. ¥ SOT-23 (8mm POCKET PITCH) Ο Ο Ο Ο 000 0 8.4mm 0.01 1<u>.</u> **h**ر USER DIRECTION OF FEED COVER TAPE

**Disclaimer Notice** - Information furnished is believed to be accurate and reliable. However, users should independently evaluate the suitability of and test each product selected for their own applications. Littlefuse products are not designed for, and may not be used in, all applications. Read complete Disclaimer Notice at <u>www.littlefuse.com/disclaimer-electronics</u>.

© 2016 Littelfuse, Inc.

Specifications are subject to change without notice. Revised: 02/16/18