### EN55022B Compliant 40V, Dual 4A or Single 8A Step-Down or 50W Inverting µModule Regulator

### **FEATURES**

- Dual 4A/Single 8A Low EMI Switch Mode Power Supply

- **EN55022 Class B Compliant**

- Two Fully Independent Channels, Each Configurable for Positive or Negative Output Voltage Polarity

- Output Voltage Range:  $0.5V \le |V_{OUT}n^+ V_{OUT}n^-| \le 26.5V$

- Wide Input Voltage Range: Up to 40V

- 3.1V or 3.6V Start-Up, Configuration-Dependent

- ±1.67% Total DC Output Voltage Error Over Line, **Load and Temperature**

- Analog Output Current Indicator (Positive-Vollt Only)

- LDO<sub>OUT</sub>: 5V Fixed, 25mA Capable LDO

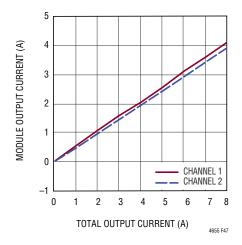

- Parallelable with LTM4651/LTM4653

- Constant-Frequency Current Mode Control

- Power Good Indicators and Programmable Soft-Start

- Overcurrent and Overtemperature Protection

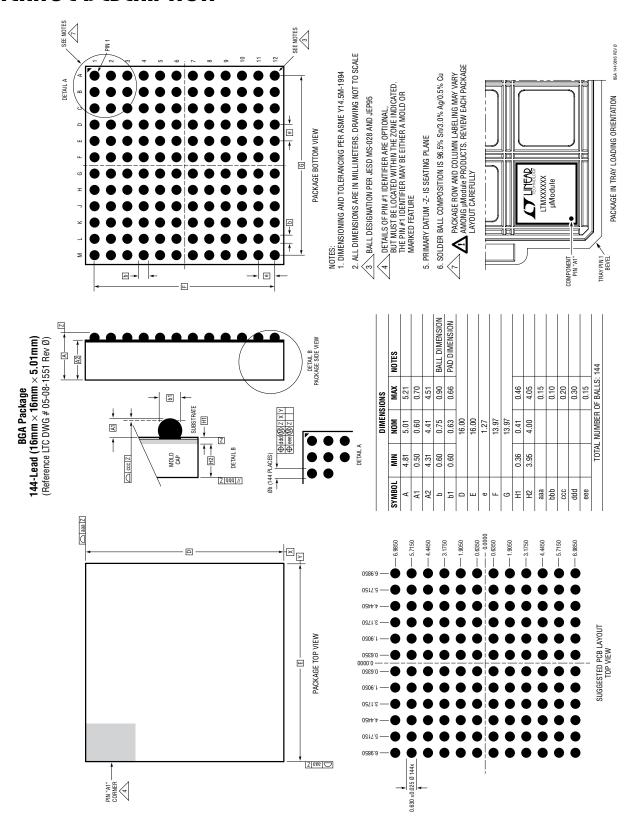

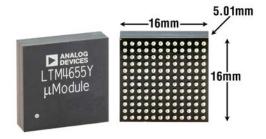

- 16mm × 16mm × 5.01mm BGA Package

### **APPLICATIONS**

- **Automated Test and Measurement**

- Avionics and Industrial Control Systems

- Video, Imaging and Instrumentation

### DESCRIPTION

The LTM<sup>®</sup>4655 is an ultralow noise 40V, dual 4A or single 8A DC/DC µModule® regulator designed to meet the radiated emissions requirements of EN55022. Its channels are fully independent, parallelable and capable of delivering positive or negative output polarity. Conducted emission requirements can be met by adding standard filter components. Included in the package are the switching controllers, power MOSFETs, inductors, filters and support components. A 5V, 25mA LDO and clock generator enable phase interleaving of the power switching stages. for improved EMC performance.

The LTM4655 can regulate positive  $V_{OUT}n^+$  voltages between 0.5V and 26.5V from a 3.1V to 40V input. The LTM4655 can regulate negative  $V_{OUTn}^-$  voltages between -0.5V and -26.5V from a maximum input range of 3.6V to 40V, with the span from  $V_{INn}$  to  $V_{OUTn}^-$  not to exceed 40V. A switching frequency range of 250kHz to 3MHz is supported.

The LTM4655 is offered in a 16mm × 16mm × 5.01mm BGA package with SnPb or RoHS compliant terminal finish.

All registered trademarks and trademarks are the property of their respective owners. Protected by U.S. Patents, including 5481178, 5705919, 5847554, 6580258

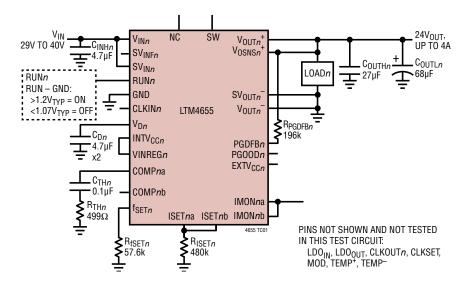

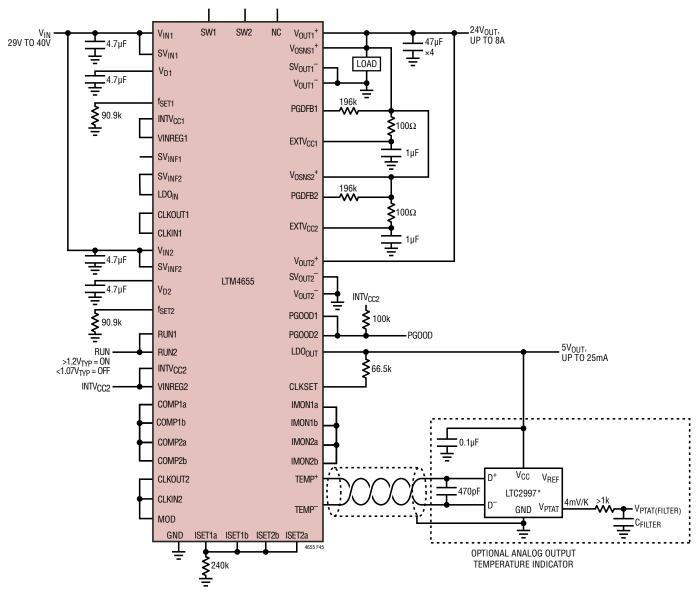

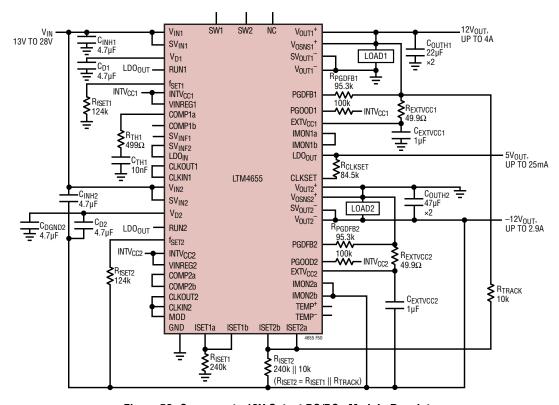

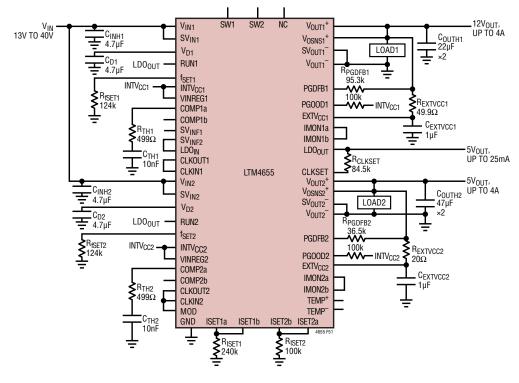

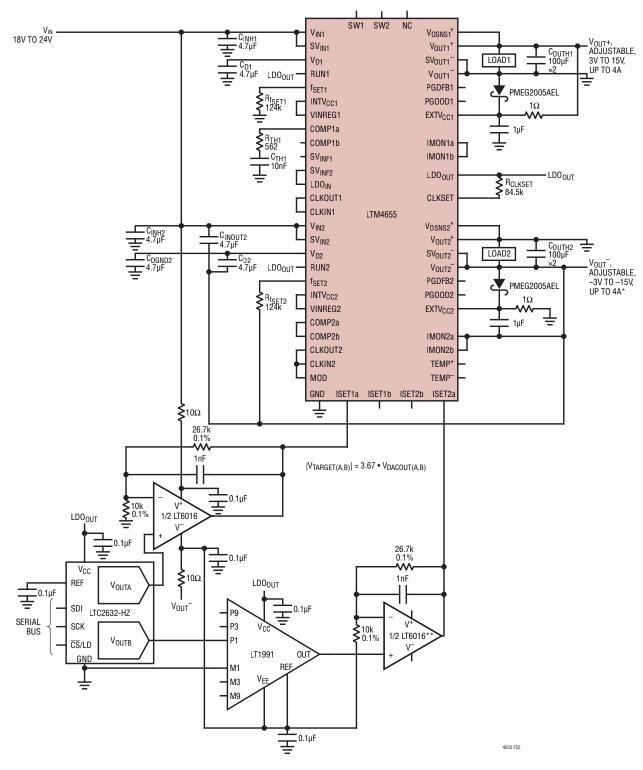

### TYPICAL APPLICATION

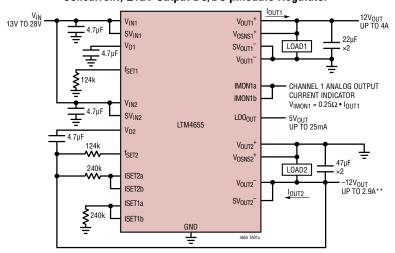

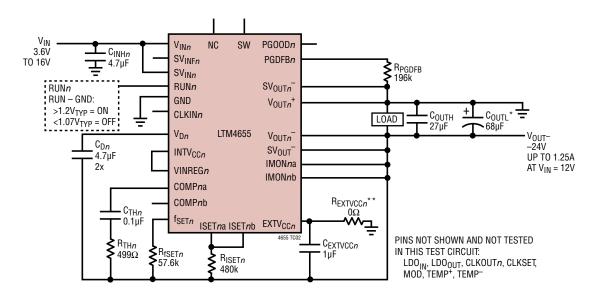

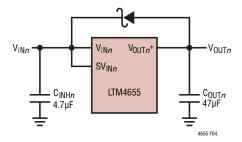

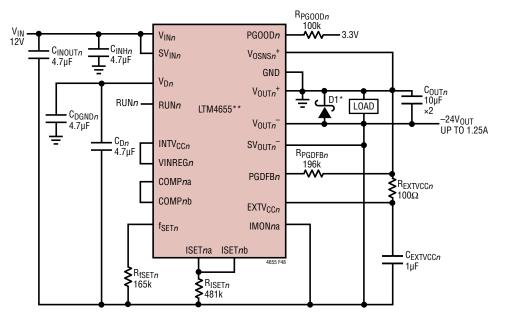

Concurrent, ±12V Output DC/DC µModule Regulator\*

FOR CHANNELS CONFIGURED TO REGULATE NEGATIVE V<sub>OUTD</sub>.: CURRENT LIMIT FREQUENCY-FOLDBACK INCEPTION IS A FUNCTION OF V<sub>IND</sub>. V<sub>OUTD</sub>., AND f<sub>SWD</sub>. CONTINUOUS OUTPUT CURRENT CAPABILITY IS SUBJECT TO DETAILS OF APPLICATION IMPLEMENTATION. SEE NOTES 2 AND 3 AND THE APPLICATIONS INFORMATION SECTION, FOR DETAILS.

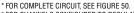

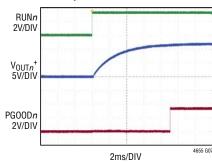

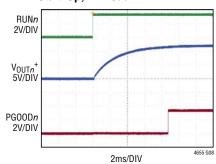

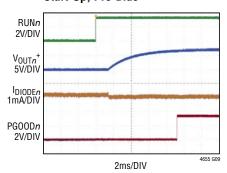

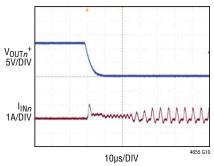

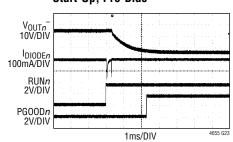

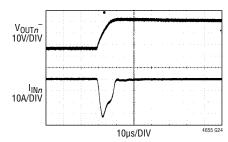

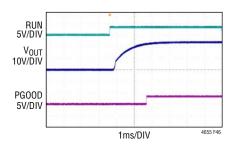

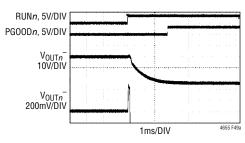

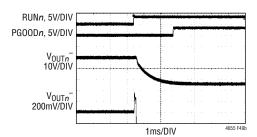

### **Output Voltage Start-Up Waveforms**

## LTM4655

### TABLE OF CONTENTS

| Features                                               | 1          |

|--------------------------------------------------------|------------|

| Applications                                           | 1          |

| Typical Application                                    |            |

| Description                                            | 1          |

| Absolute Maximum Ratings                               | 3          |

| Pin Configuration                                      | 3          |

| Order Information                                      |            |

| Electrical Characteristics                             |            |

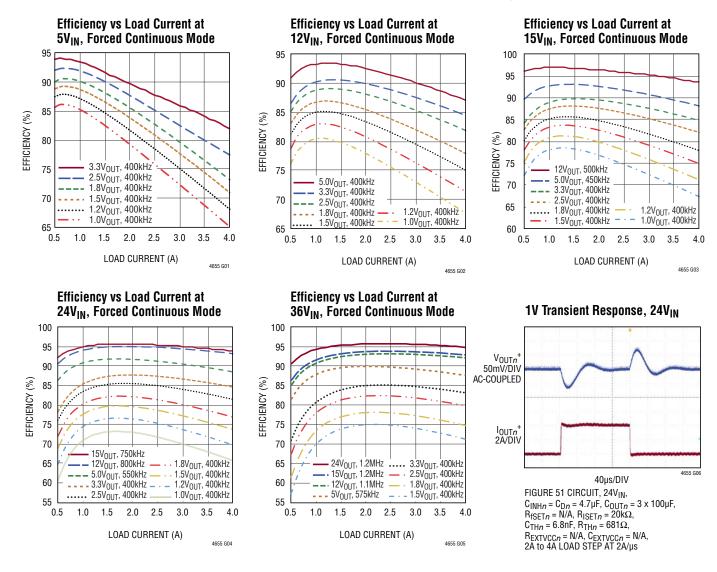

| Typical Performance Characteristics                    |            |

| Pin Functions                                          | 14         |

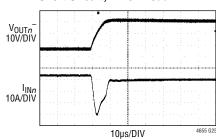

| Simplified Block Diagram                               | 21         |

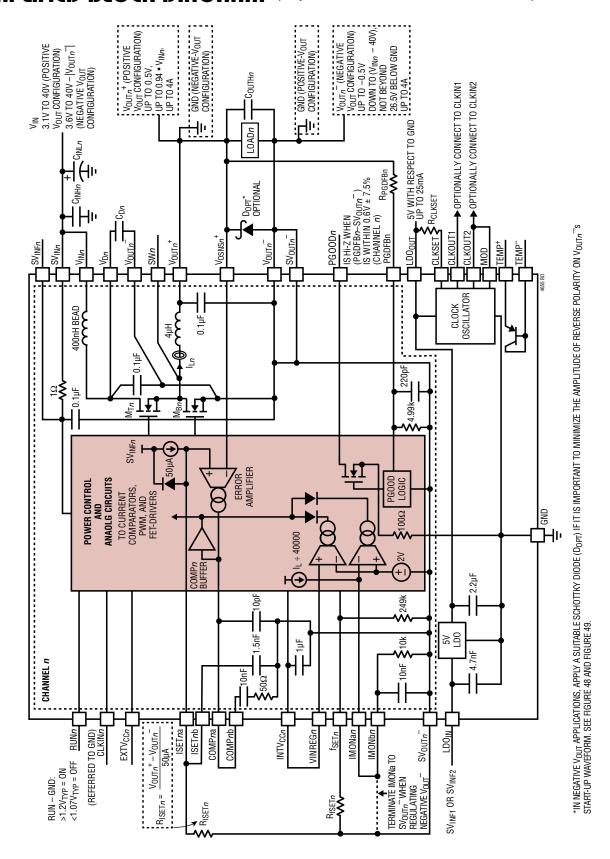

| Test Circuit                                           | 22         |

| Decoupling Requirements                                | 23         |

| Operation                                              | <b>2</b> 4 |

| Power Module Overview                                  |            |

| V <sub>IN</sub> to V <sub>OUT</sub> Conversion Ratios  |            |

| Input Capacitors, Positive-V <sub>OUT</sub> Operation  | 25         |

| Output Capacitors, Positive-V <sub>OUT</sub> Operation | 26         |

| Forced Continuous Operation                            | 26         |

| Output Voltage Programming, Tracking and               |            |

| Soft-Start                                             | 26         |

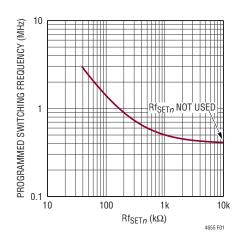

| Frequency Adjustment                                   | 27         |

| Applications information                                    | . 28 |

|-------------------------------------------------------------|------|

| Power Module Protection                                     | . 28 |

| RUN Pin Enable                                              | . 28 |

| Loop Compensation                                           | . 28 |

| Hot Plugging Safely                                         | . 29 |

| Input Disconnect/Input Short Considerations                 | . 29 |

| INTV <sub>CCn</sub> and EXTV <sub>CCn</sub> Connection      | . 29 |

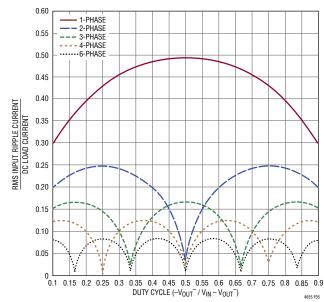

| Multiphase Operation                                        | .30  |

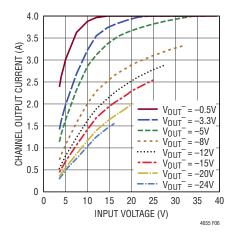

| Negative Output Current Capability Varies as a              |      |

| Function of $V_{INn}$ to $V_{OUTn}^-$ Conversion Ratios,    |      |

| Negative-V <sub>OUT</sub> Operation                         | . 31 |

| Input Capacitors, Negative-V <sub>OUT</sub> - Operation     |      |

| Output Capacitors, Negative-V <sub>OUT</sub> Operation      | . 33 |

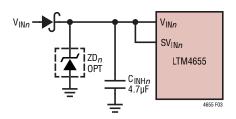

| Optional Diodes to Guard Against Overstress,                |      |

| Negative-V <sub>OUT</sub> Operation                         | .33  |

| Frequency Adjustment, Negative-V <sub>OUT</sub> Operation . | .34  |

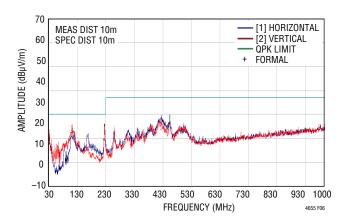

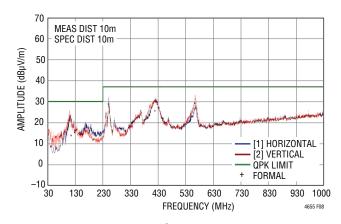

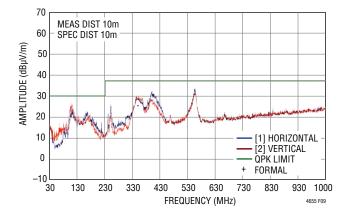

| Radiated EMI Noise                                          | .35  |

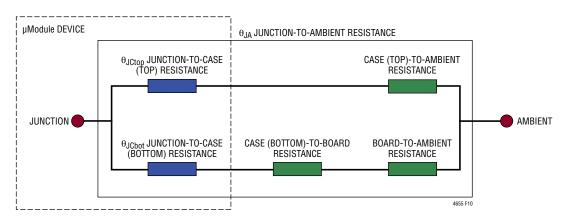

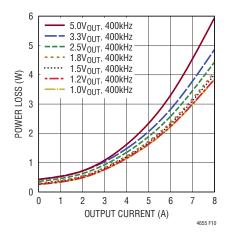

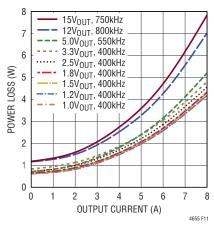

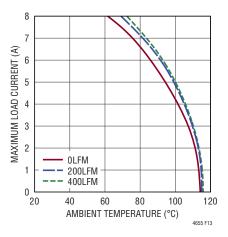

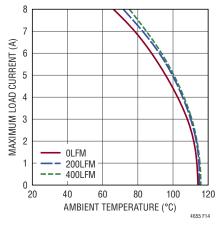

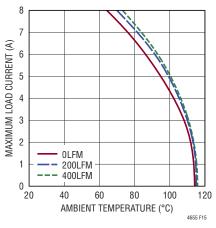

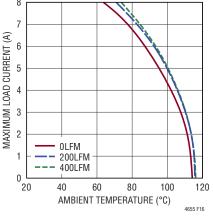

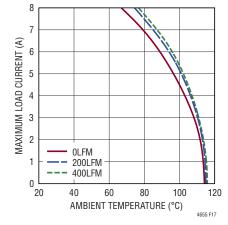

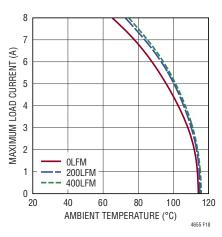

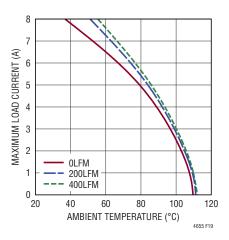

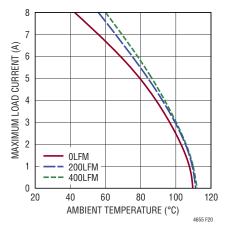

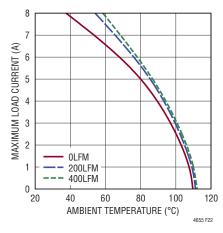

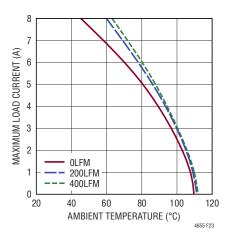

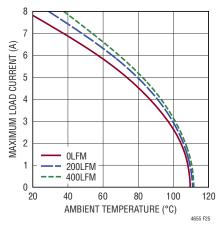

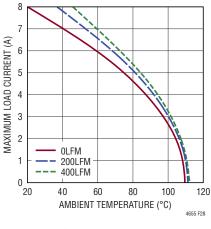

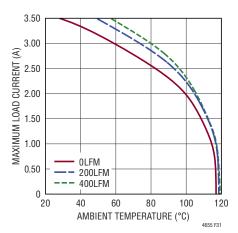

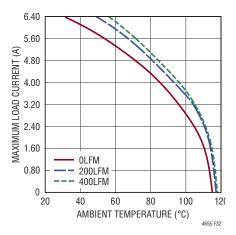

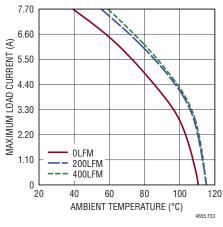

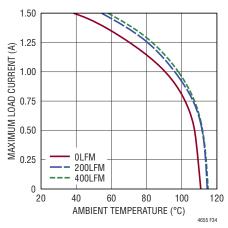

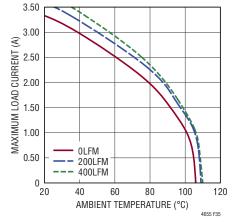

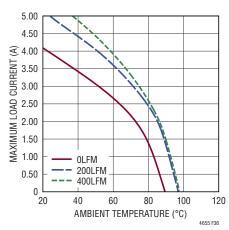

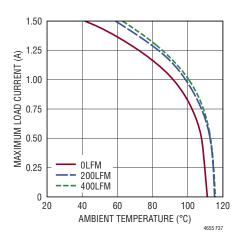

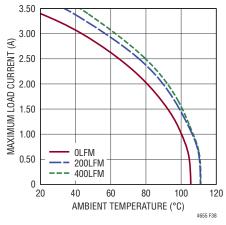

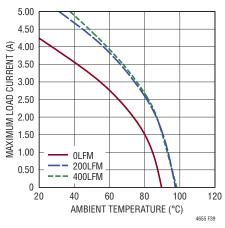

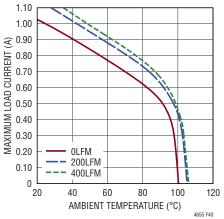

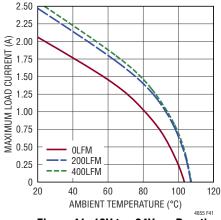

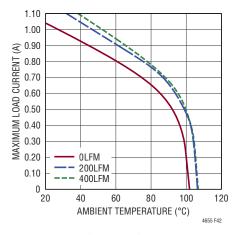

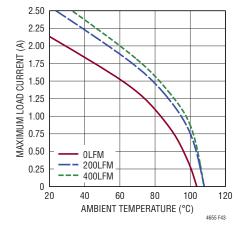

| Thermal Considerations and Output Current                   |      |

| Derating                                                    | .35  |

| Safety Considerations                                       |      |

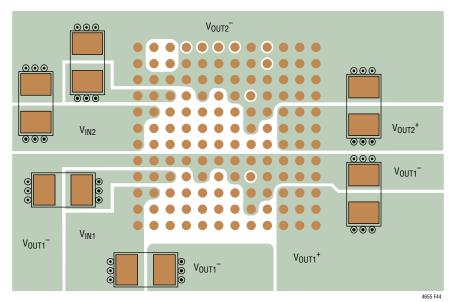

| Layout Checklist/Example                                    |      |

| ypical Applications                                         |      |

| Package Description                                         |      |

| Package Photograph                                          |      |

| Design Resources                                            |      |

| Palatad Darta                                               | E /  |

### **ABSOLUTE MAXIMUM RATINGS**

(Note 1 and Note 5)

# Channel 1 Terminal Voltages (All Channel 1 Terminal Voltages Relative to V<sub>0UT1</sub> Unless Otherwise Indicated)

| V <sub>IN1</sub> , V <sub>D1</sub> , SV <sub>IN1</sub> , SV <sub>INF1</sub> , SW | /10.3V to 42V                    |

|----------------------------------------------------------------------------------|----------------------------------|

| GND, EXTV <sub>CC1</sub> , V <sub>OUT1</sub> +, V <sub>OS</sub>                  | NS1 <sup>+</sup> ,               |

| ISET1a, ISET1b                                                                   | 0.3V to 28V                      |

| INTV <sub>CC1</sub> , PGDFB1, VINREG1                                            | , COMP1a,                        |

| IMON1a, IMON1b                                                                   | 0.3V to 4V                       |

| f <sub>SFT1</sub>                                                                | 0.3V to INTV <sub>CC1</sub>      |

| RUN1                                                                             | . GND-0.3V to $V_{OUT1}^- + 32V$ |

| PGOOD1, CLKIN1 (Relative                                                         | to GND)0.3V to 6V                |

|                                                                                  |                                  |

# Channel 2 Terminal Voltages (All Channel 2 Terminal Voltages Relative to V<sub>0UT2</sub> Unless Otherwise Indicated)

| ) 42V     |

|-----------|

|           |

| 28V       |

|           |

| to 4V     |

| $V_{CC2}$ |

| - 32V     |

| to 6V     |

|           |

# LDO and Clock Generator Voltages (All LDO and Clock Generator Terminal Voltages Relative to GND Unless Otherwise Indicated)

| LDO <sub>IN</sub> |                                   |

|-------------------|-----------------------------------|

| CLKSET, MOD       | 0.3V to LDO <sub>OUT</sub> + 0.3V |

#### Terminal Currents

| INTV <sub>CCn</sub> Peak Output Current | : (Note 10)30mA |

|-----------------------------------------|-----------------|

| TEMP <sup>+</sup>                       | –1mA to 10mA    |

| TEMP <sup>-</sup>                       | –10mA to 1mA    |

### Temperatures Internal Operating Temperature

| Range (Note 2 and Note 9)       |                     |

|---------------------------------|---------------------|

| E- and I-Grade                  | 40°C to 125°C       |

| MP-Grade                        | 55°C to 125°C       |

| Storage Temperature Range       | 55°C to 125°C       |

| Peak Package Body Temperature [ | Ourina Reflow 245°C |

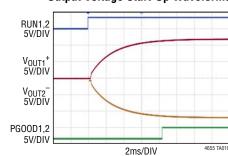

### PIN CONFIGURATION

\_ \_...

### ORDER INFORMATION

|                |                    | PART MARKING* |             | PACKAGE     | MSL | TEMPERATURE RANGE |

|----------------|--------------------|---------------|-------------|-------------|-----|-------------------|

| PART NUMBER    | PAD OR BALL FINISH | DEVICE        | FINISH CODE | 11101111011 |     | (SEE NOTE 2)      |

| LTM4655EY#PBF  | SAC305 (RoHS)      | LTM4655Y      | e1          | BGA         | 3   | -40°C to 125°C    |

| LTM4655IY#PBF  | SAC305 (RoHS)      | LTM4655Y      | e1          | BGA         | 3   | -40°C to 125°C    |

| LTM4655MPY#PBF | SAC305 (RoHS)      | LTM4655Y      | e1          | BGA         | 3   | –55°C to 125°C    |

| LTM4655IY      | SnPb (63/37)       | LTM4655Y      | e0          | BGA         | 3   | -40°C to 125°C    |

| LTM4655MPY     | SnPb (63/37)       | LTM4655Y      | e0          | BGA         | 3   | –55°C to 125°C    |

Contact the factory for parts specified with wider operating temperature ranges. \*Pad or ball finish code is per IPC/JEDEC J-STD-609.

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified internal operating temperature range (Note 2). Specified as each individual output channel (Note 5).  $T_A = 25^{\circ}C$ , Test Circuit 1 (positive- $V_{OUT}$ , noninverting step-down configuration with  $V_{OUT}_{n-} = GND$ ),  $V_{IN}_{n-} = SV_{IN}_{n-} = 36V$ , EXTV $_{CC}_{n-} = 24V$ , RUN $_{n-} = 3.3V$ ,  $R_{ISET}_{n-} = 480k$ ,  $R_{fSET}_{n-} = 57.6k\Omega$ ,  $f_{SW}_{n-} = 1.5MHz$  (CLKIN $_{n-}$  driven with 1.5MHz clock signal) and voltages referred to GND unless otherwise noted.

| SYMBOL                                            | PARAMETER                                                                                 | CONDITIONS                                                                                                                                                                                                                         |       | MIN        | TYP                | MAX        | UNITS             |

|---------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|--------------------|------------|-------------------|

| $SV_{INn(DC)}, V_{INn(DC)}$                       | Input DC Voltage in Positive-V <sub>OUT</sub><br>Configuration                            | $V_{OUTn}^- = GND$                                                                                                                                                                                                                 | •     | 3.1        |                    | 40         | V                 |

| $\overline{V_{\text{OUT}n(\text{RANGE})}^+}$      | Range of Positive Output Voltage<br>Regulation                                            | $0.5V \le ISET na-SV_{OUTn}^- \le 26.5V$ , $I_{OUTn}^+ = 0A$ (See Note 7)                                                                                                                                                          | •     | 0.5        |                    | 26.5       | V                 |

| V <sub>OUTn(24VDC)</sub> <sup>+</sup>             | Output Voltage Total Variation with Line and Load at V <sub>OUTn</sub> <sup>+</sup> = 24V | $29V \le V_{\text{IN}n} \le 40V$ , $0A \le I_{\text{OUT}n}^+ \le 4A$ , $C_{\text{INH}n} = 4.7 \mu\text{F}$ , $C_{\text{D}n} = 4.7 \mu\text{F}$ , $C_{\text{OUTH}n} = 2 \times 47 \mu\text{F}$ , CLKIN $n$ Driven with 1.5MHz Clock | •     | 23.6       | 24                 | 24.4       | V                 |

| V <sub>OUT</sub> n(0.5VDC) <sup>+</sup>           | Output Voltage Total Variation with Line and Load at $V_{OUT}n^+ = 0.5V$                  | Measuring $V_{OSNSn}^+$ to ISET $n$ a 3.1V $\leq V_{INn} \leq$ 13.2V, 0A $\leq I_{OUTn}^+ \leq$ 4A, $C_{INHn} =$ 4.7μF, $C_{Dn} =$ 4.7μF, $C_{OUTHn} =$ 2 $\times$ 47μF, ISET $n$ a = 500mV, $R_{fSETn} =$ N/U (Note 6)            | •     | -15        | 0                  | 15         | mV                |

| R <sub>SVINFn</sub>                               | Resistor Between SV <sub>INn</sub> and SV <sub>INFn</sub>                                 |                                                                                                                                                                                                                                    |       |            | 1                  |            | Ω                 |

| Input Specifications                              |                                                                                           |                                                                                                                                                                                                                                    |       |            |                    |            |                   |

| V <sub>INn(UVL0)</sub>                            | SV <sub>INn</sub> Undervoltage Lockout Threshold                                          | SV <sub>INn</sub> Rising<br>SV <sub>INn</sub> Falling<br>Hysteresis                                                                                                                                                                | • • • | 2.4<br>150 | 2.85<br>2.6<br>250 | 3.1<br>2.9 | V<br>V<br>mV      |

| INRUSH(VINn)                                      | Input Inrush Current at Start-Up                                                          | $C_{INHn}$ = 4.7 $\mu$ F, $C_{Dn}$ = 4.7 $\mu$ F, $C_{OUTHn}$ = 2 × 47 $\mu$ F; $I_{OUTn}$ <sup>+</sup> = 0A, ISET <i>n</i> a Electrically Connected to ISET <i>n</i> b                                                            |       |            | 300                |            | mA                |

| $I_{\mathbb{Q}(\mathbb{SVIN}n)}$                  | Input Supply Bias Current                                                                 | Shutdown, RUNn = GND<br>RUNn = 3.3V                                                                                                                                                                                                |       |            | 16<br>450          | 30         | μA<br>μA          |

| I <sub>S(VINn)</sub>                              | Input Supply Current                                                                      | CLKINn Open Circuit, I <sub>OUTn</sub> <sup>+</sup> = 4A                                                                                                                                                                           |       |            | 2.9                |            | А                 |

| I <sub>S(VIN<i>n</i>, SHUTDOWN)</sub>             | Input Supply Current in Shutdown                                                          | Shutdown, RUNn = GND                                                                                                                                                                                                               |       |            | 4                  |            | μА                |

| Output Specification                              | is                                                                                        |                                                                                                                                                                                                                                    |       |            |                    |            |                   |

| I <sub>OUT</sub> n <sup>+</sup>                   | V <sub>OUTn</sub> <sup>+</sup> Output Continuous Current<br>Range                         | (Note 3)                                                                                                                                                                                                                           |       | 0          |                    | 4          | A                 |

| $\frac{\Delta V_{OUTn(LINE)}^{+/}}{V_{OUTn}^{+}}$ | Line Regulation Accuracy                                                                  | $I_{OUTn}^+ = 0A, 29V \le V_{INn} \le 40V$                                                                                                                                                                                         | •     |            | 0.05               | 0.1        | %                 |

| $\Delta V_{OUTn(LOAD)}^{+/}$ $V_{OUTn}^{+}$       | Load Regulation Accuracy                                                                  | $V_{INn} = 36V, 0A \le I_{OUTn}^+ \le 4A$                                                                                                                                                                                          | •     |            | 0.05               | 0.75       | %                 |

| $V_{OUTn(AC)}^+$                                  | Output Voltage Ripple, V <sub>OUTn</sub> +                                                | $V_{INn} = 12V$ , ISET $na = 5V$                                                                                                                                                                                                   |       |            | 2                  |            | mV <sub>P-P</sub> |

Recommended LGA and BGA PCB Assembly and Manufacturing Procedures

<sup>•</sup> LGA and BGA Package and Tray Drawings

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified internal operating temperature range (Note 2). Specified as each individual output channel (Note 5).  $T_A = 25^{\circ}\text{C}$ , Test Circuit 1 (positive- $V_{0UTn}^+$ , noninverting step-down configuration with  $V_{0UTn}^- = \text{GND}$ ),  $V_{\text{IN}n} = \text{SV}_{\text{IN}n} = 36\text{V}$ , EXTV<sub>CCn</sub> = 24V, RUNn = 3.3V, R<sub>ISETn</sub> = 480k, R<sub>fSETn</sub><sup>+</sup> = 57.6kΩ, f<sub>SWn</sub> = 1.5MHz (CLKINn driven with 1.5MHz clock signal) and voltages referred to GND unless otherwise noted.

| SYMBOL                              | PARAMETER                                              | CONDITIONS                                                                                                                                                                                                                                                                                                                                     |   | MIN        | TYP               | MAX        | UNITS      |

|-------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------|-------------------|------------|------------|

| $\overline{f_{Sn}}$                 | V <sub>OUTn</sub> <sup>+</sup> Ripple Frequency        | R <sub>fSETn</sub> = 57.6k, CLKIN <i>n</i> Open Circuit                                                                                                                                                                                                                                                                                        | • | 1.7        | 1.95              | 2.2        | MHz        |

| $\Delta V_{OUTn(START)}^+$          | Turn-On Overshoot                                      |                                                                                                                                                                                                                                                                                                                                                |   |            | 8                 |            | m۷         |

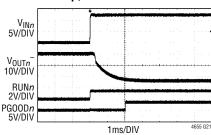

| t <sub>START</sub> ,                | Turn-On Start-Up Time                                  | Delay Measured from $V_{INn}$ Toggling from $0V$ to $36V$ to $PGOODn$ Exceeding $3V$ ; $PGOODn$ . Having a $100k\Omega$ Pull-Up to $3.3V$ with Respect to GND, $VPGFBn$ Resistor Divider Network as Shown in Test Circuit 1, $R_{ISETna} = 480k\Omega$ and $ISETna$ Electrically Connected to $ISETnb$ and $ISETnb$ Driven with $1.5MHz$ Clock | • |            | 4                 | 9          | ms         |

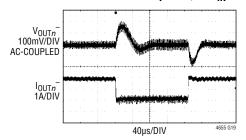

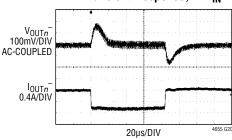

| $\Delta V_{OUTn(LS)}^+$             | Peak Output Voltage Deviation for<br>Dynamic Load Step | $I_{OUTn}^+$ : OA to 2A and 2A to 0A Load Steps in 1 $\mu$ s, $C_{OUTHn}$ = 47 $\mu$ F × 2                                                                                                                                                                                                                                                     |   |            | 400               |            | mV         |

| t <sub>SETTLE</sub> n               | Settling Time for Dynamic Load Step                    | $I_{OUTn}^+$ : OA to 2A and 2A to 0A Load Steps in 1 $\mu$ s, $C_{OUTHn}$ = 47 $\mu$ F × 2                                                                                                                                                                                                                                                     |   |            | 50                |            | μs         |

| I <sub>OUTn(OCL)</sub> <sup>+</sup> | I <sub>OUTn</sub> <sup>+</sup> Output Current Limit    |                                                                                                                                                                                                                                                                                                                                                |   |            | 5.5               |            | A          |

| <b>Control Section</b>              |                                                        |                                                                                                                                                                                                                                                                                                                                                |   |            |                   |            |            |

| I <sub>ISET<i>n</i>a</sub>          | Reference Current of ISET <i>n</i> a Pin               | $V_{ISETna} = 0.5V, 3.1V \le V_{INn} \le 13.2V$<br>$V_{ISETna} = 24V, 29V \le V_{INn} \le 40V$                                                                                                                                                                                                                                                 | • | 49.3<br>49 | 50<br>50          | 50.7<br>51 | μA<br>μA   |

| I <sub>VOSNS</sub> n <sup>+</sup>   | V <sub>OSNSn</sub> <sup>+</sup> Leakage Current        | $V_{VOSNSn}^+ = 28V$                                                                                                                                                                                                                                                                                                                           |   |            | 290               |            | μА         |

| $\overline{t_{ONn(MIN)}}$           | Minimum On-Time                                        | (Note 4)                                                                                                                                                                                                                                                                                                                                       |   |            | 60                |            | ns         |

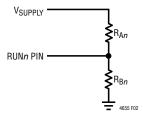

| V <sub>RUN</sub> n                  | RUN <i>n</i> Turn-On/-Off Thresholds                   | RUN <i>n</i> Input Turn-On Threshold, RUN <i>n</i> Rising RUN <i>n</i> Hysteresis                                                                                                                                                                                                                                                              | • | 1.08       | 1.2<br>130        | 1.32       | V<br>mV    |

| I <sub>RUNn</sub>                   | RUN <i>n</i> Leakage Current                           | RUN <i>n</i> = 3.3V                                                                                                                                                                                                                                                                                                                            | • |            | 0.1               | 50         | nA         |

| Oscillator and Pha                  | ase-Locked Loop (PLL)                                  |                                                                                                                                                                                                                                                                                                                                                |   |            |                   |            |            |

| f <sub>OSCn</sub>                   | Oscillator Frequency Accuracy                          | $V_{INn}$ = 12V, ISET $na$ = 5V, and:<br>$f_{SET}$ $n$ Open-Circuit<br>$R_{fSET}$ $n$ = 57.6k $\Omega$ (See $f_{SN}$ Specification)                                                                                                                                                                                                            | • | 360        | 400<br>1.95       | 440        | kHz<br>MHz |

| f <sub>SYNCn</sub>                  | PLL Synchronization Capture Range                      | $V_{INn}$ = 12V, ISET $na$ = 5V, CLKIN $_n$ Driven with a GND Referred Clock Toggling from 0.4V to 1.2V and Having a Clock Duty Cycle: From 10% to 90%; f <sub>SET<math>n</math></sub> Open Circuit From 40% to 60%; R <sub>fSET<math>n</math></sub> = 57.6k $\Omega$                                                                          |   | 250<br>1.3 |                   | 550<br>3   | kHz<br>MHz |

| V <sub>CLKIN</sub> n                | CLKIN <i>n</i> Input Threshold                         | V <sub>CLKINn</sub> Rising<br>V <sub>CLKINn</sub> Falling                                                                                                                                                                                                                                                                                      |   | 1.2        |                   | 0.4        | V          |

| I <sub>CLKINn</sub>                 | CLKINn Input Current                                   | $V_{\text{CLKIN}n} = 5V$<br>$V_{\text{CLKIN}n} = 0V$                                                                                                                                                                                                                                                                                           |   | -20        | 230<br><i>-</i> 5 | 500        | μA<br>μA   |

| Power Good Feed                     | back Input and Power Good Output                       |                                                                                                                                                                                                                                                                                                                                                |   |            |                   |            |            |

| OV <sub>PGDFB</sub> n               | Output Overvoltage PG00D <i>n</i> Upper<br>Threshold   | PGDFBn Rising                                                                                                                                                                                                                                                                                                                                  | • | 620        | 645               | 675        | mV         |

| UV <sub>PGDFB</sub> n               | Output Undervoltage PG00D <i>n</i> Lower Threshold     | PGDFB <i>n</i> Falling                                                                                                                                                                                                                                                                                                                         | • | 525        | 555               | 580        | m۷         |

| $\Delta V_{PGDFB}$                  | PG00Dn Hysteresis                                      | PGDFBn Returning                                                                                                                                                                                                                                                                                                                               |   |            | 8                 |            | m۷         |

| $R_{PGDFBn}$                        | Resistor Between PGDFB1n and SV <sub>OUTn</sub>        |                                                                                                                                                                                                                                                                                                                                                |   | 4.94       | 4.99              | 5.04       | kΩ         |

| R <sub>PGOOD</sub> n                | PGOOD <i>n</i> Pull-Down Resistance                    | V <sub>PGOODn</sub> = 0.1V, V <sub>PGDFBn</sub> < UV <sub>PGDFBn</sub> or V <sub>PGDFBn</sub> > OV <sub>PGDFBn</sub>                                                                                                                                                                                                                           |   |            | 700               | 1500       | Ω          |

| I <sub>PGOOD</sub> n(LEAK)          | PGOOD <i>n</i> Leakage Current                         | $V_{PGOODn} = 3.3V$ , $UV_{PGDFBn} < V_{PGDFBn} < OV_{PGDFBn}$                                                                                                                                                                                                                                                                                 |   |            | 0.1               | 1          | μА         |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified internal operating temperature range (Note 2). Specified as each individual output channel (Note 5).  $T_A = 25^{\circ}C$ , Test Circuit 1 (positive- $V_{0UTn}^+$ , noninverting step-down configuration with  $V_{0UTn}^- = GND$ ),  $V_{INn} = SV_{INn} = 36V$ , EXTV<sub>CCn</sub> = 24V, RUNn = 3.3V,  $R_{ISETn} = 480k$ ,  $R_{fSETn}^+ = 57.6k\Omega$ ,  $f_{SWn} = 1.5$ MHz (CLKINn driven with 1.5MHz clock signal) and voltages referred to GND unless otherwise noted.

| SYMBOL                                         | PARAMETER                                                                                             | CONDITIONS                                                                                                                 |   | MIN          | TYP                                            | MAX          | UNITS  |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---|--------------|------------------------------------------------|--------------|--------|

| t <sub>PGOOD</sub> n(DELAY)                    | PGOOD <i>n</i> Delay                                                                                  | PGOOD <i>n</i> Low to High (Note 4)<br>PGOOD <i>n</i> High to Low (Note 4)                                                 |   |              | 16/f <sub>SW(Hz</sub><br>64/f <sub>SW(Hz</sub> | )<br>)       | S<br>S |

| <b>Current Monitor an</b>                      | d Input Voltage Regulation Pins                                                                       |                                                                                                                            |   |              |                                                |              |        |

| h <sub>IMON<i>n</i>a</sub>                     | I <sub>OUT</sub> n <sup>+/I</sup> IMONna                                                              | Ratio of $V_{OUTn}^+$ Output Current to $I_{IMONna}$<br>Current, $I_{OUTn}^+ = 4A$                                         | • | 36           | 40                                             | 44           | k      |

| I <sub>OSn(IMON)</sub>                         | I <sub>IMONna</sub> Offset Current                                                                    | $I_{\text{IMON}na}$ at $I_{\text{OUT}n}^+ = 0A$                                                                            |   | <b>-</b> 5   |                                                | 5            | μA     |

| IMONnb Resistor                                | Resistor Between IMONnb and SV <sub>OUTn</sub>                                                        |                                                                                                                            |   | 9.8          | 10                                             | 10.2         | kΩ     |

| $V_{\text{IMON}na}$                            | IMONna Servo Voltage                                                                                  | IMON <i>n</i> a Voltage During Output Current<br>Regulation                                                                | • | 1.9          | 2.0                                            | 2.1          | V      |

| $V_{VINREG}$                                   | V <sub>INREGn</sub> Servo Voltage                                                                     | VINREG <i>n</i> Voltage During Output Current Regulation                                                                   | • | 1.8          | 2.0                                            | 2.2          | V      |

| I <sub>VINREG</sub> n                          | V <sub>INREGn</sub> Leakage Current                                                                   | VINREGn = 2V                                                                                                               |   |              | 1                                              |              | nA     |

| INTV <sub>CCn</sub> Regulator                  |                                                                                                       |                                                                                                                            |   |              |                                                |              |        |

| V <sub>INTVCC</sub> n                          | Channel Internal V <sub>CC</sub> Voltage, No INTV <sub>CCn</sub> Loading (I <sub>INTVCCn</sub> = 0mA) | $3.6V \le SV_{INn} \le 40V$ , EXTV <sub>CCn</sub> Open Circuit $5V \le SV_{INn} \le 40V$ , $3.2V \le EXTV_{CCn} \le 26.5V$ |   | 3.15<br>2.85 | 3.4<br>3.0                                     | 3.65<br>3.15 | V      |

| V <sub>EXTVCCn(TH)</sub>                       | EXTV <sub>CCn</sub> Switchover Voltage                                                                | (Note 4)                                                                                                                   |   |              | 3.15                                           |              | V      |

| $\frac{\Delta V_{INTVCCn}(LOAD)}{V_{INTVCCn}}$ | INTV <sub>CCn</sub> Load Regulation                                                                   | 0mA ≤ I <sub>INTVCCn</sub> ≤ 30mA                                                                                          |   | -2           | 0.5                                            | 2            | %      |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified internal operating temperature range (Note 2). Specified as each individual output channel (Note 5).  $T_A = 25^{\circ}C$ , Test Circuit 2 (negative- $V_{OUTn}^{-}$ , inverting buck-boost configuration with  $V_{OUTn}^{+} = GND$ ),  $V_{INn} = 12V$  and electrically connected to  $SV_{INn}$ , RUNn-GND = 3.3V,  $ISET_{na} = SV_{OUTn}^{-} = 24V$ ,  $EXTV_{CCn} = GND$ , CLKINn open circuit,  $R_{fSETn} = 57.6k\Omega$  and  $R_{ISETn} = 480k\Omega$  and voltages referred to GND unless otherwise noted.

| SYMBOL                                 | PARAMETER                                                                      | CONDITIONS                                                                                                                                                                                                                                                |   | MIN   | TYP | MAX   | UNITS |

|----------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------|-----|-------|-------|

| $SV_{INn(DC)}, V_{INn(DC)}$            | Input DC Voltage in<br>Negative-V <sub>OUT</sub> Configuration                 | $V_{INn^+} V_{OUTn^-}  \le 40V$                                                                                                                                                                                                                           | • | 3.6   |     | 40    | V     |

| V <sub>OUT<i>n</i>(RANGE)</sub>        | Range of Negative Output Voltage<br>Regulation                                 | $0.5V \le ISET na - SV_{OUTn}^{-} \le 26.5V$                                                                                                                                                                                                              | • | -26.5 |     | -0.5  | V     |

| V <sub>OUTn(-24VDC)</sub> <sup>-</sup> | Output Voltage Total Variation with Line and Load at V <sub>OUT</sub> n = -24V | $3.6V \le V_{INn} \le 16V$ , $0A \le I_{OUTn}^- \le 0.3A$ , CLKINn<br>Driven per Note 8, $C_{INHn} = 4.7\mu$ F, $C_{Dn} = 4.7\mu$ F $\times$ 2, $C_{OUTHn} = 47\mu$ F $\times$ 2                                                                          | • | -24.4 | -24 | -23.6 | V     |

| V <sub>OUTn(-5VDC)</sub>               | Output Voltage Total Variation with Line and Load at V <sub>OUTn</sub> = -5V   | Measuring $V_{OSNSn}^+$ – ISET $na$ , $12V \le V_{INn} \le 35V$ , $0A \le I_{OUT}^- \le 3A$ , CLKIN $n$ Driven by 550kHz Clock, $C_{INHn} = 4.7 \mu F$ , $C_{Dn} = 4.7 \mu F \times 2$ , $C_{OUTHn} = 47 \mu F \times 2$ , ISET $na$ -S $V_{OUTn}^- = 5V$ | • | -15   | 0   | 15    | mV    |

| R <sub>SVINF</sub>                     | Resistor Between SV <sub>INn</sub> and SV <sub>INFn</sub>                      |                                                                                                                                                                                                                                                           |   |       | 1   |       | Ω     |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified internal operating temperature range (Note 2). Specified as each individual output channel (Note 5).  $T_A = 25^{\circ}C$ , Test Circuit 2 (negative- $V_{0UTn}^{-}$ , inverting buck-boost configuration with  $V_{0UTn}^{+} = GND$ ),  $V_{INn} = 12V$  and electrically connected to  $SV_{INn}$ , RUNn - GND = 3.3V,  $ISET_{na} - SV_{0UTn}^{-} = 24V$ ,  $EXTV_{CCn} = GND$ , CLKINn open circuit,  $R_{fSETn} = 57.6k\Omega$  and  $R_{ISETn} = 480k\Omega$  and voltages referred to GND unless otherwise noted.

| SYMBOL PARAMETER CONDIT                                                 |                                                                                                                                  | CONDITIONS                                                                                                                                                                                                                                                                                                                          |           | MIN        | TYP               | MAX        | UNITS        |

|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------|-------------------|------------|--------------|

| Input Specifications                                                    |                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                     |           | l.         |                   |            |              |

| V <sub>INn(UVLO)</sub> SV <sub>INn</sub> Undervoltage Lockout Threshold |                                                                                                                                  | SV <sub>INn</sub> Rising<br>SV <sub>INn</sub> Falling<br>Hysteresis                                                                                                                                                                                                                                                                 | •         | 2.1<br>400 | 3.2<br>2.5<br>700 | 3.6<br>2.8 | V<br>V<br>mV |

| INRUSH(VINn)                                                            | Input Inrush Current at Start-Up                                                                                                 | $C_{INHn} = 4.7 \mu F$ , $CDn = 4.7 \mu F \times 2$ , $C_{OUTHn} = 47 \mu F \times 2$ ; $I_{OUTn}^- = 0A$ , ISET <i>n</i> a Electrically Connected to ISET <i>n</i> b                                                                                                                                                               |           |            | 1.1               |            | А            |

| $I_{\mathbb{Q}(SVINn)}$                                                 | Input Supply Bias Current                                                                                                        | Shutdown, RUN <i>n</i> = GND<br>RUN <i>n</i> –GND = 3.3V                                                                                                                                                                                                                                                                            |           |            | 16<br>450         | 30         | μA<br>μA     |

| I <sub>S(VINn)</sub>                                                    | Input Supply Current                                                                                                             | CLKINn Open Circuit, I <sub>OUTn</sub> = 1.25A                                                                                                                                                                                                                                                                                      |           |            | 3.0               |            | A            |

| I <sub>S(VINn, SHUTDOWN)</sub>                                          | Input Supply Current in Shutdown                                                                                                 | Shutdown, RUNn = GND                                                                                                                                                                                                                                                                                                                |           |            | 4                 |            | μА           |

| Output Specifications                                                   |                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                     | •         | •          |                   |            |              |

| l <sub>OUT</sub> n                                                      | V <sub>OUTn</sub> <sup>-</sup> Output Continuous Current Range                                                                   | $V_{INn}$ = 12V, Regulating $V_{OUTn}^-$ = -24V at $f_{SWn}$ = 1MHz $V_{INn}$ = 12V, Regulating $V_{OUTn}^-$ = -5V at $f_{SWn}$ = 550kHz (See Note 3. Capable of Up to 4A Output Current for Some Combinations of $V_{INn}$ , $V_{OUTn}^-$ and $f_{SWn}$ )                                                                          |           | 0          |                   | 1.25<br>3  | A<br>A       |

| $\Delta V_{OUTn(LINE)}^{-}/V_{OUTn}^{-}$                                | Line Regulation Accuracy                                                                                                         | $I_{OUTn}^-$ = 0A, 3.6V $\leq$ $V_{INn} \leq$ 16V, ISET $na$ -S $V_{OUTn}^-$ = 24V, CLKIN $n$ Driven by 1.8MHz Clock                                                                                                                                                                                                                | •         |            | 0.05              | 0.25       | %            |

| $\Delta V_{OUTn(LOAD)}^{-} \mathcal{N}_{OUTn}^{-}$                      | $V_{\rm IN} = 12V, 0A \le I_{\rm OUTn}$ Load Regulation Accuracy $V_{\rm IN} = 12V, 0A \le I_{\rm OUT}$ Load Regulation Accuracy |                                                                                                                                                                                                                                                                                                                                     | •         |            | 0.05              | 0.75       | %            |

| V <sub>OUTn(AC)</sub> <sup>-</sup>                                      | Output Voltage Ripple, V <sub>OUTn</sub> -                                                                                       | $V_{INn} = 12V$ , $I_{SETna} - SV_{OUTn}^- = 5V$                                                                                                                                                                                                                                                                                    |           |            | 10                |            | $mV_{P-P}$   |

| $f_{SN}$                                                                | V <sub>OUTn</sub> <sup>-</sup> Ripple Frequency                                                                                  | $V_{INn} = 12V$ , $I_{SETna} - SV_{OUTn}^- = 5V$                                                                                                                                                                                                                                                                                    | •         | 1.7        | 1.95              | 2.2        | MHz          |

| $\Delta V_{OUTn(START)}^{-}$                                            | Turn-On Overshoot                                                                                                                |                                                                                                                                                                                                                                                                                                                                     |           |            | 8                 |            | mV           |

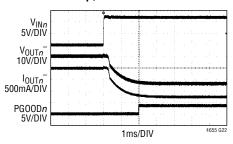

| t <sub>START</sub> Turn-On Start-Up Time                                |                                                                                                                                  | Delay Measured from $V_{INn}$ Toggling from 0V to 12V to PG00Dn Exceeding 3V Above GND; PG00Dn Having a $100k\Omega$ Pull-Up to 3.3V with Respect to GND, $V_{PGFBn}$ Resistor Divider Network as Shown in Test Circuit 2, $R_{ISETna} = 480k\Omega$ , ISETna Electrically Connected to ISETnb, and CLKINn Driven with 1.2MHz Clock |           |            | 4                 | 9          | ms           |

|                                                                         |                                                                                                                                  | $I_{OUTn}^-$ : OA to 1A and 1A to OA Load Steps in 1 $\mu$ s, $C_{OUTHn} = 47\mu$ F × 2                                                                                                                                                                                                                                             | s in 1µs, |            | 400               |            | mV           |

| t <sub>SETTLE</sub> n                                                   | Settling Time for Dynamic Load Step                                                                                              | $I_{OUTn}^-$ : OA to 1A and 1A to OA Load Steps in 1 $\mu$ s, $C_{OUTH2}$ = 47 $\mu$ F × 2 X5R                                                                                                                                                                                                                                      |           |            | 50                |            | μѕ           |

| I <sub>OUTn(OCL)</sub> <sup>-</sup>                                     | I <sub>OUT</sub> <sup>-</sup> Output Current Limit                                                                               |                                                                                                                                                                                                                                                                                                                                     |           |            | 1.7               |            | A            |

| Control Section                                                         |                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                     |           |            |                   |            |              |

| I <sub>ISET<i>n</i>a</sub> Reference Current of ISET <i>n</i> a Pin     |                                                                                                                                  | $V_{\text{ISET}na}$ -S $V_{\text{OUT}n}$ -= 0.5 $V$ , 3.6 $V$ $\leq$ $V_{\text{IN}n}$ $\leq$ 28 $V$ 0 $V$ $\leq$ $V_{\text{ISET}na}$ -S $V_{\text{OUT}n}$ - $\leq$ $V_{\text{IN}n}$ -S $V_{\text{OUT}}$ - $\leq$ 40 $V$                                                                                                             |           | 49.3<br>49 | 50<br>50          | 50.7<br>51 | μA<br>μA     |

| I <sub>VOSNSn</sub> <sup>+</sup>                                        | V <sub>OSNSn</sub> <sup>+</sup> Leakage Current                                                                                  | t $V_{OSNSn}^+ - SV_{OUTn}^- = 28V$                                                                                                                                                                                                                                                                                                 |           |            | 290               |            | μA           |

| t <sub>ONn(MIN)</sub>                                                   | Minimum On-Time                                                                                                                  | (Note 4)                                                                                                                                                                                                                                                                                                                            |           |            | 60                |            | ns           |

| V <sub>RUNn</sub>                                                       | RUN <i>n</i> Turn-On/-Off Thresholds                                                                                             | RUN <i>n</i> Input Turn-On Threshold, RUN <i>n</i> Rising<br>RUN <i>n</i> Hysteresis<br>(RUN <i>n</i> Thresholds Measured with Respect to GND)                                                                                                                                                                                      |           | 1.08       | 1.2<br>130        | 1.32       | V<br>mV      |

| I <sub>RUNn</sub>                                                       | RUN <i>n</i> Leakage Current                                                                                                     | $V_{INn}$ = 12V, RUN $n$ -GND = 3.3V                                                                                                                                                                                                                                                                                                | •         |            | 0.1               | 50         | nA           |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified internal operating temperature range (Note 2). Specified as each individual output channel (Note 5).  $T_A = 25^{\circ}C$ , Test Circuit 2 (negative- $V_{0UTn}^{-}$ , inverting buck-boost configuration with  $V_{0UTn}^{+} = GND$ ),  $V_{INn} = 12V$  and electrically connected to  $SV_{INn}$ , RUNn - GND = 3.3V,  $ISET_{na} - SV_{0UTn}^{-} = 24V$ ,  $EXTV_{CCn} = GND$ , CLKINn open circuit,  $R_{fSETn} = 57.6k\Omega$  and  $R_{ISETn} = 480k\Omega$  and voltages referred to GND unless otherwise noted.

| SYMBOL                                                              | PARAMETER CONDITIONS                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                    |   |                                                  | TYP         | MAX          | UNITS       |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------------------------------------------|-------------|--------------|-------------|

| Oscillator and Phase                                                | -Locked Loop (PLL)                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                    |   |                                                  |             |              |             |

| foscn                                                               | Oscillator Frequency Accuracy                                                                                                                                                                                                                                              | $V_{INn}$ = 12V, ISET $na$ -SV $_{OUTn}^-$ = 5V, and:<br>$f_{SETn}$ Open Circuit<br>$R_{fSETn}$ = 57.6k $\Omega$ (See $f_{SN}$ Specification)                                                                                      |   |                                                  | 400<br>1.95 | 440          | kHz<br>MHz  |

| f <sub>SYNCn</sub>                                                  | PLL Synchronization Capture Range $V_{INn} = 12V$ , ISET $na$ -SV $_{OUTn}^- = 5V$ , CLKINn Driven with a GND Referred Clock Toggling from 0.4V to 1.2V and Having a Clock Duty Cycle: From 10% to 90%; $f_{SETn}$ Open Circuit From 40% to 60%; $R_{ISETn} = 57.6k\Omega$ |                                                                                                                                                                                                                                    |   | 250<br>1.3                                       |             | 550<br>3     | kHz<br>MHz  |

| V <sub>CLKIN</sub> n                                                | CLKINn Input Threshold                                                                                                                                                                                                                                                     | V <sub>CLKINn</sub> Rising with Respect to GND V <sub>CLKINn</sub> Falling with Respect to GND                                                                                                                                     |   | 1.2                                              |             | 0.4          | V           |

| I <sub>CLKIN</sub> n                                                | CLKINn Input Current  V <sub>CLKINn</sub> = 5V with Respect to GND V <sub>CLKINn</sub> = 0V with Respect to GND                                                                                                                                                            |                                                                                                                                                                                                                                    |   | -20                                              | 230<br>-5   | 500          | μA<br>μA    |

| Power Good Feedba                                                   | ck Input and Power Good Output                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                    |   |                                                  |             |              | <u> </u>    |

| OV <sub>PGDFBn</sub>                                                | Output Overvoltage PGOOD <i>n</i> Upper Threshold                                                                                                                                                                                                                          | PGDFB <i>n</i> Rising, Differential Voltage from PGDFB <i>n</i> to SV <sub>OUT</sub> <i>n</i>                                                                                                                                      | • | 620                                              | 645         | 675          | mV          |

| UV <sub>PGDFBn</sub>                                                | Output Undervoltage PGOOD <i>n</i> Lower Threshold                                                                                                                                                                                                                         | PGDFB <i>n</i> Falling, Differential Voltage from PGDFB <i>n</i> to SV <sub>OUT,n</sub> <sup>-</sup>                                                                                                                               | • | 525                                              | 555         | 580          | mV          |

| $\Delta V_{PGDFB}$                                                  | PGOOD <i>n</i> Hysteresis                                                                                                                                                                                                                                                  | PGDFB <i>n</i> Returning                                                                                                                                                                                                           |   |                                                  | 8           |              | mV          |

| R <sub>PGDFB</sub> n                                                | Resistor Between PGDFB <i>n</i> and SV <sub>OUTn</sub> <sup>-</sup>                                                                                                                                                                                                        |                                                                                                                                                                                                                                    |   | 4.94                                             | 4.99        | 5.04         | kΩ          |

| R <sub>PGOOD</sub> n                                                | PG00D <i>n</i> Pull-Down Resistance $V_{PG00Dn} = 0.1V$ with Respect to GND, $V_{PGDFBn} - SV_{OUTn}^- < UV_{PGDFBn}$ or $V_{PGDFBn} - SV_{OUTn}^- > 0V_{PGDFBn}$                                                                                                          |                                                                                                                                                                                                                                    |   |                                                  | 700         | 1500         | Ω           |

| I <sub>PGOODn(LEAK)</sub>                                           | PGOOD <i>n</i> Leakage Current                                                                                                                                                                                                                                             | $V_{PGOODn} = 3.3V$ with Respect to GND,<br>$UV_{PGDFBn} < V_{PGDFBn} - SV_{OUTn}^- < OV_{PGDFBn}$                                                                                                                                 |   |                                                  | 0.1         | 1            | μА          |

| t <sub>PGOOD</sub> n(DELAY)                                         | PGOOD <i>n</i> Delay                                                                                                                                                                                                                                                       | PGOOD <i>n</i> Low to High (Note 4)<br>PGOOD <i>n</i> High to Low (Note 4)                                                                                                                                                         |   | 16/f <sub>SW(Hz)</sub><br>64/f <sub>SW(Hz)</sub> |             | S<br>S       |             |

| Input Voltage Regula                                                | ntion Pin                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                    |   |                                                  |             |              |             |

| V <sub>VINREG</sub> n                                               | V <sub>INREGn</sub> Servo Voltage                                                                                                                                                                                                                                          | V <sub>INREGn</sub> Voltage During Output Current Regulation,<br>Measured with Respect to SV <sub>OUTn</sub>                                                                                                                       | • | 1.8                                              | 2.0         | 2.2          | V           |

| I <sub>VINREG</sub>                                                 | V <sub>INREGn</sub> Leakage Current                                                                                                                                                                                                                                        | V <sub>INREG</sub> -SV <sub>OUTn</sub> - = 2V                                                                                                                                                                                      |   |                                                  | 1           |              | nA          |

| INTV <sub>CCn</sub> Regulator                                       |                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                    |   |                                                  |             |              |             |

| VINTVCCn                                                            | Channel Internal V <sub>CC</sub> Voltage, No INTV <sub>CCn</sub> Loading (I <sub>INTVCCn</sub> = 0mA)                                                                                                                                                                      | $3.6V \le SV_{INn} - SV_{OUTn}^- \le 40V$ , EXTV <sub>CCn</sub> = Open Circuit $5V \le SV_{INn} - SV_{OUTn}^- \le 40V$ , $3.2V \le EXTV_{CCn}^ V_{OUTn}^- \le 26.5V$ (INTV <sub>CCn</sub> Measured with Respect to $SV_{OUTn}^-$ ) |   | 3.15<br>2.85                                     | 3.4<br>3.0  | 3.65<br>3.15 | V<br>V<br>V |

| V <sub>EXTVCCn(TH)</sub>                                            | EXTV <sub>CCn</sub> Switchover Voltage                                                                                                                                                                                                                                     | (EXTV <sub>CCn</sub> Measured with Respect to SV <sub>OUTn</sub> <sup>-</sup> )<br>(Note 4)                                                                                                                                        |   |                                                  | 3.15        |              | V           |

| $\frac{\Delta V_{\text{INTVCC}n(\text{LOAD})}}{V_{\text{INTVCC}n}}$ | $C_{n(LOAD)}$ INTV <sub>CCn</sub> Load Regulation 0mA $\leq I_{INTVCCn} \leq 30$ mA                                                                                                                                                                                        |                                                                                                                                                                                                                                    |   | -2                                               | 0.5         | 2            | %           |

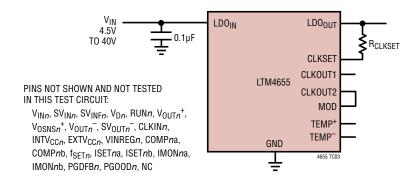

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the specified internal operating temperature range (Note 2). $T_A = 25^{\circ}C$ , Test Circuit 3 and voltages referred to GND unless otherwise noted.

| SYMBOL                                            | PARAMETER                                                                                                                                                                          | CONDITIONS                                                                                                                                                                                                |   | MIN        | TYP          | MAX        | UNITS             |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------|--------------|------------|-------------------|

| LDO <sub>IN(DC)</sub>                             | LDO Input DC Voltage                                                                                                                                                               |                                                                                                                                                                                                           | • | 4.5        |              | 40         | V                 |

| V <sub>LDOOUT(DC)</sub>                           | LDO Output Voltage                                                                                                                                                                 | $\begin{split} &V_{LDOIN} = 36V,0\text{mA} \leq I_{LDOOUT} \leq 25\text{mA} \\ &V_{LDOIN} = 4.5V,0\text{mA} \leq I_{LDOOUT} \leq 20\text{mA} \end{split}$                                                 | • | 4.8<br>2.7 | 5.0<br>4.1   | 5.2        | V                 |

| V <sub>LDOOUT(AC)</sub>                           | Output Voltage Ripple                                                                                                                                                              |                                                                                                                                                                                                           |   |            | 2            |            | mV <sub>P-P</sub> |

| I <sub>LDOOUT(OCL)</sub>                          | Output Current Limit, 5V LDO                                                                                                                                                       | LDO <sub>IN</sub> = 36V                                                                                                                                                                                   |   |            | 140          |            | mA                |

| Clock Generator                                   |                                                                                                                                                                                    |                                                                                                                                                                                                           |   |            |              |            |                   |

| $\Delta f_{OUT}$                                  | Clock-Generator Frequency Accuracy                                                                                                                                                 | $2.7V \le LDO_{OUT} \le 5.2V$ , $200kHz \le f_{OUT} \le 3MHz$ , MOD Connected to CLKOUT2                                                                                                                  | • |            | ±2.5<br>±2.5 | ±7.5<br>±3 | %<br>%            |

| R <sub>CLKSET(RANGE)</sub>                        | Frequency Setting Resistor Range                                                                                                                                                   | $\begin{array}{l} R_{CLKSET} \ Resistance \ for \ Which \ -7.5\% \leq \Delta f_{OUT} \leq \\ 7.5\%, \ Over \ 2.7V \leq LDO_{OUT} \leq 5.2V, \\ MOD \ Electrically \ Connected \ to \ CLKOUT2 \end{array}$ | • | 33.2       |              | 499        | kΩ                |

|                                                   | Period Variation (Frequency Spreading)                                                                                                                                             | LDO <sub>OUT</sub> = 5V, $R_{CLKSET}$ = 100kΩ, MOD Open Circuit                                                                                                                                           |   |            | ±10          |            | %                 |

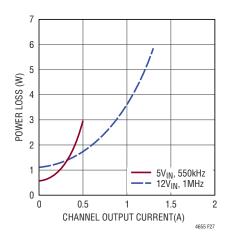

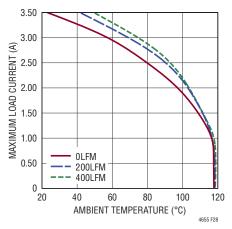

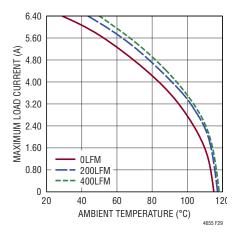

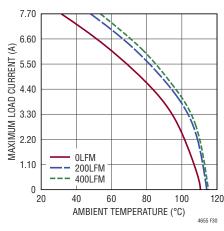

|                                                   | Duty Cycle                                                                                                                                                                         | $2.7V \le LDO_{OUT} \le 5.2V$ , $200kHz \le f_{OUT} \le 3MHz$ , MOD Electrically Connected to CLKOUT2                                                                                                     | • | 40         |              | 60         | %                 |