# **BMA580**

Advanced, ultra-small, triaxial high performance low-g accelerometer with digital interfaces

## **BMA580 Datasheet**

Document revision 1.1

Document release date Feb 6th 2025

Document number BST-BMA580-DS000-05

Sales part number(s) 0 273 017 046

Notes Data and descriptions in this document are subject to change without notice.

Product photos and pictures are for illustration purposes only and may differ from the

real product appearance.

## **Basic Description**

The BMA580 is an advanced,ultra-small, triaxial high performance low-g accelerometer with digital interfaces. The sensor is suitable for low-power and demanding consumer electronics applications. The BMA580 integrates

- a 16 bit digital, triaxial accelerometer with range configurable to  $\pm 2\,\mathrm{g}$ ,  $\pm 4\,\mathrm{g}$ ,  $\pm 8\,\mathrm{g}$ ,  $\pm 16\,\mathrm{g}$

- lacktriangle a 8 bit digital temperature sensor for an operating temperature range  $-40\,^{\circ}\mathrm{C}$  ... 85  $^{\circ}\mathrm{C}$

#### **Key Features**

- Compact size 1.2 × 0.8 mm² Wafer Level Chip Scale Package (WLCSP), 6 pins, height 0.55 mm

- Primary digital interface with 10 MHz slave SPI (4-wire, 3-wire), 12.5 MHz I3C and up to 1 MHz I2C (Fm+)

- Sample rates (output data rates ODR): 1.5625 Hz . . . 6.4 kHz (nominal)

- Programmable low-pass filtering

- Wide power supply range: analog VDD 1.62 V ... 3.63 V

- Ultra low current consumption: typ.  $125\mu A$  (in full ODR and aliasing free operation)

- Built-in power management unit (PMU) for advanced power management and low power modes

- Power on time: 1.8ms for communication readiness

- up to 1 KB on-chip FIFO buffer for accelerometer, temperature sensor and sensor time stamps

- Fast offset error compensation for accelerometer

- Sensor time stamps for accurate system (host) and sensor time synchronization

- Two independent programmable I/O pins for interrupt and synchronization events

- On-chip interrupt engine and integrated smart features for always-on applications (e.g., activity, action, and gesture recognition) using the sensor ultra-low power domain:

- single tap, double tap, and triple tap detection

- Audio feature for hearables: "Voice Activity Detection"

- generic interrupts (three parallel instances of a highly configurable flexible interrupt)

- RoHS compliant, halogen and lead free

# **Table of contents**

| Ba | sic D | escription                                                                                                                                                                                                                |                                                     | 2  |

|----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----|

| 1  | Spe   | cification                                                                                                                                                                                                                |                                                     | 9  |

| 2  | Abs   | olute Max                                                                                                                                                                                                                 | imum Ratings                                        | 12 |

| 3  | Quid  | 4.4.1 Temperature sensor and external voltage measurement  4.5 Interrupt Pin Configuration  4.5.1 Electrical Interrupt Pin Behavior  4.5.2 Interrupt Pin Mapping  4.5.3 Measurement of external signals on Interrupt Pins | 13                                                  |    |

| 4  | Fun   | ctional De                                                                                                                                                                                                                | scription and Advanced Features                     | 22 |

|    | 4.1   | Power Mo                                                                                                                                                                                                                  | ode States                                          | 22 |

|    |       | 4.1.1                                                                                                                                                                                                                     | ACTIVE State                                        | 22 |

|    |       | 4.1.2                                                                                                                                                                                                                     | SUSPEND State                                       | 22 |

|    |       | 4.1.3                                                                                                                                                                                                                     | Power on Time                                       | 22 |

|    | 4.2   | Acceleror                                                                                                                                                                                                                 | neter                                               | 23 |

|    |       | 4.2.1                                                                                                                                                                                                                     | Accelerometer Data                                  | 23 |

|    |       | 4.2.2                                                                                                                                                                                                                     | Accelerometer Data Processing                       | 23 |

|    |       | 4.2.3                                                                                                                                                                                                                     | Accelerometer Configuration                         | 24 |

|    |       | 4.2.4                                                                                                                                                                                                                     | Accelerometer Performance Mode                      | 24 |

|    |       | 4.2.5                                                                                                                                                                                                                     | Accelerometer Effective Bandwidth                   | 24 |

|    |       | 4.2.6                                                                                                                                                                                                                     | Accelerometer Change Configuration                  | 24 |

|    |       | 4.2.7                                                                                                                                                                                                                     | Accelerometer Self-Test                             | 25 |

|    |       | 4.2.8                                                                                                                                                                                                                     | Accelerometer Data Ready Interrupt                  | 26 |

|    |       | 4.2.9                                                                                                                                                                                                                     | Accelerometer Startup Time (Time to valid data)     | 26 |

|    |       | 4.2.10                                                                                                                                                                                                                    | Accelerometer Offset Compensation                   | 26 |

|    | 4.3   | Sensor tir                                                                                                                                                                                                                | ne                                                  | 27 |

|    | 4.4   | Temperat                                                                                                                                                                                                                  | ure Sensor                                          | 27 |

|    |       | 4.4.1                                                                                                                                                                                                                     | Temperature sensor and external voltage measurement | 27 |

|    | 4.5   | Interrupt I                                                                                                                                                                                                               | Pin Configuration                                   | 28 |

|    |       | •                                                                                                                                                                                                                         |                                                     |    |

|    |       | 4.5.2                                                                                                                                                                                                                     | Interrupt Pin Mapping                               | 28 |

|    |       | 4.5.3                                                                                                                                                                                                                     |                                                     |    |

|    |       | 4.5.4                                                                                                                                                                                                                     | Clear Interrupt Status                              | 29 |

|    |       | 4.5.5                                                                                                                                                                                                                     | Interrupt Behavior Example                          | 29 |

|    | 4.6   | FIFO                                                                                                                                                                                                                      |                                                     | 30 |

|    |       | 4.6.1                                                                                                                                                                                                                     | FIFO Configuration                                  |    |

|    |       | 4.6.2                                                                                                                                                                                                                     | FIFO Frames                                         |    |

|    |       | 4.6.3                                                                                                                                                                                                                     | FIFO Interrupts                                     |    |

|    |       | 4.6.4                                                                                                                                                                                                                     | FIFO Reset/Flush                                    |    |

|    | 4.7   | Soft-Rese                                                                                                                                                                                                                 | et                                                  | 34 |

|    | 4.8   |                                                                                                                                                                                                                           | ealth Status                                        |    |

|    | 4.9   | Advanced                                                                                                                                                                                                                  | d Features                                          | 34 |

|    |       | 4.9.1                                                                                                                                                                                                                     | General Configuration                               |    |

|    |       | 4.9.2                                                                                                                                                                                                                     | Generic Interrupt                                   |    |

|    |       |                                                                                                                                                                                                                           |                                                     |    |

|   |      | 4.9.3       | Any-Motion Detector                               | 39  |

|---|------|-------------|---------------------------------------------------|-----|

|   |      | 4.9.4       | No-Motion Detector                                | 39  |

|   |      | 4.9.5       | Tap Detection                                     |     |

|   |      | 4.9.6       | Self Wake-up                                      |     |

|   |      | 4.9.7       | In-Ear/Out-Ear Detection                          |     |

|   |      | 4.9.8       | Voice Activity Detection                          |     |

|   |      | 4.9.9       | Fast Offset Compensation (FOC)                    | 44  |

| 5 | Digi | tal Interfa | ces                                               | 45  |

|   | 5.1  | Electrical  | Specification                                     | 45  |

|   | 5.2  | Digital Int | erface Protocols                                  | 45  |

|   |      | 5.2.1       | Protocol Selection                                | 45  |

|   |      | 5.2.2       | SPI Protocol                                      | 46  |

|   |      | 5.2.3       | I <sup>2</sup> C Protocol                         | 50  |

|   |      | 5.2.4       | I3C Protocol                                      | 53  |

|   |      | 5.2.5       | Automatic Address Increment for Burst Access      | 61  |

| 6 | Men  | nory Map    |                                                   | 62  |

|   | 6.1  | Register I  | Map Description                                   | 62  |

|   |      | 6.1.1       | Register Map Overview                             | 63  |

|   |      | 6.1.2       | Register Map Details                              | 66  |

|   | 6.2  | Extended    | Register Map Description                          | 135 |

|   |      | 6.2.1       | Extended Register Map Overview                    | 136 |

|   |      | 6.2.2       | Extended Register Map Details                     | 138 |

| 7 | Pin  | Out and C   | onnection Diagrams                                | 182 |

|   | 7.1  | Pin Out .   |                                                   | 182 |

|   | 7 2  | Connectio   | on Diagrams                                       | 184 |

|   | 1.2  |             | Connection Diagrams with I <sup>2</sup> C and I3C |     |

|   |      | 7.2.2       | Connection Diagrams with SPI (3-Wire)             |     |

|   |      | 7.2.3       | Connection Diagrams with SPI (4-Wire)             |     |

| 8 | Pac  | kage        |                                                   | 188 |

|   | 8.1  | _           | ns                                                | 188 |

|   | 8.2  |             | Axis Orientation                                  |     |

|   | 8.3  | _           | Pattern Recommendation                            |     |

|   | 8.4  | _           |                                                   |     |

|   | 8.5  | _           | Reel Information                                  |     |

|   |      |             |                                                   |     |

|   | 8.6  | _           | Guidelines                                        |     |

|   | 8.7  | _           | Instructions                                      |     |

|   | 8.8  | Environm    | ental Safety                                      | 193 |

| 9 | Lega | al Disclain | ner                                               | 194 |

10 Document History and Modifications

195

# List of figures

| Figure 1:  | Device communication test                                                         | 14 |

|------------|-----------------------------------------------------------------------------------|----|

| Figure 2:  | Configure the SPI 3-wire interface                                                | 15 |

| Figure 3:  | Configure the I3C interface                                                       | 15 |

| Figure 4:  | Configure the device power mode                                                   | 16 |

| Figure 5:  | Configure the device suspend mode                                                 | 16 |

| Figure 6:  | Configure the sensor parameters and read sensor data                              | 17 |

| Figure 7:  | Mapping hardware interrupt                                                        | 18 |

| Figure 8:  | Change FIFO size                                                                  | 18 |

| Figure 9:  | Read registers in the extended register map                                       | 19 |

| Figure 10: | Write registers in the extended register map                                      | 19 |

| Figure 11: | Enable generic interrupt 1                                                        | 20 |

| Figure 12: | Enable FOC feature in combination with INT1                                       | 21 |

| Figure 13: | Sensor power mode state diagram                                                   | 22 |

| Figure 14: | Power on Time                                                                     | 23 |

| Figure 15: | Accelerometer Startup Time                                                        | 26 |

| Figure 16: | Power on Time and Accelerometer Startup Time                                      | 26 |

| Figure 17: | Interrupt output in latch mode                                                    | 29 |

| Figure 18: | Interrupt output in pulses mode                                                   | 30 |

| Figure 19: | Interrupt output when auto clear mechanism of the data ready interrupt is enabled | 30 |

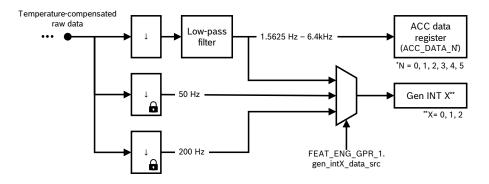

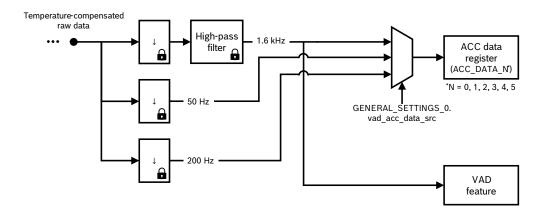

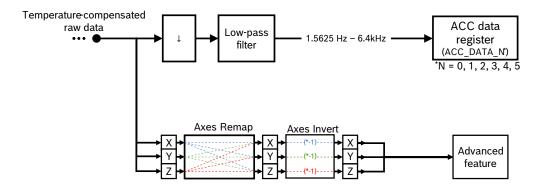

| Figure 20: | Data Path of generic interrupt                                                    | 35 |

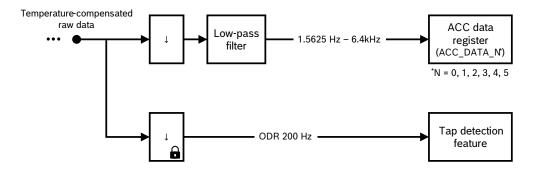

| Figure 21: | Data path of tap detection                                                        | 35 |

| Figure 22: | Data path of VAD                                                                  | 36 |

| Figure 23: | Axis remapping of datapath                                                        | 36 |

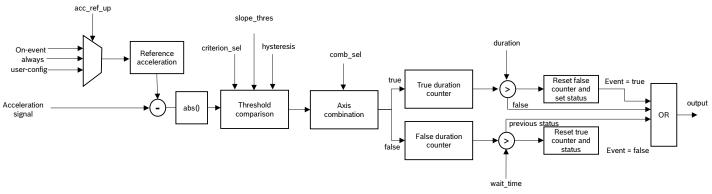

| Figure 24: | Functional behavior of generic interrupt                                          | 38 |

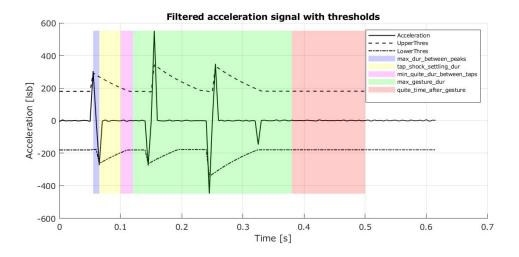

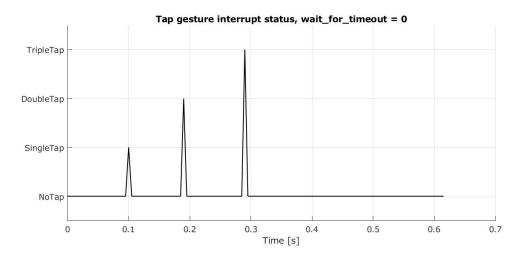

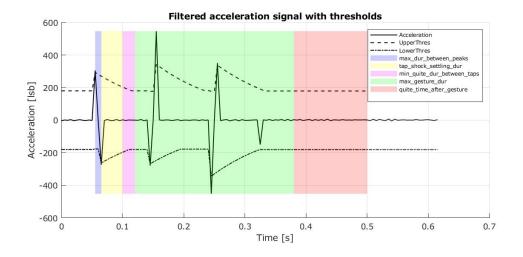

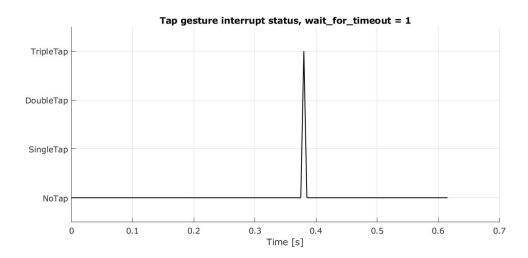

| Figure 25: | Reporting of tap gesture when TAP_DETECTOR_1.wait_for_timeout = 0b0               | 41 |

| Figure 26: | Reporting of tap gesture when settings_1.wait_for_timeout = 0b1                   | 42 |

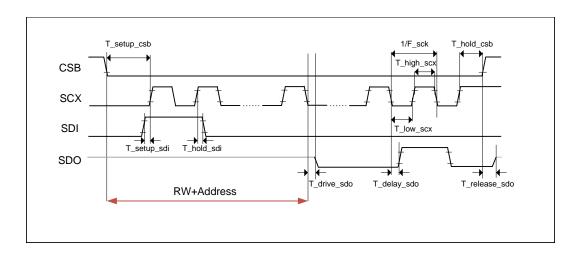

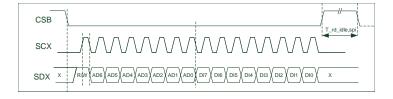

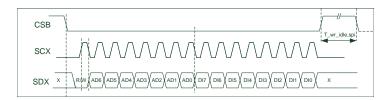

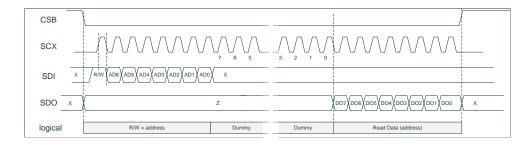

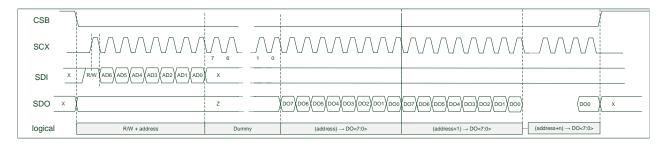

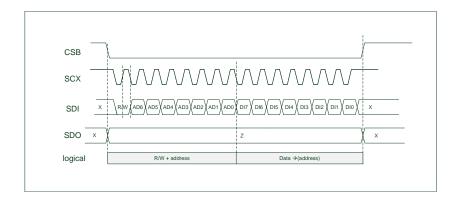

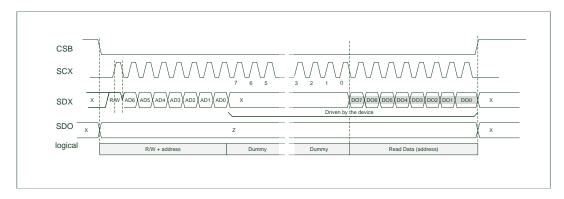

| Figure 27: | SPI timing diagram                                                                | 47 |

| Figure 28: | SPI idle read timing                                                              | 47 |

| Figure 29: | SPI idle write timing                                                             | 47 |

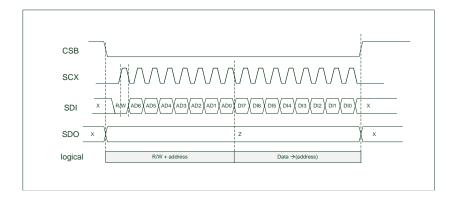

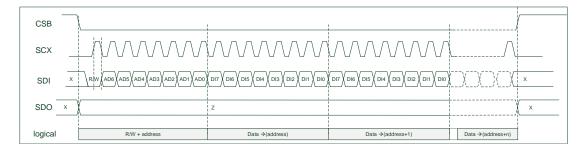

| Figure 30: | Single-byte write operation of 4-wire SPI with mode 0                             | 48 |

| Figure 31: | Multiple-byte write operation of 4-wire SPI with mode 0                           | 48 |

| Figure 32: | Single-byte read operation of 4-wire SPI with mode 0                              | 48 |

| Figure 33: | Multiple-byte read operation of 4-wire SPI with mode 0                            | 49 |

| Figure 34: | Single-byte write operation of 4-wire SPI with mode 3                             | 49 |

| Figure 35: | Single-byte read operation of 3-wire SPI with mode 0                              | 49 |

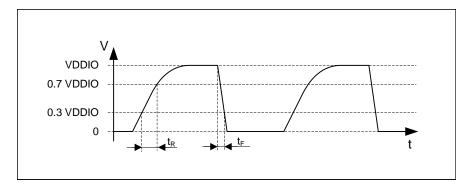

| Figure 36: | Definition of rise- and fall-time of I <sup>2</sup> C interface signals           | 50 |

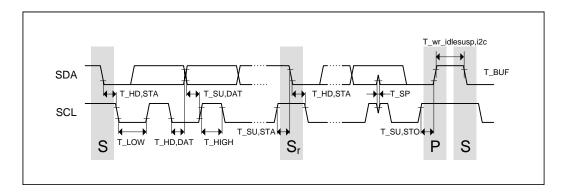

| Figure 37: | I <sup>2</sup> C timing diagram                                                   | 51 |

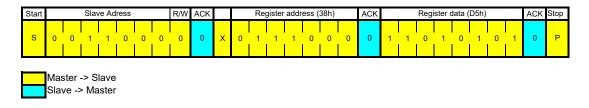

| Figure 38: | Single-byte write operation of I <sup>2</sup> C                                   | 51 |

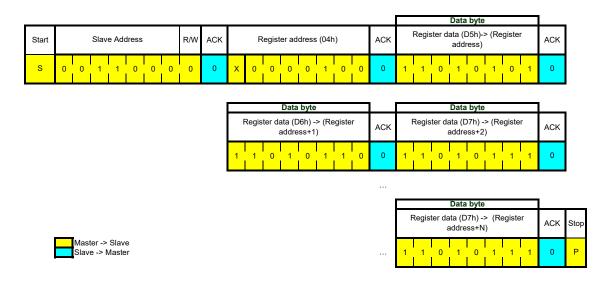

| Figure 39: | Multiple-byte write operation of I <sup>2</sup> C                                 | 52 |

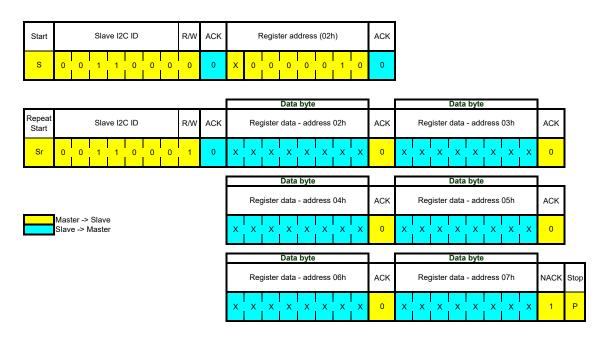

| Figure 40: | Multiple-byte read operation of I <sup>2</sup> C                                  | 52 |

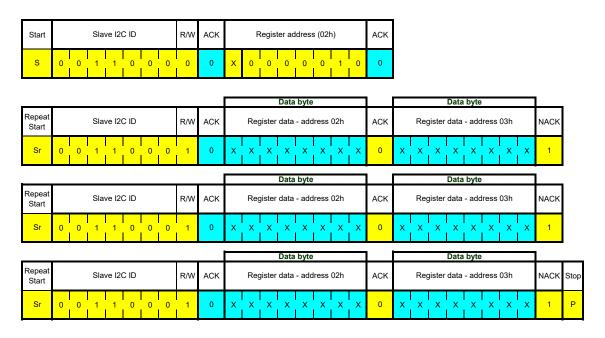

| Figure 41: | Multiple read transmissions of I <sup>2</sup> C from the same start address       | 53 |

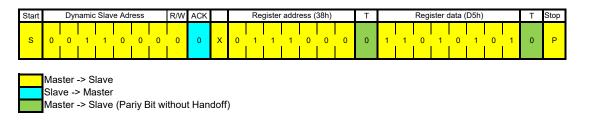

| Figure 42: | Single-byte write protocol of I3C                                                 | 58 |

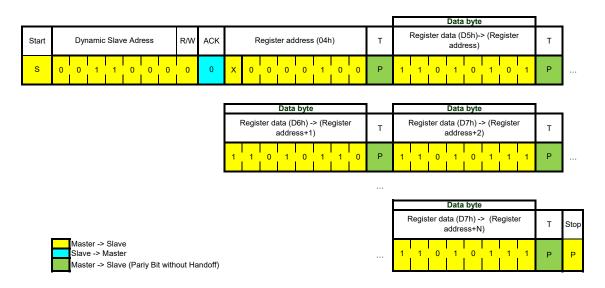

| Figure 43: | Multi-Byte write protocol of I3C                                                  | 59 |

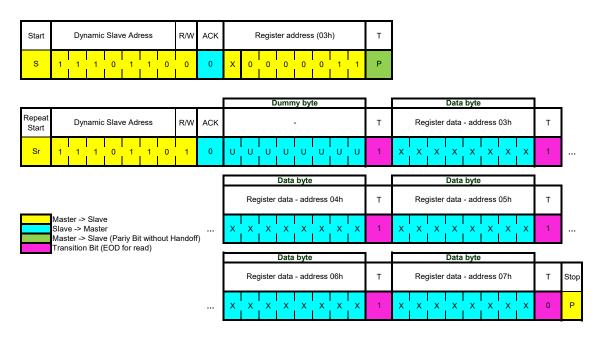

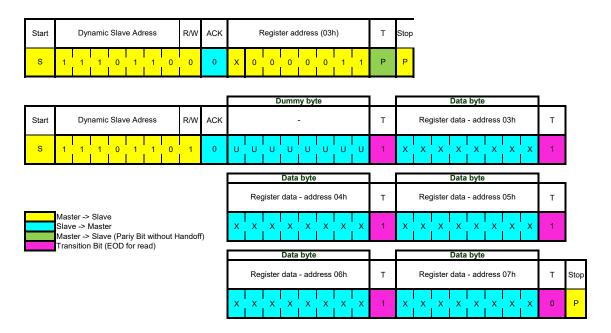

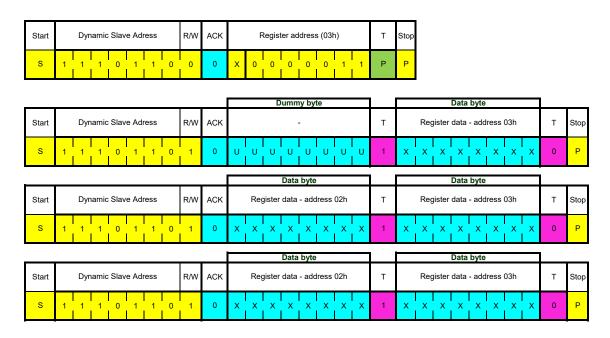

| Figure 44: | Multi-byte read protocol of I3C with repeated start                               | 60 |

|            |                                                                                   |    |

| Figure 45: | Multi-byte read protocol of I3C with stop-start                                                                         | . 60 |

|------------|-------------------------------------------------------------------------------------------------------------------------|------|

| Figure 46: | Multi-byte read protocol of I3C from the same start address with stop-start                                             | . 61 |

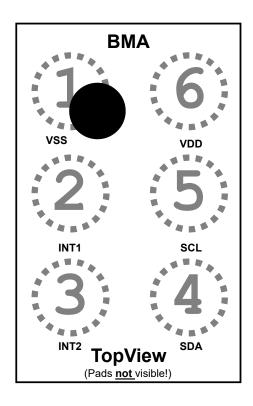

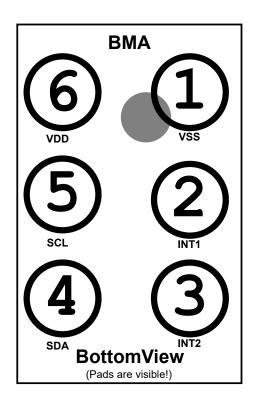

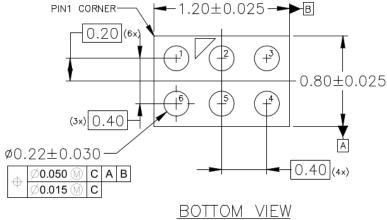

| Figure 47: | Pin-out: top view                                                                                                       | 182  |

| Figure 48: | Pin-out: bottom view                                                                                                    | 183  |

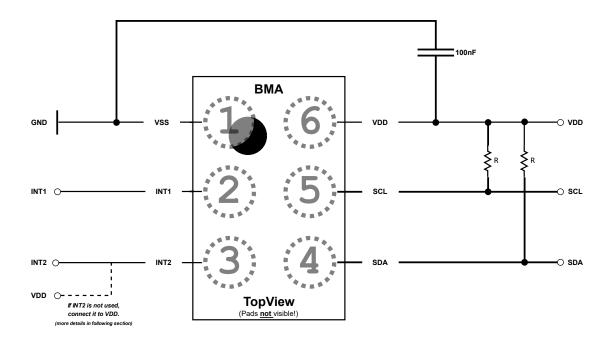

| Figure 49: | Connection Diagram with I <sup>2</sup> C and I3C                                                                        | 184  |

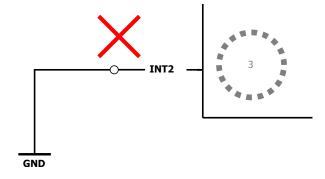

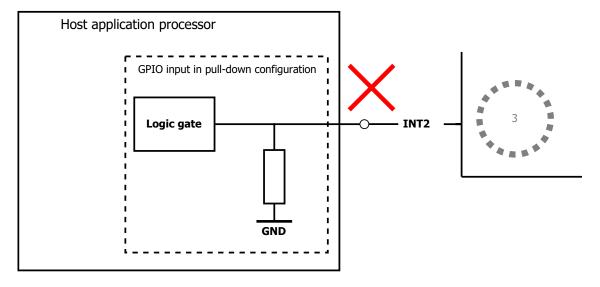

| Figure 50: | Connection that is not allowed in I <sup>2</sup> C and I3C before the pin 3 is configured to the output characteristics | 185  |

| •          | Connection that is not allowed in I <sup>2</sup> C and I3C before the pin 3 is configured to the output characteristics |      |

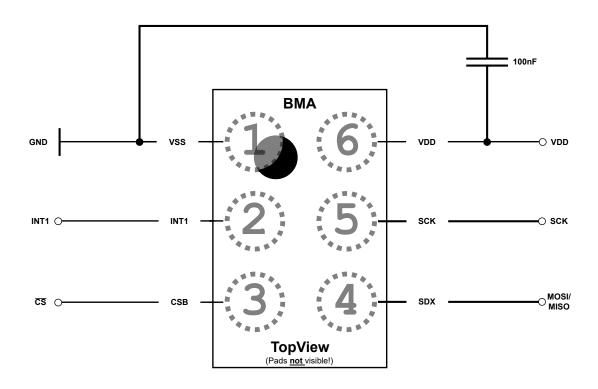

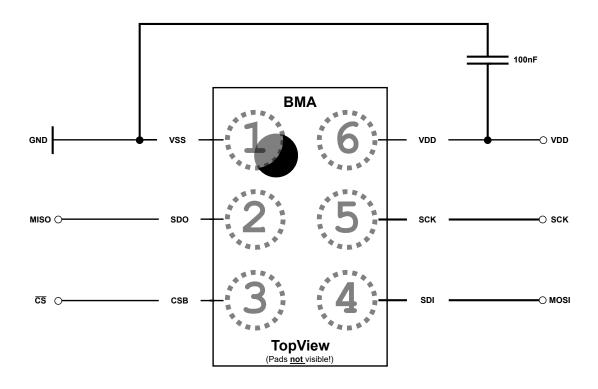

| Figure 52: | Connection Diagram with SPI 3-Wire                                                                                      | 186  |

| Figure 53: | Connection Diagram with SPI 4-Wire                                                                                      | 187  |

| •          | Dimensions from top (in mm)                                                                                             |      |

|            | Dimensions from bottom view (in mm)                                                                                     |      |

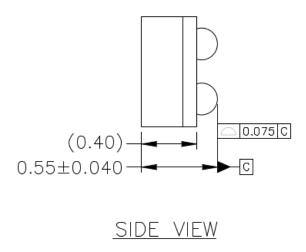

| Figure 56: | Dimensions from side view (in mm)                                                                                       | 189  |

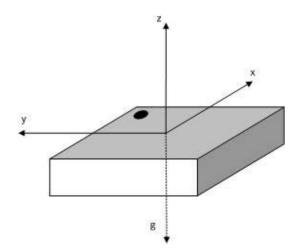

| Figure 57: | Definition of the sensing axes orientation for the raw device                                                           | 189  |

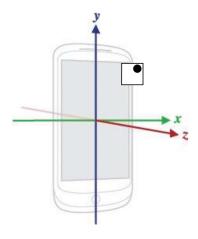

| _          | Definition of the sensing axes orientation within a device                                                              |      |

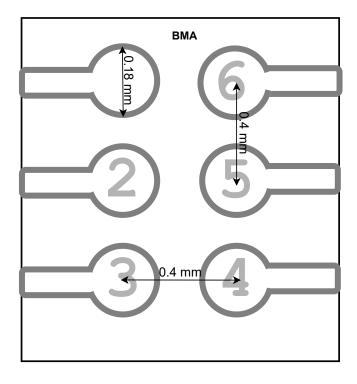

|            | Landing pattern recommendation                                                                                          |      |

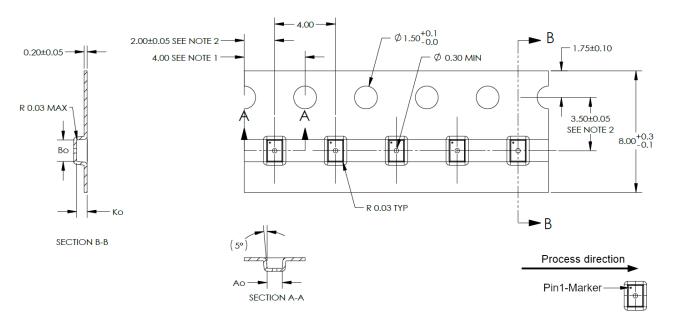

| Figure 60: | Tape and Reel information                                                                                               | 192  |

|            |                                                                                                                         |      |

|            |                                                                                                                         |      |

| List of t  | ables                                                                                                                   |      |

| Table 1:   | Basic electrical parameter specification                                                                                | 9    |

| Table 2:   | Operating conditions for the accelerometer                                                                              |      |

| Table 3:   | Performance characteristics of the accelerometer                                                                        |      |

| Table 4:   | Mechanical characteristics of the accelerometer                                                                         | . 10 |

| Table 5:   | Characteristics of the temperature sensor                                                                               | . 11 |

| Table 6:   | Absolute maximum ratings                                                                                                |      |

| Table 7:   | Sensitivity under different acceleration ranges                                                                         | . 23 |

| Table 8:   | Current Consumption (typical values) depending on ODR and number of averaged samples in LPM at                          |      |

|            | $V_{DD} = 1.8 \text{ V}, T_{A} = 25^{\circ}\text{C}.$                                                                   | . 24 |

| Table 9:   | Minimum threshold value of self-test                                                                                    | . 25 |

| Table 10:  | Pulse duration in the short and long pulses mode                                                                        | . 28 |

| Table 12:  | Register Map Overview                                                                                                   | . 31 |

| Table 14:  | Register Map Overview                                                                                                   | . 32 |

| Table 16:  | Register Map Overview                                                                                                   | . 32 |

|            | Register Map Overview                                                                                                   | . 32 |

| Table 19:  | Overview of supported ODRs in generic interrupts, any-motion/motion detector and no-motion/stationary detector.         | . 37 |

| Table 20:  | Supported ODRs in tap detection.                                                                                        | . 37 |

|            | Pin mapping of the digital interface                                                                                    |      |

|            | Electrical specification of the digital interface                                                                       |      |

|            | SPI mode 0 and mode 3 configuration                                                                                     |      |

|            | SPI interface timing specifications                                                                                     |      |

|            | I <sup>2</sup> C timing requirements (standard mode, fast mode snf fast mode plus)                                      |      |

|            | I3C Bus Identifier                                                                                                      |      |

|            | IBI Payload Format                                                                                                      |      |

|            | Mapping of I3C interrupts status bits to IBI payload                                                                    |      |

|            | • • •                                                                                                                   |      |

| Table 29: | GETCAPS returning value                    | 55  |

|-----------|--------------------------------------------|-----|

| Table 30: | GETSTATUS returning value                  | 55  |

| Table 31: | GETMXDS returning value                    | 56  |

| Table 32: | GETMWL returning value                     | 56  |

| Table 33: | GETMRL returning value                     | 56  |

| Table 34: | GETXTIME returning value                   | 57  |

| Table 35: | Open drain timing parameters of I3C        | 57  |

| Table 36: | Push-pull timing parameters for SDR of I3C | 58  |

| Table 37: | Register map overview                      | 63  |

| Table 38: | Extended register map overview             | 136 |

| Table 39: | Pin-out and pin connections                | 183 |

| Table 40: | Marking – Mass Production                  | 191 |

| Table 41: | Marking – Engineering Samples              | 191 |

| Table 42: | Change log                                 | 195 |

## 1 Specification

This chapter provides the specifications for the BMA580. Minimum values and maximum values are provided for standard distributed quantities as  $\mu \pm 3\sigma$ , typical values as  $\mu \pm \sigma$ . Unless stated otherwise, the specifications provide the characteristics for a nominal supply voltage of  $V_{\rm DD} = V_{\rm DDIO} = 1.8 \rm V$  either at an ambient temperature of  $T_{\rm A} = 25^{\circ} \rm C$ . This definition for minimum (Min), maximum (Max) and typical (Typ) values is also used throughout the other following chapters. Table 1 provides the electrical characteristics for the device.

Condition **Parameter Symbol** Min Max Unit Тур Supply voltage core 1.62 1.8 3.63 V  $V_{

m DD}$ (and I/O) domain  $V_{\rm DDIO}$ SPI, I<sup>2</sup>C & I3C V Voltage input low  $0.3 \cdot V_{\rm DDIO}$  $V_{\rm IL}$ level SPI, I<sup>2</sup>C & I3C 0.7 · V<sub>DDIO</sub> V Voltage input high  $V_{\rm IH}$ level Voltage output low SPI  $0.2 \cdot V_{\rm DDIO}$ V  $V_{\rm IL}$ level Voltage output high SPI 0.8 · V<sub>DDIO</sub> V  $V_{\rm IH}$ level 4.75 Suspend mode Current 18 Low power mode, μΑ  $I_{\rm DD}$ consumption  $f_{A,lp} = 100$ Hz High performance mode, 125  $f_{A,\cdot} = \max$ Time from supply "on" to 1.8 Power on time  $\Delta t_{\rm PO}$ ms serial I/F operational (and stable register access) °C Operating  $T_{\rm A}$ -40 +85 temperature  $\Delta f_{\rm A}$ Any mode enabled 3.0 % Accuracy of the @  $T_{\rm A} = 25^{\circ} C$ output data rate  $\Delta f_{\rm T}$ (accelerometer and temperature sensor)

Table 1: Basic electrical parameter specification

The Tables 2, 3 and 4 provide the operating conditions for the accelerometer and the related performance and mechanical characteristics.

**Parameter** Symbol Condition Min Тур Max **Units**  $\pm 2$ Selectable via serial digital ±4 Acceleration range  $a_{FS}$ g ±8 interface  $\pm 16$ From suspend mode to first data Start-up time - Time to valid data sample (in high performance 3.15 ms  $t_{A,SU}$ mode  $f_{A,.} = 1600 Hz$ )

Table 2: Operating conditions for the accelerometer

Table 3: Performance characteristics of the accelerometer

| Parameter              | Symbol                 | Condition                                                              | Min    | Тур   | Max  | Units                            |  |

|------------------------|------------------------|------------------------------------------------------------------------|--------|-------|------|----------------------------------|--|

| Resolution             |                        |                                                                        |        | 16    |      | bit                              |  |

|                        | S <sub>A,2g</sub>      | $a_{\rm FS}$ = 2 $g$                                                   |        | 16384 |      |                                  |  |

| Concitivity            | $S_{A,4g}$             | $a_{\rm FS}$ = 4 $g$                                                   |        | 8192  |      | LSB                              |  |

| Sensitivity            | $S_{A,8g}$             | $a_{\rm FS}$ = 8 $g$                                                   |        | 4096  |      |                                  |  |

|                        | S <sub>A,16g</sub>     | $a_{\rm FS}$ = $16g$                                                   |        | 2048  |      |                                  |  |

| Sensitivity error      | $S_{A,err}$            | Soldered, over life time,                                              |        |       | 0.5  | %                                |  |

|                        |                        | $a_{\rm FS}$ = 8 $g$                                                   |        |       |      |                                  |  |

| Sensitivity error      | TCS                    | Full $T_{\rm A}$ range, best fit                                       |        | 0.005 |      | %<br>K                           |  |

| temperature drift      |                        | straight line                                                          |        |       |      |                                  |  |

| Zero-g offset          | O <sub>A</sub>         | Soldered                                                               |        | ±35   |      | mg                               |  |

| Zero-g onset           | $O_{ m A,life}$        | Soldered, over life time                                               |        | ±50   |      | mg                               |  |

| Zero-g offset          | TCO                    | Full $T_{\rm A}$ range, best fit                                       |        | ±0.2  |      | mg<br>K                          |  |

| temperature drift      |                        | straight line                                                          |        |       |      | K                                |  |

| Noise density          | n <sub>A,density</sub> | High performance mode,                                                 |        | 120   |      | $\frac{\mu g}{\sqrt{\text{Hz}}}$ |  |

|                        |                        | $a_{\rm FS}$ = 8 $g$                                                   |        |       |      | VIIZ                             |  |

| Nonlinearity error     | $S_{ m A,NL}$          | Best fit straight line,                                                |        | 0.2   |      | %FS                              |  |

|                        |                        | $a_{\rm FS}$ = 2 $g$                                                   |        |       |      |                                  |  |

| Output data rata (ODD) | $f_{A,\mathrm{hpm}}$ , | High performance mode                                                  | 12.5   |       | 6400 | Hz                               |  |

| Output data rate (ODR) | $f_{A,n}$              |                                                                        |        |       |      | HZ                               |  |

|                        | $f_{ m A,lpm}$         | Low-power mode                                                         | 1.5625 |       | 400  |                                  |  |

|                        | B <sub>A=12.5Hz</sub>  |                                                                        |        | 6.3   |      |                                  |  |

|                        | $B_{A=25Hz}$           |                                                                        |        | 12.5  |      |                                  |  |

|                        | $B_{A=50Hz}$           |                                                                        |        | 25    |      |                                  |  |

|                        | B <sub>A=100Hz</sub>   | $0Hz \le f \le f_{3dB-cutoff} \text{ of the }$                         |        | 50    |      |                                  |  |

| Bandwidth (BW) in high | $B_{\text{A=200Hz}}$   | accelerometer, $B_A = \frac{1}{2}f_A$                                  |        | 100   |      | Hz                               |  |

| performance            | $B_{A=400\mathrm{Hz}}$ | $-\frac{\text{accelerometer, } D_{A} - \frac{1}{2}I_{A}}{\text{[Hz]}}$ |        | 200   |      | 112                              |  |

|                        | $B_{\rm A=800Hz}$      | [ [114]                                                                |        | 400   |      |                                  |  |

|                        | B <sub>A=1600Hz</sub>  |                                                                        |        | 800   |      |                                  |  |

|                        | B <sub>A=3200Hz</sub>  |                                                                        |        | 850   |      |                                  |  |

|                        | B <sub>A=6400Hz</sub>  |                                                                        |        | 1675  |      |                                  |  |

Table 4: Mechanical characteristics of the accelerometer

| Parameter              | Symbol              | Condition              | Min | Тур | Max | Units |

|------------------------|---------------------|------------------------|-----|-----|-----|-------|

| Cross axis sensitivity | $S_{A,X}$           | Relative contribution  |     | 0.3 |     | %     |

|                        |                     | between any two of the |     |     |     |       |

|                        |                     | three axes             |     |     |     |       |

| Alignment error        | $\Delta \xi_{ m A}$ | Relative to package    |     | 0   |     | 0     |

|                        |                     | outline                |     |     |     |       |

Table 5 provides the temperature sensor related characteristics.

Table 5: Characteristics of the temperature sensor

| Parameter                     | Symbol           | Condition                    | Min    | Тур             | Max | Units    |

|-------------------------------|------------------|------------------------------|--------|-----------------|-----|----------|

| Resolution                    |                  |                              |        | 8               |     | bits     |

| Measurement Range             | $T_{\mathrm{S}}$ |                              | -41    |                 | 87  | °C       |

| Output at 23°C                |                  |                              |        | 0               |     | LSB      |

| Sensitivity                   | $S_{\mathrm{T}}$ |                              |        | 1               |     | LSB<br>K |

| Temperature offset            | O <sub>T</sub>   | After soldering              |        | ±1.5            |     | K        |

|                               |                  | @ $T_{\rm A} = 25^{\circ} C$ |        |                 |     |          |

| Temperature sensitivity error |                  | After soldering, $T_{ m P}$  |        |                 | ±18 | %        |

| Output Data Rate              | $f_{ m T,LPM}$   | Accelerometer in low         |        | $f_{\rm A,lpm}$ |     | Hz       |

| Output Data Nate              |                  | power mode                   |        | _               |     | пх       |

|                               | $f_{ m T,HPM}$   | Accelerometer in high        | 1.5625 |                 | 200 |          |

|                               |                  | performance mode             |        |                 |     |          |

## 2 Absolute Maximum Ratings

**Important:** Stress above limits stated in Table 6 may cause damage to the device. Exceeding the specified limits may affect the reliability of the device or can cause malfunction.

Table 6: Absolute maximum ratings

| Parameter                | Condition                         | Min  | Max               | Units |

|--------------------------|-----------------------------------|------|-------------------|-------|

| Voltage at Supply Pin    | $V_{\rm DD}$ = $V_{\rm DDIO}$ Pin | -0.3 | 4                 | V     |

| Voltage at any Logic Pin | Non-Supply Pin-out                | -0.3 | VDD + 0.3 and < 4 | V     |

| Passive Storage          | ≤ <b>6</b> 5                      | -50  | 150               | °C    |

| Temperature Range        |                                   |      |                   |       |

| OTP Non-Volatile         | <i>T</i> ≤ 85°C                   | 10   |                   | a     |

| Memory Data Retention    |                                   |      |                   |       |

| Mechanical Shock         | Duration $\leq 200 \mu s$         |      | 20000             | g     |

| ESD                      | HBM at any pin                    |      | 2000              | V     |

| 130                      | CDM                               |      | 500               | V     |

## 3 Quick Start Guide

The purpose of this chapter is to help developers to start working with the device by giving basic hands-on application examples. Before starting, the device has to be properly connected to the host and powered up.

## Notes on the Serial Interface Support

The communication between host processor and the device happens over one of the interfaces: I<sup>2</sup>C, I3C or SPI (4-wire and 3-wire). Each register read operation includes the following number of inserted dummy bytes before the payload:

- I<sup>2</sup>C: 0

- I3C: 1

- SPI: 1

For simplicity, the dummy bytes are not shown in the examples within this chapter. For more information about the interfaces and the protocol selection, please see Chapter 5. After power on reset or soft reset, the device is automatically configured in suspend mode.

## First Application Setup Example Procedures

After the proper power-up by applying the stable supply voltage to the corresponding device pins, the device enters automatically into the Power On Reset (POR) sequence. To ensure proper use of the device, certain configuration steps from the host are a mandatory prerequisite. The most typical operations will be explained in the following application examples by flow diagrams:

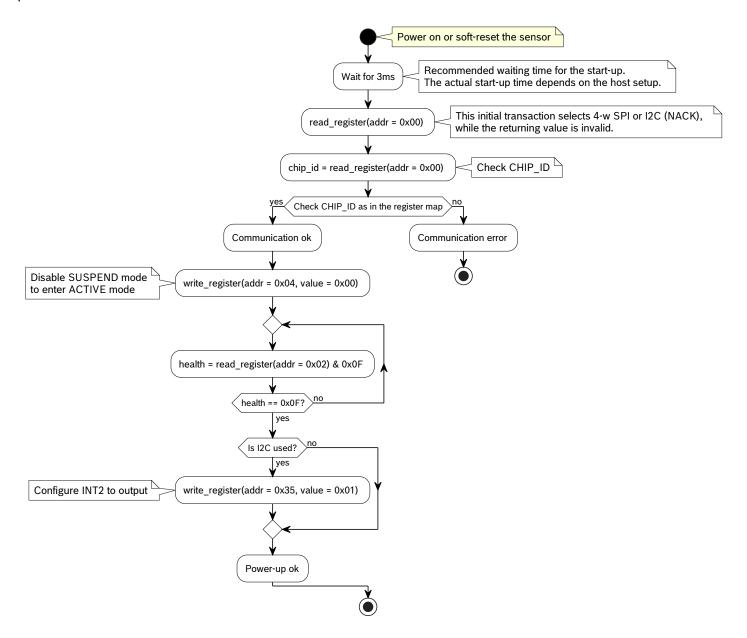

#### ■ Test communication and initialize the device in I<sup>2</sup>C or SPI 4-wire

Read the CHIP\_ID.chip\_id to ensure the correct communication. Before reading the CHIP\_ID.chip\_id, one initial transaction is required, while the returning value is invalid. This initial transaction determines the serial interface in either I<sup>2</sup>C or SPI 4-wire for later communication. Notably, the initial transaction through the I<sup>2</sup>C interface is not acknowledged by the sensor (NACK). Since the default power mode state of BMA580 is SUSPEND power mode state, the host must disable it for further operations. Also, it is recommended to read the health status of the sensor to ensure the proper power-on.

Figure 1: Device communication test

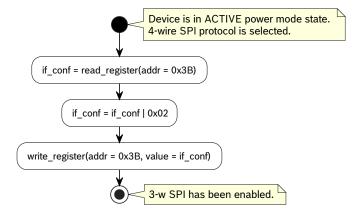

#### ■ Enable the SPI 3-wire interface:

Figure 2: Configure the SPI 3-wire interface

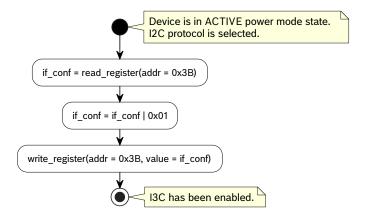

## ■ Enable the I3C interface:

Figure 3: Configure the I3C interface

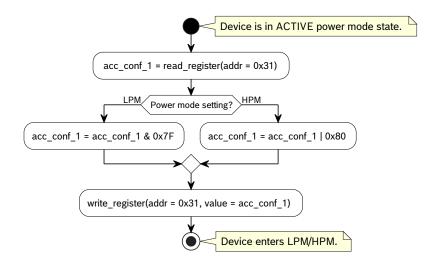

Configure the power mode state:

Figure 4: Configure the device power mode

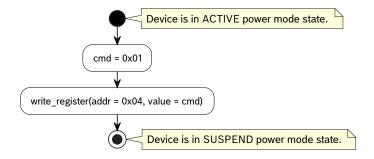

Configure the device in suspend mode:

Figure 5: Configure the device suspend mode

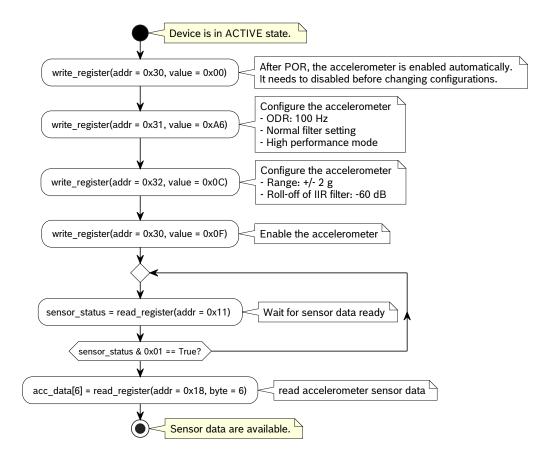

• Set the sensor parameters followed by reading the sensor data:

Figure 6: Configure the sensor parameters and read sensor data

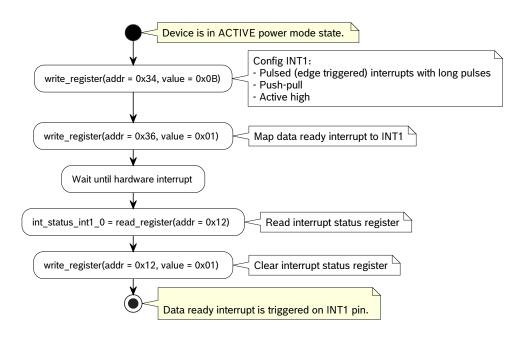

Map the data ready hardware interrupt:

Figure 7: Mapping hardware interrupt

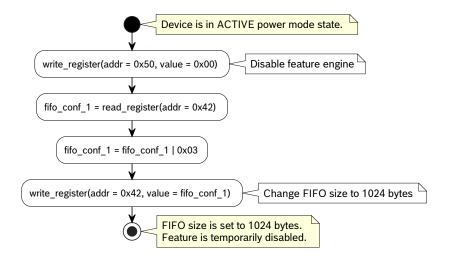

## Change the FIFO size:

Figure 8: Change FIFO size

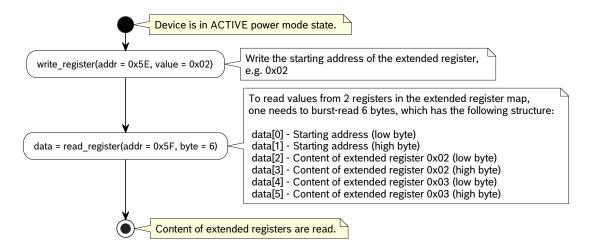

• Read the registers in the extended register map:

Figure 9: Read registers in the extended register map

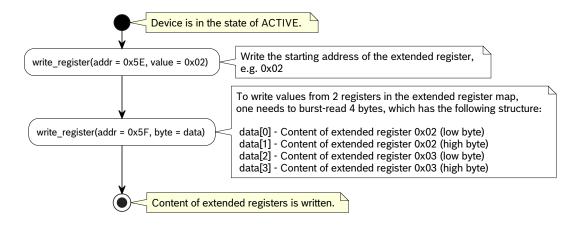

Write the registers in the extended register map:

Figure 10: Write registers in the extended register map

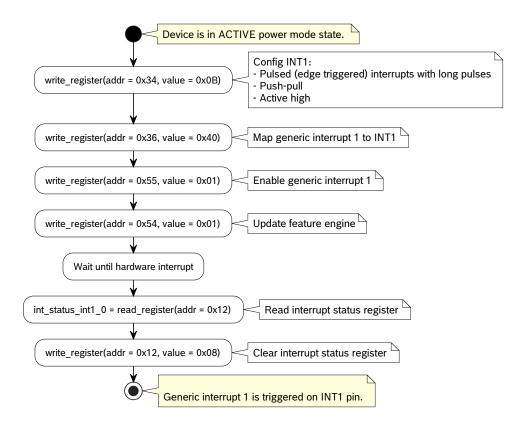

■ Enable advanced feature, e.g., generic interrupt 1:

Figure 11: Enable generic interrupt 1

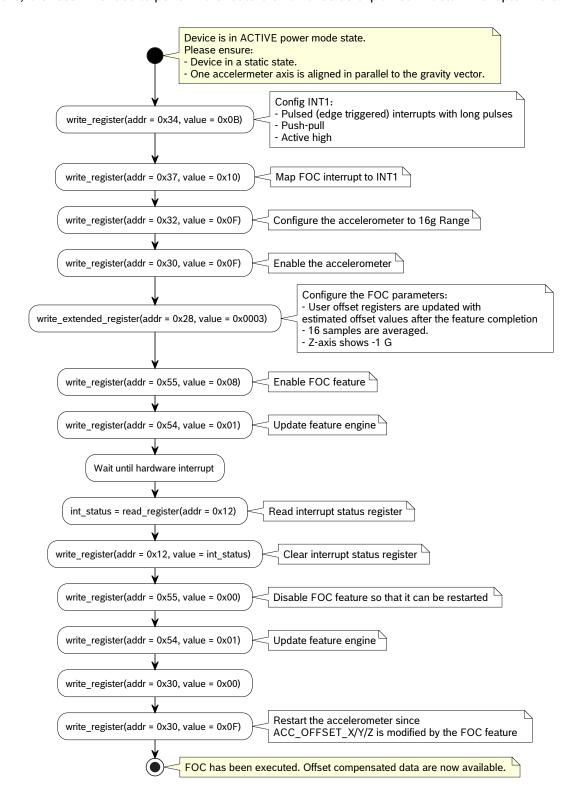

■ Enable the Fast Offset Compensation (FOC) feature on Z-axis in combination with INT1. For a complete FOC procedure, it is recommended to perform the feature on all axes as explained in detail in chapter 4.9.9.

Figure 12: Enable FOC feature in combination with INT1

## 4 Functional Description and Advanced Features

#### 4.1 Power Mode States

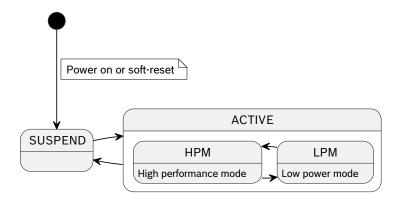

The BMA580 supports ACTIVE and SUSPEND power mode states, which can be switched in CMD\_SUSPEND. After power on or soft-reset, the default power mode state of BMA580 is SUSPEND. Conclusively, the switch process is illustrated in Figure 13.

Figure 13: Sensor power mode state diagram

#### 4.1.1 ACTIVE State

In ACTIVE state, the accelerometer is active and there is no restriction in accessing the register map. The device can enter two further performance modes, namely low power mode (LPM) and high performance mode (HPM), and switch between them while in the ACTIVE state. The main difference between the two modes is the data sampling behavior of the acceleration signal.

## High Performance Mode (HPM)

In HPM, data is sampled continuously and fed to the filter that is configured by the host.

## Low Power Mode (LPM)

In LPM, only the necessary number of data is sampled for the average purpose, so that one can optimize the power consumption. However, since the acceleration signal is undersampled, the duty-cycling mode is prone to aliasing effects.

#### 4.1.2 SUSPEND State

In the SUSPEND state, the accelerometer is inactive and the internal oscillator is also shut down. In this mode, the register content prior to entering this power mode will be retained. Also, the host is limited to access the CHIP\_ID, CMD\_SUSPEND and CMD.cmd registers. Notably, executing soft-reset is possible in the SUSPEND mode.

Please also note that, once in the SUSPEND state, both INT1 and INT2 pins are configured in high-impedance state. To prevent the error interrupt detection by the host due to signal cross-talk, it is suggested to pull-up or pull-down the interrupt pins from the host side.

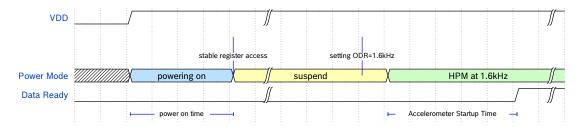

#### 4.1.3 Power on Time

The power on time of the BMA580 is typically 1.8ms (see also specification table 1). The power on time describes the time between powering the device ( $V_{\rm DD} \ge 1.62$ V) and the interface being ready to respond with stable register access. During the powering phase, the device will not be able to respond to any command sent on the serial interface.

Note that the power on time may vary if the ramp of VDD between 0V and 1.62V, which is controlled by the host, takes a longer time.

Figure 14: Power on Time

The power on time does not include the processing of the first acceleration value. See chapter 4.2.9 for more information about the time for the first valid data.

#### 4.2 Accelerometer

#### 4.2.1 Accelerometer Data

The three-dimensional acceleration data are provided with 16 bits width in two's complement representation, which are available in registers from ACC\_DATA\_0 to ACC\_DATA\_5. The 16 bits acceleration data for each axis contain a high byte and a low byte. To ensure the data integrity, the content in ACC\_DATA\_0 to ACC\_DATA\_5 must be read in a single burst read.

The output acceleration data are in LSB unit. They can be converted to a g unit using the following formula:

$$ACC [g] = 2's(ACC_{High} [LSB] \ll 8 + ACC_{Low} [LSB]) \times \frac{a_{FS}}{2^{15}}, \tag{4.1}$$

where  $a_{FS}$  is the acceleration range. The selection of the acceleration range leads to different sensitivity, as concluded in table 7;  $ACC_{High}$  and  $ACC_{Low}$  are the high byte and low byte of the acceleration data, respectively; "2's()" is the calculation of two's complement.

| Acceleration range | Sensitivity (t  | ypical value)      |

|--------------------|-----------------|--------------------|

| 2 g                | 1 g = 16384 LSB | 1 LSB = 61.035 µg  |

| 4 g                | 1 g = 8192 LSB  | 1 LSB = 122.070 μg |

| 8 g                | 1 g = 4096 LSB  | 1 LSB = 244.141 μg |

| 16 g               | 1 g = 2048 LSB  | 1 LSB = 488.281 μg |

Table 7: Sensitivity under different acceleration ranges

For example, if  $a_{\rm FS}$ = 8 g is selected, the acceleration data of 0x7FFF represents 8 g, while 0x8001 represents -8 g. Please note that, the the acceleration data of 0x8000 represents an invalid value, which occurs e.g., when the host sets an invalid configuration, or when the acceleration data is not yet ready after the power-on or during the configuration change.

## 4.2.2 Accelerometer Data Processing

The acceleration signals and the temperature data are processed according to the configured settings from corresponding registers (ACC\_CONF\_0 - ACC\_CONF\_2 and TEMP\_CONF). Additionally, the acceleration signals of the device can be compensated through the registers from ACC\_OFFSET\_0 to ACC\_OFFSET\_5. Please note that values in these registers are not persistent and must be written each time after the power-up or reset of the device.

## 4.2.3 Accelerometer Configuration

The host can configure the accelerometer via registers from ACC\_CONF\_0 - ACC\_CONF\_2. In detail:

- ACC\_CONF\_0 is used to enable or disable the accelerometer. Please note that, in BMA580, the accelerometer is disabled by default after power on, since the default power mode state is SUSPEND.

- ACC\_CONF\_1 is used to select the output data rate (ODR), the bandwidth parameter (BWP) for the filter configuration and the performance mode.

- ACC\_CONF\_2 is used to select the dynamic range, the filter roll-off, the measurement preference and clear mechanism

of the acceleration data ready interrupt.

- CONFIG\_STATUS.acc\_conf\_err indicates invalid or valid accelerometer configurations.

## 4.2.4 Accelerometer Performance Mode

The device has two performance modes, namely low power mode (LPM) and high performance mode (HPM). The mode switching is controlled by the register field ACC\_CONF\_1.power\_mode. Only in LPM the overall power consumption depends strongly on the chosen ODR and the amount of averaged samples. Typical values can be seen in table 8.

Table 8: Current Consumption (typical values) depending on ODR and number of averaged samples in LPM at  $V_{DD}$  = 1.8 V,  $T_A$  = 25°C.

|         | current consumption - typical (μΑ) |       |       |  |  |  |

|---------|------------------------------------|-------|-------|--|--|--|

| ODR(Hz) | No Avg                             | Avg 2 | Avg 4 |  |  |  |

| 1.5625  | 7.1                                | 7.1*  | 7.1*  |  |  |  |

| 12.5    | 8.3                                | 8.4*  | 8.8*  |  |  |  |

| 25      | 9.6*                               | 10.0* | 10.9* |  |  |  |

| 50      | 12.4                               | 13.2* | 15.0* |  |  |  |

| 100     | 18.0                               | 19.7  | 23.3  |  |  |  |

| 200     | 28.9                               | 32.7* | 39.9* |  |  |  |

| 400     | 51.1                               | 58.6* | 73.1* |  |  |  |

(\*) estimated values.

## 4.2.5 Accelerometer Effective Bandwidth

The effective bandwidth of the accelerometer depends on the selection of ODR and BWP in register ??. For the HPM the effective bandwidth is nearly half of ODR for BWP=2 ("normal mode") or BWP=3 ("CIC mode") and ODR smaller than 1.6 kHz. The effective bandwidth is ODR/4 for BWP=1 ("OSR2 mode") and ODR/8 for BWP=0 ("OSR4 mode"). The effective bandwidth for ODR bigger than 1.6 kHz is limited to a value of 1.675 kHz.

For the LPM the effective bandwidth is only determined by the ODR and is always equal to ODR/2. With the help of the BW value the number of averaged samples for each ODR data sample can be selected: higher number of averaged samples lead to less noise but higher current consumption.

## 4.2.6 Accelerometer Change Configuration

Before the host changes the accelerometer configuration, it is recommended to disable the accelerometer first. The host can again enable the accelerometer after the configuration is finished. Any change of the accelerometer configuration is applied immediately.

After the configuration change, the host needs to wait for a certain time until the first valid sample is available. This waiting time depends on the changed configuration and the timing of the change. Please note that, in HPM, all samples after the first valid sample are given at the expected ODR. In LPM, it can sometimes occur that the time interval between the first and second samples is not as expected. This is meant for a quick data delivery in the LPM mode. The host can skip the first and second samples if an accurate ODR is necessary.

#### 4.2.7 Accelerometer Self-Test

The BMA580 has a comprehensive self-test function for the MEMS element by applying electrostatic forces to the sensor core instead of external accelerations. By actually deflecting the seismic mass, the entire signal path of the sensor can be tested. The activation of the self-test results in a static offset of the acceleration data. Any external acceleration or gravitational force applied to the sensor during active self-test will be observed in the output as a superposition of both acceleration and self-test signal.

The self-test is activated and deactivated for all axes via ACC\_SELF\_TEST.self\_test. It is also possible to control the direction of the deflection through ACC\_SELF\_TEST.self\_test\_sign. The excitation occurs in positive (negative) direction if ACC\_SELF\_TEST.self\_test\_sign = 0b1 (0b0).

In below, the recommended procedure to use the self-test is given:

- 1. Disable all advanced features and interrupts, if any of them are enabled.

- 2. Activate the self-test

- a. Disable the accelerometer in ACC\_CONF\_0.sensor\_ctrl

- **b.** Apply the following configurations:

- ACC\_CONF\_1.acc\_odr = 10

- ACC\_CONF\_1.acc\_bwp = 2

- ACC\_CONF\_1.power\_mode = 1

- ACC\_CONF\_2.acc\_range = 2

- ACC\_CONF\_2.acc\_iir\_ro = 1

- ACC\_CONF\_2.noise\_mode = 0

- ACC\_CONF\_2.acc\_drdy\_int\_auto\_clear = 0

- c. Enable the accelerometer in ACC\_CONF\_0.sensor\_ctrl

- d. Wait for at least 10 ms

- e. Enable self-test and set the negative self-test polarity by setting

- ACC\_SELF\_TEST.self\_test\_sign = 0

- ACC\_SELF\_TEST.self\_test = 1

- f. Wait for at least 10 ms

- **g.** Read and store valid data of each axis from registers ACC\_DATA\_0 to ACC\_DATA\_5. Please check in SENSOR\_STATUS. acc\_data\_rdy before reading, if the valid data is ready.

- h. Enable self-test and set the positive self-test polarity by setting

- ACC\_SELF\_TEST.self\_test\_sign = 1

- ACC\_SELF\_TEST.self\_test = 1

- i. Wait for at least 10 ms

- j. Read and store valid data of each axis from registers ACC\_DATA\_0 to ACC\_DATA\_5. Please check in SENSOR\_STATUS. acc\_data\_rdy before reading, if the valid data is ready.

- k. Check self-test results:

- i. Convert values from steps 2g and 2j for each axis. Please note that those values are signed values, so the host has to apply the two's complement calculation to the raw data.

- ii. Calculate the difference between the values from step 2g and 2j

- **iii.** Compare the difference against the minimum threshold values in Table 9. To pass the self-test, the measured difference has to exceed the minimum threshold value.

Table 9: Minimum threshold value of self-test

| x-axis (LSB) | y-axis (LSB) | z-axis (LSB) |

|--------------|--------------|--------------|

| 17500        | 17500        | 8000         |

- I. Disable the self-test by setting

- ACC\_SELF\_TEST.self\_test = 0

- **3.** It is recommended to perform a soft-reset of the device after the self-test. Please note that, after the soft-reset, all user configuration settings are overwritten with their default state. If the soft-reset cannot be performed, the following sequence is required to reset the signal path:

- a. Disable the accelerometer in ACC\_CONF\_0.sensor\_ctrl

- **b.** Wait for at least 1 ms

- c. Enable the accelerometer in ACC\_CONF\_0.sensor\_ctrl

- **4.** Now the host can apply user configuration to the accelerometer and again enable the advanced features and interrupts.

## 4.2.8 Accelerometer Data Ready Interrupt

This interrupt fires whenever a new data sample set from accelerometer. This allows a low latency data readout.

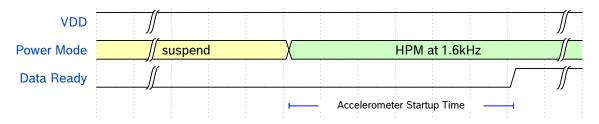

## 4.2.9 Accelerometer Startup Time (Time to valid data)

The accelerometer startup time of the BMA580 is typically 3.15ms (see also specification table 2). The accelerometer startup time describes the time between leaving the suspend mode and the availability of the first valid acceleration data, if the selected power mode is HPM and the selected ODR is 1600Hz. The BMA580 can indicate this time point with an interrupt, if the data ready trigger is selected. See chapter 4.5 for more details. During the powering phase the device will not be able to respond to any command sent on the serial interface.

Please note, that the accelerometer startup time may vary, if a different power mode is selected or a different ODR.

Figure 15: Accelerometer Startup Time

The accelerometer startup time is also related to the power on time, but not overlapping. For more information on the power on time, see chapter 4.1.3. The following picture shows both times in an example illustration:

Figure 16: Power on Time and Accelerometer Startup Time

## 4.2.10 Accelerometer Offset Compensation

The BMA580 offers manual compensation. The offset compensation is effective for data in ACC\_DATA\_0 - ACC\_DATA\_5 and FIFO, and signals for the advanced features. If necessary the result of this computation is saturated to prevent any overflow errors (the smallest or biggest possible value is set, depending on the sign).

The offset compensation uses of the registers ACC\_OFFSET\_0 to ACC\_OFFSET\_5, providing a compensation value for each accelerometer axis x, y, z, respectively. The contents of the compensation register ACC\_OFFSET\_0 to ACC\_OFFSET\_5

may be set manually via the digital interface. It is recommended to restart the accelerometer after writing new values to the compensation register or write to the compensation register, while the accelerometer is disabled (see register ACC\_CONF\_0).

To disable the offset compensation, a value of 0x0 has to be written to all the compensation register ACC\_0FFSET\_0 to ACC\_0FFSET\_5.

The offset compensation registers have a width of 9 bit using two's-complement binary notation. The offset resolution is 0.98 mg (1024 LSB/g) with an offset range of +/-0.25 g. Please note that the resolution of the offset register is independent of the range setting (see register ACC\_CONF\_2.acc\_range). The compensation offset values are not persistent and must be written each time after power-up or reset of the device.

The BMA580 offers also the "Fast Offset Compensation" (FOC) feature, which is described in chapter 4.9.9.

## 4.3 Sensor time

The device supports the concept of sensor time. Its core element is a free running counter with a width of 24 bits. It runs at the frequency of 3.2 kHz, while the time resolution is 312.5 µs. The host can access the current state of the counter by reading registers from SENSOR\_TIME\_0 to SENSOR\_TIME\_2. The sensor time counter is synchronized with the data capturing event in the register from ACC\_DATA\_0 to ACC\_DATA\_5 and FIFO.

Please note that a burst read on register from SENSOR\_TIME\_0 to SENSOR\_TIME\_2 delivers always consistent values. Once the device enters the SUSPEND power mode state, the sensor time counter stops.

## 4.4 Temperature Sensor

The BMA580 provides a temperature sensor, sensing the internal temperature of the device. The temperature sensor is always on, when the accelerometer sensor is active.

The temperature sensor has 8 bits, the data can be read from register field TEMP\_DATA.temp\_data. The data register output is of the unit K. A data value of 0x0 means 23°C. The sensor can be configured via the register TEMP\_CONF: The output data rate for the temperature sensor can be set in the field TEMP\_CONF.temp\_rate

When there is no valid temperature information available, the temperature indicates an invalid value (0x80) and the register field SENSOR\_STATUS.temperature\_rdy shows a 0x0.

## 4.4.1 Temperature sensor and external voltage measurement

By using the temperature sensor, the BMA580 can also measure the external voltages via interrupt pins in the I<sup>2</sup>C mode. In below, the recommended procedure to use the external measurement feature is given:

- Enable accelerometer by setting ACC\_CONF\_0.sensor\_ctrl = 0x0F.

- 2. Configure the temperature sensor via TEMP\_CONF

- a. Choose 200 Hz as the sample rate by setting TEMP\_CONF.temp\_rate = 0b111

- Select the external voltage as the input source for the temperature sensor by setting TEMP\_CONF.temp\_meas\_src= 0b0

- c. Select the interrupt pin for the voltage measurement via TEMP\_CONF.temp\_ext\_sel

- **d.** Be sure to set the reserved bits (bits 5 to 7) in TEMP\_CONF to 0b000.

- 3. Apply the external voltage on the selected interrupt pin

- 4. Clear the temperature ready flag SENSOR\_STATUS.temperature\_rdy

- 5. Wait until SENSOR\_STATUS.temperature\_rdy becomes 0b1

- **6.** Burst-read measurement data from  $AUX_{Low}$  [LSB] = AUX\_DATA\_0 and  $AUX_{High}$  [LSB] = AUX\_DATA\_1

- **7.** Combine  $AUX_{Low}$  and  $AUX_{High}$  to 16-bit value AUX:

$$AUX[LSB] = AUX_{High}[LSB] \ll 8 + AUX_{Low}[LSB]$$

(4.2)

**8.** Calculate the external voltage  $V_{ext}$  using the following equation:

$$V_{ext}[V] = \frac{AUX[LSB] - 2^{15}}{2^{15}} \times 1.6$$

(4.3)

After the measurement of the external voltage is finished, the host needs to configure TEMP\_CONF so that the temperature sensor can be again used.

## 4.5 Interrupt Pin Configuration

The BMA580 has two external pins to provide the status of feature events. For certain digital interface settings, these pins are not available for this interrupt behavior but used by the digital interface. In I<sup>2</sup>C and I3C mode the two external pins are available for the feature events. In SPI 3-Wire mode, one pin is still available and in SPI 4-Wire mode no external pin is available to provide feature events. See table 39 and chapter 5 for more details.

## 4.5.1 Electrical Interrupt Pin Behavior

The electrical behavior of interrupt pins INT1 and INT2 can be configured in the register INT1\_CONF and INT2\_CONF, respectively.

## 4.5.1.1 Output Mode

In the register fields INT1\_CONF.mode and INT2\_CONF.mode, the output on the pins can be enabled/disabled, and the output mode can be configured between latch, short pulses and long pulses mode. Please note that, if the output pin is disabled, the interrupt status will not be updated.

- In the latch mode, the interrupt output is active when the status bit of any mapped interrupt source is set. It will remain active until cleared.

- In the short and long pulses mode, the interrupt output is active when the status bit of any mapped interrupt source is set. Then, after a certain pulse duration, the the interrupt output becomes automatically inactive, while the corresponding status bit of any mapped interrupt source remains uncleared. In other words, the host needs to clear the interrupt status bit if necessary. Table 10 provides the typical pulse duration in the short and long pulses mode.

Table 10: Pulse duration in the short and long pulses mode

|                     | Short pulses mode | Long pulses mode |

|---------------------|-------------------|------------------|

| Typ. pulse duration | 625 ns            | 10 us            |

Especially, in addition to the common output mode setting, the auto clear mechanism of the data ready interrupt can be configured in ACC\_CONF\_2.acc\_drdy\_int\_auto\_clear. When this option is enabled, the status flag of acc\_drdy\_int is cleared automatically after the half of the ODR duration. This saves the need for the host to clear each data ready interrupt status. Please note that, it is recommended to enable the auto clear mechanism in latch mode, but not in pulses mode, since the pulses mode behaves already similarly to the auto clearing with small difference.

#### 4.5.1.2 Output Characteristics

The characteristic of the output driver of the interrupt pins may be configured with fields INT1\_CONF.od and INT2\_CONF. od. By setting these bits to 0b1, the output driver shows open-drain characteristic. By setting the configuration bits to 0b0, the output driver shows push-pull characteristic. The electrical behavior of the interrupt pins, whenever an interrupt is triggered, can be configured as either "active-high" or "active-low" via INT1\_CONF.1v1 respectively INT2\_CONF.1v1.

Please note the high impedance state of interrupt pins when the BMA580 is in the SUSPEND state, as already mentioned in chapter 4.1.2.

## 4.5.2 Interrupt Pin Mapping

In order for the host to react to the features output, they can be mapped to the external pin INT1 or pin INT2, by setting the corresponding bits from the registers INT\_MAP\_0, INT\_MAP\_1 and INT\_MAP\_3. To disconnect the features outputs to the

external pins, the same corresponding bits must be reset, from those registers. Once a feature triggers the output pin, the host can read out the corresponding bit from the register INT\_STATUS\_INT1\_0, INT\_STATUS\_INT1\_1,INT\_STATUS\_INT2\_0 or INT\_STATUS\_INT2\_1.

Besides to the two external pins, the interrupts can also be mapped to the I3C in band interrupts (IBI), if the BMA580 is in I3C mode. In this case, the status can be handled in the register INT\_STATUS\_I3C\_0 and INT\_STATUS\_I3C\_1.

BMA580 allows the host to map multiple interrupt sources to the same destinations, e.g. INT1, INT2, I3C IBI. In this case, to clear the status of that destination, each single mapped source needs to be cleared individually. On the other hand, BMA580 does not support mapping a interrupt source to several destinations in parallel.

## 4.5.3 Measurement of external signals on Interrupt Pins

Instead of using the external pins INT1 and INT2 as destination for internal triggers, the pins can be configured to be an input for an external voltage in the range of 0.1V to 0.9V. If this feature is enabled via the register field TEMP\_CONF. temp\_meas\_src and TEMP\_CONF.temp\_ext\_sel, no temperature value is available anymore. The data of the external voltage is digitalized and can be read in the register field AUX\_DATA\_0.aux\_data\_7\_0 and AUX\_DATA\_1.aux\_data\_15\_8.

## 4.5.4 Clear Interrupt Status

In BMA580, the interrupt status is cleared upon writing 1'b1 to the corresponding interrupt status bit.

## 4.5.5 Interrupt Behavior Example

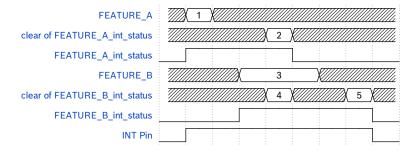

For a better understanding of the interrupt pin behavior of BMA580, the following examples under various configurations are provided. For simplicity, the "INT pin" represents both INT1 and INT2 pins, and the electrical behavior of the interrupt pins is configured as "active-high".

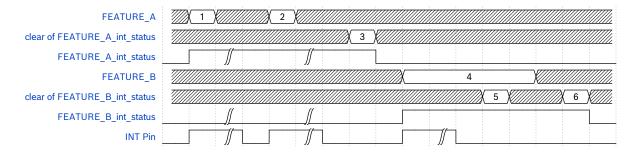

**Latch Mode** Figure 17 shows the timing diagram when the latch mode is configured. FEATURE\_A and FEATURE\_B can represent any interrupt source, and are mapped to the same INT pin target. Detailed explanations of the timing diagram are provided in below:

- When the interrupt event "1" of FEATURE\_A comes, the corresponding FEATURE\_A\_int\_status is set immediately high. FEATURE\_A\_int\_status is cleared after the host executes the clear operation at "2".

- When the interrupt event "3" of FEATURE\_B comes, the corresponding FEATURE\_B\_int\_status is set immediately high. While the interrupt event "3" of FEATURE\_B remains active, a clear operation such as "4" will fail to clear the FEATURE\_B\_int\_status. This describes the case of e.g., FIFO full interrupt. FEATURE\_B\_int\_status can be cleared at "5", when FEATURE\_B is no more active.

- The INT pin is set to high as long as one of the interrupt status is active.

Figure 17: Interrupt output in latch mode

**Pulses Mode** Figure 18 shows the timing diagram when the pulses mode is configured. FEATURE\_A and FEATURE\_B can represent any interrupt source, and are mapped to the same INT pin target. Detailed explanations of the timing diagram are provided in below:

- When the interrupt event "1" of FEATURE\_A comes, the corresponding FEATURE\_A\_int\_status is set immediately high, so is the INT pin. Since the pulses mode is configured, the INT pin turns to low after the duration defined in table 10. Then, when another interrupt event "2" of FEATURE\_A comes, a pulse signal is again generated on the INT pin without the FEATURE\_A\_int\_status to be cleared. At the end, FEATURE\_A\_int\_status is cleared after the host executes the clear operation at "3".

- When the interrupt event "4" of FEATURE\_B comes, the corresponding FEATURE\_B\_int\_status is set immediately high, so is the INT pin. Since the pulses mode is configured, the INT pin turns to low after the duration defined in table 10. While the interrupt event "4" of FEATURE\_B remains active, a clear operation such as "5" will fail to clear the FEATURE\_B\_int\_status. This describes the case of e.g., FIFO full interrupt. FEATURE\_B\_int\_status can be cleared at "6", when the FEATURE\_B is no more active.

Figure 18: Interrupt output in pulses mode

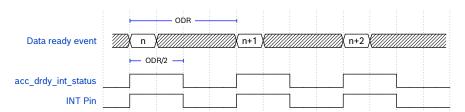

**Auto Clear Mechanism of the Data Ready Interrupt** Figure 19 shows the timing diagram when the auto clear mechanism of the data ready interrupt is enabled. Both the acc\_drdy\_int and INT pin is cleared automatically after the half of the ODR duration.

Figure 19: Interrupt output when auto clear mechanism of the data ready interrupt is enabled

#### **4.6 FIFO**

The BMA580 provides a first-in first-out (FIFO) data buffer for the accelerometer data as well as optionally the sensor time. The size of this FIFO is configurable with a maximum of 1024 bytes.

## 4.6.1 FIFO Configuration

The FIFO can be configured by the user registers FIFO\_CONF\_0 and FIFO\_CONF\_1.

#### 4.6.1.1 Enabling FIFO

The register FIFO\_CONF\_0 is used to enable or disable the complete FIFO functionality or to sample only individual axis.

#### 4.6.1.2 FIFO Compression

The field FIFO\_CONF\_0.fifo\_compression can be configured to store only 8 bit of acceleration data. If the compression is enabled, only the high byte of the acceleration data is stored, e.g., ACC\_DATA\_1.acc\_x\_15\_8.

#### 4.6.1.3 Sensor Time in FIFO

The field FIFO\_CONF\_1.fifo\_sensor\_time can be configured to disable the sensor time, to send dedicated sensor time frame, or to append sensor time to each frame. For more information of the dedicated sensor time frame, please refer to section 4.6.2.4.

## 4.6.1.4 FIFO Stop-on-full Mode

The FIFO stop-on-full mode can be configured in the field FIFO\_CONF\_1.fifo\_stop\_on\_full, and the full level is defined as the FIFO size minus two times the payload size.

#### 4.6.1.5 FIFO Size

The size of this FIFO is configurable with a maximum of 1024 bytes. The default is 512 bytes, which allows the feature engine to work in parallel to the FIFO. The FIFO size can be configured with the help of the register field FIFO\_CONF\_1. fifo\_size. Since FIFO and the feature engine share a common memory, the size configuration is locked when the feature engine is enabled. Then this register is controlled by the feature engine and the value might change depending on the chosen features with their possible configuration.

The register field FIFO\_CONF\_1.fifo\_size can only be changed, once the feature engine is disabled. With the feature engine disabled, a FIFO size up to 1024 bytes is possible, while with the feature engine enabled, a FIFO size of 512 bytes or less is possible.

## 4.6.2 FIFO Frames

#### 4.6.2.1 FIFO Header

The FIFO header has the following structure in below:

Table 12: Register Map Overview

| Legend |        | Read  | Read-only Read/Wri |            | /Write | Vrite Write-only |          | Reserved |          |          |

|--------|--------|-------|--------------------|------------|--------|------------------|----------|----------|----------|----------|

| Index  | Name   | Value | bit7               | bit6       | bit5   | bit4             | bit3     | bit2     | bit1     | bit0     |

| 0x0    | HEADER | 0x80  | const_1            | frame_type |        | compr_en         | acc_z_en | acc_y_en | acc_x_en | acc_t_en |

Please note that the FIFO header is not stored in the memory while generated during the FIFO read-out process. This needs to be considered cautiously, when the host calculates the correct number of data frames in the FIFO.

**Field frame\_type** Field frame\_type encodes the type of payload data:

- 2'b00: empty frame

- 2'b10: acceleration data frame

- 2'b01: dedicated sensor time frame

**Field acc\_x/y/z\_en** Field acc\_x/y/z\_en displays the selection of accelerometer axis in the FIFO. If the acc\_x/y/z\_en field of the header equals 1'b1, the corresponding axis data is contained in the FIFO frame. Otherwise, the axis data is not part of the FIFO frame. The order of the payload bytes is x, y and z.

**Field compr\_en** Field compr\_en displays the enabling state of FIFO data compression. If data compression is enabled (FIFO\_CONF\_0.fifo\_compression = 1'b1), each enabled axis contributes one byte (the MSB) to the payload. Otherwise, each enabled axis contributes two bytes to the payload.

**Field acc\_t\_en** Field acc\_t\_en displays the enabling state of sensor time in each FIFO frame. The host can choose the way to display sensor time by configuring FIFO\_CONF\_1.fifo\_sensor\_time, which can change the header format. This is explained in 4.6.2.3 and 4.6.2.4.

## 4.6.2.2 Empty Frame

An empty frame has no payload and only consists of a single byte as header.

Table 14: Register Map Overview

| Legend |        | Read-only Rea |         | Read       | /Write | Write-only |          | Reserved |          |          |

|--------|--------|---------------|---------|------------|--------|------------|----------|----------|----------|----------|

| Index  | Name   | Value         | bit7    | bit6       | bit5   | bit4       | bit3     | bit2     | bit1     | bit0     |

| 0x0    | HEADER | 0x80          | const_1 | frame_type |        | compr_en   | acc_z_en | acc_y_en | acc_x_en | acc_t_en |

#### 4.6.2.3 Acceleration Data Frame

The number of payload bytes depends on the configuration of FIFO\_CONF\_0 and FIFO\_CONF\_1. If the FIFO is configured in such a way that the payload would be 0 (i.e. no axis enabled, no sensor time), no data will be stored in the FIFO memory and only empty frames will be read.

The minimum data frame size is 2 byte, when only a single axis and data compression is enabled.

If FIFO\_CONF\_1.fifo\_sensor\_time is configured as 2'b10, the sensor time is appended to each data frame. Please note that the sensor time data in each data frame occupies the FIFO space.

For an acceleration data frame the maximum frame size looks as follows:

Table 16: Register Map Overview

| Legend |           | Read-only |                    | Read/Write |          | Write-only |          | Reserved |          |      |

|--------|-----------|-----------|--------------------|------------|----------|------------|----------|----------|----------|------|

| Index  | Name      | Value     | bit7               | bit6       | bit5     | bit4       | bit3     | bit2     | bit1     | bit0 |

| 0x0    | HEADER    | 0xCF      | const_1 frame_type |            | compr_en | acc_z_en   | acc_y_en | acc_x_en | acc_t_en |      |

| 0x1    | PAYLOAD_0 | 0x00      |                    | acc_x_7_0  |          |            |          |          |          |      |

| 0x2    | PAYLOAD_1 | 0x00      |                    | acc_x_15_8 |          |            |          |          |          |      |