SOP-8EP

Pin Definition:

1. GND 8. EN 2. FB 7. POK 3. VOUT 6. VCNTL 4. VOUT 5. VIN

#### **General Description**

The TS9230 is a 3A ultra low dropout voltage regulator. This product is specifically designed to provide well supply voltage for front-side-bus termination on motherboards and NB applications. The IC needs two supply voltages, a control voltage for the circuitry and a main supply voltage for power conversion, to reduce power dissipation and provide extremely low dropout. The TS9230 integrates multi-functions. A Power-On-Reset (POR) circuit monitors both supply voltages to prevent wrong operations. A thermal shutdown and current limit functions protect the device against thermal and current over-loads. A POK indicates the output status with time delay which is set internally. It can control other converter for power sequence. The TS9230 can be enabled by other power system. Pulling and holding the EN pin below 0.4V shuts off the output.

### **Features**

- Ultra Low Dropout 200mV(typ) @ I<sub>OUT</sub>=3A

- Suit for Low ESR Output Capacitor (MLCC)

- 0.5V Reference Voltage

- Fast Transient Response

- Adjustable Output Voltage

- Power-On-Reset for VCNTL and VIN Pins

- Internal Soft-Start

- Under-Voltage Protection

- Current-Limit Protection

- Thermal Shutdown Protection

- Power-OK Output with a Delay Time

### **Ordering Information**

| Part No.     | Package | Packing            |  |

|--------------|---------|--------------------|--|

| TS9230CS RLG | SOP-8EP | 2.5Kpcs / 13" Reel |  |

Note: "G" denote for Halogen Free Product

### <u>Application</u>

- Telecommunication

- Notebook

- Mother Board

### **Absolute Maximum Rating**

| Parameter                                           | Symbol            | Limit                          | Unit      |     |

|-----------------------------------------------------|-------------------|--------------------------------|-----------|-----|

| V <sub>CNTL</sub> Supply Voltage                    | V <sub>CNTL</sub> | -0.3 to 7                      | V         |     |

| V <sub>IN</sub> Supply Voltage                      |                   | V <sub>IN</sub>                | -0.3 to 6 | V   |

| EN and FB Pin Voltage                               | V <sub>I/O</sub>  | -0.3 to V <sub>CNTL</sub> +0.3 | V         |     |

| Power good Voltage                                  | V <sub>POK</sub>  | -0.3 to 7                      | V         |     |

| Power Dissipation SOP-8EP                           |                   | PD                             | 2.5       | W   |

| Storage Temperature Range                           | T <sub>ST</sub>   | -65 to +150                    | C         |     |

| Junction Temperature Range                          | TJ                | -40 to 125                     | C         |     |

| Operating Temperature Range                         | T <sub>OP</sub>   | -40 to +85                     | C         |     |

| Thermal Resistance from Junction to case SOP-8EP    |                   | $\theta_{JC}$                  | 15        | €\M |

| Thermal Resistance from Junction to ambient SOP-8EP |                   | $\theta_{JA}$                  | 40        | €\M |

**Recommended Operating Condition**

| Parameter                        | Symbol           | Conditions                                | Limit                                     | Unit |

|----------------------------------|------------------|-------------------------------------------|-------------------------------------------|------|

| V <sub>CNTL</sub> Supply Voltage | $V_{CNTL}$       |                                           | 3 to 5.5                                  | V    |

| V <sub>IN</sub> Supply Voltage   | V <sub>IN</sub>  |                                           | 0.9 to 3.65                               | V    |

| Output Voltage                   | V <sub>OUT</sub> | V <sub>CNTL</sub> -V <sub>OUT</sub> >1.9V | 0.6 to V <sub>IN</sub> -V <sub>DROP</sub> | V    |

| Output Current                   | I <sub>OUT</sub> |                                           | 0 to 3                                    | Α    |

### **Electrical Specifications**

$(V_{CNTL}$ =5V,  $V_{IN}$ =1.5V,  $V_{OUT}$  =1.2V,  $T_A$ =25 $^{\circ}$ C unless otherwise specified)

| Parameter                                 | Symbol                 | Conditions                                                                        | Min       | Тур  | Max  | Units |

|-------------------------------------------|------------------------|-----------------------------------------------------------------------------------|-----------|------|------|-------|

| V <sub>CNTL</sub> POR Threshold           | $V_{CNTL}$             |                                                                                   | 2.5       | 2.7  | 2.9  | V     |

| V <sub>CNTL</sub> POR Hysteresis          | V <sub>CNTL(hys)</sub> |                                                                                   | A         | 0.5  |      | V     |

| V <sub>IN</sub> POR Threshold             | V <sub>IN</sub>        |                                                                                   | 0.6       | 0.7  | 8.0  | V     |

| V <sub>IN</sub> POR Hysteresis            | V <sub>IN(hys)</sub>   |                                                                                   | \ <u></u> | 0.4  |      | V     |

| V <sub>CNTL</sub> Nominal Supply Current  | I <sub>CNTL</sub>      | EN= V <sub>CNTL</sub>                                                             |           | 1    | 1.8  | mA    |

| V <sub>CNTL</sub> Shutdown Current        | I <sub>SD</sub>        | EN= 0V                                                                            |           | 15   | 30   | uA    |

| Feedback Voltage                          | $V_{FB}$               | V <sub>CNTL</sub> =5V, I <sub>QUT</sub> =10mA                                     | 0.49      | 0.5  | 0.51 | V     |

| Load Regulation                           |                        | I <sub>OUT</sub> =0A ~3A                                                          |           | 0.2  | 0.6  | %     |

| Line Regulation                           |                        | $V_{CNTL} \neq V_{EN} = 5V$ $V_{IN} = V_{OUT} \neq 0.5V \sim 5V$ $I_{OUT} = 10mA$ |           | 0.01 | 0.1  | %/V   |

| Dropout Voltage                           | V <sub>DROP</sub>      | $V_{OUT} = 3A,$ $V_{OUT} = 0.9V$                                                  |           | 0.20 | 0.28 | V     |

| V <sub>OUT</sub> Pull Low Resistance      |                        | EN=0V                                                                             |           | 85   |      | Ω     |

| Soft Start Time                           | Tss                    |                                                                                   |           | 2    | 4    | mS    |

| EN Pin Logic High threshold voltage       | V <sub>ENH</sub>       | Enable                                                                            | 1.2       |      |      | V     |

| EN FIII Logic Fligh threshold voltage     | $V_{ENL}$              | Disable                                                                           |           |      | 0.4  |       |

| EN Hysteresis                             |                        |                                                                                   |           | 50   |      | mV    |

| EN Pin Pull-Up Current                    | I <sub>EN</sub>        | EN=GND                                                                            |           | 10   |      | uA    |

| Current Limit                             | I <sub>LIM</sub>       | $V_{CNTL}=3\sim5.5V$<br>$T_{J}=-40\sim125$ °C                                     | 4.2       |      |      | Α     |

| Pipple Rejection                          | PSRR                   | E 120Hz I 100m A                                                                  |           | 65   |      | ٩D    |

| Ripple Rejection V <sub>CNTL</sub>        |                        | F=120Hz, I <sub>OUT</sub> =100mA                                                  |           | 65   |      | dB    |

| Under-Voltage Threshold                   |                        | VFB Falling                                                                       |           | 0.25 |      | V     |

| POK Threshold Voltage for Power OK        | $V_{POK}$              | VFB Rising                                                                        | 90%       | 93%  | 96%  | VFB   |

| POK Threshold Voltage for Power<br>Not OK | V <sub>PNOK</sub>      | VFB Falling                                                                       | 82%       | 85%  | 88%  | VFB   |

| POK Low Voltage                           |                        | POK sinks 5mA                                                                     |           | 0.25 | 0.4  | V     |

| POK Delay Time T <sub>DELAY</sub>         |                        |                                                                                   | 0.8       | 2    | 4    | mS    |

| Thermal shutdown Temp                     | T <sub>SD</sub>        |                                                                                   |           | 160  |      | S.    |

| Thermal Shutdown Hysteresis               | T <sub>SH</sub>        |                                                                                   |           | 50   |      | C     |

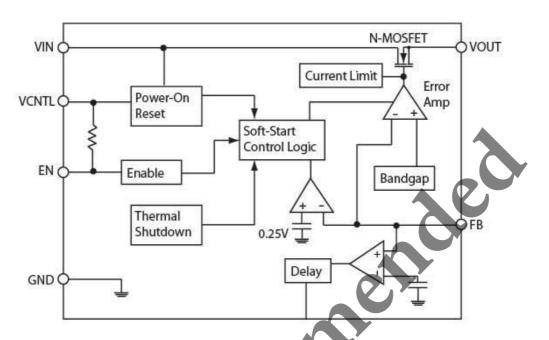

### **Block Diagram**

**Pin Function Description**

| Pin Name | Pin Description                                                                                              |

|----------|--------------------------------------------------------------------------------------------------------------|

| VIN      | Main supply input pins for power conversions. The voltage at this pin is monitored for Power-On              |

| VIIV     | Reset purpose                                                                                                |

|          | Power input pin of the control circuitry. Connecting this pin to a +5V (recommended) supply                  |

| VCNTL    | voltage provides the bias for the control circuitry. The voltage at this pin is monitored for Power-         |

|          | On Reset purpose.                                                                                            |

| GND      | Ground Pin.                                                                                                  |

|          | Power-OK signal output pin. This pin is an open-drain output used to indicate status of output               |

| POK      | voltage by sensing FB voltage. This pin is pulled low when the rising FB voltage is not above the            |

| FOR      | $V_{POK}$ threshold or the falling FB voltage is below the $V_{POK}$ threshold, indicating the output is not |

| _        | OK .                                                                                                         |

|          | Enable control pin. Pulling and holding this pin below 0.4V shuts down the output. When re-                  |

| EN       | enabled, the IC undergoes a new soft-start cycle. Left this pin open, this pin is internal pulled up         |

|          | to V <sub>CNTL</sub> voltage, enabling the regulator.                                                        |

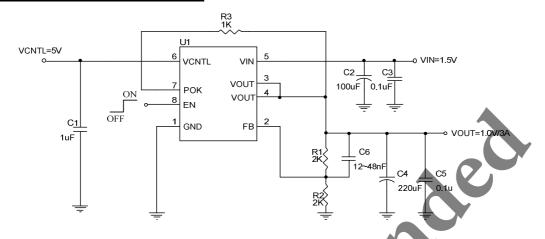

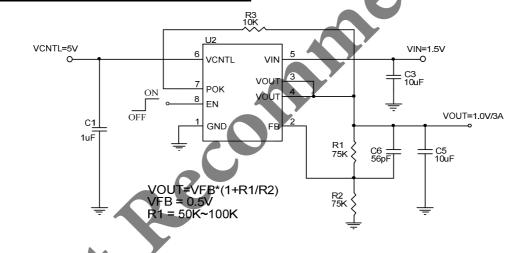

|          | Connecting this pin to an external resistor divider receives the feedback voltage of the regulator.          |

|          | The output voltage set by the resistor divider is determined by:                                             |

|          | $V_{OUT} = 0.5 \times (1 + \frac{R1}{R2})(V)$                                                                |

| FB       | 112                                                                                                          |

|          | Where R1 is connected from $V_{\text{OUT}}$ to FB with Kelvin sensing and R2 is connected from FB to         |

|          | GND. A bypass capacitor may be connected with R1in parallel to improve load transient                        |

|          | response. The recommended R2 and R1 are in the range of 1K~100KΩ.                                            |

### **Typical Application Circuit**

### Using an Output Capacitor with ESR≥20mΩ

### **Using an MLCC as the Output Capacitor (SOP-8EP)**

### **Function Description**

#### **Power-On-Reset**

A Power-On-Reset (POR) circuit monitors both input voltages at VCNTL and VIN pins to prevent wrong logic controls. The POR function initiates a soft-start process after the two supply voltages exceed their rising POR threshold voltages during powering on. The POR function also pulls low the POK pin regardless the output voltage when the VCNTL voltage falls below its falling POR threshold.

#### **Internal Soft-Start**

An internal soft-start function controls rise rate of the output voltage to limit the current surge at start-up. The typical soft-start interval is about 2mS.

### **Output Voltage Regulation**

An error amplifier working with a temperature compensated 0.5V reference and an output NMOS regulates output to the preset voltage. The error amplifier designed with high bandwidth and DC gain provides very fast transient response and less load regulation. It compares the reference with the feedback voltage and amplifies the difference to drive the output NMOS which provides load current from VIN to VOUT.

### **Current Limit**

The TS9230 monitors the current via the output NMOS and limits the maximum current to prevent load and TS9230 from damages during overload or short circuit conditions.

### **Under Voltage Protection**

The TS9230 monitors the voltage on FB pin after soft-start process is finished. Therefore the UVP is disabling during soft-start. When the voltage on FB pin falls below the under-voltage threshold, the UVP circuit shuts off the output immediately. After a while, the TS9230 starts a new soft-start to regulate output.

### **Thermal Shutdown**

A thermal shutdown circuit limits the junction temperature of TS9230. When the junction temperature exceeds +160°C, a thermal sensor turns off the output NMOS, allowing the device to cool down. The regulator regulates the output again through initiation of a new soft-start cycle after the junction temperature cools by 50°C, resulting in a pulsed output during continuous thermal overload conditions. The thermal shutdown designed.

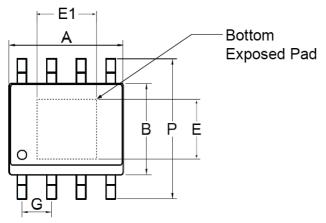

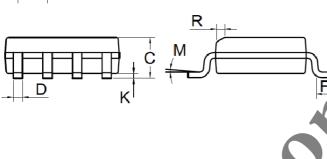

# **SOP-8EP Mechanical Drawing**

| SOP-8EP DIMENSION |        |            |        |       |  |

|-------------------|--------|------------|--------|-------|--|

| DIM               | MILLIM | ETERS      | INCHES |       |  |

|                   | MIN    | MAX        | MIN    | MAX.  |  |

| Α                 | 4.80   | 5.00       | 0.189  | 0.196 |  |

| В                 | 3.80   | 4.00       | 0.150  | 0.157 |  |

| С                 | 1.35   | 1.75       | 0.054  | 0.068 |  |

| D                 | 0.35   | 0.49       | 0.014  | 0.019 |  |

| Е                 | 2.05   | 2.41       | 0.081  | 0.095 |  |

| E1                | 2.82   | 3.30       | 0.111  | 0.130 |  |

| F                 | 0.40   | 1.25       | 0.016  | 0.049 |  |

| G                 | 1.27   | 1.27BSC    |        | BSC   |  |

| K                 | 0.10   | 0.25       | 0.004  | 0.009 |  |

| М                 | 00     | <b>7</b> ° | 0°     | 7°    |  |

| Р                 | 5.80   | 6.20       | 0.229  | 0.244 |  |

| R                 | 0.25   | 0.50       | 0.010  | 0.019 |  |

Specifications of the products displayed herein are subject to change without notice. TSC or anyone on its behalf, assumes no responsibility or liability for any errors or inaccuracies.

Information contained herein is intended to provide a product description only. No license, express or implied, to any intellectual property rights is granted by this document. Except as provided in TSC's terms and conditions of sale for such products, TSC assumes no liability whatsoever, and disclaims any express or implied warranty, relating to sale and/or use of TSC products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright, or other intellectual property right.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications. Customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify TSC for any damages resulting from such improper use or sale.