#### **FEATURES**

- Redundant Quad 3.2-Gbps Transceiver Configurable as 10-Gbps Attachment Unit Interface (XAUI) Transceiver

- IEEE P802.3ae-2002 10 Gbps Ethernet XGXS (XGMII Extender Sublayer) Compliant

- Redundancy: Fast Switching from Primary to Secondary XAUI channel with Provisionable Error Character or Local Code Fault Insertion at Switch Time

- XAUI: Transmit Pre-Emphasis and Receive Adaptive Equalization to Allow Extended Backplane Reach

- Selectable Full Duplex XAUI Retimer Mode

- Support PRBS 2 <sup>7</sup>-1 and 2<sup>23</sup>-1

Generate/verify. Support Standard Defined

CJPAT, CRPAT, High Freq, Low Freq, and

Mixed Freq testing

- XGMII: HSTL Class 1 I/O with On-Chip 50-Ω

Termination on Inputs/Outputs

- XGMII: Source Centered Timing

- Supports Jumbo Packet (9600 byte maximum)

Operation

- Align Character Skew Support of 40 bit times at Chip Pins

- MDIO: IEEE 802.3ae Clause 45 Compliant Management Data Input/Output Interface

- 1.2-V Core Voltage Supply, 1.5-V HSTL I/O Supply, and 2.5-V LVCMOS and Bias Supply

- JTAG: IEEE 1149.1 Test Interface

- Fabricated in Advanced 130-nm CMOS

#### **Technology**

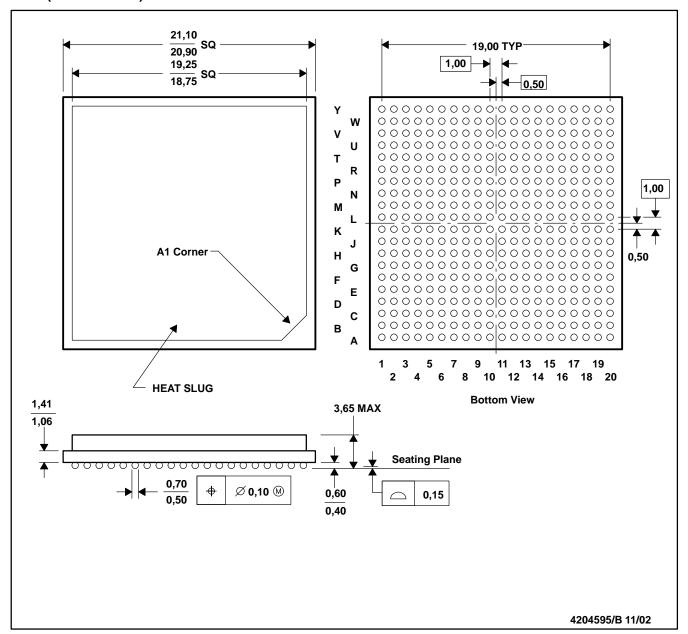

Package: Small Footprint 21x21mm, 400-Ball, Fine Pitch (1mm) PBGA

#### DESCRIPTION

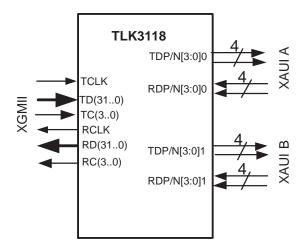

The TLK3118 is a flexible, redundant XAUI serial transceiver that is compliant to 10-Gbps Ethernet XAUI specification. The TLK3118 provides high-speed bi-directional point-to-point data transmissions with up to 12.5 Gbps of raw data transmission capacity. The primary application of this device for use in backplanes and front panel connections requiring redundant 10Gbps connections over controlled impedance media of approximately  $50~\Omega$ . The transmission media can be printed circuit board (PCB) traces, copper cables or fiber-optical media. The ultimate rate and distance of data transfer is dependent upon the attenuation characteristics of the media and the noise coupling into the lines.

The TLK3118 performs the parallel-to-serial, serial-to-parallel conversion, and clock extraction functions for a physical layer interface. The TLK3118 provides two complete XGXS/PCS functions defined in Clause 47/48 of the IEEE P802.3ae 10Gbps Ethernet standard. The serial transmitter is implemented using differential Current Mode Logic (CML) with integrated termination resistors.

The TLK3118 can be configured as a redundant XAUI transceiver or a full duplex XAUI re-timer. TLK3118 supports a 32-bit data path, 4-bit control, 10 Gigabit Media Independent Interface (XGMII) to the protocol device. Figure 1 shows an example system block diagram for TLK3118 used to provide the 10-Gbps Ethernet Physical Coding Sublayer to Coarse Wave-length Division Multiplexed optical transceiver or parallel optics.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## **DESCRIPTION CONTINUED**

#### Line Card TCLK CWDM or XGMII Xchannel A TD(31:0) Xchannel Parallel **Optics** TC(3:0) **TLK3118** MAC/ **TLK3118** Packet Processor CWDM or RC(3:0) Xchannel XGMII Xchannel Parallel RCLK **Optics** RD(31:0)

Figure 1. System Block Diagram - PCS

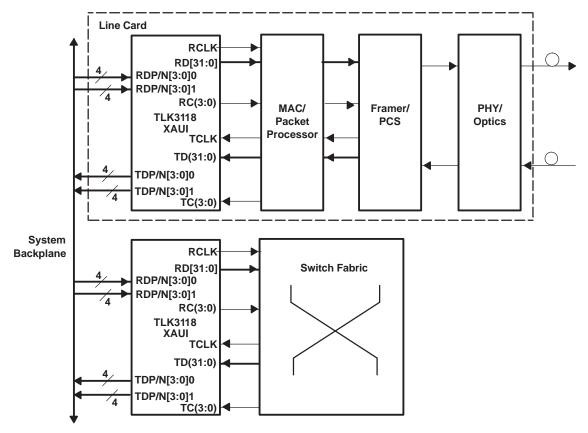

Figure 2 shows an example system block diagram for TLK3118 used to provide the system backplane interconnect.

Figure 2. System Block Diagram - XAUI Backplane

The TLK3118 supports the IEEE 802.3 defined Management Data Input/Output (MDIO) Interface to allow ease in configuration and status monitoring of the link. The bi-directional data pin (MDIO) should be externally pulled up to 2.5 V.

The TLK3118 supports the IEEE 1149.1 defined JTAG test port for ease in board manufacturing test. It also supports a comprehensive series of built-in tests for self-test purposes including PRBS generation and verification, CRPAT, CJPAT, Mixed/High/Low Frequency testing.

The TLK3118 operates with a 1.2-V core voltage supply, a 1.5-V HSTL I/O voltage supply and a 2.5-V bias supply. The device consumes 1.75 watts.

The TLK3118 is packaged in a 21x21mm, 400-ball, 1-mm ball pitch Flip Chip Ball Grid Array (FC-BGA) package and is characterized for operation from 0°C to 70°C, 105°C Junction, and 5% power supply variation unless noted otherwise.

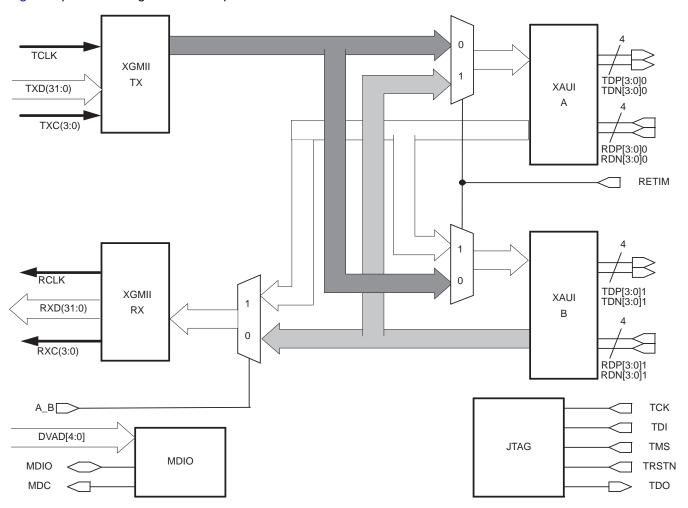

Figure 3 provides a high level description of the TLK3118.

Figure 3. TLK3118 Block Diagram

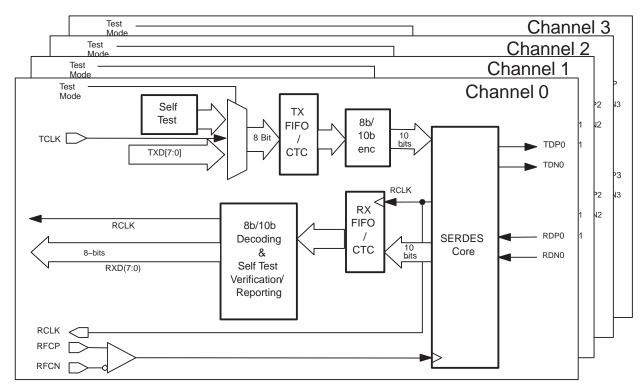

Figure 4 is a more detailed block diagram description of XAUI core.

Figure 4. Detailed XAUI Core Block Diagram

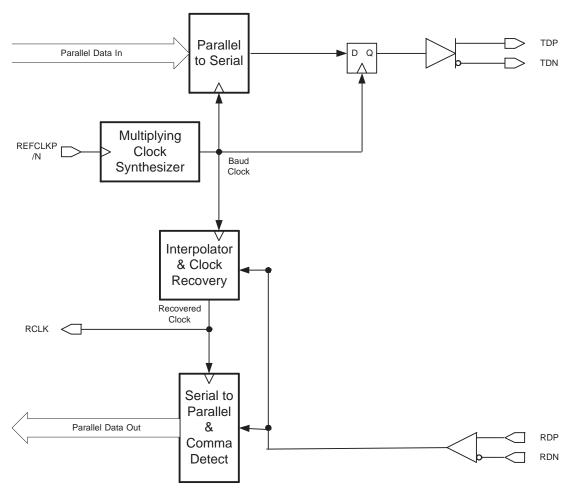

Figure 5. Block Diagram of SERDES Core

#### **Detailed Description**

The TLK3118 has two operational interface modes controlled by the state of pins A/B and RETIM. The RETIM pin controls whether the TLK3118 operates as a re-timer and the A/B pin controls which is the active bi-directional XAUI channel reflected on the bi-directional XGMII interface during transceiver mode operations.

## Transceiver Operation (RETIM = LOW)

When RETIM is held low, the TLK3118 operates as a redundant XAUI transceiver. The device will serialize data input on TXD (31:0) and output on the selected serial output signals. Serial data input on selected channel is de-serialized, aligned and output on RXD (31:0) outputs. When A/B is asserted high, serial links RD [P/N] [3/2/1/0]0 form the primary XAUI channel. Data input on TXD (31:0) is output on TD [P/N] [3/2/1/0]0 and serial data input from RD [P/N] [3/2/1/0]0 is de-serialized, aligned and output on the RXD (31:0) outputs. When A/B is asserted low, serial links RD [P/N] [3/2/1/0]1 form the primary XAUI channel. Data input on TXD(31:0) is serialized and output on TD[P/N][3/2/1/0]1 and serial data input from the RD[P/N][3:0]1 is de-serialized, aligned and output on the RXD(31:0) outputs.

While communication is occurring on the primary XAUI channel, the secondary XAUI channel is fully functional capable of transmitting and receiving data. All registers are valid and accessible. The only difference between the primary and secondary channels is the primary channel is routed to the XGMII bus. The TLK3118 transceiver mode default condition will be to broadcast the data input on the XGMII inputs, TXD (31:0), to both the primary and secondary XAUI channels. The receive path of the secondary XAUI channel will default to an active state recovering and aligning data.

## **Detailed Description (continued)**

A completely active secondary XAUI channel will allow transition from primary to secondary channels within a few XGMII clock cycles. During the transition from primary to secondary XAUI channels, the data on each byte of the XGMII bus will be 0xFE (code violation), which is the ERROR indication, or local fault indication (based on provisioned register value).

Also, when the primary input IDLE = HIGH, the secondary transmit XAUI channel transmits legal A/K/R characters instead of the 8B/10B encoded packet stream. When IDLE = LOW, the transmit packet stream is bridged to both sets of XAUI output channels.

## Re-Timer Operation (RETIM = HIGH)

When RETIM is asserted high, the TLK3118 will operate as a full duplex XAUI re-timer. All the functions of transceiver operations are performed with the exception input from the XGMII. The recovered data on each XAUI channel is de-serialized, de-skewed, aligned to the reference clock, and re-serialized. In the re-timer mode inputs from the TXD (31:0) are ignored.

Note that when RETIM is high, the XAUI A receive data is eventually routed out to the XAUI B transmit serial lines. Similarly, the XAUI B receive data is eventually routed out to the XAUI A transmit serial lines.

The TLK3118 re-timer mode default condition will be to enable the XGMII receive output bus, RXD (31:0). However, a software setting is available to put the RXD bus into a high-impedance state desired for power savings. The TLK3118 can be configured, via MDIO or pin, to monitor the recovered data on either XAUI channel. If the re-timer monitoring mode is enabled, the state of the A/B pin will determine which XAUI channel recovered data is output on the XGMII receive output bus. If A/B is toggled when in re-timer monitor mode, the data on each byte of the XGMII receive output bus will be 0xFE (code violation) for several XGMII clock cycles, or local fault (based on the provisioned register value).

## **Parallel Interface Clocking**

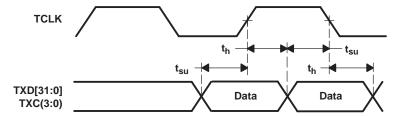

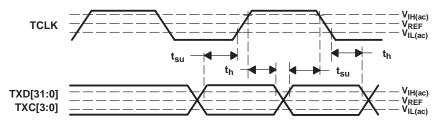

The TLK3118 supports source centered timing on the XGMII transmit input bus. The timing supported is the timing defined in P802.3ae Clause 46 with the TCLK centered within the transmit data bit timing, as shown in Figure 6.

Figure 6. Transmit Interface Timing - Source Centered

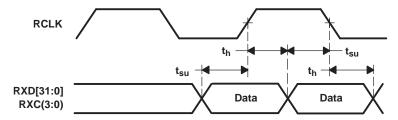

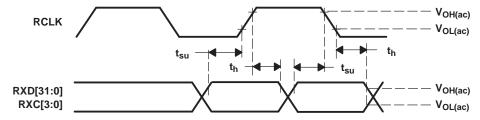

On the receive data path, the data is synchronized and output referenced to RCLK, with the RCLK placed in the center of the data window, as shown in Figure 7. RCLK is derived from the transmit reference clock. A FIFO, placed on the output of the serial to parallel conversion logic for each serial link, compensates for channel skew, clock phase and frequency tolerance differences between the recovered clocks for each serial links and the receive output clock, RCLK. This FIFO has a total depth of nine ten bit entries, giving 40 bit time deskew (channel-to-channel skew) alignment capability. See Table 94 and Table 95 for more details on XGMII timing.

Figure 7. Receive Interface Timing

## **Detailed Description (continued)**

#### **Parallel Interface Data**

Data placed on the XGMII transmit input bus is latched on the rising and falling edge of the transmit data clock, TCLK, as shown in Figure 6. The latched data is then phase aligned to the internal version of the transmit reference clock, 8b/10b encoded, serialized, then transmitted sequentially beginning with the LSB of the encoded data byte over the differential high speed serial transmit pins.

The XGMII receive data bus outputs four bytes on RXD (31:0). Control character (K-characters) reporting for each byte is done by asserting the corresponding control pin, RXC (3:0). When RXC is asserted, the 8 bits of data corresponding to the control pin is to be interpreted as a K-character. If an error is uncovered in decoding the data, the control pin is asserted and 0xFE is output for the corresponding byte.

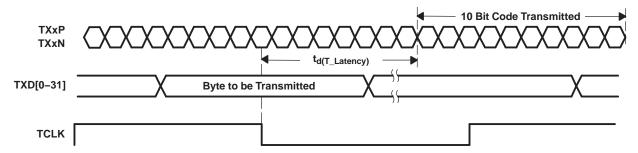

#### **Transmission Latency**

For each channel, the data transmission latency of the TLK3118 is defined as the delay from the rising or falling edge of the selected transmit clock when valid data is on the transmit data pins to the serial transmission of bit 0, as shown in the following figure. The maximum transmit latency (TLATENCY) is 600 bit times; the standard allows a combined latency (TX + RX) of 2048 bit times.

Figure 8. Transmission Latency

#### **Channel Clock to Serial Transmit Clock Synchronization**

The TLK3118 allows ±200 ppm difference between the serdes transmit reference on the XAUI side, versus the input TCLK on the XGMII side. There exists a FIFO capable of CTC operations, and has a depth of 32 locations (32 bits wide per location).

The reference clock and the transmit data clock(s) may be from a common source, but the design allows for up to +/- 200 ppm of frequency difference should the application require it.

#### **Data Reception Latency**

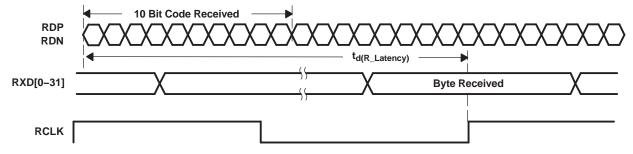

For each serial link, the serial-to-parallel data latency is the time from when the first bit arrives at the serial receiver input until it is output in the aligned parallel word on the XGMII, as shown in Figure 9. The maximum receive latency (RLATENCY) is 700 bit times; the standard allows a combined latency (TX + RX) of 2048 bit times.

Figure 9. Receiver Latency

## **Detailed Description (continued)**

#### 8B/10B Encoder

All true serial interfaces require a method of encoding to insure sufficient transition density for the receiving PLL to acquire and maintain lock. The encoding scheme also maintains the signal DC balance by keeping the number of ones and zeros are balanced which allows for AC coupled data transmission. The TLK3118 uses the 8B/10B encoding algorithm that is used by 10Gbps and 1Gbps Ethernet and Fiber Channel standards. This provides good transition density for clock recovery and improves error checking. The 8B/10B encoder/decoder function is enabled for all serial links. The TLK3118 will internally encode and decode the data such that the user reads and writes actual 8-bit data on each channel.

The 8B/10B encoder converts 8-bit wide data to a 10-bit wide encoded data character to improve its transition density. This transmission code includes D Characters, used for transmitting data, and K Characters, used for transmitting protocol information. Each K or D character code word can also have both a positive and a negative disparity version. The disparity of a code word is selected by the encoder to balance the running disparity of the serialized data stream.

The generation of K-characters to be transmitted on each channel is controlled by transmit control pins, TXC(3:0). When the control pin is asserted along with the 8 bits of data, an 8B/10B K-character is transmitted. Similarly, reception of K-characters is reported by the receive control pins, RXC(3:0). When receive control pin is asserted, the corresponding byte on the receive data bus should be interpreted as a K-character. The TLK3118 will transmit and receive all of the twelve valid K-characters as defined below.

K-Code TXC(3:0) or **Data Bus Bytes Encoded K-code K-Code Description** RXC(3:0) (RXD[x: x-7] or Negative **Positive** TXD[x: x-7]) Running Running Disparity Disparity 00 through FF 0 DDD DDDDD dddddd dddd dddddd dddd Normal data K28.0 1 000 11100 001111 0100 110000 1011 IdleO/busv K28.1 1 001 11100 001111 1001 110000 0110 IdleE/busy K28.2 1 110000 1010 010 11100 001111 0101 K28.3 1 011 11100 001111 0011 110000 1100 Channel Alignment Pre-Cursor K28.4 1 100 11100 001111 0010 110000 1101 K28.5 1 101 11100 001111 1010 110000 0101 IdleE/not-busy K28.6 1 110 11100 110000 1001 001111 0110 K28.7 1 111 11100 001111 1000 110000 0111 Code Violation or Parity Error K23.7 1 111 10111 111010 1000 000101 0111 IdleO/not-busy K27.7 1 111 11011 110110 1000 001001 0111 SOP(S) EOP(T) K29.7 1 111 11101 101110 1000 010001 0111 K30.7 1 111 11110 011110 1000 100001 0111

Table 1. Valid K-Codes

Table 2 provides additional transmit data control coding and descriptions that have been incorporated into 10 Gigabits per second Ethernet. Data patterns put on XGMII transmit data bus other than those defined in Table 2 when the transmit control pin is asserted will result in an invalid K-character being transmitted which will result in a code error at the receiver.

**Table 2. Valid XGMII Channel Encodings**

| Data Bus (TXD[x: x-7] or RXD[x: x-7]) | TXC(3:0) or RXC(3:0) | Description                        |

|---------------------------------------|----------------------|------------------------------------|

| 00 through FF                         | 0                    | Normal Data Transmission           |

| 00 through 06                         | 1                    | Reserved                           |

| 07                                    | 1                    | Idle                               |

| 08 through 9B                         | 1                    | Reserved                           |

| 9C                                    | 1                    | Sequence (only valid in Channel A) |

| 9D through FA                         | 1                    | Reserved                           |

#### Table 2. Valid XGMII Channel Encodings (continued)

| Data Bus (TXD[x: x-7] or RXD[x: x-7]) | TXC(3:0) or RXC(3:0) | Description                     |

|---------------------------------------|----------------------|---------------------------------|

| FB                                    | 1                    | Start (only valid in Channel A) |

| FC                                    | 1                    | Reserved                        |

| FD                                    | 1                    | Terminate                       |

| FE                                    | 1                    | Transmit error propagation      |

| FF                                    | 1                    | Reserved                        |

## Comma Detect and 8B/10B Decoding

When parallel data is clocked into a parallel to serial converter, the byte boundary that was associated with the parallel data is lost in the serialization of the data. When the serial data is received and converted to parallel format again, a method is needed to be able to recognize the byte boundary again. Generally this is accomplished through the use of a synchronization pattern. This is a unique a pattern of 1's and 0's that either cannot occur as part of valid data or is a pattern that repeats at defined intervals. 8B/10B encoding contains a character called the comma (b'0011111' or b'1100000') which is used by the comma detect circuit to align the received serial data back to its original byte boundary. The decoder detects the K28.5 comma, generating a synchronization signal aligning the data to their 10-bit boundaries for decoding. It then converts the data back into 8-bit data. It is important to note that the comma can be either a (b'0011111') or the inverse (b'1100000') depending on the running disparity. The TLK3118 decoder will detect both patterns.

The reception of K-characters is reported by the assertion of receive control pin, RXC (3:0) for the corresponding byte on the XGMII receive bus. When a code word error or running disparity error is detected in the decoded data received on a serial link, the receive control pin is asserted and a 0xFE is placed on the receive data bus for that channel, as shown in Table 3.

**Table 3. Receive Data Controls**

| Event                                      | Receive Data Bus RXD[x: 7-x] | RXC(3:0) |

|--------------------------------------------|------------------------------|----------|

| Normal Data                                | XX                           | 0        |

| Normal K-character                         | Valid K-code                 | 1        |

| Code word error or running disparity error | FE                           | 1        |

#### **Channel Initialization and Synchronization**

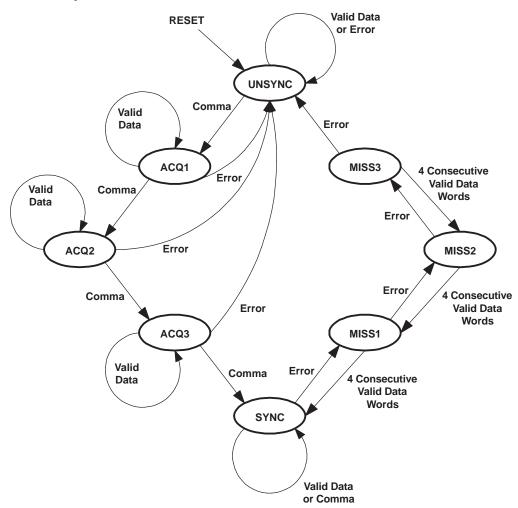

The TLK3118 has a synchronization state machine which is responsible for handling link initialization and synchronization for each channel. The initialization and synchronization state diagram is provided in Figure 10. The status of any channel can be monitored by reading MDIO register 4:5.24.3:0.

#### **Channel State Descriptions**

Figure 10. Channel Synchronization State Machine

#### **UNSYNC**

This is the initial state for each channel upon device power up or reset. In this state, the TLK3118 will have the comma detect circuit active and will make code word alignment adjustments based on the position of a comma in the incoming data stream. While in this state the TLK3118 will set the Lane Sync bit to '0' for the particular channel in MDIO register bits 4:5.24.3:0, indicating the lane is not synchronized. The channel state will transition to the ACQ1 state upon the detection of a comma.

#### NOTE:

The Lane Sync bit = '0' bit from any/or all channels will cause a local fault to be output on the receive data bus.

#### ACQ1

During this state the comma detect circuit is active but code word re-alignment is disabled. The TLK3118 will remain in this state until either a comma is detected in the same code word alignment position as found in state UNSYNC or a decode error is encountered. While in this state, the Lane Sync bit for the particular channel will remain de-asserted indicating the lane is not synchronized. A decode or running disparity error will return the channel state to UNSYNC. A detected comma will cause the channel state to transition to ACQ2.

#### NOTE:

The Lane Sync bit = '0' will cause a local fault to be output on the receive data bus.

#### ACQ2

During this state, the comma detect circuit is active but code word re-alignment is disabled. The TLK3118 will remain in this state until either a comma is detected in the same code word alignment position as found in state UNSYNC or a decode error is encountered. While in this state, the Lane Sync bit for the particular channel will remain de-asserted indicating the lane is not synchronized. A decode or running disparity error will return the channel state to UNSYNC. A detected comma will cause the channel state to transition to ACQ3.

#### ACQ3

During this state the comma detect circuit is active but code word re-alignment is disabled. The TLK3118 will remain in this state until either a comma is detected or a decode error encountered. While in this state, the Lane Sync bit for the particular channel will remain de-asserted indicating the lane is not synchronized.7 A decode or running disparity error will return the channel state to UNSYNC. A detected comma will cause the channel state to transition to SYNC.

#### SYNC

This is the normal state for receiving data. When in this state, the TLK3118 will set the Lane Sync bit to '1' for the particular channel in the MDIO register bits 4:5.24.3:0 indicating the lane has been synchronized. During this state the comma detect circuit is active but code word re-alignment is disabled. A decode or running disparity error will cause the channel state to transition to MISS1.

#### MISS<sub>1</sub>

When entering this state an internal error counter is cleared. If the next four consecutive codes are decoded without error, the channel state reverts back to SYNC. If a decode or running disparity error is detected, the channel state will transition to MISS2.

#### MISS<sub>2</sub>

When entering this state an internal error counter is cleared. If the next four consecutive codes are decoded without error, the channel state reverts back to MISS1. If a decode or running disparity error is detected, the channel state will transition to MISS3.

#### MISS3

When entering this state an internal error counter is cleared. If the next four consecutive codes are decoded without error, the channel state reverts back to MISS1. If a decode or running disparity error is detected, the channel state will transition to UNSYNC.

#### **End-of-Packet Error Detection**

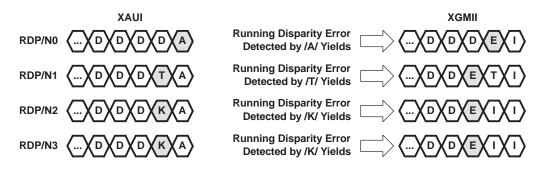

Because of their unique data patterns, /A/ (K28.3), /K/ (K28.5), and /T/ (K29.7) will catch running disparity errors that may have propagated undetected from previous codes in a packet. Running disparity errors detected by these control codes at the end of packets will cause the previous data codes to be reported as errors (0xFE) to allow the protocol device to reject the packet (see Figure 11).

D = Data, T = K29.7, A = K28.3, K = K28.5, E = Error (0xFE), I = Idle

Figure 11. End-of-Packet Error Detection

## **Fault Detection and Reporting**

The TLK3118 will detect and report local faults as well as forward both local and remote faults as defined in the IEEE P802.3ae 10Gbps Ethernet Standard to aid in fault diagnosis. All faults detected by the TLK3118 are reported as local faults to the upper layer protocols. Once a local fault is detected in the TLK3118, MDIO register bit 4:5.1.7 is set. Fault sequences, sequence ordered sets received by the TLK3118, either on the Transmit Data Bus or on the high speed receiver pins, are forwarded without change to the MDIO registers in the TLK3118. Also, note that the TLK3118 is capable of performing CTC operation where only RF and LF or any Q sequences are transported (not generated) in either the transmit or receive direction.

TLK3118 reports a fault by outputting a K28.4 (0x9C) on RXD(7:0), 0x00 on RXD(15:8) and RXD(23:8) and 0x01 for local faults on RXD(31:24). Forwarding of remote faults is handled as a normal transmission. Note that the TLK3118 will not generate a remote fault indication or any other type of Q.

#### **Receive Synchronization and Skew Compensation**

Regardless of which mode is selected, the TLK3118 has a FIFO enabled on the receive data path coming from each serial link to compensate for channel skew and clock phase and frequency tolerance differences between the recovered clocks for each channel and the receive output clock RCLK. This FIFO has a depth of 32 locations (32 bits wide for each location).

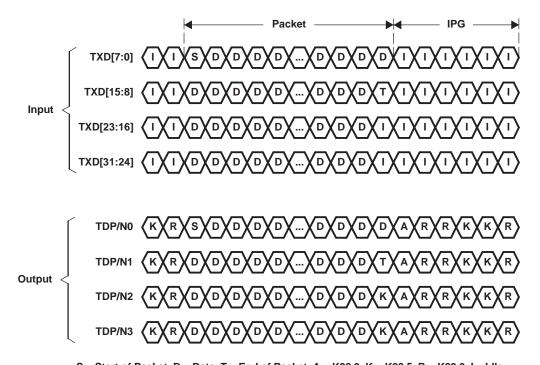

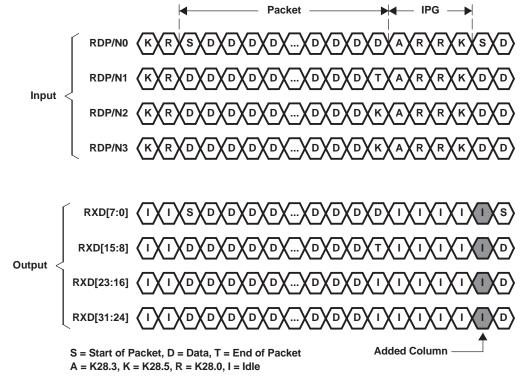

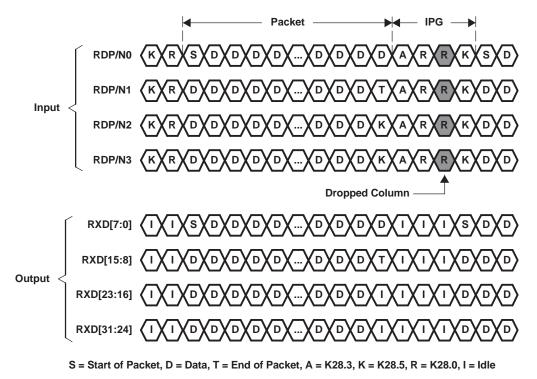

The de-skew of the 4 serial links that make up each XAUI channel into a single 32 bit wide column of data is accomplished by alignment of the receive FIFO's on each serial link to a K28.3 control code sent during the inter-packet gap (IPG) between data packets or during initial link synchronization. The K28.3 code (referred to as the "A" or alignment code) is transmitted on the first column following the end of the data packet as shown in Figure 13.

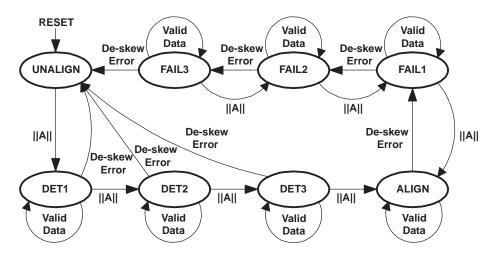

The column de-skew state machine is provided in the following figure. The status of column alignment can be monitored by reading MDIO registers 4:5.24.12 for global alignment or 4:5.24.3:0 for particular channel synchronization.

Figure 12. Column De-Skew State Machine

#### **Column State Descriptions**

#### **UNALIGN**

This is the initial state for the column state machine upon device power up or reset. If any of the channel state machines are set to UNSYNC, the column state is set to UNALIGN. In this state, the column state machine will search for alignment character codes (K28.3 or /A/) on each channel and align the FIFO pointers on each channel to the /A/ character code. While in this state, the Column Alignment Sync bit is set to '0' in MDIO registers 4:5.24.12, indicating the column is not aligned. The column state will transition to the DET1 state upon the detection and alignment of /A/ character codes in all four channels.

#### DET1

During this state, the alignment character code detect circuit is active on each channel but the column re-alignment is disabled. The column state machine will remain in this state looking for a column of alignment character codes. If an incomplete alignment column is detected (alignment character codes not found on all channels) or a deskew error is detected, the column state machine will transition to state UNALIGN. While in this state, the Column Alignment Sync bit is set to '0' in MDIO registers 4:5.24.12 indicating the column is not aligned. Detection of a complete alignment column will cause the column state machine to transition to state DET2.

#### NOTE:

The XGXS Lane Alignment bit = '0' will cause a local fault to be output on the receive data bus.

#### DET2

During this state, the alignment character code detect circuit is active on each channel but the column re-alignment is disabled. The column state machine will remain in this state looking for a column of alignment character codes. If an incomplete alignment column is detected (alignment character codes not found on all channels) or a deskew error is detected, the column state machine will transition to state UNALIGN. While in this state, the Column Alignment Sync bit is set to '0' in MDIO registers 4:5.24.12 indicating the column is not aligned. Detection of a complete alignment column will cause the column state machine to transition to state DET3.

#### NOTE:

The XGXS Lane Alignment bit = '0' will cause a local fault to be output on the receive data bus.

## TLK3118 Redundant XAUI Transceiver

SLLS628C-DECEMBER 2004-REVISED APRIL 2007

#### DET3

During this state, the alignment character code detect circuit is active on each channel but the column re-alignment is disabled. The column state machine will remain in this state looking for a column of alignment character codes. If an incomplete alignment column is detected (alignment character codes not found on all channels) or a deskew error is detected, the column state machine will transition to state UNALIGN. While in this state, the Column Alignment Sync bit is set to '0' in MDIO registers 4:5.24.12 indicating the column is not aligned. Detection of a complete alignment column will cause the column state machine to transition to state ALIGN.

#### NOTE:

The XGXS Lane Alignment bit = '0' will cause a local fault to be output on the receive data bus.

#### **ALIGN**

This is the normal state for receiving data. When in this state, the column state machine will set the Column Alignment Sync bit to '1' in MDIO registers 4:5.24.12 indicating that all channels are aligned. During this state the alignment character code detect circuit is active on each channel but the column re-alignment is disabled. If a deskew error is detected in the correct position within the Inter-Packet Gap, the column state machine will transition to state FAIL1.

#### FAIL1

When in this state, the Column Alignment Sync bit is '1' in MDIO registers 4:5.24.12. During this state the alignment character code detect circuit is active on each channel but the column re-alignment is disabled. If a complete alignment column is not detected in the correct position within the Inter-Packet Gap, the column state machine will transition to state FAIL2.

#### FAIL2

When in this state, the Column Alignment Sync bit is '1' in MDIO registers 4:5.24.12. During this state the alignment character code detect circuit is active on each channel but the column re-alignment is disabled. If a complete alignment column is not detected in the correct position within the Inter-Packet Gap, the column state machine will transition to state FAIL3.

#### FAIL3

When in this state, the Column Alignment Sync bit is '1' in MDIO registers 4:5.24.12. During this state the alignment character code detect circuit is active on each channel but the column re-alignment is disabled. If complete alignment column is not detected in the correct position within the Inter-Packet Gap, the column state machine will transition to state UNALIGN.

#### **Inter-Packet Gap Management**

When in transceiver mode, the TLK3118 replaces the idle codes (see Table 2) during the Inter-Packet Gap (IPG) with the necessary codes to perform all channel alignment, byte alignment, and clock tolerance compensation as defined in IEEE 802.3ae 10Gbps Ethernet Standard. According to the Ethernet Standard, a valid packet must begin on TXD(0:7) of the XGMII. However, due to variable packet sizes, the IPG can begin on any channel. The TLK3118 will replace idle codes latched on the same XGMII clock edge as the end of packet code with /K/ codes (as shown in Figure 13).

$S = Start \ of \ Packet, \ D = Data, \ T = End \ of \ Packet, \ A = K28.3, \ K = K28.5, \ R = K28.0, \ I = Idle$

Figure 13. Inter-Packet Gap Management

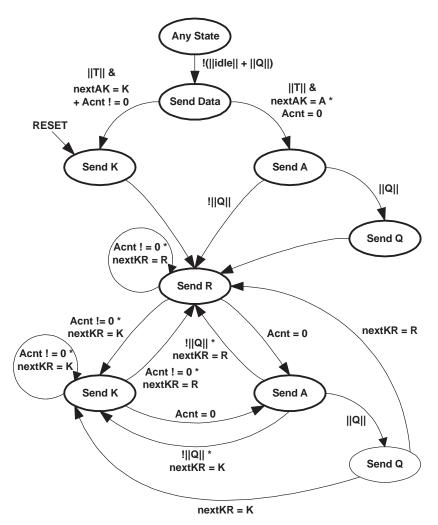

The subsequent idles in the IPG will be replaced by "columns" of channel alignment codes (K28.3), byte alignment codes (K28.5), or clock tolerance compensation codes (K28.0). The state machine which governs the IPG replacement procedure is illustrated in Figure 14, with notation defined in Table 2. Note that any IPG management state will transition to send data if the IPG is terminated.

The repetition of the "/A/" pattern on each serial channel allows the FIFO's to remove or add the required phase and frequency difference to align the data from all four serial links of a XAUI channel and allow output of the aligned 32 bit wide data on a single edge of the receive clock, RCLK, as shown in Figure 15.

SLLS628C-DECEMBER 2004-REVISED APRIL 2007

Figure 14. IPG Management State Machine

**Table 4. IPG Management State Machine Notation**

| Symbol | Definition                                                                                                                                                                      |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| idle   | XGMII idle. 0x07 on TXD(x:: :x-7),                                                                                                                                              |

| Q      | Link status message: K28.4, Dx.y, Dx.y, Dx.y.                                                                                                                                   |

| nextAK | A Boolean variable. It takes the value K when an A is sent at the beginning of the IPG and the value A when a K is sent at the beginning of the IPG. Its initial value is K.    |

| Acnt   | When an A character is sent, variable Acnt is loaded with a random number such that $16 \le Acnt \le 31$ . Acnt is decremented each time a column of A characters is generated. |

| nextKR | A randomly-generated Boolean that can assume the value K or R.                                                                                                                  |

| T      | Terminate Character Column (Terminate Character in Any Lane).                                                                                                                   |

Figure 15. Channel Synchronization Using Alignment Code

## **Clock Tolerance Compensation (CTC)**

The XAUI interface is defined to allow for separate clock domains on each side of the link. If the reference clocks difference for two devices on a XAUI link is not compensated for, it will lead to over or under run of the FIFO's on the receive/transmit data path. The TLK3118 provides compensation for these differences in clock frequencies via the insertion or the removal of /R/ characters on all channels, as shown in Figure 16 and Figure 17.

Figure 16. Clock Tolerance Compensation: Add

The /R/ code is disparity neutral, allowing its removal or insertion without affecting the current running disparity of each channel's serial stream.

Figure 17. Clock Tolerance Compensation: Drop

#### **Parallel to Serial**

The parallel-to-serial shift register on each channel takes in data and converts it to a serial stream. The shift register is clocked by the internally generated bit clock, which is 10 times the reference clock (REFCLKP/REFCLKN) frequency. The least significant bit (LSB) for each channel is transmitted first.

#### Serial to Parallel

For each channel, serial data is received on the RDPx/RDNx pins. The interpolator and clock recovery circuit will lock to the data stream if the clock to be recovered is within ±200 PPM of the internally generated bit rate clock. The recovered clock is used to retime the input data stream. The serial data is then clocked into the serial-to-parallel shift registers. If enabled, the 10-bit wide parallel data is then fed into 8b/10b decoders.

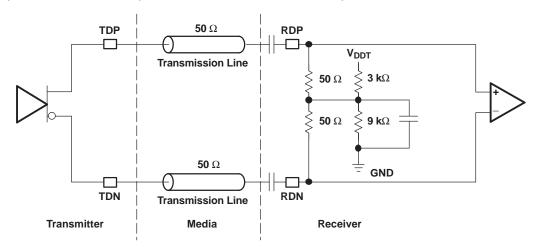

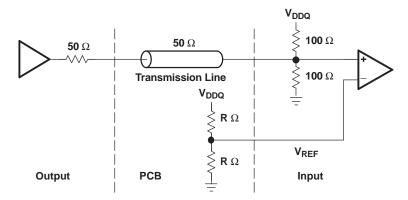

#### **High-Speed CML Output**

The high speed data output driver is implemented using Current Mode Logic (CML) with integrated pull up resistors requires no external components. The line must be AC coupled.

Figure 18. Example High Speed I/O AC Coupled Mode

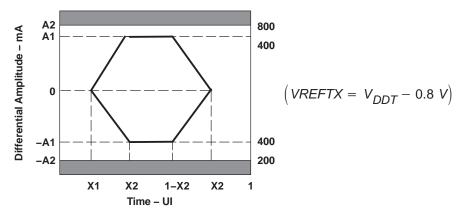

Standard Current Mode Logic (CML) drivers usually require external components. The disadvantage of the external edge control is a limited edge rate due to package and line parasitic. The CML driver on TLK3118 has on-chip  $50-\Omega$  termination resistors terminated to VDDT therefore provides optimum performance for increased speed requirements. The transmitter output driver is highly configurable allowing, output amplitude and pre-emphasis to be turned to a channel's individual requirements. An internal voltage reference derived from VDDT is also available to provide the target for output amplitude control loop. This reference is enabled by holding register bit 4/5.32900.6 low and will result in a nominal output amplitude of  $\sim 1010$ mV differential pk-pk for 100% swing. The receiver input is internally biased to  $2\times VDDT/3$ , which is the optimum voltage for input sensitivity. As the input and output references are derived from VDDT, the tolerance of this supply will dominate the accuracy of the internal reference. Applications requiring higher tolerance output amplitude are advised to provide a high accuracy external reference.

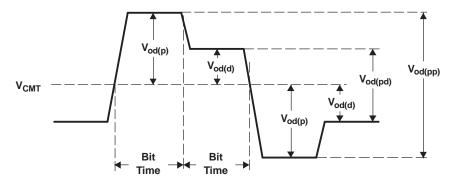

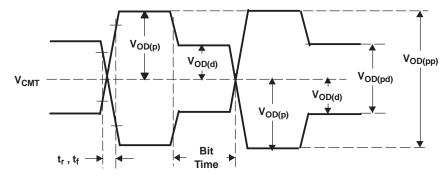

When transmitting data across long lengths of PCB trace or cable, the high frequency content of the signal is attenuated due to the skin effect of the media. This causes a "smearing" of the data eye when viewed on an oscilloscope. The net result is reduced timing margins for the receiver and clock recovery circuits. In order to provide equalization for the high frequency loss, 2-tap finite impulse response (FIR) transmit pre-emphasis is implemented. In a 1-tap FIR pre-emphasis, differential swing is increased or "pre-emphasized" for the bit immediately following a transition and subsequently reduced or "de-emphasized" for run lengths greater than one, as shown in Figure 19. This provides additional high frequency energy to compensate for PCB or cable loss.

Figure 19. Output Differential Voltage with 1-Tap FIR Pre-Emphasis

The 2-stage mode operates in a similar manner but considers the logic level of the previous two transmitted bits when determined how much pre-emphasis to apply. The level and mode of the pre-emphasis is programmable via MDIO Register bits 4/5.32900.14:11. Users can control the strength of the pre-emphasis to optimize for a specific system requirement.

#### **High-Speed Receiver**

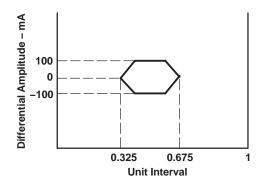

The high speed receiver is conformed to the physical layer requirements of IEEE 802.3ae Clause 47(XAUI), Gigabit Ethernet, and Fiber channel 1 and 2. The termination impedances of the receiver is configured as  $100\Omega$  with the center tap weakly tied to  $2\times VDDT/3$  with a capacitor to create an AC ground. AC coupling is always required on receiver inputs.

All receive channels incorporate an adaptive equalizer. This circuit compensates for channel insertion loss by amplifying the high frequency components of the signal, reducing inter-symbol interference. Setting 4/5.32900.2 will enable adaptive equalization. In this mode, both the gain and bandwidth of the equalizer with be controlled by the receiver equalization logic. Bandwidth selection will be based on the setting applied to 4/5.32901.14:13 and 4/5.32900.3. Equalization can be disabled by setting 4/5.32900.2 low.

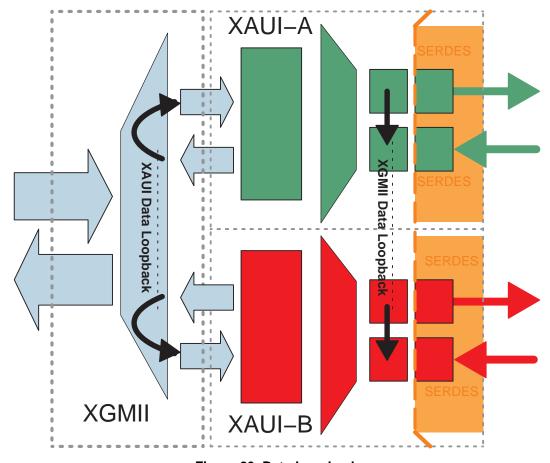

#### Loopback

Two internal loopback modes are possible for each XAUI Channel Group A and B. One, called XGMII loopback, allows the transmit 10 bit data to be looped back to the receive 10 bit data inputs. The other, called XAUI loopback, allows the receive XGMII data to be looped back to the transmit data path. These configurations are listed in Table 5.

| RETIM | 4/5.0.14 | 4/5.32792.1 | 4/5.32792.0 | Configuration                                                                                                                  |

|-------|----------|-------------|-------------|--------------------------------------------------------------------------------------------------------------------------------|

| 0     | 0        | 0           | 0           | Transceiver Mode — Normal Operation                                                                                            |

| 1     | Х        | Х           | Х           | Retime Mode(XAUI A receiver data is routed out to XAUI B. XAUI B receiver data is routed to XAUI A)                            |

| 0     | 1        | Х           | Х           | If configured as PHY XS, XAUI is loopback to the same channel. If configured as DTE XS, XGMII is loopback to the same channel. |

| 0     | 0        | 1           | 0           | XAUI data loopback                                                                                                             |

| 0     | 0        | 0           | 1           | XGMII data loopback                                                                                                            |

**Table 5. Loopback Configuration**

An external loopback (requiring external connection) is also supported, which can be used with the PRBS patterns, as well as the CJPAT, CRPAT, Mixed/High/Low Frequency tests.

Figure 20. Data Loopback

## **XGMII Bus Buffers**

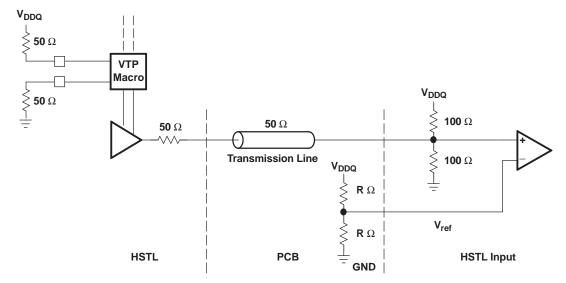

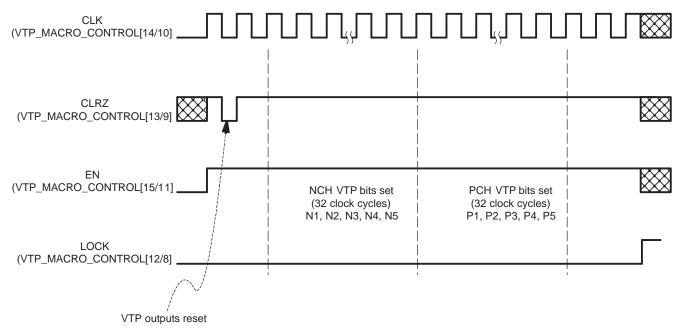

The XGMII bus is implemented using 1.5-V HSTL buffer in compliance with JEDEC 1.5-V standard JESD8-6 with VTP-controlled driver, receiver and an optional termination. The VTP macro function is to adjust the HSTL buffer output impedance to match the external resistors. (In this case  $50 \Omega$ )

SLLS628C-DECEMBER 2004-REVISED APRIL 2007

Figure 21. XGMII Bus Buffers

#### **Link Test Functions**

The TLK3118 has an extensive suite of built in test functions to support system diagnostic requirements. Each channel has built-in link test generator and verification logic. Several patterns can be selected via the MDIO that offer extensive test coverage. The patterns are: 2<sup>7</sup>-1 or 2<sup>23</sup>-1 PRBS (Pseudo Random Binary Sequence), CJPAT, CRPAT, high and low and mixed frequency patterns.

## **MDIO Management Interface**

The TLK3118 supports the Management Data Input/Output (MDIO) Interface as defined in Clauses 45 of the IEEE 802.3ae Ethernet specification. The MDIO allows register-based management and control of the serial links. Normal operation of the TLK3118 is possible without use of this interface since all of the essential signals necessary for operations are accessible via the device pins. However, some additional features are accessible only through the MDIO.

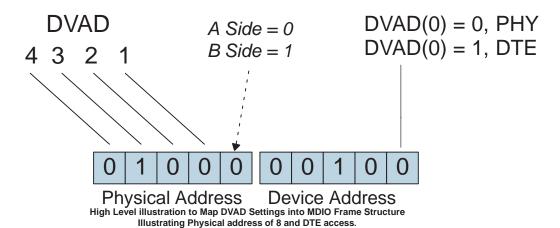

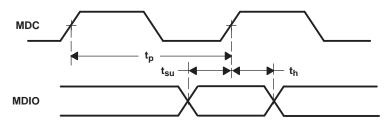

The MDIO Management Interface consists of a bi-directional data path (MDIO) and a clock reference (MDC). The device address is defined by the external inputs DVAD (4:1). DVAD (0) indicates whether the device is responding as a DTE (5.xxx) (DVAD (0) = 1) or PHY (4.xxx) (DVAD (0) = 0). Note that each register is accessed as either DTE or PHY devices in the TLK3118; although physically there is only one register accessed two different ways. Also note, the XAUI interfaces must both be DTE devices or both be PHY devices. An even PHY Address (as shown below) indicates an access to XAUI A register space, and an odd PHY Address indicates access to XAUI B register space.

Write transactions which address an invalid register or device or a read only register will be ignored. Read transactions which address an invalid register or device will return a 0.

#### NOTE:

Registers from address 32900 and above can be accessed from A side or B side. These registers are implemented from the top level and can control the entire device (XAUI-A & XAUI-B).

Figure 22. Device Address

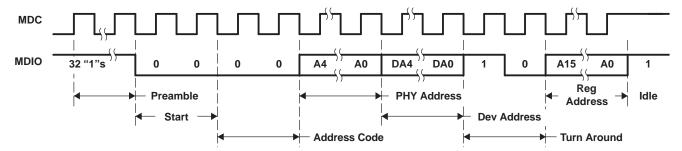

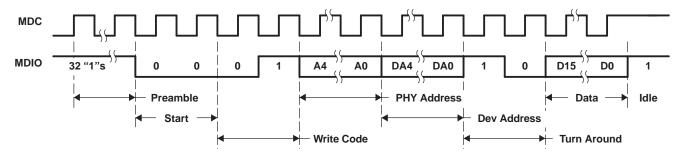

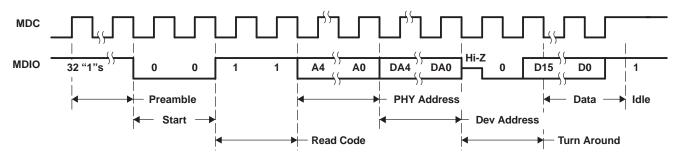

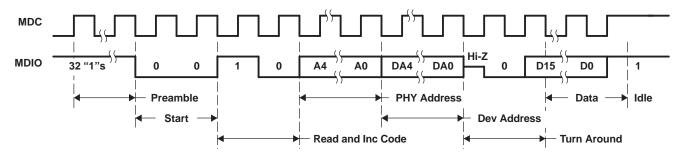

Timing for an address transaction is shown in Figure 23. The timing required to write to the internal registers is shown in Figure 24. The timing required to read from the internal registers is shown in Figure 25. The timing required to read from the internal registers and then increment the active address for the next transaction is shown in Figure 26.

Figure 23. Management Interface Extended Space Address Timing

Figure 24. Management Interface Extended Space Write Timing

Figure 25. Management Interface Extended Space Read Timing

Figure 26. Management Interface Extended Space Read and Increment Timing

The IEEE 802.3 Clause 45 specification defines many of the registers, and additional registers have been implemented for expanded functionality.

## PROGRAMMER'S REFERENCE

## Table 6. XS<sup>(1)</sup>\_CONTROL\_1

|           |                 | ·                                                           | <del>_</del>                                                                                                                                                                                                                             |                       |  |

|-----------|-----------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|

|           | Address:        | 0x0000                                                      | Default:0x2040                                                                                                                                                                                                                           |                       |  |

| Bit(s)    | Name            |                                                             | Description                                                                                                                                                                                                                              | Access <sup>(2)</sup> |  |

| 4/5.0.15  | Reset           | 1 = XS reset (including all re<br>0 = Normal operation      | 1 = XS reset (including all registers)<br>0 = Normal operation                                                                                                                                                                           |                       |  |

| 4/5.0.14  | Loop back       | XAUI_LOOPBACK will be per<br>If the device is configured as | f the device is configured as PHY XS (DVAD(0) = 0), then KAUI_LOOPBACK will be performed (RX parallel to TX parallel) f the device is configured as DTE XS (DVAD(0) = 1), then KGMII_LOOPBACK will be performed (TX serial to RX serial) |                       |  |

| 4/5.0.13  | Speed Selection | This bit always reads 1 indic                               | ating operation at 10 Gb/s and above.                                                                                                                                                                                                    |                       |  |

| 4/5.0.11  | Low power       | 1 = Low power mode<br>0 = Normal operation                  |                                                                                                                                                                                                                                          |                       |  |

| 4/5.0.6   | Speed Selection | This bit always reads 1 indic                               | ating operation at 10Gbps and above.                                                                                                                                                                                                     |                       |  |

| 4/5.0.5:2 | Speed Selection | These bits always read 0 inc                                | licating operation at 10Gbps.                                                                                                                                                                                                            |                       |  |

|           |                 |                                                             |                                                                                                                                                                                                                                          |                       |  |

- (1) In this section XS refers to either PHY or DTE XS device.

- (2) RO: Read-Only , RW: Read-Write, SC: Self-Clearing, LL: Latching-Low, LH: Latching-High, COR: Clear-on-Read

#### Table 7. XS\_STATUS\_1

|         | Address:0x000 | 1                                                                                                 | Default:0x0082 |        |

|---------|---------------|---------------------------------------------------------------------------------------------------|----------------|--------|

| Bit(s)  | Name          |                                                                                                   | Description    | Access |

| 4/5.1.7 | Fault         | 1 = Fault condition detected (eversion of 4/5.8.10 and 4/5.8.1<br>0 = No fault condition detected | ,              | RO     |

## Table 7. XS\_STATUS\_1 (continued)

| Address:0x0001 |                         |                                                                                                 | Default:0x0082                 |        |

|----------------|-------------------------|-------------------------------------------------------------------------------------------------|--------------------------------|--------|

| Bit(s)         | Name                    |                                                                                                 | Description                    | Access |

| 4/5.1.2        | XS Transmit Link Status | 1 = XS Transmit link is up<br>0 = XS Transmit links is down<br>(This bit is latched low version | of 4/5.24.12)                  | RO/LL  |

| 4/5.1.1        | Low Power Ability       | This bit always reads 1 indicat                                                                 | ing support for low power mode | RO     |

## Table 8. XS\_DEVICE\_IDENTIFIER\_1

| Address:0x0002 |         | Default:0x4000                  |        |    |

|----------------|---------|---------------------------------|--------|----|

| Bit(s) Name    |         | Description                     | Access |    |

| 4/5.2.15.0     | OUI c:r | Organizationally unique identif | er.    | RO |

## Table 9. XS\_DEVICE\_IDENTIFIER\_2

| Address:0x003 |         | Default:0x50B0                 |                           |        |

|---------------|---------|--------------------------------|---------------------------|--------|

| Bit(s)        | Name    | Description                    |                           | Access |

| 4/5.3.15:0    | OUI c:r | Device identifier. Manufacture | model and revision number | RO     |

## Table 10. XS\_SPEED\_ABILITY

| Address:0x004 |             | Default:0x0001                  |                        |        |

|---------------|-------------|---------------------------------|------------------------|--------|

| Bit(s)        | Name        | Description                     |                        | Access |

| 4/5.4.0       | 10G Capable | This bit always reads 1 indicat | ng operation at 10Gb/s | RO     |

## Table 11. XS\_DEVICES\_IN\_PACKAGE\_1

|         | Address:0x000               | 5 Default:0x0010                                                                                                    |                                                                                                                   |  |        |

|---------|-----------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|--------|

| Bit(s)  | Name                        |                                                                                                                     | Description                                                                                                       |  | Access |

| 4/5.5.5 | DTE XS Present              | 0 = DTE XS not present in the                                                                                       | = DTE XS present in the package<br>= DTE XS not present in the package<br>ead will return 1, when dvad_in is high |  | RO     |

| 4/5.5.4 | PHY XS Present              | = PHY XS present in the package<br>0 = PHY XS not present in the package<br>Read will return 1, when dvad_in is low |                                                                                                                   |  |        |

| 4/5.5.3 | PCS Present                 | Always reads 0                                                                                                      |                                                                                                                   |  |        |

| 4/5.5.2 | WIS Present                 | Always reads 0                                                                                                      | ways reads 0                                                                                                      |  |        |

| 4/5.5.1 | PMD/PMA Present             | Always reads 0                                                                                                      | ways reads 0                                                                                                      |  |        |

| 4/5.5.0 | Clause 22 registers Present | Always reads 0                                                                                                      |                                                                                                                   |  |        |

## Table 12. XS\_DEVICES\_IN\_PACKAGE\_2

|          | Address:0x00                        | 06                                         | Default:0x0000                                |        |

|----------|-------------------------------------|--------------------------------------------|-----------------------------------------------|--------|

| Bit(s)   | Name                                | Description                                |                                               | Access |

| 4/5.6.15 | Vendor Specific Device 2<br>Present | This bit always reads 0 indicat in package | ing that vendor specific device 2 not present | RO     |

| 4/5.6.14 | Vendor Specific Device 1<br>Present | This bit always reads 0 indicat in package | ing that vendor specific device 1 not present |        |

## Table 13. XS\_STATUS\_2

|             | Address:0x0008 |                                | Default:0x8C00                  |        |

|-------------|----------------|--------------------------------|---------------------------------|--------|

| Bit(s)      | Name           |                                | Description                     | Access |

| 4/5.8.15:14 | Device present | Always read 10 indicating that | device responds at this address | RO     |

## Table 13. XS\_STATUS\_2 (continued)

|          | Address:0x000  | 8                                                                  | Default:0x8C00 |        |

|----------|----------------|--------------------------------------------------------------------|----------------|--------|

| Bit(s)   | Name           |                                                                    | Description    | Access |

| 4/5.8.11 | Transmit fault | 1 = Fault condition on transmit<br>0 = No fault condition on trans |                | RO/LH  |

| 4/5.8.10 | Receive fault  | 1 = Fault condition on receive<br>0 = No fault condition on recei  |                |        |

## Table 14. XS\_PACKAGE\_IDENTIFIER\_1

|             | Address:0x000E |                                 | Default:0x4000 |        |

|-------------|----------------|---------------------------------|----------------|--------|

| Bit(s)      | Name           | Description                     |                | Access |

| 4/5.14.15:0 | OUI c:r        | Organizationally unique identif | ier.           | RO     |

## Table 15. XS\_PACKAGE\_IDENTIFIER\_2

|             | Address:0x000F |                                 | Default:0x50B0                             |        |

|-------------|----------------|---------------------------------|--------------------------------------------|--------|

| Bit(s)      | Name           | Description                     |                                            | Access |

| 4/5.15.15:0 | OUI c:r        | Organizationally unique identif | er Manufacturer model and revision number. | RO     |

## Table 16. XS\_LANE\_STATUS

|           | Address:0x              | 0018                                                         | Default:0x0C0                                             | 00     |

|-----------|-------------------------|--------------------------------------------------------------|-----------------------------------------------------------|--------|

| Bit(s)    | Name                    |                                                              | Description                                               | Access |

| 4/5.24.12 | Align status            | When 1, indicates all lanes are                              | When 1, indicates all lanes are aligned                   |        |

| 4/5.24.11 | Pattern testing ability | Always reads 1. Able to gener                                | ate test patterns                                         |        |

| 4/5.24.10 | Loopback ability        | Always read 1. Has the ability                               | to perform loopback function                              |        |

| 4/5.24.3  | Lane 3 sync             | 1 = Lane 3 is synchronized<br>0 = Lane 3 is not synchronized | 1 = Lane 3 is synchronized 0 = Lane 3 is not synchronized |        |

| 4/5.24.2  | Lane 2 sync             | 1 = Lane 2 is synchronized<br>0 = Lane 2 is not synchronized |                                                           |        |

| 4/5.24.1  | Lane 1 sync             | 1 = Lane 1 is synchronized<br>0 = Lane 1 is not synchronized | 1 = Lane 1 is synchronized 0 = Lane 1 is not synchronized |        |

| 4/5.24.0  | Lane 0 sync             | 1 = Lane 0 is synchronized<br>0 = Lane 0 is not synchronized | d                                                         |        |

## Table 17. XS\_TEST\_CONTROL

| Address:0x0019 |                             |                                                                                                                    | Default:0x0                                                                       | 000    |

|----------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------|

| Bit(s)         | Name                        |                                                                                                                    | Description                                                                       | Access |

| 4/5.25.2       | Receive test-pattern enable | When 1, indicates test pattern                                                                                     | function is enabled.                                                              | RW     |

| 4/5.25.1:0     | Test-pattern select         | 00 = High frequency test patte<br>01 = Low frequency test patte<br>10 = Mixed frequency test patt<br>11 = Reserved | <ul><li>Low frequency test pattern</li><li>Mixed frequency test pattern</li></ul> |        |

## Table 18. TEST\_CONFIG

|             | Address:0x8000 |                             | Default:0x0000               |        |

|-------------|----------------|-----------------------------|------------------------------|--------|

| Bit(s)      | Name           |                             | Description                  | Access |

| 4/5.32768.1 | CRPAT enable   | When set, enables the CRPAT | test pattern on all 4 lanes. | RW     |

| 4/5.32768.0 | CJPAT enable   | When set, enables the CJPAT | test pattern on all 4 lanes. |        |

## Table 19. 9.4.1 TEST\_VERIFICATION\_CONTROL

|             | Address:0x8001     |                                | Default:0x0000            |        |

|-------------|--------------------|--------------------------------|---------------------------|--------|

| Bit(s)      | Name               |                                | Description               | Access |

| 4/5.32769.1 | CRPAT check enable | When set, enables the verifica | tion of CRPAT test modes. | RW     |

| 4/5.32769.0 | CJPAT check enable | When set, enables the verifica | tion of CJPAT test modes. |        |

## Table 20. TX\_FIFO\_STATUS

|             | Address:0x86     | 002                                                                                              | Default:0x0000                                                                                  |        |

|-------------|------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------|

| Bit(s)      | Name             |                                                                                                  | Description                                                                                     | Access |

| 4/5.32770.9 | Lane 3 overflow  |                                                                                                  | When high, indicates that transmit FIFO overflow condition occurred for the corresponding lane. |        |

| 4/5.32770.8 | Lane 2 overflow  | corresponding lane.                                                                              |                                                                                                 |        |

| 4/5.32770.7 | Lane 1 overflow  |                                                                                                  |                                                                                                 |        |

| 4/5.32770.6 | Lane 0 overflow  |                                                                                                  |                                                                                                 | -      |

| 4/5.32770.5 | Lane 3 underflow | When high, indicates that transmit FIFO underflow condition occurred for the corresponding lane. |                                                                                                 |        |

| 4/5.32770.4 | Lane 2 underflow |                                                                                                  |                                                                                                 |        |

| 4/5.32770.3 | Lane 1 underflow |                                                                                                  |                                                                                                 |        |

| 4/5.32770.2 | Lane 0 underflow |                                                                                                  |                                                                                                 |        |

| 4/5.32770.1 | Overflow         | When high, indicates that tran lane                                                              | smit FIFO overflow condition occurred in any                                                    |        |

| 4/5.32770.0 | Underflow        | When high, indicates that tran lane                                                              | smit FIFO underflow condition occurred in any                                                   |        |

## Table 21. TX\_FIFO\_DROP\_COUNT

|                    | Address:0x8003 |                                | Default:0xFFFD          |        |

|--------------------|----------------|--------------------------------|-------------------------|--------|

| Bit(s)             | Name           |                                | Description             | Access |

| 4/5.32771.15:<br>0 | Drop count     | Counter for number of idle dro | ps in the transmit FIFO | RO/COR |

## Table 22. TX\_FIFO\_INSERT\_COUNT

|                    | Address:0x8004 |                                 | Default:0xFFFD            |        |

|--------------------|----------------|---------------------------------|---------------------------|--------|

| Bit(s)             | Name           |                                 | Description               | Access |

| 4/5.32772.15:<br>0 | Insert count   | Counter for number of idle inse | erts in the transmit FIFO | RO/COR |

## Table 23. TX\_CODEGEN\_STATUS

|             | Address:                          |                                      | Default:                                                                           |        |

|-------------|-----------------------------------|--------------------------------------|------------------------------------------------------------------------------------|--------|

| Bit(s)      | Name                              |                                      | Description                                                                        | Access |

| 4/5.32773.6 | Invalid XGMII character in lane 3 | When high, indicates invalid X lane. | GMII character received in the corresponding                                       | RO/LH  |

| 4/5.32773.5 | Invalid XGMII character in lane 2 |                                      |                                                                                    |        |

| 4/5.32773.4 | Invalid XGMII character in lane 1 |                                      |                                                                                    |        |

| 4/5.32773.3 | Invalid XGMII character in lane 0 |                                      |                                                                                    |        |

| 4/5.32773.2 | Invalid XGMII character error     | When high, indicates invalid X       | GMII character received in any lane                                                |        |

| 4/5.32773.1 | Invalid T column error            |                                      | erminate column (column that contains ed by Idle character(s)) received from the   |        |

| 4/5.32773.0 | Invalid S column error            |                                      | tart column (column that contains Start lane 0) received from the XGMII interface. |        |

#### Table 24. LANE\_0\_TEST\_ERROR\_COUNT

|                    | Address:0x8006                    |  | Default:0xFFFD                                                            |        |

|--------------------|-----------------------------------|--|---------------------------------------------------------------------------|--------|

| Bit(s)             | Name                              |  | Description                                                               | Access |

| 4/5.32774.15:<br>0 | Lane 0 test pattern error counter |  | High, Medium or Low Frequency test er increments by one for each received | RO/COR |

## Table 25. LANE\_1\_ TEST\_ERROR\_COUNT

|                    | Address:0x8007                    |  | Default:0xFFFD                                                               |        |

|--------------------|-----------------------------------|--|------------------------------------------------------------------------------|--------|

| Bit(s)             | Name                              |  | Description                                                                  | Access |

| 4/5.32775.15:<br>0 | Lane 1 test pattern error counter |  | High, Medium or Low Frequency test<br>er increments by one for each received | RO/COR |

#### Table 26. LANE\_2\_ TEST\_ERROR\_COUNT

|                    | Address:0x8008                    |  | Default:0xFFFD                                                               |        |

|--------------------|-----------------------------------|--|------------------------------------------------------------------------------|--------|

| Bit(s)             | Name                              |  | Description                                                                  | Access |

| 4/5.32776.15:<br>0 | Lane 2 test pattern error counter |  | High, Medium or Low Frequency test<br>er increments by one for each received | RO/COR |

#### Table 27. LANE\_3\_ TEST\_ERROR\_COUNT

|                    | Address:0x8009                    |  | Default:0xFFFD                                                            |        |

|--------------------|-----------------------------------|--|---------------------------------------------------------------------------|--------|

| Bit(s)             | Name                              |  | Description                                                               | Access |

| 4/5.32777.15:<br>0 | Lane 3 test pattern error counter |  | High, Medium or Low Frequency test er increments by one for each received | RO/COR |

## Table 28. CRPAT\_CJPAT\_TEST\_ERROR\_COUNT\_1<sup>(1)</sup>

|                    | Address:0x800A                 |                             | Default:0xFFFF         |        |

|--------------------|--------------------------------|-----------------------------|------------------------|--------|

| Bit(s)             | Name                           |                             | Description            | Access |

| 4/5.32778.15:<br>0 | CRPAT/CJPAT test error counter | MSB of CRPAT/CJPAT error of | ounter for all 4 lanes | RO     |

(1) User has to make sure that register 32778 is read first and then register 32779. If user reads register 32779 without reading register 32778 first, then the count value read through 32779 register may not be correct.

## Table 29. CRPAT\_CJPAT\_TEST\_ERROR\_COUNT\_2<sup>(1)</sup>

|                    | Address:0x800B                 |                             | Default:0xFFFD         |        |

|--------------------|--------------------------------|-----------------------------|------------------------|--------|

| Bit(s)             | Name                           |                             | Description            | Access |

| 4/5.32779.15:<br>0 | CRPAT/CJPAT test error counter | LSB of CRPAT/CJPAT error co | ounter for all 4 lanes | RO     |

(1) User has to make sure that register 32778 is read first and then register 32779. If user reads register 32779 without reading register 32778 first, then the count value read through 32779 register may not be correct.

## Table 30. LANE\_0\_EOP\_ERROR\_COUNT<sup>(1)</sup>

| Address:0x800C     |                                    |                                                                                                                                                                                                             | Default:0xFFFD                                 |        |

|--------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------|

| Bit(s)             | Name                               | Description                                                                                                                                                                                                 |                                                | Access |

| 4/5.32780.15:<br>0 | Lane 0 end of packet error counter | End of packet termination error counter for lane 0. End of packet error for lane 0 is detected on the RX side. It is detected when Terminate character is in lane 0 and one or both of the following holds: |                                                | RO/COR |

|                    |                                    | Terminate character is not                                                                                                                                                                                  | followed by /K/ characters in lanes 1, 2 and 3 |        |

|                    |                                    | The column following the to                                                                                                                                                                                 | erminate column is neither   K   or   A  .     |        |

(1) Counter will increment by 1 when EOP error is found on the corresponding lane and when all the lanes are aligned (align\_status should be high). Counter will hold on to its value when align\_status goes low or when the counter reaches its maximum value. It will be cleared when it is read.

#### Table 31. LANE 1 EOP ERROR COUNT<sup>(1)</sup>

| Address:0x800D     |                                    | Default:0xFFFD                                                                             |                                                                                                                                                                                                        |        |

|--------------------|------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Bit(s)             | Name                               | Description                                                                                |                                                                                                                                                                                                        | Access |

| 4/5.32781.15:<br>0 | Lane 1 end of packet error counter | lane 1 is detected on the RX s is in lane 1 and one or both of  Terminate character is not | r counter for lane 1. End of packet error for ide. It is detected when Terminate character the following holds: followed by /K/ characters in lanes 2 and 3 erminate column is neither   K   or   A  . | RO/COR |

(1) Counter will increment by 1 when EOP error is found on the corresponding lane and when all the lanes are aligned (align\_status should be high). Counter will hold on to its value when align\_status goes low or when the counter reaches its maximum value. It will be cleared when it is read.

#### Table 32. LANE 2 EOP ERROR COUNT(1)

| Address:0x800E     |                                    | Default:0xFFFD                                                                                    |                                                                                                                                                                                                |        |

|--------------------|------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Bit(s)             | Name                               | Description                                                                                       |                                                                                                                                                                                                | Access |

| 4/5.32782.15:<br>0 | Lane 2 end of packet error counter | lane 2 is detected on the RX s<br>is in lane 2 and one or both of<br>• Terminate character is not | r counter for lane 2. End of packet error for ide. It is detected when Terminate character the following holds: followed by /K/ character in lane 3 erminate column is neither   K   or   A  . | RO/COR |

(1) Counter will increment by 1 when EOP error is found on the corresponding lane and when all the lanes are aligned (align\_status should be high). Counter will hold on to its value when align\_status goes low or when the counter reaches its maximum value. It will be cleared when it is read.

#### Table 33. LANE 3 EOP ERROR COUNT<sup>(1)</sup>

| Address:0x800F     |                                    | Default:0xFFFD                 |                                                                                                                                            |        |

|--------------------|------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Bit(s)             | Name                               | Description                    |                                                                                                                                            | Access |

| 4/5.32783.15:<br>0 | Lane 3 end of packet error counter | lane 3 is detected on the RX s | r counter for lane 3. End of packet error for ide. It is detected when Terminate character lowing the terminate column is neither   K   or | RO/COR |

(1) Counter will increment by 1 when EOP error is found on the corresponding lane and when all the lanes are aligned (align\_status should be high). Counter will hold on to its value when align\_status goes low or when the counter reaches its maximum value. It will be cleared when it is read.

#### Table 34. LANE 0 CODE ERROR COUNT<sup>(1)</sup>

|                    | Address:0x8010            |  | Default:0xFFFD                                                                       |        |

|--------------------|---------------------------|--|--------------------------------------------------------------------------------------|--------|

| Bit(s)             | Name                      |  | Description                                                                          | Access |