# Microsemi G.8262/Stratum3 System Synchronizer/SETS

Data Sheet

March 2013

#### **Features**

- Supports the requirements of ITU-T G.8262 for synchronous Ethernet Equipment slave Clocks (EEC option 1 and 2)

- Supports the requirements of Telcordia GR-1244 Stratum 3 and GR-253, ITU-T G.813, and G.781 SETS

- Supports ITU-T G.823, G.824 and G.8261 for 2048 kbit/s and 1544 kbit/s interfaces

- Meets the SONET/SDH jitter generation requirements up to OC-48/STM-16

- Synchronizes to telecom reference clocks (2 kHz, N\*8 kHz up to 77.76 MHz, 155.52 MHz) or to Ethernet reference clocks (25 MHz, 50 MHz, 62.5 MHz, 125 MHz)

- Supports composite clock inputs (64 kHz, 64 kHz + 8 kHz, 64kHz + 8 kHz + 400 Hz)

- Generates standard SONET/SDH clock rates (e.g., 19.44 MHz, 38.88 MHz, 77.76 MHz, 155.52 MHz, 622.08 MHz) or Ethernet clock rates (e.g., 25 MHz, 50 MHz, 125 MHz, 156.25 MHz, 312.5 MHz) for synchronizing Gigabit Ethernet PHYs

- Programmable output synthesizers (P0, P1) generate telecom clock frequencies from any multiple of 8 kHz up to 100 MHz

- Generates several styles of telecom frame pulses with selectable pulse width, polarity and frequency

- Provides two DPLLs which are independently configurable through a serial interface

#### **Ordering Information**

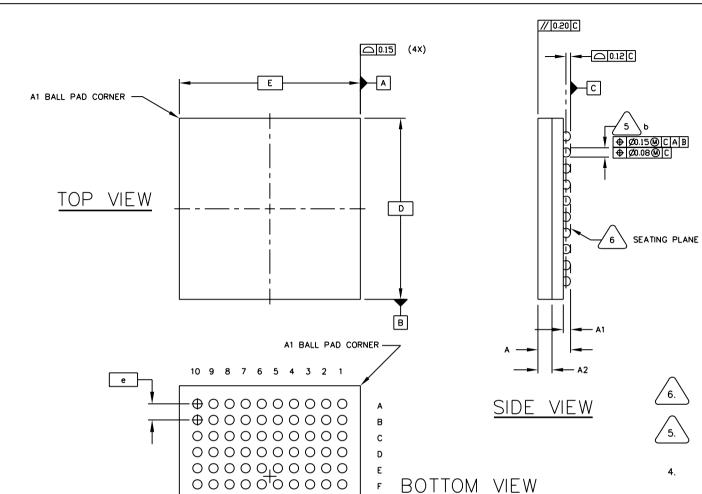

ZL30143GGG 100 Pin CABGA Trays ZL30143GGG2 100 Pin CABGA\* Trays \*Pb Free Tin/Silver/Copper

-40°C to +85°C

- Internal state machine automatically controls mode of operation (free-run, locked, holdover)

- Flexible input reference monitoring automatically disqualifies references based on frequency and phase irregularities

- Provides automatic reference switching and holdover during loss of reference input

- Supports master/slave configuration and dynamic input to output delay compensation for AdvancedTCA<sup>TM</sup>

- Configurable input to output delay and output to output phase alignment

#### **Applications**

- ITU-T G.8262 System Timing Cards which support 1 GbE and 10 GbE interfaces

- Telcordia GR-253 Carrier Grade SONET/SDH Stratum 3 System Timing Cards

- System Timing Cards which supports ITU-T G.781 SETS (SDH Equipment Timing Source)

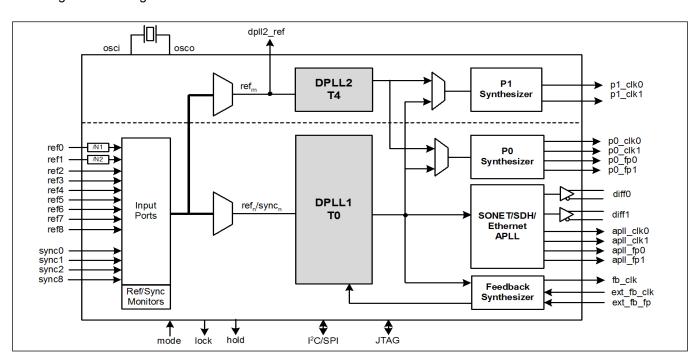

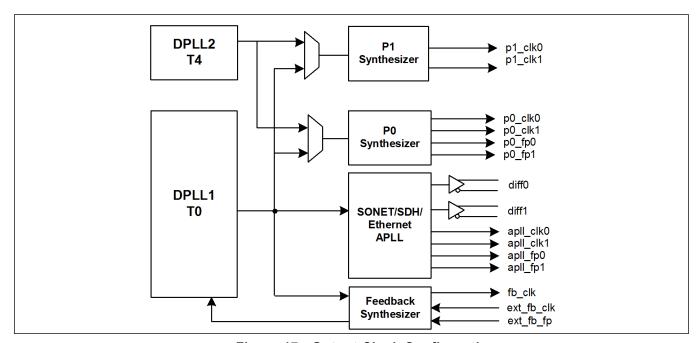

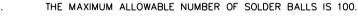

Figure 1 - Functional Block Diagram

## **Table of Contents**

|     | Pin Diagram                                                   |      |

|-----|---------------------------------------------------------------|------|

| 2.0 | Overview                                                      | . 13 |

|     | 2.1 DPLL Features                                             | . 15 |

|     | 2.2 DPLL Mode Control                                         | . 16 |

|     | 2.2.1 DPLL1 Mode Of Operation                                 | . 17 |

|     | 2.2.1.1 ToP (Timing over Packet) Client Mode                  | . 17 |

|     | 2.2.2 DPLL2 Mode of Operation                                 | . 17 |

|     | 2.3 Loop Bandwidth                                            |      |

|     | 2.4 Pull-in/hold-in Range                                     |      |

|     | 2.5 Phase Slope Limiting                                      |      |

|     | 2.6 Hitless Reference Switching                               |      |

|     | 2.7 Free-run Frequency Offset                                 | . 19 |

|     | 2.8 Holdover                                                  |      |

|     | 2.9 Reference and Sync Inputs                                 |      |

|     | 2.9.1 Receiving Composite Clocks                              |      |

|     | 2.10 Reference Input Selection                                |      |

|     | 2.11 Reference Monitoring                                     |      |

|     | 2.12 Sync Monitoring                                          |      |

|     | 2.13 Reference Monitoring for Custom Configurations           |      |

|     | 2.14 9th Input Reference (Ref8/Sync8)                         |      |

|     | 2.15 Output Clocks and Frame Pulses                           |      |

|     | 2.15.1 Output Clock and Frame Pulse Squelching                |      |

|     | 2.15.2 Disabling Output Clocks and Frame Pulses               |      |

|     | 2.15.3 Disabling Output Synthesizers                          |      |

|     | 2.16 Configurable Input-to-Output and Output-to-Output Delays |      |

|     | 2.17 Master/Slave Configuration                               |      |

|     | 2.18 External Feedback Inputs                                 |      |

|     | 2.19 Master Clock Interface                                   |      |

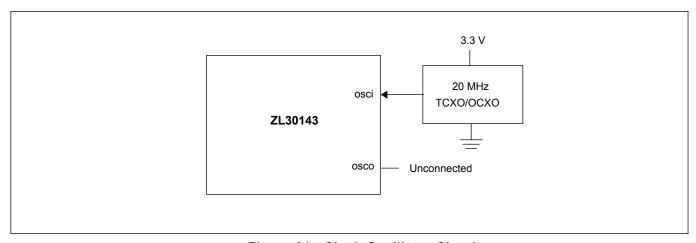

|     | 2.19.1 Clock Oscillator                                       |      |

|     | 2.20 Power Up/Down Sequence                                   |      |

|     | 2.21 Power Supply Filtering                                   |      |

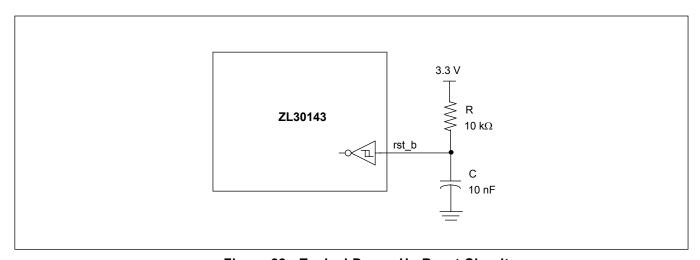

|     | 2.22 Reset Circuit                                            |      |

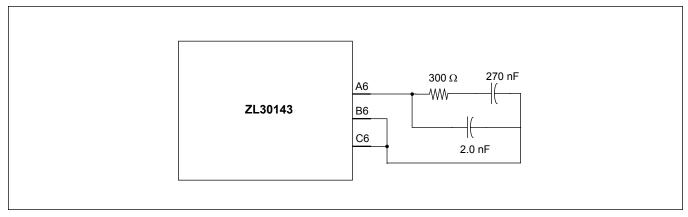

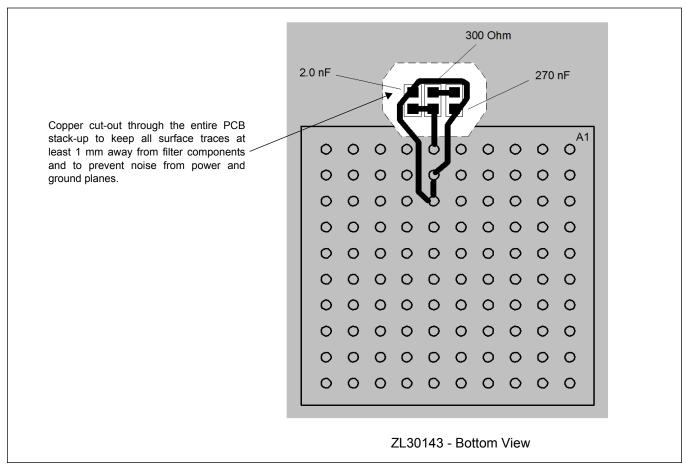

|     | 2.23 APLL Filter Components and Recommended Layout            |      |

|     | 2.24 Serial Interface                                         |      |

|     | 2.24.1 Serial Peripheral Interface                            |      |

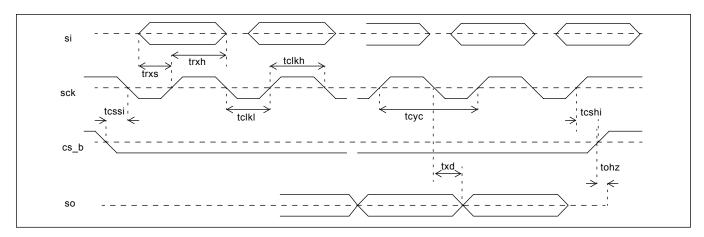

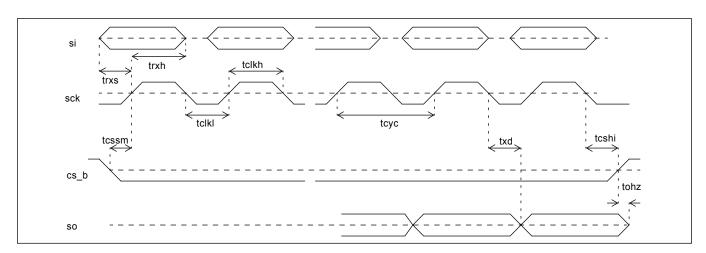

|     | 2.24.2 SPI Functional Waveforms.                              |      |

|     | 2.24.3 I2C Interface.                                         | . 47 |

| 3.0 | Software Configuration                                        | . 49 |

|     | 3.1 Interrupts                                                |      |

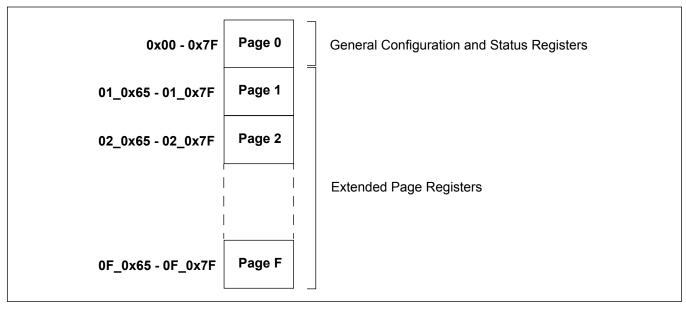

|     | 3.2 Extended Page Registers                                   |      |

|     | 3.3 Multi-byte Register Values                                |      |

| 1.0 | Detailed Register Map                                         | . 61 |

|     | AC and DC Electrical Characteristics                          |      |

|     |                                                               | 164  |

|     |                                                               |      |

## **List of Figures**

| Figure 1 - Functional Block Diagram                                                      | 1    |

|------------------------------------------------------------------------------------------|------|

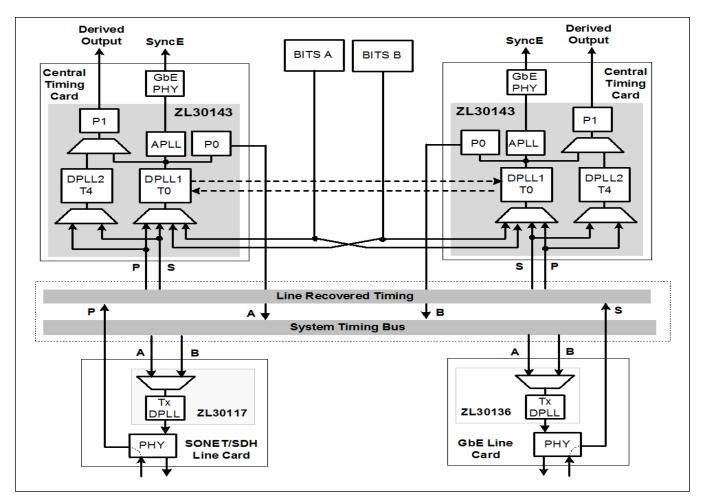

| Figure 2 - Typical Application of the ZL30143                                            | . 13 |

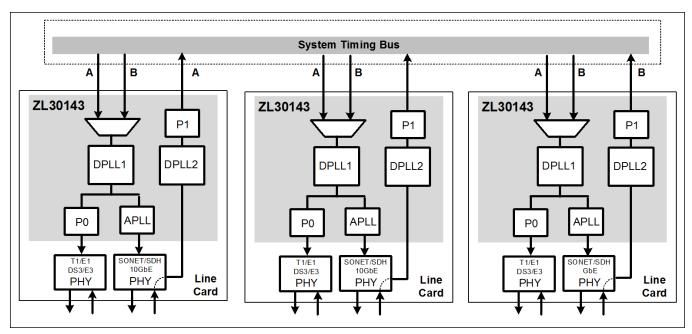

| Figure 3 - The ZL30143 as a Timing Card and a Line Card Device                           | . 14 |

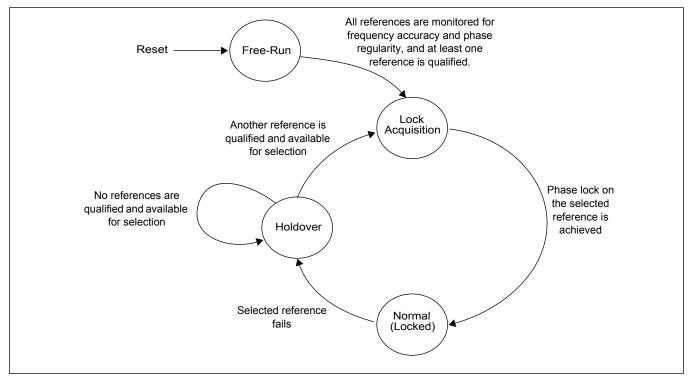

| Figure 4 - Automatic Mode State Machine                                                  | . 16 |

| Figure 5 - Reference and Sync Inputs                                                     | . 20 |

| Figure 6 - Output Frame Pulse Alignment                                                  | . 21 |

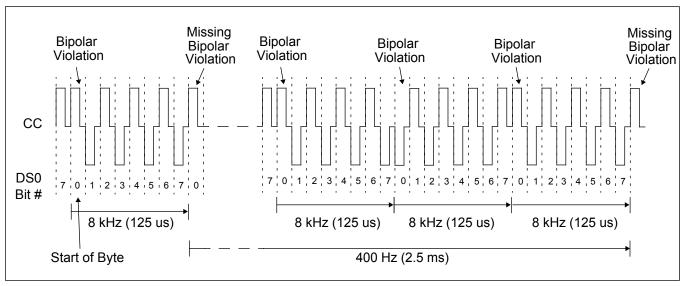

| Figure 7 - GR-378/G.703 Composite Clock Format                                           | . 22 |

| Figure 8 - External Circuit for Converting a Bipolar CC Signal into Two Unipolar Signals | . 23 |

| Figure 9 - G.703 Japanese Composite Clock (Appendix II)                                  |      |

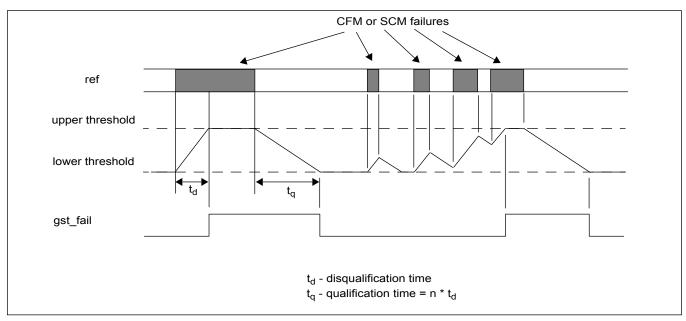

| Figure 10 - Behaviour of the Guard Soak Timer during CFM or SCM Failures                 | . 26 |

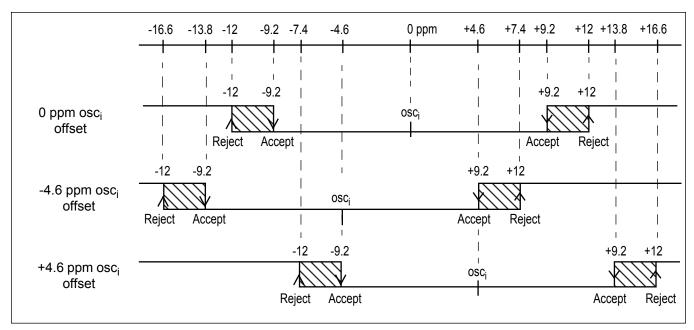

| Figure 11 - Stratum 3/G.813 Option I Frequency Acceptance and Rejection Ranges           | . 27 |

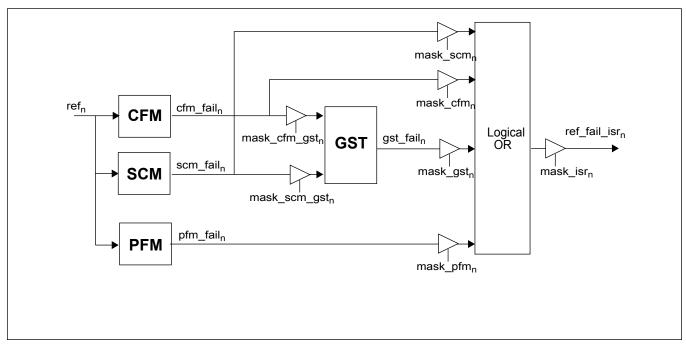

| Figure 12 - Reference Monitoring Block Diagram                                           | . 28 |

| Figure 13 - Sync Monitoring                                                              | . 28 |

| Figure 14 - Defining SCM Limits for Custom Configurations                                | . 29 |

| Figure 15 - Custom CFM Configuration for 25 MHz                                          | . 30 |

| Figure 16 - Reference and Sync Inputs                                                    | . 31 |

| Figure 17 - Output Clock Configuration                                                   | . 33 |

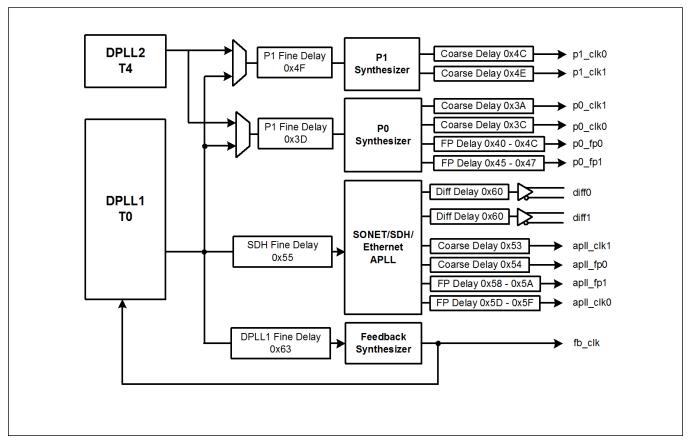

| Figure 18 - Phase Delay Adjustments                                                      | . 38 |

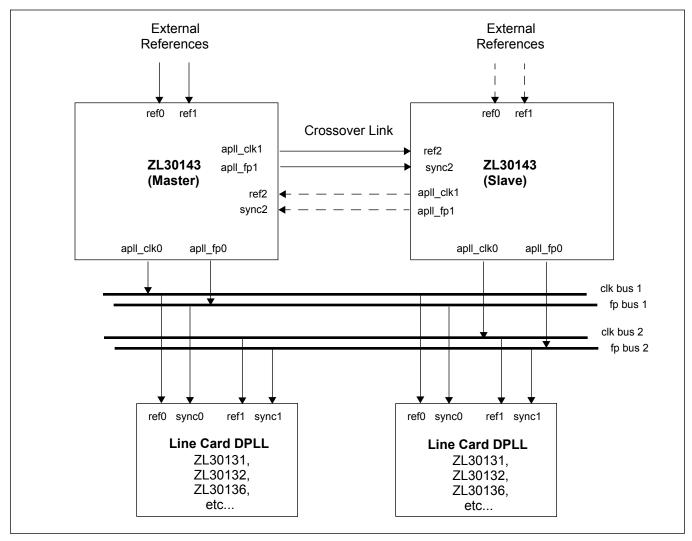

| Figure 19 - Typical Master/Slave Configuration                                           | . 40 |

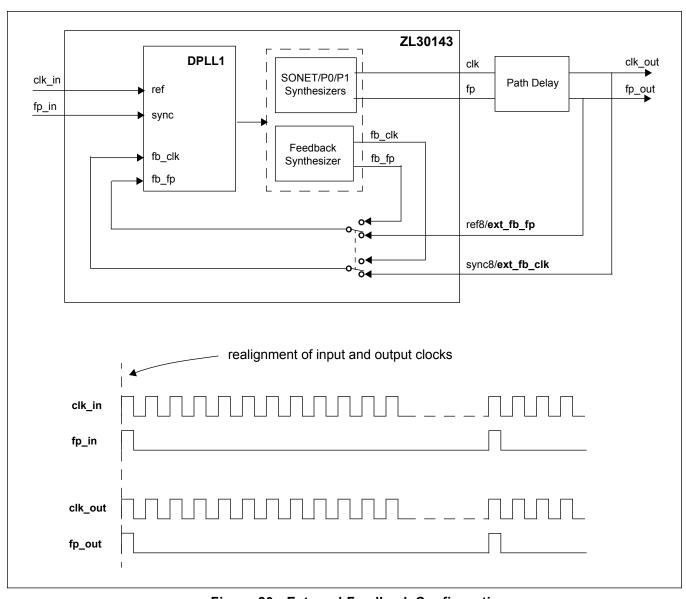

| Figure 20 - External Feedback Configuration                                              | . 41 |

| Figure 21 - Clock Oscillator Circuit                                                     |      |

| Figure 22 - Typical Power-Up Reset Circuit                                               |      |

| Figure 23 - APLL Filter Component Values                                                 |      |

| Figure 24 - Recommended APLL Filter Layout                                               |      |

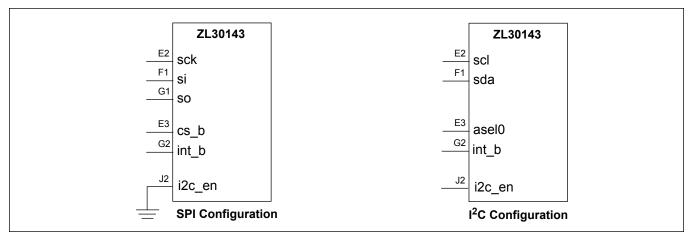

| Figure 25 - Serial Interface Configuration                                               |      |

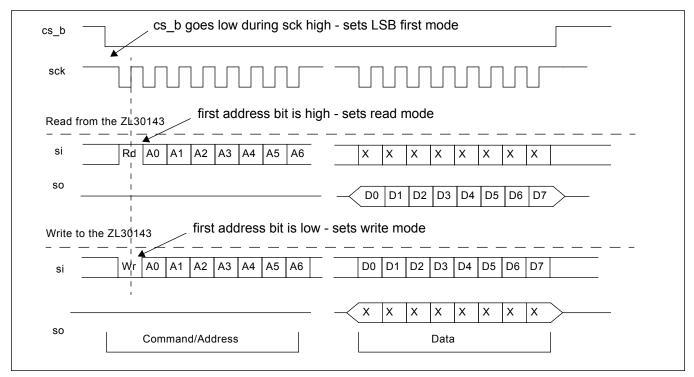

| Figure 26 - LSB First Mode - One Byte Transfer                                           |      |

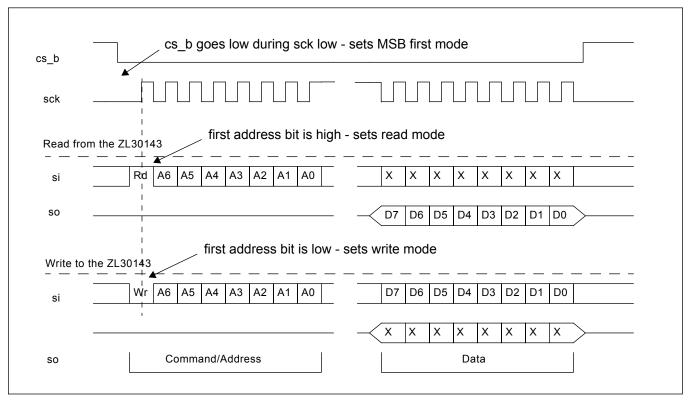

| Figure 27 - MSB First Mode - One Byte Transfer                                           |      |

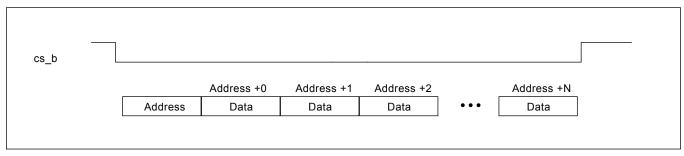

| Figure 28 - Example of a Burst Mode Operation                                            |      |

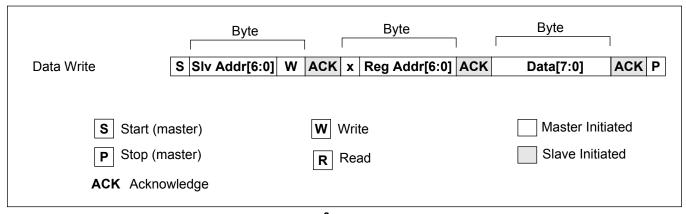

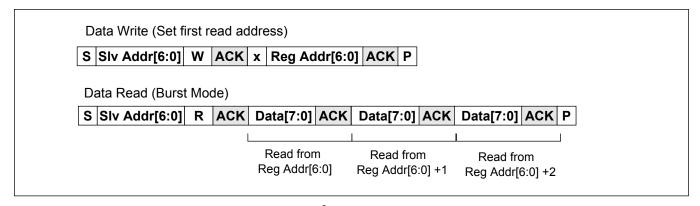

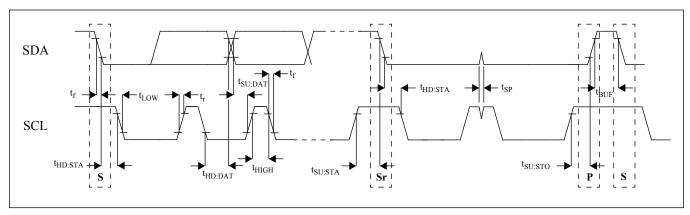

| Figure 29 - I2C Data Write Protocol                                                      |      |

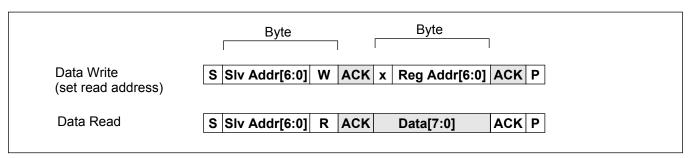

| Figure 30 - I2C Data Write Protocol                                                      |      |

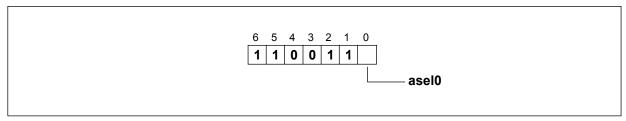

| Figure 31 - ZL30143 I2C 7-bit slave address                                              |      |

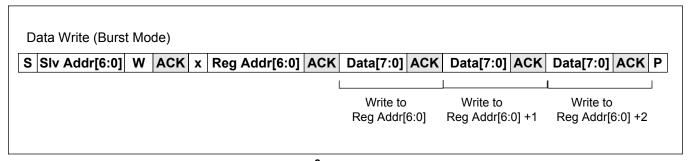

| Figure 32 - I2C Data Write Burst Mode                                                    |      |

| Figure 33 - I2C Data Read Burst Mode                                                     |      |

| Figure 34 - Memory Map Organization                                                      |      |

| Figure 35 - Accessing Multi-byte Register Values                                         | . 50 |

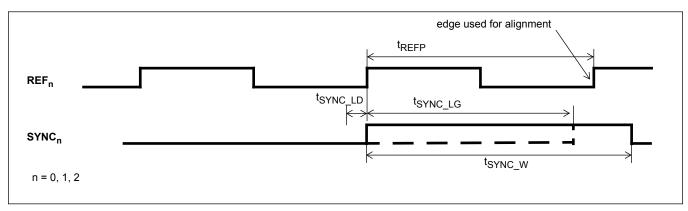

| Figure 36 - Sync Input Timing                                                            |      |

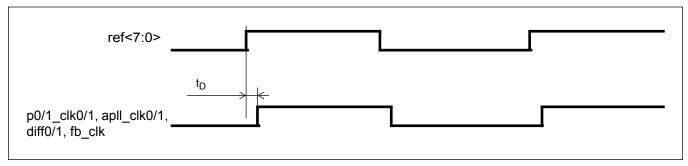

| Figure 37 - Input To Output Timing                                                       |      |

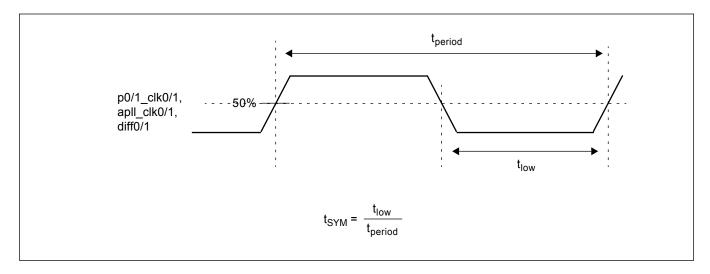

| Figure 38 - Output Duty Cycle                                                            |      |

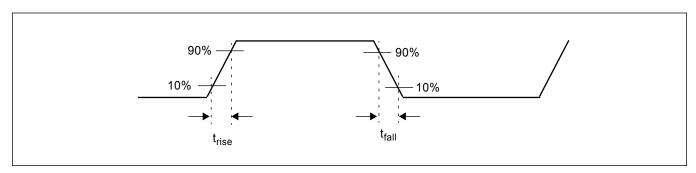

| Figure 39 - Output Clock Fall and Rise Times                                             |      |

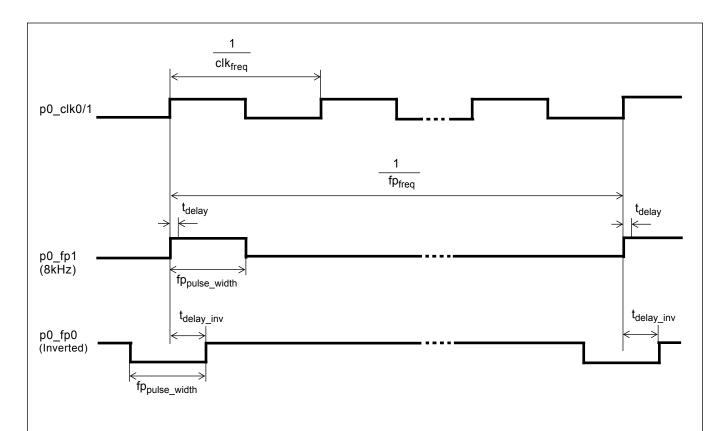

| Figure 40 - E1 Output Frame Pulse Timing                                                 |      |

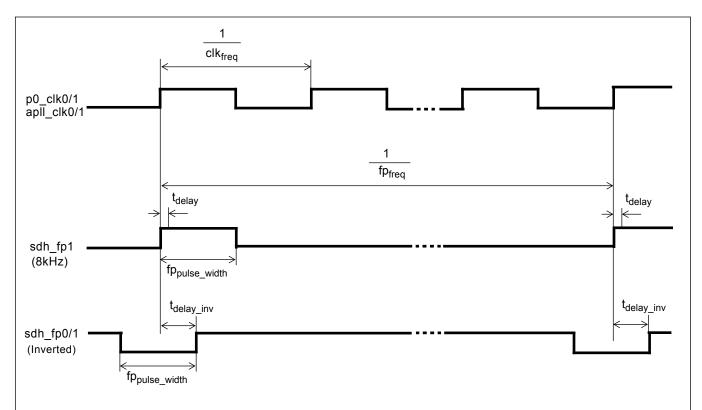

| Figure 41 - SONET Output Frame Pulse Timing                                              |      |

| Figure 42 - Serial Peripheral Interface Timing - LSB First Mode                          |      |

| Figure 43 - Serial Peripheral Interface Timing - MSB First Mode                          |      |

| Figure 44 - I2C Serial Microport Timing                                                  | 159  |

## **List of Tables**

| Table 1 - DPLL1 and DPLL2 Features                         | 15  |

|------------------------------------------------------------|-----|

| Table 2 - DPLL1 Default Mode Selection                     | 17  |

| Table 3 - DPLL1 Loop Bandwidth                             | 18  |

| Table 4 - DPLL1 Pull-in Range                              | 18  |

| Table 5 - DPLL Phase Slope Limiting                        | 18  |

| Table 6 - Set of Pre-Defined Auto-Detect Clock Frequencies | 20  |

| Table 7 - Set of Pre-Defined Auto-Detect Sync Frequencies  | 21  |

| Table 8 - Frequency Out of Range Limits                    | 26  |

| Table 9 - Ref8 and Sync8 Control and Status Registers      | 32  |

| Table 10 - APLL LVCMOS Output Clock Frequencies            | 34  |

| Table 11 - APLL Differential Output Clock Frequencies      | 34  |

| Table 12 - APLL Frame Pulse Frequencies                    |     |

| Table 13 - APLL Frame Pulse Widths                         | 36  |

| Table 14 - P0 Frame Pulse Frequencies                      | 36  |

| Table 15 - P0 Frame Pulse Widths                           | 37  |

| Table 16 - Master Oscillator Frequency Accuracy            | 42  |

| Table 17 - Register Map                                    |     |

| Table 18 - Serial Peripheral Interface Timing              | 158 |

| Table 19 - I2C Serial Microport Timing                     |     |

| Table 20 - Thermal Data                                    | 164 |

## **Change Summary**

The following table captures changes from September 2010 issue to March 2013 issue.

| Page     | Item                            | Change                                           |

|----------|---------------------------------|--------------------------------------------------|

| Multiple | Zarlink logo and name reference | Updated to Microsemi <sup>®</sup> logo and name. |

Below are the changes from the April 2010 issue to the September 2010 issue.

| Page                               | Item                            | Change                              |

|------------------------------------|---------------------------------|-------------------------------------|

| 21                                 | Table 8                         | Added note for 1 Hz sync detection. |

| 141                                | Register "1Hz_enable (08_0x71)" | Added register description.         |

| 118 Register "Page Pointer" (0x64) |                                 | Updated register description.       |

Below are the changes from the July 2009 issue to the April 2010 issue.

| Page                                           | Item                                           | Change           |

|------------------------------------------------|------------------------------------------------|------------------|

| 134                                            | Page_Address: 01_0x75 to Page_Address: 01_0x7C | Added Registers. |

| 143                                            | Page_Address: 0A_0x72                          | Replaced Table.  |

| Page_Address: 0A_0x76 to Page_Address: 0A_0x7D |                                                | Added Registers. |

Below are the changes from the February 2009 issue to the July 2009 issue.

| Page | Item                                                    | Change                                                                                 |

|------|---------------------------------------------------------|----------------------------------------------------------------------------------------|

| 15   | Table 1 -, "DPLL1 and DPLL2 Features"                   | Updated lock times and add ToP Client mode                                             |

| 17   | Section 2.2.1.1, "ToP (Timing over Packet) Client Mode" | Added section for ToP Client Mode                                                      |

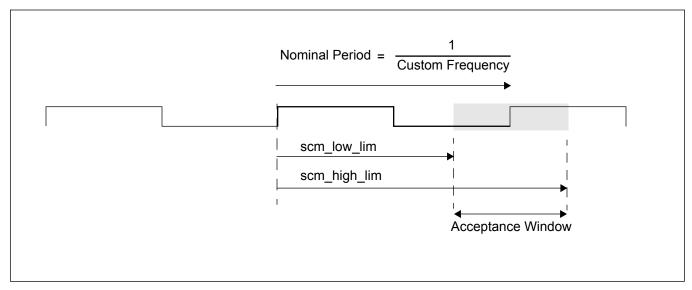

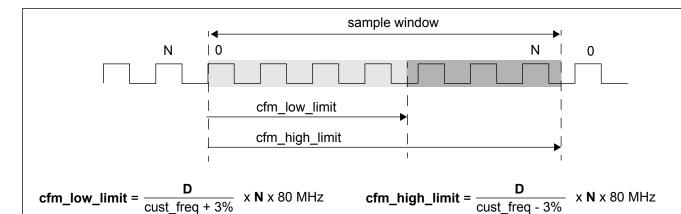

| 29   | 2.13, "Reference Monitoring for Custom Configurations"  | Added instructions for SCM and CFM limits when using low frequency customs frequencies |

| 33   | 2.15, "Output Clocks and Frame Pulses"                  | Added reference to ZLAN-254.                                                           |

| 36   | Table 14 - P0 Frame Pulse<br>Frequencies                | Added 1 Hz option for p0_fpn outputs                                                   |

| 81   | Register Address: 0x1F                                  | Added ToP Client Mode                                                                  |

| 101  | Register address: 0x3E                                  | Added 1 Hz option for po_fp0                                                           |

| 101  | Register address: 0x3F                                  | Updated descriptions for 1 Hz option                                                   |

| 103  | Register address: 0x43                                  | Added 1 Hz option for po_fp1                                                           |

| Page     | Item                                                                                     | Change                                       |

|----------|------------------------------------------------------------------------------------------|----------------------------------------------|

| 103      | Register address: 0x44                                                                   | Updated descriptions for 1 Hz option         |

| 131      | Register Addresses 01_0x69 to 01_0x70                                                    | Added DCO_Phase_0 to DCO_Phase_7 registers   |

| 133      | Register Addresses: 01_0x71 to 01_0x74                                                   | Added Local_Time_0 to Local_Time_4 registers |

| 142      | Register Address: 0A_0x6C                                                                | Added DCO_Update register                    |

| 143      | Register Address: 0A_0x71                                                                | Added DCO_update_interval register           |

| 137      | Register Address: 0A_0x72                                                                | Added ToP_1 Hz_Alignment register            |

| 146      | Register Address: 0F_0x65                                                                | Corrected the bit descriptions               |

| 146      | Register Address: 0F_0x67                                                                | Clarified bit descriptions.                  |

| 148      | Register Address: 0F_0x6E                                                                | Added ToP_isr register                       |

| 148      | Register Address: 0F_0x6F                                                                | Added ToP_isr_mask register                  |

| 148      | Register Address: 0F_0x7D                                                                | Added isr0_reg                               |

| 149      | Register Address: 0F_0x7E                                                                | Added Register                               |

| 130, 131 | Register Address: 01_0x65, Register<br>Address: 01_0x67 and Register<br>Address: 01_0x68 | Corrected description                        |

## **Pin Description**

| Pin#                                         | Name                                    | I/O<br>Type    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|----------------------------------------------|-----------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Input I                                      | Input Reference                         |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| C1<br>B2<br>A3<br>C3<br>B3<br>B4<br>C4<br>A4 | ref0 ref1 ref2 ref3 ref4 ref5 ref6 ref7 | I <sub>u</sub> | Input References 7:0 (LVCMOS, Schmitt Trigger). These input references are available to both DPLL1 and DPLL2 for synchronizing output clocks. All eight input references can lock to any multiple of 8 kHz up to 77.76 MHz including 25 MHz and 50 MHz. Input ref0 and ref1 have additional configurable predividers allowing input frequencies of 62.5 MHz, 125 MHz, and 155.52 MHz. These pins are internally pulled up to $V_{\rm dd}$ .                                                              |  |  |  |

| B1<br>A1<br>A2                               | sync0<br>sync1<br>sync2                 | I <sub>u</sub> | Frame Pulse Synchronization References 2:0 (LVCMOS, Schmitt Trigger). These are optional frame pulse synchronization inputs associated with input references 0, 1 and 2. These inputs accept frame pulses in a clock format (50% duty cycle) or a basic frame pulse format with minimum pulse width of 5 ns. These pins are internally pulled up to $V_{\rm dd}$ .                                                                                                                                       |  |  |  |

| C5                                           | ref8/ext_fb_clk                         | I <sub>u</sub> | Input Reference 8/External DPLL Feedback Clock (LVCMOS, Schmitt Trigger). This pin acts as either an ext_fb_clk input or as the ref8 input. The desired function for the pin is selectable through the software interface with a programmable register bit. This pin is internally pulled up to V <sub>dd.</sub> Leave open when not in use.                                                                                                                                                             |  |  |  |

| B5                                           | sync8/ext_fb_fp                         | I <sub>u</sub> | Frame Pulse Synchronization Reference 8/External DPLL Feedback Frame Pulse (LVCMOS, Schmitt Trigger). This pin acts as either an ext_fb_fp input or as the sync8 input. The desired function for the pin is selectable through the software interface with a programmable register bit. This pin is internally pulled up to V <sub>dd</sub> . Leave open when not in use.                                                                                                                                |  |  |  |

| Outpu                                        | t Clocks and Fra                        | me Puls        | es                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| A9<br>B10                                    | diff0_p<br>diff0_n                      | 0              | <b>Differential Output Clock 0 (LVPECL).</b> When in SONET/SDH mode, this output can be configured to provide any one of the available SONET/SDH clocks (6.48 MHz, 19.44 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz, 155.52 MHz, 311.04 MHz, 622.08 MHz). When in Ethernet mode, this output can be configured to provide any of the Ethernet clocks (25 MHz, 50 MHz, 62.5 MHz, 125 MHz, 156.25 MHz, 312.5 MHz). See "Output Clocks and Frame Pulses" on page 33 for more details on clock frequency settings. |  |  |  |

| A10<br>B9                                    | diff1_p<br>diff1_n                      | 0              | Differential Output Clock 1 (LVPECL). When in SONET/SDH mode, this output can be configured to provide any one of the available SONET/SDH clocks (6.48 MHz, 19.44 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz, 155.52 MHz, 311.04 MHz, 622.08 MHz). When in Ethernet mode, this output can be configured to provide any of the Ethernet clocks (25 MHz, 50 MHz, 62.5 MHz, 125 MHz, 156.25 MHz, 312.5 MHz). See "Output Clocks and Frame Pulses" on page 33 for more details on clock frequency settings.        |  |  |  |

| D10                                          | apll_clk0                               | 0              | <b>APLL Output Clock 0 (LVCMOS).</b> When in SONET/SDH mode, this output can be configured to provide any one of the available SONET/SDH clocks up to 77.76 MHz. When in Ethernet mode, this output can be configured to provide any of the Ethernet clocks up to 125 MHz. See "Output Clocks and Frame Pulses" on page 33 for more details on clock frequency settings. The default frequency for this output is 77.76 MHz.                                                                             |  |  |  |

| Pin#    | Name      | I/O<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|---------|-----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| G10     | apll_clk1 | 0           | APLL Output Clock 1 (LVCMOS). When in SONET/SDH mode, this output can be configured to provide any one of the available SONET/SDH clocks up to 77.76 MHz. When in Ethernet mode, this output can be configured to provide any of the Ethernet clocks up to 125 MHz. See "Output Clocks and Frame Pulses" on page 33 for more details on clock frequency settings. The default frequency for this output is 19.44 MHz. |  |

| E10     | apll_fp0  | 0           | <b>APLL Output Frame Pulse 0 (LVCMOS).</b> This output can be configured to provide virtually any style of output frame pulse synchronized with an associated SONET/SDH family output clock. The default frequency for this frame pulse output is 8 kHz.                                                                                                                                                              |  |

| F10     | apll_fp1  | 0           | <b>APLL Output Frame Pulse 1 (LVCMOS).</b> This output can be configured to provide virtually any style of output frame pulse synchronized with an associated SONET/SDH family output clock. The default frequency for this frame pulse output is 2 kHz.                                                                                                                                                              |  |

| K9      | p0_clk0   | 0           | <b>Programmable Synthesizer 0 - Output Clock 0 (LVCMOS).</b> This output can be configured to provide any frequency with a multiple of 8 kHz up to 100 MHz in addition to 2 kHz. The default frequency for this output is 2.048 MHz.                                                                                                                                                                                  |  |

| K7      | p0_clk1   | 0           | Programmable Synthesizer 0 - Output Clock 1 (LVCMOS). This is programmable clock output configurable as a multiple or division of the p0_c frequency within the range of 2 kHz to 100 MHz. The default frequency for toutput is 8.192 MHz.                                                                                                                                                                            |  |

| K8      | p0_fp0    | 0           | Programmable Synthesizer 0 - Output Frame Pulse 0 (LVCMOS). This output can be configured to provide virtually any style of output frame pulse associated with the p0 clocks. The default frequency for this frame pulse output is 8 kHz.                                                                                                                                                                             |  |

| J7      | p0_fp1    | 0           | Programmable Synthesizer 0 - Output Frame Pulse 1 (LVCMOS). This output can be configured to provide virtually any style of output frame pulse associated with the p0 clocks. The default frequency for this frame pulse output is 8 kHz                                                                                                                                                                              |  |

| J10     | p1_clk0   | 0           | Programmable Synthesizer 1 - Output Clock 0 (LVCMOS). This output can be configured to provide any frequency with a multiple of 8 kHz up to 100 MHz in addition to 2 kHz. The default frequency for this output is 1.544 MHz (DS1).                                                                                                                                                                                   |  |

| K10     | p1_clk1   | 0           | Programmable Synthesizer1 - Output Clock 1 (LVCMOS). This is programmable clock output configurable as a multiple or division of the p1_clk frequency within the range of 2 kHz to 100 MHz. The default frequency for thi output is 3.088 MHz (2x DS1).                                                                                                                                                               |  |

| H10     | fb_clk    | 0           | <b>Feedback Clock (LVCMOS).</b> This output is a buffered copy of the feedback clock for DPLL1. The frequency of this output always equals the frequency of selected reference.                                                                                                                                                                                                                                       |  |

| E1      | dpll2_ref | 0           | <b>DPLL2 Selected Output Reference (LVCMOS).</b> This is a buffered copy of the output of the reference selector for DPLL2. Switching between input reference clocks at this output is not hitless.                                                                                                                                                                                                                   |  |

| Control |           |             |                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| H5      | rst_b     | ı           | Reset (LVCMOS, Schmitt Trigger). A logic low at this input resets the device. To ensure proper operation, the device must be reset after power-up. Reset should be asserted for a minimum of 300 ns.                                                                                                                                                                                                                  |  |

| Pin#     | Name                             | I/O<br>Type    | Description                                                                                                                                                                                                                                                                                                                                                                                        |  |

|----------|----------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| J5       | dpll1_hs_en                      | I <sub>u</sub> | <b>DPLL1 Hitless Switching Enable (LVCMOS, Schmitt Trigger).</b> A logic high at this input enables hitless reference switching. A logic low disables hitless reference switching and re-aligns DPLL1's output phase to the phase of the selected reference input. This feature can also be controlled through software registers. This pin is internally pulled up to Vdd.                        |  |

| C2<br>D2 | dpll1_mod_sel0<br>dpll1_mod_sel1 | I <sub>u</sub> | <b>DPLL1 Mode Select 1:0 (LVCMOS, Schmitt Trigger).</b> During reset, the levels on these pins determine the default mode of operation for DPLL1 (Automatic, Normal, Holdover or Freerun). After reset, the mode of operation can be controlled directly with these pins, or by accessing the dpll1_modesel register (0x1F) through the serial interface. This pin is internally pulled up to Vdd. |  |

| D1       | slave_en                         | l <sub>u</sub> | Master/Slave control (LVCMOS, Schmitt Trigger). This pin selects the mode of operation for the device. If set high, slave mode is selected. If set low, master mode is selected. This feature can also be controlled through software registers. This pin is internally pulled up to Vdd.                                                                                                          |  |

| K1       | diff0_en                         | l <sub>u</sub> | <b>Differential Output 0 Enable (LVCMOS, Schmitt Trigger).</b> When set high, the differential LVPECL output 0 driver is enabled. When set low, the differential driver is tristated reducing power consumption. This pin is internally pulled up to Vdd.                                                                                                                                          |  |

| D3       | diff1_en                         | I <sub>u</sub> | <b>Differential Output 1 Enable (LVCMOS, Schmitt Trigger).</b> When set high, the differential LVPECL output 1 driver is enabled. When set low, the differential driver is tristated reducing power consumption. This pin is internally pulled up to Vdd.                                                                                                                                          |  |

| Status   |                                  |                |                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| H1       | dpll1_lock                       | 0              | <b>Lock Indicator (LVCMOS).</b> This is the lock indicator pin for DPLL1. This output goes high when DPLL1's output is frequency and phase locked to the input reference.                                                                                                                                                                                                                          |  |

| J1       | dpll1_holdover                   | 0              | <b>Holdover Indicator (LVCMOS).</b> This pin goes high when DPLL1 enters the holdover mode.                                                                                                                                                                                                                                                                                                        |  |

| Serial   | Interface                        |                |                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| E2       | sck_scl                          | I/B            | Clock for Serial Interface (LVCMOS). Serial interface clock. When i2c_en = 0, this pin acts as the sck pin for the serial interface. When i2c_en = 1, this pin acts as the scl pin (bidirectional) for the I <sup>2</sup> C interface.                                                                                                                                                             |  |

| F1       | si_sda                           | I/B            | <b>Serial Interface Input (LVCMOS).</b> Serial interface data pin. When i2c_en = 0, this pin acts as the si pin for the serial interface. When i2c_en = 1, this pin acts as the sda pin (bidirectional) for the I <sup>2</sup> C interface.                                                                                                                                                        |  |

| G1       | so                               | 0              | <b>Serial Interface Output (LVCMOS).</b> Serial interface data output. When i2c_en 0, this pin acts as the so pin for the serial interface. When i2c_en = 1, this pin i unused and should be left unconnected.                                                                                                                                                                                     |  |

| E3       | cs_b_asel0                       | I <sub>u</sub> | Chip Select/Address Select 0 for the Serial Interface (LVCMOS). Serial interface chip select. When i2c_en = 0, this pin acts as the cs pin (active low) for the serial interface. When i2c_en = 1, this pin acts as the asel0 pin for the I <sup>2</sup> C interface.                                                                                                                              |  |

| Pin#                 | Name          | I/O<br>Type    | Description                                                                                                                                                                                                                                                                                                                             |  |  |  |

|----------------------|---------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| G2                   | int_b         | 0              | Interrupt Pin (LVCMOS). Indicates a change of device status prompting the processor to read the enabled interrupt service registers (ISR). This pin is an open drain, active low and requires an external pulled up to VDD.                                                                                                             |  |  |  |

| J2                   | i2c_en        | l <sub>u</sub> | $I^2C$ Interface Enable (LVCMOS). If set high, the $I^2C$ interface is enabled, if set low, the SPI interface is enabled. Internally pull-up to Vdd.                                                                                                                                                                                    |  |  |  |

| APLL                 | Loop Filter   |                |                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| A6                   | apll_filter   | А              | External Analog PLL Loop Filter terminal.                                                                                                                                                                                                                                                                                               |  |  |  |

| В6                   | filter_ref0   | Α              | Analog PLL External Loop Filter Reference.                                                                                                                                                                                                                                                                                              |  |  |  |

| C6                   | filter_ref1   | Α              | Analog PLL External Loop Filter Reference.                                                                                                                                                                                                                                                                                              |  |  |  |

| JTAG                 | and Test      |                |                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| J4                   | tdo           | 0              | <b>Test Serial Data Out (Output).</b> JTAG serial data is output on this pin on the falling edge of tck. This pin is held in high impedance state when JTAG scan is not enabled.                                                                                                                                                        |  |  |  |

| K2                   | tdi           | l <sub>u</sub> | <b>Test Serial Data In (Input).</b> JTAG serial test instructions and data are shifted in on this pin. This pin is internally pulled up to Vdd. If this pin is not used then it should be left unconnected.                                                                                                                             |  |  |  |

| H4                   | trst_b        | I <sub>u</sub> | <b>Test Reset (LVCMOS).</b> Asynchronously initializes the JTAG TAP controller by putting it in the Test-Logic-Reset state. This pin should be pulsed low on power-up to ensure that the device is in the normal functional state. This pin is internally pulled up to Vdd. If this pin is not used then it should be connected to GND. |  |  |  |

| K3                   | tck           | I              | <b>Test Clock (LVCMOS):</b> Provides the clock to the JTAG test logic. If this pin is not used then it should be pulled down to GND.                                                                                                                                                                                                    |  |  |  |

| J3                   | tms           | I <sub>u</sub> | <b>Test Mode Select (LVCMOS).</b> JTAG signal that controls the state transitions of the TAP controller. This pin is internally pulled up to $V_{DD}$ . If this pin is not used then it should be left unconnected.                                                                                                                     |  |  |  |

| Maste                | r Clock       |                |                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| K4                   | osci          | I              | Oscillator Master Clock Input (LVCMOS). This input accepts a 20 MHz reference from a clock oscillator (TCXO, OCXO). The stability and accuracy of the clock at this input determines the free-run accuracy and the long term holdover stability of the output clocks.                                                                   |  |  |  |

| K5                   | osco          | 0              | Oscillator Master Clock Output (LVCMOS). This pin must be left unconnected when the osci pin is connected to a clock oscillator.                                                                                                                                                                                                        |  |  |  |

| Miscel               | Miscellaneous |                |                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| J6                   | IC            |                | Internal Connection. Connect to ground.                                                                                                                                                                                                                                                                                                 |  |  |  |

| K6                   | IC            |                | Internal Connection. Leave unconnected.                                                                                                                                                                                                                                                                                                 |  |  |  |

| F2<br>F3<br>G3<br>H7 | NC            |                | No Connection. Leave unconnected.                                                                                                                                                                                                                                                                                                       |  |  |  |

| Pin #                                                                                        | Name               | I/O<br>Type                   | Description                                                  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------|--------------------|-------------------------------|--------------------------------------------------------------|--|--|--|--|--|

| Power                                                                                        | Power and Ground   |                               |                                                              |  |  |  |  |  |

| D9<br>E4<br>G8<br>G9<br>J8<br>J9<br>H6<br>H8                                                 | V <sub>DD</sub>    | P P P P P P                   | Positive Supply Voltage. +3.3V <sub>DC</sub> nominal.        |  |  |  |  |  |

| E8<br>F4                                                                                     | V <sub>CORE</sub>  | P<br>P                        | Positive Supply Voltage. +1.8V <sub>DC</sub> nominal.        |  |  |  |  |  |

| A5<br>A8<br>C10                                                                              | AV <sub>DD</sub>   | P<br>P<br>P                   | Positive Analog Supply Voltage. +3.3V <sub>DC</sub> nominal. |  |  |  |  |  |

| B7<br>B8<br>H2                                                                               | AV <sub>CORE</sub> | P<br>P<br>P                   | Positive Analog Supply Voltage. +1.8V <sub>DC</sub> nominal. |  |  |  |  |  |

| D4<br>D5<br>D6<br>D7<br>E5<br>E6<br>E7<br>F5<br>F6<br>F7<br>G4<br>G5<br>G6<br>G7<br>E9<br>F8 | V <sub>SS</sub>    | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | Ground. 0 Volts.                                             |  |  |  |  |  |

| A7<br>C7<br>C8<br>C9<br>D8<br>H3                                                             | AV <sub>SS</sub>   | G<br>G<br>G<br>G              | Analog Ground. 0 Volts.                                      |  |  |  |  |  |

d - Input, Internally pulled down

${\rm I_u}$  - Input, Internally pulled up

O - Output

A - Analog

P - Power

G - Ground

I - Inpi

## 1.0 Pin Diagram

**TOP VIEW**

| 1 | 1          | 2                  | 3                   | 4                  | 5                     | 6                  | 7                     | 8                           | 9                   | 10                          |

|---|------------|--------------------|---------------------|--------------------|-----------------------|--------------------|-----------------------|-----------------------------|---------------------|-----------------------------|

| Α | Sync1      | Sync2              | ref2                | ref7               | O<br>AV <sub>DD</sub> | apll_filter        | O<br>AV <sub>SS</sub> | $\bigcirc$ AV <sub>DD</sub> | diff0_p             | diff1_p                     |

| В | sync0      | ref1               | ref4                | ref5               | sync8/<br>ext_fb_fp   | filter_ref0        | AV <sub>CORE</sub>    | AV <sub>CORE</sub>          | Odiff1_n            | diff0_n                     |

| С | ref0       | dpll1_mod_<br>sel0 | ref3                | ref6               | ref8/<br>ext_fb_clk   | filter_ref1        | $\bigcup_{AV_{SS}}$   | $\bigcap_{AV_{SS}}$         | $\bigcup_{AV_{SS}}$ | $\bigcirc$ AV <sub>DD</sub> |

| D | Slave_en   | dpll1_mod_<br>sel1 | diff1_en            | $\bigcup_{V_{SS}}$ | $\bigcup_{V_{SS}}$    | $\bigvee_{V_{SS}}$ | $\bigvee_{V_{SS}}$    | $\bigcup_{AV_{SS}}$         | $\bigvee_{V_{DD}}$  | apll_clk0                   |

| E | dpll2_ref  | sck/<br>scl        | cs_b/<br>asel0      | VDD                | $\bigvee_{v_{ss}}$    | $\bigvee_{V_{SS}}$ | $\bigvee_{V_{SS}}$    | V <sub>CORE</sub>           | $\bigvee_{V_{SS}}$  | apll_fp0                    |

| F | si/<br>sdh | NC                 | NC NC               | V <sub>CORE</sub>  | $\bigcup_{V_{SS}}$    | $\bigcup_{V_{SS}}$ | $\bigvee_{V_{SS}}$    | $\bigcup_{V_{SS}}$          | $\bigvee_{V_{SS}}$  | apll_fp1                    |

| G | so         | int_b              | NC NC               | $\bigvee_{V_{SS}}$ | $\bigvee_{V_{SS}}$    | $\bigvee_{V_{SS}}$ | $\bigvee_{V_{SS}}$    | $\bigvee_{V_{DD}}$          | $\bigvee_{V_{DD}}$  | apll_clk1                   |

| Н | dpll1_lock | AV <sub>CORE</sub> | $\bigcup_{AV_{SS}}$ | trst_b             | rst_b                 | $\bigvee_{V_{DD}}$ | NC                    | $\bigvee_{V_{DD}}$          | $\bigvee_{V_{SS}}$  | fb_clk                      |

| J | dpll1_hold | i2c_en             | tms                 | tdo                | dpll1_hs_en           | IC                 | <br>p0_fp1            | $\bigvee_{V_{DD}}$          | $\bigvee_{V_{DD}}$  | p1_clk0                     |

| К | diff0_en   | tdi                | tck                 | osci               | osco                  | IC                 | D0_clk1               | <br>p0_fp0                  | p0_clk0             | p1_clk1                     |

$\wedge$

- A1 corner is identified with a dot.

#### 2.0 Overview

The ZL30143 System Synchronizer and SETS device is a highly integrated device that provides all of the functionality that is required for a central timing card in carrier grade network equipment. The basic functions of a central timing card include:

- Input reference monitoring for both frequency accuracy and phase irregularities

- · Automatic input reference selection

- Support of both external timing and line timing modes

- · Hitless reference switching

- · Wander and jitter filtering

- · Master/slave crossover for minimizing phase alignment between redundant timing cards

- · Independent derived output timing path for support of the SETS functionality

In a typical application, the main timing path uses DPLL1 to synchronize to either an external BITS source or to a recovered line timed source. DPLL1 monitors all references and automatically selects the best available reference based on configurable priority and revertive properties. DPLL1 provides the wander filtering function and the P0 synthesizer generates a jitter filtered clock and frame pulse for the system timing bus which supplies all line cards with a common timing reference. The APLL is used to generate a reference clock for an Ethernet PHY which can be used to synchronize remote equipment. A derived output timing path using DPLL2 is available to support the SETS function. In this case DPLL2 uses a filter above 10 Hz to prevent it from filtering wander.

Figure 2 - Typical Application of the ZL30143

Alternatively, the ZL30143 could be used in systems that were not designed with central timing cards in mind. In this case, the ZL30143 provides all of the features required to meet both the timing card and the line card functions in one package. This application is shown in Figure 3. DPLL1 recovers the reference clock from the backplane and filters wander. The APLL and the P0 synthesizer filter jitter and generate transmit clocks for a SONET/SDH/10GbE PHY (up to OC-48/STM-16) and/or a PDH PHY (T1/E1, DS3/E3, etc). DPLL2 is used to recover the line timing reference, filter jitter, and translate its frequency to the rate required by the backplane.

Figure 3 - The ZL30143 as a Timing Card and a Line Card Device

#### 2.1 DPLL Features

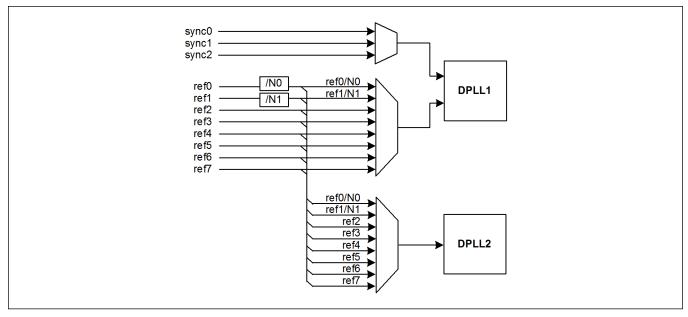

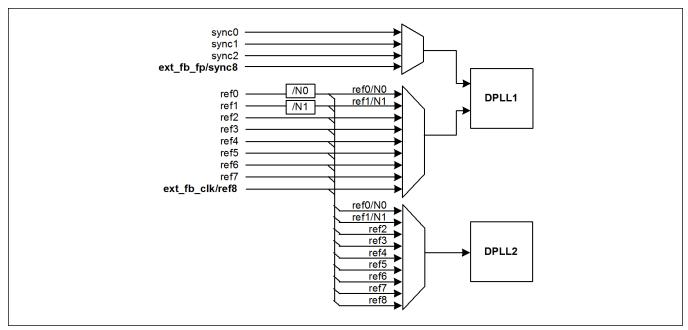

The ZL30143 provides two independently controlled Digital Phase-Locked Loops (DPLL1, DPLL2) for clock and/or frame pulse synchronization. Table 1 shows a feature summary for both DPLLs.

| Feature                                                                                 | DPLL1                                                                                                                                                 | DPLL2                                                                                                               |  |

|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|

| Modes of Operation                                                                      | Free-run, Normal (locked), Holdover,<br>ToP (Timing over Packet) Client Mode                                                                          | Free-run, Normal (locked), Holdover                                                                                 |  |

| Loop Bandwidth (BW)                                                                     | User selectable: 0.1 Hz, 1.7 Hz, 3.5 Hz, fast lock (7 Hz), 14 Hz, 28 Hz <sup>1</sup> , or wideband <sup>2</sup> (890 Hz / 56 Hz / 14 Hz)              | Fixed: 14 Hz                                                                                                        |  |

| Lock Time                                                                               | < 60 s for 0.1 Hz, 1.7 Hz, 3.5 Hz BW <10 s for all other BW (PSL = 885 ns/s) < 1 s for all other BW (PSL = 7.5 $\mu$ s/s, 61 $\mu$ s/s, or unlimited) | < 1 s (fixed 14 Hz BW)                                                                                              |  |

| Phase Slope Limiting User selectable: 885 ns/s, 7.5 μs/s, 61 μs/s, or unlimited         |                                                                                                                                                       | User selectable: 61 μs/s, or unlimited                                                                              |  |

| Pull-in Range                                                                           | User selectable: 12 ppm, 52 ppm, 83 ppm, 130 ppm                                                                                                      | Fixed: 130 ppm                                                                                                      |  |

| Holdover Parameters                                                                     | Selectable Update Times: 26 ms, 1 s, 10 s, 60 s, and Selectable Holdover Post Filter BW: 18 mHz, 0.6 Hz, 10 Hz.                                       | Fixed Update Time: 26 ms<br>No Holdover Post Filtering                                                              |  |

| Holdover Frequency<br>Accuracy                                                          | Better than 1 ppb (Stratum 3E) initial frequency offset. Frequency drift depends on the 20 MHz external oscillator (OCXO or TCXO).                    | Better than 50 ppb (Stratum 3) initial frequency offset. Frequency drift depends on the 20 MHz external oscillator. |  |

| Reference Inputs                                                                        | Ref0 to Ref8                                                                                                                                          | Ref0 to Ref8                                                                                                        |  |

| Sync Inputs                                                                             | Sync0, Sync1, Sync2, Sync8                                                                                                                            | Sync inputs are not supported.                                                                                      |  |

| Input Reference Automatic (based on programmable priority and revertiveness), or manual |                                                                                                                                                       | Automatic (based on programmable priority and revertiveness), or manual                                             |  |

| Hitless Ref Switching                                                                   | Can be enabled or disabled                                                                                                                            | Can be enabled or disabled                                                                                          |  |

| External Status Pin Indicators                                                          | Lock, Holdover                                                                                                                                        | None                                                                                                                |  |

Table 1 - DPLL1 and DPLL2 Features

<sup>1.</sup> Limited to 14 Hz for 2 kHz references)

<sup>2.</sup> In the wideband mode, the loop bandwidth depends on the frequency of the reference input. For reference frequencies greater than

<sup>8</sup> kHz, the loop bandwidth = 890 Hz. For reference frequencies equal to 8 kHz, the loop bandwidth = 56 Hz. The loop bandwidth is equal to 14 Hz for reference frequencies of 2 kHz.

#### 2.2 DPLL Mode Control

Both DPLL1 and DPLL2 independently support three modes of operation - free-run, normal, and holdover. The mode of operation can be manually set or controlled by an automatic state machine as shown in Figure 4.

Figure 4 - Automatic Mode State Machine

#### Free-run

The free-run mode occurs immediately after a reset cycle or when the DPLL has never been synchronized to a reference input. In this mode, the frequency accuracy of the output clocks is equal to the frequency accuracy of the external master oscillator.

#### **Lock Acquisition**

The input references are continuously monitored for frequency accuracy and phase regularity. If at least one of the input references is qualified by the reference monitors, then the DPLL will begin lock acquisition on that input. Given a stable reference input, the ZL30143 will enter in the Normal (locked) mode.

#### Normal (locked)

The usual mode of operation for the DPLL is the normal mode where the DPLL phase locks to a selected qualified reference input and generates output clocks and frame pulses with a frequency accuracy equal to the frequency accuracy of the reference input. While in the normal mode, the DPLL's clock and frame pulse outputs comply with the MTIE and TDEV wander generation specifications as described in Telcordia and ITU-T telecommunication standards.

#### Holdover

When the DPLL operating in the normal mode loses its reference input, and no other qualified references are available, it will enter the holdover mode and continue to generate output clocks based on historical frequency data collected while the DPLL was synchronized. The transition between normal and holdover modes is controlled by the DPLL so that its initial frequency offset is better than 1 ppb which meets the requirement of Stratum 3E. The frequency drift after this transition period is dependant on the frequency drift of the external master oscillator.

#### 2.2.1 DPLL1 Mode Of Operation

During reset, the level on the **dpll1\_mod\_sel1:0** pins determine the default start-up mode of operation for DPLL1. Table 2 shows the settings for these pins. When left unconnected, the default mode of operation will be set to automatic normal mode. The selected value is reflected in the *dpll1\_modesel* register (0x1F).

After reset, the mode of operation can be controlled by software using the *dpll1\_modesel* register (0x1F), or it can be controlled using the **dpll1\_mod\_sel1:0** pins by setting the *dpll1\_mode\_hsw* bit of the *use\_hw\_ctrl* register (0x01) to 1.

| dpll1_mode_sel1:0 |   |                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|-------------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1                 | 0 | Function                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 0                 | 0 | Set the default mode of operation to <b>Manual Normal Mode</b> . In this mode, automatic reference switching is disabled and the selected reference is determined by the dpll1_refsel register (0x20). If the selected reference fails, the device automatically enters the holdover mode.                                                                                                                                             |  |  |

| 0                 | 1 | Set the default state of operation to <b>Manual Holdover Mode</b> . In this mode, automatic reference switching is disabled and DPLL1 stays in the holdover mode.                                                                                                                                                                                                                                                                      |  |  |

| 1                 | 0 | Set the default state to <b>Manual Freerun Mode</b> . In this mode, automatic reference switching is disabled and DPLL1 stays in the free-run mode.                                                                                                                                                                                                                                                                                    |  |  |

| 1                 | 1 | Set the default state to <b>Automatic Normal Mode</b> . In this mode, automatic reference switching is enabled so that DPLL1 automatically selects the highest priority qualified reference. If that reference fails, an automatic reference switchover to the next highest priority and qualified reference is initiated. If there are no suitable references for selection, DPLL1 will stay in free-run or enter the holdover state. |  |  |

Table 2 - DPLL1 Default Mode Selection

#### 2.2.1.1 ToP (Timing over Packet) Client Mode

In software control mode the ZL30143 can also be set in Timing over Packet (ToP) Client Mode using the dpll1\_modesel register (0x1F).

ToP Client mode allows external software to control DCO frequency offset of DPLL1 using the 28 bit 2's complement value in the DCO\_freq\_offset registers (page 1, addresses 0x65 to 0x68). The offset is programmed in steps according to the following equation.

LSB =  $2^{-40}$  \* (80MHz/65,536MHz) \* $10^{9}$ ppb

In ToP client mode, the zl30143 also samples the DCO Phase Word and Local System time to be read by the ToP clock recovery algorithm software.

The 64 bit DCO phase Word is available in the DCO\_Phase registers (page 1, address 0x69 to 0x70). The 32 bit Local System Time is available in the Local Time registers (page 1, address 0x71 to 0x74)

For more details contact your local Microsemi FAE.

#### 2.2.2 DPLL2 Mode of Operation

The mode of operation for DPLL2 can only be controlled in software using the *dpll2\_modesel* register (0x2C). By default, its mode of operation is set to Free Run.

#### 2.3 Loop Bandwidth

The loop bandwidth determines the amount of wander and jitter filtering that is provided by the DPLL. The loop bandwidth for DPLL1 is programmable using the *bandwidth* field of the *dpll1\_control\_register\_0* register (0x1D). The bandwidth should be set according to the application. Table 3 gives examples of typical applications and their bandwidth settings. DPLL2's loop bandwidth is not programmable and is fixed at 14 Hz.

| bandwith[3:1] | BW (Hz)   | Application                                               |  |

|---------------|-----------|-----------------------------------------------------------|--|

| 000           | 0.1       | GR-253 SONET Stratum 3, SMC, G.813 option 2, G.8262 EEC 2 |  |

| 001           | 1.7       | GR-1244 Stratum 3, G.813 option 1                         |  |

| 010           | 3.5       | G.813 option 1, G.8262 EEC 1                              |  |

| 101           | 14/56/890 | Wide Band Mode. BW depends on input frequency.            |  |

| 110           | 7         | Fast Lock                                                 |  |

| 111           |           | Reserved                                                  |  |

Table 3 - DPLL1 Loop Bandwidth

#### 2.4 Pull-in/hold-in Range

The **pull-in range** defines the maximum input frequency range that the DPLL can lock to. The pull-in range for DPLL1 is programmable using the *dpll1\_pull\_in\_range* register (0x29). The pull-in range should be set according to the application as shown in Table 4. The **hold-in range**, which defines the range of input frequencies that the PLL will continue to lock to, is equal to the pull-in range. The pull-in/hold-in range for DPLL2 is fixed at +/-130 ppm.

| pull_in_range[1:0] | +/- ppm | Application                                 |  |

|--------------------|---------|---------------------------------------------|--|

| 00                 | 12      | Stratum 3, G.813 option 1, G.8262 EEC 1 & 2 |  |

| 01                 | 52      | SONET Minimum Clock, G.813 option 2         |  |

| 10                 | 130     | ITU-T G.703, ETSI ETS 300 011               |  |

| 11                 | 83      | ANSI T1.403, Stratum 4                      |  |

Table 4 - DPLL1 Pull-in Range

#### 2.5 Phase Slope Limiting

DPLL1 offers a phase slope limit feature which can be used to limit the rate of output phase movement of the output clocks and frame pulses during an input transient. This feature is used for meeting the phase slope requirements of Telcordia and ITU-T standards. The level of phase slope limiting depends on the application. The *dpll1\_ph\_slopelim* field of the *dpll1\_ctrl\_0* register (0x1D) allows four levels of phase slope limiting as shown in Table 5. By default, the phase slope limit is unrestricted. DPLL2 also has a phase slope limiting feature which can be enabled using the *ph\_slopelim* bit of the *dpll2\_ctrl\_0* (0x2A) register. When enabled, a phase slope ANSI T1.403, Stratum 4 limit of 61 μs/s is applied, otherwise it is unrestricted.

| dpll1_ph_slopelim[1:0] | Phase Slope Limiting | Application                   |

|------------------------|----------------------|-------------------------------|

| 00                     | 885 ns/s             | GR-1244 Stratum 3 (objective) |

| 01 7.5 μs/s            |                      | G.813 option 1 and G.8262     |

Table 5 - DPLL Phase Slope Limiting

| dpll1_ph_slopelim[1:0] | Phase Slope Limiting         | Application                    |  |

|------------------------|------------------------------|--------------------------------|--|

| 10                     | 61 μs/s                      | GR-1244 Stratum 3              |  |

| 11                     | Unrestricted (default)       |                                |  |

| dall2 ab alanalim      | <b>5</b> 1 <b>6</b> 1 11 11  |                                |  |

| dpll2_ph_slopelim      | Phase Slope Limiting         | Application                    |  |

| 0                      | Phase Slope Limiting 61 μs/s | Application  GR-1244 Stratum 3 |  |

Table 5 - DPLL Phase Slope Limiting

#### 2.6 Hitless Reference Switching

With hitless reference switching enabled, the phase difference between the originally selected reference and the newly selected reference is absorbed by the DPLL preventing a possible non-compliant phase transient at its output. The  $hs_en$  bit of the  $dpll_n_ctrl_0$  registers (0x1D, 0x2A) allows this feature to be enabled or disabled. When disabled, the DPLL will align its output to the new reference at a rate of alignment which is dependant on the phase slope limit set in the  $dpll_ph_slopelim$  field of the  $dpll_ctrl_0$  register (0x1D).

#### 2.7 Free-run Frequency Offset

When operating in Free Run mode, the accuracy of the output clocks is equal to that of the oscillator connected to the Master Clock Input (OSCi). The ZL30143 allows the user to offset this frequency by +/-149 ppm by using the 28 bit 2's complement value in the DCO\_freq\_offset registers (page 1, addresses 0x65, 0x66, 0x67, and 0x68). The offset is programmed in steps according to the following equation.

LSB =

$$2^{-40}$$

\* (80MHz/65,536MHz) \*10<sup>9</sup>ppb

The offset can be enabled or disabled independently for each of the two DPLLs. To enable the free run frequency offset for DPLL1 set the freq\_offset\_en bit of the dpll1\_ctrl\_1 register (page 0, address 0x1E, bit 1). To enable the free run frequency offset for DPLL2 set the freq\_offset\_en bit of the dpll2\_ctrl\_1 register (page 0, address 0x2B, bit 1).

#### 2.8 Holdover

The DPLLs continuously collect phase data while synchronized to a valid reference. These data samples are accumulated and averaged to determine a stable holdover frequency in the event that all of the valid references are lost. To prevent reference input jitter from corrupting the final holdover value, samples are taken on phase data filtered by the DPLL's loop bandwidth. DPLL1 offers an additional stage of filtering that can be enabled if the DPLL's loop bandwidth does not provide adequate filtering. This allows the DPLL to operate in a wide bandwidth mode and still provide an accurate holdover value. This is useful when the DPLL1 is used in a slave mode. The holdover filter bandwidth is programmable using the hold\_filt\_bw field of the dpll1\_ctrl\_1 register (0x1E).

The holdover performance of the output clocks will depend on two factors. One is the initial offset of the DPLL, and the other is the frequency drift (or stability) of the external oscillator. The initial offset of the DPLL meets both Stratum 3/G.813 opt 1 and Stratum 3E/G.812 type 3 leaving the overall holdover performance dependant on the frequency drift of the external oscillator. An OCXO or TCXO is recommended for Stratum 3/G.813.

#### 2.9 Reference and Sync Inputs

There are eight reference clock inputs (**ref0** to **ref7**) available to both DPLL1 and DPLL2. The selected reference input is used to synchronize the output clocks. Each of the DPLLs have independent reference selectors which can be controlled using a built-in state machine or set in a manual mode.

Figure 5 - Reference and Sync Inputs

Each of the **ref** inputs accept a single-ended LVCMOS clock with a frequency ranging from 2 kHz to 77.76 MHz. Built-in frequency detection circuitry automatically determines the frequency of the reference if its frequency is within the set of pre-defined frequencies as shown in Table 6. Once detected, the resulting frequency of the reference can be read from the ref\_frq\_detected registers (0x10 - 0x13). Two additional custom reference frequencies (Custom A and Custom B) are also programmable using the *custA\_mult* and *custB\_mult* registers (0x67, 0x68, 0x71, 0x72). These custom frequencies are programmable as 8 kHz \* N up to 77.76 MHz (where N = 1 to 9720), or 2 kHz (when N = 0). The *ref\_freq\_mode\_0* register (0x65) are used to configure each of the reference inputs as auto-detect, custom A, or custom B.

| 16.384 MHz |

|------------|

| 19.44 MHz  |

| 38.88 MHz  |

| 77.76 MHz  |

|            |

|            |

|            |

|            |

Table 6 - Set of Pre-Defined Auto-Detect Clock Frequencies

The first two reference inputs (**ref0** and **ref1**) have programmable pre-dividers which allows them to lock to frequencies higher than 77.76 MHz or to non-standard frequencies. By default the pre-dividers divide by 1, but they can be programmed to divide by 1.5, 2, 2.5, 3, 4, 5, 6, 7, and 8 using the *ref0\_div* and *ref1\_div* bits of the *predivider\_control* register (0x7E). For example, an input frequency of 125 MHz can be divided down by 5 using the pre-dividers to create a 25 MHz input reference. The 25 MHz can then be programmed as a custom input frequency. Similarly, a 62.5 MHz input clock can be divided by 2.5 to create 25 MHz. **Note that division by non-integer values (e.g., 1.5, 2.5) is achieved by using both the rising and falling edges of the input reference.**

# This may cause higher jitter levels at the output clocks when the reference input does not have a 50% duty cycle.

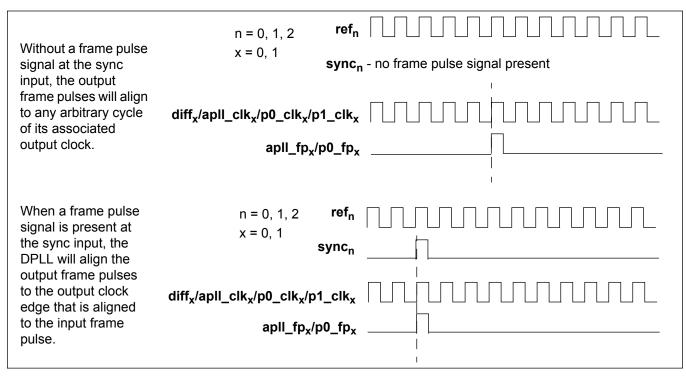

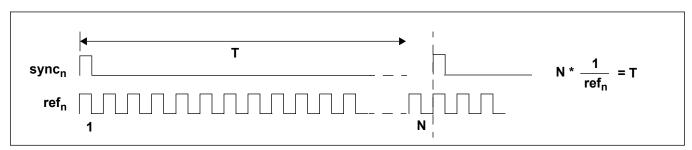

In addition to the reference inputs, DPLL1 has three optional frame pulse synchronization inputs (**sync0** to **sync2**) used to align the output frame pulses. The  $sync_n$  input is selected with its corresponding  $ref_n$  input, where n = 0, 1, 2. Note that the sync input cannot be used to synchronize the DPLL, it only determines the alignment of the frame pulse outputs. An example of output frame pulse alignment is shown in Figure 6.

Figure 6 - Output Frame Pulse Alignment

Each of the **sync** inputs accept a single-ended LVCMOS frame pulse. Since alignment is determined from the rising edge of the frame pulse, there is no duty cycle restriction on this input, but there is a minimum pulse width requirement of 5 ns. Frequency detection for the sync inputs is automatic for the supported frame pulse frequencies shown in Table 7.

| 1 Hz <sup>1</sup>             |

|-------------------------------|

| 166.67 Hz (48x 125 μs frames) |

| 400 Hz                        |

| 1 kHz                         |

| 2 kHz                         |

| 8 kHz                         |

| 64 kHz                        |

<sup>1.</sup> Bit 0 of 1Hz\_Enable Register (08\_0x71) must be set to 1 for 1Hz detection

Table 7 - Set of Pre-Defined Auto-Detect Sync Frequencies

Each of the **sync** inputs can be enabled or disabled using the *sync\_en* bits of the *sync\_enable* register (08\_0x68). By default all sync inputs are enabled so that DPLL1 generates frame aligned frame pulse outputs when a frame pulse is available at the selected sync input. It is also possible to invert the sync inputs using the *sync\_inv* bits of the *sync\_enable* register (08\_0x68).

An additional 9<sup>th</sup> input clock and sync reference (**ref8** and **sync8**) is also available. Refer to the "9th Input Reference (Ref8/Sync8)" section on page 31 for more details.

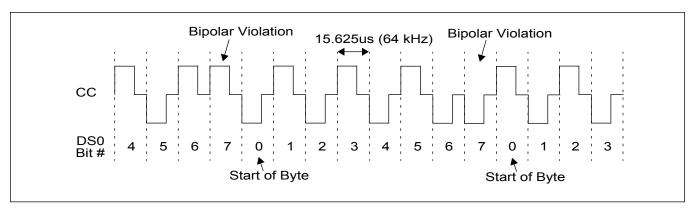

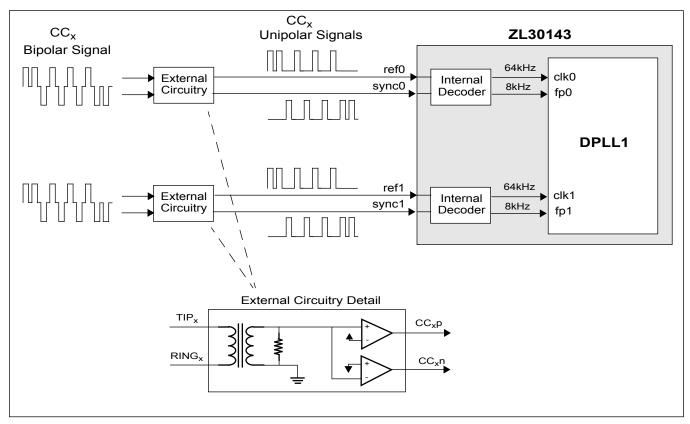

#### 2.9.1 Receiving Composite Clocks