#### ADIN6310 Hardware and TSN Switch Evaluation User Guide

## **FEATURES**

- ▶ 6 port TSN switch with RGMII or SGMII interface

- 6 RGMII ports to 10 Mbps/100 Mbps/1000 Mbps ADIN1300 PHYs

- ▶ RJ45 with integrated magnetics

- ▶ 4 SGMII ports connected to on board SFP cages

- ▶ Host interface hardware strapping with jumpers, choice of

- ▶ S/D/Q SPI interface

- ► Ethernet port through RJ45 (Port 0)

- ▶ FMC (LPC) connector

- ▶ Host port access through S/D/Q SPI interface or Port 0

- ▶ PHY Strapping through surface-mount configuration resistors

- ▶ Default state is software power down from Port 1 to Port 5

- ▶ Switch firmware manages PHY operation over MDIO

- ▶ Operates from a single, external 9 V to 17 V supply

- ▶ LED indicators on GPIO pins

- ▶ IEEE 802.1AS Time Synchronization

- ▶ Scheduled traffic (IEEE 802.1Qbv)

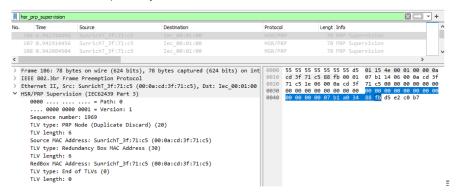

- ► Frame preemption (IEEE 802.1Qbu)

- ► Frame replication and elimination for reliability (IEEE 802.1CB)

- ▶ Per stream filtering and policing (IEEE 802.1Qci)

- ► VLAN table control (remapping, reprioritization)

- IGMP snooping

- ▶ GPIO/Timer control

#### **EVALUATION KIT CONTENTS**

- ▶ EVAL-ADIN6310EBZ evaluation board

- ▶ 9 V or 12 V, 18 W wall adapter with international adapters

- ▶ 1 Ethernet cable

# **EQUIPMENT NEEDED**

- ► EVAL-ADIN6310EBZ evaluation kit

- ▶ Ethernet cables

- ▶ PC running Windows® 10

# **DOCUMENTS NEEDED**

► ADIN6310 data sheet

#### **SOFTWARE NEEDED**

- ▶ TSN application suite (switch configuration GUI and web server)

- Npcap packet capture

# **GENERAL DESCRIPTION**

The EVAL-ADIN6310EBZ is a flexible platform, which enables an efficient evaluation of the ADIN6310 industrial Ethernet Switch with time sensitive networking (TSN) capability. This user guide describes the hardware kit and software evaluation package (**TSN Switch Evaluation** application). It discusses how to use the kit to interface to one or more Switches to configure the Switch, TSN, or redundancy features to meet the requirements of an industrial network.

The **TSN Switch Evaluation** application enables the initial evaluation of the Switch and its functionality, which further enables the users to familiarize themselves with the Switch capability in advance of migrating to the driver library. Simply connect a PC through Ethernet port to Port 0 on the evaluation board and run the application. The **TSN Switch Evaluation** application can identify and allow configuration of a chain of up to 10 ADIN6310 devices. The application launches a PC-based web server and NETCONF server for each Switch device it finds. A user can interact with the web server to configure the Switch functionality or load YANG configurations from a NETCONF client. Once configuration completes, the user applications can communicate with other devices over the TSN network.

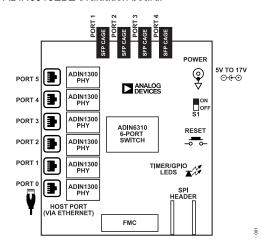

Figure 1 shows an overview of the evaluation board. Full specifications on the ADIN6310 are available in the ADIN6310 data sheet available from Analog Devices, Inc., and must be consulted with this user guide and hardware reference manual when using the EVAL-ADIN6310EBZ evaluation board.

Figure 1. Hardware Overview

# **TABLE OF CONTENTS**

| eatures                                 | 1  | VLAN Reprioritization                  | 38 |

|-----------------------------------------|----|----------------------------------------|----|

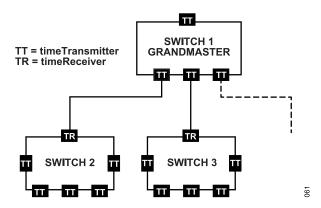

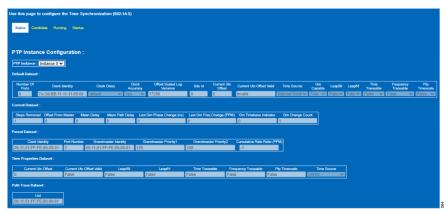

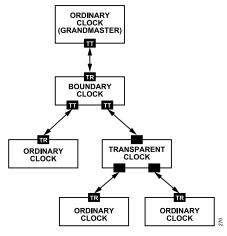

| Evaluation Kit Contents                 | 1  | Time Synchronization IEEE 802.1AS      | 40 |

| Equipment Needed                        | 1  | Candidate Page                         |    |

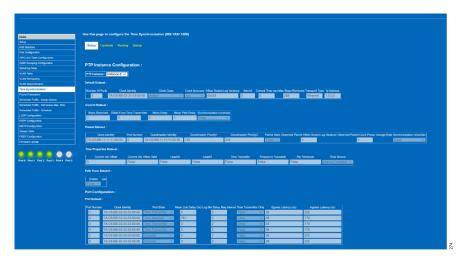

| Documents Needed                        | 1  | PTP Configuration                      | 40 |

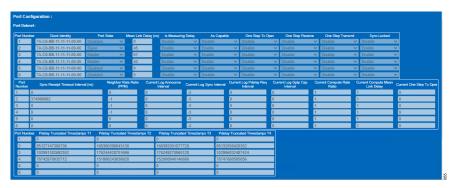

| Software Needed                         | 1  | Port Configuration                     | 41 |

| General Description                     | 1  | Common Services                        | 43 |

| Evaluation Board Hardware               | 5  | PTP Instances                          | 44 |

| Power Supplies                          | 5  | Hardware Clock                         | 46 |

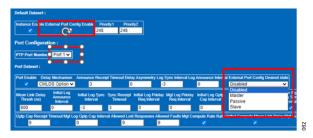

| Power Sequencing                        |    | External Port Config                   | 46 |

| Evaluation Board Use Cases              |    | Status Page                            | 47 |

| Jumper And Switch Options               |    | Time Sync Messaging                    |    |

| GPIO and TIMER Headers                  |    | Running Page                           |    |

| Clock Options                           |    | Startup Page                           |    |

| On-Board LEDs                           |    | Timer Pins, 1PPS Signal                |    |

| Strapping And Configuration             |    | Time Synchronization, IEEE 1588        |    |

| MDIO Interface                          |    | Candidate Page                         |    |

| FMC Connector                           |    | Status Page                            |    |

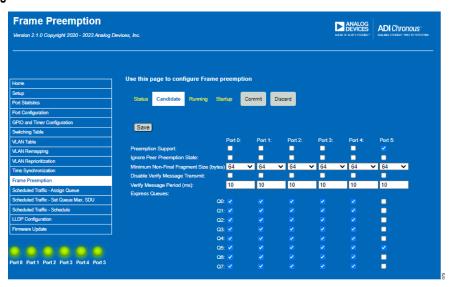

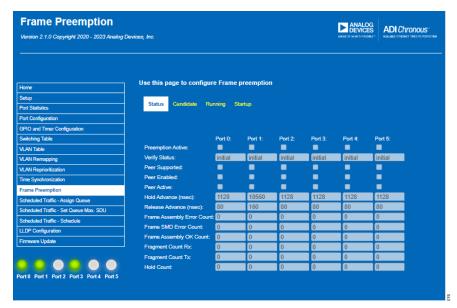

| Software Installation                   |    | Frame Preemption                       |    |

| Installing the TSN Switch Evaluation    |    | Candidate Page                         |    |

| Application Software                    | g  | Status Page                            |    |

| Npcap Installation                      |    | Frame Preemption Example               |    |

| TSN Switch Evaluation Contents Overview |    | Scheduled Traffic                      |    |

| Initial Evaluation Board Setup          |    | Assigning Queues                       |    |

| Software Execution                      |    | Scheduled Traffic – Set Queue Max. SDU |    |

| rsn Switch Evaluation Web Page Overview |    | Scheduled Traffic – Schedule           |    |

| Candidate/Running/Startup Pages         |    | Schedule Enabled                       |    |

| Setup Page                              |    | Guard Bands                            |    |

| Save and Load Candidate Datastore       |    | Cycle Time                             |    |

| Datastore Management                    |    | Base Time                              |    |

| Advanced                                |    | Cycle Time Extension                   |    |

| Performing a Reset                      |    | Gate States When Disabled              |    |

| Port Statistics                         |    | Cut-Through Allowed                    |    |

|                                         |    | Gate Control List, Time Intervals      |    |

| Port Configuration                      |    |                                        |    |

| Candidate Page                          |    | Hold En                                |    |

| Status Page                             |    | Candidate Page                         |    |

| MDIO Control                            |    | Running Page                           |    |

| GPIO and Timer Configuration            |    | Startup Page                           |    |

| TSN Output Timer                        |    | Schedule on the Timer Pins             |    |

| 1PPS Periodic Output                    |    | LLDP Configuration                     |    |

| Periodic Output                         |    | Link Layer Discovery Protocol (LLDP)   |    |

| Capture Input                           |    | LLDP Candidate View                    |    |

| Other Modes                             |    | LLDP Status                            |    |

| Switching Table                         |    | LLDP Example                           |    |

| Candidate View                          |    | LLDP Example (Fast Tx)                 |    |

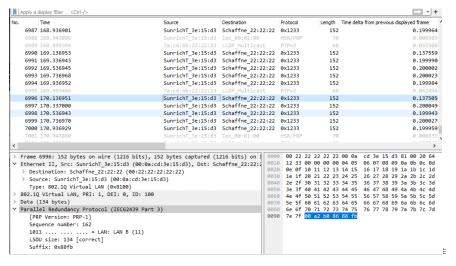

| Status View – Dynamic Entries           |    | Parallel Redundancy Protocol (PRP)     |    |

| Stream Table                            |    | Enabling PRP Example                   |    |

| /LAN Control                            |    | PRP Configuration Web Page Views       |    |

| VLAN Table                              |    | PRP Status Page                        |    |

| VLAN Remapping                          | 36 | PRP - Supervision Frames               | 81 |

# **TABLE OF CONTENTS**

| PRP – Capture of PRP Tagged Traπic          |            | Sequence Recovery                        |     |

|---------------------------------------------|------------|------------------------------------------|-----|

| GPIO/Timer Configuration Tab When Usir      |            | Individual Recovery                      |     |

| PRP Mode                                    |            | FRER Stream Table                        |     |

| VLAN Table Operation in PRP Mode            |            | FRER Configuration–Candidate View        |     |

| Switching Table in PRP Mode                 |            | FRER Status                              | 114 |

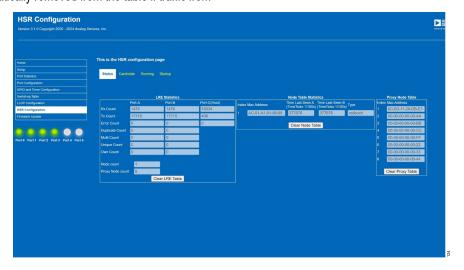

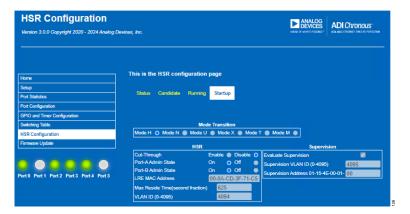

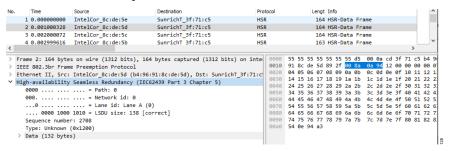

| High Availability Seamless Redundancy (HS   |            | Talker–Listener Configuration Example    |     |

| HSR Operating Modes                         | 84         | Talker System                            |     |

| Enabling HSR Example                        |            | Listener System                          |     |

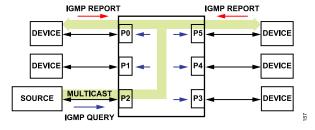

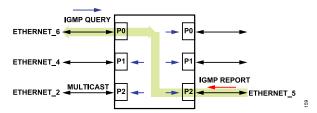

| HSR Candidate View                          | 85         | Internet Group Management Protocol (IGMP | ')  |

| HSR Status View                             | 87         | Snooping                                 |     |

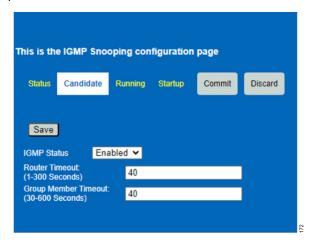

| HSR Running View                            |            | Router Timeout                           | 119 |

| HSR Startup View                            | 89         | Group Member Timeout                     | 120 |

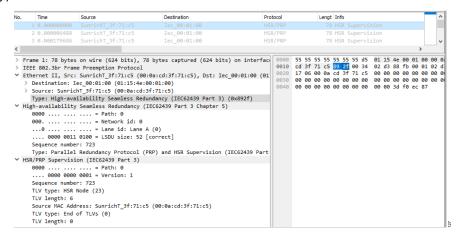

| HSR – Supervision Frames                    | 90         | IGMP Versions                            | 121 |

| HSR – Capture of HSR Tagged Traffic         | 91         | IGMP Snooping Example                    | 121 |

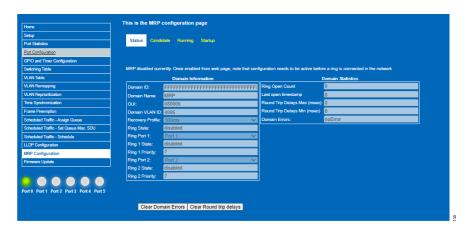

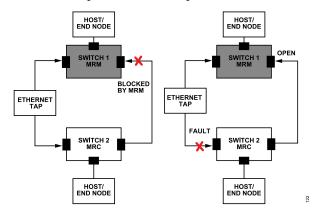

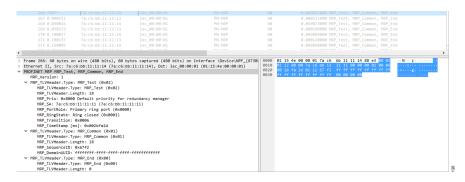

| Media Redundancy Protocol (MRP)             | 92         | NETCONF/YANG                             | 125 |

| MRP Stack on the Switch                     | 92         | Sysrepo Datastore                        | 125 |

| Recovery Profiles                           | 92         | YANG Models                              | 125 |

| Configuring MRP                             | 92         | Custom Leaf Nodes                        | 125 |

| Candidate Page                              | 92         | Startup Configuration                    | 125 |

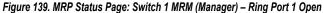

| MRP Scenarios: MRM and MRC                  | 94         | Web Server Use and NETCONF               |     |

| MRP Scenarios: MRA                          | 96         | YANG Model Examples                      |     |

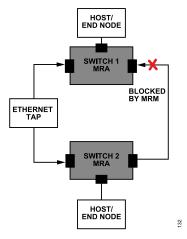

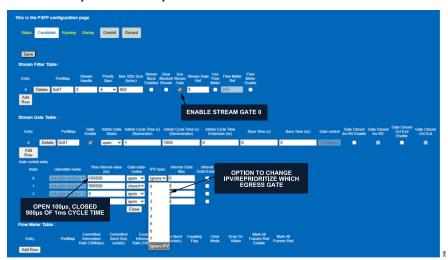

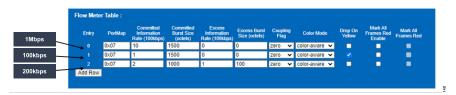

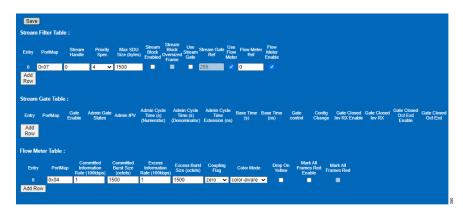

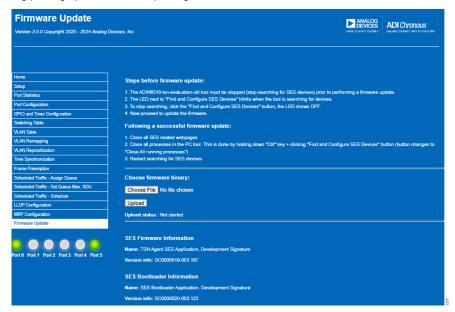

| Per-Stream Filtering And Policing, Qci      | 98         | Firmware Update                          |     |

| PSFP Candidate Page                         |            | Automatic Firmware Update                |     |

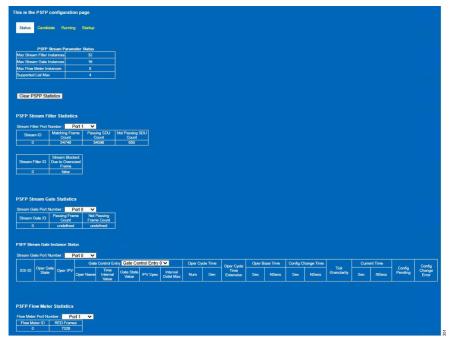

| PSFP Status Page                            |            | Paired Firmware and Web Server           | 128 |

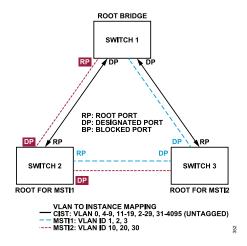

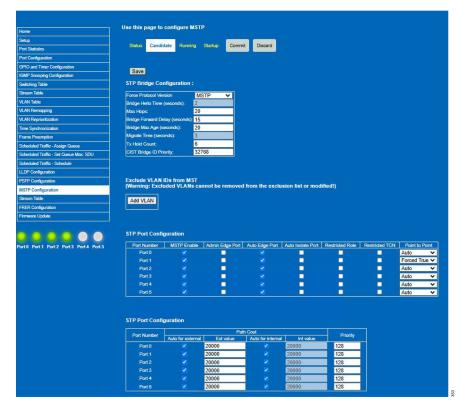

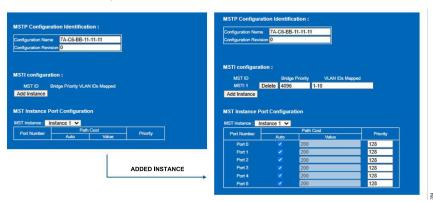

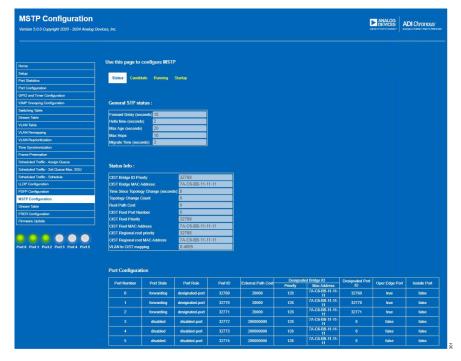

| Multiple Spanning Tree Protocol (MSTP)      |            | Firmware Downgrade                       |     |

| MSTP Candidate Page                         |            | Troubleshooting                          |     |

| MSTP Status Page                            |            | GUI Does Not Find ADIN6310 Devices       |     |

| Frame Replication and Elimination for       |            | GUI Table Remains Blank                  | 130 |

| Reliability (FRER), 802.1CB                 | 108        | Web Page Fails to Load                   | 130 |

| Redundancy Tag                              |            | Firmware Did Not Update                  |     |

| Stream Identification                       |            | GUI Inconsistent at Finding Devices      |     |

| REVISION HISTORY                            |            |                                          |     |

| 2/2025—Rev. 0 to Rev. A                     |            |                                          |     |

|                                             |            |                                          |     |

| Changes to Figure 17 to Figure 20           |            |                                          | 14  |

| Changes to MRP Specific Configuration Sec   | ction      |                                          | 15  |

| Changed ADIN6310 and 10BASET1L Hardy        | ware Secti | ion to EVAL-ADIN6310T1L Hardware Section | 16  |

|                                             |            |                                          |     |

|                                             |            |                                          |     |

| Change to Initial Evaluation Board Setup Se | ection     |                                          | 16  |

|                                             |            |                                          |     |

| Changes to Figure 24                        |            |                                          | 18  |

|                                             |            |                                          |     |

|                                             |            | ew Section                               |     |

| Changes to Figure 26                        |            |                                          | 19  |

| Changes to Port Statistics Section and Figu | re 29      |                                          | 23  |

| Changes to Candidate Page Section           |            |                                          | 24  |

|                                             |            |                                          |     |

# **TABLE OF CONTENTS**

| Changes to Candidate View Section                                                           | 29  |

|---------------------------------------------------------------------------------------------|-----|

| Changes to Dynamic Table Section                                                            | 29  |

| Added Stream Table Section and Figure 41                                                    | 33  |

| Changed Time Synchronization Section to Time Synchronization IEEE 802.1AS                   | 40  |

| Changes to Time Synchronization IEEE 802.1AS                                                |     |

| Changes to PTP Configuration Section and Figure 52                                          |     |

| Change to Table 11                                                                          |     |

| Changes to Hardware Clock Section                                                           |     |

| Added Time Synchronization, IEEE 1588 Section and Figure 70                                 |     |

| Added Candidate Page Section, Figure 71 to Figure 73, and Table 13 and Table 14; Renumbered |     |

| Sequentially                                                                                |     |

| Added Status Page Section and Figure 74                                                     | 54  |

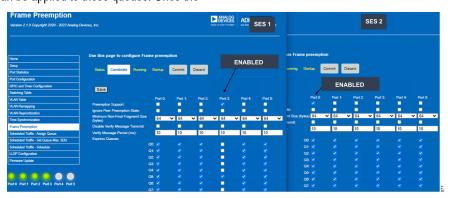

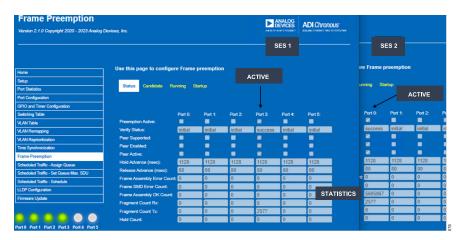

| Changes to Frame Preemption Section                                                         |     |

| Changes to Scheduled Traffic Section                                                        |     |

| Changes to MRP Stack on the Switch Section                                                  |     |

| Changes to Configuring MRP Section                                                          |     |

| Changes to Figure 145                                                                       | 98  |

| Changes to Stream Filter Section and Figure 146                                             | 99  |

| Changes to Stream Gate Section and Figure 148                                               |     |

| Changes to PSFP Status Page Section                                                         | 102 |

| Deleted Figure 144                                                                          | 102 |

| Changes to Figure 151                                                                       | 102 |

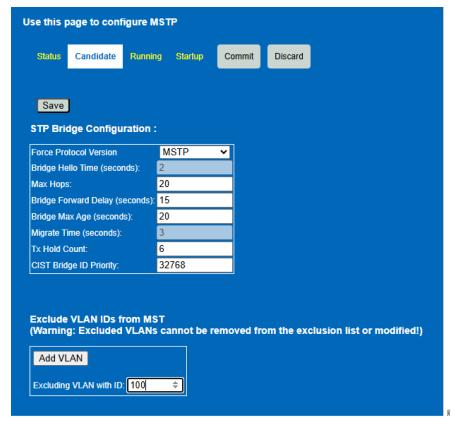

| Added Multiple Spanning Tree Protocol (MSTP) Section and Figure 152                         | 103 |

| Added MSTP Candidate Page Section, Figure 153, and Figure 154                               | 103 |

| Added MSTP Status Page Section and Figure 155                                               |     |

| Changes to Frame Replication and Elimination for Reliability (FRER), 802.1CB Section        | 108 |

| Added Figure 157                                                                            | 108 |

| Changed Stream Table Section to FRER Stream Table Section                                   | 111 |

| Changes to FRER Stream Table Section                                                        | 111 |

| Changes to Stream Table Configuration Section                                               | 111 |

| Changes to Figure 160 Caption                                                               | 112 |

| Changes to FRER Configuration—Candidate View Section                                        | 112 |

| Changes to Talker-Listener Configuration Example Section                                    |     |

| Changes to Talker System Section and Figure 164                                             |     |

| Replaced Figure 165                                                                         |     |

| Changes to GUI Does Not Find ADIN6310 Devices Section                                       |     |

| Added Figure 185                                                                            | 130 |

# 10/2024—Revision 0: Initial Version

analog.com Rev. A | 4 of 131

#### **POWER SUPPLIES**

The EVAL-ADIN6310EBZ operates from a single, external, 5 V to 17 V supply rail. A 9 V or 12 V wall adapter is supplied as part of the kit.

Apply the wall adapter to P2 connector or alternatively 5 V to 17 V to the P1 plug. Switch BRD\_ON\_OFF to the ON position. The LED DS4 lights up to indicate a successful power up of the main power rails.

The EVAL-ADIN6310EBZ power requirements are generated from the input power rail by an on-board LTM4668A µModule regulator, which provides the four rails required for operation of the ADIN6310 Switch, the six ADIN1300 Ethernet PHYs and other support circuitry. The default nominal voltages are listed in Table 1.

By default, the VDDIO\_A and VDDIO\_B share the same voltage rail and default to 1.8 V with the installed components and jumper settings.

Table 1. Default Device Power Supply Configuration

| LTM4668A          | Nominal |                  |                  |

|-------------------|---------|------------------|------------------|

| Output            | Voltage | ADIN6310 Switch  | ADIN1300 PHY     |

| V <sub>OUT1</sub> | 3.3 V   | VDD3P3           | AVDD3P3          |

| $V_{OUT2}$        | 1.8 V   | VDDIO_A/B        | VDDIO            |

| $V_{OUT3}$        | 1.1 V   | VDDCORE          | N/A <sup>1</sup> |

| $V_{\text{OUT4}}$ | 0.9 V   | N/A <sup>1</sup> | VDD0P9           |

<sup>&</sup>lt;sup>1</sup> N/A means not applicable.

The VDDIO\_A rail provides a separate voltage domain for the Switch interface pins that can connect to a Host interface. This includes SPI interface, TIMER, GPIO, and Port 0 MAC interface pins. The motivation for partitioning the VDDIO\_A/B voltage rails is to ensure flexible Host interface I/O voltage while helping to reduce overall power consumption for the Switch ports and PHY devices. For normal operation of the evaluation hardware, the default voltage rail should be sufficient. If user is connecting own Host interface over SPI or FMC connector, flexibility to change the VDDIO\_A rail may be beneficial.

If a different VDDIO\_A voltage is required, user can adjust by changing the placement of configuration jumpers. The VDDIO\_A rail can be changed from 1.8 V default to either 2.5 V or 3.3 V. To change the VDDIO\_A rail to 2.5 V, the LDO, U3 must be used. The jumpers to reconfigure this are P3, P4, P5, and P33.

For more details, see Table 2 and the evaluation board schematics.

Table 2. VDDIO\_A Configuration

| _       | -                                  |

|---------|------------------------------------|

| VDDIO_A | Jumper Setting                     |

| 1.8 V   | P3 (1-2), P4 (1-2), P33 (OPEN)     |

| 2.5 V   | P3 (OPEN), P4 (2-3), P33 (1-2)     |

| 3.3 V   | P3 (1-2), P4 (2)-P5(1), P33 (OPEN) |

Table 3 shows an overview of the EVAL-ADIN6310EBZ current for various operating modes.

Table 3. Board Quiescent Current (P2 = 9 V)

| Board Status                              | Typical Quiescent Current |  |

|-------------------------------------------|---------------------------|--|

| On Power-Up (S1 on)                       | 104 mA initially          |  |

| In Hardware Power-Down (RESET_N Held Low) | 72 mA                     |  |

| 1000BASE-T, 2 RGMII + HOST Port           | 250 mA                    |  |

| 1000BASE-T, 5 RGMII + HOST Port           | 360 mA                    |  |

## **POWER SEQUENCING**

The ADIN6310 device does not have any power supply sequencing requirements, however the preferred power up sequence is to bring up VDDCORE last and removed first on power down. There are no power sequence requirements for the ADIN1300 devices. The evaluation board is configured to bring up the power rails in the following order VDD3P3 and VDD0P9 -> VDDIO A/B -> VDDCORE.

# **EVALUATION BOARD USE CASES**

The EVAL-ADIN6310EBZ can be used in two general modes. The default and expected use case utilize Port 0 as the Host interface port through the RJ45 connector. Port 0 is connected to a PC running the TSN evaluation software package for network configuration and control. Port 0 can still be used for data traffic, but it is not a part of the time aware network as it is connected to the PC. In this use case, the other five RGMII ports and four SGMII ports on the EVAL-ADIN6310EBZ can be used to evaluate IEEE802.3 and TSN features of the ADIN6310, establish links with other link partners and evaluate the performance of the chip.

Alternatively, the user can connect their own Host directly to the EVAL-ADIN6310EBZ. If Host interface is SPI, then option to connect directly through the SPI header or the FMC LPC connector (FPGA mezzanine card low pin count). The FMC connector can be plugged into an FPGA development board. When the Switch hardware is used with an FPGA board, the media independent interfaces (MIIs) for Port 0, SPI interface, GPIO, and TIMER signals can be connected to the FPGA. In this use case, a MAC-MAC type Host interface can be used on Port 0 or the SPI (quad, dual, or single) interface can be used for control and configuration with the FGPA as the Host processor for evaluation of the ADIN6310 in a full system. With the SPI interface as the HOST interface, the system can have six TSN capable ports.

# **JUMPER AND SWITCH OPTIONS**

Several jumpers on the EVAL-ADIN6310EBZ must be set for the required operating setup before using the EVAL-ADIN6310EBZ for evaluation. The default settings and functions of these jumper options are described in Table 4.

Table 4. Default Jumper, Switch Options and Descriptions

| Link       | Position | Function            |

|------------|----------|---------------------|

| BRD_ON_OFF | OFF      | Power ON/OFF Switch |

| S1         | 3        | Reset options       |

| P3         | Inserted |                     |

analog.com Rev. A | 5 of 131

Table 4. Default Jumper, Switch Options and Descriptions (Continued)

| Link                              | Position     | Function                                                    |

|-----------------------------------|--------------|-------------------------------------------------------------|

| P4                                | 1-2 Inserted | VDDIO_A = VDDIO_B = 1.8 V; runs off the Switching regulator |

| P33                               | Open         | Enable for VDDIO_A LDO                                      |

| TIMER2                            | Open         | Host strapping (RGMII No Tx Rx Delay)                       |

| SPI_SS, TIMER0,<br>TIMER1, TIMER3 | 1-2 Inserted | Host strapping (RGMII No Tx Rx Delay 1000 Mbps)             |

| P28                               | 1-2 Inserted | Power to TIMER/GPIO LEDs                                    |

| P41                               | 1-2 Inserted | Connect VCCIO supply of FTDI to VDDIO_A                     |

| P11, P13, P17, P18                | 1-2 inserted | PortX link from PHY                                         |

| P36                               | Open         | Connect power to U26                                        |

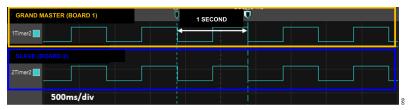

#### **GPIO AND TIMER HEADERS**

The EVAL-ADIN6310EBZ provides a header (P10) for observation of all Timer and GPIO signals. In addition to the header, there are LEDs on these pins. When using the **TSN Switch Evaluation** application, TIMER2 is configured for a 1 pulse per second (1PPS) signal by default and the LED connected to TIMER2 pin can be observed to blink at a 1 second rate when the board is powered and has been successfully configured using the **TSN Switch Evaluation** application.

If the Switch Host strapping is changed to SPI interface (default is Ethernet Host - RGMII), the TIMER0 pin functionality changes to be an Interrupt signal to the Host and TIMER0 is no longer available for timer or TSN functionality.

#### **CLOCK OPTIONS**

A crystal oscillator, Y8, is used to provide the ADIN6310 a clock signal. It is a 25 MHz crystal connected across the XTAL\_I pin and XTAL\_O pin of the ADIN6310 on the board. The clock for the ADIN1300 Ethernet PHYs can be provided from a buffered 25 MHz clock from the ADIN6310 or alternatively from a dedicated 25 MHz crystal local to each PHY (default). If the buffered clock option is selected, once the ADIN6310 has successfully powered up it generates a 25 MHz clock on CLK\_OUT\_1 pin. This clock is routed to a clock buffer chip, SI5330F-B00214-GMR (U31), which provides a buffered version of 25 MHz clock to each of the six ADIN1300 transceivers on the board.

#### **ON-BOARD LEDS**

The EVAL-ADIN6310EBZ has one LED, DS4, that lights up to indicate a successful power up of the circuit. There are eight LEDs, that are controlled by GPIO (0-3) and the Timer (0-3) signals when link P28 is inserted.

For the ports that support SGMII interface, there are LEDs (DS1, DS2, DS3, DS5) close to the SFP modules. When an SFP module is inserted and the link is up, the LOS signal from the SFP module is used to indicate optical activity/link status.

## STRAPPING AND CONFIGURATION

# **ADIN6310 Host Port Strapping**

The ADIN6310 Switch supports stack Processor/Host control over SPI or any of the six Ethernet ports. There is no stack processor/microcontroller used on this board, instead use a Windows PC as the Host with the **TSN Switch Evaluation** package.

When using this hardware, the user can connect a Host in a few different ways, firstly, via Port 0 Ethernet Port, alternatively, connected to RMII/RGMII directly over the FMC connector or otherwise via SPI through the dedicated headers (P39, P40). The Host Hardware strapping jumpers must be set according to the Host interface required.

The default Host port strapping configuration for this hardware is using Ethernet interface with Port 0 as the Host interface. The Switch port is configured for RGMII with no TXC or RXC delays and port speed of 1000 Mbps. In a typical application, with an MII interface to the Host, the Switch MAC port is directly connected to the Host MAC interface without a PHY in the path. As a result, when the Switch is configured for MAC interface Host, the Switch does not expect a PHY and does not perform any PHY configurations for that port. The EVAL-ADIN6310EBZ hardware does include a PHY on Port 0 (default RGMII Host interface), but the TSN Switch **Evaluation** application does not configure this PHY directly. As a result, the link brought up by the PHY on the Host port must match the Switch port speed set by strapping jumpers, default 1000 Mbps. The PHY is hardware strapped to auto-negotiate all speeds, if it brings up a lower speed link, there is a link mismatch between the Switch port and the PHY, which blocks the communication between the Host and Switch.

The Host port and Host port interface selection are configured via jumpers labeled TIMER 0/ 1/ 2/ 3 and SPI SS.

The Timer and SPI pins have internal pull-up/-down resistors, as shown in Table 5, the strapping jumpers provide user with ability to reconfigure the strapping to select alternative Host port types. For more details on all options available, refer to the Host Strapping section in the data sheet.

Table 5. Host Port Selection Jumpers

| Host Port                                  | SPI_SS | TIMER3 | TIMER2 | TIMER1 | TIMER0 |

|--------------------------------------------|--------|--------|--------|--------|--------|

| Internal Pull up<br>(PU)/Pull down<br>(PD) | PU     | PD     | PD     | PU     | PU     |

| SPI (Single)                               | OPEN   | OPEN   | OPEN   | OPEN   | OPEN   |

| SPI (dual)                                 | OPEN   | INSERT | OPEN   | OPEN   | OPEN   |

| SPI (quad) (low drive strength)            | INSERT | OPEN   | INSERT | OPEN   | OPEN   |

| SPI (quad) (high drive strength)           | INSERT | INSERT | INSERT | OPEN   | OPEN   |

analog.com Rev. A | 6 of 131

Table 5. Host Port Selection Jumpers (Continued)

| Host Port                              | SPI_SS | TIMER3 | TIMER2 | TIMER1 | TIMER0 |

|----------------------------------------|--------|--------|--------|--------|--------|

| RGMII 1000M<br>(default H/W<br>config) | INSERT | INSERT | OPEN   | INSERT | INSERT |

# **ADIN1300 Strapping**

There are six ADIN1300 devices on this evaluation board. The PHY on Port 0 is hardware strapped for auto-negotiation for all speeds (10 Mbps/100 Mbps/1000 Mbps), which allow it to bring a link up with a remote partner without any configuration from the Switch/Host. By default, the Switch Host strapping is configured for Port 0 as Host interface, the PHY needs to be able to bring up a link to enable communication path between the Host and the Switch so the **TSN Switch Evaluation** package can configure the Switch.

The other five PHYs (on Port 1 to Port 5) are configured for the same speeds (10 Mbps/100 Mbps/1000 Mbps), but power up in software power down mode with the Switch bringing them out of software power down and configuring them over the MDIO interface.

The PHY strapping upon power up is shown in Table 6.

Table 6. ADIN1300 PHY Port Configuration

| Tubic o. Abiitioo | Tuble of Abilition in The Comiguration               |                                                             |  |  |  |

|-------------------|------------------------------------------------------|-------------------------------------------------------------|--|--|--|

| Function          | PHY Port 0                                           | PHY Port (1-5)                                              |  |  |  |

| MAC Interface     | RGMII With Tx& Rx DLL Enabled                        | RGMII With Tx& Rx DLL<br>Enabled                            |  |  |  |

| MDI Mode<br>Speed | AutoMDI, Pref MDI<br>10/100 HD/FD, 1000 FD<br>Target | AutoMDI, Pref MDI<br>10/100 HD/FD, 1000 FD<br>Target, SftPd |  |  |  |

# **ADIN1300 Link Status Polarity**

The ADIN1300 LINK\_ST output pin is active high by default, whereas the P0\_LINK input of the ADIN6310 is active low by default, therefore the EVAL-ADIN6310EBZ hardware includes an inverter in the path between the Port 0 PHY LINK\_ST and the P0\_LINK of the Switch. The other five ports do not include this inverter, instead the PHY link polarity is changed to default low during the initial configuration.

As a result of this hardware difference on the Host Port 0, when the board first powers up, prior to configuration, the right LED of Port 1 to Port 5 lights. Once the configuration has been loaded from the **TSN Switch Evaluation** application, the PHY link signal as seen at the LEDs matches for all ports. The RJ45 right LEDs light to indicate link up, the left LEDs are on for link up and blink for traffic activity.

# ADIN1300 Link Status Voltage Domain

The ADIN1300 LINK\_ST is primarily intended to drive the Switch Px\_LINK input signal, therefore, resides on the VDDIO\_A/B voltage domain (default voltage rail is 1.8 V). If using the LINK\_ST pin to drive an LED to indicate link active, a level shifter must be used to

provide voltage and drive capability for the LED function. The LED anode is connected to 3.3 V through a 470  $\Omega$  resistors.

# **ADIN1300 PHY Addressing**

The ADIN1300 PHY addresses are configured by sampling their RXD pins after power on, when they come out of reset. The ADIN6310 Switch has internal pull-up/-down resistors on its RXD pins to support assignment of unique PHY addresses to each PHY per port. As a result, external PHY address strapping resistors are not necessary, unless different PHY addressing is required. The default PHY addresses assigned to the ADIN1300 devices is shown in Table 7

Table 7. Default PHY Addressing (set by ADIN6310)

| - rand the container that the containing (containing) |             |  |

|-------------------------------------------------------|-------------|--|

| Port Number                                           | PHY Address |  |

| 0                                                     | 0           |  |

| 1                                                     | 1           |  |

| 2                                                     | 2           |  |

| 3                                                     | 4           |  |

| 4                                                     | 8           |  |

| 5                                                     | 9           |  |

#### **MDIO INTERFACE**

The MDIO bus of the ADIN6310 connects to the MDIO bus of each of the six PHYs on the evaluation board. Configuration of the PHYs is done by the Switch firmware via this MDIO bus. The **TSN Switch Evaluation** application supports read and write access of the PHYs on all ports.

# **FMC CONNECTOR**

This evaluation board is fitted with a low pin count FPGA mezzanine card (LPC FMC) connector on the back of the board. This allows it to interface directly with a compatible FPGA board. All port 0 signals, SPI, TIMER, and GPIO signals are brought directly to the connector. This allows users to directly interface with the ADIN6310 with any one of the three Host interface options SPI, RGMII, and RMII. To use the FMC connector to interface with an FPGA or a processor board, make the changes to the resistor set, as shown in Table 8.

Table 8. Resistor configuration for FMC Use

| Signal     | Remove | Install |

|------------|--------|---------|

| RGMII\RMII |        |         |

| P0_TXC     | R239   | R227    |

| P0_TXCTL   | R240   | R228    |

| P0_TXD0    | R238   | R226    |

| P0_TXD1    | R237   | R225    |

| P0_TXD2    | R236   | R224    |

| P0_TXD3    | R235   | R217    |

| P0_RXC     | R242   | R219    |

| P0_RXCTL   | R241   | R218    |

| P0_RXD0    | R243   | R220    |

analog.com Rev. A | 7 of 131

Table 8. Resistor configuration for FMC Use (Continued)

| Signal     | Remove | Install |  |

|------------|--------|---------|--|

| RGMII\RMII |        |         |  |

| P0_RXD1    | R244   | R221    |  |

| P0_RXD2    | R245   | R222    |  |

| P0_RXD3    | R246   | R223    |  |

|            | SPI    |         |  |

| SPI_SS     | R485   | R372    |  |

| SPI_SCLK   | R484   | R329    |  |

| SPI_SIO0   | R493   | R358    |  |

| SPI_SIO1   | R492   | R365    |  |

| SPI_SIO2   | R499   | R373    |  |

| SPI_SIO3   | R501   | R379    |  |

| TIMER0     | R494   | R378    |  |

analog.com Rev. A | 8 of 131

# INSTALLING THE TSN SWITCH EVALUATION APPLICATION SOFTWARE

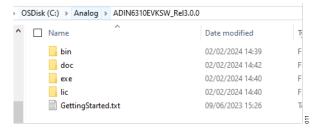

The evaluation package runs on Windows 10. To use the **TSN Switch Evaluation** software, first run the installer package to install the GUI and PC based web server. The installation steps are listed in the following section. The default location for the TSN Switch software install is **C:\Analog\ADINx310EVKSW-Relx.x.x folder**.

When the **TSN Switch Evaluation** software installation is complete, install Npcap if not already present on the machine. Download from Packet capture library for windows on the Npcap website. Npcap is recommended over WinPcap.

#### TSN Switch Evaluation Software Installation

To install the **TSN Switch Evaluation** software package, do the following steps:

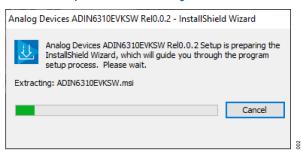

- Launch the installer file to begin the TSN Switch Evaluation software installation.

- 2. If a window appears asking for permission to allow the program to make changes to the PC, click **Yes**.

- 3. The installation process starts, see Figure 2.

Figure 2. Installation Begins

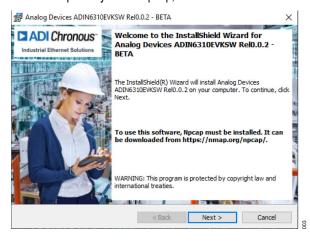

**4.** The welcome window appears (see Figure 3), with prompts that user must separately install Npcap, click **Next**.

Figure 3. Welcome Message

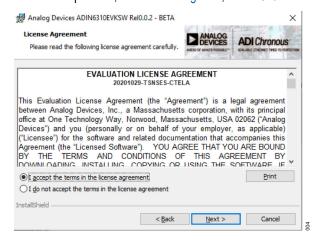

A license agreement appears. Read the agreement and click I accept the terms in the license agreement to allow the installation to proceed, as shown in Figure 4, click Next.

Figure 4. License Agreement

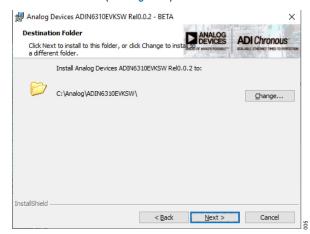

Select the location to install the TSN Switch Evaluation software and click Next (see Figure 5).

Figure 5. Select Destination Folder

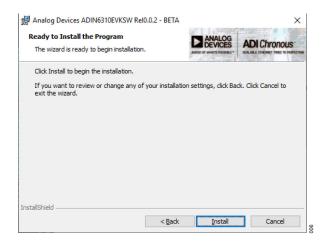

7. At the next step, click **Install** (see Figure 6).

analog.com Rev. A | 9 of 131

Figure 6. Installation Begins

**8.** A window appears, which shows the progress of the installation. When installation is complete, click **Finish**. (see Figure 7).

Figure 7. Installation Completes

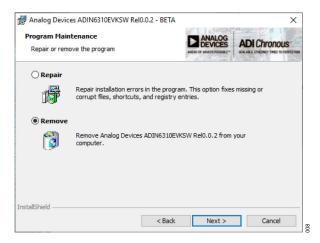

# Repair/Remove Installation

The installer also supports removing or repairing the installation. Launch the installer to remove or repair and do the following steps:

1. Select Repair or Remove and click Next (see Figure 8).

Figure 8. Remove or Repair Installation

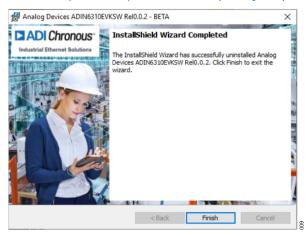

2. Follow the steps until complete, click **Finish** (see Figure 9).

Figure 9. Remove or Repair Completes

# **NPCAP INSTALLATION**

Install Npcap if not already present on the machine. Npcap is recommended over WinPcap. Download from Packet capture library for Windows on the Npcap website.

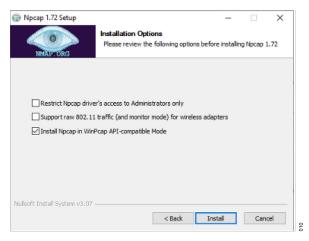

When installing NPCAP, ensure that the **Install Npcap in WinPcap API-compatible Mode** check box is selected, as shown in Figure 10.

analog.com Rev. A | 10 of 131

Figure 10. Npcap Installation Option (WinPcap API-Compatible Mode Selected)

# TSN SWITCH EVALUATION CONTENTS OVERVIEW

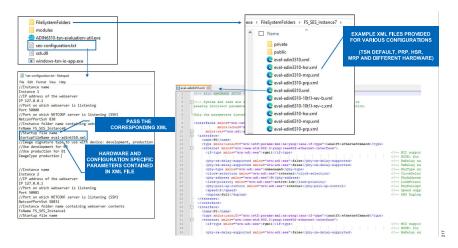

The software consists of GUI used to identify the Switch or chain of Switches and launch a PC based web server for each ADIN6310 device connected. The following section shows the different portions of the software. The default location for the TSN Switch Evaluation software install is C:\Analog\ADINx310EVKSW-Relx.x.x folder (see Figure 11).

Figure 11. Main Folder

This main folder contains the following sub-folders:

- ► The bin folder contains the firmware. New versions of the TSN Switch Evaluation package take care of automatically updating the latest firmware when initially run.

- ► The doc folder contains release note, schematics, and layout for the evaluation board in PDF format.

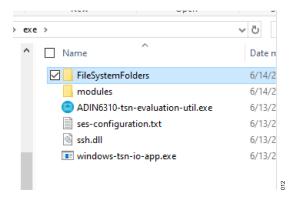

- ► The exe folder contains the executable (GUI), configuration files, and the web server file system (see Figure 12).

- ▶ The lic contains the license files (ELA license).

Figure 12. Contents of the exe Sub-Folder

# ADIN6310-tsn-evaluation-util

The TSN Switch Evaluation application GUI is named as ADIN6310-tsn-evaluation-util.exe. This application executes on a Windows PC platform and is used to query ADIN6310 boards that are present on a network. When an ADIN6310 board is found, the GUI configures the device primary MAC address, and allow the user to launch the TSN Switch Evaluation web page.

# **Process Application (windows-tsn-io-app)**

The process tool runs automatically in the background for each instance of SES device found and does not need to be launched by the user.

## **Modules Folder**

The **modules** folder contains yang models and start-up configuration.

## **FileSystemFolders**

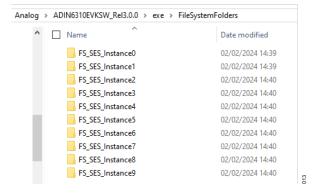

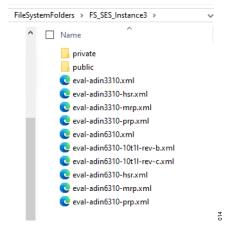

The **FileSystemFolders** folder (see Figure 13) contains the PC-based web server pages for each instance of the Switch that can be supported by the GUI (up to 10 max). Each device has its own file system, which is emulated on the PC by having a unique folder to act as the file system root.

Figure 13. Contents of the FileSystemFolders

analog.com Rev. A | 11 of 131

# **SOFTWARE INSTALLATION**

When the application is first run, the process needs to create a repository inside the file system instance, this can take some time, on order of 30 seconds to complete. Creating the repository is done first, prior to communicating with the Switch. Once the repository is successfully created, only then the process starts to communicate with the Switch and load the default start up configuration.

Figure 14. Contents of an FS\_SES\_Instance\_0 Folder Prior to First Run of Application

Once the application runs successfully, additional folders can be observed in the **FileSystemFolders**, specifically the **eventLog**, **log**, and **repository** folders (see Figure 15).

Figure 15. Contents of an FS\_SES\_Instance\_0 Folder After Running Application and Successfully Configuring Device

# ses-configuration File

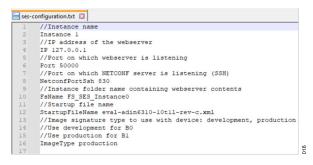

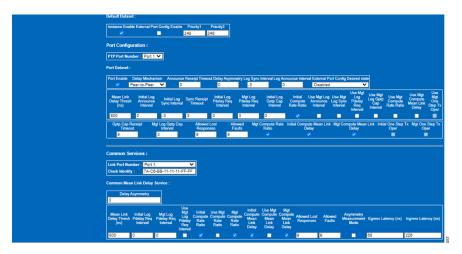

The **ses-configuration.txt** file shown in Figure 16 contains configuration parameters for the PC based web server, such as IP address, Port, NETCONF server port, location of file system, and hardware configuration XML file:

▶ IP and Port address: Specifies the IP and Port address used by the process application instance web pages. For the ADIN6310 evaluation kit the IP address must be set to use the local Host,

otherwise known as the loop back address, which is fixed to 127.0.0.1. Given the IP must remain the same for all process instances a port number must be used to identify which process instance the web pages belong to. This allows multiple instances of the process application to execute while controlling each board independently.

- ▶ **FsName**: Name of file system folder for each device.

- NetconfPortSsh: Port on which NETCONF server is listening (SSH), different port for each SES device.

- ▶ ImageType: Pass Production. Production applies for all released material or sample material with -U3 branding on the package.

There are 10 instances included in the folder, one instance for each possible Switches in the network (up to 10 maximum supported by GUI). The **StartupFileName** points to the board specific configuration for the device, and for this example is using the EVAL-ADIN6310EBZ evaluation board. The software also supports operation with the EVAL-ADIN3310 and EVAL-ADIN6310T1L versions of hardware.

Figure 16. Contents of ses-configuration

The device/hardware specific configuration is contained in XML files within in each FS\_SES\_Instance folder inside the FileSystemFolders.

Pass the matching xml file name to the **ses-configuration.txt** instance for the version of hardware being used and the required mode of operation.

Example XML files are provided for various configurations and parameters can be modified within the XML files. The Switch configuration is volatile and power cycling the Switch requires reconfiguration:

- ▶ **Default configuration** is for TSN functionality (for example, file names **eval-adin6310** and **eval-adin6310-10t1l.xml** all support TSN capability).

- Redundancy configuration examples are provided for HSR, PRP. and MRP.

Syntax and case are important when modifying parameters in the XML file. Errors or passing incorrect parameters is not supported and affect the operation of application.

analog.com Rev. A | 12 of 131

# **SOFTWARE INSTALLATION**

**Per-port configuration** parameters, including MII mode and PHY related specifics, see Figure 18.

- MII/Port MAC Interface Selection: All ports support RMII/ RGMII, additionally Port 1 to Port 4 support the following MAC interfaces, however hardware must be configured to match the required MAC interface:

- ▶ SGMII

- ▶ 1000base-SX/LX

- ▶ 1000Base-KX

- ▶ 100BASE-FX

- If-type: The default configuration for the EVAL-ADIN6310EBZ is RGMII interface to the ADIN1300 PHYs. The hardware does not support RMII interface to the PHYs. Port 0 (Ethernet Host) is always configured in unmanaged mode and the Switch does not configure that PHY directly. Hardware must be capable of the MII configured by software, for example, EVAL-ADIN6310 and EVAL-ADIN3310 hardware can support MII modes: rgmii, sgmii, sgmii-100base-sxlx, or sgmii-100base-fx. EVAL-ADIN6310T1LEBZ supports RGMII interface for all PHYs and can optionally support sgmii, sgmii-100base-kx, or sgmii-100base-fx options on Port 2 and Port 3.

- Phy-rx-delay-supported/phy-tx-delay-supported: RxDelay/TxDelay: RXC and TXC delays configuration for the Port.

- ▶ Phy-type: Per port identification of what PHY is connected. Choice of ADIN1100, ADIN1200, ADIN1300, or Unmanaged for ports that either have no PHY or have a different PHY. Hardware must match/support. By default Unmanaged is passed to Port 0.

- clock-selection: For use with RMII mode only. A setting of 0 enables a 50 MHz clock to be output onto the Port TXC pin for use by the PHY. Only use RMII mode where hardware is configured appropriately, EVAL-ADIN6310EBZ evaluation board supports RGMII mode by default for all ports.

- ▶ PHY Address: PHY address as configured by internal/external strapping. EVAL-ADIN6310 evaluation board uses ADIN6310 internal strapping to provide unique PHY address to each PHY, see ADIN1300 PHY Addressing section.

- ▶ Link-polarity: ADIN6310 expects Port \_LINK pin to be driven low for link up, high for link down. The default polarity of the ADIN1200/ADIN1300/ADIN1100 PHYs is for the LINK\_ST pin to be active high with link up, however the polarity can be inverted via MDIO write if needed as part of the port initialization. In the ses-configuration.txt file, for this parameter, a setting of active-low indicates the default is active low (no inversion needed), while passing active-high instructs the ADIN6310 to perform a MDIO write to invert polarity of LINK signal in PHY

- as part of the initialization routine. For the EVAL-ADIN6310EBZ evaluation hardware, there are six ADIN1300 PHYs, the PHY on Port 0 includes an inverter in the path between the LINK\_ST and the Switch P0\_LINK pin, therefore the inversion is already done for that port. For the remaining PHYs on Port 1 to Port 5, there is no inverter in the path, instead the ADIN6310 configuration needs to invert the polarity of the PHY LINK\_ST pin by writing over MDIO to configure the PHY.

- ▶ Phy-pull-up-control: Options of: internal, external, do-not-disable. Allows configuration of whether the PHY address strapping uses the internal pull resistors from the Switch RXD lines or uses external strapping resistors for PHY addressing. With EVAL-ADIN6310EBZ, the internal or do-not-disable options must be used. Do not use the external option as there are no external PHY address strapping resistors and this results in all PHYs defaulting to Address 0.

- ▶ Internal: Internal pulls are enabled. Default setting for the EVAL-ADIN6310EBZ evaluation board, the Switch sets unique PHY addresses for each PHY. No external strapping resistors are required for PHY addressing as a result. The strapping resistors are enabled until the PHY is brought out of reset and then disabled.

- External: Internal pulls are disabled. Use with EVAL-ADIN6310T1LEBZ evaluation board, external resistors are used to configure PHY addresses, therefore the internal pulls are disabled.

- ▶ **Do not disable**: Internal pulls are enabled and left enabled even after the PHYs are configured.

- ▶ **Speed**: Choice of 1, 0.1, 0.01 (Gbps).

- ▶ **Duplex**: Choice of full or half. The default is full.

**Device**: Configuration specifics such as device MAC Address, what redundancy capability is enabled and PHY latencies for PTP stack are passed next. See Figure 19.

- ▶ MAC address: Specifies the mac address the ADIN6310 hard-ware uses. The MAC address is unique to each device found and is also used by the process application to establish point-to-point communication with each device.

- ▶ **MSTP**: MSTP is enabled by default in the EVAL-ADIN6310EBZ.xml example.

- ▶ PhylngressLatency/EgressLatency: Pass the ingress and egress latency if there is an Ethernet PHY connected to the Port. Must match the hardware, the values passed show the ADIN1300 PHY latency parameters.

analog.com Rev. A | 13 of 131

Figure 17. Ses-configuration.txt File Overview and Location of Hardware Configuration XML

```

| Compared to the compared to the configuration parameters in this file, errors or compared to the configuration parameters in this file, errors or compared to the configuration parameters are neglected and an area important when modifying parameters in this file, errors or compared to the configuration parameters are neglected and an area important to the configuration parameters are not expected and the file of the configuration parameters are not expected and the configuration parameters

```

Figure 18. EVAL-ADIN6310EBZ: Per-Port Specific Configuration

Figure 19. Device MAC Address, Redundancy Configuration, MSTP, PTP/PHY Latency

analog.com Rev. A | 14 of 131

# **SOFTWARE INSTALLATION**

Figure 20. EVAL-ADIN6310EBZ-HSR: HSR Specific Configuration

# **HSR Specific Configuration**

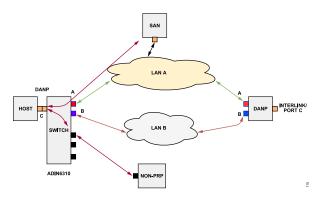

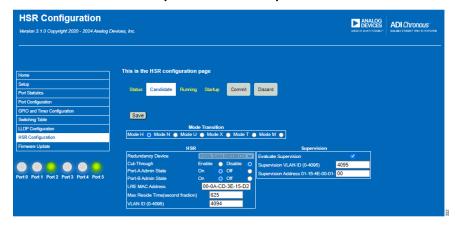

Figure 20 shows an example of **eval-adin6310-hsr.xml** file where HSR is enabled. All TSN functionality is disabled when PRP/HSR is enabled, therefore the **TSN Switch Evaluation** web server only exposes HSR functionality and any TSN related functionality is hidden. The configuration specific parameters for HSR functionality are:

- ▶ IreNodeType: LRE node type supported: none (redundancy disabled), prpmode1 for PRP operation or hsr to configure the device for HSR mode. Pass the relevant parameter to this field.

- ▶ IreSwitchingEndNode: Defines the type of functionality, use hsrnode for a DANH or hsrredboxsan for HSR redbox.

- ▶ LreDuplisResideMaxTime: Duplicate list reside max time in second fraction units.

- ▶ LreMacAddress: MAC address of the LRE device, this must be the MAC address of the Host interface.

- ▶ **LrePortX**: Pass which ports are A, B ports.

- ▶ LreDanPortC: Pass which port is used as Port C. If using SPI Host interface, pass none to this parameter.

- RedboxInterlinkPortCx: For redbox configurations, identify which ports are interlink ports.

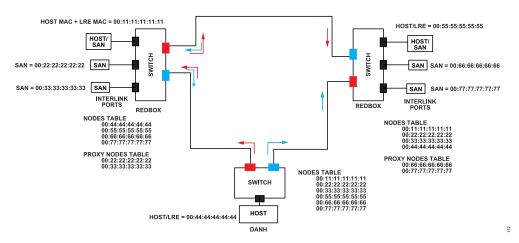

# **PRP Specific Configuration**

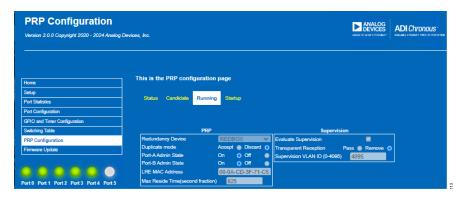

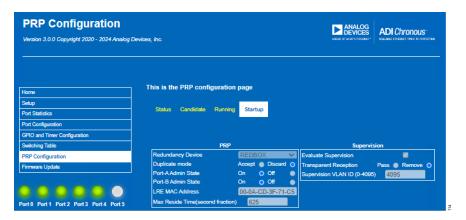

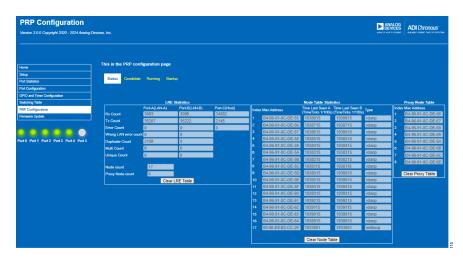

Figure 21 shows an example of **eval-adin6310-prp.xml** file where PRP is enabled. All TSN functionality is disabled when PRP is enabled, therefore the PC-based web server only exposes the PRP related functionality and all TSN related functionality is hidden.

Figure 21. PRP Configuration

The configuration specific parameters for PRP functionality are:

- IreNodeType: LRE node type supported: none (redundancy disabled), prpmode1 for PRP operation.

- IreSwitchingEndNode: Defines the type of functionality, use prpnode.

- LreDuplisResideMaxTime: Duplicate list reside max time in second fraction units.

- LreMacAddress: MAC address of the LRE device, this must be the MAC address of the Host interface.

- ▶ LrePortX: Pass which ports are A, B ports.

- LreDanPortC: Pass which port is used as Port C. If using SPI Host interface, pass none to this parameter.

- RedboxInterlinkPortCx: For redbox configurations, identify which ports are interlink ports.

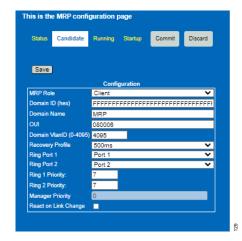

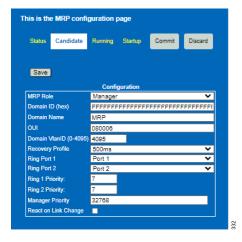

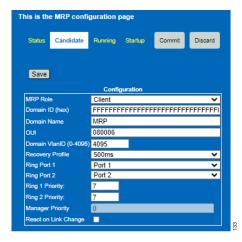

# **MRP Specific Configuration**

MRP can be enabled up front or alternatively use the default **eval-adin6310.xml** configuration and enable the function through the MRP web server page. Other redundancy features such as PRP or HSR must be disabled if MRP is enabled.

Figure 22 shows an example of **eval-adin6310-mrp.xml** file where MRP is enabled. TSN functionality is supported with MRP, so the full web server configuration is exposed.

- ▶ Domain ID: Unique domain ID for the MRP ring.

- ▶ MRP OUI: MRP OUI, defaults to 0x080006 (Siemens OUI).

- ▶ Domain Name: Domain name for the ring.

- ▶ **MRP Role**: Choice of client (default), manager or auto-manager.

- ▶ Ring Ports 1, 2: Default Port 1 and Port 2, choice of any port.

- ▶ Domain VLANID: Defaults to untagged/4095.

- React on Link Change: For faster recovery, use react on link change enabled for which the manager does not wait for test frames to timeout, instead, reacts on the link change frames.

- Recovery rate: Recovery profile choice of 30 ms, 200 ms, and 500 ms.

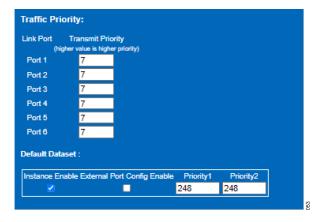

- ▶ MRP Port Tx Priority: Default Queue 7 is highest priority. PTP traffic also egresses in Queue 7. If using lowest recovery profile, change default PTP queue from 7 to a lower priority in the Time Synchronization IEEE 802.1AS page.

analog.com Rev. A | 15 of 131

#### SOFTWARE INSTALLATION

```

| Composition | December 1 | December 2 | De

```

Figure 22. MRP Configuration Example

## **EVAL-ADIN6310T1L Hardware**

The EVAL-ADIN6310T1LEBZ is a field switch using the six port ADIN6310 with four ADIN1100 10BASE-T1L spur ports and two standard Gigabit capable Ethernet trunk ports. The hardware includes single-pair power over Ethernet (SPoE) LTC4296-1 circuit. The default operation of the hardware is an unmanaged mode where the MAX32690 Arm Cortex-M4 microcontroller configures the switch into basic switching mode and the PSE for Class 12 operation. It is also possible to configure this version of hardware using the TSN evaluation application. For this purpose, there are two versions of XML file for this version of hardware. Check which revision of hardware prior to configuring and only use the matching XML file. Use eval-adin6310-10t1l-rev-c.xml for both REV C and D versions. The revision of hardware is printed on the evaluation board. For more detail on this evaluation board, access UG-2299 from the ADIN6310 product page.

#### **EVAL-ADIN3310 Hardware**

Use the **eval-adin3310.xml** files to configure the 3-port version of hardware.

# **INITIAL EVALUATION BOARD SETUP**

The **TSN Switch Evaluation** software can be used to test the Switch features. Connect the Switch evaluation board to another TSN capable device and do the following steps:

- 1. Perform the steps shown in Installing the TSN Switch Evaluation Application Software to install the software.

- 2. Pass the matching XML configuration file for the hardware/set-up required (TSN, HSR, PRP, MRP).

- Apply power to the board with the wall adapter provided by connecting to P2.

- 4. Turn Switch S1 to ON position, LED DS4 lights up.

- **5.** Connect PC through an Ethernet cable to Host Port 0 (Port 0 is the control plane for Switch configuration, it can also pass data traffic).

- Launch software by double-clicking the application ADIN6310tsn-evaluation-util.exe in the C:\Analog\ADINx310EVKSW-Relx.x.x\Files folder.

- 7. When the package is first run, it can take time to create the repository (less than 1 minute). The repository is created first, then the application starts communicating with the device for configuration purposes. The LED in the GUI blinks yellow until web server is ready to launch, when configuration is complete, the LEDs for any Switches found goes green.

- If daisy-chaining a number of Switch boards, allow a couple of minutes for each board as a repository needs to be created for each instance of the web server.

- **9.** In the event it takes a lot longer than 2 minutes for the LED to go green, close the GUI and reopen, power cycle the board and start searching again.

analog.com Rev. A | 16 of 131

#### SOFTWARE EXECUTION

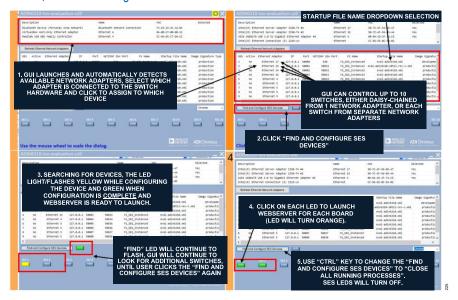

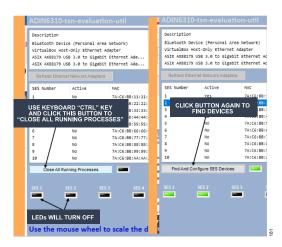

Start the application by double-clicking the **ADIN6310-tsn-evaluation-util.exe** executable. The GUI application window appears, as shown in Figure 24.

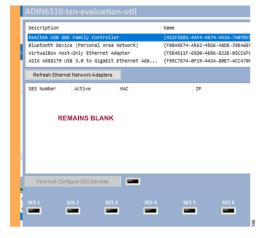

- The GUI automatically detects the available network adapters. Select the adapter that is connected to the ADIN6310 board Host (Port 0) by double-clicking the description line for that adapter. Once the adapter is selected, the device configuration information pulled from the ses-configuration.txt and XML files load and populate the lower window.

- 2. The GUI supports configuration of a chain of up to 10 devices from one network adapter, alternatively, the user can control multiple switches from individual network adapters. Select the chosen adapter in the upper window and then assign it to the switch Ethernet Adapter field by clicking in the GUI in that area. The GUI also supports selection of different startup files through the dropdown in the Startup File Name column. Click Find and Configure SES Devices button to start searching for connected Switch boards.

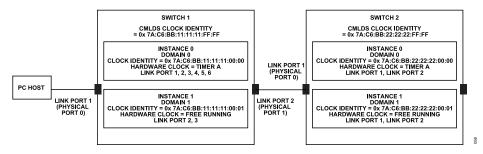

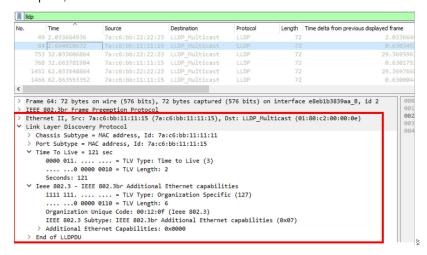

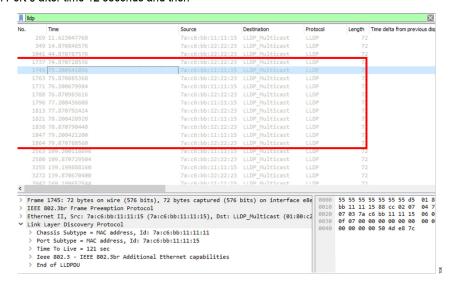

- 3. The GUI searches for and configures the MAC address for any ADIN6310 device it finds. Each Switch powers up with the same default MAC address (7a:c6:bb:ff:fe:00). The first thing the GUI application does during configuration is to assign a primary MAC address (based on XML configuration). If observing the traffic from Host to Switch using Wireshark, initially messages are sent from the PC to the default multicast address (79:c6:bb:ff:fe:00) and responses come from default MAC address 7a:c6:bb:ff:fe:00 until the primary MAC address gets assigned. An LED turns green for each board found. Clicking on the LED for each connected ADIN6310 device launches a browser for each board as shown in Figure 24. Once the web server is launched, the LED color changes to orange. Keep the PC application open, it needs to stay running while interacting with the web server. The GUI application continues to search for more ADIN6310 devices, so if all connected devices have been identified, stop the application searching by clicking the Find and configure button again. The find LED then stops flashing.

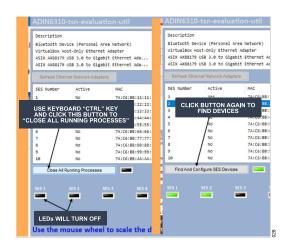

- 4. If boards are power cycled or reset button is pressed, the device reverts to the default MAC address and if the GUI application is searching, it sees them as new devices (additional LED lights go green). To avoid this, close the older processes associated with those instances of boards on the keyboard, use Ctrl and Close All Running Processes, as shown in point 4 of Figure 24.

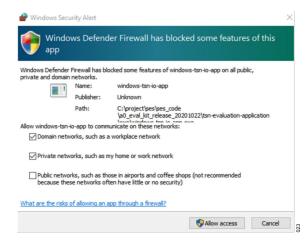

Note that the first time the application launches the web page, a user may receive a security warning regarding Windows firewall settings. Ensure that the firewall settings are configured to allow communications to pass through the firewall.

Figure 23. Firewall Security Pop-Up

analog.com Rev. A | 17 of 131

User Guide

# **SOFTWARE EXECUTION**

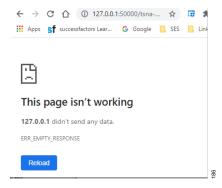

The application keeps searching for devices. In the event it does not discover more switches, there may be a pop-up window indicating that it found not other devices, like shown in Figure 25. Click

**OK** and proceed to launch the web server for the devices the application discovered.

Figure 24. Starting the GUI Application

Figure 25. GUI Pop-Up When the Application Does Not Find a Switch

analog.com Rev. A | 18 of 131

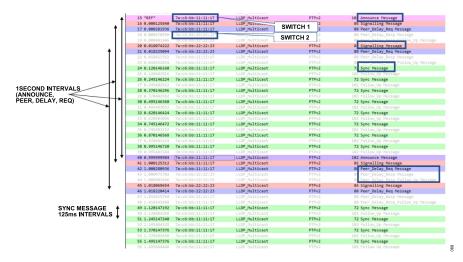

#### TSN SWITCH EVALUATION WEB PAGE OVERVIEW

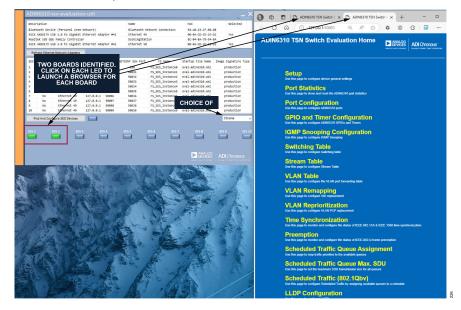

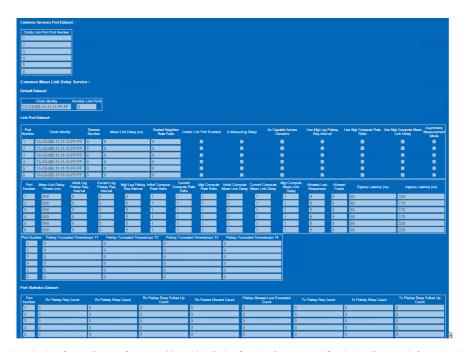

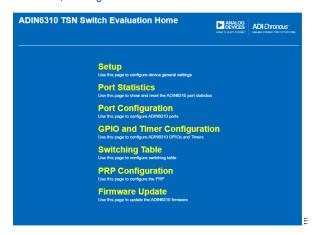

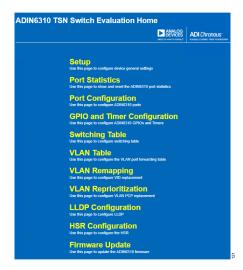

The **TSN Switch Evaluation** software package contains a set of web pages to configure the Switch for use in a TSN network or with redundancy features (see Figure 26).

A separate instance of the web server is used for each evaluation board connected to the PC and identified by the GUI.

The **TSN Switch Evaluation – Home** page provides access to the following web pages:

- ▶ **Setup**: Which allows the user to perform global actions, such as loading, storing, and managing the overall TSN database.

- ▶ **Port Statistics**: Provides an overview of each port transmit and receive information and any errors observed.

- ▶ Port Configuration: Provides user ability to control the port configuration and change port speed, interface type (hardware must support). It is not supported to change MAC interface modes during run-time. MAC interface must be configured during initial configuration. User can also communicate directly with the Ethernet PHYs via an MDIO read/write from this page.

- ▶ **GPIO** and **Timer Configuration**: Configure the functionality of the GPIO and Timer pins.

- ▶ **IGMP Snooping Configuration**: Provides user ability to enable and configure timeouts for IGMP snooping in the Switch.

- ▶ Switching Table: Provides user ability to install static entries in the lookup table, install extended table entries and flush the dynamic table. Status view provides insight into the learned dynamic entries. Per stream filtering and policing filters can be linked with static and extended entries in the Switching table.

- ▶ **Stream Table**: Provides user ability to install entries into the Stream table.

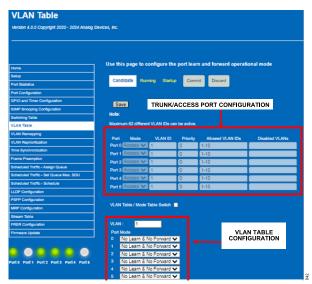

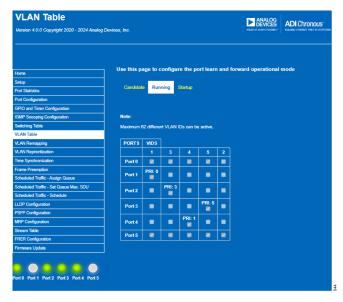

- ▶ VLAN Table: Provides user ability to configure the port behavior for virtual LAN (VLAN) IDs. Choice of standard VLAN configuration or configuring ports as Trunk or Access ports.

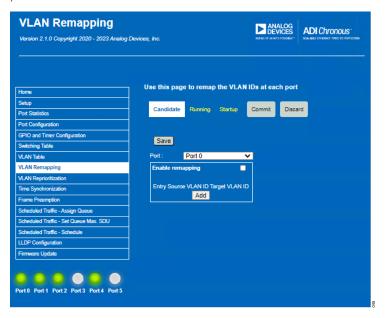

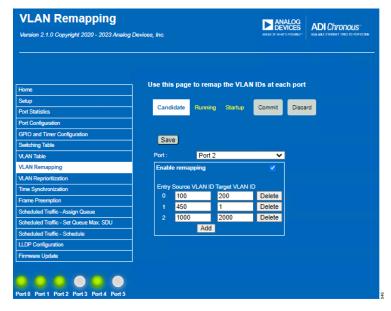

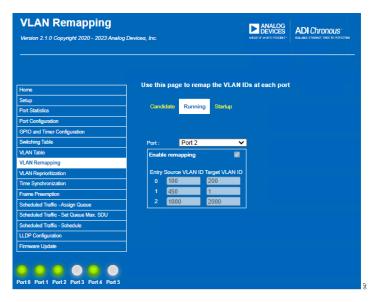

- ▶ VLAN Remapping: Provides the ability to remap VLAN IDs for each port.

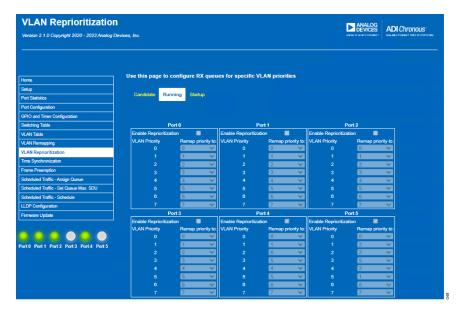

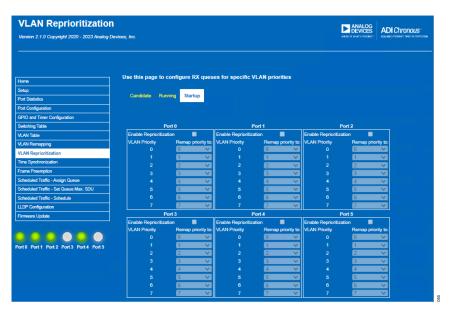

- ▶ VLAN Reprioritization: Gives user ability to configure remapping of VLAN priority on a port basis.

- ▶ **Time Synchronization**: Provides ability to configure and observer status of time synchronization (IEEE802.1AS).

- ▶ **Frame Preemption**: Provides ability to configure frame preemption on each port and observe preemption statistics.

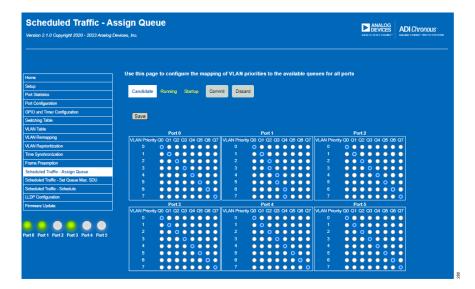

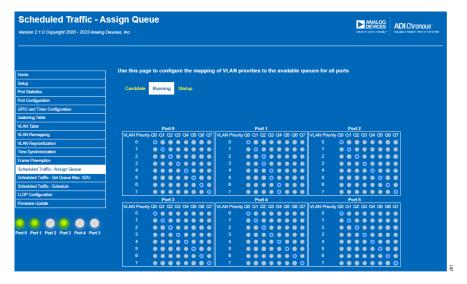

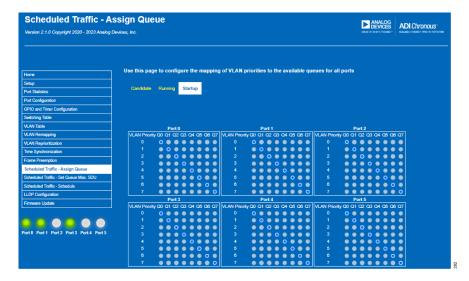

- ➤ Scheduled Traffic Assign Queue: Provides user the ability to configure the mapping of VLAN priorities to the available queues for each port.

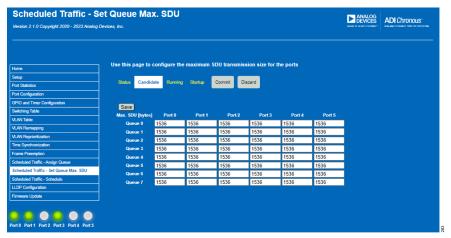

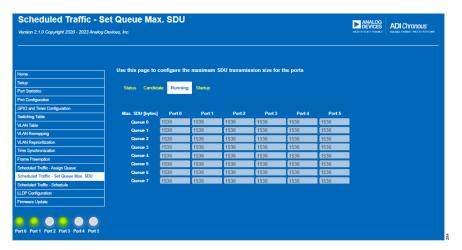

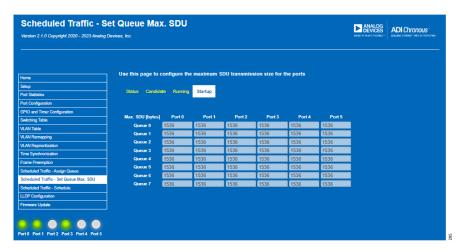

- ▶ Scheduled Traffic Set Queue Max. SDU: Provides ability to configure the maximum SDU transmission size for each port and each queue.

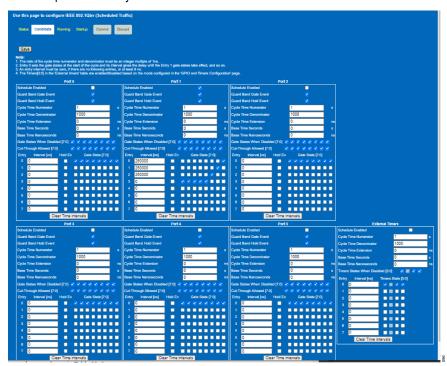

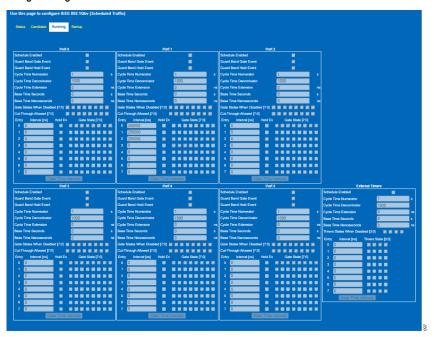

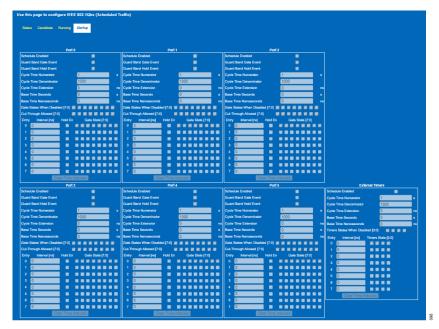

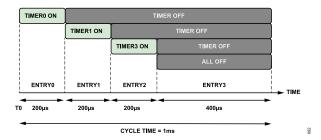

- Scheduled Traffic Schedule: Provides ability to set up schedules per port and also configure a schedule for the hardware Timer pins.

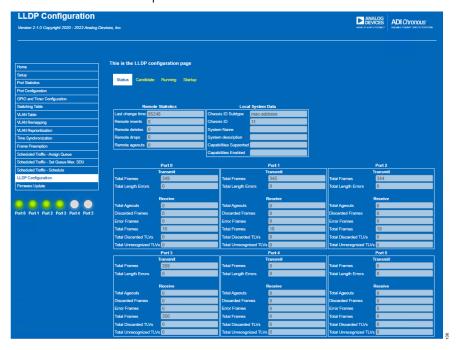

- ▶ **LLDP Configuration**: Provides LLDP configuration.

- ▶ **PSFP Configuration**: Provides ability to configure Per-Stream filtering and policing, Qci.

- ▶ **MSTP Configuration**: Provides ability to configure multiple spanning tree protocol.

- ▶ FRER Configuration: Frame replication and elimination for Reliability, 802.1CB, configuration page and stream entry for FRER streams.

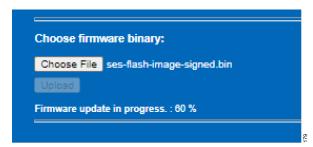

- ▶ **Firmware Update**: Provides ability to update/check version of device firmware.

Click any of these links to go to the required page. Once in a page, use the menu on the left to navigate to any of the other pages at any time. Ensure the GUI is kept running while navigating the web pages.

Figure 26. TSN Switch Evaluation – Home Page

analog.com Rev. A | 19 of 131

User Guide

# **TSN SWITCH EVALUATION WEB PAGE OVERVIEW**

# **CANDIDATE/RUNNING/STARTUP PAGES**

All configuration pages have **Candidate/Running/Startup** views and are linked to the sysrepo repository. To tune the way a function performs, users can change several parameters in the **Candidate** pages. Once the user has a new set of values for the candidate configuration, click **Save** followed by **Commit** to send the candidate configuration entries to the **Running** configuration. Click **Discard** to revert the candidate configuration back to current running configuration. The **Startup** page shows the current startup configuration. This may be the default startup configuration or user may have saved a previous configuration to **Startup**.

analog.com Rev. A | 20 of 131

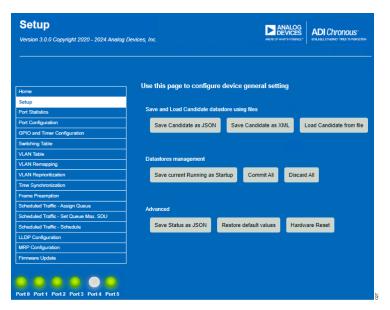

#### **SETUP PAGE**

This page is used to perform global operations on the **Candidate**, **Running**, and Startup configurations. Figure 27 shows these three configurations and which commands act on each configuration from the **Setup** page. Click the following command labels to perform the following actions:

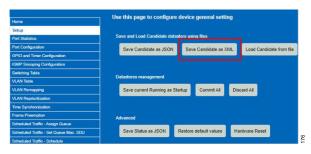

## SAVE AND LOAD CANDIDATE DATASTORE

- ▶ Save Candidate as: Save Candidate in JSON or XML format. The file gets saved to **Downloads** folder.

- ▶ Load Candidate from file: Select JSON or XML file to load.

# **DATASTORE MANAGEMENT**

- ▶ Save current Running as Startup: To store the running configuration to the startup configuration.

- ▶ **Commit All**: To push saved configuration to the device.

- ▶ **Discard All**: To discard configuration and revert to startup.

#### **ADVANCED**

Save Status as JSON: The operational file gets saved in JSON format to Downloads folder.

- ▶ Restore default values: Revert to default.

- ▶ Hardware Reset: Provides ability to do a reset of the ADIN6310 over the Ethernet Port. This also resets all the ADIN1300 PHYs (except for the Host Port PHY on Port 0). When this reset is used, this requires that any previous application processes running on the PC (running the web server) need to be closed. To close the process instances, press the keyboard Ctrl key, click Close all running processes. Release the Ctrl key, click Find and Configure SES Devices to resume operation, as shown in Performing a Reset section.

**Port 0 to Port 5 Status**: The LEDs on the left of page visually show which ports have established a link, these LEDs do not update automatically and require a refresh of the page.

Figure 27. TSN Switch Evaluation - Setup Page

analog.com Rev. A | 21 of 131

User Guide

# **SETUP PAGE**

# **PERFORMING A RESET**

After performing a reset, either using the RESET push button on the Evaluation kit or alternatively through the **Hardware Reset** button in the **Setup** page, the Switch reverts to it's power on reset configuration and the device MAC address reverts to default, therefore if the GUI is searching for devices, it likely finds it as a new device, not one of the previously found devices. Either reset the GUI or do the following steps (see Figure 28):

- To reestablish communication with the device, return to the GUI. Using the keyboard Ctrl button, click Close All Running Processes. All LEDs should turn off on the GUI.

- Click Find And Configure SES Devices to identify and connected boards (shown with green LEDs) the devices again.

**EVAL-ADIN6310**

Figure 28. After a Reset - Close Processes and Find Again

analog.com Rev. A | 22 of 131

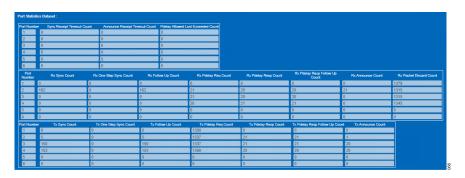

#### **PORT STATISTICS**

The **Port Statistics** page provides visibility into the various transmit and receive statistics reported for each port. As shown in Figure 29, click **Port Statistics** in the menu item on the **Home** page or in the menu on the left of the page to access the **Port Statistics** page. The upper table on this page shows traffic counts for packets that have been transmitted and received on each port and provides insight into any errors observed during reception or transmission. The Clear buttons enable clearing of individual ports or all port statistics.

The second table shows the extended statistics providing insight into the per port, per queue drop counters, and information about the buffer utilization and the interrupts (IRQ) available. Note that once an IRQ statistic is set, it remains set until actively cleared (clear button on the web page). The components of the second table are as follows:

Queue 0 Drop Count to Queue 7 Drop Count: These drop counters show the number of dropped packets for transmit on Queue 0 through Queue 7.

- ▶ **Highest Number of Buffers Used**: Number of the highest buffer reached since reset. The value ranges from 0 to 219.

- ► Current Number of Buffers in Use: Indicates how many buffers are currently being used. The value ranges from 0 to 219.

- ▶ Buffer Limit IRQ Status: Set to 1 if the buffer limit of 219 is reached.

- Buffer Parity Error IRQ Status: Set to 1 if a buffer parity error occurred.

- Buffer Allocate IRQ Status: Set to 1 if a buffer cannot be allocated

- Buffer Return Error IRQ Status: Set to 1 if a buffer cannot be returned.

The **Port Statistics** page updates automatically on a refresh rate of 5 seconds. To update on demand, refresh the page in the browser.

There is a **Download as CSV** option on the bottom right of each table on this page, where the current snapshot of statistics can be saved to an excel file.

Figure 29. Port Statistics Page

analog.com Rev. A | 23 of 131

# **PORT CONFIGURATION**

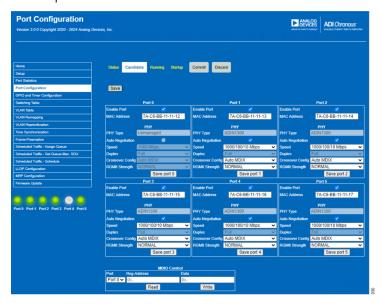

#### **CANDIDATE PAGE**

The **Port Configuration** page provides the user ability to configure port specific parameters in addition to seeing the current status of the ports.

As shown in Figure 26 or Figure 27, in the menu item on the **Home** page or in the menu on the left of the page, click **Port Configuration**. Similar to other pages, there are **Status**, **Candidate**, **Running**, and **Startup** views for this page.

The **Candidate** page provides user ability to configure some parameters for the port operation. Note that the XML file in the package is the primary opportunity for port configuration, but some additional run-time configuration is possible within the **Candidate** page.

Each port can be configured independently and saved, or alternatively, there is a **Save** button at top of page. Click the **Commit** button to push any changes to the device.

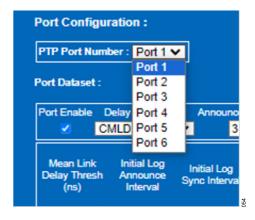

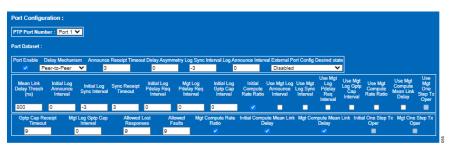

As shown in Figure 30, the configuration provided here as follows:

- ▶ **Enable Port**: This check box allows user to enable or disable ports. By default, all ports are enabled.

- ▶ MAC Address: The default MAC addresses shown corresponds to the MAC addresses assigned to each port based on the

primary MAC address set by the XML configuration file. Changes to this field are supported within the web page, enter the required MAC address and click **Save** button.

- ▶ PHY Type: This shows what is provided in the XML configuration file.

- ▶ PHY Auto-Negotiation: This check box is enabled by default and if disabled, indicates that the PHY is in Forced Speed mode, therefore only speeds 10 Mbps/100 Mbps are available.

- ▶ Speed: For Auto-Negotiation enabled options of 10 Mbps/100 Mbps/1000 Mbps, 10 Mbps/100 Mbps or 10 Mbps. When Auto-Negotiation disabled, options of 10 Mbps or 100 Mbps only.

- ▶ **PHY Duplex**: Full duplex by default. PHY duplex can be configured for speeds of 10 Mbps or 100 Mbps.

- ▶ PHY Crossover Config: Enables user to decide the cable crossover configuration of the ADIN1300 PHY on each port. Defaults to Auto MDIX. The user can select the following options:

- ▶ Auto

- ▶ MDI

- ▶ MDIX

- ▶ **RGMII Strength**: Configuration of the drive strength of the RGMII from the Switch side.

Figure 30. Port Configuration Page Overview - Candidate View

analog.com Rev. A | 24 of 131

# **PORT CONFIGURATION**

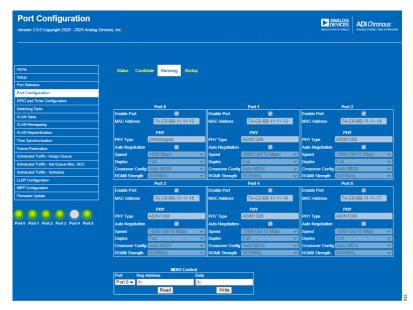

## STATUS PAGE

The **Status** page provides user snapshot of the current port configuration status.

As shown in Figure 31, the configuration provided here as follows:

▶ Interface Type: Shows the MAC interface as configured by the XML file. When using EVAL-ADIN6310EBZ, this hardware supports RGMII on all ports and SGMII interfaces on Port 1 to Port 4. SGMII modes need to be configured during initial configuration by editing the XML configuration. This hardware does not have any PHYs connected via RMII, therefore no RMII connectivity is possible.

- ▶ MAC Address: Shows the assigned MAC address to the port.

- ▶ PHY Type: Shows what PHY is connected.

- ▶ **Crossover**: Shows the actual crossover configuration.

- ▶ **Link**: Shows whether the link is up or down.

- ▶ **Speed (Mbps)**: Shows the speed of the established link.

- ▶ PHY Delay: Shows the PHY Tx delays (of ADIN1300 PHY), which depends on the speed of the link established.

- ▶ **RGMII Strength**: Shows the configured drive strength of RGMII from the Switch side.

Figure 31. Port Configuration Page Overview – Status View

Figure 32. Port Configuration Page Overview - Running View

analog.com Rev. A | 25 of 131

# **PORT CONFIGURATION**

Figure 33. Port Configuration Page Overview - Startup View

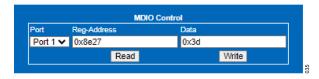

# **MDIO CONTROL**

The **MDIO Control** field is shown at the bottom of the **Port Configuration** page and provides user ability to interrogate any of the six ADIN1300 PHYs on the evaluation board.

Clause 22 read/writes are supported to the standard IEEE802.3 registers and vendor specific registers up to 0x1F. As shown in Figure 34, to read a register, in the **Port** field, select the port, in the **Reg-Address** field, enter the register address, and then click the **Read** button. The Switch communicates over MDIO bus to the appropriate PHY and the data field appears with the register information returned.

Similarly to write a PHY register, in the **Port** field, select the port, in the **Reg-Address** field, enter the register address, and then click the **Write** button to load.

Figure 34. MDIO Control – Communication with the PHYs on the Evaluation

Board

Access to Clause 45 or Extended registers is supported. Register address input format is 0xHEX.

Figure 35. MDIO Control – Access of Extended Register Space

analog.com Rev. A | 26 of 131

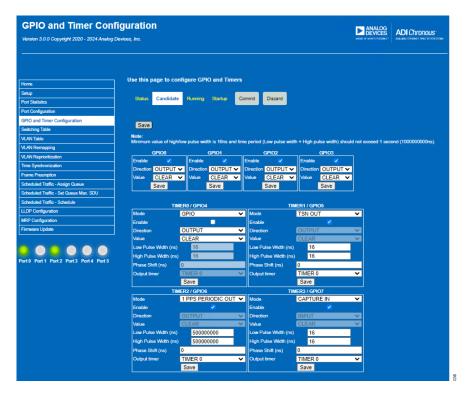

# **GPIO AND TIMER CONFIGURATION**

There are four GPIO pins and four Timer pins. This page provides user ability to control the function of these hardware pins. There are **Status**, **Candidate**, **Running**, and **Startup** pages for this functionality.

All pins are enabled by default. The GPIOs are enabled as Outputs. Timer0 is enabled as a GPIO by default, Timer1 is enabled for TSN timer function, Timer2 is enabled as a 1 pulse per second (1PPS) timer signal, and Timer3 is configured to be a Capture Input.

The available configurations and default configuration for these pins is shown in Table 9.

When changing GPIO or Timer operation, each change must be saved individually, otherwise, the user loses the change.

When SPI mode is selected as Host interface, Timer0 automatically configures as an Interrupt for the SPI interface to the Host and does not available to configure as a Timer/GPIO pin.

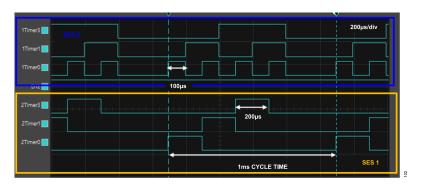

# **TSN OUTPUT TIMER**

This is the default operation for Timer1. When TSN Output Timer function is selected in this page, then a user needs to navigate to the Scheduled Traffic – Schedule page. The TSN Output Timer functionality allows the user to control the Timer pins with specific cycle times and is configured through the Scheduled Traffic – Schedule page.

# 1PPS PERIODIC OUTPUT

Timer2 and Timer3 can support a 1 pulse per second (1PPS) output. As shown in Figure 36, in the **Mode** drop-down box, select the **1PPS\_PERIODIC\_OUT** option. The low/high pulse-width fields fix at 500 ms.

Table 9. GPIO and Timer Pin Functionality

| Hardware Pin | Available Mode                                                             |

|--------------|----------------------------------------------------------------------------|

| GPIO0        | GPIO                                                                       |

| GPIO1        | GPIO                                                                       |

| GPIO2        | GPIO                                                                       |

| GPIO3        | GPIO                                                                       |

| GPIO4/TIMER0 | GPIO, TSN Output Timer (Default), Interrupt (SPI INT)                      |

| GPIO5/TIMER1 | GPIO, TSN Output Timer (Default)                                           |

| GPIO6/TIMER2 | GPIO, TSN Output Timer, Periodic Output, 1PPS Output (Default)             |

| GPIO7/TIMER3 | GPIO, TSN Output Timer, Periodic Output, 1PPS Output, Capture In (Default) |

# PERIODIC OUTPUT

Timer2 and Timer3 also support a user-configurable periodic output. As shown in Figure 36, in the **Mode** drop-down box, select the **PERIODIC\_OUT** option and enter the required high/low pulse-width for required pulse. The minimum value of high/low pulse-width is 16 ns and the time period must not exceed 1 second.

## **CAPTURE INPUT**

Timer2 and Timer3 can also support configuration as a capture Input. By default, Timer3 is a capture input. A possible usage for the capture input is to trigger the Switch to capture a hardware timestamp in response to a transition on the Timer3 and send that timestamp information to the Host. Note the web server does not support this configuration, the driver APIs need to be used to enable this and send the message to the Host.

## **OTHER MODES**

Any greyed out options are not available yet and intended for future releases.

analog.com Rev. A | 27 of 131

# **GPIO AND TIMER CONFIGURATION**

Figure 36. GPIO and Timer - Candidate Page

analog.com Rev. A | 28 of 131

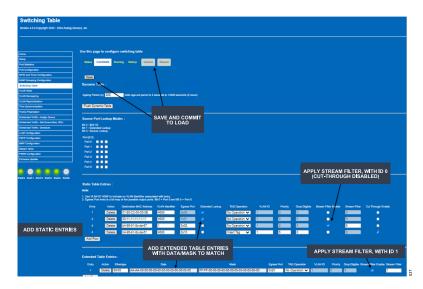

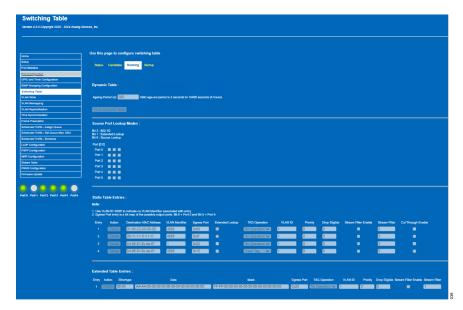

#### **SWITCHING TABLE**

#### **CANDIDATE VIEW**

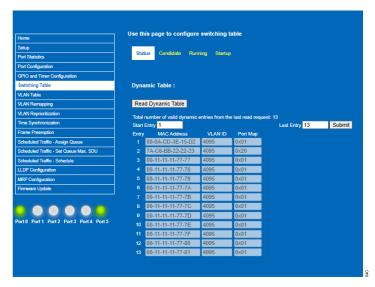

The **Switching Table** page provides user ability to install entries into the switch forwarding table. Static entries can be installed in addition to extended entries. The learned dynamic entries can also be viewed through the **Status** page.

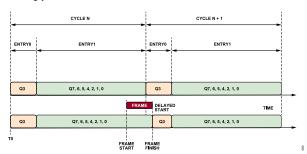

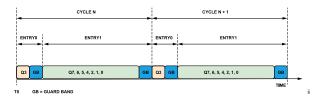

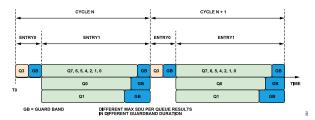

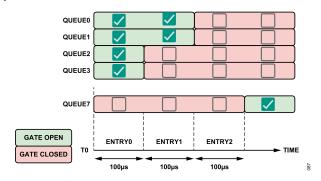

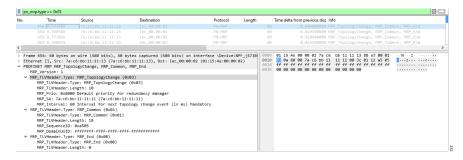

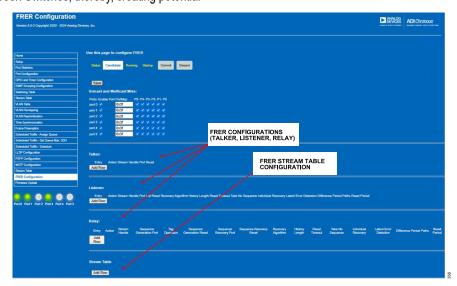

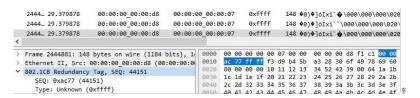

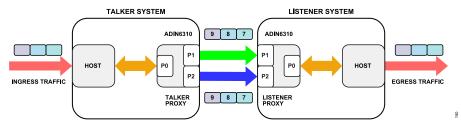

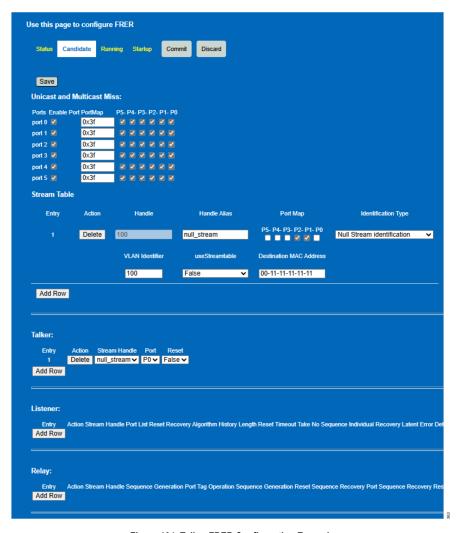

# **Dynamic Table**