### **POWER MANAGEMENT**

#### **Features**

- Supports DC and AC systems

- Switch to Controller scalable galvanic isolation

- Differential signaling interface for transient-immune differential serial protocol

- Device powered via galvanically-isolated interface CLK/NCLK. No power rail needed VGG for decoupling cap only

- Switch Characteristics

- Bi-directional blocking in OFF state

- Single 36V switch, 24omΩ R<sub>DS(on)</sub>

- Up to 1A operating current

- Steady-state over-current protection, 1.5A nominal

- Inrush current tolerant for 40ms, 3A nominal

- Transient protection for SW1 and SW2:

- IEC 61000-4-2 (ESD) ±24kV (air), ±16kV (contact)

- IEC 61000-4-4 (EFT) 40A (5/50ns) level 4

- IEC 61000-4-5 (Surge/Lightning) 8oV with 2Ω internal impedance (1.2/50μs)

### **Summary Specification**

- Junction operating temperature -40 °C to 125 °C

- Packaged in a 8 pin SOIC-EP

- Product is lead-free, Halogen Free, RoHS / WEEE

## Description

TS13501 is a bi-directional blocking 36V power DC or AC switch device which offers galvanic isolation between the control system and load. The device includes integrated 240m $\Omega$  36V switch allowing high efficiency switching of power loads or other high current applications. The differential input controls the state of the switch by way of a transient-immune serial protocol.

The TS13501 includes an over-current protection feature. Load current is monitored when the switch is in on state, notifying the system microcontroller of over-current faults by way of the STAT status pin.

### **Applications**

- Fire Safety Applications

- Automatic door controls

- Intrusion alarm sensors

- Industrial control

- Sprinkler control

- Power load/rail switching

- Input supply multiplexing

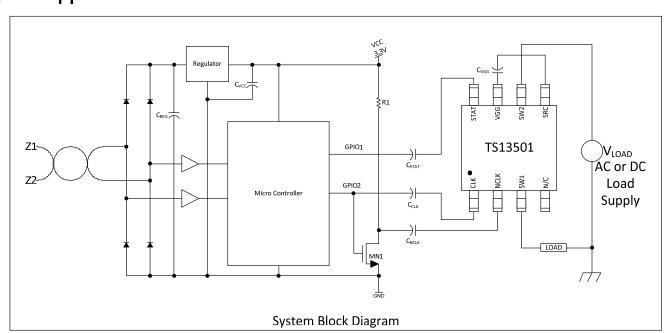

# **Typical Application Circuit**

# **Pin Description**

| Pin Name        | Pin # | Function             | Description                                                              |

|-----------------|-------|----------------------|--------------------------------------------------------------------------|

| CLK             | 1     | Switch Control Input | Serial interface to control device when correct protocol sent            |

| NCLK            | 2     | CLK Compliment Input | Drive compliment of CLK on this pin                                      |

| SW1             | 3     | Switch Terminal 2    | First switch terminal (Connect to Load or Supply)                        |

| N/C             | 4     | No Connection        | Pin not used                                                             |

| SRC             | 5     | Supply Reference     | Supply return                                                            |

| SW <sub>2</sub> | 6     | Switch Terminal 1    | Second switch terminal (Connect to Load or Supply)                       |

| VGG             | 7     | Internal Supply      | Device internally generated supply (connect decoupling capacitor to SRC) |

| STAT            | 8     | Device Status Output | Sends status output when switch is closed (Enabled)                      |

| SUB             | PAD   | Thermal Pad          | Pad for improved thermal performance - do not connect to any other net   |

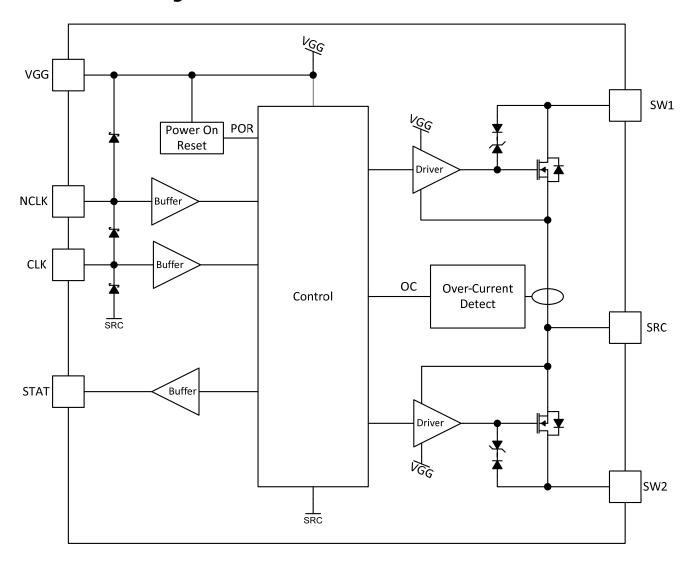

# **Functional Block Diagram**

### **Absolute Maximum Ratings**

Over operating free-air temperature range unless otherwise noted (1)

| Parameter                                                          | Range       | Unit |

|--------------------------------------------------------------------|-------------|------|

| SW1, SW2 <sup>(2)</sup>                                            | -1 to 45    | V    |

| VGG, CLK, NCLK, STAT <sup>(2)</sup>                                | -o.3 to 5.5 | V    |

| Operating Ambient Temperature Range, T <sub>A</sub>                | -40 to 85   | °C   |

| Storage Temperature Range, T <sub>STG</sub>                        | -65 to 150  | °C   |

| Electrostatic Discharge – Human Body Model                         | ±4          | kV   |

| Electrostatic Discharge – Charged-Device Model                     | ±1          | kV   |

| Electrostatic Discharge – IEC Contact (SW1 and SW2 Pins) (3)       | ±16         | kV   |

| Electrostatic Discharge – IEC Air Discharge (SW1 and SW2 Pins) (3) | ±24         | kV   |

| Peak IR Reflow Temperature (10 to 30 seconds)                      | 260         | °C   |

#### Notes:

- (1) Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated under "Recommended Operating Conditions" are not implied. Exposure to Absolute Maximum Rated conditions for extended periods may affect device reliability.

- (2) Voltage values are with respect to the SRC terminal.

- (3) SW1 and SW2 pins only, may require special system board layout techniques to achieve these levels.

### **Thermal Characteristics**

| Symbol            | Parameter                               | Value      | Unit |

|-------------------|-----------------------------------------|------------|------|

| θ <sub>JA</sub>   | Thermal Resistance, Junction to Ambient | 40         | °C/W |

| T <sub>JMAX</sub> | Maximum Junction Temperature            | 150        | °C   |

| T <sub>J</sub>    | Operating Junction Temperature Range    | -40 to 125 | °C   |

**Recommended Operating Conditions**

| Symbol           | Parameter                                                                          | Min | Тур | Max  | Unit   |

|------------------|------------------------------------------------------------------------------------|-----|-----|------|--------|

| $V_{SWX}$        | Switch Voltage,  V <sub>SW1</sub> - V <sub>SW2</sub>                               |     | 24  | 36   | V      |

| $V_{IH}$         | CLK, NCLK Input High Voltage                                                       | 1.7 | 3.3 |      | V      |

| V <sub>IL</sub>  | CLK, NCLK Input Low Voltage                                                        |     | 0   | 0.5  | V      |

| $C_{VGG}$        | VGG Bypass Capacitor                                                               |     | 470 |      | nF     |

| $C_CLK$          | CLK Isolation Capacitor                                                            |     | 68o |      | pF     |

| $C_{NCLK}$       | NCLK Isolation Capacitor                                                           |     | 68o |      | pF     |

| $C_{STAT}$       | STAT Isolation Capacitor                                                           |     | 100 |      | pF     |

| $V_{CLK}$        | CLK, NCLK Drive Voltage                                                            | 1.7 | 3.3 | 5.5  | V      |

| $F_{CLK}$        | CLK input frequency to turn on switch                                              | 75  | 100 | 1000 | kHz    |

| $N_{CLKON}$      | Number of CLK pulses to Turn On after VGG POR                                      |     | 18  |      | Pulses |

| $T_{CLKOFF}$     | CLK low time to Turn-Off                                                           | 50  |     | 150  | μs     |

| $T_{PRE-CHG}$    | Pre-charge time before VGG POR; V <sub>CLK</sub> = 3.0V; F <sub>CLK</sub> = 100kHz |     | 10  |      | ms     |

| F <sub>SYS</sub> | System Supply Frequency (Switched Load Power Source)                               | 0   | 60  | 65   | Hz     |

## **Electrical Characteristics**

$T_J = -40$ °C to 125°C (unless otherwise noted)

| Symbol              | Parameter                         | Conditions                                                                  | Min | Тур                | Max | Unit |

|---------------------|-----------------------------------|-----------------------------------------------------------------------------|-----|--------------------|-----|------|

| Supply Voltages     |                                   |                                                                             |     |                    |     |      |

| $V_{GG}$            | VGG Bias Output Voltage           | With respect to SRC, CLK and NCLK drive = 3.0V <sup>(1)</sup>               | 4.5 | 5.0                | 5.5 | V    |

| I/O Paramete        | rs                                |                                                                             |     |                    |     |      |

| V <sub>STATH</sub>  | STAT Output High Voltage Drop     | $3.0V < V_{GG} < 5.5V$ ; $I_{OH} = -4mA$<br>$V_{STATH} = V_{GG} - V_{STAT}$ |     | 0.7                | 1.3 | V    |

| V <sub>STATL</sub>  | STAT Output Low Voltage           | $3.0V < V_{GG} < 5.5V$ ; IOH = 4mA<br>$V_{STATL} = V_{STAT} - V_{SRC}$      |     | 0.1                | 0.2 | V    |

| I <sub>IL</sub>     | Input Low-level Leakage Current   | CLK Input; V <sub>CLK</sub> = V <sub>SRC</sub>                              | -1  |                    | 1   | μΑ   |

| I <sub>IH</sub>     | Input High-level Leakage Current  | $V_{CLK} = V_{GG}$                                                          | -1  |                    | 15  | μΑ   |

| T <sub>STAT</sub>   | STAT Pulse Width                  | Switch in ON state                                                          |     | 4*T <sub>CLK</sub> |     | μs   |

| Output Switch       |                                   |                                                                             |     |                    |     |      |

| R <sub>DS(on)</sub> | Switch On-Resistance              | Across SWx Pins                                                             | 150 | 240                | 405 | mΩ   |

| I <sub>SWX</sub>    | SW1/2 Leakage                     | $V_{SWX} = 24V$ ; $V_{SRC} = 0V$ , $T_{J} < 85$ °C                          | -3  |                    | 3   | μΑ   |

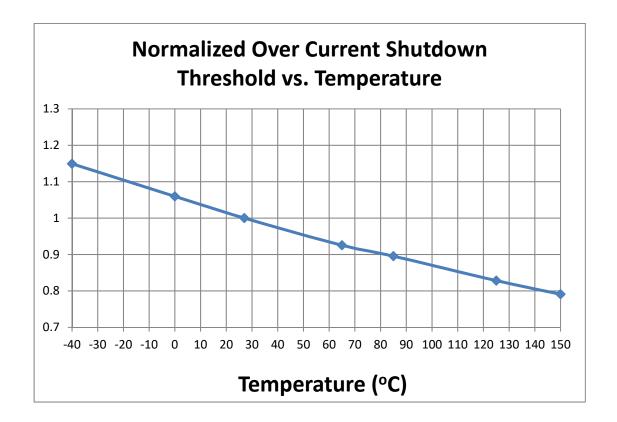

| IOUT <sub>oc</sub>  | Over Current Shutdown Threshold   | T <sub>J</sub> =25°C                                                        | 1   | 1.5                |     | Α    |

| IOUT <sub>PK</sub>  | Inrush Current Shutdown Threshold | T <sub>J</sub> =25°C                                                        | 2   | 3                  |     | Α    |

| OC <sub>FILT</sub>  | Over Current Deglitch             |                                                                             | 7   | 11                 | 15  | μs   |

| $T_IPK$             | Inrush Duration                   | 2 <sup>12</sup> /F <sub>CLK</sub> <sup>(2)</sup>                            |     | 41                 |     | ms   |

| V <sub>CLAMP</sub>  | V <sub>SWX</sub> Clamp Voltage    | $V_{SW_1}$ - $V_{SW_2}$ , $V_{SW_2}$ - $V_{SW_1}$ ; $I_{SW}$ =10mA          | 36  | 39                 | 42  | V    |

<sup>(1)</sup> Not tested in production

<sup>(2)</sup> CLK input must be present. Switch will be disabled (opened) if a CLK edge is not sensed within T<sub>CLKOFF</sub>.

# **Product Characteristics**

### **Detailed Description**

#### **Device Power Management**

The TS13501 receives power through power transfer via the galvanically-isolated interface. Galvanic power transfer depends on the GPIO driving the isolation capacitors to have sufficient drive capacity (current and voltage) to transfer needed power to the TS13501. This is usually not a problem due to the low quiescent current draw of the device. The CLK and its compliment signal, NCLK, perform two important functions. First, these form a differential signaling system which is more robust in its ability to reject transients present in the system. Second, it allows a voltage-doubling of the GPIO supply to be created within the TS13501. This allows sufficient supply voltage for operation even if used with a micro-controller with a 1.8V GPIO supply.

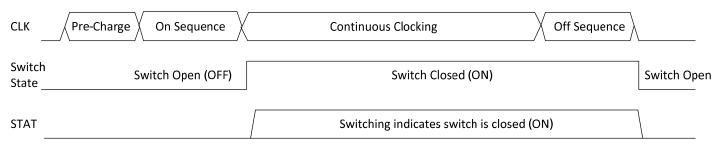

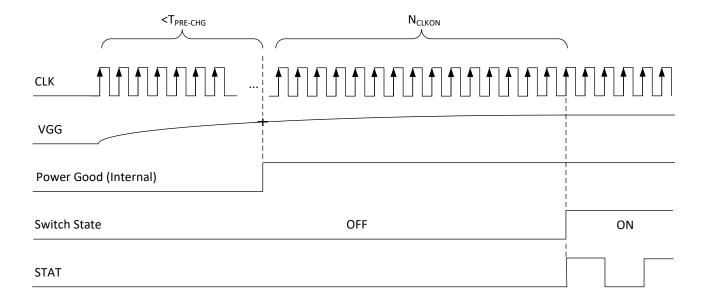

The CLK and NCLK pins must be continually switched at their recommended frequency while the switch is closed. When the device has been unpowered for a period of time, the CLK and NCLK pins must be switched for a Pre-Charge period, T<sub>PRE-CHG</sub>, of time to transfer sufficient charge to allow operation to begin.

Figure 1: Switch Command Sequences

#### The On Sequence

An initial pre-charge period must be provided to the device in order to bring up the local supply, VGG. The switch will be closed a number of clock pulses, N<sub>CLKON</sub>, after the VGG voltage has reached its internal Power Good threshold. At this point, the switch will transition to the closed (ON) state. This sequence is shown in Figure 2. The on-state of the switch can be verified by the presence of pulses on the STAT pin.

The system designer has some control over the total delay time to close the switch (T<sub>PRE-CHG</sub> + N<sub>CLKON</sub> / F<sub>CLK</sub>), which is influenced by the CLK amplitude, FCLK, Isolation capacitor value and VGG bypass capacitor value.

Figure 2: On Sequence

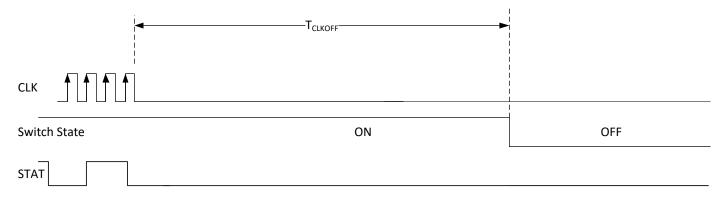

#### The Off Sequence

To transition the switch from a closed state to an open state, a valid Off Sequence must be received by the TS13501. The sequence consists of an interruption of the CLK input signal for a period of  $T_{CLKOFF}$ . A static period of duration  $T_{CLKOFF}$  will notify the device that the switch is to be transitioned to the open (OFF) state. Note that the STAT pin will indicate the switch state. The Off Sequence is illustrated in Figure 3.

Figure 3: Off Sequence

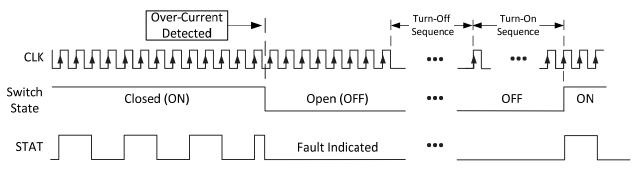

#### Switch Status Reporting

The status of the switch may be determined by the STAT signaling from the TS13501. When a valid Turn-On Sequence has been received, the switch will close and a signal received at the STAT output will indicate this condition. The STAT pin will continue to switch at a frequency of  $F_{STAT} = F_{CLK} / 4$  as long as a valid CLK input is driven to the device and the switch is in the closed (ON) state. The Status Functionality is shown in Figure 4.

Figure 4: Status Functionality

#### **Load Current Protection**

The device has the ability to protect itself from excessive current due to load faults.

#### **Shorted Load**

The load current is continually evaluated when the switch is in the "ON" state. In the event that the load current exceeds the threshold limits ( $IOUT_{OC}$  or  $IOUT_{PK}$ ), the switch will be opened and the state is indicated by the STAT pin, which will cease switching as shown in Figure 4.

#### **Inrush Current**

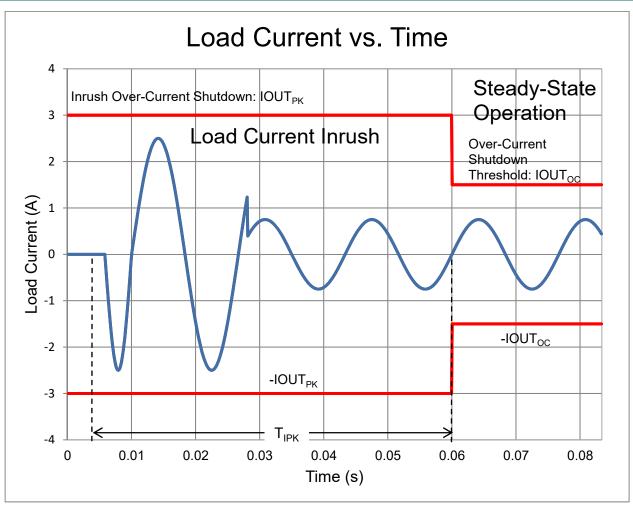

A system may present loads to the switch which result in high inrush currents when initially energized, but rapidly decrease to a lower level. If the inrush level is higher than the switch over-current shutdown (IOUT<sub>PK</sub>), it may be impossible to activate the load. This device allows the activation of loads with inrush currents on the order of twice their normal operating current for a short period of time. During the inrush period, the switch over-current shutdown is elevated, allowing current to build in the load, ensuring actuation. After the inrush delay period,  $T_{IPK}$ , the over-current threshold is reduced to a lower level to allow protection against faults. Figure 5 illustrates the time-variant peak load current in an AC system and how the inrush over-current shutdown threshold can be used to energize a load successfully when the higher inrush current would otherwise have tripped the lower steady-state over-current threshold (IOUT<sub>OC</sub>). As long as the load current stays within the red boundary area, the switch will remain closed.

Figure 5: Inrush Waveform

The device uses the CLK input signal to provide a time reference for the inrush period,  $T_{IPK}$ . Therefore,  $T_{IPK}$  is defined as:

$$T_{IPK} = \frac{2^{12}}{F_{CLK}}$$

If it is desired to change this time, it is possible to change the CLK input frequency to extend or shorten the inrush time period. Note that if there is no clock edge received by the TS13501 in  $50\mu$ s, the switch will be opened. This is to prevent creating overly long inrush times and to protect the switch and load in the event that control is lost. It is recommended that the inrush period be only as long as is required by the load in the system.

Typical inrush periods,  $T_{IPK}$ , would be 41ms when a 100kHz CLK input is supplied. If the CLK input frequency is reduced to the minimum allowed (half-period of 50 $\mu$ s), the time would be 410ms. The maximum CLK input frequency that can be used for peak inrush current timing is 1MHz, which would yield an inrush time of 4ms.

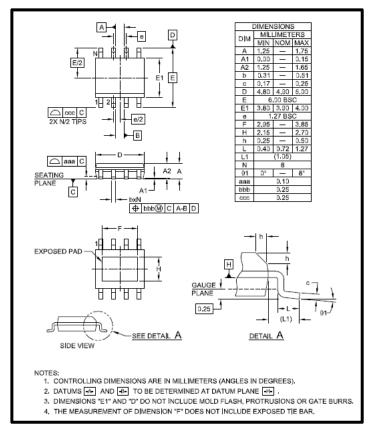

### Package Drawing for SOIC-8 EP

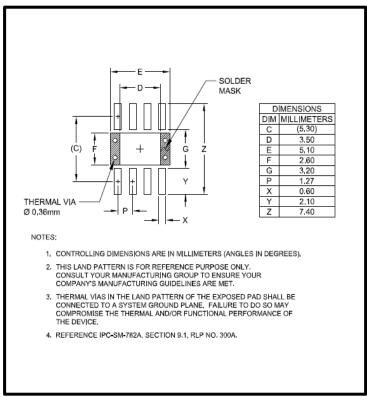

### **Landing Pattern for SOIC-8 EP**

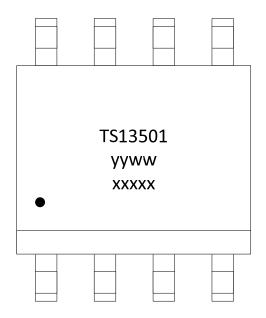

### Package Marking for SOIC-8 EP

Marking (Top View)

Marking for the SOIC 8-Lead Package:

Part Number (TS13501)

yyww = Date Code (Example: 1752, 52<sup>nd</sup> week of 2017)

xxxxx = Semtech Lot No. (Example: E9010)

## **Ordering Information**

| Device      | Package                                    |  |  |

|-------------|--------------------------------------------|--|--|

| TS13501STRT | SOIC-8 EP<br>Tape & Reel (2500 parts/reel) |  |  |

| TS13501-EVB | Evaluation Board                           |  |  |

#### **IMPORTANT NOTICE**

Information relating to this product and the application or design described herein is believed to be reliable, however such information is provided as a guide only and Semtech assumes no liability for any errors in this document, or for the application or design described herein. Semtech reserves the right to make changes to the product or this document at any time without notice. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. Semtech warrants performance of its products to the specifications applicable at the time of sale, and all sales are made in accordance with Semtech's standard terms and conditions of sale.

SEMTECH PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS, OR IN NUCLEAR APPLICATIONS IN WHICH THE FAILURE COULD BE REASONABLY EXPECTED TO RESULT IN PERSONAL INJURY, LOSS OF LIFE OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. INCLUSION OF SEMTECH PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE UNDERTAKEN SOLELY AT THE CUSTOMER'S OWN RISK. Should a customer purchase or use Semtech products for any such unauthorized application, the customer shall indemnify and hold Semtech and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs damages and attorney fees which could arise.

The Semtech name and logo are registered trademarks of the Semtech Corporation. All other trademarks and trade names mentioned may be marks and names of Semtech or their respective companies. Semtech reserves the right to make changes to, or discontinue any products described in this document without further notice. Semtech makes no warranty, representation or guarantee, express or implied, regarding the suitability of its products for any particular purpose. All rights reserved.

© Semtech 2018

### **Contact Information**

Semtech Corporation 200 Flynn Road, Camarillo, CA 93012 Phone: (805) 498-2111, Fax: (805) 498-3804 www.semtech.com