# 20 W (43 dBm), 8 GHz to 11.5 GHz, GaN Power Amplifier

**Preliminary Data Sheet**

ADPA1122AEHZ

#### **FEATURES**

High output power: 43 dBm typical at  $P_{IN} = 20$  dBm

High small signal gain: 33 dB typical

High power gain: 23 dB typical at  $P_{IN} = 20$  dBm

Frequency range: 8 GHz to 11.5 GHz

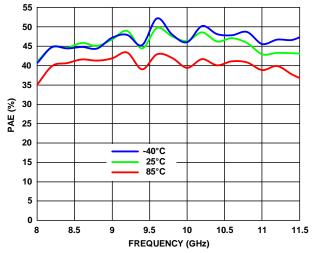

High power added efficiency: 45% typical at  $P_{IN} = 20 \text{ dBm}$

Supply voltage: V<sub>DDx</sub> = 28 V at 200 mA 18 Lead 7x7 mm SMT Package: 49 mm<sub>2</sub>

### **APPLICATIONS**

Weather radars Marine radars Military radars

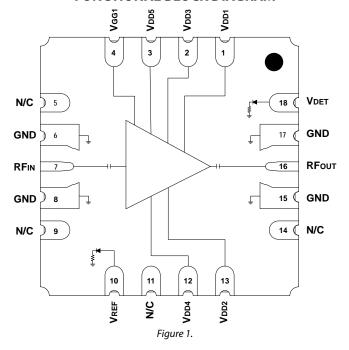

#### **FUNCTIONAL BLOCK DIAGRAM**

## **GENERAL DESCRIPTION**

The ADPA1122AEHZ is a gallium nitride (GaN), power amplifier, delivering 20 W (43 dBm) with more than 40% power added efficiency (PAE) across a bandwidth of 8 GHz to 11.5 GHz.

The ADPA1122AEHZ is ideal for pulsed applications, such as wireless weather, marine, and military radar applications.

# ADPA1122AEHZ

# **SPECIFICATIONS**

## **ELECTRICAL SPECIFICATIONS**

$T_A = 25$ °C,  $V_{DD1}$ ,  $V_{DD2}$ ,  $V_{DD3} = 28$  V, target quiescent current ( $I_{DQ}$ ) = 200 mA, drain bias pulse width = 100  $\mu$ s, 10% duty cycle, and the frequency range = 8 GHz to 11.5 GHz, unless otherwise noted.

Table 1.

| Parameter                | Symbol           | Min | Тур | Max  | Unit | Test Conditions/Comments                                                                                                                            |

|--------------------------|------------------|-----|-----|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| FREQUENCY RANGE          |                  | 8   |     | 11.5 | GHz  |                                                                                                                                                     |

| GAIN                     |                  |     |     |      |      |                                                                                                                                                     |

| Small Signal             |                  |     | 33  |      | dB   |                                                                                                                                                     |

| Small Signal Flatness    |                  |     | 1   |      | dB   |                                                                                                                                                     |

| Power Gain               |                  |     | 23  |      | dB   | Input power (P <sub>IN</sub> ) = 20 dBm                                                                                                             |

|                          |                  |     | 22  |      | dB   | $P_{IN} = 21 \text{ dBm}$                                                                                                                           |

| RETURN LOSS              |                  |     |     |      |      |                                                                                                                                                     |

| Input                    |                  |     | 20  |      | dB   |                                                                                                                                                     |

| Output                   |                  |     | 15  |      | dB   |                                                                                                                                                     |

| POWER                    |                  |     |     |      |      |                                                                                                                                                     |

| Output Power             | P <sub>OUT</sub> |     | 43  |      | dBm  | $P_{IN} = 23 \text{ dBm}$                                                                                                                           |

|                          |                  |     | 43  |      | dBm  | $P_{IN} = 21 \text{ dBm}$                                                                                                                           |

| Power Added Efficiency   | PAE              |     | 45  |      | %    | $P_{IN} = 20 \text{ dBm}$                                                                                                                           |

|                          |                  |     | 49  |      | %    | $P_{IN} = 21 \text{ dBm}$                                                                                                                           |

| TARGET QUIESCENT CURRENT | $I_{DQ}$         |     | 200 |      | mA   | Adjust the $V_{GG}$ between $-3.5$ V and $-2.0$ V to achieve an $I_{DQ}$ = 200 mA typical, $V_{GG}$ = $-2.6$ V typical to achieve $I_{DQ}$ = 200 mA |

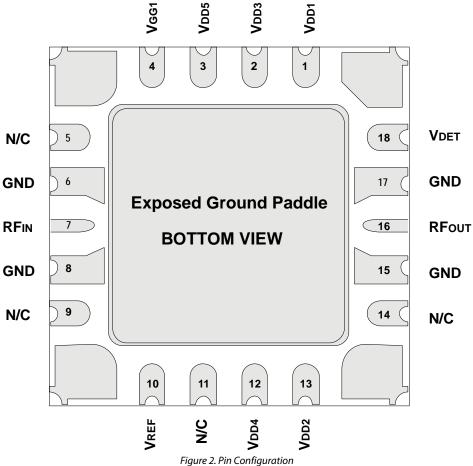

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

**Table 2. Pin Function Descriptions**

| Pin No. Mnemonic |                                                                                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 5, 9, 11, 14     | NIC                                                                                               | No Internal Connection. These pins must be connected to RF and dc ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 6, 8, 15, 17     | GND                                                                                               | Ground. These pins must be connected to RF and dc ground. See Figure 3 for the GND interface schematic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

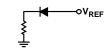

| 10               | $V_{REF}$                                                                                         | Reference Diode for Temperature Compensation of $V_{\text{DET}}$ RF Output Power Measurements. See Figure 9 for the $V_{\text{REF}}$ interface schematic. Detector Diode to Measure RF Output Power. Output power detection via this pin requires the application of a dc bias voltage through an external series resistor. Used in combination with the $V_{\text{REF}}$ pin, the difference voltage ( $V_{\text{REF}} - V_{\text{DET}}$ ) is a temperature compensated dc voltage that is proportional to the RF output power. See Figure 8 for the interface schematic. |  |  |  |

| 18               | V <sub>DET</sub>                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 7                | RFIN                                                                                              | RF Input. This pin is ac-coupled and matched to 50 $\Omega$ . See Figure 4 for the RFIN interface schematic.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

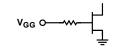

| 4                | $V_{GG1}$                                                                                         | Gate Control Voltage Pin. See Figure 5 for the V <sub>GG2</sub> interface schematic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 1, 2, 3, 12, 13  | V <sub>DD1</sub> , V <sub>DD2</sub> , V <sub>DD3</sub> ,<br>V <sub>DD4</sub> , V <sub>DD5</sub> , | Drain Bias Pins for the Amplifier. See Figure 7 for the V <sub>DD1</sub> , V <sub>DD2</sub> , V <sub>DD3</sub> , V <sub>DD4</sub> , V <sub>DD5</sub> interface schematic.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 16               | RFOUT                                                                                             | RF Output. This pin is ac-coupled and matched to 50 $\Omega$ . See Figure 6 for the RFOUT interface schematic.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                  | EPAD                                                                                              | Exposed Pad. The exposed pad must be connected to RF and dc ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

## **INTERFACE SCHEMATICS**

Figure 3. GND Interface Schematic

Figure 4. RFIN Interface Schematic

Figure 5. V<sub>GG</sub> Interface Schematic

Figure 9. V<sub>REF</sub> Interface Schematic

Figure 6. RFOUT Interface Schematic

Figure 7.  $V_{DD1 to} V_{DD3}$  Interface Schematic

Figure 8. V<sub>DET</sub> Interface Schematic

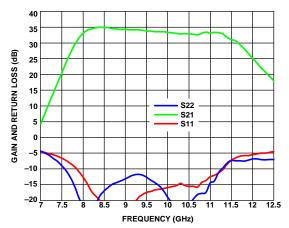

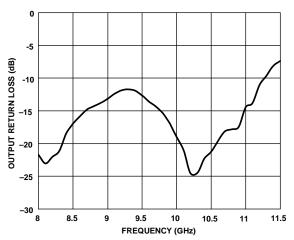

# TYPICAL PERFORMANCE CHARACTERISTICS

Figure 10. Gain and Return Loss vs. Frequency

Figure 11. Output Return Loss vs. Frequency

Figure 12. PAE vs. Frequency Pin = 20dBm

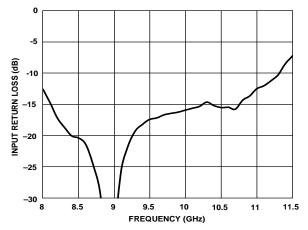

Figure 13. Input Return Loss vs. Frequency

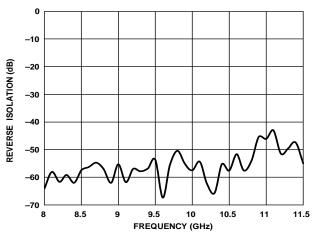

Figure 14. Reverse Isolation vs. Frequency

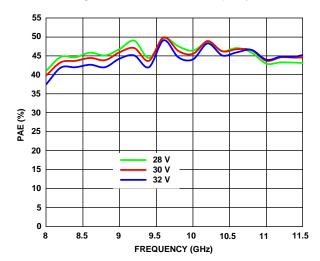

Figure 15. PAE vs. Frequency Over Vdd Pin = 20dBm

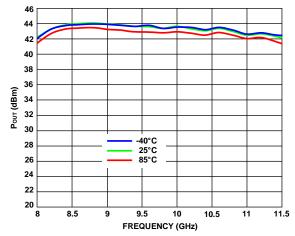

Figure 16. Poυτ vs. Frequency

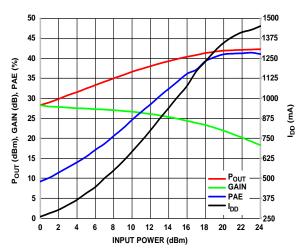

Figure 17. Output Power (Pour), Gain, PAE, and Total Supply Current (IDD) with RF Power Applied vs. Input Power at 8 GHz

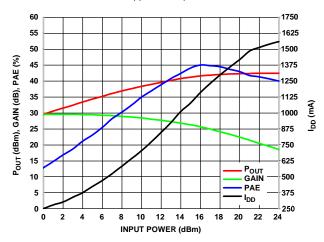

Figure 18. Output Power (Pour), Gain, PAE, and Total Supply Current (IDD) with RF Power Applied vs. Input Power at 11 GHz

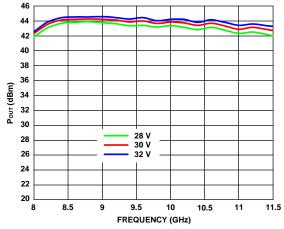

Figure 19. Роит vs. Frequency Over Vdd

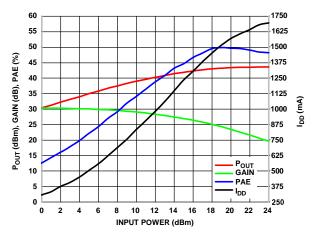

Figure 20. Output Power (Pout), Gain, PAE, and Total Supply Current (IDD) with RF Power Applied vs. Input Power at 9.5 GHz

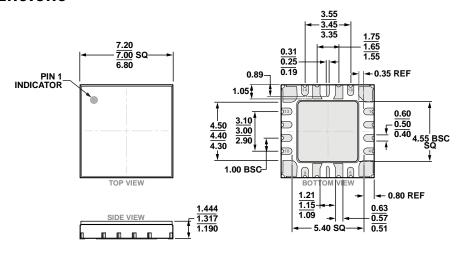

# **OUTLINE DIMENSIONS**

Figure 21. 16-Lead Ceramic Terminal Package [LCC\_HS] 7 mm × 7 mm Body and 0.75mm Package Height (EP-18-1) Dimensions shown in millimeters

## **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature    | MSL Rating | Description <sup>2</sup>        | Package Option |

|--------------------|----------------|------------|---------------------------------|----------------|

| ADPA1122AEHZ       | −40°C to +85°C | 3          | 16-Lead Ceramic Terminal LCC_HS | EP-18-1        |

| ADPA1122AEHZ-R7    | −40°C to +85°C | 3          | 16-Lead Ceramic Terminal LCC_HS | EP-18-1        |

| ADPA1122-EVALZ     |                |            | Evaluation Board                |                |

<sup>&</sup>lt;sup>1</sup> The ADPA1122AEHZ and ADPA1122AEHZ-R7 are RoHS compliant parts.

$<sup>^2</sup>$  The ADPA1122AEHZ and ADPA1122AEHZ-R7 are low stress injection molded plastic and their lead finish is 100% matte Sn.