## 28V, 4A Ideal Diode

### **FEATURES**

- ► Internal 50mΩ Power Path

- ▶ Wide Operating Voltage Range: 1.9V to 28V

- Reverse Current Protection

- ► Low 10µA Quiescent Current

- ► Fast 3µs Response to Load Steps

- ► Low 500nA Off State Current

- Smooth Switchover in Diode-OR Applications

- ▶ 10-Lead (3mm x 2mm x 0.75mm) LDFN Package

## **APPLICATIONS**

- Schottky Diode Replacement

- Battery and Wall Adapter Diode ORing

- Backup Battery Diode ORing

- ► Industrial and Consumer Hand-Held Applications

## **GENERAL DESCRIPTION**

The LT®4422 is an ideal 1.9V to 28V diode with integrated P-channel MOSFET. When enabled, 15mV forward voltage regulation minimizes power dissipation while increasing operating headroom and efficiency compared to a Schottky diode.

The LT4422 easily ORs power supplies together to increase system reliability and prevent reverse conduction. A non-enabled LT4422 blocks up to 28V at the output while exhibiting less than 1µA (typical) leakage current, providing orders of magnitude improvement over typical Schottky diodes, which leads to extended battery life.

Fast OUT to IN reverse bias detection minimizes reverse current, preventing undesired charging of input batteries. The open-drain STATUS output pulls low when the LT4422 is in shutdown or reverse bias.

All registered trademarks and trademarks are the property of their respective owners.

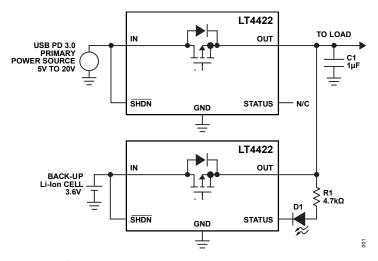

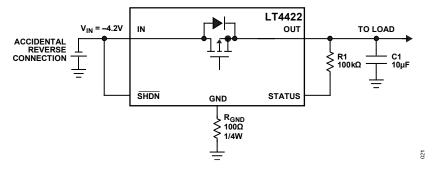

#### SIMPLIFIED APPLICATION DIAGRAM

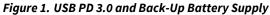

Figure 2. LT4422 I-V CURVE

# **TABLE OF CONTENTS**

| Features                                     | 1  |

|----------------------------------------------|----|

| Applications                                 | 1  |

| General Description                          | 1  |

| Simplified Application Diagram               | 1  |

| Revision History                             | 2  |

| Specifications                               | 3  |

| Absolute Maximum Ratings                     | 2  |

| Pin Configurations and Function Descriptions |    |

| Typical Performance Characteristics          | 6  |

| Block Diagram                                | 8  |

| Theory of Operation                          | 8  |

| Applications Information                     |    |

| USB PD 3.0 and Back-Up Battery Supply        |    |

| Automatic Power Path Control                 |    |

| 5V Power Ride-Through                        | 10 |

| High-Voltage Diode-OR                        | 11 |

| Layout and Thermal Considerations            | 11 |

| Typical Application                          | 12 |

| High-Load Current Application                | 12 |

| Reverse Input Voltage Protection             | 13 |

| Related Parts                                | 15 |

| Outline Dimensions                           | 15 |

| Ordering Guide                               | 17 |

# **REVISION HISTORY**

| REVISION | REVISION | DESCRIPTION     | PAGES   |

|----------|----------|-----------------|---------|

| NUMBER   | DATE     |                 | CHANGED |

| 0        | 09/24    | Initial Release | _       |

# **SPECIFICATIONS**

**Table 1. Electrical Characteristics**

(Specifications are at  $T_A = 25$ °C, IN =  $\overline{SHDN} = 8.4$ V, unless otherwise noted.)

| PARAMETER                                | SYMBOL                | CONDITIONS/COMMENTS                                                                                             |                                                   | MIN | TYP  | MAX  | UNITS |

|------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----|------|------|-------|

| Operating Voltage Range                  | $V_{IN}$              | -40°C ≤ T <sub>J</sub> ≤ 125°C                                                                                  |                                                   | 1.9 |      | 28   | V     |

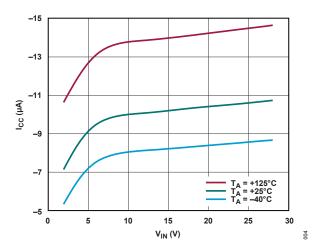

| Quiescent Current in Forward Regulation  | I <sub>cc</sub>       | I <sub>OUT</sub> = -10mA<br>Measured<br>Through GND                                                             | -40°C ≤ T <sub>J</sub> ≤ 125°C                    |     | -10  | -18  | μА    |

| Quiescent Current in<br>Shutdown         | I <sub>SD</sub>       | SHDN = GND<br>Measured<br>Through GND                                                                           | -40°C ≤ T <sub>J</sub> ≤ 125°C                    |     | -0.1 | -2   | μΑ    |

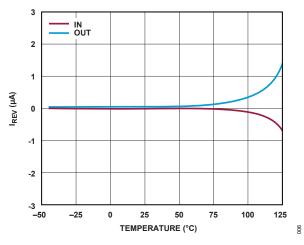

| Reverse Leakage Current<br>to IN         | I <sub>REV(IN)</sub>  | IN = GND,<br>OUT = 28V,<br>SHDN = GND                                                                           | -40°C ≤ T <sub>J</sub> ≤ 125°C                    |     | -0.1 | -2   | μА    |

| Reverse Leakage Current<br>to OUT        | I <sub>REV(OUT)</sub> | IN = GND,<br>OUT = 28V,<br>SHDN = GND                                                                           | -40°C ≤ T <sub>J</sub> ≤ 125°C                    |     | 0.1  | 4    | μА    |

| Forward Regulation<br>Voltage (IN - OUT) | $V_{REG}$             | I <sub>OUT</sub> = -10mA                                                                                        | -40°C ≤ T <sub>J</sub> ≤ 125°C                    | 5   | 15   | 25   | mV    |

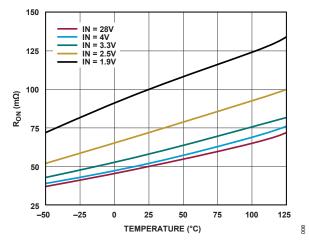

| Internal Path On-<br>Resistance          | R <sub>on</sub>       | I <sub>OUT</sub> = -2A                                                                                          | -40°C ≤ T <sub>J</sub> ≤ 125°C                    | 29  | 50   | 100  | mΩ    |

| Reverse Turn-Off Time                    | t <sub>REV</sub>      | Step OUT from<br>8.4V to 8.6V<br>STATUS Falling                                                                 | -40°C ≤ T <sub>J</sub> ≤ 125°C                    |     | 15   | 30   | μs    |

| Response Time to Load<br>Step            | t <sub>FON</sub>      | Step $I_{OUT}$ from<br>-10mA to -1A, $C_{OUT} = 10 \mu F$ $-40^{\circ}C \le T_{J} \le 125^{\circ}C$             |                                                   |     | 3    | 4    | μs    |

| SHDN Rising Threshold                    | $V_{SRT}$             | -40°C ≤ T <sub>J</sub> ≤ 125°C                                                                                  |                                                   | 1   | 1.3  | 1.6  | V     |

| SHDN Hysteresis                          | $V_{HYST}$            | -40°C ≤ T <sub>J</sub> ≤ 125°C                                                                                  |                                                   | -75 | -130 | -230 | mV    |

| SHDN Input Current                       | I <sub>SHDN</sub>     | <u>SHDN</u> = 28V                                                                                               | SHDN = 28V         -40°C ≤ T <sub>J</sub> ≤ 125°C |     | 1    | 2    | μΑ    |

| SHDN Delay to Power<br>Path Enable       | t <sub>on</sub>       | Step SHDN from<br>GND to IN<br>STATUS Released                                                                  | -40°C ≤ T <sub>J</sub> ≤ 125°C                    |     | 570  | 1000 | μs    |

| SHDN Delay to Power<br>Path Disable      | t <sub>OFF</sub>      |                                                                                                                 |                                                   |     | 85   | 160  | μs    |

| STATUS Output Voltage<br>Low             | V <sub>OL(STAT)</sub> | $\frac{I_{STATUS} = 1 \text{mA},}{\overline{SHDN} = GND} -40^{\circ}\text{C} \le T_{J} \le 125^{\circ}\text{C}$ |                                                   |     | 180  | 410  | mV    |

| STATUS Output High<br>Leakage            | I <sub>OH(STAT)</sub> | STATUS = 28V                                                                                                    | -40°C ≤ T <sub>J</sub> ≤ 125°C                    |     | ±5   | ±200 | nA    |

analog.com Rev. 0 3 of 18

## **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C^{4}$ , unless otherwise specified.

**Table 2. Absolute Maximum Ratings**

| PARAMETER                                    | RATING         |

|----------------------------------------------|----------------|

| Supply Voltage IN                            | -0.3V to 30V   |

| Supply Voltage OUT                           | -0.3V to 30V   |

| Supply Voltage (IN – OUT) <sup>3</sup>       | -30V to 0.3V   |

| Input Voltage SHDN                           | -30V to 30V    |

| Output Voltage STATUS                        | -0.3V to 30V   |

| Input Current IN                             | 6A             |

| Output Current OUT                           | -6A            |

| Operating Junction Temperature Range LT4422A | -40°C to 125°C |

| Storage Temperature Range                    | -65°C to 150°C |

<sup>&</sup>lt;sup>1</sup> All currents into pins are positive; all voltages are referenced to GND unless otherwise noted.

analog.com Rev. 0 4 of 18

The LT4422 is tested under pulsed load conditions such that  $T_J \approx T_A$ . The junction temperature ( $T_J$  in °C) is calculated from the ambient temperature ( $T_A$  in °C) and power dissipation ( $P_D$  in Watts) according to the formula:  $T_J = T_A + (P_D \bullet \theta_{JA})$ .

This voltage is set by the power path MOSFET's body diode and will safely exceed 0.3V during start-up for a limited time determined by the body diode thermal dissipation.

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

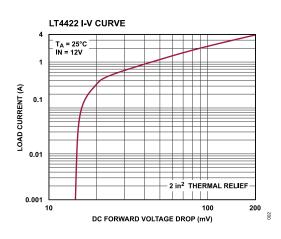

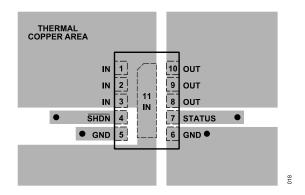

# PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configurations

**Table 3. Pin Descriptions**

| PIN                                                                | NAME | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|--------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1, 2, 3, 11                                                        | IN   | Positive Input Supply and Ideal Diode Anode. Connect the IN pin to the power source that supplies power to the load. The exposed pad is also connected to IN. Use a copper plane connected to the exposed pad for thermal management (see <i>Applications Information – Layout and Thermal Considerations</i> for sizing details). Bypass IN with a 0.1µF or larger capacitor to suppress undesired reverse turn-off in applications with load transient ringing. |  |  |

| 4                                                                  | SHDN | Shutdown Control Input. Driving SHDN low disables the ideal diode between IN and OUT, placing the part in a low quiescent current mode. SHDN may be connected to IN for automatic turn-on applications. Do not leave SHDN open.  Note that the power path body diode provides a conducting path between IN and OUT when in shutdown.                                                                                                                              |  |  |

| 5, 6                                                               | GND  | Device Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| when SHDN is pulled low or when OUT exceeds IN by approximately 20 |      | Open-Drain Status Output. When IN or OUT is greater than 1.9V, STATUS pulls low when SHDN is pulled low or when OUT exceeds IN by approximately 20mV. Connect STATUS to OUT or an external supply through a pull-up resistor. Leave STATUS open or connect to GND if not used.                                                                                                                                                                                    |  |  |

| 8, 9, 10                                                           | OUT  | Ideal Diode Cathode Output. In diode-OR applications using multiple LT4422s, connect the common output node to OUT. Bypass OUT with a 0.1µF or larger capacitor to suppress undesired reverse turn-off in applications with load transient ringing.                                                                                                                                                                                                               |  |  |

analog.com Rev. 0 5 of 18

900

## **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 4. Supply Current to GND vs IN Voltage

Figure 5. Supply Current to GND vs IN Voltage in Shutdown

Figure 6. Reverse Leakage Current vs Temperature

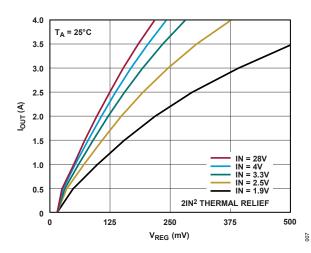

Figure 7. Load Current vs Forward Voltage Drop

Figure 8. On-Resistance vs Temperature

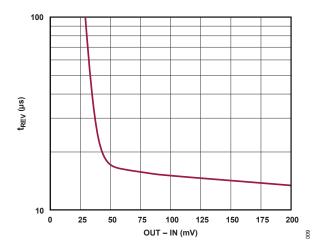

Figure 9. Turn-Off Time vs Reverse Voltage

analog.com Rev. 0 | 6 of 18

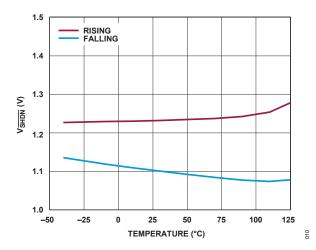

Figure 10. Shutdown Threshold vs Temperature

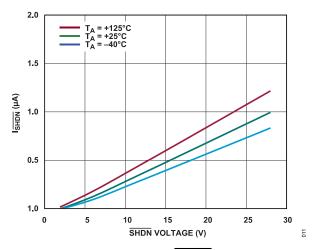

Figure 11.  $I_{\overline{SHDN}}$  vs  $\overline{SHDN}$  Voltage

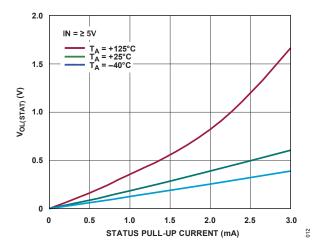

Figure 12. STATUS  $V_{\rm OL}$  vs Pull-Up Current

analog.com Rev. 0 7 of 18

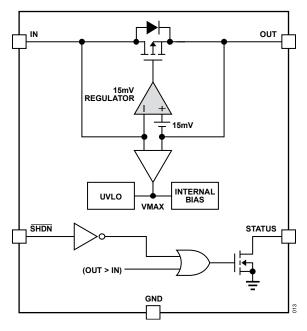

#### **BLOCK DIAGRAM**

Figure 13. Block Diagram

#### THEORY OF OPERATION

The LT4422 is a single positive voltage ideal diode, utilizing a P-channel power MOSFET with a  $R_{ON}$  of 50m $\Omega$ . The IN pins form the anode, while the OUT pins form the cathode and are typically connected in parallel with other diode cathodes in an ORing configuration.

By applying an input power supply to IN, between 1.9V and 28V, a load can be powered at OUT. An internal gate drive amplifier (see *Block Diagram*) attempts to regulate the forward (IN - OUT) voltage drop to 15mV. The MOSFET gate overdrive voltage adjusts to maintain the 15mV drop. At load currents above approximately 300mA, the internal MOSFET is fully on, and the forward voltage drop is governed by the ohmic relationship of  $I_{LOAD}$ .

Typical on-resistance ( $50m\Omega$ ) is achieved when IN  $\geq$  4V. Below IN = 4V, diminishing gate drive causes R<sub>ON</sub> to increase, as shown in the Typical Performance Curves. Operating with high R<sub>ON</sub> and high currents will cause large forward drops and temperature rise.

If the OUT voltage exceeds the IN voltage by approximately 20mV, the internal power MOSFET turns off quickly through a fast comparator, disabling the low dropout power path.

The LT4422 is placed in shutdown mode by driving SHDN low. In shutdown, the device consumes very little quiescent current (typically less than 500nA). It is important to note that the SHDN input, while disabling the LT4422 and reducing its current consumption, does not disconnect the load from the input since the internal MOSFET's body diode is ever-present. External MOSFETs may be added to configure load-switching applications.

STATUS is an open drain output intended to indicate power path conditions. STATUS is designed for connection to a power supply through a pull-up resistor. STATUS pulls low whenever the internal power path is disabled. STATUS may pull low for the following reasons. First, driving SHDN low pulls STATUS low. Second, when the power path is reverse biased (the OUT voltage exceeds the IN voltage by at approximately 20mV), STATUS also pulls low. When the power path is enabled, the STATUS pull-down is removed.

analog.com Rev. 0 8 of 18

#### APPLICATIONS INFORMATION

The LT4422 is intended for power path control applications, including diode ORing of multiple power supplies, load sharing between multiple batteries or power sources, automatic switch-over from a primary to an auxiliary power source, and charging multiple batteries from a single charger.

## **USB PD 3.0 and Back-Up Battery Supply**

The front-page schematic demonstrates the LT4422 in an application with USB PD (Power Delivery) 3.0 along with a backup Lithium-Ion battery cell. The input voltage from the USB 3.0 connector can range from 5V to 20V, all easily handled by the LT4422. On the other hand, the single lithium-ion cell can be at 3V to 3.6V, which is also easily handled by the LT4422. The common output automatically biases to the higher of the two input voltages.

The configuration of STATUS in this application allows the LED to indicate that the USB power path is active, ensuring that the higher power consumption associated with the LED occurs when the USB power source is present. Even if the USB power source is disconnected without a  $\overline{SHDN}$  control signal coming first, the application seamlessly switches to the backup power source. Note that the LED and STATUS functions are optional and easily removed for simplicity by leaving STATUS open.

The LT4422 SHDN rising threshold is 1.6V (maximum). To obtain the fastest turn-on response time, it is recommended that SHDN swing to at least the minimum device operating voltage of 1.9V for strong overdrive of the SHDN threshold. To obtain the fastest turn-off of the power path, pulling SHDN well below the minimum 1V threshold (or close to GND) is also recommended. SHDN should never be left open. If logical on/off control is not required, automatic turn-on is achieved by connecting SHDN to IN.

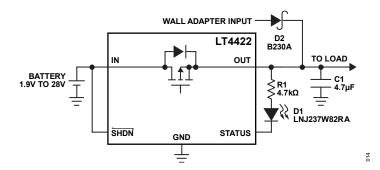

### **Automatic Power Path Control**

The automatic switchover from a battery to a wall adapter or other power source is shown in *Figure 14*. Initially, with only the battery applied, the load is powered purely through the LT4422 from the battery. If the wall adapter is applied and is greater than the battery voltage, the OUT voltage rises above the IN voltage. The LT4422 senses this increase, disables the IN to OUT connection, and electrically isolates the battery from the power path. Only the wall adapter powers the load, and the battery remains protected.

With STATUS connected, as shown in *Figure 14*, the LED indicator turns on with the wall adapter present. When the wall adapter is not present and the battery powers the load, STATUS pulls high, and the LED indicator turns off. This configuration allows the higher power consumption of the LED to be supplied by the wall adapter when it is connected.

Figure 14. Automatic Switchover of Load Between a Battery and a Wall Adapter

analog.com Rev. 0 9 of 18

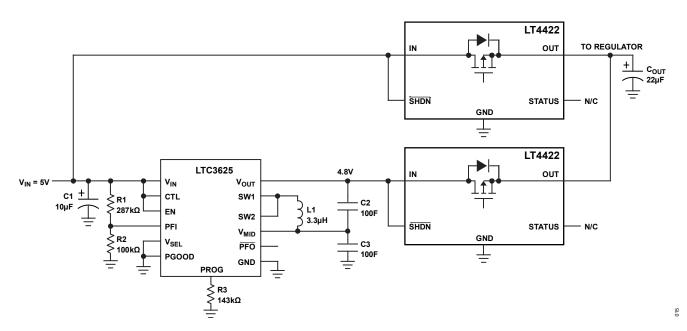

## **5V Power Ride-Through**

In a diode-OR configuration, multiple diode cathodes are connected in parallel, with the final output voltage set by the highest cathode potential. The LT4422 is well suited for these applications, with its ability to disable the power path whenever OUT exceeds IN by approximately 20mV or more, allowing no more than  $1\mu$ A of reverse current. The low reverse leakage and the ability to stand-off 28V and turn off under reverse bias make the LT4422 a high-performance diode replacement.

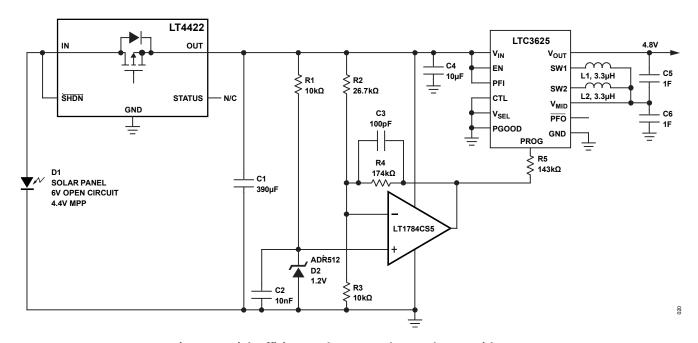

Figure 15 demonstrates a diode-OR application with a super-cap charger to provide load power ride-through in the event of input power loss. The LTC3625 charges two supercapacitors to a sum of 4.8V. Two LT4422s form a diode-OR circuit between the main 5V input and the supercapacitor 4.8V output. The cathodes of the LT4422s connect to a load or a downstream voltage regulator. If the main 5V supply is operating, load power is delivered from the 5V supply. Should the main 5V supply be removed, the 4.8V path turns on, and load power is derived from the supercapacitors.

Figure 15. Riding through Loss of Primary Power Supply

analog.com Rev. 0 | 10 of 18

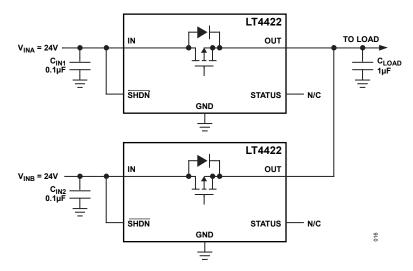

## **High-Voltage Diode-OR**

The outputs of two or more LT4422s can be combined for redundancy or for droop sharing as shown in Figure 16.

Figure 16. High Voltage Diode-OR

## **Layout and Thermal Considerations**

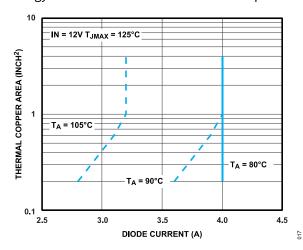

The following advice should be considered when laying out a printed circuit board (PCB) for the LT4422. First, connect the exposed pad (also connected to IN) to a sufficiently large copper plane for thermal relief. Use *Figure 17* to find the minimum copper area (connected to IN) required to limit junction temperature for a given load current and ambient temperature.

PCB traces to the IN and OUT pins should be wide and short to minimize series resistance and inductance. *Figure 18* demonstrates a copper layout strategy for effective thermal and electrical performance.

Figure 17. Minimum Thermal Copper vs Load Current and Ambient Temperature

analog.com Rev. 0 | 11 of 18

Figure 18. PCB Layout Strategy for Thermal Management

#### TYPICAL APPLICATION

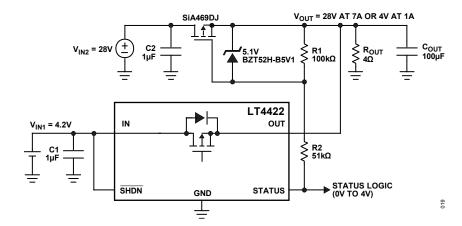

## **High-Load Current Application**

Some applications may require a power path that exceeds the 4A capability of the LT4422. The STATUS output may be used to enable an alternate power path. For example, consider the application as shown in *Figure 19*. The LT4422 provides an automatic power path from the battery input to the  $4\Omega$  load when the 28V supply is absent. When the 28V supply  $(V_{IN2})$  becomes available,  $V_{OUT}$  begins to charge through the MOSFET body diode, and the LT4422 shuts off due to the reverse bias from  $V_{OUT}$  to  $V_{IN1}$ . STATUS pulls low, allowing the P-channel MOSFET to turn on and providing a low-loss power path to the load.

Without protection components, the P-channel MOSFET  $V_{GS}$  could see 28V, which would be beyond the MOSFET absolute maximum rating. The zener diode limits the maximum  $V_{GS}$  on the MOSFET to 5.1V. R1 provides a discharge path for the MOSFET gate charge and a pull-up path for the STATUS output when the MOSFET is off.

Figure 19. Using an External MOSFET for Switching to High Current Loads

analog.com Rev. 0 | 12 of 18

If a logic-level STATUS voltage is required, R2 may be added to limit the voltage swing at the STATUS pin. When the LT4422 power path is on, STATUS pulls up to the battery voltage. When the LT4422 power path is off and R2 is not present, STATUS pulls to 4 or 5V ( $V_z$ ) below the 28V supply. With R2 in place, the STATUS pull-down current causes a voltage drop on R2, allowing the STATUS output to pull near ground. The pull-down current (28V -  $V_z$ )/R2 is shared between R1 and the zener diode.

Figure 20. High-Efficiency Solar Powered SCAP Charger with MPPT

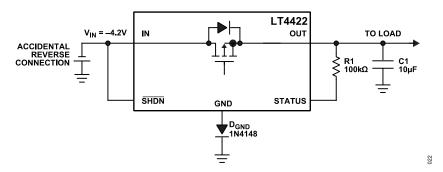

## **Reverse Input Voltage Protection**

Some applications must tolerate momentary accidental reversed voltage connections or negative voltage transients at the IN pin. Although the IN pin absolute maximum rating is limited to -0.3V. *Figure 21* and *Figure 22* demonstrate how a resistor or simple diode may be added to permit reverse input voltage tolerance.

Under reverse input voltage, an internal substrate diode is turned on and its current must be limited to below 100mA. In *Figure 21*, a  $100\Omega$  ¼-watt resistor (R<sub>GND</sub>) is added to the ground path, safely limiting internal power dissipation under the reverse connection of the 4.2V battery.

Figure 21. Protecting against Reverse Input Voltage with a Resistor

analog.com Rev. 0 | 13 of 18

Placing the protection resistor in the ground path preserves the low IN to OUT power path resistance. Minor drawbacks to using the protection resistor include a small increase in STATUS  $V_{OL}$  and minor shift in  $\overline{SHDN}$  threshold, both dependent on the current in the STATUS pull-down path.

In the case of persistent reverse voltage, a simple diode ( $D_{GND}$ ) may be used in place of the ground resistor, as shown in *Figure 22*. Using a diode removes power dissipation concerns at the expense of increased STATUS  $V_{OL}$ , a shift in SHDN threshold and increase in minimum IN voltage by an amount equal to the diode drop voltage in the ground path.

Figure 22. Protecting against Reverse Input Voltage with a Diode

analog.com Rev. 0 | 14 of 18

# **RELATED PARTS**

| PART NUMBER    | DESCRIPTION                                                              | COMMENTS                                                             |  |  |

|----------------|--------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|

| LTC4411        | 2.6A Ideal Diode, Internal N-Channel MOSFET                              | 2.6V to 5.5V Operation                                               |  |  |

| LTC4413        | 2.6A Dual Ideal Diode, Internal P-Channel<br>MOSFET                      | 1.7V to 5.5V Operation                                               |  |  |

| LTC4415        | 4A Dual Ideal Diode, Internal P-Channel<br>MOSFET                        | 2.6V to 5.5V Operation                                               |  |  |

| <u>LT4423</u>  | 2A Ideal Diode, Internal P-Channel MOSFETS                               | 1.9V to 28V Operation, Reverse Input and<br>Output Protection        |  |  |

| LTC4358        | 5A Ideal Diode, Internal N-Channel MOSFET                                | 9V to 26.5V Operation, Reverse Input<br>Protection                   |  |  |

| LTC4376        | 7A Ideal Diode, Internal N-Channel MOSFET                                | 4V to 40V Operation, Reverse Input<br>Protection                     |  |  |

| LTC4352        | Low Voltage Ideal Diode Controller with Monitoring                       | Controls N-Channel MOSFET, 0V to 18V<br>Operation                    |  |  |

| <u>LTC4359</u> | Ideal Diode Controller With Reverse Input<br>Protection                  | 4V to 80V Operation, -40V Input<br>Protection, 150μΑ I <sub>Q</sub>  |  |  |

| <u>LTC4370</u> | Two-Supply Diode-Or Current Balancing<br>Controller                      | Simple Redundant Supply Current<br>Sharing, 0V to 18V Operation      |  |  |

| <u>LTC4353</u> | Dual Low Voltage Ideal Diode Controller                                  | Controls Two N-Channel MOSFETs, 0V to 18V Operation                  |  |  |

| <u>LTC4371</u> | Dual Negative Voltage Ideal Diode-Or<br>Controller And Monitor           | Controls Two MOSFETs, 220ns Turn-Off, Withstands > ±300V Transients  |  |  |

| <u>LTC4355</u> | Positive High Voltage Ideal Diode-Or With Input Supply And Fuse Monitors | Dual N-channel, 9V to 80V                                            |  |  |

| LTC4417        | Prioritized Powerpath Controller                                         | 2.5V to 36V Operation; Ext P-Channel MOSFET; -42V Reverse Protection |  |  |

| LTC4418        | Dual Channel Prioritized Powerpath<br>Controller                         | 2.5V to 40V Operation; Ext P-Channel MOSFET; -42V Reverse Protection |  |  |

| LTC4419        | 18V Dual Input Micropower Powerpath<br>Prioritizer                       | rpath 1.8V to 18V Operation; 0.5A Switches;<br>Freshness Seal        |  |  |

| LTC4421        | High Power Prioritized Powerpath Controller                              | 0V to 18V Operation, 60V Tolerant                                    |  |  |

| <u>LTC4450</u> | 18V, 12A Ideal Diode                                                     | Internal N-Channel MOSFET                                            |  |  |

| <u>LTC4451</u> | 40V, 7A Ideal Diode                                                      | Internal N-Channel MOSFET                                            |  |  |

**analog.com** Rev. 0 | 15 of 18

LT4422

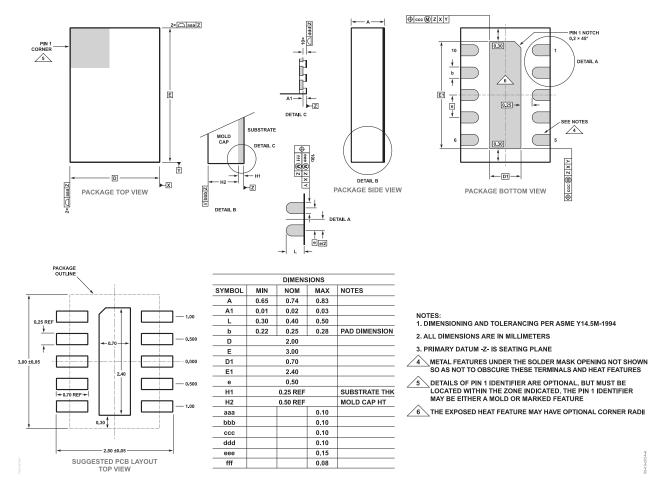

## **OUTLINE DIMENSIONS**

#### LDFN Package 10-Lead (3mm × 2mm × 0.75mm) (Reference DWG # 05-08-1686)

Figure 23. 10-Lead Plastic LDFN

analog.com Rev. 0 | 16 of 18

LT4422

## **ORDERING GUIDE**

## **Table 4. Ordering Guide**

| TAPE AND REEL* | PART MARKING | PACKAGE DESCRIPTION                  | TEMPERATURE RANGE |

|----------------|--------------|--------------------------------------|-------------------|

| LT4422AV#TRPBF | LHKY         | 10-Lead LDFN<br>(3mm x 2mm x 0.75mm) | -40°C to 125°C    |

<sup>\*</sup>For more information on tape and reel specifications, refer to the *Tape and Reel Specifications*. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix

analog.com Rev. 0 17 of 18

ALL INFORMATION CONTAINED HEREIN IS PROVIDED "AS IS" WITHOUT REPRESENTATION OR WARRANTY. NO RESPONSIBILITY IS ASSUMED BY ANALOG DEVICES FOR ITS USE, NOR FOR ANY INFRINGEMENTS OF PATENTS OR OTHER RIGHTS OF THIRD PARTIES THAT MAY RESULT FROM ITS USE. SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. NO LICENCE, EITHER EXPRESSED OR IMPLIED, IS GRANTED UNDER ANY ADI PATENT RIGHT, COPYRIGHT, MASK WORK RIGHT, OR ANY OTHER ADI INTELLECTUAL PROPERTY RIGHT RELATING TO ANY COMBINATION, MACHINE, OR PROCESS WHICH ADI PRODUCTS OR SERVICES ARE USED. TRADEMARKS AND REGISTERED TRADEMARKS ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS. ALL ANALOG DEVICES PRODUCTS CONTAINED HEREIN ARE SUBJECT TO RELEASE AND AVAILABILITY.

analog.com Rev. 0 | 18 of 18