# **AK8448**

6-Channel Linear Sensor compatible

10 Bit 40 MSPS x 3 Analog Pre-Processor

#### **Features**

Maximum Processing Speed

In CDS mode and Clamp mode

1ch, 2ch and 3ch mode: 40M samples/sec per channel 4ch and 6ch mode: 20M sample/sec per channel

In DC Direct-coupled mode

1ch, 2ch and 3ch mode:15M sample/sec per channel4ch and 6ch mode:15M sample/sec per channel

☐ Maximum Input Level: 1.35Vpp (typ.)@CDS mode and DC connection mode

1.19Vpp (typ.)@Clamp mode

☐ Compatible with both CCD and CIS Signal Polarities

☐ Simultaneously Sampling 6-Channel CDS circuits (Correlated Double Sampling)

☐ Offset DACs: Adjustable Range : ±298.7 mV (typ.), Independent 6-channel 8 Bit DACs

□ PGA: Adjustable Gain Range : 0 dB ~ 18.75 dB (typ.) Independently adjustable 6-channel 8 Bit PGAs.

Linearity: DNL = -1LSB (min.), +1LSB (max.) with guaranteed no missing code.

☐ 5 bit Output Bus: Enables to output 10 Bit Data in 5 Bit x 2 cycles

☐ 4-Wire Serial Interface

$\square$  Supply: 3.3V±0.3V

☐ Power Dissipation: 627mW(typ.)@6ch mode, at 20M samples/sec per channel

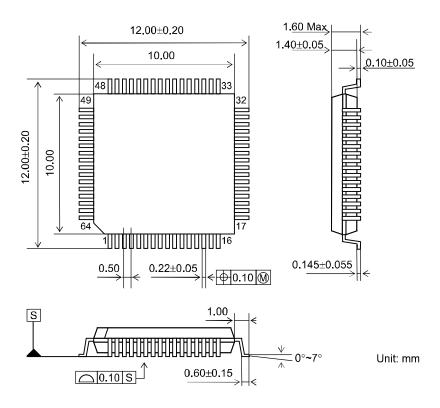

☐ Package: 64 Pin LQFP, Pin pitch 0.5 mm, Mold size 10 mm x 10 mm

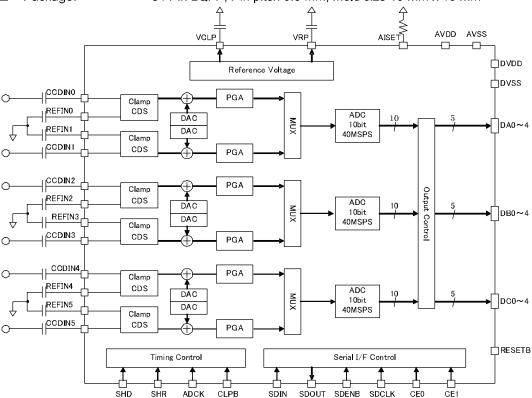

# **Functional Description of Each Block** Clamp / CDS Sensor Interface Circuit It samples the Image signal level from the sensor. The AK8448 has 3 sampling modes - CDS mode, Clamp mode and DC direct-coupled mode. There are 5 ,number of channel select modes - 1, 2, 3, 4 and 6 channels. Channel(s) to be used is selected by the number of channel mode. CDS circuits, DACs, PGAs and ADCs of the un-used channels are automatically powered-down. □ DAC Offset addition D/A converter This is a D/A converter to generate an offset voltage which is added to the sampled signal level at the Sensor Interface part. Voltage range of DAC is ±298.7mV (typ.) and its resolution is 8 Bit. An independent offset voltage can be set to each channel by register setting. ☐ PGA ( Programmable Gain Amplifier ) This is a programmable Gain amplifier to adjust signal amplitude of each channel. Adjustable range is from 0 dB to 18.75 dB (typ.), and its resolution is 8 Bit. An independent gain can be set to each channel by register setting. ☐ MUX Channel Multiplexer This is an Analog Switch to input in the time-division-multiplexed fashion the simultaneously-sampled 2 channel signals to an ADC, in 4 channel mode and 6 channel mode. In 4 channel mode and 6 channel mode, 10 Bit ADCs process dual channels in time-divisionmultiplexed method. ☐ ADC A/D Converter This is a 10 Bit, 40 MSPS A/D converter to convert an Image signal level into digital data after offset adjustment and gain adjustment are made. There are 3 ADCs and 2 channels are connected to each ADC through a channel multiplexer. ☐ Output Control ADC Output Data Control Digital circuit to control the Output Form of ADC data. ADC data can be output in either 5 Bit-wide or 10 Bit-wide by register setting. In case of 5 Bit-wide data operation, the upper 5 Bit of the ADC data is output at the rising edge of ACDK clock, and the lower 5 Bit data ,at the falling edge of ADCK.

ACDK clock, and the lower 5 Bit data ,at the falling edge of ADCK.

In case of 10 Bit-wide data operation, ADC data from two different data channels are output at

In case of 10 Bit-wide data operation, ADC data from two different data channels are output at the rising edge and at the falling edge of ADCK respectively.

It is also possible to output ADC data at only the falling edge of ADCK clock by register setting in 10 Bit-wide data operation.

| ASAHI KASEI        |                   | [AK8448]                                                                                                                    |

|--------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Circuit to gener   | ate internal Cla  | rence Voltage Generation Circuit mp level VCLP, Analog Common Level VCOM, ADC Reference Reference Voltages DAREFP & DAREFN. |

| ☐ Timing Con       | trol Timir        | ng Generating Circuit                                                                                                       |

| Digital circuit to | generate intern   | al timing pulses from those input clocks, ADCK, SHR, SHD and                                                                |

| CLPB.              |                   |                                                                                                                             |

| ADCK is a clock    | which is used     | for ADC operation and for operation of ADC Output Data Control                                                              |

| part.              |                   |                                                                                                                             |

| SHR is a timing    | pulse which is u  | sed to sample Reference level of Sensor signal.                                                                             |

| SHD is a timing    | pulse which is u  | sed to sample Data level of Sensor signal.                                                                                  |

| CLPB is a timing   | pulse to show     | Clamp period.                                                                                                               |

| ☐ Serial I/F C     | ontrol Coric      | N Pagistar Interface Circuit                                                                                                |

|                    |                   | al Register Interface Circuit                                                                                               |

|                    |                   | at the Control registers.                                                                                                   |

| Control registers  | s also can be rea | ad out.                                                                                                                     |

| By assigning sp    | ecific address to | individual devices by chip enable pins CE0 and CE1, up to 4.                                                                |

| AK8448 devices     | can be connect    | ted on the same, 4-wires.                                                                                                   |

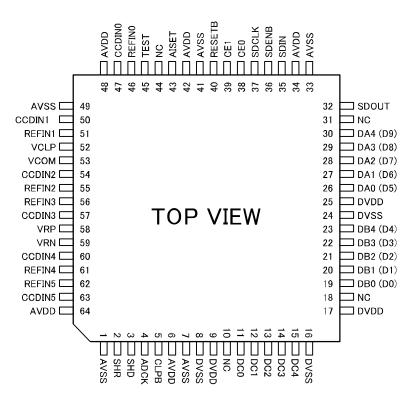

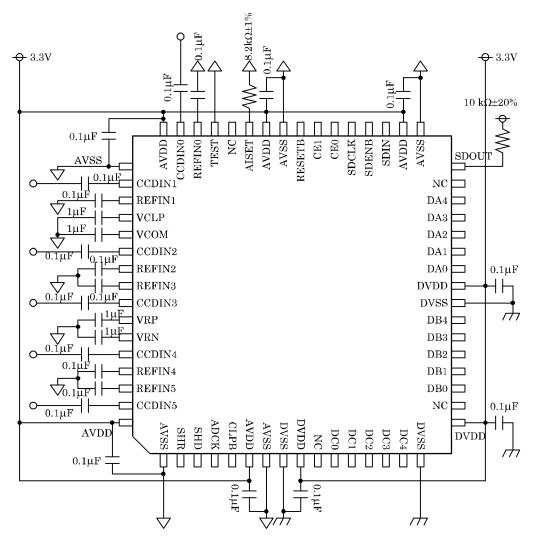

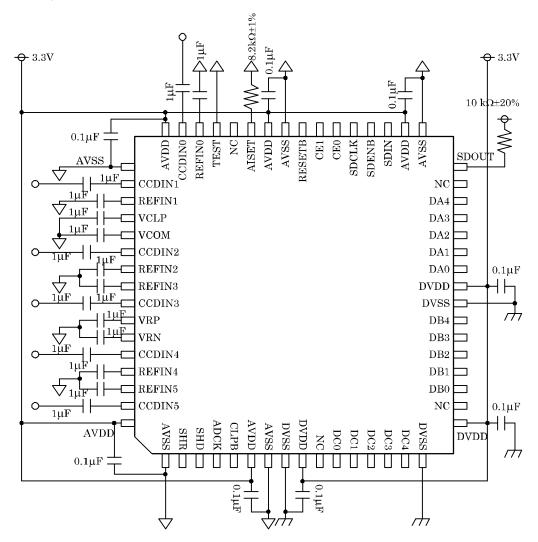

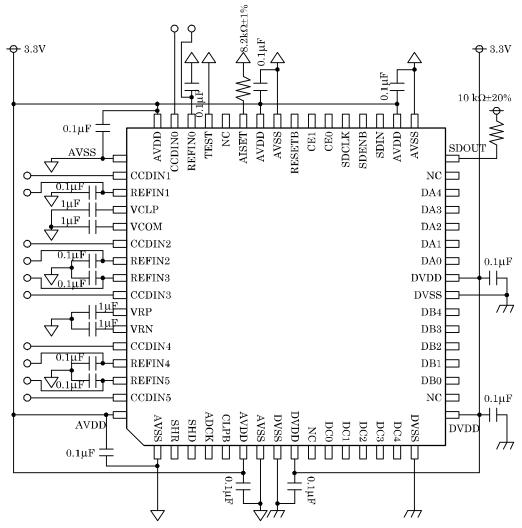

### **Pin Assignment**

Pin Layout

# **Pin Function**

| No. | Name     | Туре | Description                                                              |  |  |  |  |  |

|-----|----------|------|--------------------------------------------------------------------------|--|--|--|--|--|

| 1   | AVSS     | PWR  | Analog ground                                                            |  |  |  |  |  |

| 2   | SHR      | I    | Reference level sampling pulse input                                     |  |  |  |  |  |

| 3   | SHD      | I    | Data level sampling pulse input                                          |  |  |  |  |  |

| 4   | ADCK     | I    | ADC sampling clock input                                                 |  |  |  |  |  |

| 5   | CLPB     | ı    | Clamp control input Low : Clamp operation "ON"                           |  |  |  |  |  |

|     |          |      | High : Clamp operation "OFF"                                             |  |  |  |  |  |

|     |          |      | This should be fixed to Low during CDS mode                              |  |  |  |  |  |

| 6   | AVDD     | PWR  | Analog power supply                                                      |  |  |  |  |  |

| 7   | AVSS     | PWR  | Analog ground                                                            |  |  |  |  |  |

| 8   | DVSS     | PWR  | Digital ground                                                           |  |  |  |  |  |

| 9   | DVDD     | PWR  | Digital power supply                                                     |  |  |  |  |  |

| 10  | NC       |      | left open or should be connected to VSS                                  |  |  |  |  |  |

| 11  | DC0      | 0    | ADC output in a straight binary code( DC0 : LSB side , DC4 : MSB         |  |  |  |  |  |

| 12  | DC1      | 0    | side )                                                                   |  |  |  |  |  |

| 13  | DC2      | 0    | In 5 Bit-wide output operation in 3-channel and 6 channel modes,         |  |  |  |  |  |

| 14  | DC3      | 0    | Data output corresponds to CCDIN4 and CCDIN5.                            |  |  |  |  |  |

| 15  | DC4      | 0    | In 10 Bit-wide output operation and in 5 Bit-wide output operation in 1  |  |  |  |  |  |

|     |          |      | channel, 2 channel and 4 channel modes, these outputs are not            |  |  |  |  |  |

|     |          |      | used. When these modes are selected, low level is output in normal       |  |  |  |  |  |

|     |          |      | operation and either low level or high-Z output is programmable in       |  |  |  |  |  |

|     |          |      | power-down mode by register setting.                                     |  |  |  |  |  |

| 16  | DVSS     | PWR  | Digital ground                                                           |  |  |  |  |  |

| 17  | DVDD     | PWR  | Digital power supply                                                     |  |  |  |  |  |

| 18  | NC       |      | left open or should be connected to AVSS                                 |  |  |  |  |  |

| 19  | DB0 (D0) | 0    | ADC output in a straight binary code.                                    |  |  |  |  |  |

| 20  | DB1 (D1) | 0    | Signal name with parenthesis means a signal name in 10 Bit-wide          |  |  |  |  |  |

| 21  | DB2 (D2) | 0    | output operation (in 5 Bit-wide output operation, DB0 : LSB side, DB4 :  |  |  |  |  |  |

| 22  | DB3 (D3) | 0    | MSB side and in 10 Bit-wide output operation, D0 : LSB ).                |  |  |  |  |  |

| 23  | DB4 (D4) | 0    | When in 5 Bit-wide output operation in 1 channel mode, these outputs     |  |  |  |  |  |

|     |          |      | are not used. They become low level output in normal operation and       |  |  |  |  |  |

|     |          |      | either low level or high-Z output is programmable by register setting in |  |  |  |  |  |

|     |          |      | power-down mode.                                                         |  |  |  |  |  |

| 24  | DVSS     | PWR  | Digital ground                                                           |  |  |  |  |  |

| 25  | DVDD     | PWR  | Digital power supply                                                     |  |  |  |  |  |

| No. | Name     | Туре | Description                                                              |  |  |  |  |  |  |

|-----|----------|------|--------------------------------------------------------------------------|--|--|--|--|--|--|

| 26  | DA0 (D5) | 0    | ADC output in a straight binary code.                                    |  |  |  |  |  |  |

| 27  | DA1 (D6) | 0    | Signal name with parenthesis means a signal name in 10 Bit-wide          |  |  |  |  |  |  |

| 28  | DA2 (D7) | 0    | output operation ( in 5 Bit-wide output operation, DA0 : LSB side, DA4 : |  |  |  |  |  |  |

| 29  | DA3 (D8) | 0    | MSB side and in 10 Bit-wide output operation, D9 : MSB ).                |  |  |  |  |  |  |

| 30  | DA4 (D9) | 0    |                                                                          |  |  |  |  |  |  |

| 31  | NC       |      | left open or should be connected to AVSS.                                |  |  |  |  |  |  |

| 32  | SDOUT    | 0    | Serial I/F Data output, Pull up or pull down please.                     |  |  |  |  |  |  |

| 33  | AVSS     | PWR  | Analog ground                                                            |  |  |  |  |  |  |

| 34  | AVDD     | PWR  | Analog power supply                                                      |  |  |  |  |  |  |

| 35  | SDIN     | 1    | Serial I/F Data input                                                    |  |  |  |  |  |  |

| 36  | SDENB    | 1    | Serial I/F Data enable                                                   |  |  |  |  |  |  |

| 37  | SDCLK    | 1    | Serial I/F clock                                                         |  |  |  |  |  |  |

| 38  | CE0      | ı    | Chip Enable                                                              |  |  |  |  |  |  |

| 39  | CE1      | 1    |                                                                          |  |  |  |  |  |  |

| 40  | RESETB   | 1    | Reset                                                                    |  |  |  |  |  |  |

|     |          |      |                                                                          |  |  |  |  |  |  |

| 41  | AVSS     | PWR  | Analog ground                                                            |  |  |  |  |  |  |

| 42  | AVDD     | PWR  | Analog power supply                                                      |  |  |  |  |  |  |

| 43  | AISET    | 1    | Internal Bias current                                                    |  |  |  |  |  |  |

|     |          |      | Connect a 8.2Kohm resistor between AVSS and this pin.                    |  |  |  |  |  |  |

| 44  | NC       |      | left open or should be connected to AVSS.                                |  |  |  |  |  |  |

| 45  | TEST     | 1    | For test , connect to AVSS.                                              |  |  |  |  |  |  |

| 46  | REFIN0   | 1    | Reference input                                                          |  |  |  |  |  |  |

|     |          |      | Connect a same value capacitor as CCDIN0 input capacitor between         |  |  |  |  |  |  |

|     |          |      | AVSS and this pin. In DC direct-coupled mode, an externally-fed signal   |  |  |  |  |  |  |

|     |          |      | reference level should be input.                                         |  |  |  |  |  |  |

| 47  | CCDIN0   | 1    | Sensor signal input                                                      |  |  |  |  |  |  |

| 48  | AVDD     | PWR  | Analog power supply                                                      |  |  |  |  |  |  |

| 49  | AVSS     | PWR  | Analog ground                                                            |  |  |  |  |  |  |

| 50  | CCDIN1   | 1    | Sensor signal input                                                      |  |  |  |  |  |  |

| 51  | REFIN1   | 1    | Reference input                                                          |  |  |  |  |  |  |

|     |          |      | Connect a same value capacitor as CCDIN1 input capacitor between         |  |  |  |  |  |  |

|     |          |      | AVSS and this pin.                                                       |  |  |  |  |  |  |

|     |          |      | In DC direct-coupled mode, an externally-fed signal reference level      |  |  |  |  |  |  |

|     |          |      | should be input.                                                         |  |  |  |  |  |  |

| 52  | VCLP     | 0    | Clamp level output                                                       |  |  |  |  |  |  |

|     |          |      | Connect a stabilizing capacitor between AVSS and this pin.               |  |  |  |  |  |  |

| No. | Name   | Туре | Description                                                         |

|-----|--------|------|---------------------------------------------------------------------|

| 53  | VCOM   | 0    | Internal Reference voltage                                          |

|     |        |      | Connect a stabilizing capacitor between AVSS and this pin           |

| 54  | CCDIN2 | 1    | Sensor signal input                                                 |

| 55  | REFIN2 | 1    | Reference input                                                     |

|     |        |      | Connect a same value capacitor as CCDIN2 input capacitor between    |

|     |        |      | AVSS and this pin.                                                  |

|     |        |      | In DC direct-coupled mode, an externally-fed signal reference level |

|     |        |      | should be input.                                                    |

| 56  | REFIN3 | 1    | Reference input                                                     |

|     |        |      | Connect a same value capacitor as CCDIN3 input capacitor between    |

|     |        |      | AVSS and this pin.                                                  |

|     |        |      | IN DC direct-coupled mode, an externally-fed signal reference level |

|     |        |      | should be input.                                                    |

| 57  | CCDIN3 | 1    | Sensor signal input                                                 |

| 58  | VRP    | 0    | ADC reference voltage positive side                                 |

|     |        |      | Connect a stabilizing capacitor between AVSS and this pin.          |

| 59  | VRN    | 0    | ADC reference voltage negative side                                 |

|     |        |      | Connect a stabilizing capacitor between AVSS and this pin.          |

| 60  | CCDIN4 | 1    | Sensor signal input                                                 |

| 61  | REFIN4 | 1    | Reference input                                                     |

|     |        |      | Connect a same value capacitor as CCDIN4 input capacitor between    |

|     |        |      | AVSS and this pin.                                                  |

|     |        |      | In DC direct-coupled mode, an externally-fed signal reference level |

|     |        |      | should be input.                                                    |

| 62  | REFIN5 | 1    | Reference input                                                     |

|     |        |      | Connect a same value capacitor as CCDIN5 input capacitor between    |

|     |        |      | AVSS and this pin.                                                  |

|     |        |      | In DC direct-coupled mode, an externally-fed signal reference level |

|     |        |      | should be input.                                                    |

| 63  | CCDIN5 | 1    | Sensor signal input                                                 |

| 64  | AVDD   | PWR  | Analog power supply                                                 |

Type description

I : input pin

O : output pin

PWR: power supply pin

Note ) AVDD is a power supply for Analog part and Digital part.

DVDD is a power supply for the Digital output bufferes.

### **Absolute Maximum Ratings**

AVSS = DVSS = 0 V. All voltages are referenced to ground.

| Parameter             | Symbol | Min. | Max.       | Unit | Notes              |

|-----------------------|--------|------|------------|------|--------------------|

| Power Supplies        | AVDD   | -0.3 | 4.5        | V    |                    |

|                       | DVDD   | -0.3 | 4.5        | V    |                    |

| Input Current         | IIN    | -10  | 10         | A    | Except Supply      |

|                       | IIIN   | -10  | 10         | mA   | Pins               |

| Analog Input Voltage  | VINA   | -0.3 | AVDD+0.3   | V    |                    |

| Digital Input Voltage | A/INII | 0.2  | AVDD 10.2  | V    |                    |

| (Input Pins)          | VINL   | -0.3 | AVDD+0.3   | V    |                    |

| Digital Input Voltage | VONII  | 0.0  | DVDD : 0.2 |      | Restriction on the |

| (Output Pins)         | VONL   | -0.3 | DVDD+0.3   | V    | over input         |

| Storage Temperature   | Tstg   | -65  | 150        | °C   |                    |

Operation under a condition exceeding above limits may cause permanent damage to the device. Normal operation is not guaranteed under the above extreme conditions.

# Recommended Operating Conditions

AVSS = DVSS = 0 V. All voltages are referenced to ground.

| Parameter                                                    | Symbol | Min. | Тур. | Max.     | Unit | Notes |

|--------------------------------------------------------------|--------|------|------|----------|------|-------|

| Power Supplies                                               |        |      |      |          |      |       |

| Analog                                                       | AVDD   | 3.0  | 3.3  | 3.6      | V    |       |

| Output buffer                                                | DVDD   | 3.0  | 3.3  | 3.6      | V    |       |

| REFINn ( n = 0 ~ 5 ) Input voltage at DC direct-coupled mode | VREFIN | 0    |      | AVDD-1.3 | V    |       |

| Ambient Operating<br>Temperature                             | Та     | 0    |      | 70       | °C   |       |

| Case Surface<br>Temperature                                  | Тс     |      |      | 98       | °C   |       |

Operation is guaranteed only when AVDD=DVDD.

Please supply all power (AVDD, DVDD).

(note) CCDIN input voltage can't surpass AVDD.

(note) If Ta is not satisfied, Tc must be satisfied.

# **Electrical Characteristics**

#### ■ DC Characteristics

(AVDD =  $3.0 \sim 3.6 \text{ V}$ , DVDD =  $3.0 \sim 3.6 \text{ V}$ , Ta =  $0 \sim 70 ^{\circ}\text{C}$ )

| Parameter                   | Symbol | Pin    | Min.    | Max.    | Unit     | Notes        |

|-----------------------------|--------|--------|---------|---------|----------|--------------|

| High level input voltage    | VIH    | Note 1 | 0.7AVDD |         | V        |              |

| Low level input voltage     | VIL    | Note 1 |         | 0.3AVDD | ٧        |              |

| High level output voltage 1 | VOH1   | Note 2 | 0.8DVDD |         | >        | IOH= –1mA    |

| Low level output voltage 1  | VOL1   | Note 2 |         | 0.2DVDD | <b>V</b> | IOL= 1mA     |

| High level output voltage 2 | VOH2   | Note 3 | 0.8DVDD |         | >        | IOH= -0.25mA |

| Low level output voltage 2  | VOL2   | Note 3 |         | 0.2DVDD | >        | IOL= 0.25mA  |

| Input leakage current       | ILIKG  | Note 1 | -10     | 10      | μΑ       |              |

| High-Z leakage current      | IOZ    | Note 2 | -10     | 10      | μΑ       |              |

(note 1) SHD, SHR, ADCK, CLPB, SDCLK, SDENB, SDIN, CE0, CE1, RESETB

( note 2 ) DA0 ~ DA4, DB0 ~ DB4, DC0 ~ DC4

(note 3) SDOUT

Downloaded from Arrow.com.

# ■ Analog Characteristics

(AVDD = 3.3 V, DVDD = 3.3 V, Ta = 25 °C, ADCK at 40MHz unless otherwise specified)

| Parameter         | Symbol   | Condition                      | Min.   | Тур.     | Max.   | Unit               |

|-------------------|----------|--------------------------------|--------|----------|--------|--------------------|

|                   |          | Reference Voltage part         |        |          |        |                    |

| Clamp Voltage     | VCLP     | Positive Polarity              | 0.94   | 1.04     | 1.14   | V                  |

|                   |          | Negative Polarity              | 2.15   | 2.3      | 2.45   |                    |

| Common Voltage    | VCOM     |                                | 1.1    | 1.2      | 1.3    | V                  |

| ADC Reference     |          |                                |        |          |        |                    |

| Voltage           |          |                                |        |          |        |                    |

| Positive          | VRP      |                                | 1.5    | 1.6      | 1.7    | V                  |

| Negative          | VRN      |                                | 0.7    | 0.8      | 0.9    |                    |

|                   |          | Clamp / CDS part               |        |          |        |                    |

| Input Range       | VI       | At PGA Gain= 0dB               |        |          |        |                    |

|                   |          | CDS mode                       | 1.20   | 1.35     | 1.50   | Vpp                |

|                   |          | Clamp mode                     | 1.04   | 1.19     | 1.34   |                    |

|                   |          | DC direct-coupled mode         | 1.20   | 1.35     | 1.50   |                    |

| Input Capacitance | CIN      | CCDIN                          |        | 10       |        | pF                 |

| Input Bandwidth   | CBW      | CCDIN~ADC                      |        | 1        |        |                    |

| ( note 1 )        |          | At PGA Gain= 0dB               |        |          |        | pixel              |

| CDS Effect        | CDS      | noise 0.4Vpp 150kHz            |        | -35      |        | dB                 |

|                   |          | signal 0.8Vpp 1MHz             |        |          |        |                    |

|                   | •        | Offset Adjust DAC              |        |          |        |                    |

| Resolution        | DRES     |                                |        |          | 8      | Bit                |

| Range             | DRNG     | Input referred value           | ±252.0 | ±298.7   | ±366.6 | mV                 |

| Differential      | DNL      | Guaranteed monotonicity        | -1.0   |          | +1.5   | LSB                |

| Non-Linearity     |          |                                |        |          |        |                    |

| _                 |          | PGA                            | •      | •        |        |                    |

| Maximum Gain      | GMAX     | CCDIN~ADC                      | 18.25  | 18.75    | 19.25  | dB                 |

|                   |          | Relative value to 0dB          |        |          |        |                    |

| Step Width        | GSTA     | Guaranteed monotonicity        | 0.001  | 0.03     |        | dB                 |

| Otop Width        | 0017     | Sudianteed monotomony          | 0.001  | ~0.26    |        | GD                 |

|                   | <u> </u> | ADC                            |        | 0.20     |        |                    |

| Resolution        | RES      | 1                              |        |          | 10     | bit                |

| Differential      | DNL      | CCDIN~ADC                      | -1.0   |          | +1.0   | LSB                |

| Non-Linearity     | 5.42     | Guaranteed no-missing code     | '      |          |        | LOB                |

|                   | 1        | Noise, Internal Offset, Cross- | talk   | l .      | l      |                    |

| Input Idle State  | NI       | At PGA Gain=0dB                | - CIT  | 0.4      |        | LSB <sub>rms</sub> |

| Noise ( note 2 )  | "        | At PGA Gain=18dB               |        | 1.0      |        | _ODrms             |

| Internal Offset   | VOFST    | At PGA Gain=0dB                | -50    | 0        | 50     | mV                 |

| ( note 3 )        |          | , ter S, t Sain Sub            |        |          |        | 111.0              |

| Cross-Talk        | XTALK1   | ( note 4 )                     |        | ±1       |        | LSB                |

| o.coo rain        | XTALK2   | (note 5)                       | -3     | <u> </u> | +3     |                    |

|                   | J        | 1/                             |        | l        |        |                    |

(AVDD = 3.3 V, DVDD = 3.3 V, Ta = 25 °C, ADCK at 40MHz unless otherwise specified)

| Parameter                             | Symbol              | Condition                                                                                 | Min. | Тур. | Max. | Unit |  |  |

|---------------------------------------|---------------------|-------------------------------------------------------------------------------------------|------|------|------|------|--|--|

|                                       | Current Consumption |                                                                                           |      |      |      |      |  |  |

| Analog Part<br>In Normal<br>Operation |                     | 160                                                                                       | 202  | mA   |      |      |  |  |

| Digital Output ID<br>Part             |                     | 6 channel mode, a full scale<br>minus 2 dB 1 MHz<br>sine-wave input signal,<br>CL = 10 pF |      | 14.5 | 30   | mA   |  |  |

| At Power-Down                         | IPD                 | Analog part + Digital part                                                                |      |      | 0.1  | mA   |  |  |

Characteristics above are when same external components and time-constant are used as shown in the recommended, external circuit configuration examples.

(note 1)

Time till the ADC output settles within +/- 1 LSB of the final value when a full-scale minus 2 dB step signal is input.

(note 2)

Defined as a sigma of ADC output code variations.

(note 3)

It defines that the Offset DAC setting value in no input signal condition exists between Offset DAC setting value of A0h ( equivalent to an input-referred, - 50 mV ) and 60h ( equivalent to an input-referred, + 50 mV ) where ADC output code changes from 000h to 001h.

Since a total adjustable range of Offset Adjust DAC includes this internal Offset adjust range, a practical adjustable range of input signal is reduced by the internal Offset amount.

(note 4)

Definition at ADCK = 40 MHz, A/D conversion rate mode, 6 channels, CDS mode. PGA gain of the channel to be measured is set at its maximum value, all other channels' PGA gains are set at minimum values.

Then measure how much the output code of the target channel to be measured fluctuates when input to the measured channel is fixed and a full-scale minus 1 dB step signal is input on all other channels.

( note 5 )

Definition at ADCK = 10 MHz, A/D conversion rate mode, all channels' PGA gains at minimum values.

Then measure how much the output code of the target channel to be measured fluctuates when input to the measured channel is fixed and a full-scale minus 1 dB step signal is input on all other channels.

■ Switching Characteristics 1 : in ADC conversion rate mode, DC direct-coupled mode

- Timing Diagrams (1) 5 Bit wide, 1 channel, 2 channel, 3 channel modes

- Timing Diagrams (3) 5 Bit wide, 4 channel, 6 channel modes

- Timing Diagrams (5) 10 Bit wide, 1 channel mode

- Timing Diagrams (7) 10 Bit wide, 2 channel mode

- Timing Diagrams (9) 10 Bit wide, 4 channel mode

( AVDD =  $3.0 \sim 3.6 \text{ V}$ , DVDD =  $3.0 \sim 3.6 \text{ V}$ , Ta =  $0 \sim 70 \text{ }^{\circ}\text{C}$ )

| No. | Parameter                  | Pin     | Min. | Тур. | Max. | Unit   | Condition          |

|-----|----------------------------|---------|------|------|------|--------|--------------------|

| 1   | ADCK Cycle Time ( T )      | ADCK    | 33.3 |      | 2000 | ns     | 4, 6ch mode        |

|     |                            |         | 66.6 |      | 2000 |        | 1, 2, 3 ch mode    |

| 2   | ADCK Low Level Width       | ADCK    | 15.0 |      |      | ns     | 4, 6 ch mode       |

|     |                            |         | 31.7 |      |      |        | 1, 2, 3 ch mode    |

| 3   | ADCK High Level Width      | ADCK    | 15.0 |      |      | ns     | 4, 6 ch mode       |

|     |                            |         | 31.7 |      |      |        | 1, 2, 3 ch mode    |

| 4   | ADCK Rise Time             | ADCK    |      |      | 6    | ns     |                    |

| 5   | ADCK Fall Time             | ADCK    |      |      | 6    | ns     |                    |

| 6   | SHD Cycle Time             | SHD     |      | 2T   |      | ns     | 4, 6 ch mode       |

|     |                            |         |      | Т    |      |        | 1, 2, 3 ch mode    |

| 8   | SHD Pulse Width            | SHD     | 12   |      |      | ns     |                    |

| 9   | SHD Set-up Time            | SHD     | 0    |      |      | ns     |                    |

|     | ( time to ADCK to rise )   |         |      |      |      |        |                    |

| 10  | SHD Delay Time             | SHD     | 14   |      |      | ns     |                    |

|     | ( time from ADCK to fall ) |         |      |      |      |        |                    |

| 12  | SHD Aperture Delay         | SHD     |      | 2.5  |      | ns     |                    |

| 13  | Output Data Delay Time     | DA4~DA0 | 1    |      | 9    | ns     | C=10pF             |

|     | ( time from ADCK edge )    | DB4~DB0 |      |      |      |        |                    |

|     |                            | DC4~DC0 |      |      |      |        |                    |

| 14  | Pipe Line Delay            | DA4~DA0 |      | 9    |      | unit:  | 2, 3, 4, 6 ch mode |

|     |                            | DB4~DB0 |      |      |      | # of   | and                |

|     |                            | DC4~DC0 |      |      |      | ADCK   | 1 ch 5 bits Width  |

|     |                            |         |      |      |      | cycles | mode               |

|     |                            |         |      | 8.5  |      |        | 1 ch 10 bits       |

|     |                            |         |      |      |      |        | Width mode         |

| 15  | SHD = " H " inhibit period | SHD     | T+1  |      |      | ns     | 4, 6ch mode        |

|     | ( time till the first ADCK |         |      |      |      |        |                    |

|     | to rise after SHD to fall) |         |      |      |      |        |                    |

■ Switching Characteristics 2 : in ADC conversion rate mode, CDS, Clamp modes

- Timing Diagrams (2) 5 Bit wide,1 channel, 2 channel, 3 channel modes

- Timing Diagrams (4) 5 Bit wide, 4 channel, 6 channel modes

- Timing Diagrams (6) 10 Bit wide, 1 channel mode

- Timing Diagrams (8) 10 Bit wide, 2 channel mode

- Timing Diagrams (10) 10 Bit wide, 4 channel mode

( AVDD =  $3.0 \sim 3.6 \text{ V}$ , DVDD =  $3.0 \sim 3.6 \text{ V}$ , Ta =  $0 \sim 70 \text{ }^{\circ}\text{C}$ )

| No. | Parameter                     | Pin      | Min. | Тур. | Max. | Unit   | Condition         |

|-----|-------------------------------|----------|------|------|------|--------|-------------------|

| 1   | ADCK Cycle Time ( T )         | ADCK     | 25   | •    | 2000 | ns     |                   |

| 2   | ADCK Low Level Width          | ADCK     | 10.9 |      |      | ns     |                   |

| 3   | ADCK High Level Width         | ADCK     | 10.9 |      |      | ns     |                   |

| 4   | ADCK Rise Time                | ADCK     |      |      | 6    | ns     |                   |

| 5   | ADCK Fall Time                | ADCK     |      |      | 6    | ns     |                   |

| 6   | SHR, SHD Cycle Time           | SHR, SHD |      | 2T   |      | ns     | 4, 6ch mode       |

|     |                               |          |      | Т    |      |        | 1, 2, 3ch mode    |

| 7   | SHR Pulse Width               | SHR      | 8    |      |      | ns     |                   |

| 8   | SHD Pulse Width               | SHD      | 8    |      |      | ns     |                   |

| 9   | SHD Set-up Time               | SHD      | 0    |      |      | ns     |                   |

|     | ( time to ADCK to rise )      |          |      |      |      |        |                   |

| 10  | SHD Delay Time                | SHD      | 10   |      |      | ns     |                   |

|     | ( time from ADCK to fall )    |          |      |      |      |        |                   |

| 11  | SHR Aperture Delay            | SHR      |      | 3.0  |      | ns     |                   |

| 12  | SHD Aperture Delay            | SHD      |      | 2.5  |      | ns     |                   |

| 13  | Output Data Delay Time        | DA4~DA0  | 1    |      | 9    | ns     | C=10pF            |

|     | ( time from ADCK edge )       | DB4~DB0  |      |      |      |        |                   |

|     |                               | DC4~DC0  |      |      |      |        |                   |

| 14  | Pipe Line Delay               | DA4~DA0  |      | 9    |      | unit:  | 2, 3, 4, 6ch mode |

|     |                               | DB4~DB0  |      |      |      | # of   | and               |

|     |                               | DC4~DC0  |      |      |      | ADCK   | 1CH 5 bits Width  |

|     |                               |          |      |      |      | cycles | mode              |

|     |                               |          |      | 8.5  |      |        | 1CH 10 bits       |

|     |                               |          |      |      |      |        | Width mode        |

| 15  | SHD = " H " inhibit period    | SHD      | T+1  |      |      | ns     | 4, 6ch mode       |

|     | ( time till the first ADCK to |          |      |      |      |        |                   |

|     | rise after SHD to fall )      |          |      |      |      |        |                   |

■ Switching Characteristics 3 : in total pixel rate mode, DC direct-coupled mode

- Timing Diagrams (11) 10 Bit wide, 2 channel mode

- Timing Diagrams (13) 10 Bit wide, 3 channel mode

- Timing Diagrams (15) 10 Bit wide, 4 channel mode

- Timing Diagrams (17) 10 Bit wide, 6 channel mode

$(AVDD = 3.0 \sim 3.6 \text{ V}, DVDD = 3.0 \sim 3.6 \text{ V}, Ta = 0 \sim 70^{\circ}\text{C})$

| No. | Parameter                                              | Pin                | Min. | Тур. | Max.  | Unit                   | Condition    |

|-----|--------------------------------------------------------|--------------------|------|------|-------|------------------------|--------------|

| 1   | ADCK Cycle Time ( T )                                  | ADCK               | 12.5 |      | 333   | ns                     | 6ch mode     |

|     | , ,                                                    |                    | 16.6 |      | 500   |                        | 4ch mode     |

|     |                                                        |                    | 22.2 |      | 666   |                        | 3ch mode     |

|     |                                                        |                    | 33.3 |      | 1000  |                        | 2ch mode     |

| 2   | ADCK Low Level Width                                   | ADCK               | 4.6  |      |       | ns                     | 6ch mode     |

|     |                                                        |                    | 6.7  |      |       |                        | 4ch mode     |

|     |                                                        |                    | 9.5  |      |       |                        | 3ch mode     |

|     |                                                        |                    | 15.0 |      |       |                        | 2ch mode     |

| 3   | ADCK High Level Width                                  | ADCK               | 4.6  |      |       | ns                     | 6ch mode     |

|     |                                                        |                    | 6.7  |      |       |                        | 4ch mode     |

|     |                                                        |                    | 9.5  |      |       |                        | 3ch mode     |

|     |                                                        |                    | 15.0 |      |       |                        | 2ch mode     |

| 4   | ADCK Rise Time                                         | ADCK               |      |      | 6     | ns                     |              |

| 5   | ADCK Fall Time                                         | ADCK               |      |      | 6     | ns                     |              |

| 6   | SHD Cycle Time                                         | SHD                |      | 6T   |       | ns                     | 6ch mode     |

|     |                                                        |                    |      | 4T   |       |                        | 4ch mode     |

|     |                                                        |                    |      | 3T   |       |                        | 3ch mode     |

|     |                                                        |                    |      | 2T   |       |                        | 2ch mode     |

| 8   | SHD Pulse Width                                        | SHD                | 12   |      |       | ns                     |              |

| 9   | SHD Set-up Time<br>( time to ADCK to rise )            | SHD                | 0    |      | T/2-2 | ns                     |              |

| 10  | SHD Delay Time<br>( note 1 )                           | SHD                | 14   |      |       | ns                     |              |

| 12  | SHD Aperture Delay                                     | SHD                |      | 2.5  |       | ns                     |              |

| 13  | Output Data Delay Time<br>( time from ADCK edge )      | DA4~DA0<br>DB4~DB0 | 1    |      | 9     | ns                     | C=10pF       |

| 14  | Pipe Line Delay                                        | DA4~DA0<br>DB4~DB0 |      | 30   |       | unit:<br># of          | 3ch,6ch mode |

|     |                                                        |                    |      | 20   |       | ADC<br>K<br>cycle<br>s | 2ch,4ch mode |

| 15  | SHD = " H " inhibit period                             | SHD                | 3T+1 |      |       | ns                     | 6ch mode     |

|     | ( time till the first ADCK to rise after SHD to fall ) |                    | 2T+1 |      |       |                        | 4ch mode     |

(note 1)

Time from the ADCK edge where a falling edge of the internal A / D clock is generated.

In 2 channel, 4 channel modes, it is from ADCK to rise.

In 3 channel, 6 channel modes, it is from ADCK to fall.

■ Switching Characteristics 4 : in total pixel rate mode, CDS, Clamp modes

- Timing Diagrams (12) 10 Bit wide, 2 channel mode

- Timing Diagrams (14) 10 Bit wide, 3 channel mode

- Timing Diagrams (16) 10 Bit wide, 4 channel mode

- Timing Diagrams (18) 10 Bit wide, 6 channel mode

$(AVDD = 3.0 \sim 3.6 \text{ V}, DVDD = 3.0 \sim 3.6 \text{ V}, Ta = 0 \sim 70^{\circ}\text{C})$

| No. | Parameter                                              | Pin      | Min. | Тур. | Max.  | Unit  | Condition    |

|-----|--------------------------------------------------------|----------|------|------|-------|-------|--------------|

| 1   | ADCK Cycle Time ( T )                                  | ADCK     | 12.5 |      | 333   | ns    | 6ch mode     |

|     |                                                        |          | 12.5 |      | 500   |       | 4ch mode     |

|     |                                                        |          | 12.5 |      | 666   |       | 3ch mode     |

|     |                                                        |          | 12.5 |      | 1000  |       | 2ch mode     |

| 2   | ADCK Low Level Width                                   | ADCK     | 4.6  |      |       | ns    |              |

| 3   | ADCK High Level Width                                  | ADCK     | 4.6  |      |       | ns    |              |

| 4   | ADCK Rise Time                                         | ADCK     |      |      | 6     | ns    |              |

| 5   | ADCK Fall Time                                         | ADCK     |      |      | 6     | ns    |              |

| 6   | SHR, SHD Cycle Time                                    | SHR, SHD |      | 6T   |       | ns    | 6ch mode     |

|     |                                                        |          |      | 4T   |       |       | 4ch mode     |

|     |                                                        |          |      | 3T   |       |       | 3ch mode     |

|     |                                                        |          |      | 2T   |       |       | 2ch mode     |

| 7   | SHR Pulse Width                                        | SHR      | 8    |      |       | ns    |              |

| 8   | SHD Pulse Width                                        | SHD      | 8    |      |       | ns    |              |

| 9   | SHD Set-up Time                                        | SHD      | 0    |      | T/2-2 | ns    |              |

|     | ( time to ADCK to rise )                               |          |      |      |       |       |              |

| 10  | SHD Delay Time                                         | SHD      | 10   |      |       | ns    |              |

|     | ( note 1 )                                             |          |      |      |       |       |              |

| 11  | SHR Aperture Delay                                     | SHR      |      | 3.0  |       | ns    |              |

| 12  | SHD Aperture Delay                                     | SHD      |      | 2.5  |       | ns    |              |

| 13  | Output Data Delay Time                                 | DA4~DA0  | 1    |      | 9     | ns    | C=10pF       |

|     | ( time from ADCK edge )                                | DB4~DB0  |      |      |       |       |              |

| 14  | Pipe Line Delay                                        | DA4~DA0  |      | 30   |       | unit: | 3ch,6ch mode |

|     |                                                        | DB4~DB0  |      |      |       | # of  |              |

|     |                                                        |          |      | 20   |       | ADC   | 2ch,4ch mode |

|     |                                                        |          |      |      |       | K     |              |

|     |                                                        |          |      |      |       | cycle |              |

|     |                                                        |          |      |      |       | s     |              |

| 15  | SHD = " H " inhibit period                             | SHD      | 3T+1 |      |       | ns    | 6ch mode     |

|     | ( time till the first ADCK to rise after SHD to fall ) |          | 2T+1 |      |       |       | 4ch mode     |

( note 1 )

Time from the ADCK edge where a falling edge of the internal A / D clock is generated.

In 2 channel, 4 channel modes, it is from ADCK to rise.

In 3 channel, 6 channel modes, it is from ADCK to fall.

Timings are specified at the points where specified levels by the DC Characteristics are intersected.

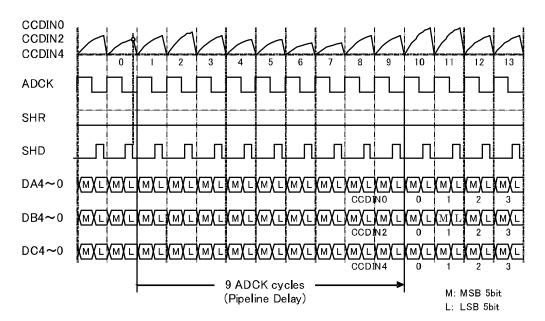

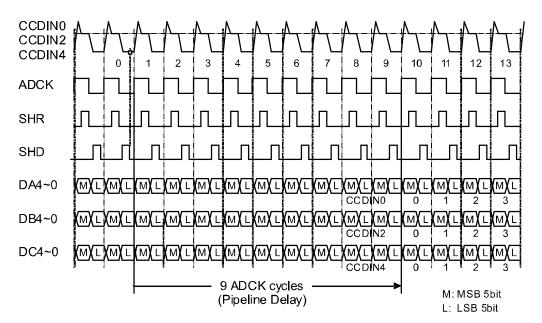

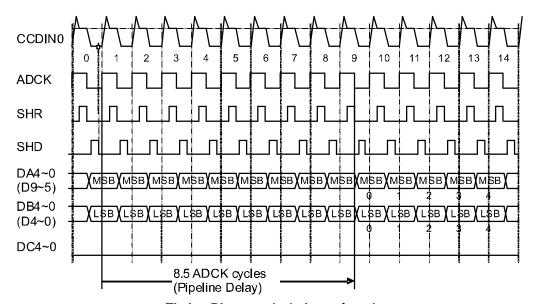

■ Timing Diagrams (1): ADCK frequency = A/D conversion rate mode (5 Bit-wide output)

• 1 channel, 2 channel, 3 channel modes ( DC direct-coupled, positive polarity ) Please refer to Switching Characteristics 1 table.

Timing Diagrams in 1 channel, 2 channel, 3 channel modes

Detailed Timing Diagrams in 1 channel, 2 channel, 3 channel modes

Timings are specified at the points where specified levels by the DC Characteristics are intersected.

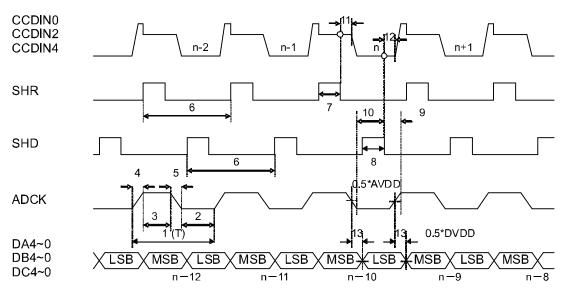

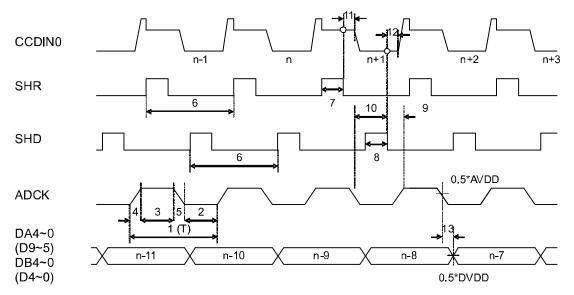

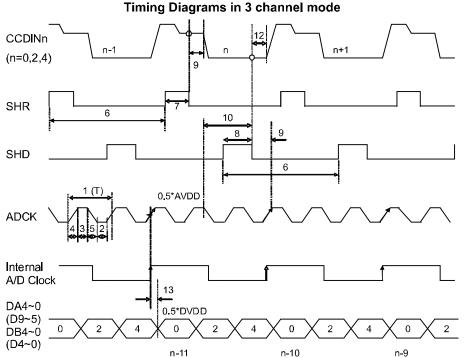

■ Timing Diagrams (2): ADCK frequency = A/D conversion rate mode (5 Bit-wide output)

1 channel, 2 channel, 3 channel modes

( CDS mode & Clamp modes, negative polarity )

Please refer to Switching Characteristics 2 table.

Timing Diagrams in 1 channel, 2 channel, 3 channel modes

Detailed Timing Diagrams in 1 channel, 2 channel, 3 channel modes

Timings are specified at the points where specified levels by the DC Characteristics are intersected.

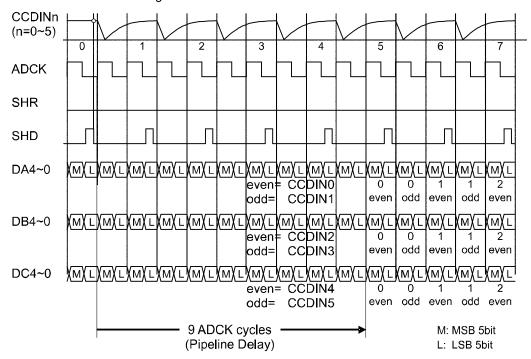

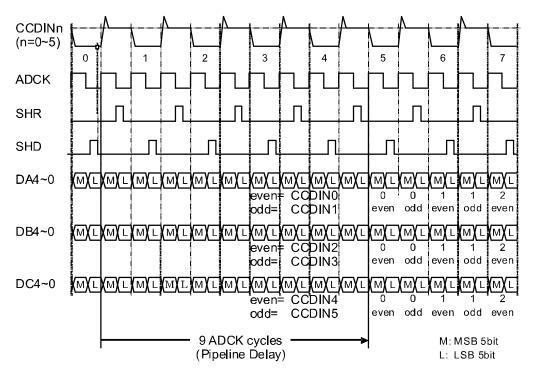

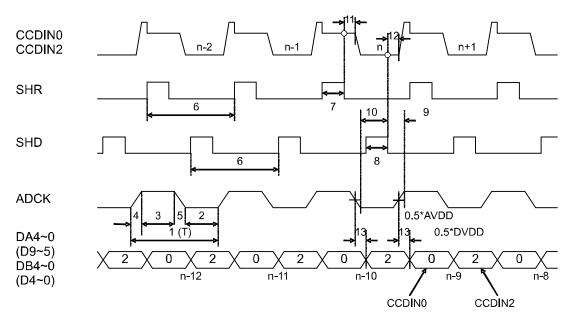

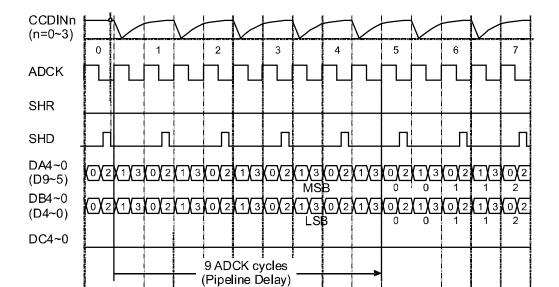

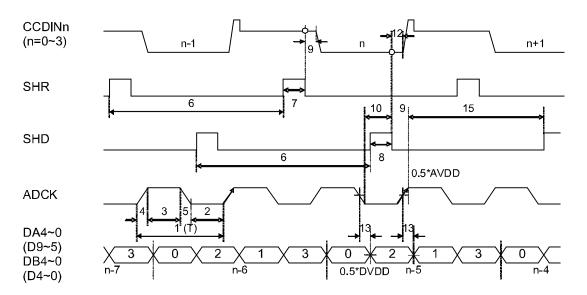

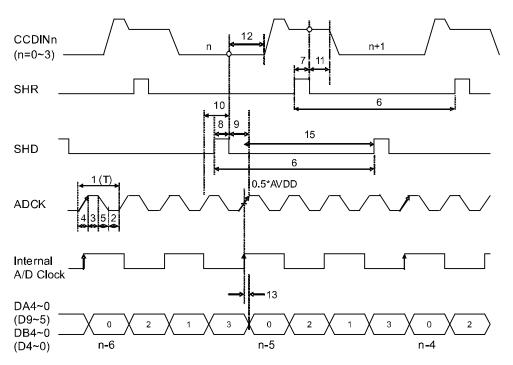

■ Timing Diagrams (3): ADCK frequency = A/D conversion rate ( 5 Bit-wide output )

• 4 channel, 6 channel modes ( DC direct-coupled mode, positive polarity ) Please refer to Switching Characteristics 1 table.

Timing Diagrams in 4 channel, 6 channel modes

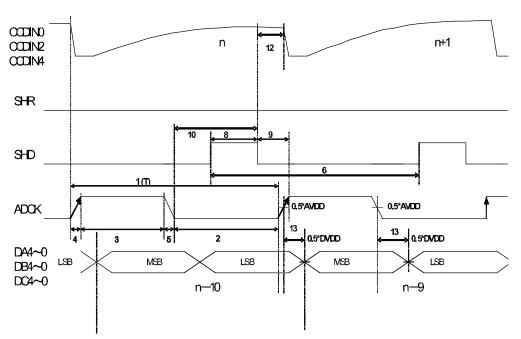

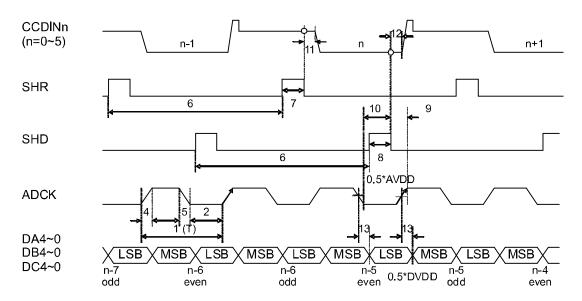

## Detailed Timing Diagrams in 4 channel, 6 channel modes

Timings are specified at the points where specified levels by the DC Characteristics are intersected.

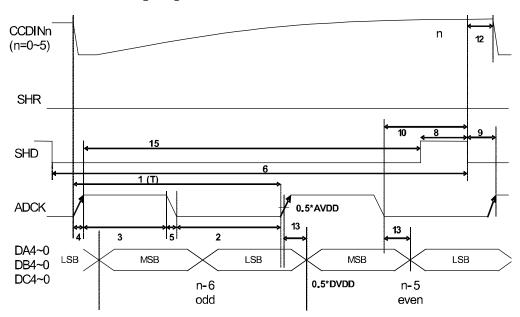

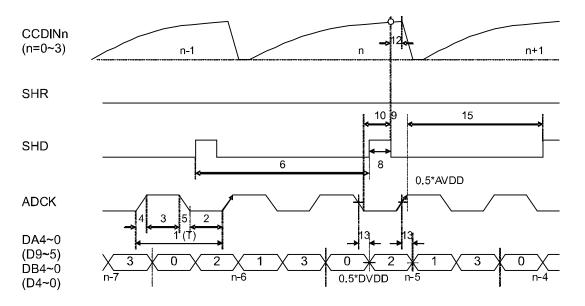

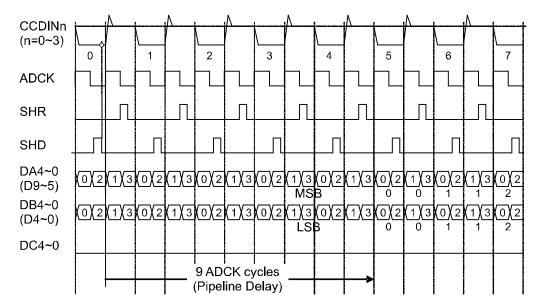

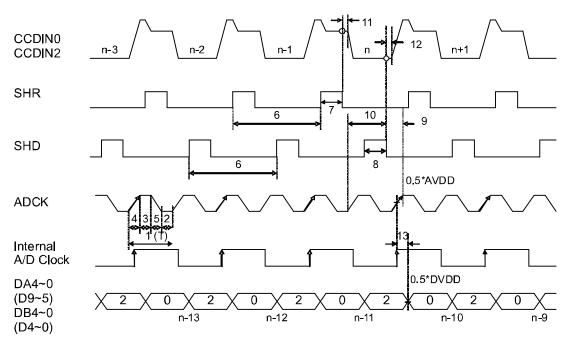

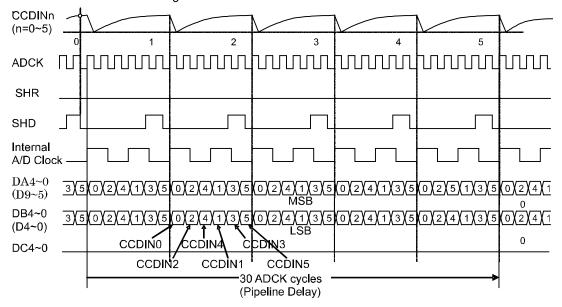

■ Timing Diagrams (4): ADCK frequency = A/D conversion rate mode ( 5 Bit-wide output )

• 4 channel, 6 channel modes ( CDS mode & Clamp mode, negative polarity ) Please refer to Switching Characteristics 2 table.

Timing Diagrams in 4 channel, 6 channel modes

Detailed Timing Diagrams in 4 channel, 6 channel modes

Timings are specified at the points where specified levels by the DC Characteristics are intersected.

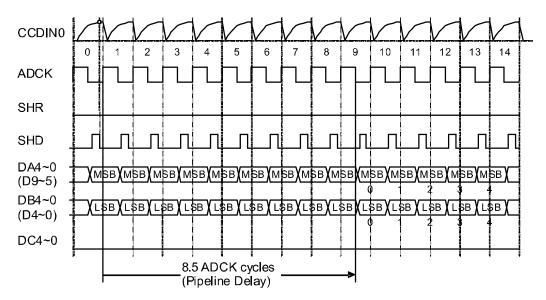

■ Timing Diagrams(5): ADCK frequency = A/D conversion rate mode (10 Bit-wide output)

• 1 channel mode ( DC direct-coupled mode, positive polarity ) Please refer to Switching Characteristics 1 table.

Timing Diagrams in 1 channel mode

**Detailed Timing Diagrams in 1 channel mode**

Timings are specified at the points where specified levels by the DC Characteristics are intersected.

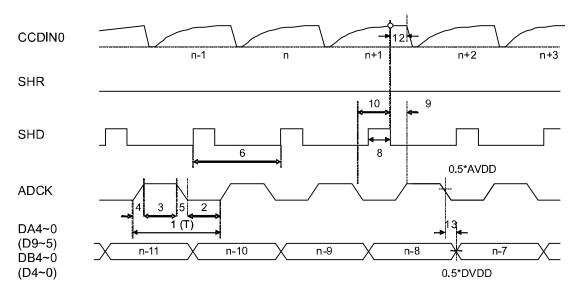

■ Timing Diagrams(6): ADCK frequency = A/D conversion rate mode (10 Bit-wide output)

• 1 channel mode ( CDS mode & Clamp mode, negative polarity ) Please refer to Switching Characteristics 2 table.

Timing Diagrams in 1 channel mode

**Detailed Timing Diagrams in 1 channel mode**

Timings are specified at the points where specified levels by the DC Characteristics are intersected.

■ Timing Diagrams(7): ADCK frequency = A/D conversion rate mode ( 10 Bit-wide output )

• 2 channel mode ( DC direct-coupled mode, positive polarity ) Please refer to Switching Characteristics 1 table.

Timing Diagrams in 2 channel mode

**Detailed Timing Diagrams in 2 channel mode**

Timings are specified at the points where specified levels by the DC Characteristics are intersected.

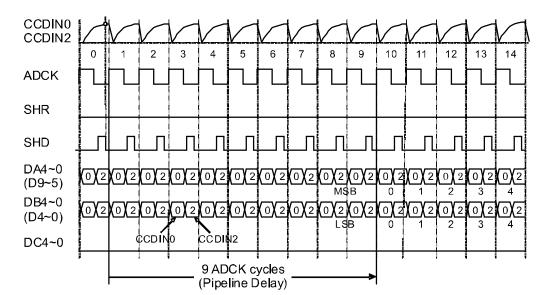

■ Timing Diagrams(8): ADCK frequency = A/D conversion rate mode ( 10 Bit-wide output )

• 2 channel mode ( CDS mode & Clamp mode, negative polarity ) Please refer to Switching Characteristics 2 table.

CCDIN0 CCDIN2 3 10 11 12 13 **ADCK** SHR SHD DA4~0 0 (2 (0 (2 0/2 (D9~5) DB4~0 0 2 0 2 <u>(0)(2)(0)(2)(0)(2)(0)(2</u> (0)(2 (D4~0) CCDINO C¢ĎIN2 DC4~0

Timing Diagrams in 2 channel mode

9 ADCK cycles (Pipeline Delay)

**Detailed Timing Diagrams in 2 channel mode**

Timings are specified at the points where specified levels by the DC Characteristics are intersected.

■ Timing Diagrams(9): ADCK frequency = A/D conversion rate mode (10 Bit-wide output)

• 4 channel mode ( DC direct-coupled mode, positive polarity ) Please refer to Switching Characteristics 1 table.

Timing Diagrams in 4 channel mode

**Detailed Timing Diagrams in 4 channel mode**

Timings are specified at the points where specified levels by the DC Characteristics are intersected.

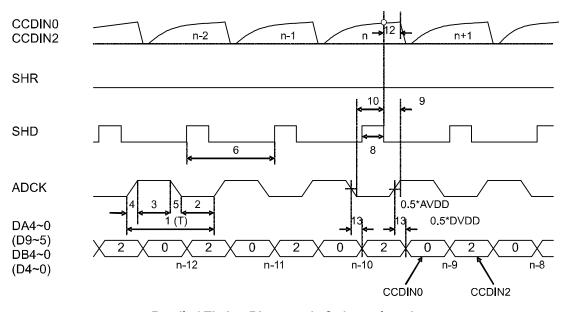

■ Timing Diagrams(10):ADCK frequency = A/D conversion rate mode ( 10Bit-wide output )

• 4 channel mode ( CDS mode & Clamp mode, negative polarity ) Please refer to Switching Characteristics 2 table.

**Timing Diagrams in 4 channel mode**

**Detailed Timing Diagrams in 4 channel mode**

Timings are specified at the points where specified levels by the DC Characteristics are intersected.

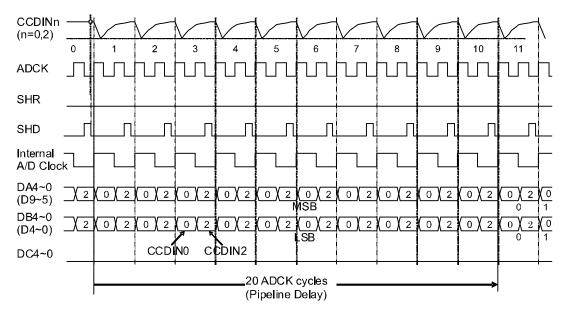

■ Timing Diagrams(11): ADCK frequency = total pixel rate mode (10 Bit-wide output)

• 2 channel mode ( DC direct-coupled mode, positive polarity ) Please refer to Switching Characteristics 3 table.

Timing Diagrams in 2 channel mode

**Detailed Timing Diagrams in 2 channel mode**

Timings are specified at the points where specified levels by the DC Characteristics are intersected.

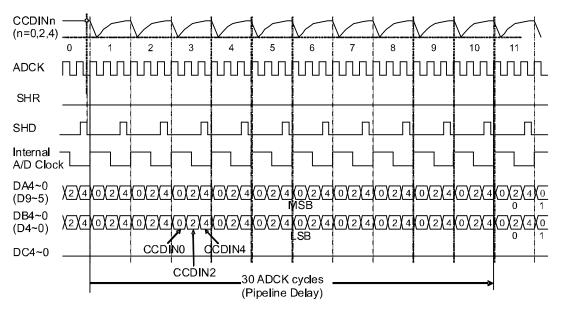

■ Timing Diagrams(12): ADCK frequency = total pixel rate mode (10 Bit-wide output)

• 2 channel mode ( CDS mode & Clamp mode, negative polarity ) Please refer to Switching Characteristics 4 table.

Timing Diagrams in 2 channel mode

**Detailed Timing Diagrams in 2 channel mode**

Timings are specified at the points where specified levels by the DC Characteristics are intersected.

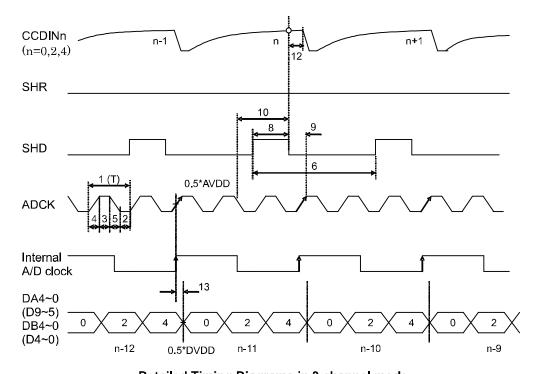

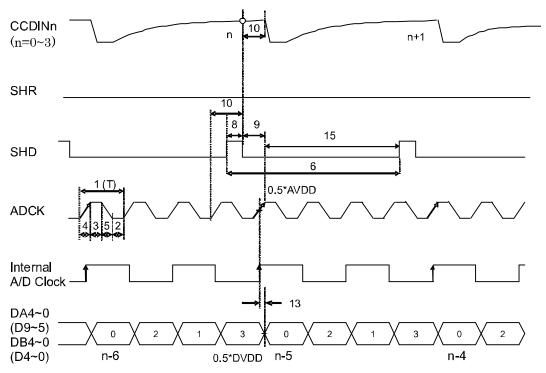

■ Timing Diagrams(13): ADCK frequency = total pixel rate mode (10 Bit-wide output)

• 3 channel mode ( DC direct-coupled mode, positive polarity )

Please refer to Switching Characteristics 3 table.

Timing Diagrams in 3 channel mode

**Detailed Timing Diagrams in 3 channel mode**

Timings are specified at the points where specified levels by the DC Characteristics are intersected.

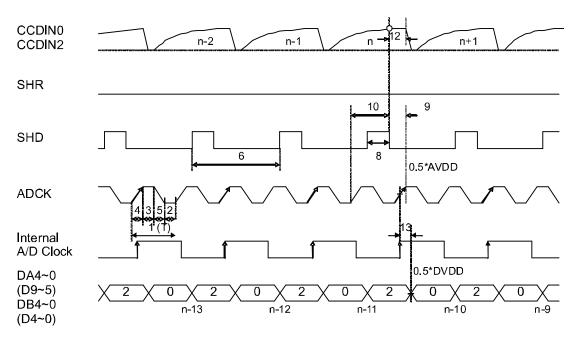

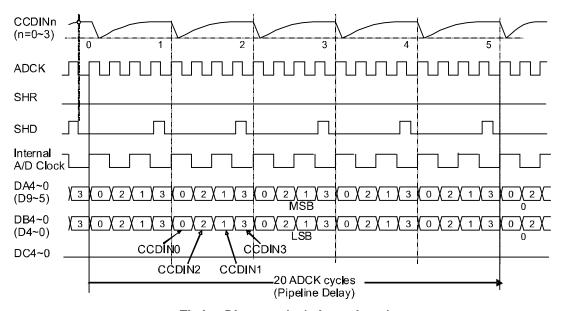

■ Timing Diagrams(14): ADCK frequency = total pixel rate mode (10 Bit-wide output)

• 3 channel mode ( CDS mode & Clamp mode, negative polarity ) Please refer to Switching Characteristics 4 table.

**Detailed Timing Diagrams in 3 channel mode**

Timings are specified at the points where specified levels by the DC Characteristics are intersected.

■ Timing Diagrams(15): ADCK frequency = total pixel rate mode (10 Bit-wide output)

• 4 channel mode ( DC direct-coupled mode, positive polarity ) Please refer to Switching Characteristics 3 table.

## Timing Diagrams in 4 channel mode

**Detailed Timing Diagrams in 4 channel mode**

Timings are specified at the points where specified levels by the DC Characteristics are intersected.

■ Timing Diagrams(16): ADCK frequency = total pixel rate mode (10 Bit-wide output)

• 4 channel mode ( CDS mode & Clamp mode, negative polarity ) Please refer to Switching Characteristics 4 table.

**Timing Diagrams in 4 channel mode**

**Detailed Timing Diagrams in 4 channel mode**

Timings are specified at the points where specified levels by the DC Characteristics are intersected.

MS1513-E-01 2013/04 31

Downloaded from Arrow.com.

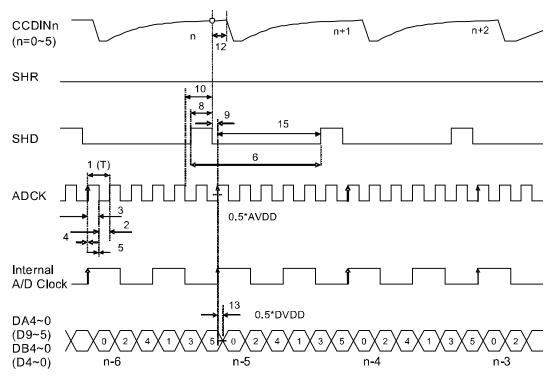

■ Timing Diagrams(17): ADCK frequency = total pixel rate mode (10 Bit-wide output)

• 6 channel mode ( DC direct-coupled mode, positive polarity )

Please refer to Switching Characteristics 3 table.

#### Timing Diagrams in 6 channel mode

#### **Detailed Timing Diagrams in 6 channel mode**

Timings are specified at the points where specified levels by the DC Characteristics are intersected.

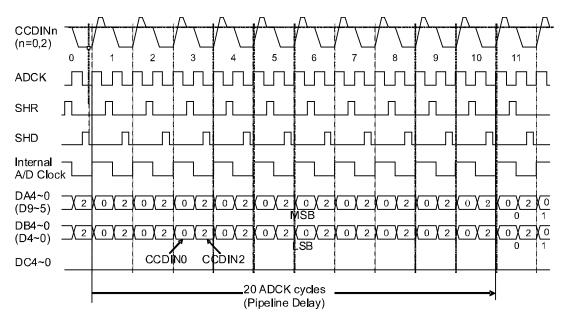

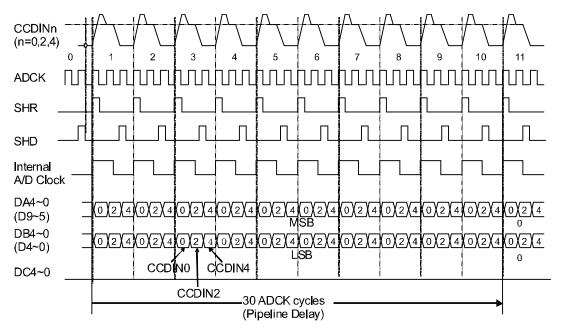

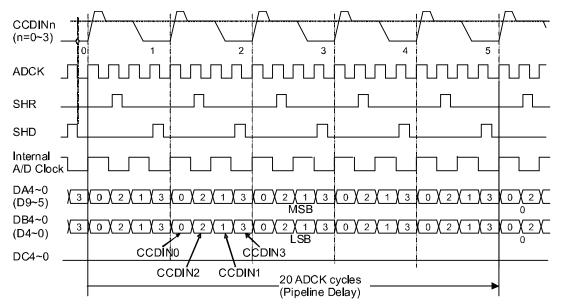

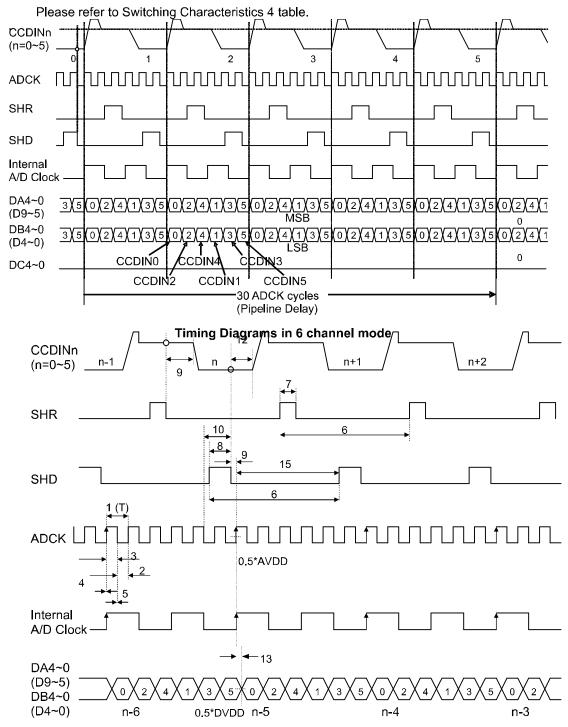

■ Timing Diagrams(18): ADCK frequency = total pixel rate mode (10 Bit-wide output)

6 channel mode ( CDS mode & Clamp mode, negative polarity )

**Detailed Timing Diagrams in 6 channel mode**

Timings are specified at the points where specified levels by the DC Characteristics are intersected.

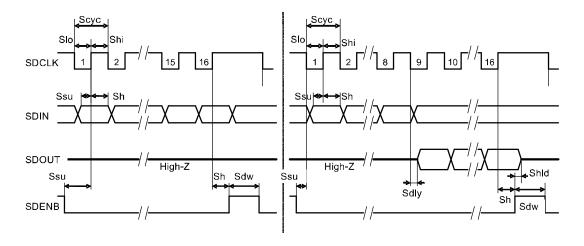

### ■ Switching Characteristics : Serial I / F

( AVDD =  $3.0 \sim 3.6$  V, DVDD =  $3.0 \sim 3.6$  V, Ta =  $0 \sim 70$  °C)

|                                 | т          | (7,17,00 | 0.0 0.0 |      |      | 0.0 0, | <u> 14 0 10 0)</u> |

|---------------------------------|------------|----------|---------|------|------|--------|--------------------|

| Parameter                       | Symb<br>ol | Pin      | Min.    | Тур. | Max. | Unit   | Condition          |

| Clock Cycle                     | Scyc       | SDCLK    |         |      | 10   | MHz    |                    |

| Clock Pulse Width               | Shi        | SDCLK    | 40      |      |      | ns     |                    |

| ( " H " period )                |            |          |         |      |      |        |                    |

| Clock Pulse Width               | Slo        | SDCLK    | 40      |      |      | ns     |                    |

| ("L"period)                     |            |          |         |      |      |        |                    |

| Set-up Time                     | Ssu        | SDIN     | 20      |      |      | ns     |                    |

| ( time to SDCLK )               |            | SDENB    |         |      |      |        |                    |

| Hold Time                       | Sh         | SDIN     | 20      |      |      | ns     |                    |

| ( time from SDCLK )             |            | SDENB    |         |      |      |        |                    |

| Rise Time of SDCLK,             | Sr         | SDCLK    |         |      | 6    | ns     | 0.3 AVDD           |

| SDENB                           |            | SDENB    |         |      |      |        | →0.7 AVDD          |

| Fall Time of SDCLK,             | Sf         | SDCLK    |         |      | 6    | ns     | 0.3 AVDD           |

| SDENB                           |            | SDENB    |         |      |      |        | →0.7 AVDD          |

| SDENB High Level Pulse<br>Width | Sdw        | SDENB    | 40      |      |      | ns     |                    |

| Data delay time                 | Sdly       | SDOUT    |         |      | 30   | ns     |                    |

| ( time from SDCLK )             |            |          |         |      |      |        |                    |

| Data Hold Time                  | Shld       | SDOUT    | 0       |      |      | ns     |                    |

| ( time from SDENB )             |            |          |         |      |      |        |                    |

| Number of Serial Data           | Snum       | SDCLK    |         | 16   |      |        |                    |

Write to AK8448

Read from AK8448

# **Control Registers**

| Address |         | Data                     |                          |          |            |            |            |          |          |

|---------|---------|--------------------------|--------------------------|----------|------------|------------|------------|----------|----------|

| (Hex)   | Initial | D7                       | D6                       | D5       | D4         | D3         | D2         | D1       | D0       |

|         | (Hex)   |                          |                          |          |            |            |            |          |          |

| 0       | 00      | Sensor                   | Interface                | Signal   | Cha        | annel Num  | nber       | ADCK     | Power    |

|         |         | Mode                     |                          | Polarity | / Freq.    |            |            |          | Down     |

| 1       | 00      | SHR                      | Output                   | Test     | 0          | Output     | Order of   | Order of | Order of |

|         |         | SHD                      | as                       | pattern  |            | Data       | Channel    | Channel  | Channel  |

|         |         | Polarity                 | Power                    | output   |            | Width      | 0 and 1    | 2 and 3  | 3 and 4  |

|         |         |                          | Down                     |          |            |            |            |          |          |

| 2       | 80      |                          |                          | O.       | ffset Data | for CCDII  | <b>1</b> 0 |          |          |

| 3       | 80      |                          |                          | O.       | ffset Data | for CCDII  | <b>V</b> 1 |          |          |

| 4       | 80      |                          | Offset Data for CCDIN2   |          |            |            |            |          |          |

| 5       | 80      |                          | Offset Data for CCDIN3   |          |            |            |            |          |          |

| 6       | 80      |                          | Offset Data for CCDIN4   |          |            |            |            |          |          |

| 7       | 80      |                          | Offset Data for CCDIN5   |          |            |            |            |          |          |

| 8       | 00      |                          | PGA Gain Data for CCDIN0 |          |            |            |            |          |          |

| 9       | 00      |                          |                          | PGA      | A Gain Da  | ta for CCI | DIN1       |          |          |

| Α       | 00      |                          | PGA Gain Data for CCDIN2 |          |            |            |            |          |          |

| В       | 00      |                          | PGA Gain Data for CCDIN3 |          |            |            |            |          |          |

| С       | 00      | PGA Gain Data for CCDIN4 |                          |          |            |            |            |          |          |

| D       | 00      | PGA Gain Data for CCDIN5 |                          |          |            |            |            |          |          |

| Е       | 08      | TEST                     |                          |          |            |            |            |          |          |

| F       | 00      |                          | TEST                     |          |            |            |            |          |          |

In this data sheet, R0 indicates a register at address 0, for example.

R0, D0 description means, D0 bit of register at address 0.

Each bit of registers to be described in the following is set to a condition as noted to be default after the reset.

### ☐ R0 Register

#### ■ R0, D7-D6 Sensor I/F mode

| D7 | D6 | Sensor Interface Mode         |

|----|----|-------------------------------|

| 0  | 0  | DC direct-coupled ( default ) |

| 0  | 1  | CDS                           |

| 1  | 0  | Clamp                         |

#### ■ R0, D5 Signal polarity

| D5 | Signal   | Sensor Type                                                      |

|----|----------|------------------------------------------------------------------|

|    | Polarity |                                                                  |

| 0  | Negative | Signal swings to low voltage side from the reference level. CCD  |

|    |          | sensors etc. ( default )                                         |

| 1  | Positive | Signal swings to high voltage side from the reference level. CIS |

|    |          | sensors etc.                                                     |

#### ■ R0, D4 ~ D2 Cannel Number

| D4 | D3 | D2 | Cannel       | CCDIN |   |   |   |   |   |

|----|----|----|--------------|-------|---|---|---|---|---|

|    |    |    | Number       | 0     | 1 | 2 | 3 | 4 | 5 |

| 0  | 0  | 0  | 1( default ) | 0     | - | - | - | - | - |

| 0  | 0  | 1  | 2            | 0     | - | 0 | - | - | - |

| 0  | 1  | 0  | 3            | 0     | - | 0 | - | 0 | - |

| 0  | 1  | 1  | 4            | 0     | 0 | 0 | 0 | - | - |

| 1  | 0  | 0  | 6            | 0     | 0 | 0 | 0 | 0 | 0 |

O: denotes input channel(s) to be used in the selected # of channel mode.

Un-used functional blocks, CDS, DAC, PGA and ADC are automatically powered-down. No capacitor connection is required on CCDINn & REFINn pins for the un-used channels. Those, un-used pins should be open.

#### ■ R0, D1 ADCK Frequency

| D1 | ADCK Input Frequency | Note                                            |

|----|----------------------|-------------------------------------------------|

| 0  | A/D Conversion Rate  | Either 5 Bit-wide or 10 Bit-wide output data    |

|    | ( default )          | is output both at the rising edge and the       |

|    |                      | falling edge of ADCLK.                          |

| 1  | Total Pixel Rate     | 10 Bit-wide output data is output at the rising |

|    |                      | edge of ADCK.                                   |

In the default mode, ADCK at the same frequency as ADC conversion rate should be input.

ADC data is output both at the rising edge and the falling edge of ADCK.

In total pixel rate mode, ADCK at the same frequency as a total sum of pixel rate of effective channels should be input. ADC data is output at the rising edge of ADCK.

#### ■ R0, D0 Power-Down

| D0 | Operation                    |

|----|------------------------------|

| 0  | Normal Operation ( default ) |

| 1  | Power-Down                   |

In Power-down mode, clock feed to the Digital part is stopped while Analog part is powered-down.

ADC data output conditions ( DA0 ~ DA4, DB0 ~ DB4, DC0 ~ DC4 ) at power-down can be selected to be either fixed low or high-Z output by D6 bit of register R1.

## ☐ R1 Register

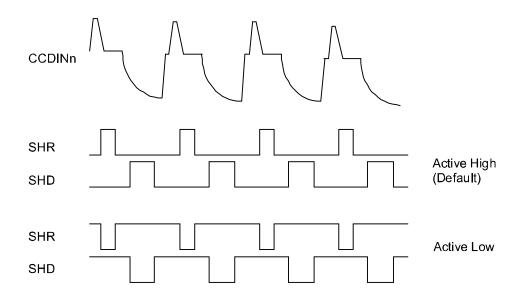

## ■ R1, D7 SHR, SHD Polarity Select

| D7 | Polarity                |  |  |  |  |  |

|----|-------------------------|--|--|--|--|--|

| 0  | Active High ( default ) |  |  |  |  |  |

| 1  | Active Low              |  |  |  |  |  |

All diagrams shown in this data sheet are when SHR and SHD polarities are set at default conditions ( active high ).

## ■ R1, D6 Output Conditions at Power-Down

| D6 | Output conditions        |

|----|--------------------------|

| 0  | Fixed to low ( default ) |

| 1  | High Z                   |

## R1, D5 Test pattern output

| D5 | Output              |  |  |  |  |

|----|---------------------|--|--|--|--|

| 0  | Normal (default)    |  |  |  |  |

| 1  | Test pattern output |  |  |  |  |

10-bit increment pattern is outputted at test pattern output.

$(0,1,2,3,\cdots,1022,1023,0,1,2,3,\cdots)$

## ■ R1, D3 Output Data width

|                     | D3 | Output Data width |  |  |

|---------------------|----|-------------------|--|--|

| 0 5 Bit ( default ) |    |                   |  |  |

|                     | 1  | 10 Bit            |  |  |

When the setting of ADCK frequency is equal to total pixel rate mode (R0, D1 = 1), output data is output in 10 Bit-wide mode, regardless of output data width setting.

## ■ R1, D2-D0 Channel Processing Order

| D2 | Channels 0, 1 Processing Order                                              |

|----|-----------------------------------------------------------------------------|

| 0  | $CCDIN0 \rightarrow CCDIN1 \rightarrow CCDIN0 \rightarrow CCDIN1$ (default) |

| 1  | CCDIN1 → CCDIN0 → CCDIN1 → CCDIN0                                           |

| D1 | Channels 2, 3 Processing Order              |  |  |  |  |  |

|----|---------------------------------------------|--|--|--|--|--|

| 0  | CCDIN2 → CCDIN3 → CCDIN2 → CCDIN3 (default) |  |  |  |  |  |

| 1  | CCDIN3 → CCDIN2 → CCDIN3 → CCDIN2           |  |  |  |  |  |

| D0 | Channels 4, 5 Processing Order                                              |

|----|-----------------------------------------------------------------------------|

| 0  | $CCDIN4 \rightarrow CCDIN5 \rightarrow CCDIN4 \rightarrow CCDIN5$ (default) |

| 1  | CCDIN5 → CCDIN4 → CCDIN5 → CCDIN4                                           |

This is to select the processing order of corresponding input channel pair of the selected, single ADC. Processing order can be individually set at every pair.

This register is valid either in 4 channel mode / 5 Bit-wide output or 6 channel mode / 5 Bit-wide output.

All diagrams shown in this data sheet are when the channel processing order is set at default condition.

# ☐ R2~R7 Registers

## ■ D7-D0 Offset Data

| D7-D0                | Offset Voltage | At Negative Mode   | At Positive                            |  |

|----------------------|----------------|--------------------|----------------------------------------|--|

| (Straight Binary)    |                |                    | Mode                                   |  |

| 11111111             | –298.7mV       | Maximum Shift to   | Maximum Shift to                       |  |

| 11111110             | -296.3mV       | White Level Side   | Black level side<br>( ADC code small ) |  |

| :                    | :              | ( ADC code large ) |                                        |  |

| 10000001             | –2.4mV         | <b>↑</b>           |                                        |  |

| 10000000 ( default ) | 0mV            |                    |                                        |  |

| 01111111             | 2.4mV          |                    | <b>↓</b>                               |  |

| :                    | :              | Maximum Shift to   | Maximum Shift to                       |  |

| 0000001              | 298.7mV        | Black Level Side   | White Level Side                       |  |

| 0000000(Inhibition)  | (298.7mV)      | ( ADC code small ) | ( ADC code large )                     |  |

$$Offset(x) = \frac{298.7}{127} \times (128 - x)$$

$mV$  Where  $x$  is register set value (  $0 < x < 255$  )

Default x=128

## ☐ R8~RD Registers

■ D7-D0 PGA Gain Data

Setting code and gain ( ideal value ) relation is expressed in the following equation.

$$Gain(x) = \frac{2 \times 208}{33.3 + 255 - x}$$

(times) \*\* Where x is register set value ( 0 <= x <= 255 )

At default x = 0

Relative PGA Gain Curves (ideal values)

\*\* PGA gain is assigned as relative value to [Register:0 setting].

## **Operations**

#### ■ Sensor I/F Mode

AK8448 has three sensor interface modes: CDS, Clamp and DC connect. The sensor interface mode is selected by Sensor Interface Mode register R0, D7~D6.

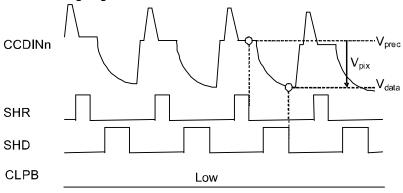

#### CDS mode

A mode to process the <u>difference Vpix</u> as its pixel level which is <u>between</u> the reference level Vprec of each pixel from the sensor output signal <u>and</u> its data level Vdata.

Reference level of the sensor signal is sampled at SHR and data level of the sensor signal is sampled at SHD respectively.

Sampling point is at the falling edge of SHR and SHD respectively.

When polarity of SHR and SHD is inverted by register (R1, D7 = 1), the sampling point becomes at the rising edge.

**CDS Mode Timing Outline**

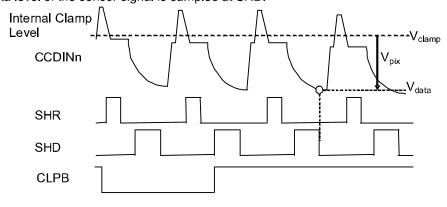

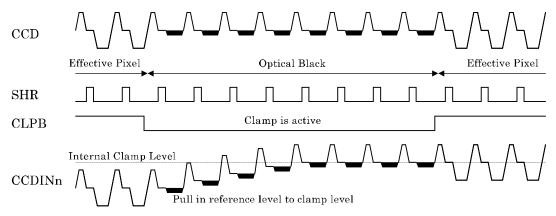

## Clamp mode

A mode to process the <u>difference Vpix</u> as its pixel level which is <u>between</u> the internally generated Clamp level Vclamp <u>and</u> data level Vdata of the sensor output signal.

Data level of the sensor signal is sampled at SHD.

Clamp Mode Timing Outline

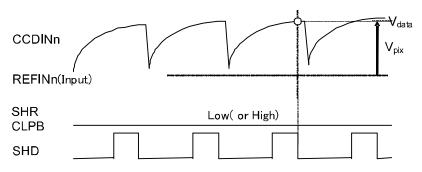

## • DC direct-coupled mode

A mode to process a <u>difference Vpix</u> as its pixel level which is <u>between</u> a reference level fed on REFINn pin externally, <u>and</u> data level Vdata of the sensor output signal.

When no reference level exists in sensor output signal, this mode is used as an example.

Data level of the sensor signal is sampled at SHD. Since SHR is not used, connect it to either Low or High.

DC Direct-coupled Mode Timing Outline

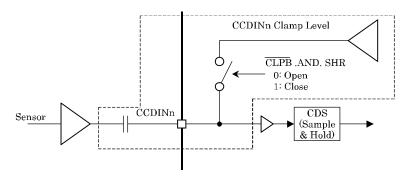

#### ■ Clamp Operation

In CDS mode and Clamp mode, Clamping is made in order to adjust the reference DC level of sensor signal to match the internal reference level of the AK8448.

Clamp operation is controlled by CLPB and SHR.

Clamp switch closes during CLPB = Low and SHR = High ( " Low " when SHR, SHD polarities are inverted ), and CCDINn (  $n=0\sim5$  ) pin signal is pulled toward the internal clamp level.

REFINn (  $n = 0 \sim 5$  ) is also clamped in the same way.

In CDS mode, fix CLPB to low so that clamping is always enabled.

Clamp Circuit Outline

Clamp Operation Timing Outline

MS1513-E-01 2013/04 42

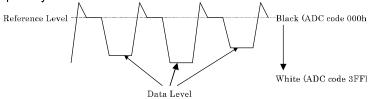

#### ■ Signal Polarity

The AK8448 accepts both positive and negative input polarities.

Either signal polarity is selected by setting Signal Polarity register ( R0,D5 ) to meet sensor types to be used.

In general, CCD exhibits negative polarity characteristics and CIS exhibits positive polarity characteristics. Either polarity can be selected, regardless of sensor I/F mode setting.

## • Positive polarity characteristics

#### Output Data Control

ADC output data is output in either 5 Bit-wide or 10 Bit-wide by setting Data Width register (R1, D3).

When 5 Bit-wide data mode is selected, data is output on each of three 5 Bit buses – DA4 ~ DA0, DB4 ~ DB0 and DC4 ~ DC0 respectively which correspond to each ADC.

When 10 Bit-wide data mode is selected, data is output on 10 pins – DA4 ( MSB )  $\sim$  DA0 and DB4  $\sim$  DB0 ( LSB ).

In 5 Bit-wide data mode, the upper 5 Bit of data is output at the rising edge of ADCK, and the lower 5 Bit at the falling edge of ADCK.

In 10 Bit-wide data mode, two different channel data are output at the rising edge and at the falling edge of ADCK respectively.

It is also possible to output data at only the falling edge of ADCK in 10 Bit-wide data mode, by setting ADCK Frequency register (R0, D1).

In this operation, it is required to input ADCK at the frequency of a total sum of pixel rate of all channels (total pixel rate). Un-used buses DB4 ~ DB0 and DC4 ~ DC0 such as a case in 1 channel mode with 5 Bit-wide output, will output Low levels.

#### ■ ADCK

A/D Conversion Rate mode and Total Pixel Rate mode

ADCK generates ADC conversion timing and ADC data output timing.

Whether to output data at both the rising edge and the falling edge of ADCK or to output data at only the rising edge can be selected by ADCK Frequency mode register.

A/D conversion rate mode is a mode where data is output at both the rising edge and the falling edge of ADCK.

In A/D conversion rate mode, input an ADCK clock of same frequency as ADC conversion rate.

Total pixel rate mode is a mode where data is output at only the ADCK rising edge. In this mode, input an ADCK clock of same frequency as a total sum of effective channels' pixel rates.

For example, when to process a 20 MHz / channel sensor signal in 3 channel mode, a 20 MHz ADCK is input in A/D conversion rate mode which is equal to ADC conversion rate.

#### Maximum Conversion Rate

Maximum operating speed of ADC data output buffers DA0  $\sim$  DA4, DB0  $\sim$  DB4, DC0  $\sim$  DC4 is designed to be 80 Mbps.

When a total pixel rate mode is selected as ADCK frequency mode, maximum sampling rate per channel in 3 channel and 6 channel modes is limited by this output buffer speed.

For example, maximum conversion rate in 6 channel mode is 80 MSPS / 6 = 13.3 MSPS per channel, and not 20 MSPS.

Number of channels and its ADCK frequency, a possible data width combination and its maximum conversion rate per channel are listed in the following table.

[CDS, Clamp mode]

|                  | A/D Conversion Rate Mode |                  |                                        | Total Pixel Rate Mode |                    |                                           |

|------------------|--------------------------|------------------|----------------------------------------|-----------------------|--------------------|-------------------------------------------|

| # of<br>Channels | 5 bits<br>Width          | 10 bits<br>Width | Maximum<br>Conversion<br>Rate [SPS/CH] | 5 bits<br>Width       | 10 bits<br>Width   | Maximum<br>Conversion<br>Rate<br>[SPS/CH] |

| 1                | 0                        | 0                | 40M                                    | I                     | O <sup>Note1</sup> | 40M                                       |

| 2                | 0                        | 0                | 40M                                    | -                     | 0                  | 40M                                       |

| 3                | 0                        | -                | 40 <b>M</b>                            | -                     | 0                  | 26.6M                                     |

| 4                | 0                        | 0                | 20M                                    |                       | 0                  | 20M                                       |

| 6                | 0                        | -                | 20M                                    | -                     | 0                  | 13.3M                                     |

[DC Direct mode]

|                  | A/D Conversion Rate Mode |                                         |          | Total Pixel Rate Mode |                    |                                |  |  |  |

|------------------|--------------------------|-----------------------------------------|----------|-----------------------|--------------------|--------------------------------|--|--|--|

| # of<br>Channels | 5 bits<br>Width          | 10 bits Width  Maximum Conversio n Rate |          | 5 bits<br>Width       | 10 bits<br>Width   | Maximum<br>Conversio<br>n Rate |  |  |  |

|                  |                          |                                         | [SPS/CH] |                       |                    | [SPS/CH]                       |  |  |  |

| 1                | 0                        | 0                                       | 15M      | -                     | O <sup>Note1</sup> | 15M                            |  |  |  |

| 2                | 0                        | 0                                       | 15M      | -                     | 0                  | 15M                            |  |  |  |

| 3                | 0                        | -                                       | 15M      | -                     | 0                  | 15M                            |  |  |  |

| 4                | 0                        | 0                                       | 15M      | -                     | 0                  | 15M                            |  |  |  |