AP43671

# HIGHLY INTEGRATED INTELLIGENT USB PD DECODER WITH EMBEDDED SR CONTROLLER

### Description

The DIODES™ AP43671 is a highly integrated and intelligent USB Type-C power delivery (PD) controller with an embedded synchronous rectification (SR) controller. It is ideally targeted for cost-performance-sensitive USB Type-C adaptors and charger applications.

The device supports USB PD3. 0 V1.2, and Programmable Power Supply (PPS) and Qualcomm QC4/QC4+ protocols. Leveraging its embedded MCU and supporting circuitry, the AP43671 can accommodate popular quick-charging protocols for firmware stored in One-Time-Programmable (OTP) memory.

To enable optimal system BOM and performance implementation of quick chargers, the AP43671 embeds a multiple-mode adaptive SR controller where its key performance and safety parameters can be fine-tuned by a built-in MCU.

The AP43671 also adopts a relatively small current-sensing resistor  $(5m\Omega)$  that is used to provide accurate current measurements without sacrificing power consumption.

The AP43671 provides robust protection schemes, which includes a CC1/CC2 short protection against VBUS (up to 24V) as well as built-in OVP/OCP/SCP/OTP features to provide necessary safety protection.

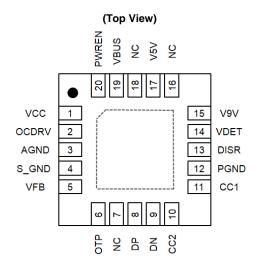

### **Pin Assignments**

W-QFN4040-20 (Type A1)

### **Features**

- Supports USB PD3.0 Programmable Power Supply (PPS)

- USB-IF PD3.0/PPS Certificated TID = 4999

- Compatible with QC4/QC4+ protocol

- MCU-based implementation for protocol decoding, application firmware, parameter fine-tuning and calibration.

- OTP (One-Time-Programmable) for main protocol and application firmware

- MTP (Multi-Time-Programmable) for system configuration options

- Built-in regulator for CV and CC control, no need for external CC/CV reference circuitry

- Ultra-low current consumption (550uA) at sleep mode

- Supports power-saving mode to enable low standby power of chargers

- Embed Synchronous Rectification (SR) Controller, which supports Adaptive Quasi-Resonant (QR) and Continuous Conduction Mode (CCM) for matching PWM controllers.

- Small current-sensing resistor (5 mΩ) for efficiency improvement

- Adaptive gate drive for external N-MOSFET output enable switch

- Supports e-marker cable detection and V<sub>CONN</sub> power (20mA)

- Supports SCP/OTP/OVP/UVP with auto-restart

- CC1/CC2 pins shorted to VBUS protection up to 24V

- Minimum system BOM components for quick charger implementations.

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

- For automotive applications requiring specific change control (i.e. parts qualified to AEC-Q100/101/104/200, PPAP capable, and manufactured in IATF 16949 certified facilities), please contact us or your local Diodes representative. https://www.diodes.com/quality/product-definitions/

### **Applications**

- Battery chargers for smart phones, table PCs, and any USB Type-C PD-equipped mobile devices

- Wall and travel chargers for AC-DC adaptors (USB Type-Cequipped Notebook PCs)

Notes:

- 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

- See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

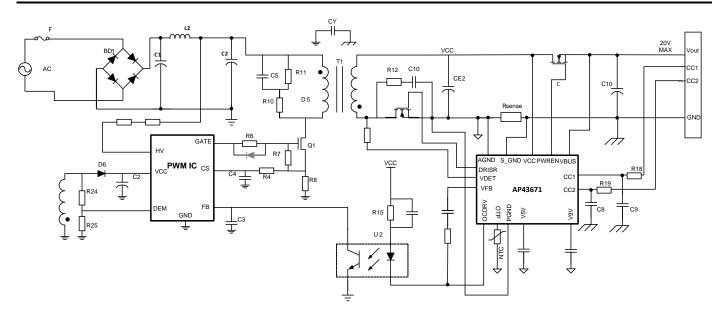

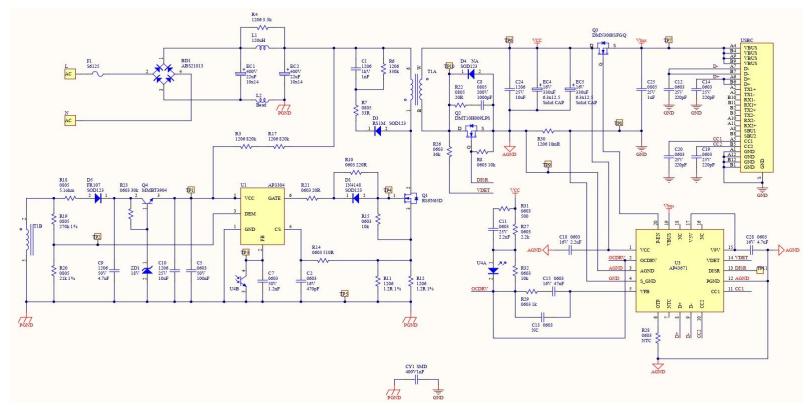

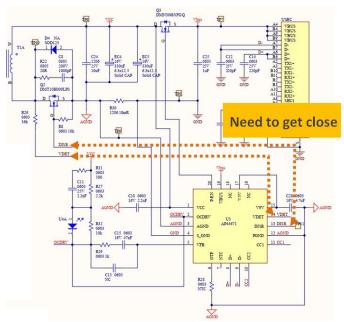

# **Typical Applications Circuit**

Figure 1. Typical Application Circuit of AP43671 for PD3.0 PPS Charger

# Pin Descriptions

| Pin Number | Pin Name | Function                                                                             |

|------------|----------|--------------------------------------------------------------------------------------|

| 1          | VCC      | The power supply of the IC, which also is input Current Sense Negative Node          |

| 2          | OCDRV    | CC/CV Output. Open Drain Output for Opto-Coupler.                                    |

| 3          | AGND     | Analog Ground                                                                        |

| 4          | S_GND    | System reference ground.                                                             |

| 5          | VFB      | CV Input. Negative Node of CV OPAMP for Opto-Coupler.                                |

| 6          | OTP      | Source Current to External NTC Sensor for overtemperature protection (OTP).          |

| 7          | NC       | No Connect (Keep floating)                                                           |

| 8          | DP       | USB Type-C_DP                                                                        |

| 9          | DN       | USB Type-C_DN                                                                        |

| 10         | CC2      | USB Type-C_CC2                                                                       |

| 11         | CC1      | USB Type-C_CC1                                                                       |

| 12         | PGND     | Ground of SR controller                                                              |

| 13         | DISR     | Gate Driver of SR MOS;                                                               |

| 14         | VDET     | Sync signal of SR controller; connecting to SR MOS Drain node with a series resistor |

| 15         | V9V      | Power for SR gate driver                                                             |

| 16         | NC       | No Connect                                                                           |

| 17         | V5V      | LDO -5V Output                                                                       |

| 18         | NC       | No Connect                                                                           |

| 19         | VBUS     | Output Terminal for Discharge Path                                                   |

| 20         | PWREN    | To drive external NMOS VBUS Switch                                                   |

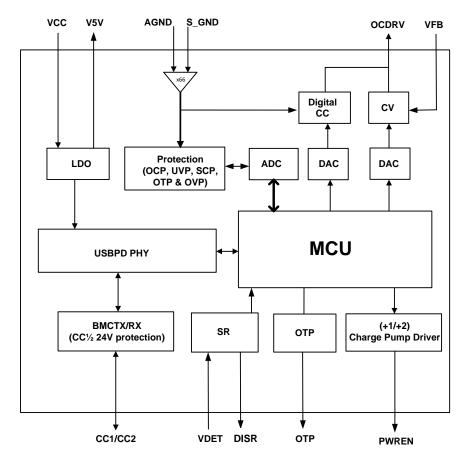

# **Functional Block Diagram**

Figure 2. Functional Block Diagram of AP43671

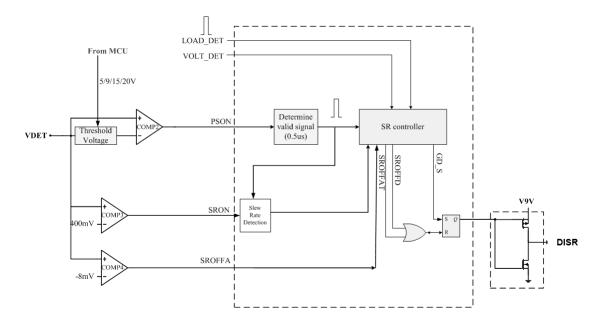

Figure 3. Functional Block Diagram of SR controller

## Absolute Maximum Ratings (@ T<sub>A</sub> = +25°C, unless otherwise specified.) (Note 4)

| Symbol                                                      | Parameter                                                                                                        | Rating      | Unit |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------|------|

| V <sub>VCC</sub> , Vcc1, Vcc2                               | Input Voltage at VCC, CC1, CC2 Pin                                                                               | -0.3 to 24  | V    |

| V <sub>V5V</sub>                                            | Input Voltage at V5V Pin                                                                                         | -0.3 to 7   | V    |

| V <sub>VFB</sub> , V <sub>OTP</sub>                         | Input Voltage at VFB, OTP Pins                                                                                   | -0.3 to 7   | V    |

| V <sub>VBUS</sub> , V <sub>PWREN</sub> , V <sub>OCDRV</sub> | Input Voltage at VBUS, PWREN, OCDRV Pins                                                                         | -0.3 to 24  | V    |

| V <sub>V9V</sub>                                            | Input Voltage at V9V Pin                                                                                         | -0.3 to 7   | V    |

| Vdisr                                                       | Input Voltage at DISR Pin                                                                                        | -0.3 to 7   | V    |

| Others                                                      | Input Voltage at other Pin                                                                                       | -0.3 to 7   | V    |

| TJ                                                          | Operating Junction Temperature                                                                                   | -40 to +150 | °C   |

| T <sub>STG</sub>                                            | Storage Temperature                                                                                              | -65 to +150 | °C   |

| T <sub>LEAD</sub>                                           | Lead Temperature (Soldering, 10s)                                                                                | +300        | °C   |

| θ <sub>JA</sub> (QFN-20)                                    | Thermal Resistance (Junction to Ambient) (Note 5)                                                                | 134         | °C/W |

| _                                                           | ESD (Human Body Model) Voltage on VBUS, VCC, OCDRV, PWREN, V5V, V9V, VFB, OTP, CC1, CC2 , VDET, DISR, S_GND Pins | 2000        | V    |

| _                                                           | ESD (Human Body Model) Voltage on DP, DN Pins                                                                    | 6000        | V    |

| _                                                           | ESD (Charged Device Model)                                                                                       | 750         | V    |

Notes:

## **Recommended Operating Conditions**

| Symbol           | Parameter                   | Min | Max | Unit |

|------------------|-----------------------------|-----|-----|------|

| V <sub>VCC</sub> | Power Supply Voltage at VCC | 3   | 21  | V    |

| T <sub>OP</sub>  | Operating Temperature Range | -40 | +85 | °C   |

Stresses greater than those listed under "Absolute Maximum Ratings" can cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to "Absolute Maximum Ratings" for extended periods can affect device reliability.

Test condition: Device mounted on FR-4 substrate PC board, 2oz copper, with 1inch<sup>2</sup> cooling area.

# Electrical Characteristics (@ T<sub>A</sub> = +25°C, unless otherwise specified.)

| Symbol                | Parameter                                            | Condition                    | Min   | Тур                          | Max   | Unit |

|-----------------------|------------------------------------------------------|------------------------------|-------|------------------------------|-------|------|

| VCC PIN SECTION       |                                                      |                              |       |                              |       |      |

| Vvcc_st               | VCC Startup Voltage                                  | _                            | 2.65  | 2.85                         | 3.05  | V    |

| V <sub>VCC_UVLO</sub> | VCC Minimum Operating Voltage                        | _                            | 2.5   | 2.7                          | 2.9   | V    |

| V <sub>VCC_HYS</sub>  | VCC Hysteresis (V <sub>ST</sub> -V <sub>UVLO</sub> ) | _                            | _     | 0.15                         | _     | V    |

| IVCC_DEEP SLEEP       | VCC Current in Deep Sleep Mode                       | CC1/2 Detach after 3 Seconds |       | 750                          | _     | μΑ   |

| I <sub>VCC_OPR</sub>  | VCC Operating Supply Current                         | _                            |       | 4.5                          | 6     | mA   |

| PWREN (Note 10)       |                                                      |                              |       |                              |       |      |

| Vpwren_l              | PWREN high voltage in low VCC input                  | V <sub>VCC</sub> <4.5V       | _     | 2*Vv5v+V <sub>VCC</sub> -0.7 | _     | V    |

| Vpwren_h              | PWREN high voltage in high VCC input                 | V <sub>VCC</sub> =5V         | _     | Vv5v+V <sub>VCC</sub> -0.7   | _     | V    |

| VOLTAGE CONTROL       | LOOP SECTION                                         |                              |       |                              |       |      |

| V <sub>REF_CV5</sub>  | Reference Voltage for 5V CV Control                  | _                            | 4.85  | 5                            | 5.15  | V    |

| V <sub>REF_CV9</sub>  | Reference Voltage for 9V CV Control                  | _                            | 8.73  | 9.0                          | 9.27  | V    |

| V <sub>REF_CV12</sub> | Reference Voltage for 12V CV Control                 | _                            | 11.64 | 12.0                         | 12.36 | V    |

| V <sub>CABLE</sub>    | Cable Compensation (Note 7)                          | _                            | 24    | 30                           | 36    | mV/A |

| Ios                   | Maximum OCDRV Pin Sink Current                       | V <sub>OUT</sub> = 4V        | 10    | 16                           | _     | mA   |

| Rocdry                | OCDRV Pin pull down resistor to GND                  | _                            | _     | 80                           | _     | ΚΩ   |

| PROTECTION FUNCT      | TION SECTION                                         |                              |       |                              |       |      |

| V <sub>OVP5</sub> V   | OVP_5V Enable Voltage (Note 8)                       | _                            | 5.5   | 6                            | 6.5   | V    |

| V <sub>OVP9V</sub>    | OVP_9V Enable Voltage (Note 8)                       | _                            | 9.9   | 10.8                         | 12.1  | V    |

| V <sub>OVP12V</sub>   | OVP_12V Enable Voltage (Note 8)                      | _                            | 13.2  | 14.4                         | 16.2  | V    |

| tDEBOUNCE_OVP         | OVP Debounce Time (Note 6)                           | _                            | _     | 90                           | _     | ms   |

| V <sub>UVP5V</sub>    | UVP_5V Enable Voltage (Note 8)                       | _                            | _     | 3.8                          | _     | V    |

| V <sub>UVP9V</sub>    | UVP_9V Enable Voltage (Note 8)                       | _                            | _     | 6.8                          | _     | V    |

| V <sub>UVP12V</sub>   | UVP_12V Enable Voltage (Note 8)                      | _                            | _     | 9.1                          | _     | V    |

| lovd                  | Overvoltage Discharge Current                        | _                            | _     | 240                          | _     | mA   |

| tocp                  | OCP Deglitch Time (Note 9)                           | _                            | _     | 30                           | _     | ms   |

| trestart_interval_scp | Restart Interval Time under SCP (Note 9)             | _                            | 1     | _                            | 2     | s    |

|                       | External OTP Current                                 | _                            | _     | 100                          | _     | μA   |

Notes:

- 6. OVP blanking time during V<sub>0</sub> transition from high output voltage to low output voltage, such as 9V to 5V, or 12V to 5V. 7. Cable compensation voltage can be adjusted by setting from 0 to V<sub>CABLE\*N, (N: 0 to 7)</sub>.

8. Programmable 120% OVP and 75% or 80% UVP setting.

9. Guaranteed by design.

10. Without resistor loading condition. The realistic measurement will be lower due to leakage current of prober.

# **Electrical Characteristics** (continued) (@ T<sub>A</sub> =+25°C, V<sub>VCC</sub> = 15V, unless otherwise specified.)

| Symbol                      | Parameter                                                                                      | Condition                                    | Min | Тур  | Max | Unit |

|-----------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------|-----|------|-----|------|

| PROTECTION FUNCTION SECTION |                                                                                                |                                              |     |      |     |      |

| tSLEEP                      | Enter Sleep Mode Time after Cable Detached (Note 9)                                            | _                                            | _   | 3    | _   | s    |

| tov_delay                   | Delay from OVP Threshold Trip to NMOS<br>Gate Turn-Off (Note 9)                                | _                                            | _   | _    | 50  | μs   |

| tuv_delay                   | Delay from UVP Threshold Trip to NMOS<br>Gate Turn-Off (Note 9)                                | _                                            | _   | _    | 50  | μs   |

| CC1/CC2, DP/DN              | I PIN SECTION                                                                                  |                                              |     |      |     |      |

| V <sub>L_RD3A</sub>         | Low Voltage Threshold Used to Distinguish R <sub>D</sub> Attached or Detached for 3A Delivery  | _                                            | _   | 1.35 | _   | V    |

| V <sub>H_RD3A</sub>         | High Voltage Threshold Used to Distinguish R <sub>D</sub> Attached or Detached for 3A Delivery | _                                            | _   | 2.0  | _   | V    |

| I <sub>RD3A</sub>           | CC1/CC2 Current Source for 3A<br>Advertisement                                                 | _                                            | 304 | 330  | 356 | μΑ   |

| V <sub>OVP_DN</sub>         | DN Line Overvoltage Protection Threshold                                                       | _                                            | 4.1 | 4.5  | 4.8 | V    |

| V <sub>OVP_DP</sub>         | DP Line Overvoltage Protection Threshold                                                       | _                                            | 4.1 | 4.5  | 4.8 | V    |

| V <sub>OVP_CC1</sub>        | CC1 Line Overvoltage Protection Threshold                                                      | _                                            | _   | 7    | _   | V    |

| V <sub>OVP_CC1</sub>        | CC2 Line Overvoltage Protection Threshold                                                      | _                                            | _   | 7    | _   | ٧    |

| SR SECTION                  |                                                                                                |                                              |     |      |     |      |

| V <sub>SROFFA</sub>         | VDET Negative Voltage Detection Threshold Voltage                                              | Test mode                                    | _   | -10  | _   | mV   |

| R <sub>DET</sub>            | Internal Resistor between VDET and GND                                                         | VCC=5V                                       | _   | 1.6  | _   | kΩ   |

| V <sub>DET_OVP</sub>        | VDET PIN OVP Threshold                                                                         | _                                            | _   | 4.8  | _   | V    |

| V <sub>SR_Gate</sub>        | Gate Driver High Voltage                                                                       | VCC=5V (External charge pump circuit active) |     | 5    |     | V    |

| t <sub>R_Gate</sub>         | Gate Driver Rise Time                                                                          | CL=6.5nF, VCC=5V, from 10% to 90%            | _   | 50   | _   | ns   |

| t <sub>F_Gate</sub>         | Gate Driver Fall Time                                                                          | CL=6.5nF, VCC=5V, from 90% to 10%            | _   | 30   |     | ns   |

| F <sub>CPCLK</sub>          | Charge Pump Clock Frequency                                                                    | V5V=5V, measure VCP pin                      | _   | 187  | _   | KHz  |

| t <sub>ON_min</sub>         | SR Gate-On Minimum On Time                                                                     | Fs=100K                                      |     | 667  |     | ns   |

| t <sub>ON_DT</sub>          | SR Gate-On Dead Time                                                                           | Fs=100K                                      |     | 200  |     | ns   |

| t <sub>OFF_DT</sub>         | SR Gate-Off Dead Time                                                                          | Fs=100K                                      | _   | 416  | _   | ns   |

| t <sub>d_PSON_min</sub>     | Primary-Side Minimum On Time                                                                   | _                                            | 500 | _    | _   | ns   |

Note: 9. Guaranteed by design.

### **Performance Characteristics**

#### System Power-On Sequence

When the external power source is provided, the AP43671 will wake up, and the USB PD controller and MCU will be initialized. All analog control blocks are ready and waiting for PD negotiation process. Meanwhile, the AP43671 monitors the voltage and current conditions to avoid abnormal conditions from occurring. Once any unacceptable conditions occur, the AP43671 will go into a protection procedure according to the types of abnormal conditions present.

#### **Voltage Transition**

According to USB PD's protocol, the PD device requests different power profiles. The AP43671's power control block will change the voltage and current values. The AP43671 provides corresponding Overvoltage Protection (OVP), Overcurrent Protection (OCP), and feedback system stability to guarantee monotonic voltage transition and avoid violating USB PD electrical specification.

The AP43671 provides zero-mismatch voltage methodology that is more flexible for customer system-design requirements. When UFP/DFP makes the acceptable power request deal, the AP43671 will change the VFB voltage according to the USB PD command. The voltage regulator control loop regulates the required VBUS voltage according to VFB voltage. In addition, the shunt regulator is built in to minimize the total external components and cost.

#### **Protection**

The AP43671 provides OVP/UVP/OCP/SCP/OTP functions and also supports Constant Current (CC) function. All of the protection thresholds depend on the requested power profile and provide the most reliable protection scheme.

The AP43671 provides OVP feature by turning off the power switch when VBUS is higher than OVP enable voltage. Meanwhile, it provides internal discharge path to reduce the overvoltage duration, and terminates discharge current as soon as VBUS reaches the target voltage. To avoid VBUS pin working abnormally, the AP43671 provides UVP function whenever VBUS drops to UVP enable voltage.

The AP43671 provides CC1/CC2 Overvoltage Protection (CC\_OVP). There are two CC1/CC2 Overvoltage Protection (CC\_OVP) mechanisms in the AP43671. First, the built-in switch-off circuit isolates the internal block with an external pin while the unpredictable high-voltage source shorts to the CC1/CC2 pin. Second, the AP43671 will turn off VBUS and resume to 5V if the CC1/CC2 voltage keeps higher than CC\_OVP (7V) for more than 3ms, which will avoid the VBUS from shorting to the CC1/CC2 continuously.

Both methods guarantee USB PD system safety in case the Type-C plug or receptacle is damaged.

To ensure the safe operation of USB PD, the AP43671 provides programmable OCP function to make sure output current will not be higher than the allowed maximum current. Once OCP conditions occur, the AP43671 will shut down the USB PD system and send a "Hard Reset" to the Upstream-Facing Port (UFP) device.

### CV/CC

The AP43671 supports Constant Voltage (CV) and Constant Current (CC) functions to control the output voltage and the output current by the control pin OCDRV. During the CV mode, the AP43671 operates in fixed PDO, and the output voltage will be regulated to the request voltage if the output current is below the allowed maximum current. Once the sink device draws more than I<sub>OCP</sub>, overcurrent protection occurs. When the CC mode function is enabled, the output voltage drops, and the source current is limited within 150mA whenever output current exceeds the allowed maximum current. When the output voltage drops below UVP, constant current limit turns off VBUS and starts the error-recovery procedure. The AP43671 will reset if the voltage continues dropping to the UVLO threshold.

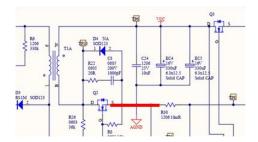

#### **Synchronization Rectifier**

In order to provide higher efficiency in the AC/DC converter system, the AP43671's built-in SR circuit replaces the schottky diode of the secondary side with a low Rds(on) MOSFET. It is suitable for low-side rectifying application systems. The AP43671 adopts proprietary SR control methodology that can work efficiently in either DCM or CCM mode. The AP43671 also has a built-in charge pump for low V<sub>OUT</sub> applications.

The AP43671 adopts a prediction method for CCM mode and detection method for DCM mode with proprietary MCU flexible control scheme. To prevent large through-current due to abnormal primary and secondary MOS turn-on, there are some criterions to guarantee safe operation. Once the minimum primary turn-on time (td\_PSON\_min) and falling slew rate meets the AP43671's threshold value, the SR controller will then recognize it as a periodical SYNC signal and the SR Gate will turn on; otherwise, the SR Gate will be disabled for at least one PWM cycle. If any large dynamic voltage/current transient occurs, the SR Gate will be turned off to avoid through-current. This can be flexibly controlled by the MCU.

To minimize the power consumption at light-load condition, AP43671 disables the SR driver and enter sleep mode when cable detach. The controller monitors the switching frequency of PWM signal and exit the burst mode.

### **Application Circuit Case**

A cost-effective 25W AC flyback adaptor schematic is shown in Figure 4 below, where the primary side uses the AP3304A (a multi-mode (QR+CCM) PWM controller) and the secondary side uses the AP43671 (a highly integrated PD controller embedded with a synchronous rectification (SR) controller). It is ideally targeted for cost-performance-sensitive USB Type-C adaptors and charger applications.

The AP3304A improves efficiency across all load levels with its multiple modes of operations, 60V processing of the VCC pin, and wide range of output applications. The device lowers BoM (bill of materials) quantity and simplifies system design for USB PD applications.

The AP43671 supports USB PD3.0 and Programmable Power Supply (PPS), and has passed the USB-IF certification. Its CC1/CC2 pins provide VBUS short protection up to 24V. Furthermore, its embedded synchronous rectification (SR) controller supports Adaptive Quasi-Resonant (QR) and Continuous Conduction Mode (CCM) for matching PWM controllers.

Figure 4. A Real 25W Flyback Adaptor based on AP43671 and AP3304A

### **Layout Guidelines**

The AP43671 performance is dramatically affected by its PCB layout. Good engineering practice of layout techniques are required to minimize parasitic inductance and signal interference; and the overshoot voltages, ringing, oscillation, and EMC issues will reduce accordingly.

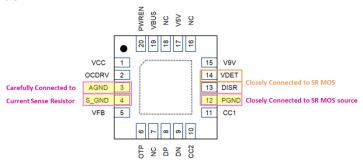

The most important guidelines for the AP43671 layout will include the current sense layout route, system ground path, and SR MOS distance from the SR controller, as shown in Figure 5.

Figure 5. AP43671 layout key points

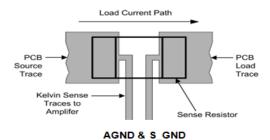

#### **Current Sense Resistor**

The four-point Kelvin connections are used for the current sense resistor.

The Kelvin sense traces should be connected to Pin3 (AGND) and Pin4 (S\_GND) of the AP43671 in parallel and equal length, and reduce the distance if possible, as shown in Figure 6.

Be noted to reduce the PCB layout distance to the current sense resistor, which will reduce parasitic effect.

Figure 6. Be Symmetrical in Layout of Current Sensing Traces.

### **GND/PGND**

To reduce impedance from Pin3 (AGND) / Pin12 (PGND) of the AP43671 to system AGND / GND, place the components according to the design priority and current direction.

According to the current direction, set the component in sequence.

Figure 7. Be Short in Ground Path.

## **Layout Guidelines**

#### **VDET and DISR**

Place the SR MOS and AP43671 as close as possible, as shown below Figure 8.

Resistor R26 needs close to PIN14 (VDET), a critical pin for SR controller, to reduce parasitic effect. It is suggested to use 100V/60V and a low Ron for SR MOS.

PIN13 (DISR) needs to reduce parasitic effect with PIN14 (VDET). The area of the PCB routing loop should not be too large, otherwise it will affect the turn-on of the SR controller.

Figure 8. Be close in placement of AP43671 and SR MOS.

#### **Decoupling Capacitor and GND**

Keep the decoupling capacitor of V5V close enough to V5V (PIN17) of the AP43671.

PGND (PIN12) is suggested to return to SR MOS source directly and independently, and avoid the cross of any high-current point to reduce interference.

#### **ESD Protection Placement**

The GND for ESD protection devices are suggested to go back to USB Type-C GND connection of the PD module. In general, ESD protection devices are put on CC1/CC2 and DP/DN of the USB Type-C connector.

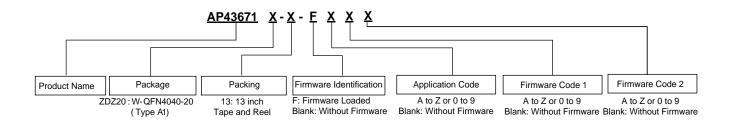

## **Ordering Information**

| Part Number     | Package                   | Identification Code | 7'Tape and Reel    |                    |  |

|-----------------|---------------------------|---------------------|--------------------|--------------------|--|

| Fait Number     | Fackage                   | identification code | Quantity           | Part Number Suffix |  |

| AP43671ZDZ20-13 | W-QFN4040-20<br>(Type A1) | В3                  | 3000/Tape and Reel | -13                |  |

# **Marking Information**

### (Top View)

XX: Identification Code

Y: Year: 0~9

<u>W</u>: Week: A~Z: 1~26 week; a~z: 27~52 week; z represents

52 and 53 week X: Internal Code

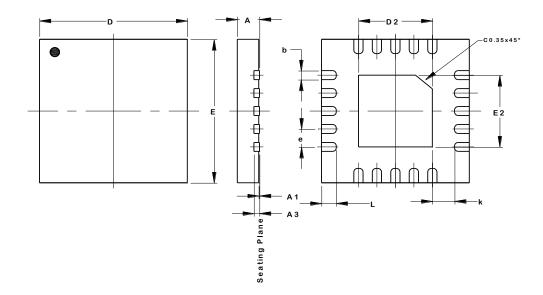

# **Package Outline Dimensions**

Please see http://www.diodes.com/package-outlines.html for the latest version.

### W-QFN4040-20 (Type A1)

| W-QFN4040-20         |                |                |      |  |  |

|----------------------|----------------|----------------|------|--|--|

|                      | (Тур           | e A1)          |      |  |  |

| Dim                  | Min            | Min Max Typ    |      |  |  |

| Α                    | 0.70           | 0.80           | 0.75 |  |  |

| A1                   | 0.00           | 0.00 0.05 0.02 |      |  |  |

| A3                   | 0.             | 203 RE         | F    |  |  |

| b                    | 0.20 0.30 0.25 |                |      |  |  |

| D                    | 4.00 BSC       |                |      |  |  |

| D2                   | 1.95 2.05 2.00 |                |      |  |  |

| Е                    | 4.00 BSC       |                |      |  |  |

| E2                   | 1.95           | 2.05           | 2.00 |  |  |

| е                    | 0.50 BSC       |                |      |  |  |

| k                    | 0.20           |                |      |  |  |

| ┙                    | 0.30           | 0.50           | 0.40 |  |  |

| All Dimensions in mm |                |                |      |  |  |

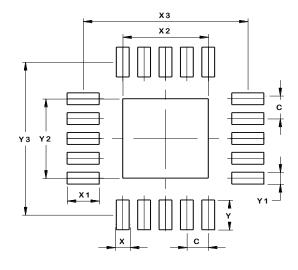

# **Suggested Pad Layout**

Please see http://www.diodes.com/package-outlines.html for the latest version.

### W-QFN4040-20 (Type A1)

| Dimensions | Value   |

|------------|---------|

| Dimensions | (in mm) |

| С          | 0.500   |

| Χ          | 0.300   |

| X1         | 0.750   |

| X2         | 2.000   |

| X3         | 3.850   |

| Υ          | 0.750   |

| Y1         | 0.300   |

| Y2         | 2.000   |

| Y3         | 3.850   |

### **Mechanical Data**

- Moisture Sensitivity: Level 1 per JESD22-A113

- Terminals: Finish Matte Tin Plated Leads, Solderable per JESD22-B102 <a>®</a>

- Weight: 0.0408 grams (Approximate)

#### **IMPORTANT NOTICE**

- 1. DIODES INCORPORATED AND ITS SUBSIDIARIES ("DIODES") MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO ANY INFORMATION CONTAINED IN THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

- 2. The Information contained herein is for informational purpose only and is provided only to illustrate the operation of Diodes products described herein and application examples. Diodes does not assume any liability arising out of the application or use of this document or any product described herein. This document is intended for skilled and technically trained engineering customers and users who design with Diodes products. Diodes products may be used to facilitate safety-related applications; however, in all instances customers and users are responsible for (a) selecting the appropriate Diodes products for their applications, (b) evaluating the suitability of the Diodes products for their intended applications, (c) ensuring their applications, which incorporate Diodes products, comply the applicable legal and regulatory requirements as well as safety and functional-safety related standards, and (d) ensuring they design with appropriate safeguards (including testing, validation, quality control techniques, redundancy, malfunction prevention, and appropriate treatment for aging degradation) to minimize the risks associated with their applications.

- 3. Diodes assumes no liability for any application-related information, support, assistance or feedback that may be provided by Diodes from time to time. Any customer or user of this document or products described herein will assume all risks and liabilities associated with such use, and will hold Diodes and all companies whose products are represented herein or on Diodes' websites, harmless against all damages and liabilities.

- 4. Products described herein may be covered by one or more United States, international or foreign patents and pending patent applications. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks and trademark applications. Diodes does not convey any license under any of its intellectual property rights or the rights of any third parties (including third parties whose products and services may be described in this document or on Diodes' website) under this document.

- 5. Diodes products are provided subject to Diodes' Standard Terms and Conditions of Sale (https://www.diodes.com/about/company/terms-and-conditions/terms-and-conditions-of-sales/) or other applicable terms. This document does not alter or expand the applicable warranties provided by Diodes. Diodes does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

- 6. Diodes products and technology may not be used for or incorporated into any products or systems whose manufacture, use or sale is prohibited under any applicable laws and regulations. Should customers or users use Diodes products in contravention of any applicable laws or regulations, or for any unintended or unauthorized application, customers and users will (a) be solely responsible for any damages, losses or penalties arising in connection therewith or as a result thereof, and (b) indemnify and hold Diodes and its representatives and agents harmless against any and all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim relating to any noncompliance with the applicable laws and regulations, as well as any unintended or unauthorized application.

- 7. While efforts have been made to ensure the information contained in this document is accurate, complete and current, it may contain technical inaccuracies, omissions and typographical errors. Diodes does not warrant that information contained in this document is error-free and Diodes is under no obligation to update or otherwise correct this information. Notwithstanding the foregoing, Diodes reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes.

- 8. Any unauthorized copying, modification, distribution, transmission, display or other use of this document (or any portion hereof) is prohibited. Diodes assumes no responsibility for any losses incurred by the customers or users or any third parties arising from any such unauthorized use.

13 of 13

www.diodes.com

Copyright © 2022 Diodes Incorporated

www.diodes.com