# Thank you for your interest in **onsemi** products.

Your technical document begins on the following pages.

# Your Feedback is Important to Us!

Please take a moment to participate in our short survey.

At **onsemi**, we are dedicated to delivering technical content that best meets your needs.

# Help Us Improve - Take the Survey

This survey is intended to collect your feedback, capture any issues you may encounter, and to provide improvements you would like to suggest.

### We look forward to your feedback.

To learn more about **onsemi**, please visit our website at **www.onsemi.com**

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, B

# Enhanced Mode GaN Power Switch with Integrated Driver

650 V, 78 m $\Omega$ , 18 A, TQFN26

### NCP58922

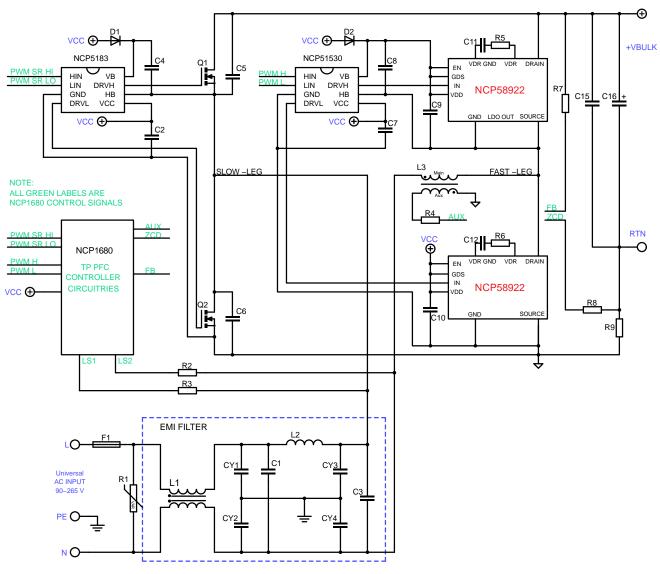

The NCP58922 integrates a high–performance, high frequency, Silicon (Si) driver and a 650 V, 78 m $\Omega$  Gallium–Nitride (GaN) High Electron Mobility Transistors (HEMT) in a single switch structure. The powerful combination of the Si Driver and power GaN HEMT Switch provides superior performance compared to discrete solution GaN HEMT and external driver. The NCP58922 integrated implementation significantly reduces circuit and package parasitics while enabling more compact design.

#### **Features**

- 650 V 78 mΩ GaN HEMT with Integrated Driver

- 30 ns Typical Driver Propagation Delay

- 8x8 mm TQFN26 Package Minimizes Parasitic Inductances

- 2.75 mm Creepage Distance for Maximum Reliability

- Driver Turn-on Process is Adjustable via External Resistor, which Enables EMI Optimization under Hard Switching Conditions

- GDS Logic Input, that Switches Driver Strength to Easy Accompanying with QR Flyback Controllers or Tweak EMI Signature

- 6.0 V Driver Clamp Voltage Regulator

- TTL Compatible Schmitt Trigger and Rail-to-rail PWM Input

- UVLO Protections for VDD and VDR Supplies

- Up to 200 V/ns dV/dt Slew Rate Transient Immunity

- 20 V Maximum VDD Ratings

- Pb-Free, Halogen Free and RoHS Compliant

#### **Typical Applications**

- Power Conversion

- High Power Density Power Supplies

- All Double-ended Topologies: Half-bridges, Full-bridge, LLC

- Active Clamp Flyback

- High-Voltage Synchronous Buck Converter

- High-Voltage Synchronous Boost Converter

- Synchronous PFC Stage

- Totem Pole PFC

CASE 518AG

#### MARKING DIAGRAM

XXXX = Specific Device Code A = Assembly Location

WL = Wafer Lot Y = Year WW = Work Week

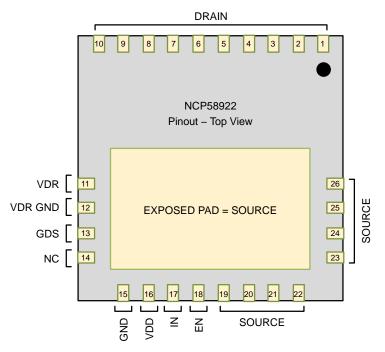

#### **PIN ASSIGMENT**

#### ORDERING INFORMATION

See detailed ordering and shipping information on page 21 of this data sheet.

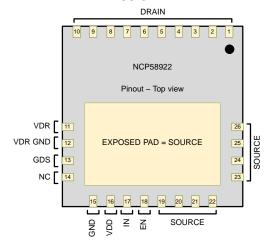

Figure 1. Minimum Application Schematic for Single Switch

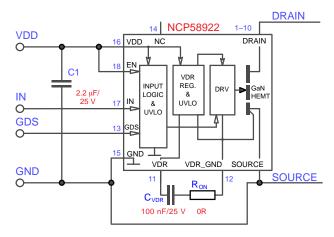

Figure 2. Application Schematic - CrM Totem-pole PFC

Figure 3. Simplified Block Diagram

Figure 4. Pin Connections

#### **PIN DESCRIPTION**

| Pin No.         | Pin Name | Function                                   | Pin Description                                                                                                                                                                           |

|-----------------|----------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1–10            | DRAIN    | GaN Power Switch Drain                     | Power path connection for the GaN Switch DRAIN                                                                                                                                            |

| 19–22,<br>23–26 | SOURCE   | GaN Power Switch Source                    | Power path connection for the GaN Switch SOURCE                                                                                                                                           |

| 11              | VDR      | Driver clamp regulator decoupling          | Connect driver clamp regulator decoupling capacitor between VDR pin and VDR GND pin. To reduce turn–on slew rate is possible connect resistor in series with driver decoupling capacitor. |

| 12              | VDR GND  | GaN Kelvin source and driver ground        | Use this pin as return path for VDR decoupling capacitor. Do not connect to SOURCE or GND pin                                                                                             |

| 13              | GDS      | Gate Drive Strength                        | According to GDS pin input level (low/ high) driver change Gate Drive Strength, thus turn-on slew rate. GDS pin can be used as interface to controller.                                   |

| 14              | NC       | Not connected                              | Not connected, (Note 1)                                                                                                                                                                   |

| 15              | GND      | Input circuitries signal ground            | Input signals should be referred to this pin                                                                                                                                              |

| 16              | VDD      | Driver supply input                        | Driver accepts up to VDD up to 20 V. Connect VDD decoupling capacitor between VDD and SGND pins.                                                                                          |

| 17              | IN       | Driver input                               | Driver signal input is 3.3 V logic compatible                                                                                                                                             |

| 18              | EN       | Logic input signal to enable the operation | Pull this pin high to allow device switching                                                                                                                                              |

<sup>1.</sup> NC Pad might be connected to trace to retain connection compatibility with NCP58921 in case of needed scalability.

#### **ABSOLUTE MAXIMUM RATINGS**

| Rating                                                                            | Symbol                  | Value                         | Unit |

|-----------------------------------------------------------------------------------|-------------------------|-------------------------------|------|

| Supply Voltage Range, Referenced to GND (Note 2)                                  | V <sub>DD</sub>         | -0.3 to 20                    | V    |

| IN, EN and GDS Inputs Voltage Range, Referenced to GND                            | IN <sub>,</sub> EN, GDS | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Driver-regulator Decoupling, Referenced to VDR_GND                                | VDR                     | -0.3 to 6.5                   | V    |

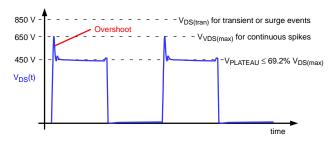

| Transient Drain-to-Source Voltage, For < 1 μs                                     | V <sub>DS(tran)</sub>   | 850                           | V    |

| Allowable Drain-to-Source Voltage Slew Rate, Device is Off                        | dV <sub>DS</sub> /dt    | 200                           | V/ns |

| Continuous Drain Current, T <sub>case</sub> = 25°C                                | I <sub>DS</sub>         | 18                            | Α    |

| Continuous Drain Current, T <sub>case</sub> = 100°C                               | I <sub>DS</sub>         | 12                            | Α    |

| Pulsed Drain Current, T <sub>case</sub> = 25°C, Pulse–width < 50 μs               | I <sub>DS-pulse</sub>   | 35                            | Α    |

| Maximum Junction Temperature                                                      | T <sub>J(max)</sub>     | 150                           | °C   |

| Storage Temperature Range                                                         | T <sub>STG</sub>        | -65 to 150                    | °C   |

| ESD Capability, Charged Device Model (Note 3)                                     | ESD <sub>CDM</sub>      | 750                           | V    |

| ESD Capability, Human Body Model (Note 3)                                         | ESD <sub>HBM</sub>      | 2.0                           | kV   |

| Lead Temperature Soldering<br>Reflow (SMD Styles Only), Pb–Free Versions (Note 4) | T <sub>SLD</sub>        | 260                           | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 2. Refer to ELECTRICAL CHĂRACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe Operating parameters.

- 3. This device series incorporates ESD protection and is tested by the following methods:

- ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114) ESD Machine Model tested per AEC-Q100-003 (EIA/JESD22-A115)

- Latch–up Current Maximum Rating: ≤150 mA per JEDEC standard: JESD78

4. For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D

#### THERMAL CHARACTERISTICS

| Rating                                                                                                                                                                          | Symbol                                                   | Value                | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------|------|

| Thermal Characteristics, TQFN26, 8x8 mm (Note 5) Thermal Resistance, Junction-to-Case (Exposed Pad) Thermal Reference, Junction-to-Top Case Thermal Resistance, Junction-to-Air | R <sub>θJC</sub><br>R <sub>θJL</sub><br>R <sub>θJA</sub> | <1.0<br>14.0<br>18.5 | °C/W |

<sup>5.</sup> Values based on copper area of 645 mm<sup>2</sup> (or 1 in<sup>2</sup>) of 2 oz copper thickness, two layers FR4 PCB substrate with black mask.

#### **RECOMMENDED OPERATING RANGES**

| Rating                                                 | Symbol                                     | Min  | Max  | Unit |

|--------------------------------------------------------|--------------------------------------------|------|------|------|

| Supply Voltage Range, (Note 7)                         | $V_{DD}$                                   | 9    | 18   | V    |

| IN, EN and GDS Inputs Voltage Range, Referenced to GND | IN <sub>,</sub> EN, GDS                    | -    | 18   | V    |

| VDR GND to GND – DC Offset Voltage                     | V <sub>VDR</sub> GND<br>– V <sub>GND</sub> | -3.5 | +3.5 | V    |

| Operation Junction Temperature                         | TJ                                         | -40  | +150 | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

# **ELECTRICAL CHARACTERISTICS** ( $V_{DD}$ = 15 V, $C_{VDD}$ = 1 $\mu$ F, $C_{VDR}$ = 0.1 $\mu$ F, for typical values $T_A$ = 25°C, $V_{BUS}$ = 400 V, unless otherwise noted. (Note 8))

| Parameter                                      | Test Conditions                                                                                                     | Symbol                  | Min  | Тур | Max | Unit |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------|------|-----|-----|------|

| GaN TRANSISTOR OUTPUT                          |                                                                                                                     |                         |      |     |     |      |

| Maximum DRAIN Voltage                          | IN = 0 V, I <sub>DSS</sub> < 35 μA                                                                                  | V <sub>DS(max)</sub>    | 650  | _   | _   | V    |

| DRAIN-SOURCE Non-synchronous<br>Drop Voltage   | I <sub>D</sub> = -1 A                                                                                               | V <sub>DSNS</sub>       | -4.5 | _   | _   | V    |

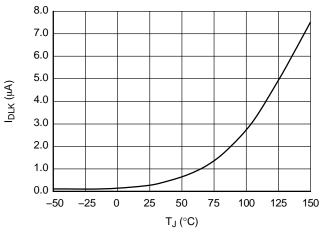

| DRAIN Leakage Current                          | V <sub>DS</sub> = 650 V, T <sub>J</sub> = 25°C, IN = 0 V                                                            | I <sub>DLK</sub>        | _    | 0.4 | 10  | μΑ   |

|                                                | V <sub>DS</sub> = 650 V, T <sub>J</sub> = 150°C, IN = 0 V, (Note 9)                                                 | I <sub>DLK</sub>        | -    | 7   | _   | μΑ   |

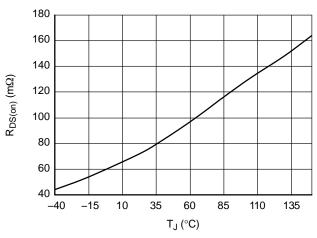

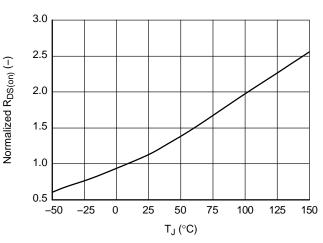

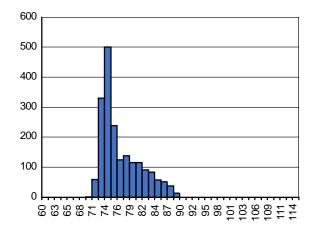

| DRAIN-SOURCE On State Resistance               | I <sub>D</sub> = 6 A, 500 μs, T <sub>J</sub> = 25°C                                                                 | R <sub>DS(on)</sub>     | _    | 78  | _   | mΩ   |

|                                                | I <sub>D</sub> = 6 A, 500 μs, T <sub>J</sub> = 150°C, (Note 9)                                                      | R <sub>DS(on)</sub>     | _    | 170 | _   | mΩ   |

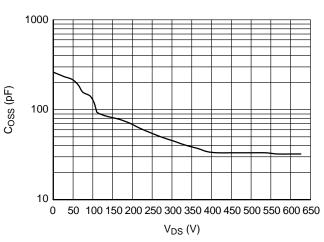

| Output Capacitance                             | IN = 0 V; V <sub>DS</sub> = 400 V, f = 100 kHz                                                                      | C <sub>OSS</sub>        | _    | 34  | _   | pF   |

| Output Capacitance Energy Related              | (Note 10, 12)                                                                                                       | C <sub>OSS(er)</sub>    | _    | 58  | _   | pF   |

| Output Capacitance Time Related                | (Note 11, 12)                                                                                                       | C <sub>OSS(tr)</sub>    | _    | 90  | _   | pF   |

| Output Charge                                  | V <sub>DS</sub> = 400 V, V <sub>IN</sub> = 0 V, (Note 12)                                                           | Q <sub>OSS</sub>        | _    | 37  | _   | nC   |

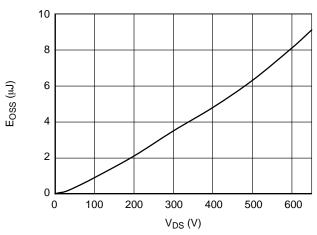

| Energy Stored in Output Capacitance            | IN = 0 V, V <sub>DS</sub> = 400 V, (Note 12)                                                                        | E <sub>OSS</sub>        | _    | 4.4 | _   | μJ   |

| Reverse Recovery Charge                        | (Note 12)                                                                                                           | Q <sub>RR</sub>         | -    | 0   | _   | nC   |

| POWER SUPPLY SECTION (VDD)                     |                                                                                                                     |                         |      |     |     |      |

| Quiescent Current                              | V <sub>EN</sub> = 0 V, V <sub>DD</sub> = 15 V                                                                       | I <sub>DDQ1</sub>       | _    | 55  | 75  | μΑ   |

|                                                | V <sub>EN</sub> = 5 V, V <sub>DD</sub> = 15 V,                                                                      | I <sub>DDQ2</sub>       | _    | 54  | 75  | μΑ   |

| Supply Current, Device Idle + EN Input Current | V <sub>EN</sub> = 15 V, V <sub>DD</sub> = 15 V, V <sub>IN</sub> = 0 V                                               | I <sub>DDQ1+ EN</sub>   | -    | 100 | _   | μΑ   |

| Operating VDD Supply Current                   | $V_{EN} = 5 \text{ V}, V_{GDS} = 0 \text{ V}, V_{DD} = 15 \text{ V},$<br>$f_{IN} = 500 \text{ kHz} 50\% \text{ DC}$ |                         | -    | 1.7 | 2.8 | mA   |

| UVLO ON Threshold                              | VDD Rising                                                                                                          | V <sub>UVLO_R</sub>     | _    | 8.5 | 9   | V    |

| UVLO OFF Threshold                             | VDD Falling                                                                                                         | $V_{UVLO_F}$            | 7.5  | 8   | _   | V    |

| UVLO Hysteresis                                |                                                                                                                     | V <sub>UVLO_HYST</sub>  | -    | 0.5 | _   | V    |

| UVLO Filter Delay Time                         | VDD Rising                                                                                                          | t <sub>UVLO_DEL_R</sub> | -    | 3   | _   | μs   |

| UVLO Filter Delay Time                         | VDD Falling                                                                                                         | tuvlo del f             | _    | 3.2 | _   | μS   |

<sup>6.</sup> Maximum Recommended Operating Drain-tó-Source Voltage or DC Bus Voltage must be considered voltage overshoots due to parasitic inductance in power loop. See page Application Drain-to-Source Voltage and its maximum recommended value.

<sup>7.</sup> The minimum VDD Supply Voltage should be high enough above UVLO-off level to avoid unwanted device turn-off during dynamic operation.

**ELECTRICAL CHARACTERISTICS** (V<sub>DD</sub> = 15 V, C<sub>VDD</sub> = 1  $\mu$ F, C<sub>VDR</sub> = 0.1  $\mu$ F, for typical values T<sub>A</sub> = 25°C, V<sub>BUS</sub> = 400 V, unless otherwise noted. (Note 8)) (continued)

| Parameter                                                          | Test Conditions                                | Symbol                  | Min | Тур  | Max | Unit |

|--------------------------------------------------------------------|------------------------------------------------|-------------------------|-----|------|-----|------|

| IN, EN INPUTS                                                      |                                                | •                       |     |      |     |      |

| IN Input High-Logic-Level Voltage                                  | IN / EN Rising                                 | $V_{IN\_H}$             | -   | 2.1  | 2.5 | V    |

| IN Input Low-Logic-Level Voltage                                   | IN / EN Falling                                | $V_{IN\_L}$             | 1.2 | 1.5  | _   | V    |

| Logic Input Voltage Hysteresis                                     |                                                | V <sub>IN_HYST</sub>    | _   | 0.6  | -   | V    |

| High-Level Logic Input Bias Current                                | V <sub>IN</sub> = 5 V / V <sub>EN</sub> = 5 V  | I <sub>IN+</sub>        | _   | 15.3 | _   | μΑ   |

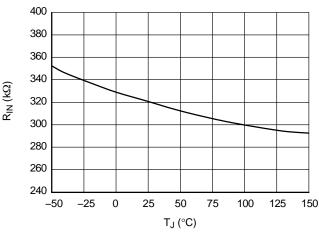

| Input Pull-down Resistance                                         | V <sub>IN</sub> = 5 V / V <sub>EN</sub> = 5 V  | R <sub>IN</sub>         | 250 | 327  | 400 | kΩ   |

| GDS INPUT                                                          |                                                |                         |     |      |     |      |

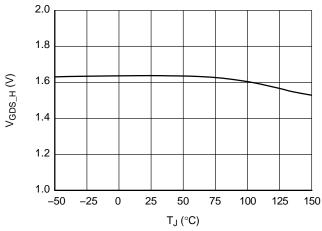

| High-Level Logic Input Voltage                                     | GDS Rising                                     | $V_{GDS\_H}$            | _   | 1.62 | 1.8 | V    |

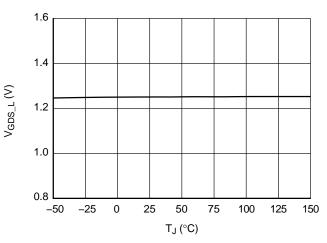

| Low-Level Logic Input Voltage                                      | GDS Falling                                    | $V_{GDS\_L}$            | 1.1 | 1.24 | _   | V    |

| Logic Input Voltage Hysteresis                                     |                                                | V <sub>GDS_HYST</sub>   | _   | 0.38 | -   | V    |

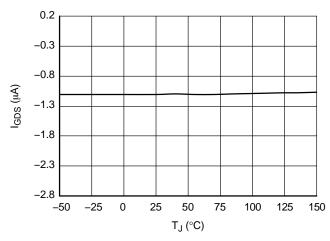

| Input Pull-up Current Source                                       | Current source referred to internal 5 V        | I <sub>GDS_PULLUP</sub> | _   | 1    | _   | μΑ   |

| Driver SRC Resistance ("Weak" Driving Level or Low Slew Rate)      | V <sub>GDS</sub> = LOW                         | R <sub>SRC_weak</sub>   | -   | 300  | -   | Ω    |

| Driver SRC resistance ("Strong" Driving Level or Higher Slew Rate) | V <sub>GDS</sub> = HIGH, (Note 12)             | R <sub>SRC_strong</sub> | -   | 10   | -   | Ω    |

| GATE DRIVER REGULATOR SECTION                                      |                                                |                         |     |      |     |      |

| V <sub>DR</sub> – V <sub>VDR_GND</sub> Regulated Voltage           | 0 mA < I <sub>O,DR</sub> < 10 mA               | $V_{DR}$                | 5.7 | 6    | 6.5 | V    |

| VDR UVLO ON Threshold                                              | VDR Rising                                     | $V_{UVTH_{R}}$          | -   | 5.5  | 5.8 | V    |

| VDR UVLO OFF Threshold                                             | VDR Falling                                    | $V_{UVTH_{F}}$          | 4.6 | 5    | -   | V    |

| VDR UVLO Hysteresis                                                |                                                | V <sub>UVTH_HYST</sub>  | -   | 0.5  | -   | V    |

| TIMING CHARACTERISTICS                                             |                                                |                         |     |      |     |      |

| Switching Frequency                                                |                                                | f <sub>SW</sub>         | -   | -    | 1   | MHz  |

| Switch Maximal Turn-On Time                                        | (Note 13)                                      | t <sub>ON(MAX)</sub>    | -   | -    | 1   | ms   |

| Switch Minimal Turn-On Time                                        |                                                | t <sub>ON(MIN)</sub>    | 25  | -    | _   | ns   |

| Switch Minimal Turn-Off Time                                       |                                                | t <sub>OFF(MIN)</sub>   | 25  | -    | -   | ns   |

| Driver to Switch Turn-on Propagation Delay                         | (Note 14)                                      | t <sub>PD_ON</sub>      | -   | 19   | -   | ns   |

| Driver to Switch Turn-off Propagation Delay                        | (Note 14)                                      | t <sub>PD_OFF</sub>     | -   | 17   | _   | ns   |

| Switch Drain to Source Rise Time                                   | $R_{ON} = 0 \Omega$ , $I_L = 10 A$ , (Note 14) | t <sub>R</sub>          | -   | 8    | -   | ns   |

|                                                                    | $R_{ON} = 0 \Omega$ , $I_D = 10 A$ , (Note 14) | t <sub>F</sub>          |     | 9    |     |      |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Production performance may not be indicated by the Electrical Characteristics if operated under different conditions.

8. Performance guaranteed over the indicated operating temperature range by design and/or characterization tested at  $T_J = T_A = 25^{\circ}C$ .

9. Low duty cycle pulse techniques are used during testing to maintain the junction temperature as close to ambient as possible.

10.  $C_{O(ER)}$  is the fixed capacitance that would give the same stored energy as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 V to the stated  $V_{DS}$ .

11.  $C_{O(TR)}$  is the fixed capacitance that would give the same charging time as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 V to the stated  $V_{DS}$ .

12. The parameter is not tested in the production; value is guaranteed by the design.

- 13. Internally limited by driver, do not use switch for continuous DC conduction.

- 14. Refer to Figure 37 and Figure 38.

#### TYPICAL CHARACTERISTICS

Figure 5. R<sub>DS(on)</sub> Drain-Source Turn-On Resistance vs. Temperature

Figure 6. Normalized R<sub>DS(on)</sub> vs. Temperature

Figure 7. R<sub>DS(on)</sub> Histogram

Figure 8. I<sub>DLK</sub> Drain-Source Leakage Current vs. Drain-Source Voltage

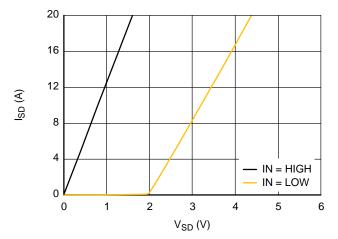

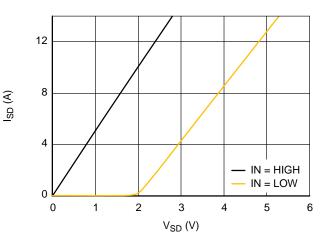

Figure 9. Typical VSD Drop vs. IDS and IN = 0 V at  $TJ = 25^{\circ}C$

Figure 10. Typical VSD Drop vs. IDS and IN = 0 V at TJ = 150 °C

#### TYPICAL CHARACTERISTICS (CONTINUED)

Ιρρα2 (μΑ)

Figure 11. Output Capacitance Stored Energy vs.

Drain-Source Voltage

Figure 12. Output Capacitance vs. Drain-Source Voltage

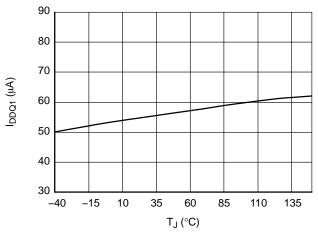

Figure 13.  $I_{DDQ1}$  Quiescent Supply Current vs. Temperature, VDD = 15 V, EN = 0 V, IN = 0 V

Figure 14.  $I_{DDQ2}$  Quiescent Supply Current vs. Temperature, VDD = 15 V, EN = 5 V, IN = 0 V

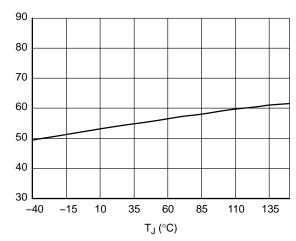

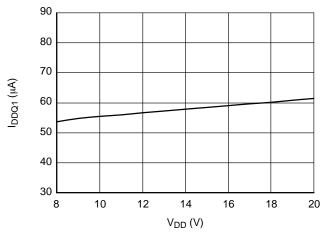

Figure 15. I<sub>DDQ1</sub> Quiescent Supply Current vs. VDD Supply Voltage, IN = 0

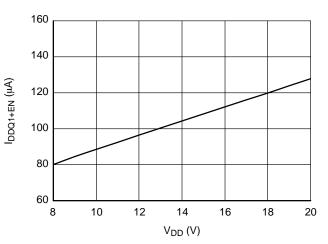

Figure 16. I<sub>DDQ1</sub> + IEN Supply Current vs. VDD Supply Voltage, EN = VDD, IN = 0

#### TYPICAL CHARACTERISTICS (CONTINUED)

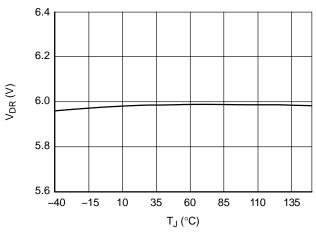

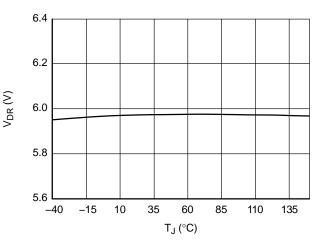

Figure 17.  $V_{DR}$  Driver Voltage vs. Temperature, IN = 0,  $R_{ON}$  = 0

Figure 18.  $V_{DR}$  Driver Voltage vs. Temperature, IN = 0,  $R_{ON}$  = 0, External Load 10 mA

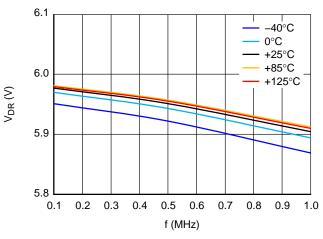

Figure 19.  $\text{V}_{\text{DR}}$  Driver Voltage vs. Frequency,  $\text{R}_{\text{ON}}$  = 0  $\Omega$

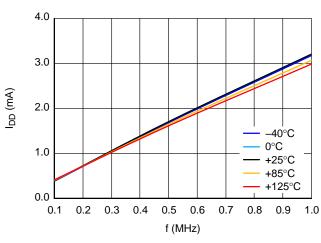

Figure 20. I<sub>DD</sub> Supply Current vs. Frequency,  $R_{ON} = 0 \Omega$ , Open Drain

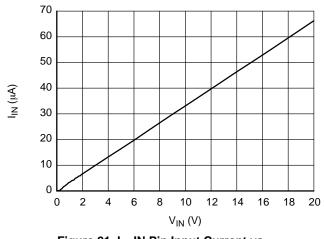

Figure 21.  $I_{\text{IN}}$  IN Pin Input Current vs.  $V_{\text{IN}}$  Input Voltage, 25°C

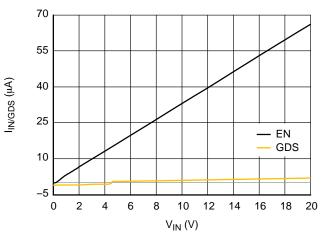

Figure 22.  $I_{EN}$ ,  $I_{GDS}$  EN and GDS Pin Input Current vs.  $V_{EN}$  Input Voltage, 25°C

#### TYPICAL CHARACTERISTICS (CONTINUED)

In (µA)

30 25 20 15 10 5 75 -25 0 25 50 100 125 150 -50 T<sub>J</sub> (°C)

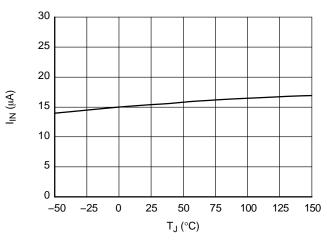

Figure 23.  $I_{IN}$  IN Input Current vs. Temperature,  $V_{IN} = 5 \text{ V}$

Figure 24.  $I_{EN}$  EN Input Current vs. Temperature,  $V_{IN} = 5 \text{ V}$

Figure 25. R<sub>IN</sub> IN Input Resistance vs. Temperature

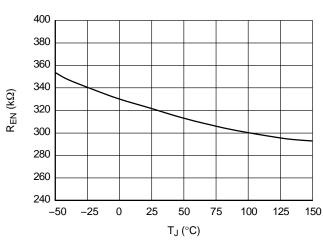

Figure 26.  $R_{\text{EN}}$  EN Input Resistance vs. Temperature

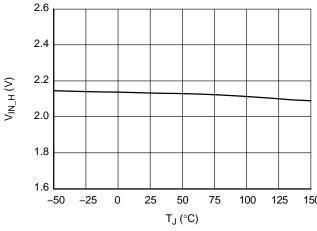

Figure 27.  $V_{\text{IN\_H}} V_{\text{IN\_H}}$  Input Threshold vs. Temperature

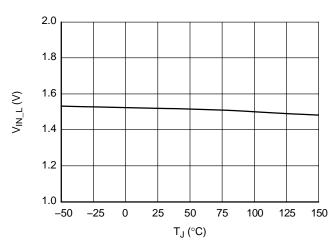

Figure 28.  $V_{\text{IN\_L}}$  IN Input Threshold vs. Temperature

### TYPICAL CHARACTERISTICS (CONTINUED)

Ven\_L (V)

2.0

1.8

1.6

1.4

1.2

-50 -25 0 25 50 75 100 125 150

T<sub>J</sub> (°C)

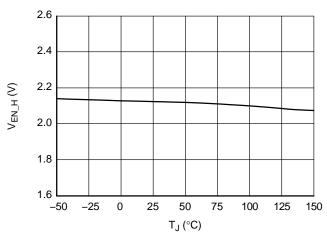

Figure 29. V<sub>EN H</sub> Input Threshold vs. Temperature

Figure 30. V<sub>EN L</sub> Input Threshold vs. Temperature

Figure 31. V<sub>GDS\_H</sub> GDS Input Threshold vs. Temperature

Figure 32.  $V_{GDS\_L}$  GDS Input Threshold vs. Temperature

Figure 33. IGDS Input GDS Current vs. Temperature, VGDS = 15 V

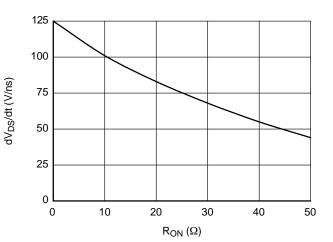

Figure 34. Half-bridge Turn-On dv/dt vs. R<sub>ON</sub> Resistance

### TYPICAL CHARACTERISTICS (CONTINUED)

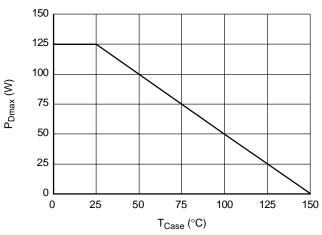

Figure 35. Power Derating vs. Case Temperature

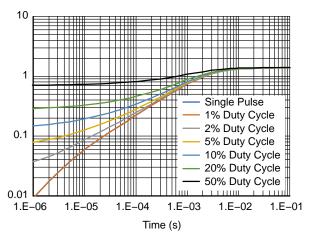

Figure 36. Transient Thermal Impedance

#### **DEFINITIONS**

#### General

All measurements are performed using short pulse low duty cycle techniques to maintain junction temperature as close as possible to ambient temperature.

#### **Switching Test Circuit**

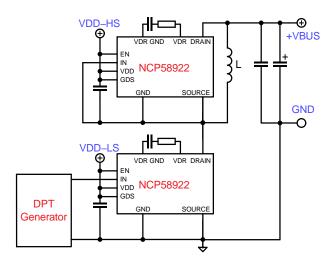

Figure 37. Half-bride Stage Arranged as Double-pulse Tester Circuit

A typical approach to determine timing parameters of switching devices is to test them in double-pulse tester or use double-pulse testing technique. The half-bridge is a basic switching structure adopted in a wide range of converter topologies, that is easy to convert into double-pulse tester. Figure 37 shows principle schematic diagram of circuit (double-pulse test) that is used to measure switching parameters. The low-side device NCP58922 is the part that actively switches. When the device is turned on, the Inductor current is built to the certain level. The inductor current for this switching interval is almost the same as Drain current and its level is basically related to +VBUS Voltage, Inductance, and turn-on pulse width (the initial current must be considered). When Low-Side device is turned-off, inductor current cannot be interrupted (or cannot change direction), so the high-side device NCP58922 naturally turns-on, operates in third quadrant and its function is the same as freewheeling diode which enables inductor current re-circulation. Operation in the third quadrant should be well considered to avoid generating excessive losses and thus device overheating. Dedicated sequence of pulses creates operating conditions that are sufficient for generating switching waveforms and measuring required parameters. The specific timing measurement is shown in. Figure 38.

#### **Timing Characterization Reference**

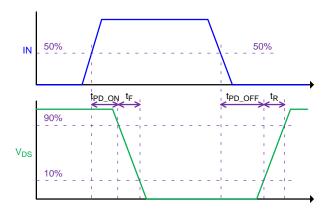

The timing of the turn—on transition is composed of two parameters: Driver to Switch Turn—on propagation delay,

Switch  $V_{DS}$  Voltage fall time. The first one component is the propagation delay of the driver from when the input goes high, measured at 50%, to when the GaN HEMT starts turning—on, while its  $V_{DS}$  voltage drops to 90% of +VBUS. The fall time is the time that takes for Switch  $V_{DS}$  Voltage to slew between 90 percent and 10 percent of +VBUS voltage. The  $R_{ON}$  (Turn—on) resistor value has significant impact on Turn—on slew rate while the Turn—on propagation delay influence is minor. The timing definition of the turn—off transition also has two components; Driver to Switch Turn—off propagation delay and  $V_{DS}$  Voltage rise time. Reference levels are the same, however difference lays in opposite order. For better explanation reference waveform is depicted in Figure 38.

Figure 38. Measurement Reference for Determining Timing

#### **High Speed Measurement Practice**

In general, the GaN HEMTs have a significantly faster switching performance than Silicon and Silicon-Carbide MOSFETs. It's essential to use proper measuring techniques to evade the parasitic elements introduced by test equipment, that may distort device parameters and lead to inaccurate measurement results. A long probing ground wire inserts undesired inductance into the probe measurement path, which results in overshoot and ringing linked to the rising and falling edges of the measured signals. Minimizing the length of the ground loop is important especially for signals which have very high dv/dt level. At least, it's recommended to use so called "pigtail" that helps to reduce probe grounding inductance and thus provides more accurate measurement. Further, it's advised to use an oscilloscope and a probe with BW more than 350 MHz, while it should be considered edge slope time distortion approximately 1.5 ns.

#### **Maximum Package Power Dissipation**

The power dissipation level is maximum allowed power dissipation for package or power dissipation at which the junction temperature reaches its maximum operating value, whichever is lower.

# NCP58922 Application Drain-to-Source Voltage and its Maximum Recommended Levels

The NCP58922 has been designed to offer design margin to withstand transient and continuous voltage levels that are typically seen in the Half-bridge stage-based topologies, such as Buck or Boost Converters, Totem-pole PFC, LLC and so on. The various voltage levels and recommended margins in a typical Half-bridge based converter is described using Figure 39. VDS(TRAN) rating is the voltage level of events that occur on a non-repetitive basis (occasional event), such as line surge, lightning strikes, start-up, over-current, short-circuit, load transient, and output voltage transition.  $V_{DS(TRAN)} = 850 \text{ V}$  ensures device robustness and derating is not required for non-repetitive events when the transient time duration is < 100 us. After the device is turned off, the energy stored in parasitic inductances (stray and leakage inductance of magnetics and PCB layout) creates overshoot voltage stress V<sub>DS</sub>(t) that is applied to Drain-Source terminals. It is necessary to design a clamp circuit that limits V<sub>DS</sub> continuous overshoot to V<sub>DS(max)</sub> 650 V level under the

worst case steady–state operating conditions. After consuming energy from parasitic inductances, the device VDS will drop to the level given by sum of the bus voltage and the reflected output voltage which is shown in Figure 39 as  $V_{PLATEAU}$ . It is recommended to design the system in such way that  $V_{PLATEAU}$  level is maximally 69.2% of  $V_{DS(max)} = 650$  V, thus  $V_{PLATEAU} \le 450$  V or in other words high voltage supply VBUS is limited to 450 V. The recommended DC Bus voltage,  $V_{PLATEAU}$  (in Figure 39) is not guaranteed spec.

Figure 39. Drain-to-Source Voltage Definition

#### **APPLICATIONS INFORMATION**

#### **Minimum Schematic Diagram**

The NCP58922 is an Integrated Device containing Power GaN HEMT Switch and Silicon Integrated Control Circuit that is equipped with dedicated two Quadrant Clamped Regulator, Driver, Level Shifter, and Input Logic circuitries. Device features VDD & VDR UVLO. Refer to following sections to gather more information. In Figure 1 is depicted minimum component circuit of a single switch, while typical application circuit Half-bridge LLC Stage is shown in Figure 2.

#### **Benefits Integrated Driver GaN**

Integrating the driver and GaN HEMT into one package is a logical step in development. Short Kelvin–connection between GaN switch and driver diminishes coupling link from Source common inductance of power terminal and minimizes the inductances between the driver output and GaN switch Gate terminals. Integrated solution offers clean driving waveforms, higher dv/dt immunity and simplified PCB design layout as well as reduces required PCB area.

#### **VDD Supply Voltage**

A DC voltage applied to VDD provides bias for the digital inputs, internal logic circuitries as well as providing bias directly to the internal driver voltage regulator (VDR) and subsequently to the driver. The GaN HEMT is driven by high-speed driver thus it requires higher current level during short charging interval of gate capacitance. This supply current is delivered through an internal regulator, from VDD bypass capacitor C<sub>VDD</sub>, that is required to decouple V<sub>DD</sub> Supply Voltage. CVDD must be connected directly between the VDD and GND pins. The C<sub>VDD</sub> capacitor should be a ceramic capacitor at least with capacitance 1 µF, located as close as possible to supply pins to properly filter out all glitches while device is switching. Use series resistance 3-30  $\Omega$  which forms low-pass filter that limits I<sub>DD</sub> peak current and minimizes noise passing through the supply rails. Also, ferrite-bead may be adopted. Under-Voltage Lock Out (UVLO) is important for protecting device and power stage against running with insufficient supply voltage. The NCP58922 includes UVLO thresholds of  $V_{UVLO\_R} > 8.5$  V, ON and  $V_{UVLO\_F} < 8$  V, OFF, making it well suited for +12 V bias rails. UVLO protection is also implementing delay filters (refer to Electrical characteristic table) that avoid unwanted UVLO protection trigger due to noise or glitch of VDD bias voltage.

#### **GND Signal Ground, VDR GND and SOURCE**

The GND is the reference ground for internal control logic and all digital inputs. The GND and VDR\_GND are two Driver IC grounds, that are separated by bidirectional level shifter structure that can handle DC offset ±3.5 V (see rating section). VDR\_GND is interconnected with GaN SOURCE internally and VDR\_GND is practically Kelvin–SOURCE of power switch. It's NOT ALLOWED to supply device while GND is separated from VDR\_GND or SOURCE. It is

forbidden to connect VDR\_GND to SOURCE. Two connections are allowed:

- GND may be connected to SOURCE for lower power application up to 500 W. When GND is tied to SOURCE, it must be done in place where no power-loop (Drain) current flows (Exposed pad corner that is close to GND pin) to ensure the noise injection into control signal is minimized.

- GND may be connected to VDR\_GND especially in high-power applications that feature high di/dt level, and this may overstress level shifter. That's the main reason for merging GND with VDR GND.

#### **VDR Internal Driver Voltage Regulator**

The NCP58922 includes an internal linear driver regulator (VDR) dedicated to providing a tightly regulated, 6 V gate drive amplitude level to the GaN HEMT. The VDR regulator is fed directly from VDD, providing the most direct interface to the internal GaN HEMT Switch. This assures the lowest possible parasitic inductance, required to avoid ringing gate drive circuit. The VDR regulator is referenced between VDR and the VDR GND (Kelvin-Source). Source current for the GaN HEMT is provided from the charge stored in the CVDR connected between VDR and VDR GND. The recommended value of the CVDR capacitor is 100 nF. As CVDR capacitor is recommended to use multi-layer ceramic capacitor (MLCC) while preferred dielectric material is X7R. The VDR regulator also includes dedicated UVLO thresholds of VUVTH\_R > 5.5 V, ON and VUVTH\_F < 5 V, OFF which protects GaN HEMT against running in higher level of R<sub>DS(on)</sub> resistance.

#### NCP5892x Turn-on Slew-rate (dv/dt) Adjustment

The NCP58922 enables Turn-on Slew-rate (dv/dt) adjustment via RON resistance in series with VDR decoupling C<sub>VDR</sub> capacitor (refer to Figure 1) Recommended VDR decoupling capacitor is Multi-Layer Ceramic Capacitor (MLCC) X7R material. C<sub>VDR</sub> capacitance is 100 nF, higher voltage rating than 25 V provides better thermal/voltage stability. Always, append series resistance (R<sub>ON</sub>) that allows to set turn-on slew rate and permits application debugging. Recommended starting  $R_{ON}$  value is 33  $\Omega$ .  $R_{ON}$  resistance level depends on application requirements as well as operating frequency, however 100  $\Omega$  should be considered as maximum value. Users ought to thoroughly check switching performance for R<sub>ON</sub> value in given application and conditions. The reason is that PCB layout parasitic capacitance as well as inductor parasitic capacitance and power loop stray inductance impact switching behavior.

#### **IN – Device PWM Input**

The IN Input is the PWM input with Schmitt trigger, Transistor-Transistor Logic (TTL) compatible and it's internally pulled low to GND (see parametric table) such that

corresponding driver input is defaulted to the inactive state. The TTL input thresholds provide buffer and logic level translation functions capable of operating from a variety of PWM signals up to VDD level of the NCP58922. TTL levels permit the input to be driven from a range of input logic signal levels for which a voltage greater than 2.1 V typically is considered logic high. Both input thresholds meet industry–standard TTL–logic defined thresholds and are therefore independent of VDD voltage. A typical hysteresis voltage of 0.6 V is dedicated to driver IN input (similarly EN Input). For optimal high–speed switching performance, the driving signal for the TTL inputs should have fast rising and falling edges with a slew rate that results in a reasonable rise

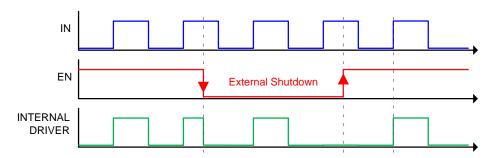

time and fall time, so maximally few percent of switching period. Switching power systems contain a lot of noise level, so due to this is recommended to implement a low–pass RC filter that filters out noise coming from switching events. The RC filter must have small time constant which introduces only minor time delay that response impact is minimal. The RC Resistor value may be in range  $10{\text -}100~\Omega$ , further RC capacitor capacitance range might be up to several hundreds of pF, however their combination must give short time constant. It should be noted that IN input is edge sensitive while EN input is level sensitive, for better understanding refer to Figure 40.

Figure 40. EN/IN Inputs Timing Behavior

#### **EN - Device Enable Input**

EN is internally pulled low to GND, so the driver is always defaulted to a disabled or idle status. Similarly, as IN Input, the EN is a Schmitt trigger TTL compatible input. Pulling the EN pin above 2.1 V typically enables the output, placing device into an active ready state. Due to the nature of high–speed switching associated with GaN power stages, and for improved noise immunity, it is recommended to connect the EN pin to VDD through a  $100\,\Omega$  pull–up resistor or directly to VDD. EN pin has fast response and noise may be caught by device input circuitries then GaN switch could be prematurely turned–off. For applications where the EN pin is actively controlled, the EN pin can be driven directly but should be bypassed with at least 1 nF decoupling

capacitor which is placed as close as possible to device EN pin. Also, as in previous case, EN input series resistance helps to form RC filter that filter out unwanted noise. As it is shown in Figure 40, if EN is pulled low during normal operation, the driver output is immediately disabled, even terminating an active IN pulse mid-cycle during the on-time. When EN is toggled high, during normal operation, a cycle-by-cycle, edge-triggered logic function is employed to prevent shortened, erroneous control pulses from being processed by the output. This behavior is highlighted in Figure 40, where EN transitions high at the same time the IN-input pulse is high. In this way, the NCP58922 is intelligent by waiting until the next rising edge to process the full input signal to the output driver stage.

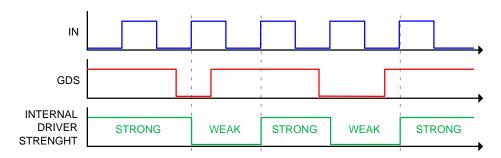

Figure 41. GDS Input Timing Behavior

#### **GDS Input – Gate Drive Strength**

Similarly, as EN Input, the GDS is a Schmitt trigger input, which typically high and low levels are 1.6 and 1.2 V, respectively. GDS Input Gate Drive Strength sets Driver

turn–on resistance. If the GDS pin is at low–level, then turn–on resistance is approximately 300  $\Omega$ . If GDS is pulled to high–level, then turn–on resistance is 10  $\Omega$ . When GDS is controlled externally, use a small filter to filter out noise

that may come from high-speed switching. If GDS feature is not needed and driver strength should be set to high level, then it's better to pull-up GDS pin to VDD via low impedance  $< 100 \Omega$  – same approach as in case of EN pin. The NCP58922 GDS feature is dedicated for accompanying device with Active Clamped Flyback controller NCP51568. In a such implementation is GDS input controlled based on NCP1568 FB signal, which sets "Low Driver Strength" for low FB levels (during burst mode or light-load mode) and "High Driver Strength" for power level, that pushes FB signal level above high threshold. GDS Input is level sensitive, and its proper level must be set approximately 15 ns before PWN (IN) signal edge comes. Once driver strength is confirmed by PWM rising edge, its level is kept until next PWM rising edge is introduced. GDS signal does not have any impact during mid-cycle change or after active level cycle change. GDS Input timing dependency is depicted in Figure 41.

#### **Boot-strap Circuit**

Typically, boot-strap supply is not fully recommended for Hard-switched applications as these are characteristic with high dv/dt level as well as big noise level, that may strongly affect operation. For lowering VDD supply noise caused by bootstrapping, it's possible to use independent capacitor that is connected to low-side VDD supply via resistor while SOURCE is used for capacitor ground. As bootstrap diode, implement soft-recovery diode with low capacitance and low reverse recovery charge Q<sub>RR</sub> like NHP160. Also, add series resistance to limit peak current. Another good option for how to reduce current peak is a ferrite bead (100  $\Omega$  @ 100 MHz). A higher resistance bootstrap resistor as well as shorter dead-time may help to prevent overcharge high side floating supply. If low side is supplied more than 16 V, it's suggested to add Zener diode clamp to limit bootstrap supply voltage and avoid overstressing or even destruction of high-side circuitry. Further, it helps to separate NCP58922 VDD supply terminal and Level Shifter or Isolator VCC supply pin with resistor to avoid charge exchange and thus current spikes between decoupling capacitor, especially during switching transition. It's recommended to evaluate bootstrapping solution and adjust component values with respect to application. To summarize above use following pars and approach at application developing phase:

- Bootstrap diodes; NRVHP160SF, NRVHP260SF, or ES1JFL

- Bootstrap resistor 5–10  $\Omega$  or ferrite bead with recommended impedance at least 100  $\Omega$  @ 100 MHz

- Short Dead–time < 150 ns, prevent staying device too long in 3<sup>rd</sup> quadrant.

- Use Zener diode clamp (MMSZ18T1G) or regulator for high side.

- Measure bootstrap current peak and check bootstrap diode commutation especially during dead–time phase.

#### Half-Bridge Stage Decoupling

Use at least one high–voltage 100 nF MLCC for Half–Bridge Stage  $+V_{BUS}$  supply decoupling. However, it's strongly recommended to implement more capacitors, same or mixture multiple values to ensure more advanced filtering. It should be noted that minimum capacitance should be more than 100 nF, while lower capacitance is deployed, there is high risk of capacitor damage as it might not accept energy stored in power loop stray inductance.

#### **Soft-Switched Application**

For soft switching topologies like CrM TP PFC, ZVS Buck or Boost Converters, the NCP51530 can be used as level shifter. A similar solution may be implemented for LLCs NCP1399x family, and its internal HB driver provides level shifting same way as NC51530. High–side portion of converter can be supplied via bootstrap circuit while appropriate bootstrap components and dead–time should be used as mentioned in Boot–strap circuit section.

#### Hard-Switched Application

For hard–switched application CCM PFC, CCM Buck or Boost Converters is highly recommended to use digital isolator such as NCP51561. Also, it's recommended to implement floating supply or insulated DC/DC converter for High–Side portion, especially when application is being developed or debugged. Bootstrap supplying for High–Side was tested up to 1 kW in CCM TP PFC and must be noted that proper PCB layout is necessary. Follow recommendation for boot–strap circuit from previous text. Hard–Switched applications generate high noise levels, that may impact input signal. Use input RC filter to filter out noise and glitches caused by Hard Switching event.

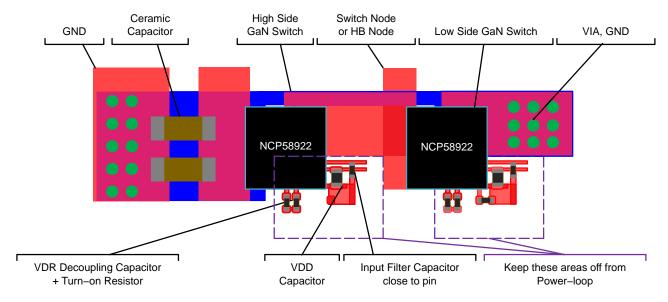

#### **General Rules for PCBs**

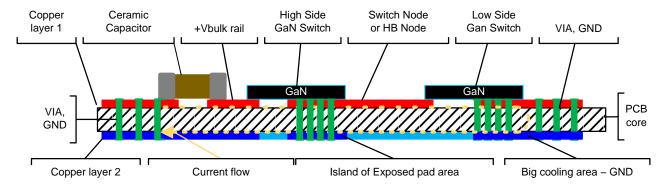

Use at least 2 oz or 70 µm copper thickness PCB, however preferred copper thickness is 2.5-3 oz (90-105 µm) due to thermal performance. 2-layers PCB is the minimum for lower power application < 400 W. PCB thermal resistance, application surface and related heat spreading capability must be well-thought-out. PCB layout design complexity must be considered and if it's too high switch to 4-layers. 4-layers PCB is preferred minimum for application that has higher power > 400 W. Use thermal vias for exposed pads to transfer heat from device to opposite side of PCB and further to heatsink if needed. For applications where power losses dominate it's recommended to mount device on Insulated Metal Substrate board (IMS). From an electrical point of view, it is important to design power loops using flux cancelation loop. For Half-Bridge power loop use flux cancelation technique that is depicted in Figure 42 and Figure 43. Do not create unreasonable big structure, keep Half-Bridge stage compact, the best is to place both half-bridge switches in one line with decoupling MLCC capacitors as in Figure 42. +VBUS or +VBULK ceramic bypass capacitors must be close to the DRAIN of high-side

switch or SOURCE of low-side switch. Return trace should be as short and direct as possible. This reduces power loop area thus power loop stray inductance that minimize switching node overshoots. Switching node and return-GND trace overlay area should be small as possible, so it won't add too much parasitic capacitance that increase switching losses, however this is not always possible.

All high—current power loop coppers traces, such as +VBUS or +VBULK, SW and SOURCE – power GND; should be short and wide enough to keep low parasitic inductance and resistance. This helps achieve a more stable and evenly distributed current flow, along with better heat radiation and system performance.

Figure 42. Half-Bridge Stage PCB Layout Recommendation

# **General Rules for Placing and Routing Surrounding Components**

First do not mix power loop together with supply rails or input control signal traces. Supply decoupling and filter capacitors should be placed as close to device as possible (see Figure 42). NCP58922 GND must be connected to Source or VDR\_GND in the shortest possible way. If GND is tied with SOURCE, then it should be in the corner of

exposed pad that is located next GND pad. The VDR regulator components (C<sub>VDR</sub>, R<sub>ON</sub>) must be kept away from power traces, especially DRAIN voltage. Minimize area of VDR regulator parts as well as traces and do not short VDR\_GND to Source. Under surrounding components place shielding ground connected to device GND at one place close to GND pad. Shielding layer mustn't conduct current from power loop (DRAIN–SOURCE).

Figure 43. Half-Bridge Stage PCB Layout Cut View

#### **Thermal Guidelines**

Power devices like NCP58922 may dissipate significant amounts of power losses. It's helpful to estimate power dissipation level and calculate maximal thermal resistance of entire cooling chain for allowable temperature rise or

maximum junction temperature  $T_{jmax}$ . Proper PCB layout design and cooling chain design ensure that the device will operate within acceptable temperature limits in the final application.

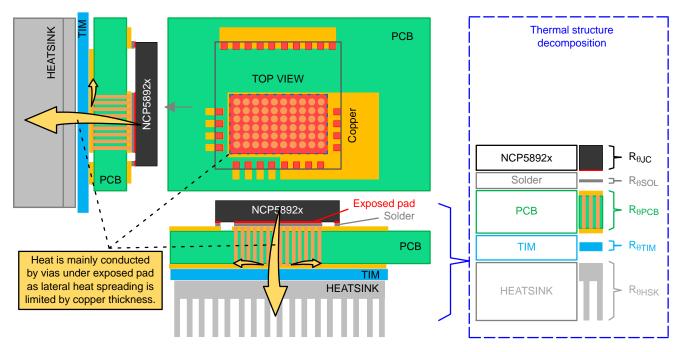

Figure 44. Heat-flux through PCB Vias

NCP58922 is bottom cooled device and generated heat is extracted from its exposed pad through subsequent cooling chain parts. Typical case is device mounted on the PCB as shows Figure 44. In this figure is depicted device mounted on PCB and Thermal structure decomposition as well as it demonstrates heat flux directions and level by simplified way. Basically, heat is taken away from exposed pad, then passing through solder joint and the PCB vias to the opposite site of PCB where is distributed into copper plane, however lateral heat spreading is limited. Further heat goes through Thermal Interface Material (TIM) and then continues to the heatsink where is released to the ambient. As mentioned previously, the spreading effect is limited due to transferring heat through thermal vias that are practically thermally insulated by PCB laminate which has typically tiny thermal conductivity 0.2 W/mK (FR4 laminate). Despite the high copper thermal conductivity 396 W/mK (at 350 K, ~+77°C), with respect to amount of main heat flow level, the lateral heat spreading within planes is limited by the PCB copper thickness due to very small ratio between copper thickness and area dimension. Thus, heat flow mainly passes perpendicularly through PCB plane thanks to copper vias and afterwards heat is removed by heatsink. Applicating simplifications afore stated and using scheme from Figure 44, it's easy to calculate 1-dimensional thermal resistance for each unknown part. Overall cooling chain thermal

resistance (Junction to Ambient)  $R_{\theta JA}$  is given by sum of elements in thermal structure as following:

$$R_{\theta JA} + R_{\theta JC} + R_{\theta SOL} + R_{\theta PBC} + R_{\theta TIM} + R_{\theta HSK} \qquad \text{ (eq. 1)}$$

where,  $R_{\theta JC}$  device junction to case thermal resistance,  $R_{\theta SOL}$  – solder layer thermal resistance,  $R_{\theta PCB}$  printed circuit board thermal resistance,  $R_{\theta TIM}$  TIM thermal resistance and  $R_{\theta HSK}$  heatsink thermal resistance. Thermal resistance of the device is shown in THERMAL CHARACTERISTICS table. Below is list of three the most used solder alloys and their thermal conductivity data (at 85°C), that can be used for calculation.

- Lead-free Solder alloys:

- Sn96.5-Ag3.5 k = 78 W/mK,

- Sn95.6-Ag3.5-Cu0.9 k = 60 W/mK,

- Sn96.2-Ag2.5-Cu0.8-Sb0.5-k=57 W/mK.

- Lead containing Solder alloys:

- Sn63-Pb37 k = 51 W/mK,

- Sn62-Pb36-Ag2-k = 50 W/mK,

- Pb50-In50 k = 22 W/mK.

In case you need some specific solder alloy, refer to its vendor or manufacturer to obtain necessary characteristics. Solder layer thermal resistance  $R_{\theta SOL}$  is proportional to solder layer thickness  $h_{SOL}$  and inverse proportional to

solder area  $A_{SOL}$  and solder thermal conductivity  $k_{SOL}$ .  $R_{\theta SOL}$  can be calculated as following:

$$R_{\theta SOL} = h_{SOL} / (A_{SOL} \times k_{SOL})$$

(eq. 2)

Let's assume that solder layer is 100  $\mu$ m, exposed pad area 24.64 mm² and conductivity 60 W/mK, then solder layer thermal resistance  $R_{\theta SOL}$  is 0.068°C/W, so this value can be considered as negligible. Similarly, thermal interface material thermal resistance  $R_{\theta TIM}$  can be computed same way as in equation 2, thus:

$$R_{\theta TIM} = h_{TIM} / (A_{TIM} \times k_{TIM})$$

(eq. 3)

and again, h<sub>TIM</sub> is TIM mounting thickness, k<sub>TIM</sub> thermal conductivity while A<sub>TIM</sub> area is limited copper plane area around thermal vias under device. Let's consider TIM thickness 0.5 mm with thermal conductivity 3.8 W/mK and active area is same as exposed pad. Then TIM layer thermal resistance  $R_{\theta TIM}$  is 5.34°C/W, this value is quite significant and TIM layer optimalization is big question. For half TIM layer thickness (0.25 mm / 3.8 W/mK) thermal resistance is halved. Summarizing the afore stated, to calculate realistic thermal resistance numbers, the size of material area (A<sub>SOL</sub>, A<sub>TIM</sub>) associated with heat transfer should be same as device exposed pad (flag) area.

#### **Thermal Resistance Calculations**

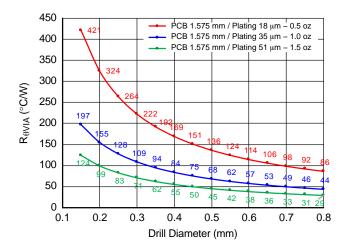

Continuing with calculations, we know thermal resistance of Device, Solder, TIM and Heatsink, however PCB thermal resistance  $R_{\theta PCB}$  is still required to develop entire cooling chain thermal resistance level. We can look at PCB from two perspectives. The first one is PCB thermal resistance from device to ambient as parallel path and its level is typically high, and it has minor impact to overall thermal resistance, especially when speak about small compact PCB. The second one is PCB thermal resistance from side where device is mounted to the opposite site, practically local thermal resistance of thermal vias under device exposed pad that significantly contributes to main cooling path thermal resistance. The most straightforward way to estimate thermal resistance of PCB portion with multiple thermal vias is to calculate single via thermal resistance and then divide it by number of active vias. To compute thermal resistance of single via use following equation 4:

$$R_{\theta VIA} = h_{PCB} / \left( \frac{\pi}{4} \left( \left( d_{drill} + h_{plt} \right)^2 - d_{drill}^2 \right) \times k_{Cu} \right)$$

(eq. 4)

where  $h_{PCB}$  is PCB height value (typically 1.575 mm),  $d_{drill}$  is via drill diameter,  $h_{plt}$  is copper layer plating thickness (typically 1 oz or 35  $\mu m)$  and  $k_{Cu}$  is copper thermal conductivity. For afore mentioned copper thermal conductivity, via height 1.575 mm, via drill 0.3 mm and copper plating 35  $\mu m$ , the  $R_{\theta VIA}$  equals to 109°C/W. To simplify whole process of computing, the chart in Figure 45 can be used for reading via thermal resistance for given setup. Furthermore, linear scaling works very well for fitting to other inputs. For example, halved PCB height gives half of thermal resistance.

Figure 45. R<sub>θVIA</sub> Thermal Resistance of Via vs. Manufacturing Parameters

Considering thermal resistance for given number n of actively heat transferring vias  $R_{\theta nVIAS}$  can be calculated as:

$$R_{\theta nVIAS} = R_{\theta VIA} / n$$

(eq. 5)

So, for 40 active vias with  $R_{\theta VIA} = 109^{\circ} C/W$  per each via (via height 1.575 mm, via drill 0.3 mm, copper plating 35 µm,), we obtain PCB thermal resistance under exposed pad  $R_{\theta PCB} = 2.73^{\circ} C/W$ . It should not be forgotten that vias contributing on main portion of heat transfer are located under device exposed pad only. To estimate cooling chain thermal resistance, let's assume that heatsink thermal resistance is  $R_{\theta HSK} = 3.0^{\circ} C/W$  and other values are already calculated or defined. Using equation 1, it can be obtained junction to ambient thermal resistance  $R_{\theta JA} \approx 12.6^{\circ} C/W$ . Then device maximum power dissipation level  $P_{Dmax}$  can be estimated as:

$$P_{Dmax} = (T_J - T_a) / R_{\theta JA}$$

(eq. 6)

where,  $T_J$  is junction temperature and  $T_a$  is ambient temperature. The junction temperature may user define up to 150°C. However, it's recommended to keep safety margin (25–30°C) that covers all manufacturing tolerances and prevent unwanted device overheating. For selected junction temperature  $T_J = 120$ °C, ambient temperature  $T_a = 60$ °C and  $R_{\theta JA} = 12.6$ °C/W, device may dissipate up to 4.76 W.

#### **Thermal Vias Considerations**

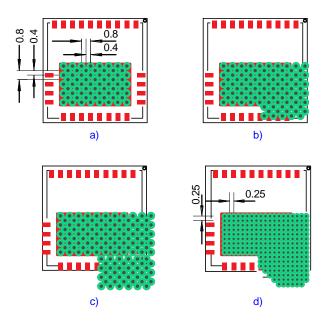

The minimum recommendation for thermal vias pattern is at least 60 vias of 0.3 mm drill that all of them are located under exposed pad. In are depicted 4 thermal vias pattern that were deployed to establish  $R_{\theta PCB}$  levels. For the same manufacturing condition, PCB thermal resistance top to bottom is given mainly by thermal vias under exposed pad area as was mentioned in previous section.

First three patterns in Figure 46 a), b), and c) use 0.3 mm drill with 0.8/0.4 mm pitch, while pattern d) uses 0.15 mm drill with 0.4 mm pitch. All patterns use same  $35 \mu m$  copper plating level. For first three patterns, the minor variation of thermal resistance was measured, and their thermal

resistance is approximately  $R_{\theta PCB} = 2.3^{\circ} \text{C/W}$  while pattern d) with denser vias pitch offers additional improvement of thermal resistance which is  $R_{\theta PCB} = 2.0^{\circ} \text{C/W}$ . NCP58922 on PCB with pattern d) mounted on  $1.0^{\circ} \text{C/W}$  fanned heatsink (using screws) via 6.0 W/mK TIM (40016005) achieves  $R_{\theta JA} = 5.6^{\circ} \text{C/W}$ .

Figure 46. Recommended Thermal Vias Arrangement

#### **ORDERING INFORMATION**

| Device        | Package Type                  | Shipping <sup>†</sup> |

|---------------|-------------------------------|-----------------------|

| NCP58922MNTWG | TQFN26 8x8, 0.8P<br>(Pb-Free) | 3000 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

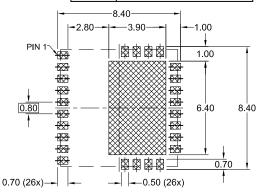

PIN 1 REFERENCE

### TQFN26 8x8, 0.8P

CASE 518AG **ISSUE B**

A

23

| 26

TOP VIEW

В

#### **DATE 29 NOV 2022**

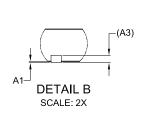

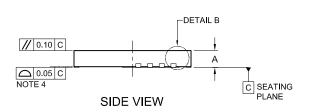

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 2009.

- CONTROLLING DIMENSION: MILLIMETERS

- DIMENSION 6 APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.30 MM FROM THE TERMINAL TIP.

COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL

- AS THE TERMINALS.

- POSITIONAL TOLERANCE APPLIES TO THE EXPOSED PAD AND ALL TERMINALS.

| DIM   | M        | ILLIMETEF | RS   |

|-------|----------|-----------|------|

| DIIVI | MIN.     | NOM.      | MAX. |

| Α     | 1.00     | 1.10      | 1.20 |

| A1    | 0.00     |           | 0.05 |

| А3    |          | 0.254 REF |      |

| b     | 0.40     | 0.45      | 0.50 |

| D     | 7.90     | 8.00      | 8.10 |

| D2    | 3.80     | 3.90      | 4.00 |

| E     | 7.90     | 8.00      | 8.10 |

| E2    | 6.30     | 6.40      | 6.50 |

| е     |          | 0.80 BSC  |      |

| e/2   |          | 0.40 BSC  |      |

| L     | 0.40     | 0.50      | 0.60 |

| k     | 2.80 REF |           |      |

| k2    | 0.30 REF |           |      |

| k3    | 0.30 REF |           |      |

|                     | D2 = e/2  |                                    |

|---------------------|-----------|------------------------------------|

| 10                  |           | (k2)                               |

| Fe/2 -=             | E E       |                                    |

|                     | -   -   E | E2                                 |

| 1-=                 | 26 23     | (k3)                               |

| L (26x)— (k)—<br>BC | TTOM      | -b (26x)<br>+ 0.10 C A B<br>0.08 C |

| \                   | /IEW      | NOTE 3<br>NOTE 5                   |

### RECOMMENDED

MOUNTING FOOTPRINT For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### **GENERIC** MARKING DIAGRAM\*

XXXX = Specific Device Code = Assembly Location Α XXXXXX XXXXXX WL = Wafer Lot **AWLYWW** = Year = Work Week \\/\\/

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "=", may or may not be present. Some products may not follow the Generic Marking.

| DOCUMENT NUMBER: | 98AON23962H      | Electronic versions are uncontrolled except when accessed directly from the Document Reposi<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:     | TQFN26 8x8, 0.8P |                                                                                                                                                                                | PAGE 1 OF 1 |  |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. **onsemi** does not convey any license under its patent rights nor the rights of others.

onsemi, Onsemi, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.or

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at www.onsemi.com/support/sales