### 16V, 12A Switching Buck Regulator Module

MCPF1412M06

### Description

The MCPF1412M06 is an easy-to-use, fully integrated and highly efficient Point-Of-Load (POL) 12A voltage regulator module. The on-chip Pulse-Width Modulation (PWM) controller and integrated MOSFETs, plus incorporated inductor and capacitors, result in an extremely compact and accurate regulator. The low-profile package is suitable for automated assembly using standard surface-mount equipment. This unique and optimized solution has yielded the highest density, full-featured 12A POL currently available.

The user can program aspects of the MCPF1412M06's operation using I<sup>2</sup>C and PMBus™ protocols. The built-in protection features include soft start protection, overvoltage protection, thermally compensated overcurrent protection with hiccup mode, and thermal shutdown with auto-recovery.

#### **Features**

- POL Module with Output Inductor Included

- Small Size: 5.8 mm x 4.9 mm x 1.6 mm

- · Continuous 12A Load Capability

- Wide Input Voltage Range: 4.5-16V

- Adjustable Output Voltage: 0.6-1.8V

- No External Compensation Required

- Programmable Operation Using I<sup>2</sup>C and PMBus™

- Enable Input, Programmable Undervoltage Lock-Out (UVLO) Circuit

- · Power-Good Indicator

- · Built-in Protection Features

- Operating Temperature from -40°C to +125°C

- · Lead-Free and Halogen-Free

- Compliant with EU REACH and RoHS

### **Applications**

- Servers, Workstations and Cloud Computing

- · Routers, Switches and Telecom Equipment

- Base Stations, Data Center Power Solutions

- High Power Density POL Conversion

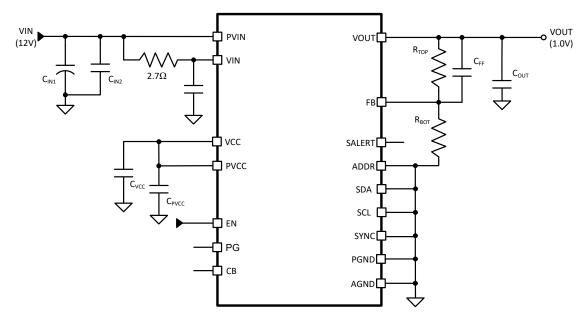

# **Typical Application**

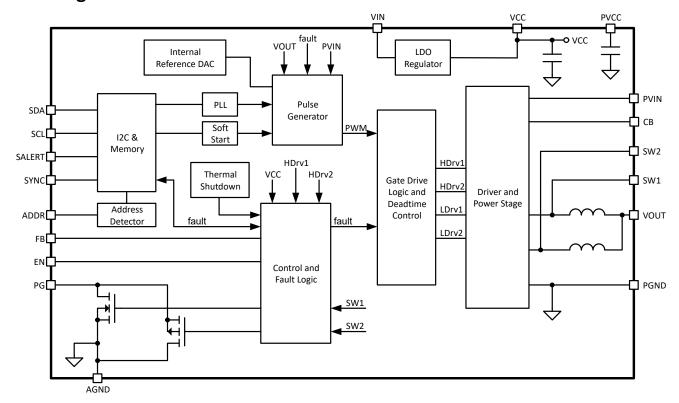

## **Block Diagram**

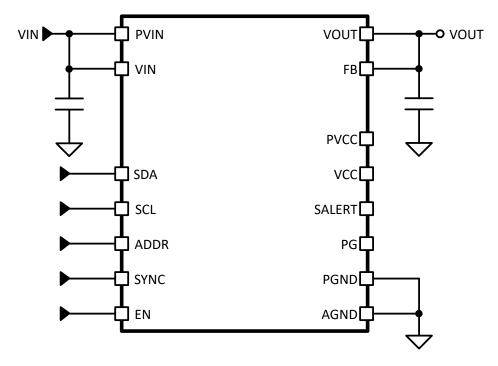

# 1. Pin Configuration

| •          | •      |                                                                                                                                                                          |

|------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Number | Name   | Description                                                                                                                                                              |

| 1          | SW2    | Test Pin                                                                                                                                                                 |

| 2          | VIN    | Input voltage and input to the LDO regulator.                                                                                                                            |

| 3          | EN     | Enable pin. Turns the MCPF1412M06 ON and OFF. A resistor divider can be used on this pin to create an external UVLO condition.                                           |

| 4          | PVCC   | Input supply for the driver circuits. Connect to VCC.                                                                                                                    |

| 5          | VCC    | Supply voltage. This is used as either a bypass capacitor connection for the internal LDO or as a connection point for an external bias voltage.                         |

| 6          | FB     | Feedback voltage to the device. Connect the tap of a voltage divider across the output voltage to this pin to set the output voltage value.                              |

| 7, 22      | AGND   | Signal level ground for the converter and the internal control circuitry. Connect this to the ground plane of the application.                                           |

| 8          | VOUT   | Output voltage of the regulator. Connect output filter capacitors and a $100\Omega$ resistor from this pin to PGND.                                                      |

| 9          | PG     | Power Good status indicator. An open drain FET pulls this pin down when Power Good is not asserted. Connect 49.9 k $\Omega$ from this pin to VCC or an external 5V rail. |

| 10         | ADDR   | Address pin. Connect a resistor from this pin to AGND to set the I <sup>2</sup> C address of the part.                                                                   |

| 11         | SYNC   | Synchronization input to synchronize the switching to an external source. Connect to AGND if not used.                                                                   |

| 12         | SDA    | $l^2 C/PMBus$ data $l/O$ pin. Pull this pin up to the bus voltage with 4.99 $k\Omega$ or connect to AGND if not used.                                                    |

| 13         | SCL    | $l^2 C/PMBus$ clock pin. Pull this pin up to the bus voltage with 4.99 $k\Omega$ or connect to AGND if not used.                                                         |

| 14         | SALERT | SMBAlert# line. Pull this up to bus voltage with a 4.99 $k\Omega$ resistor.                                                                                              |

| 15         | SW1    | Optional connection for a capacitor to CB. A 0.1 to 1 $\mu\text{F},$ 16V or higher rated MLCC capacitor is recommended.                                                  |

| 16, 20, 21 | PGND   | Power Ground. This is a separate ground connection for the internal power devices. Connect to the application power ground plane.                                        |

| 17         | СВ     | An optional capacitor can be connected from this pin to SW1.                                                                                                             |

| 18, 19     | PVIN   | Power input terminal for the power switching stage.                                                                                                                      |

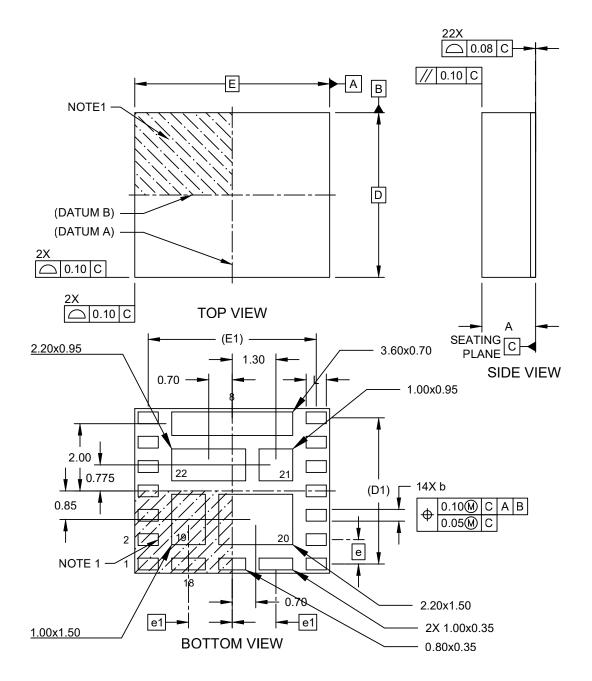

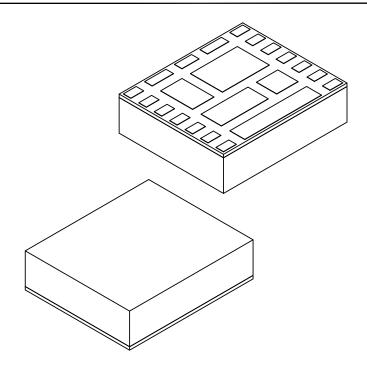

# 1.1. Package

Figure 1-1. Pin Configuration 20-Lead 5.8 mm x 4.9 mm LGA (Top View)

| [1]     | $[ \underline{18} ] [ \underline{17} ] [ \underline{16}$ | [15] |

|---------|----------------------------------------------------------|------|

| [ _2_ ] |                                                          | [14] |

| [3]     | 19   20                                                  | [13] |

| [4]     |                                                          | -    |

| [5]     | 22   21                                                  | [11] |

| [_6_]   | :                                                        | [10] |

| [7]     | 8                                                        | _    |

### 2. Functional Description

#### 2.1. Overview

The MCPF1412M06 is a user-friendly, fully integrated, and highly efficient DC/DC regulator. Its operation, including output voltage and system optimization parameters, can be programmed via the I²C/PMBus™ protocol. It employs a proprietary modulator to ensure rapid transient response. The modulator features internal compensation, making it suitable for a wide range of applications with various types of output capacitors, without encountering loop stability issues.

The MCPF1412M06 is a versatile device that offers significant flexibility for configuration and system monitoring through the I<sup>2</sup>C/PMBus<sup>™</sup> interface. Additionally, it supports standalone operation without a digital interface, allowing designers to easily configure output voltages using simple resistor divider adjustments and monitor the system via the Power Good output.

### 2.2. Operation and Topology

The MCPF1412M06 employs an interleaved buck converter design, which minimizes voltage stress on internal power components, leading to a more compact size but with switching losses similar to those of a conventional interleaved buck converter with the same rating. Additionally, it features an inherent current-sharing mechanism between the two phases.

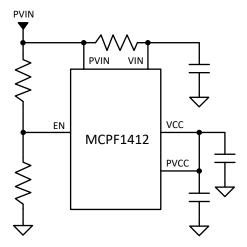

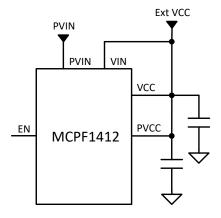

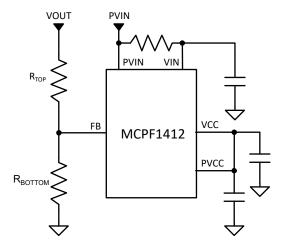

#### 2.3. Bias Voltage

The MCPF1412M06 features an integrated Low Drop-Out (LDO) regulator that supplies the DC bias voltage for its internal circuitry, typically outputting 5.2V. For single-rail operation with internal bias, connect the VIN pin to the PVIN pin (see Figure 2-1). When using an external bias voltage, connect the VIN pin to the VCC pin to bypass the internal LDO regulator (see Figure 2-2). A separate pin (PVCC) is provided for driver bias and should be connected to VCC in the application circuit. The supply voltage, whether internal or external, increases with VIN and does not require enabling via the EN pin. Therefore, I<sup>2</sup>C/PMBus<sup>™</sup> communication can commence once the following conditions are met:

- The VCC UVLO start threshold is surpassed

- Memory contents are loaded

- · Initialization is complete

- · The address offset is read

**Attention:** During initialization, a small leakage current (approximately 3.4  $\mu$ A) may flow from the device to the output, potentially pre-biasing the output voltage in applications with prolonged VIN/VCC rise times. To mitigate this, connect a small load capable of sinking 3.4  $\mu$ A in such applications.

The I<sup>2</sup>C bus can be pulled up to either VCC or a system I<sup>2</sup>C bus voltage. The MCPF1412M06 allows for two I<sup>2</sup>C bus voltage ranges, selectable via the user register bit Bus\_voltage\_sel, as shown below:

| Register | Bits | Name/ Description      |  |  |  |

|----------|------|------------------------|--|--|--|

| 0x7A     | [2]  | Bus_voltage_sel        |  |  |  |

|          |      | 0: 1.8-2.5V, 1: 3.3-5V |  |  |  |

Figure 2-1. Single Supply Configuration: Internal LDO Regulator and Adjustable PVIN Undervoltage Lockout (UVLO)

Figure 2-2. Setup for Using an External Bias Voltage

#### 2.4. I<sup>2</sup>C Base Address and Offsets

The MCPF1412M06 features user-configurable registers to set its  $I^2C$  and PMBus<sup>™</sup> base addresses. By default, the  $I^2C$  base address is 0x08, and the PMBus<sup>™</sup> base address is 0x70. An offset ranging from 0 to 15 is determined by connecting the ADDR pin to the AGND pin, either directly or via a resistor. At startup, an address detector measures the resistance of this connection to set the offset, which is then added to the base  $I^2C$  address to establish the address for  $I^2C$  communication with the MCPF1412M06. The same offset is added to the base PMBus<sup>™</sup> address to set the PMBus<sup>™</sup> communication address.

To select offsets from 0 to 15, connect the pins as follows:

- $0 0\Omega$  (short ADDR to AGND)

- +1 1.13 kΩ

- +2 1.87 kΩ

- +3 2.61 kΩ

- $+4 3.4 \text{ k}\Omega$

- $+5 4.12 \text{ k}\Omega$

- $+6 4.87 \text{ k}\Omega$

- +7 5.62 kΩ

- +8 6.34 kΩ

- +9 7.15 kΩ

- $+10 7.87 \text{ k}\Omega$

- +11 8.66 kΩ

- $+12 9.31 \text{ k}\Omega$

- +13 10.2 kΩ

- +14 11 kΩ

- +15 12.1 kΩ

**Note:** Avoid using the 7-bit address 0x0C, as it corresponds to the Alert Response Address in the SMBus<sup>™</sup> protocol.

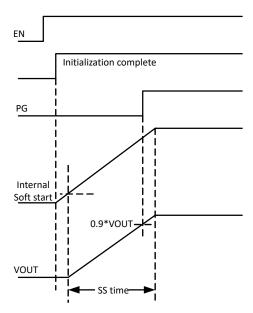

### 2.5. Soft Start and Target Output Voltage

The MCPF1412M06 features an internal digital soft start circuit designed to manage the output voltage rise-time and limit current surges during start-up. When VCC surpasses its start threshold (VCC\_UVLO<sub>(START)</sub>), the MCPF1412M06 exits reset mode, initiating the loading of non-volatile memory contents into working registers and calculating the address offset as previously described. After initialization, the internal soft start ramps up towards the set reference voltage at a rate specified by the TON\_RISE registers (associated with the TON\_RISE command), provided the following conditions are met:

- A valid enable signal is detected, as defined by the Enable pin, Operation register, ON\_OFF\_CONFIG register, input voltage PVIN, and PVIN UVLO threshold corresponding to the VIN\_ON registers.

- 2. The internal pre-charge circuit ensures balanced PVIN/2 voltages across all FETs when the device begins switching.

During initial start-up, the MCPF1412M06 operates with minimal high-drive (HDrv) pulses until the output voltage increases (refer to Switching frequency and minimum values for ON-time, OFF-time). The ON time is increased until VOUT reaches the target value set by the VOUT\_COMMAND registers. For optimal start-up performance, it is recommended to use a  $100\Omega$  resistor connected in parallel with the output capacitors ( $C_{OUT}$ ). A minimum wait time of  $600\Omega \times C_{OUT}$  is advised between successive power or Enable cycling operations. For instance, with a  $100\Omega$  resistor across four 47 µF output capacitors, a new Enable assertion should not occur until at least 78 ms (allowing the reduction of capacitance at a bias of 1V - see Design Example) after disabling the MCPF1412M06.

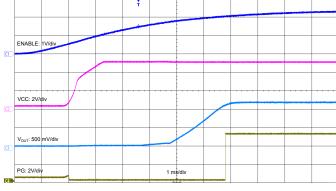

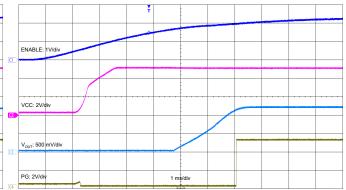

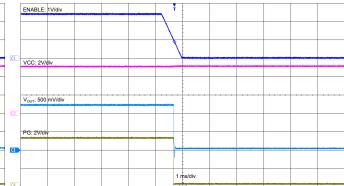

Figure 2-3. Soft Start Operation

Overcurrent Protection (OCP) and Overvoltage Protection (OVP) are active during soft start to safeguard the MCPF1412M06 from short circuits and excessive voltages.

A resistor divider can be utilized with a standard MCPF1412M06 device to set the desired output voltage (Figure 2-4). This provides system designers with the flexibility to configure all power rails in the system across the entire output voltage range (0.6–1.8V) using a single component.

Figure 2-4. Resistor Divider to Set Output Voltage

The following equation describes the appropriate resistor divider selection to set the output voltage using an MCPF1412M06 programmed to 0.6V:

$$R_{BOTTOM} = \frac{R_{TOP}}{1.7975 \times VOUT - 1.0639 - 0.00894 \times R_{TOP}}$$

#### Where:

$R_{TOP}$  and  $R_{BOTTOM}$  are in  $k\Omega$ .

It is recommended that system designers place a capacitor ( $C_{FF}$  in Figure 5-1) of 47 pF to 470 pF in parallel with  $R_{TOP}$ . 4.12 k $\Omega$  is suggested as a value for  $R_{TOP}$ . The recommended value for  $R_{BOTTOM}$

depends on the output voltage, as shown in the table below. Designers should validate these values in their specific applications.

| VOUT (V) | R <sub>BOTTOM</sub> (kΩ) |

|----------|--------------------------|

| 0.72     | 21                       |

| 0.85     | 9.76                     |

| 0.9      | 8.06                     |

| 0.95     | 6.81                     |

| 1        | 5.9                      |

| 1.05     | 5.23                     |

| 1.1      | 4.75                     |

| 1.2      | 3.92                     |

| 1.5      | 2.55                     |

| 1.8      | 1.91                     |

Alternatively, the output voltage can be set using I<sup>2</sup>C/PMBus<sup>™</sup> commands (see PMBus Commands) or the corresponding user registers, instead of an external resistor divider. The table below lists VOUT\_COMMAND codes to set the specified voltages. The MCPF1412M06 supports this command with a resolution of 1/256V.

| VOUT (V) | VOUT_COMMAND | VOUT (V) | VOUT_COMMAND |

|----------|--------------|----------|--------------|

| 0.65     | 00A7         | 1.20     | 0134         |

| 0.70     | 00B4         | 1.25     | 0140         |

| 0.72     | 00B9         | 1.30     | 014E         |

| 0.75     | 00C0         | 1.35     | 015A         |

| 0.78     | 00C8         | 1.40     | 0167         |

| 0.80     | 00CD         | 1.45     | 0174         |

| 0.85     | 00DA         | 1.50     | 0180         |

| 0.88     | 00E2         | 1.55     | 018D         |

| 0.90     | 00E7         | 1.60     | 019A         |

| 0.95     | 00F4         | 1.65     | 01A7         |

| 1.00     | 0100         | 1.70     | 01B4         |

| 1.05     | 010D         | 1.75     | 01C0         |

| 1.10     | 011A         | 1.80     | 01CD         |

| 1.15     | 0127         |          |              |

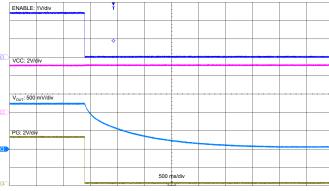

#### 2.6. Shutdown Mechanisms

The MCPF1412M06 features two shutdown mechanisms:

#### 1. Hard Shutdown or Load-Dependent Decay:

A valid hard-disable is detected based on the Enable pin, Operation register, ON\_OFF\_CONFIG register, input voltage PVIN, and PVIN UVLO threshold corresponding to the VIN\_ON registers. Both drivers are immediately turned OFF, and the soft start is pulled down instantly.

#### 2. Soft-Stop or Controlled Ramp Down:

A valid soft-OFF request is detected based on the Enable pin, Operation register, and ON\_OFF\_CONFIG register. After a delay defined by the TOFF\_DELAY registers, the SS signal gradually decreases to 0 over a period specified by the TOFF\_FALL registers. The drivers are disabled only when the SS signal reaches 0, causing the output voltage to follow the SS signal down to 0.

By default, the device is set for hard shutdown. Shutdown using PVIN is always a hard shutdown.

### 2.7. Switching Frequency, Minimum ON and OFF Time, PVIN

The switching frequency of the MCPF1412M06 is influenced by the output voltage and can operate in one of two modes:

- Mode A: Pseudo constant-frequency COT mode (default)

- Mode B: PLL-modulated COT mode

For the default output voltage of 0.6V, the switching frequency is typically 470 kHz, and the device functions in Mode A. In this mode, if the output voltage is adjusted using an external resistor divider, the switching frequency automatically adapts to the correct value:

$$F_{SW} = 470 \text{ kHz} \times \frac{VOUT}{0.6}$$

When the output voltage is configured via the VOUT\_COMMAND user registers instead of an external resistor divider, Mode B should be selected. To implement this, the user must enable the Phase-Locked Loop (PLL), which is disabled by default, and toggle the Enable pin. This action automatically sets the switching frequency to the factory-programmed values listed in the table below. The PLL adjusts the ON-time to ensure a constant switching frequency regardless of the load.

| VOUT Range (V) | F <sub>SW</sub> (MHz) |

|----------------|-----------------------|

| < 0.65         | 0.5                   |

| 0.65 to 1.1    | 1.00                  |

| 1.1 to 1.32    | 1.25                  |

| 1.32 to 1.8    | 1.5                   |

With either approach, system designers do not need to worry about selecting the switching frequency. When the input voltage is significantly higher than the target output voltage, the high side MOSFETs are switched ON for shorter durations. The shortest reliable ON-time is defined by the minimum ON-time ( $T_{ON(MIN)}$ ). During start-up, when the output voltage is very low, the MCPF1412M06 operates with the minimum ON-time.

The maximum conversion ratio is influenced by two factors:

- 1. When the input voltage is low, relative to the target output voltage, the Control MOSFET is switched ON for longer durations. The shortest OFF-time is defined by the minimum OFF-time (T<sub>OFF(MIN)</sub>). During this period, the Synchronous MOSFET remains ON, and its current is monitored for overcurrent protection. This determines the minimum input voltage that can still allow the device to regulate its output at the target voltage.

- 2. To maintain balanced switching amplitudes in both phases, this topology requires no overlap between the high sides of the two phases, unlike a conventional buck topology. This imposes theoretical maximums of 50% on the duty cycle of each phase and 25% on the conversion ratio. In practice, considering circuit delays and dead-times, the conversion ratio should not exceed 16% at full load.

The maximum conversion ratio is influenced by both system efficiency and load transient requirements. It is recommended that system designers validate these values in their specific applications.

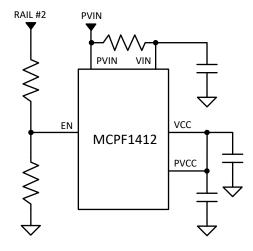

### 2.8. Enable Pin (EN)

The Enable (EN) pin serves multiple purposes:

- By default, according to the ON\_OFF\_CONFIG command, it controls the power state of the MCPF1412M06. It features a precise threshold monitored by the UVLO circuit. If left unconnected, an internal 1 MΩ resistor pulls it down to prevent accidental activation of the MCPF1412M06.

- It can be utilized to establish a precise input voltage UVLO. The EN pin's input is derived from the PVIN voltage through a set of resistive dividers (Figure 2-1). Users can adjust the UVLO threshold

voltage by selecting different resistor ratios, allowing for finer control over the PVIN UVLO voltage levels than the VIN\_ON/VIN\_OFF commands provide.

• It can also be used to monitor other power rails for specific power sequencing schemes (Figure 2-5).

Figure 2-5. EN Pin Used to Monitor a Second Rail for Startup

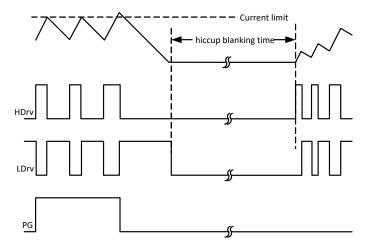

### 2.9. Overcurrent Protection (OCP)

Overcurrent Protection (OCP) is achieved by monitoring the voltage across the channel RDS(ON) of the Synchronous MOSFET. When this surpasses the OCP threshold, a fault condition is triggered.

This approach offers several advantages:

- Ensures precise overcurrent protection without compromising converter efficiency (the current sensing is lossless)

- Lowers costs by eliminating the need for a current-sense resistor

- Minimizes layout-related noise issues

The OCP threshold is set by the IOUT\_OC\_FAULT\_LIMIT command (or corresponding user registers) and can be programmed in 0.5A increments, up to a maximum of 16A. The recommended minimum overcurrent threshold is 10A. The OCP threshold is internally compensated to remain nearly constant across different ambient temperatures.

When the current exceeds the OCP threshold, the PG and SS signals are pulled low. The Synchronous MOSFET stays ON until the current drops to 0, after which the MCPF1412M06 enters hiccup. Both the Control MOSFET and the Synchronous MOSFET remain OFF during the hiccupblanking period. After this period, the MCPF1412M06 attempts to restart. If an overcurrent fault is still present, the previous actions are repeated. The MCPF1412M06 stays in hiccup mode until the overcurrent fault is resolved. The MCPF1412M06 can also be reprogrammed to enter a latched shutdown mode upon detecting an overcurrent fault.

Figure 2-6. Overcurrent Protection and Hiccup Operation

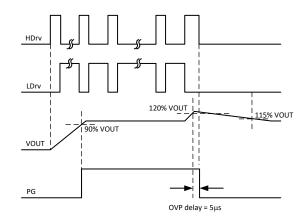

### 2.10. Overvoltage Protection (OVP)

Overvoltage Protection (OVP) is achieved by monitoring the voltage at the FB pin. If the FB pin voltage surpasses the output OVP threshold for more than the output OVP delay (typically 5  $\mu$ s), a fault condition is triggered.

The OVP threshold is determined by the VOUT\_OV\_FAULT\_LIMIT command (or the corresponding user registers). This command enables the overvoltage level to be set relative to the output voltage, with a resolution of 1/256V. Internally, these values are rounded to one of four settings, as indicated in the table below.

| VOUT_OV_FAULT_LIMIT (% of VOUT_COMMAND) | Actual V <sub>OUT</sub> OV Threshold<br>(% of VOUT_COMMAND) |

|-----------------------------------------|-------------------------------------------------------------|

| 100 to 105.4                            | 105                                                         |

| 105.4 to 110.1                          | 110                                                         |

| 110.1 to 114.8                          | 115                                                         |

| less than 100 or more than 114.8        | 120 (Default)                                               |

The default setting is 120%. All MOSFETs are immediately switched OFF, and the PG pin is pulled low. The MOSFETs stay latched off until reset by cycling either VCC or EN. Figure 2-7 illustrates a timing diagram for overvoltage protection.

Figure 2-7. OVP Operation for Latched OVP

The MCPF1412M06 issues warnings for output overvoltage and undervoltage, and provides protection against output undervoltage faults. These functions are controlled by three commands (or their corresponding user registers):

- VOUT\_OV\_WARN\_LIMIT

- VOUT\_UV\_WARN\_LIMIT

- VOUT\_UV\_FAULT\_LIMIT

The threshold mechanism for these warnings differs from the overvoltage protection mechanism: the warnings use a digital comparison of the digitized and processed VOUT telemetry against the thresholds, while the overvoltage protection uses an all-analog signal path and an internal high-speed comparator.

#### 2.11. Overtemperature Protection (OTP)

The MCPF1412M06 includes an internal temperature sensing feature. The Overtemperature Protection (OTP) threshold is determined by a fixed internal threshold, set at 145°C. This threshold is monitored by an internal analog comparison. If the temperature exceeds this limit, the device halts switching and turns OFF all MOSFETs until the temperature falls below the threshold, at which point it automatically restarts.

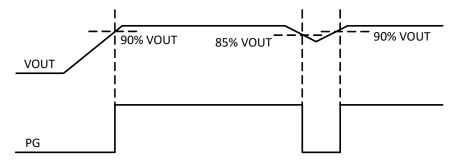

#### 2.12. Power Good (PG)

Power Good (PG) behavior is defined through the PGControl register bits and the POWER\_GOOD\_ON command. When the PGControl bit is enabled, the PMBus™ command can set the upper Power Good threshold relative to the output voltage with a resolution of 1/256V. Internally, these values are rounded to one of four settings, as illustrated in the table below.

| POWER_GOOD_ON            | Actual Threshold    |  |  |

|--------------------------|---------------------|--|--|

| (% of VOUT_COMMAND)      | (% of VOUT_COMMAND) |  |  |

| Above 96.1 or below 79.6 | 80                  |  |  |

| Above 79.6 to 85.1       | 85                  |  |  |

| Above 85.1 to 89.8       | 90 (default)        |  |  |

| Above 89.8 to 96.1       | 95                  |  |  |

The default setting is 90%, meaning the PG signal will be activated when the voltage at the FB pin surpasses 90% of the VOUT\_COMMAND setting (default 0.6V). A 5% hysteresis is applied, creating a lower threshold. If the voltage at the FB pin falls below this lower threshold, the PG signal will be deactivated.

Figure 2-8 illustrates the case where the PGControl bit is set to 1.

Figure 2-8. PG Operation With PGControl Bit Set to 1

The behavior remains consistent during start-up and normal operation. The PG signal is asserted when:

- Both EN and VCC exceed their thresholds

- No faults are present (including overcurrent, overvoltage, and overtemperature)

- VOUT is within the target range (monitored continuously to ensure FB is above the PG threshold)

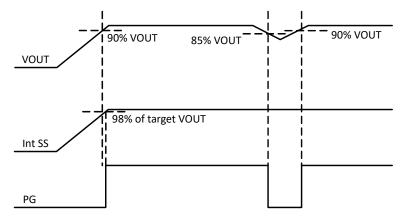

With the PGControl bit set to '0' the operation is as shown in Figure 2-9.

Figure 2-9. PG Operation With PGControl Bit Set to '0'

During normal operation, the PG signal functions identically to when the PGControl bit is set to '1'. However, at start-up, the PG signal is asserted once FB is within 2% of the target output voltage, rather than when FB surpasses the upper PG threshold. The MCPF1412M06 also includes an additional PMOS in parallel with the NMOS, internally connected to the PG pin (see Block Diagram). This PMOS ensures that the PG signal remains at a logic low level, even if VCC is low and the PG pin is pulled up to an external voltage other than VCC.

#### 3. Electrical Characteristics

#### 3.1. Absolute Maximum Ratings

| PVIN, VIN, EN to PGND, CB to SW1                | -0.3V to 18V   |

|-------------------------------------------------|----------------|

| VCC to PGND                                     | -0.3V to 6V    |

| SW1, SW2                                        | -0.3V to 15V   |

| FB, SYNC, ADDR, SCL, SDA, SALERT, to AGND       | -0.3V to VCC   |

| PG to AGND                                      | -0.3V to VCC   |

| PGND to AGND                                    | -0.3V to 0.3V  |

| ESD HBM JESD22-A114                             | Class 1C       |

| Maximum Junction Temperature (T <sub>J</sub> )  | -40°C to 150°C |

| Storage Temperature (T <sub>S</sub> )           | -55°C to 150°C |

| Moisture Sensitivity Rating (JEDEC, J-STD-020D) | MSL 3          |

|                                                 |                |

**Note:** Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational sections of this specification is not intended. Exposure to maximum rating conditions for extended periods may affect device reliability.

### 3.2. Recommended Operating Ratings<sup>(1)</sup>

| Input Voltage Range with External VCC <sup>(2)(4)</sup> , PVIN | 6*VOUT to 16V  |

|----------------------------------------------------------------|----------------|

| Input Voltage Range with Internal LDO <sup>(3)(4)</sup> , PVIN | 6*VOUT to 16V  |

| Bias Input voltage Range <sup>(3)</sup> , VIN                  | 4.5V to 16V    |

| Supply Voltage Range <sup>(5)</sup> , VCC                      | 4.5V to 5.5V   |

| Output Voltage Range, VOUT                                     | 0.6V to 1.8V   |

| Continuous Output Current Range, I <sub>O</sub>                | 0A to 12A      |

| Operating Junction Temperature Range, T <sub>J</sub>           | -40°C to 125°C |

#### **Notes:**

- 1. The device is not guaranteed to operate outside its operating ratings.

- 2. VIN is connected to VCC to bypass the internal Low Drop-Out (LDO) regulator.

- 3. VIN is connected to PVIN (for single-rail applications with PVIN = VIN = 4.5V 16V).

- 4. Maximum switch node voltage should not exceed 15V.

- 5. Must not exceed 6V.

### 3.3. DC/AC Characteristics

| Electrical Characteristics: $6*V_{OUT} < PV_{IN} < 16V$ , $4.5V < V_{IN} < 16V$ , $0°C < T_A < 125°C$ unless specified otherwise, Typicals at $T_A = 25°C$ |                          |      |             |      |       |                                                     |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|-------------|------|-------|-----------------------------------------------------|--|

| Parameter                                                                                                                                                  | Symbol                   | Min. | Typ. Max. l |      | Units | Conditions                                          |  |

| Input Current                                                                                                                                              |                          |      |             |      |       |                                                     |  |

| VIN Supply Current (Standby)                                                                                                                               | I <sub>IN(STANDBY)</sub> |      | 7           | 8    | mA    | Enable low                                          |  |

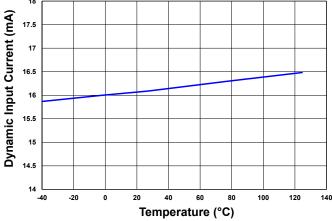

| VIN Supply Current (Dynamic)                                                                                                                               | I <sub>IN(DYN)</sub>     |      | 16          | 18   | mA    | Enable High, F <sub>SW</sub> = 470 kHz              |  |

| Soft Start                                                                                                                                                 |                          |      |             |      |       |                                                     |  |

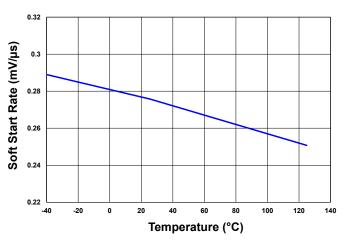

| Soft Start Rate <sup>(1)</sup>                                                                                                                             | SS <sub>RATE</sub>       | 0.17 | 0.28        | 0.37 | V/ms  | Default VOUT = 0.6V,<br>T <sub>ON_RISE</sub> = 2 ms |  |

| Output Voltage                                                                                                                                             |                          |      |             |      |       |                                                     |  |

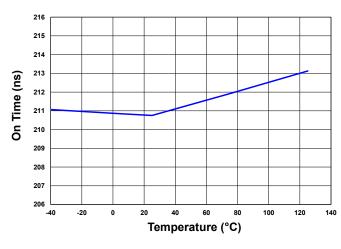

#### DC/AC Characteristics (continued) $Electrical\ Characteristics:\ 6*V_{OUT} < PV_{IN} < 16V,\ 4.5V < V_{IN} < 16V,\ 0^{\circ}C < T_{A} < 125^{\circ}C\ unless\ specified\ otherwise,\ Typicals\ at$ $T_A = 25^{\circ}C$ Symbol **Parameter** Min. Max. Units **Conditions** Тур. VOUT (default) Output voltage Range 0.6 ٧ Range 0.6 1.8 Resolution 5 m۷ +/-0.75 % $T_I = 25$ °C, $V_{OUT} = 0.6V$ Accuracy -40°C $< T_1 < 125$ °C<sup>(2)</sup> -1 +1 % **On-Time Timer Control** On Time 185 $PV_{IN}$ = 12V, $V_{OUT}$ = 0.6V, $F_{SW}$ $T_{ON}$ 211 235 ns = 470 kHz Minimum On Time<sup>(1)</sup> 50 T<sub>ON(MIN)</sub> ns **Internal Low Drop Out Regulator (LDO** Regulator Output Voltage VCC 4.89 5.2 5.4 $5.5 < V_{IN} < 16V, 0-40 \text{ mA}$ ٧ 4.19 4.26 $4.5 < V_{IN} < 5.5V$ , 0-40 mA Load Regulation $V_{LD}$ 0.19 ٧ 0-40 mA **Thermal Shutdown** Thermal Shutdown<sup>(1)</sup> 145 C C Hysteresis<sup>(1)</sup> 25 **Undervoltage Lock Out** V<sub>CC</sub> Start Threshold VCC\_UVLO(START) 4.0 4.2 4.4 V VCC rising ٧ V<sub>CC</sub> Stop Threshold VCC\_UVLO<sub>(STOP)</sub> 3.6 3.8 4.1 VCC falling **Enable Threshold** En<sub>(HIGH)</sub> 1.05 1.20 1.34 ٧ EN rising 1.11 0.92 1.00 ٧ EN falling En<sub>(LOW)</sub> Input Impedance $\mathsf{R}_{\mathsf{EN}}$ 500 1000 1500 kΩ **Current Limit Current Limit Threshold** $T_1 = 25$ °C I<sub>OC</sub> (default) 14.5 16 17.5 Α 10 16 Α I<sub>OC</sub> (range) Hiccup Blanking Time 20 T<sub>BLK(HICCUP)</sub> ms **Over Voltage Protection (OVP)** OVP Threshold(1) V<sub>OVP</sub> (default) 115 120 125 % 105 % V<sub>OVP</sub> (range) 120 V<sub>OVP</sub> (resolution) 5 % **OVP** Delay 5 T<sub>OVPDEL</sub> μs **Power Good Upper Threshold** V<sub>PG(UPPER)</sub> (default) 85 90 95 % V<sub>OUT</sub> rising Hysteresis V<sub>PG(LOWER)</sub> 7 % V<sub>OUT</sub> falling Sink Current 9 mA $V_{PG} = 0.5V$ , EN = 2V $I_{PG}$ **Telemetry** Input Voltage Reporting Accuracy PV<sub>IN</sub>\_report\_err -2 +2 % PVIN = 12V, -40°C < TJ < 125°C -5 % 5V < PVIN < 16V, +5 -40°C < TJ < 125°C **Output Voltage Reporting** -18 +18 m۷ VOUT = VFB = 0.6V, -40°C < V<sub>OUT</sub>\_report\_err Accuracy TI < 125°C °C **Temperature Reporting** T\_report\_err -20 +20 -40°C < TJ < 125°C Accuracy<sup>(1)</sup>

#### DC/AC Characteristics (continued)

Electrical Characteristics:  $6*V_{OUT} < PV_{IN} < 16V$ ,  $4.5V < V_{IN} < 16V$ ,  $0^{\circ}C < T_{A} < 125^{\circ}C$  unless specified otherwise, Typicals at  $T_{A} = 25^{\circ}C$

| Parameter Symbol | Min. | Тур. | Max. | Units | Conditions |

|------------------|------|------|------|-------|------------|

|------------------|------|------|------|-------|------------|

#### Notes:

- 1. Characterized parameter, not production tested.

- 2. Hot and cold temperature performance is assured by correlation using statistical quality control, but not tested in production; performance at 25°C is tested and guaranteed in production environment.

Electrical Characteristics:  $6*V_{OUT} < PV_{IN} < 16V$ ,  $4.5V < V_{IN} < 16V$ ,  $0°C < T_A < 125°C$  unless specified otherwise, Typicals at  $T_A = 25°C$

| Parameter <sup>(1 - all</sup>              | Symbol              | Fast-mo                    | de                    | Fast-mod                   | e Plus                | Unit | Conditions                                 |

|--------------------------------------------|---------------------|----------------------------|-----------------------|----------------------------|-----------------------|------|--------------------------------------------|

| parameters)                                |                     | Min.                       | Max.                  | Min.                       | Max.                  |      |                                            |

| I <sup>2</sup> C Parameters                | •                   |                            |                       |                            |                       | _    |                                            |

| I <sup>2</sup> C Bus Voltage               | V <sub>BUS</sub>    | 1.8                        | 5.5                   | 1.8                        | 5.5                   | ٧    |                                            |

| Vin Low                                    | V <sub>IL</sub>     | -0.5                       | 0.3*V <sub>BUS</sub>  | -0.5                       | 0.3*V <sub>BUS</sub>  | V    |                                            |

| Vin High                                   | V <sub>IH</sub>     | 0.7*V <sub>BUS</sub>       |                       | 0.7*V <sub>BUS</sub>       |                       | V    |                                            |

| Input Hysteresis                           | V <sub>HYS</sub>    | 0.05*V <sub>BUS</sub>      |                       | 0.05*V <sub>BUS</sub>      |                       | V    |                                            |

| Low Level Output<br>Voltage 1              |                     | 0                          | 0.4                   | 0                          | 0.4                   | ٧    | 3 mA sink current,<br>V <sub>CC</sub> > 2V |

| Low Level Output<br>Voltage 2              | V <sub>OL2</sub>    | 0                          | 0.2* V <sub>BUS</sub> | 0                          | 0.2* V <sub>BUS</sub> |      | 2 mA sink current,<br>V <sub>CC</sub> < 2V |

| Low level sink                             | I <sub>OL</sub>     | 3                          |                       | 3                          |                       | mA   | V <sub>OL</sub> = 0.4V                     |

| Current                                    |                     | 6                          |                       | 6                          |                       | mA   | V <sub>OL</sub> = 0.6V                     |

| Output Fall Time                           | T <sub>OF</sub>     | 20*(V <sub>BUS</sub> /5.5) | 250                   | 20*(V <sub>BUS</sub> /5.5) | 125                   | ns   |                                            |

| Max Noise Spike<br>Width                   | T <sub>SP</sub>     | 0                          | 50                    | 0                          | 50                    | ns   |                                            |

| Input Current                              | I <sub>IN</sub>     | -10                        | 10                    | -10                        | 10                    | mA   |                                            |

| Input Capacitance                          | C <sub>I</sub>      | -                          | 10                    | -                          | 10                    | pF   |                                            |

| SCL Frequency                              | F <sub>SCL</sub>    | 0                          | 400                   | 0                          | 1000                  | kHz  |                                            |

| Repeated Start Hold<br>Time                | T <sub>HD;STA</sub> | 0.6                        | -                     | 0.26                       | -                     | μs   |                                            |

| SCL Low Time                               | T <sub>LOW</sub>    | 1.3                        | -                     | 0.5                        | -                     | μs   |                                            |

| SCL High Time                              | T <sub>HIGH</sub>   | 0.6                        | -                     | 0.26                       | -                     | μs   |                                            |

| Repeated Start<br>Setup Time               | T <sub>SU;STA</sub> | 0.6                        | -                     | 0.26                       | -                     | μs   |                                            |

| Data Hold Time                             | T <sub>HD;DAT</sub> | 0                          | -                     | 0                          | -                     | μs   |                                            |

| Data Setup Time                            | T <sub>SU;DAT</sub> | 100                        | -                     | 50                         | -                     | ns   |                                            |

| SDA, SCL Rise Time                         | T <sub>R</sub>      | 20                         | 300                   | -                          | 120                   | ns   |                                            |

| SDA, SCL Fall Time                         | T <sub>F</sub>      | 20*(V <sub>DD</sub> /5)    | 300                   | 20*(V <sub>BUS</sub> /5)   | 120                   | ns   |                                            |

| STOP setup Time                            | T <sub>SU;STO</sub> | 0.6                        | -                     | 0.26                       | -                     | μs   |                                            |

| Bus Free Time<br>between STOP and<br>START | T <sub>BUF</sub>    | 1.3                        | -                     | 0.5                        | -                     | μs   |                                            |

| Bus Capacitive Load                        | C <sub>BUS</sub>    | -                          | 400                   | -                          | 550                   | pF   |                                            |

| Data Valid Time                            | T <sub>VD;DAT</sub> | -                          | 0.9                   | -                          | 0.45                  | μs   |                                            |

| Data Valid ACK Time                        | T <sub>VD;ACK</sub> | -                          | 0.9                   | -                          | 0.45                  | μs   |                                            |

| Noise Margin at<br>LOW Level               | V <sub>NL</sub>     | 0.1*V <sub>DD</sub>        | -                     | 0.1*V <sub>DD</sub>        | -                     | ٧    |                                            |

| Noise Margin at<br>HIGH Level              | V <sub>NH</sub>     | 0.2*V <sub>DD</sub>        | -                     | 0.2*V <sub>DD</sub>        | -                     | ٧    |                                            |

#### DC/AC Characteristics (continued)

Electrical Characteristics:  $6*V_{OUT} < PV_{IN} < 16V$ ,  $4.5V < V_{IN} < 16V$ ,  $0^{\circ}C < T_{A} < 125^{\circ}C$  unless specified otherwise, Typicals at  $T_{A} = 25^{\circ}C$

| Parameter <sup>(1 - all</sup> | Symbol          | Fast-mod | de   | Fast-mod | e Plus | Unit | Conditions |

|-------------------------------|-----------------|----------|------|----------|--------|------|------------|

| parameters)                   | Min. Max.       |          | Max. | Min.     | Max.   |      |            |

| SDA Timeout                   | T <sub>TO</sub> | 200      |      | 200      |        | μs   |            |

#### Note:

1. Characterized parameter, not production tested.

**Table 3-1.** Package Thermal Characteristics

| Parameter                                 | Symbol              | Min. | Тур. | Max. | Units | Conditions       |

|-------------------------------------------|---------------------|------|------|------|-------|------------------|

| Junction to Ambient Thermal<br>Resistance | $R_{\theta JA}$     | _    | 20.5 | _    | °C/W  | JEDEC JESD 51-2A |

| Junction to PCB Thermal<br>Resistance     | R <sub>0J-PCB</sub> | _    | 5.5  | _    | °C/W  | JEDEC JESD 51-8  |

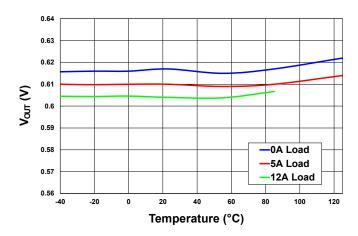

### 4. Typical Performance Curves

The graphs and tables provided in this section are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

**Important:** Unless otherwise stated, test conditions are 12V input, 1.2V output, mode A operation, using a voltage divider to set the output voltage.

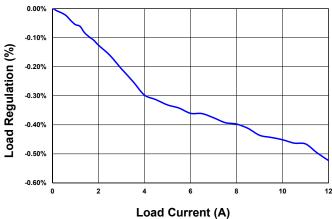

Figure 4-1. Load Regulation vs. Temperature

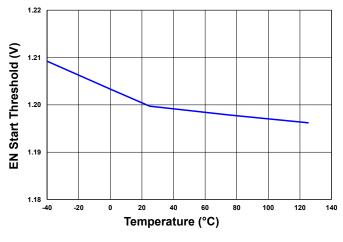

Figure 4-2. Enable Start Threshold vs. Temperature

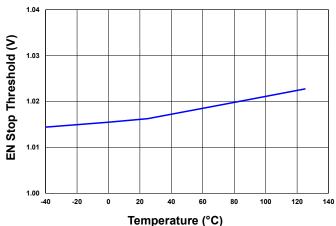

Figure 4-3. Enable Stop Threshold vs. Temperature

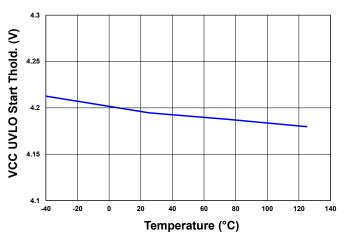

Figure 4-4. VCC Start Threshold vs. Temperature

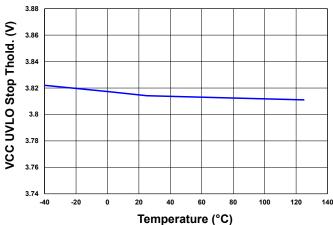

Figure 4-5. VCC Stop Threshold vs. Temperature

Figure 4-6. ON Time vs. Temperature

Figure 4-7. OFF Time vs. Temperature

Figure 4-8. Soft Start Rate vs. Temperature

Figure 4-9. Dynamic Input Current vs. Temperature

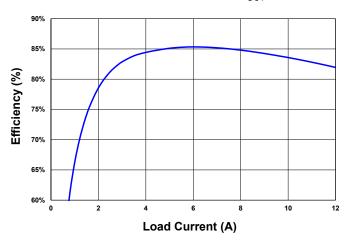

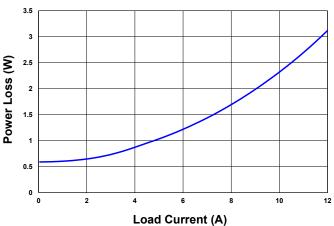

**Figure 4-10.** Typical Efficiency (PVIN = 12V,  $V_{OUT} = 1.0V$ )

**Figure 4-11.** Typical Power Loss (PVIN = 12V,  $V_{OUT} = 1.0V$ )

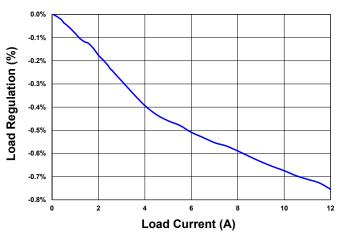

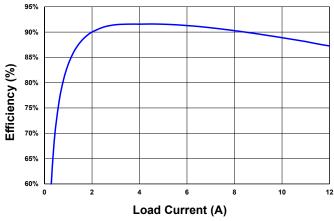

Figure 4-12. Typical Load Regulation (PVIN = 12V,  $V_{OUT} = 1.0V$ , Figure 4-13. Typical Efficiency (PVIN = 12V,  $V_{OUT} = 1.8V$ , I<sub>OUT</sub> = 0-12A, Room Temeperature, No Air Flow, All Loses Included)

External VCC Source Applied)

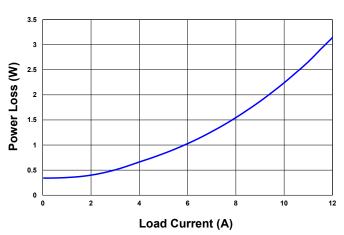

**Figure 4-14.** Typical Power Loss (PVIN = 12V, V<sub>OUT</sub> = 1.8V, External VCC Source Applied)

**Figure 4-15.** Typical Load Regulation (PVIN = 12V,  $V_{OUT} = 1.8V$ , External VCC Source Applied)

Figure 4-16. Startup (No Load)

Figure 4-17. Startup (12A Load)

Figure 4-18. Shutdown via EN De-assertion (No Load)

Figure 4-19. Shutdown via EN De-assertion (12A Load)

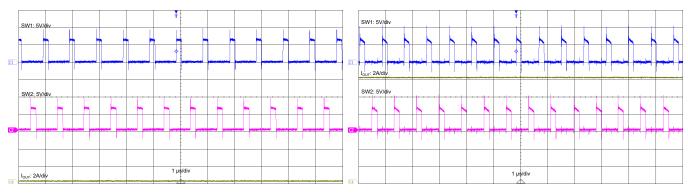

Figure 4-20. Switching Waveforms (No Load)

Figure 4-21. Switching Waveforms (12A Load)

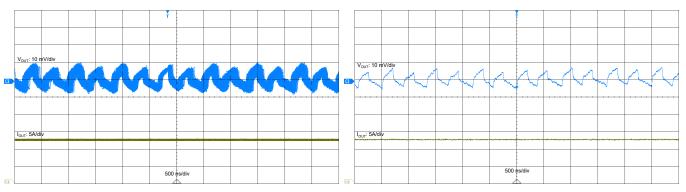

Figure 4-22.  $V_{OUT}$  Ripple - Persistent

Figure 4-23. V<sub>OUT</sub> Ripple

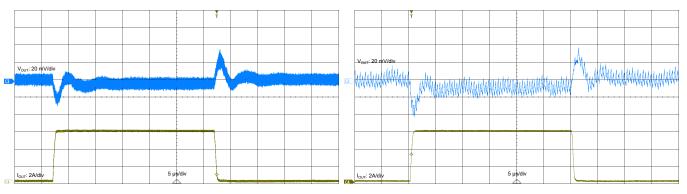

Figure 4-24. Transient Response - Persistent

Figure 4-25. Transient Response

### 5. Design Example

For this example, the specifications are:

- $PV_{IN} = V_{IN} = 12V$

- V<sub>OUT</sub> = 1.0V

- I<sub>OLIT</sub> = 12A

- $F_{SW} = 800 \text{ kHz}$

- $C_{OLIT} = 4 \times 47 \mu F$

- $C_{IN} = 3 \times 22 \,\mu\text{F}$

- Ripple Voltage = ±1% × V<sub>OUT</sub>

- $\Delta V_{OUT(MAX)} = \pm 3\% \times V_{OUT}$  (for 50% load transient @ 40 A/µs)

#### **Input Capacitor**

The input capacitor chosen for this design must:

- Accommodate the peak and RMS input currents required by the MCPF1412M06

- Possess low equivalent series resistance (ESR) and inductance (ESL) to minimize input voltage ripple

MLCCs (multi-layer ceramic capacitors) are ideal for this purpose. Typically, in an 0805 case size, they can handle 2A RMS current with less than a 5°C temperature rise. For the MCPF1412M06 converter topology operating at duty cycle D and output current  $I_{OUT}$ , the RMS value of the input current is:

$$I_{RMS} = 0.5 \times I_{OUT} \times \sqrt{D \times (1 - D)}$$

In this application  $I_{OUT}$  is 12A and D is 2 × VOUT/VIN (aggregate duty for a 2 phase converter) or 0.167. Thus, the input capacitor  $I_{RMS}$  is 2.23A, and we can choose three 22  $\mu$ F 25V ceramic capacitors for the input capacitors (C2012X5R1E226M125AC from TDK). If the MCPF1412M06 is not positioned near the 12V power supply, an additional bulk capacitor (68–330  $\mu$ F) may be used alongside the ceramic capacitors.

For VIN, which serves as the input to the LDO, it is recommended to place a 1  $\mu$ F capacitor very close to the pin. The VIN pin should be connected to PVIN via a 2.7 $\Omega$  resistor and a 1  $\mu$ F capacitor at the PVIN pin, to help filter noise on PVIN.

#### **Output Voltage and Output Capacitor**

The MCPF1412M06 is factory-calibrated to deliver a 0.6V output in a closed-loop configuration. When opting for a resistor divider instead of using  $I^2C/PMBus^{\text{TM}}$ , as illustrated in the application example, resistor values should be selected based on the guidelines provided in Section 2.5. Consequently,  $R_{\text{TOP}}$  is set to 4.12 k $\Omega$ ,  $R_{\text{BOTTOM}}$  to 5.9 k $\Omega$ , and  $C_{\text{FF}}$  to 220 pF. The design necessitates minimal output capacitance to achieve the desired output voltage ripple and maximum output voltage deviation during load transients. For the MCPF1412M06, the minimum number of output capacitors needed to meet the target peak-to-peak VOUT ripple is:

$$N_{MIN} = 5.8 \times \frac{\frac{(1-D)}{8 \times C \times F_{SW}} + ESR \times (1-D) + \frac{ESL \times F_{SW} \times (1-D^2)}{D}}{\Delta VOUT_{ripple(p-p)}}$$

#### Where:

- N<sub>MIN</sub> is the minimum number of output capacitors required

- C is the equivalent capacitance of each capacitor

- F<sub>SW</sub> is the switching frequency

- ESR is the equivalent series resistance of each output capacitor

- ELS is the equivalent series inductance of each capacitor

- ΔVOUT<sub>ripple(p-p)</sub> is the maximum peak to peak output ripple allowed

This design uses the TDK C2012X5R0J476M125AC, a 47  $\mu$ F MLCC with an 0805 case size and a 6.3V rating. Considering DC bias and AC ripple derating at 1.0V, its equivalent capacitance is 33  $\mu$ F. The equivalent series resistance (ESR) is 3  $m\Omega$ , and the equivalent series inductance (ESL) is 0.44 nH. Using these parameters in the equation results in:

$$N_{MIN} = 2.27$$

To achieve the maximum voltage deviation  $\Delta V_{Omax}$  during a  $\Delta I_O$  load transient, the minimum number of output capacitors needed is:

$$N_{MIN} = \frac{0.196 \times \Delta I^2}{4 \times \Delta V_{Omax} \times F_{SW} \times C}$$

#### Where:

- ΔI is the load step

- ΔV<sub>Omax</sub> is the maximum voltage deviation allowed

- F<sub>SW</sub> is the switching frequency

- C is the capacitance of each capacitor

Using a capacitance of 33  $\mu$ F, it is determined that a minimum of 2.22 output capacitors are needed. For our design, which is intended for space-constrained applications, we have chosen to use four C2012X5R0J476M125AC capacitors.

It is important to note that the calculation for the minimum number of output capacitors under a load transient is based on several assumptions:

- No Equivalent Series Resistance (ESR) or Equivalent Series Inductance (ESL) (a)

- The converter can instantly saturate its duty cycle (b)

- No latency (c)

- Step load with an infinite slew rate (d)

Assumptions (a), (b), and (c) are optimistic, while assumption (d) is conservative. Therefore, in practical applications, additional capacitance may be necessary to meet transient requirements, and this should be carefully evaluated by the system designer.

Even without a specified target VOUT ripple or maximum voltage deviation under load transient, a minimum of one 22  $\mu$ F capacitor is necessary to ensure stable operation without excessive jitter. Up to eight 47  $\mu$ F capacitors can be used in the design. If additional capacitance is needed, it is advisable to use a high-value capacitor with a relatively high ESR (>3 m $\Omega$ ).

#### **VCC and PVCC Capacitors**

The MCPF1412M06 incorporates on-package capacitors for both VCC and PVCC to ensure efficient high-frequency bypassing. However, for applications utilizing an external VCC supply, it is advisable for system designers to place 2.2  $\mu$ F/0603/X7R/10V capacitors on the application board as close as possible to the VCC and PVCC pins (see Figure 5-1).

Figure 5-1. Application Circuit Design for  $PV_{IN}$  = 12V,  $V_{OUT}$  = 1.0V and  $I_{OUT}$  = 12A

Table 5-1. Application Circuit Design Components

| C <sub>IN1</sub>  | 68 μF, 25V (optional)             |

|-------------------|-----------------------------------|

| C <sub>IN2</sub>  | 2 x 22 μF, 16V, 0805, X5R         |

| $C_{VCC}$         | 2.2 μF, 10V, 0603, X5R (optional) |

| C <sub>PVCC</sub> | 2.2 μF, 10V, 0603, X5R (optional) |

| C <sub>FF</sub>   | 220 pF                            |

| $R_{TOP}$         | 4.12 kΩ                           |

| R <sub>BOT</sub>  | 5.9 kΩ                            |

| C <sub>OUT</sub>  | 4 x 47 μF, 6.3V, 0805, X5R        |

### 6. Layout Recommendations

#### General

The MCPF1412M06 is a highly integrated device requiring minimal external components, which simplifies PCB layout. However, to ensure optimal performance, adhere to these general PCB design guidelines:

- Place bypass capacitors, including input/output capacitors and the VCC bypass capacitor (if used), as close as possible to the MCPF1412M06 pins.

- Sense the output voltage with a separate trace directly from the output capacitor.

- For thermal dissipation, connect the PGND pad to the power ground plane using vias. Copperfilled vias are preferred, but plated-through-hole vias are acceptable if not covered with solder mask. VIPPO techniques are also acceptable.

- Use an adequate number of vias to connect between layers, especially for power traces.

- Connect AGND pins to the PGND copper layer using vias.

- To minimize power losses and improve thermal dissipation, use wide copper polygons for input and output power connections.

#### **Thermal**

The MCPF1412M06 has undergone thermal testing and modeling in line with JEDEC standards JESD 51-2A and JESD 51-8. Testing was conducted using a 4-layer application PCB, featuring thermal vias beneath the device to aid in cooling.

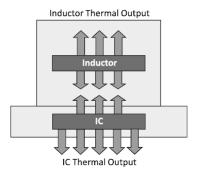

The MCPF1412M06 has two main heat sources:

- The power MOSFET section of the IC

- The inductor

The IC is effectively coupled to the PCB, which serves as its primary cooling pathway. While the inductor is also connected to the PCB, its main cooling mechanism is through convection. Ultimately though, both heat sources dissipate heat through convection. The PCB functions as a heat spreader or, to some extent, a heat sink.

Figure 6-1. Heat Sources in the MCPF1412M06

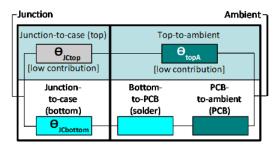

Figure 6-2 illustrates the thermal resistances in the MCPF1412M06, described as follows:

- $\theta_{JA}$  represents the measure of natural convection from the assembled test sample within a confined enclosure of approximately 30 x 30 cm. The air in this environment is passive, with movement occurring solely due to convection from the device under test.

- $\theta_{\text{JCbottom}}$  indicates the heat flow from the IC to the bottom of the package, where it is well-coupled. The testing method follows the procedure outlined in JESD 51-8, with the test PCB clamped between cold plates at specified distances from the device.

θ<sub>JCtop</sub> theoretically represents the heat flow from the IC to the top of the package. However, this

is not applicable to the MCPF1412M06 for two reasons: firstly, it is not the primary conduction

path of the IC, and more importantly, the inductor is positioned directly over the IC. Since the

inductor generates a similar amount of heat as the IC, a meaningful value for junction-to-case

(top) cannot be determined.

Figure 6-2. Thermal Resistances of the MCPF1412M06. Internal on the Left, External on the Right

The thermal resistance values are as follows:

- $\theta_{IA} = 20.5$ °C/W

- $\theta_{\text{ICbottom}} = 5.5^{\circ}\text{C/W}$

While these values provide a comparison of the MCPF1412M06 with similar POL products under identical conditions and specifications, they are not sufficient for predicting overall thermal performance. For precise modeling of the device's interaction with its environment, Computational Fluid Dynamics (CFD) simulation software is required to simultaneously calculate the combined effects of conduction and convection.

**Note:** All tests assume passive or static airflow; applications using forced air may achieve better cooling.

#### 7. PMBus Commands

Table 7-1. PMBus Commands List

| No. | Name                 | Adr.            | No. | Name                   | Adr. | No. | Name               | Adr. |

|-----|----------------------|-----------------|-----|------------------------|------|-----|--------------------|------|

| 1   | OPERATION            | 0x01            | 18  | VOUT_OV_FAULT_RESPONSE | 0x41 | 35  | STATUS_BYTE        | 0x78 |

| 2   | ON_OFF_CONFIG        | 0x02            | 19  | VOUT_OV_WARN_LIMIT     | 0x42 | 36  | STATUS_WORD        | 0x79 |

| 3   | CLEAR_FAULTS         | 0x03            | 20  | VOUT_UV_WARN_LIMIT     | 0x43 | 37  | STATUS_VOUT        | 0x7A |

| 4   | WRITE_PROTECT        | 0x10            | 21  | VOUT_UV_FAULT_LIMIT    | 0x44 | 38  | STATUS_IOUT        | 0x7B |

| 5   | STORE_USER_ALL       | 0x15            | 22  | VOUT_UV_FAULT_RESPONSE | 0x45 | 39  | STATUS_INPUT       | 0x7C |

| 6   | RESTORE_USER_ALL     | 0x16            | 23  | IOUT_OC_FAULT_LIMIT    | 0x46 | 40  | STATUS_TEMPERATURE | 0x7D |

| 7   | CAPABILITY           | 0x19            | 24  | IOUT_OC_FAULT_RESPONSE | 0x47 | 41  | STATUS_CML         | 0x7E |

| 8   | SMBALERT_MASK        | 0x1B            | 25  | VIN_OV_FAULT_LIMIT     | 0x55 | 42  | READ_VIN           | 0x88 |

| 9   | VOUT_MODE            | 0x20            | 26  | VIN_OV_FAULT_RESPONSE  | 0x56 | 43  | READ_VOUT          | 0x8B |

| 10  | VOUT_COMMAND         | 0x21            | 27  | VIN_UV_WARN_LIMIT      | 0x58 | 44  | READ_TEMPERATURE   | 0x8D |

| 11  | VOUT_MAX             | 0x24            | 28  | POWER_GOOD_ON          | 0x5E | 45  | PMBUS_REVISION     | 0x98 |

| 12  | VOUT_MARGIN_HIGH     | 0x25            | 29  | TON_DELAY              | 0x60 | 46  | MFR_ID             | 0x99 |

| 13  | VOUT_MARGIN_LOW      | 0x26            | 30  | TON_RISE               | 0x61 | 47  | MFR_MODEL          | 0x9A |

| 14  | VOUT_TRANSITION_RATE | 0x27            | 31  | TON_MAX_FAULT_LIMIT    | 0x62 | 48  | MFR_REVISION       | 0x9B |

| 15  | VIN_ON               | 0x35 32 TON_MAX |     | TON_MAX_FAULT_RESPONSE | 0x63 | 49  | IC_DEVICE_ID       | 0xAD |

| 16  | VIN_OFF 0x36         |                 | 33  | TOFF_DELAY             | 0x64 | 50  | IC_DEVICE_REV      | 0xAE |

| 17  | VOUT_OV_FAULT_LIMIT  | 0x40            | 34  | TOFF_FALL              | 0x65 |     |                    |      |

#### **OPERATION (0x01)**

The OPERATION command is used to turn the device output ON or OFF. It is also used to set the output voltage to the upper or lower MARGIN voltages.

| COMMAND   | OPERATION |     |   |   |   |   |   |   |  |  |  |  |  |

|-----------|-----------|-----|---|---|---|---|---|---|--|--|--|--|--|

| Bit       | 7         | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |  |

| Access    | R/W       | R/W |   |   |   |   |   |   |  |  |  |  |  |

| Default # | 1         | 0   | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |  |  |

Bit [7]: Controls if PMBus device output is ON or OFF

- 0: Output is OFF

- 1: Output is ON

Bit [6]: Controls the power down behavior

- 0 : Output is turned OFF immediately

- 1: The device is powered down following the values set in the TOFF\_DELAY command

Bit [5:4]: Voltage command source

- 00 : The nominal output voltage is set by the PMBus VOUT\_COMMAND data

- 01 : The nominal output voltage is set by the PMBus VOUT\_MARGIN\_LOW data

- 10: The nominal output voltage is set by the PMBus VOUT\_MARGIN\_HIGH data

- 11 : AVS Bus (AVS Bus not supported)

Bit [3:2]: Margin fault response

- 00: Invalid

- 01 : The faults caused by VOUT\_MARGIN\_HIGH or VOUT\_MARGIN\_LOW are ignored

- 10: The faults caused by VOUT\_MARGIN\_HIGH or VOUT\_MARGIN\_LOW are acted upon

- 11: Invalid

Bit [1]: Transition control (AVS Bus not implemented)

Bit [0]: Reserved

#### ON\_OFF\_CONFIG (0x02)

| COMMAND   | ON_OFF_C | ON_OFF_CONFIG |   |   |   |   |   |   |  |  |  |  |  |

|-----------|----------|---------------|---|---|---|---|---|---|--|--|--|--|--|

| Bit       | 7        | 6 5 4 3 2 1 0 |   |   |   |   |   |   |  |  |  |  |  |

| Access    | R/W      | R/W           |   |   |   |   |   |   |  |  |  |  |  |

| Default # | 0        | 0             | 0 | 1 | 1 | 1 | 1 | 1 |  |  |  |  |  |

Bit [7:5]: Reserved

Bit [4]: Sets the default to either operate when power is present or for the ON/OFF to be controlled by serial bus commands

- 0 : Device powers up when the power is present

- 1 : Device does not power up until commanded by the OPERATION command

Bit [3]: Controls how the unit responds to commands received via the serial bus

- 0 : Device ignores the ON/OFF portion of the OPERATION command from serial bus

- 1 : Device requires the ON/OFF portion of the OPERATION command

Bit [2]: Controls how the unit responds to the EN pin

- 0 : Unit ignores the EN pin (ON/OFF controlled only the OPERATION command)

- 1: Unit requires the EN pin to be asserted to start the unit

Bit [1]: Polarity of the EN pin

- 0 : Active low

- 1 : Active high

Bit [0]: EN pin action

- 0: Use the programmed turn OFF delay and fall time

- 1 : Turn OFF the output and stop transferring energy to the output as fast as possible

#### CLEAR FAULTS (0x03)

The CLEAR\_FAULTS command is used to clear any fault bits that have been set. This command clears all bits in all status registers simultaneously. At the same time, the device releases its SMBALERT signal output if the device is asserting the SMBALERT signal. The CLEAR\_FAULTS command does not cause a unit that has latched off for a fault condition to restart. If the fault is still present when the bit is cleared, the fault bit is immediately reset and the host notified by the usual means.

#### WRITE\_PROTECT (0x10)

| COMMAND   | WRITE_PRC | WRITE_PROTECT |   |   |   |   |   |   |  |  |  |  |  |

|-----------|-----------|---------------|---|---|---|---|---|---|--|--|--|--|--|

| Bit       | 7         | 6 5 4 3 2 1 0 |   |   |   |   |   |   |  |  |  |  |  |

| Access    | R/W       | R/W           |   |   |   |   |   |   |  |  |  |  |  |

| Default # | 0         | 0             | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |  |  |

Bit [7]: Control writing to the PMBus device for protection against accidental changes

- 0 : Enable all writes as permitted in bit 5 or bit 6

- 1 : Disable all writes except the WRITE\_PROTECT command (bit 5 and bit 6 must be 0)

Bit [6]: Control writing to the PMBus device for protection against accidental changes

- 0 : Enable all writes as permitted in bit 5 or bit 7

- 1 : Disable all writes except for the WRITE\_PROTECT, and OPERATION commands (bit 5 and bit 7 must be 0)

Bit [5]: Control writing to the PMBus device for protection against accidental changes

- 0: Enable all writes as permitted in bit 6 or bit 7

- 1 : Disable all writes except the WRITE\_PROTECT, OPERATION, ON\_OFF\_CONFIG, and VOUT\_COMMAND. (bit 6 and bit 7 must be 0)

Bit [4:0]: Reserved

#### STORE\_USER\_ALL (0x15)

The STORE\_USER\_ALL command stores all of the current storable register settings in the EEPROM memory as the new defaults on power up. It is permissible to use this command while the device is switching. To use this command:

- 1. Set all settings to the desired power up configuration.

- 2. Pull EN low to disable switching.

- 3. Apply  $7.5 \pm 0.25$ V to the VIN pin

- 4. Execute the command.

- 5. Execute a RESTORE\_USRE\_ALL command..

- 6. Compare the settings in the part values with the expected settings. If they differ, repeat this procedure. If the settings differ a second time, discard the part.

#### RESTORE\_USER\_ALL (0x16)

The RESTORE\_USER\_ALL command restores all of the storable register settings from EEPROM memory to those registers which are unprotected. This command should not be used while the part is converting power.

#### CAPABILITY (0x19)

| COMMAND   | CAPABILITY | CAPABILITY |   |   |   |   |   |   |  |  |  |  |  |

|-----------|------------|------------|---|---|---|---|---|---|--|--|--|--|--|

| Bit       | 7          | 6          | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |  |

| Access    | R          |            |   |   |   |   |   |   |  |  |  |  |  |

| Default # | 0          | 0          | 1 | 1 | 0 | 0 | 0 | 0 |  |  |  |  |  |

Bit [7]: Packet Error Checking

0 : Packet Error Checking not supported

Bit [6:5]: Maximum Bus Speed

01: Maximum supported bus speed is 400 kHz

Bit [4]: SMBALERT#

1 : Enable the SMBus Alert Response protocol

Bit [3]: Numeric Format

0: Numeric data is in LINEAR11, ULINEAR16, SLINEAR16

Bit [2]: AVSBus Support

0 : AVSBus not supported

Bit [1:0]: Reserved

#### SMBALERT MASK (0x1B)

The SMBALERT\_MASK command may be used to prevent a warning or fault condition from asserting the SMBALERT# signal. The bits in the mask byte align with the bits in the corresponding status register. For example if the STATUS\_TEMPERATURE command code were sent with the mask byte 01000000b, then an Overtemperature Warning condition would be blocked from asserting SMBALERT#. This command cannot be used with STATUS\_BYTE or STATUS\_WORD. Since these commands are the logical or of underlying status registers, use the underlying status commands as the status command code sent to set a mask value. The access mode is a write word transaction for the write and a block write block read transaction for reading. Refer to the SMBus specification for details on this transaction.

#### VOUT\_MODE (0x20)

The data byte for the VOUT\_MODE command is one byte that consists of bit [7:5] as Mode and bit[4:0] as Exponent Parameter. The three-bit Mode sets whether the device uses the ULINEAR16, Half-precision IEEE 754 floating point, VID or DIRECT modes for output voltage related commands. The five-bit Parameter provides more information about the selected mode.

| COMMAND   | VOUT_MOI | VOUT_MODE |   |   |   |   |   |   |  |  |  |  |  |

|-----------|----------|-----------|---|---|---|---|---|---|--|--|--|--|--|

| Bit       | 7        | 6         | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |  |

| Access    | R        |           |   |   |   |   |   |   |  |  |  |  |  |

| Default # | 1        | 0         | 0 | 1 | 1 | 0 | 0 | 0 |  |  |  |  |  |

Bit [7]: Data type

• 1 : Device supports relative mode

Bit [6:5]: Data type

• 00 : Five bit two's complement exponent for the mantissa delivered as the data bytes for an output voltage related command

Bit [4:0]: Exponent parameter

#### **VOUT COMMAND (0x21)**

The VOUT\_COMMAND command sets the output voltage in volts

| COMMAND   | VOUT   | VOUT_COMMAND                         |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|-----------|--------|--------------------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Bit       | 15     | 5 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| Access    | R/W, I | R/W, Linear 16 format                |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| Default # | 0      | 0                                    | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 |

Bit [15:0]: Two linear16 data bytes

Note that this part does not use VOUT\_SCALE\_LOOP. The value provided via the VOUT\_COMMAND command is the voltage that the part will regulate the FB pin to. Any voltage divider used on that pin will need to be accounted for by the user when using VOUT\_COMMAND.

#### VOUT\_MAX (0x24)

The VOUT\_MAX command sets the maximum output voltage. The purpose is to protect the devices on the output rail supplied by this device from a higher than acceptable output voltage

| COMMAND   | VOUT   | VOUT_MAX                             |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|-----------|--------|--------------------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Bit       | 15     | 5 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| Access    | R/W, I | R/W, Linear 16 format                |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| Default # | 0      | 0                                    | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Bit [15:0]: Two linear 16 data bytes

#### **VOUT MARGIN HIGH (0x25)**

This VOUT\_MARGIN\_HIGH command loads the unit with the voltage to which the output is to be changed when the OPERATION command is set to "Margin High."

| COMMAND   | VOUT | _MARG                              | IN_HIG | iН |   |   |   |   |   |   |   |   |   |   |   |   |

|-----------|------|------------------------------------|--------|----|---|---|---|---|---|---|---|---|---|---|---|---|

| Bit       | 15   | 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |        |    |   |   |   |   |   |   |   |   |   |   |   |   |

| Access    | R/W, | R/W, Linear 16 format              |        |    |   |   |   |   |   |   |   |   |   |   |   |   |

| Default # | 0    | 0                                  | 0      | 0  | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 |

Bit [15:0]: Two linear 16 data bytes

#### VOUT\_MARGIN\_LOW (0x26)

This VOUT\_MARGIN\_LOW command loads the unit with the voltage to which the output is to be changed when the OPERATION command is set to "Margin Low."

| COMMAND   | VOUT | _MARG                              | in_lo\ | V |   |   |   |   |   |   |   |   |   |   |   |   |

|-----------|------|------------------------------------|--------|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Bit       | 15   | 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |        |   |   |   |   |   |   |   |   |   |   |   |   |   |

| Access    | R/W, | R/W, Linear 16 format              |        |   |   |   |   |   |   |   |   |   |   |   |   |   |

| Default # | 0    | 0                                  | 0      | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 |

Bit [15:0]: Two linear 16 data bytes

#### VOUT\_TRANSITION\_RATE (0x27)

VOUT\_TRANSITION\_RATE command sets the rate in mV/µs at which the output should change voltage.

| COMMAND   | VIN_C | NC                    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|-----------|-------|-----------------------|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Bit       | 15    | 14                    | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Access    | R/W,  | X/W, Linear 11 format |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Default # | 1     | 1                     | 1  | 1  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

Bits [15:11]: A 5 bit, two's complement exponent for the calculation, fixed at -2

Bits [10:0]: An 11 bit, two's complement mantissa for the calculation

Valid range: 0 to 31.75 mV/ms

#### VIN ON (0x35)

The VIN\_ON command sets the value of the input voltage, in Volts, at which the unit should start power conversion.

| COMMAND   | VIN_C | N                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|-----------|-------|-----------------------|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Bit       | 15    | 14                    | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Access    | R/W,  | R/W, Linear 11 format |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Default # | 1     | 1                     | 1  | 1  | 1  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

Bits [15:11]: A 5 bit, two's complement exponent, fixed at -1.

Bits [10:0]: An 11 bit, two's complement mantissa

Valid range: 0V to 15.5V

#### VIN\_OFF (0x36)

The VIN\_OFF command sets the value of the input voltage, in Volts, at which the unit, once operation has started, should stop power conversion.

| COMMAND   | VIN_0 | OFF                   |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|-----------|-------|-----------------------|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Bit       | 15    | 14                    | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Access    | R/W,  | R/W, Linear 11 format |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Default # | 1     | 1                     | 1  | 1  | 1  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

Bits [15:11]: A 5 bit, two's complement exponent, fixed at -1

Bit [10:0]: An 11 bit, two's complement mantissa

Valid range: 0V to 15.5V

#### **VOUT OV FAULT LIMIT (0x40)**

The VOUT\_OV\_FAULT\_LIMIT command sets the value of the output voltage measured at the sense or output pins that causes an output overvoltage fault.

| COMMAND   | VOUT   | _OV_FA                             | AULT_LI | MIT |   |   |   |   |   |   |   |   |   |   |   |   |

|-----------|--------|------------------------------------|---------|-----|---|---|---|---|---|---|---|---|---|---|---|---|

| Bit       | 15     | 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |         |     |   |   |   |   |   |   |   |   |   |   |   |   |

| Access    | R/W, I | R/W, Linear 16 relative format     |         |     |   |   |   |   |   |   |   |   |   |   |   |   |

| Default # | 0      | 0                                  | 0       | 0   | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

Bit [15:0]: A 16 bit, two's complement integer

#### VOUT\_OV\_FAULT\_RESPONSE (0x41)

The VOUT\_OV\_FAULT\_RESPONSE command instructs the device on what action to take in response to an output overvoltage fault

| COMMAND   | VOUT_OV_ | FAULT_RESP | VOUT_OV_FAULT_RESPONSE |   |   |   |   |   |  |  |  |  |  |  |  |

|-----------|----------|------------|------------------------|---|---|---|---|---|--|--|--|--|--|--|--|

| Bit       | 7        | 6          | 5                      | 4 | 3 | 2 | 1 | 0 |  |  |  |  |  |  |  |

| Access    | R/W      |            |                        |   |   |   |   |   |  |  |  |  |  |  |  |

| Default # | 1        | 0          | 0                      | 0 | 0 | 0 | 0 | 0 |  |  |  |  |  |  |  |

Valid values:

0x00: Continue without interruption

0x80: Shuts down and does not attempt to restart

0xC0: Shuts down and attempts to restart when the fault condition is no longer present

#### VOUT\_OV\_WARN\_LIMIT (0x42)

The VOUT\_OV\_WARN\_LIMIT command sets the value of the output voltage at the sense or output pins that causes an output voltage high warning. This value is typically less than the output overvoltage threshold.

| COMMAND   | VOUT   | _OV_W                          | /ARN_L | IMIT |    |    |   |   |   |   |   |   |   |   |   |   |

|-----------|--------|--------------------------------|--------|------|----|----|---|---|---|---|---|---|---|---|---|---|

| Bit       | 15     | 14                             | 13     | 12   | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Access    | R/W, I | R/W, Linear 16 relative format |        |      |    |    |   |   |   |   |   |   |   |   |   |   |

| Default # | 0      | 0                              | 0      | 0    | 0  | 0  | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 |

Bit [15:0]: A 16 bit, two's complement integer

#### VOUT\_UV\_WARN\_LIMIT (0x43)

The VOUT\_UV\_WARN\_LIMIT command sets the value of the output voltage at the sense or output pins that causes an output voltage low warning. This value is typically greater than the output undervoltage fault threshold.

| COMMAND   | VOUT   | _UV_W                                | ARN_LI | MIT |   |   |   |   |   |   |   |   |   |   |   |   |

|-----------|--------|--------------------------------------|--------|-----|---|---|---|---|---|---|---|---|---|---|---|---|

| Bit       | 15     | 5 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |        |     |   |   |   |   |   |   |   |   |   |   |   |   |

| Access    | R/W, I | R/W, Linear 16 relative format       |        |     |   |   |   |   |   |   |   |   |   |   |   |   |

| Default # | 0      | 0                                    | 0      | 0   | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 |

Bit [15:0]: A 16 bit, two's complement integer

#### **VOUT UV FAULT LIMIT (0x44)**

The VOUT\_UV\_FAULT\_LIMIT command sets the value of the output voltage at the sense or output pins that causes an output undervoltage fault. This fault is masked until the unit reaches the programmed output voltage. This fault is also masked when the unit is disabled.

| COMMAND   | VOUT | _UV_FA                             | AULT_LI | IMIT |   |   |   |   |   |   |   |   |   |   |   |   |

|-----------|------|------------------------------------|---------|------|---|---|---|---|---|---|---|---|---|---|---|---|

| Bit       | 15   | 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |         |      |   |   |   |   |   |   |   |   |   |   |   |   |

| Access    | R/W, | R/W, Linear 16 relative format     |         |      |   |   |   |   |   |   |   |   |   |   |   |   |

| Default # | 0    | 0                                  | 0       | 0    | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

Bit [15:0]: A 16 bit, two's complement integer

#### **VOUT UV FAULT RESPONSE (0x45)**

The VOUT\_UV\_FAULT\_RESPONSE command instructs the device on what action to take in response to an output undervoltage fault

| COMMAND   | VOUT_UV_F | AULT_RESPO  | NSE |   |   |   |   |   |  |  |  |  |  |  |

|-----------|-----------|-------------|-----|---|---|---|---|---|--|--|--|--|--|--|

| Bit       | 7         | 6 5 4 3 2 1 |     |   |   |   |   |   |  |  |  |  |  |  |

| Access    | R/W       |             |     |   |   |   |   |   |  |  |  |  |  |  |

| Default # | 0         | 0           | 0   | 0 | 0 | 0 | 0 | 0 |  |  |  |  |  |  |

Valid values:

0x00: Continue without interruption

0x80: Shuts down and does not attempt to restart

#### IOUT\_OC\_FAULT\_LIMIT (0x46)

The IOUT\_OC\_FAULT\_LIMIT command sets the value of the output current, in Amperes, that causes the overcurrent detector to indicate an overcurrent fault condition