## DATASHEET

**Revision: 1.03**

Release date: 07/11/2014

## **RDA8810P**

## **GSM/GPRS/EDGE Smartphone Application Processor**

The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of RDA.

1 / 127

## **RDA8810P Smartphone Application Processor**

## PLATFORM FEATURES

## **MODEM FEATURES**

#### AP MCU subsystem

- ARM Cortex-A5 32-bit RISC processor, with FPU and SIMD NEON engine, up to 1G Hz

- 32kB L1 I-cache and 32kB L1 D-cache; 256kB unified L2 cache

- In-house VOC DSP for voice and image process

- 64-bit AXI fabric, up to 400MHz

- 64kB on-chip ROM for system boot

- 64kB on-chip SRAM for internal use

#### Memory interface

- Integrated 2Gb LPDDR2 SDRAM

- Integrated 4Gb 8Bit 2.8V 4K SLC Nand Flash

- Two SDIO interfaces, for TF cards and WIFI

- support 4.4.1 EMMC interface

- support SPI-NAND and SPI-NOR

#### Connectivity

- Support 3 SIM cards and both 1.8V and 3.0V device

- USB2.0 high-speed OTG

- 3 UARTs for GPS, BT, FM, and debugging interfaces

- 3 SPI for peripheral devices

- 3 I2C for peripheral devices

- 1 I2S for peripheral devices

- 4 10-bit GPADC for sampling peripheral signals

- 64 GPIOs, includes 16 interruptable GPIOs

- Pulse Width Modulation (PWM) 1 PWL, 1 PWT and 1 LPG

- 2 memory card controller

- 8x8 Keypad scanner with multiple key detection, support ADC serial interface Keypad

#### System CPU(XCUP)

- RDA RISC Core 32x32 bits

- 16/32 bit instruction set

- 4KB I-cache and 4KB D-cache

#### Base Band CPU (BCPU)

- RDA RISC Core32x32 bits

- 16/32 bit instruction set

- 1KB I-cache and 1KB D-cache

- GSM/GPRS Dedicated accelerators

- RF Interface (RF IF)

- DigRF interface for communication with the integrated transceiver

- EGPRS class 12

#### RF Transceiver

- Quad bands integrated transceiver

- Integrated RF transceiver, Saw-Less, only needs external PA.

- Digital low-IF receiver

- Direct modulation transmitter

- Frequency synthesizer

- Integrated VCO, loop filters, etc.

- Digital AFC

- DigRF interface between digital baseband and transceiver

- RF FEM control

#### Voice and Modem codec

- Supports HR, FR, EFR, AMR voice codec

- Integrated microphone bias:

- DTMF and Comfort Tone generator

- 4 samples In and Out Fifos

- I2S / DAI Interface

- Serial Input / Output at 8/16 ks/s

- Can be used for test purpose in DAI mode

- Audio Interface To ABB

- 13 bit RX Data from audio ADC

- 16 bit TX Data to stereo DAC

## **M**ULTI-MEDIA **F**EATURES

# Power Management FEATURES

#### LCD display

- Support LCD module interface with 8/16/24 bit parallel interface or SPI series interface

- Support RGB565/666/888 interface

- Typical image sizes: QCIF, QVGA, WQVGA, CIF,VGA,WVGA,FWVGA

- Support image size up to qHD

- 4-layers blending graphical engine capable of resizing and YUV2RGB conversion

- Support 2chip select

#### Image signal processor

- Support 8-bit parallel or 1/2/4-bit series interface

- Support CSI-2 interface, up to 1GHz

- Support up to 2Mpix sensor

#### Video

- Separate video processor

- Decodes up to 1080p 30fps

- Encodes up to 1080p 30fps for H.264 format

#### Graphics

- Separate graphic processor, Vivante's GC860

- support OpenGLES1.1/2.0

- support OpenVG1.4

- support DirectFB

- support GDI/DirecShow

- 30M Triangle/s, 250M Pixel/s

#### Audio

- 2 channels voice ADC, 8kHz, 13 bits/sample for headset and on-board microphone

- Voice DAC, 8kHz, 13 bits/sample for receiver

- High fidelity Stereo DAC, up to 48kHz, 16 bits per sample

- Stereo Audio speaker driver

- 1.5W differential output stereo amplifier for loudspeaker, Class K

- Stereo analog audio line input

#### Power Management

- Power On reset control

- Internal 32K OSC for standby/ shutoff/ sleep state

- Integrated Li-ion battery charger (from USB or AC charger)

- Integrated all internal voltages from VBAT

- Provide all LDOs for external components

- Integrated 4 DC-DC, 1 BOOST

- Integrated LCD backlight controller

- Integrated Touch screen controller

- Integrated RGB, keypad backlight controller

### 1. GENERAL DESCRIPTION

# A high performance, high integrated system-on-chip solution for low cost, low power GSM/GPRS/EDGE smartphone.

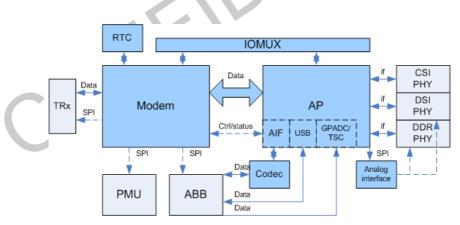

RDA8810P is a high performance, highly integrated system-on-chip solution for low cost, low power, GSM/GPRS/EDGE smartphone.

Integrating all essential electronic components, including AP MCU, GSM/GPRS/EDGE Module baseband, multimedia accelerators, quad band RF transceiver, saw-less, power management, audio amplifier onto a single system on chip, RDA8810P offers best in class bill of material, space requirement and cost/feature ratio for complete phone handsets.

RDA8810P Is capable of running the ARM cortex-A5 32-bit RISC processor at up to 1.2GHz, support NAND flash memory, 32-bit mobile DDR for optimal performance. An extensive set of interfaces and connectivity peripherals are included to interface to cameras, touch-screen displays, MMC/SD cards, and external Bluetooth, WiFi, FM, GPS modules.

Built around a cost effective 32-bit XCPU RISC core running at up to 312MHz with 4kB of Instruction cache and 4k of Data cache, A high performance proprietary 16/32-bit digital signal processing engine can further improve overall performance and user experience when performing complex multimedia tasks.

RDA8810P is GPRS Class 12 enabled, EDGE, and supports Full Rate (FR), Half Rate (HR), Enhanced Full Rate (EFR) and Adaptive Multi Rate (AMR) voice coders. It also integrates a SIM controller with integrated level shifters that can support three SIM cards. RDA8810P is available in a small footprint, fine pitch, 14X16, 325 ball LFBGA package.

Figure 1.1: System Block Diagram