|                                                                                |                                                                |                                                    |          |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                               |                       | F            | REVISI  | ONS              |              |                      |                        |                                         |                            |                                           |                                           |                                     |                 |   |

|--------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------|----------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------|--------------|---------|------------------|--------------|----------------------|------------------------|-----------------------------------------|----------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------|-----------------|---|

| LTR                                                                            |                                                                |                                                    |          |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DESCR                                         | IPTION                | ١            |         |                  |              |                      |                        | DATE (Y                                 | /R-MO-D                    | A)                                        |                                           | APPF                                | ROVED           |   |

| А                                                                              | Add                                                            | device                                             | types 0  | 5, 06,0               | 7, 08, a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | and 09.                                       | Editor                | ial cha      | nges th | nrougho          | out. –       | TVN                  | N 00-06-13             |                                         |                            | 13 Monica L. Poelking                     |                                           |                                     |                 |   |

| В                                                                              | Upda                                                           | ate boile                                          | erplate  | to MIL-               | PRF-38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8535 re                                       | quirem                | ents         | · CFS   |                  |              |                      |                        | 05-1                                    | 0-04                       |                                           | -                                         | Thomas                              | nas M. Hess     |   |

|                                                                                |                                                                |                                                    |          |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                               |                       |              |         |                  |              |                      |                        |                                         |                            |                                           |                                           |                                     |                 |   |

|                                                                                |                                                                |                                                    |          |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                               |                       |              |         |                  |              |                      |                        |                                         |                            |                                           |                                           |                                     |                 |   |

| DEV.                                                                           | 1                                                              |                                                    | <u> </u> | <u> </u>              | · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                               | <u> </u>              |              |         |                  |              |                      |                        |                                         | 1                          | 1                                         |                                           | 1                                   | ı               | Ī |

| REV                                                                            |                                                                |                                                    |          |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                               |                       |              |         |                  |              |                      |                        |                                         |                            |                                           |                                           |                                     |                 |   |

| SHEET                                                                          | В                                                              | В                                                  | В        | В                     | В                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | В                                             | В                     | В            | В       | В                | В            | В                    | В                      | В                                       | В                          | В                                         | В                                         | В                                   |                 |   |

| HEET<br>EV                                                                     | B 15                                                           | B 16                                               | B 17     | B 18                  | B 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | B 20                                          | B 21                  | B 22         | B 23    | B 24             | B 25         | B 26                 | B 27                   | B 28                                    | B 29                       | B 30                                      | B 31                                      | B 32                                |                 |   |

| SHEET REV SHEET REV STATUS                                                     | 15                                                             |                                                    |          |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                               |                       |              |         |                  |              |                      |                        |                                         |                            |                                           |                                           |                                     | В               |   |

| SHEET SHEET SHEET                                                              | 15                                                             |                                                    |          | 18                    | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                               | 21                    | 22           | 23      | 24               | 25           | 26                   | 27                     | 28                                      | 29                         | 30                                        | 31                                        | 32                                  | B 13            | - |

| SHEET REV SHEET REV STATUS OF SHEETS                                           | 15                                                             |                                                    |          | 18<br>REV<br>SHEE     | 19<br>ET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 20                                            | 21<br>B               | 22<br>B<br>2 | 23<br>B | 24<br>B          | 25<br>B<br>5 | 26<br>B<br>6         | 27<br>B<br>7           | 28<br>B<br>8                            | 29<br>B<br>9               | 30<br>B<br>10                             | 31<br>B<br>11                             | 32<br>B<br>12                       | 13              |   |

| SHEET REV SHEET REV STATUS OF SHEETS PMIC N/A                                  | 15                                                             | 16                                                 |          | 18<br>REV<br>SHEE     | 19 ET PARED TH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 20<br>BY<br>nanh V.                           | 21<br>B<br>1<br>Nguye | 22<br>B<br>2 | 23<br>B | 24<br>B          | 25<br>B<br>5 | 26<br>B<br>6         | B<br>7<br>SE SI        | 28<br>B<br>8<br>UPPL<br>IBUS,           | 29<br>B<br>9<br>Y CE, OHIO | 30<br>B<br>10                             | 31<br>B<br>11<br>R COL<br>218-39          | 32<br>B<br>12                       | 13              | - |

| SHEET REV SHEET REV STATUS DF SHEETS PMIC N/A STA                              | 15                                                             | 16  RD CUIT                                        | 17       | 18 REV SHEE           | 19 ET PARED TH CKED I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 20<br>BY<br>nanh V.<br>BY<br>homas            | 21<br>B<br>1<br>Nguye | B 2          | 23<br>B | 24<br>B<br>4     | 25<br>B<br>5 | 26<br>B<br>6<br>EFEN | 27 B 7 SE SI OLUM http | 28<br>B<br>8<br>UPPL<br>IBUS,           | 29<br>B<br>9<br>Y CE, OHIO | 30<br>B<br>10<br>NTER<br>O 432<br>scc.dla | 31<br>B<br>11<br>R COL<br>218-39<br>a.mil | 32<br>B<br>12<br>JUMB               | 13<br><b>US</b> | 1 |

| SHEET REV SHEET REV STATUS OF SHEETS PMIC N/A STAI MICRO DRA                   | NDAI<br>DCIR(                                                  | RD<br>CUIT<br>IG                                   | 17       | 18 REV SHEE PREF      | 19 ET PARED TH CKED I TI ROVED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 20<br>D BY<br>manh V.<br>BY<br>homas          | 21 B 1 Nguye M. Hes   | B 2 en ess   | 23<br>B | 24<br>B<br>4     | 25 B 5 DI    | 26 B 6 EFEN CC       | 27 B 7 SE SI OLUM http | 28<br>B<br>8<br>UPPL<br>IBUS,<br>o://ww | 29<br>B<br>9<br>Y CE, OHIO | 30<br>B<br>10<br>NTER<br>O 432            | 31<br>B<br>11<br>R COL<br>218-39<br>a.mil | 32<br>B<br>12<br>.UMB<br>990        | 13<br><b>US</b> | 1 |

| SHEET REV SHEET REV STATUS OF SHEETS PMIC N/A STAI MICRO DRA THIS DRAWII FOR U | NDAI<br>OCIRO<br>AWIN<br>NG IS A<br>ISE BY<br>RTMEN<br>NCIES O | RD<br>CUIT<br>IG<br>WAILAI<br>ALL<br>ITS<br>OF THE | 17       | 18 REV SHEE PREF CHEC | THE CKED IN THE CK | 20 D BY hanh V. BY homas D BY onlica L. APPRO | 21 B 1 Nguye M. Hes   | B 2 en ess   | 23<br>B | B 4 MIC MIC SIZE | 25 B 5 DI    | 26 B 6 EFEN CC       | 27 B 7 SE SI OLUM http | B<br>8<br>UPPL<br>IBUS,<br>o://ww       | 29<br>B<br>9<br>Y CE, OHIO | 30 B 10 NTER O 432 GCC.dla                | 31<br>B<br>11<br>R COL<br>218-39<br>a.mil | 32<br>B<br>12<br>UMB<br>990<br>RISC | 13<br><b>US</b> | 1 |

DSCC FORM 2233 APR 97

### 1. SCOPE

- 1.1 <u>Scope</u>. This drawing documents two product assurance class levels consisting of high reliability (device classes Q and M) and space application (device class V). A choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). When available, a choice of Radiation Hardness Assurance (RHA) levels are reflected in the PIN.

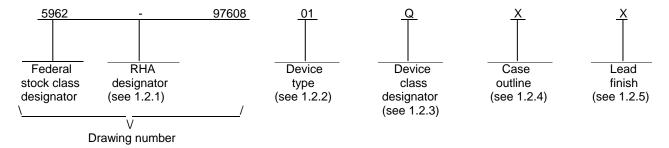

- 1.2 PIN. The PIN is as shown in the following example:

- 1.2.1 RHA designator. Device classes Q and V RHA marked devices meet the MIL-PRF-38535 specified RHA levels and are marked with the appropriate RHA designator. Device class M RHA marked devices meet the MIL-PRF-38535, appendix A specified RHA levels and are marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

- 1.2.2 <u>Device type(s)</u>. The device type(s) identify the circuit function as follows:

| Device type | Generic number | Circuit function           |

|-------------|----------------|----------------------------|

| 01          | PC603E-80      | 32-bit RISC microprocessor |

| 02          | PC603E-100     | 32-bit RISC microprocessor |

| 03          | PC603E-120     | 32-bit RISC microprocessor |

| 04          | PC603E-133     | 32-bit RISC microprocessor |

| 05          | PC603R-166     | 32-bit RISC microprocessor |

| 06          | PC603R-200     | 32-bit RISC microprocessor |

| 07          | PC603R-233     | 32-bit RISC microprocessor |

| 08          | PC603R-266     | 32-bit RISC microprocessor |

| 09          | PC603R-300     | 32-bit RISC microprocessor |

1.2.3 <u>Device class designator</u>. The device class designator is a single letter identifying the product assurance level as follows:

| Device class | <u>Device requirements documentation</u>                                                                                                                  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| М            | Vendor self-certification to the requirements for MIL-STD-883 compliant, non-JAN class level B microcircuits in accordance with MIL-PRF-38535, appendix A |

| Q or V       | Certification and qualification to MIL-PRF-38535                                                                                                          |

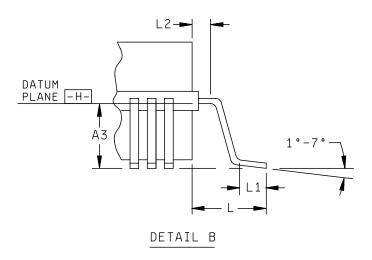

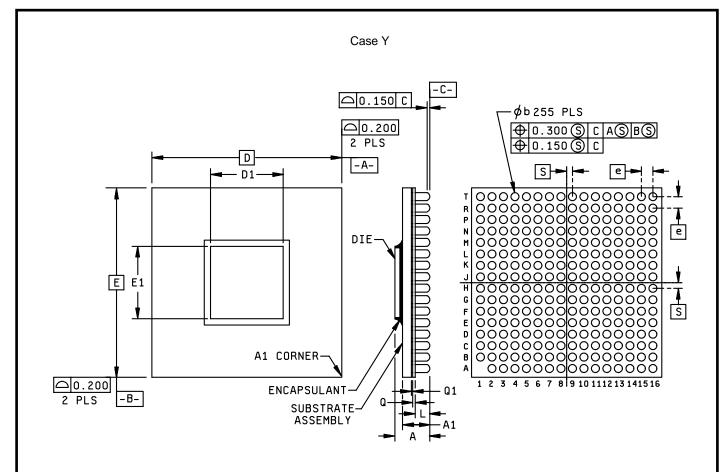

1.2.4 <u>Case outline(s)</u>. The case outline(s) are as designated in MIL-STD-1835 and as follows:

| Outline letter | Descriptive designator | <u>Terminals</u> | Package style               |

|----------------|------------------------|------------------|-----------------------------|

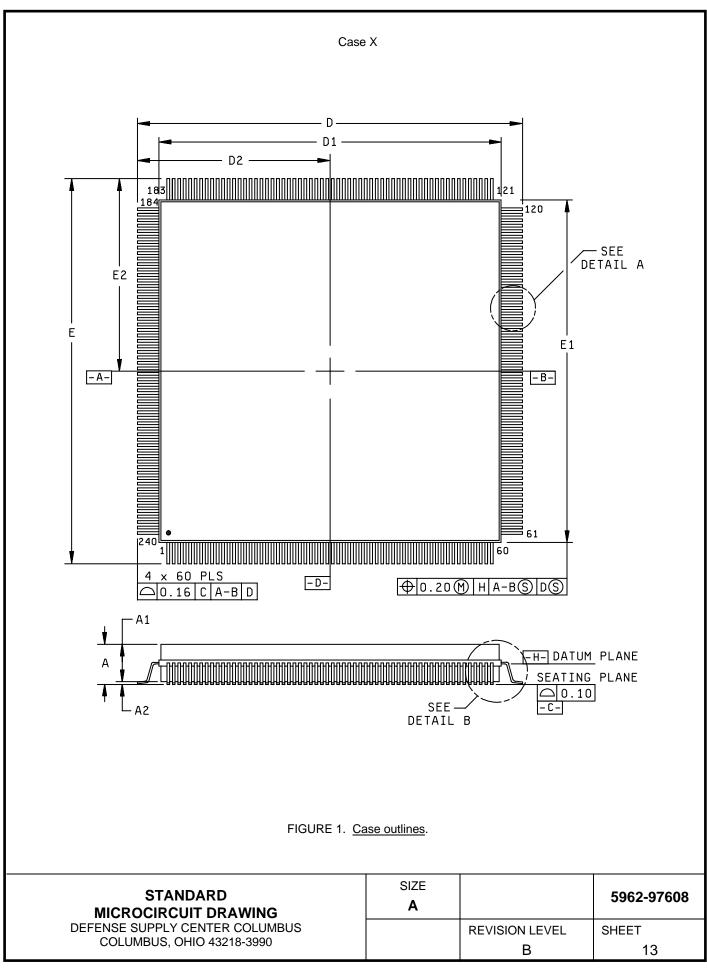

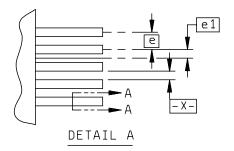

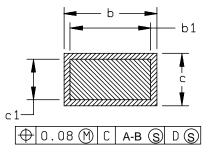

| X              | See figure 1           | 240              | Ceramic leaded chip carrier |

| Υ              | See figure 1           | 255              | Ceramic column grid array   |

1.2.5 <u>Lead finish</u>. The lead finish is as specified in MIL-PRF-38535 for device classes Q and V or MIL-PRF-38535, appendix A for device class M.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-97608 |

|-------------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>B | SHEET 2    |

# 1.3 Absolute maximum ratings. 1/ Core supply voltage range (V<sub>CC</sub>): Device types 01 - 04 ......-0.3 V dc to +4.0 V dc Device types 05 - 09 ......-0.3 V dc to +2.75 V dc I/O supply voltage range for device types 05 - 09 (OV<sub>CC</sub>)......-0.3 V dc to +3.6 V dc Maximum power dissipation at (P<sub>D</sub>): Device types 01 - 04 ...... 5.3 W Storage temperature range (T<sub>STG</sub>) ......-55°C to +150°C Lead temperature for device types 01 - 04 (soldering, 10 seconds)......+300°C Thermal resistance, junction-to-case ( $\Theta_{JC}$ ): Device types 05 - 09 ...... 0.1°C/W Thermal resistance, junction-to-column for device types 05 - 09 ( $\Theta_{JS}$ ) ...... 3.7°C/W 1.4 Recommended operating conditions. Core supply voltage range (V<sub>CC</sub>): PLL supply voltage range for device types 05 - 09 (AV<sub>CC</sub>)......+2.375 V dc to +2.625 V dc I/O supply voltage range for device types 05 - 09 (OV<sub>CC</sub>) ......+3.135 V dc to +3.465 V dc Logic high input voltage range (V<sub>IH</sub>): Frequency of operation ( $f_{OP}$ ): Device type 07 233 MHz Maximum operating junction temperature (T<sub>J</sub>): Device types 01 - 04 ......+137°C Device types 05 - 09 ......+126°C Minimum operating case temperature (T<sub>C</sub>) ......-55°C

1/ Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-97608 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |                  | B              | 3          |

#### 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standards, and handbooks</u>. The following specification, standards, and handbooks form a part of this drawing to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

#### DEPARTMENT OF DEFENSE SPECIFICATION

MIL-PRF-38535 - Integrated Circuits, Manufacturing, General Specification for.

### DEPARTMENT OF DEFENSE STANDARDS

MIL-STD-883 - Test Method Standard Microcircuits.

MIL-STD-1835 - Interface Standard Electronic Component Case Outlines.

### DEPARTMENT OF DEFENSE HANDBOOKS

MIL-HDBK-103 - List of Standard Microcircuit Drawings.

MIL-HDBK-780 - Standard Microcircuit Drawings.

(Copies of these documents are available online at <a href="http://assist.daps.dla.mil/quicksearch/">http://assist.daps.dla.mil/quicksearch/</a> or <a href="http://assist.daps.dla.mil/quicksearch/">http://assist.daps.dla.mil/quicksearch/</a> or <a href="http://assist.daps.dla.mil">http://assist.daps.dla.mil</a> or from the Standardization Document Order Desk, 700 Robbins Avenue, Building 4D, Philadelphia, PA 19111-5094.)

2.2 <u>Non-Government publications</u>. The following document(s) form a part of this document to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation.

### INSTITUTE OF ELECTRICAL AND ELECTRONICS ENGINEERS (IEEE)

IEEE Standard 1149.1 - IEEE Standard Test Access Port and Boundary Scan Architecture.

(Copies of these documents are available from the Institute of Electrical and Electronics Engineers, 445 Hoes Lane, Piscataway, NJ 08854-4150.)

2.3 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

### 3. REQUIREMENTS

3.1 <u>Item requirements</u>. The individual item requirements for device classes Q and V shall be in accordance with MIL-PRF-38535 and as specified herein or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein. The individual item requirements for device class M shall be in accordance with MIL-PRF-38535, appendix A for non-JAN class level B devices and as specified herein.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-97608 |

|-------------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>B | SHEET 4    |

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38535 and herein for device classes Q and V or MIL-PRF-38535, appendix A and herein for device class M.

- 3.2.1 Case outlines. The case outlines shall be in accordance with 1.2.4 herein and figure 1.

- 3.2.2 Terminal connections. The terminal connections shall be as specified on figure 2.

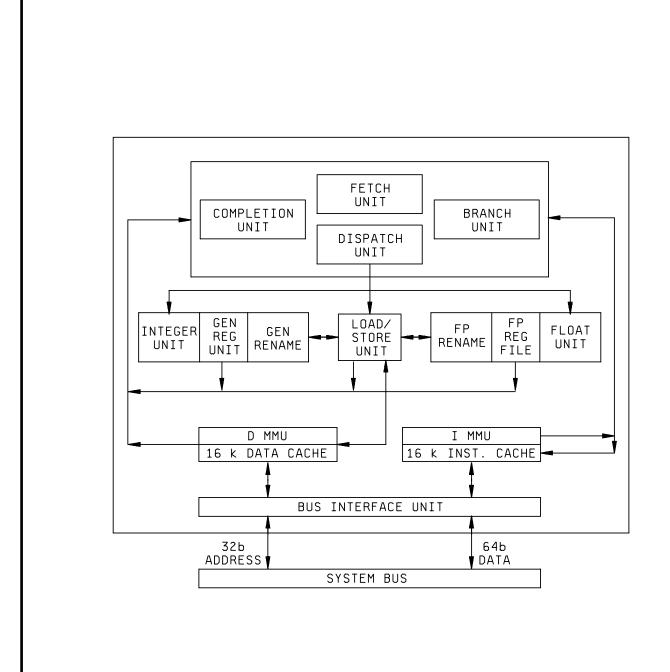

- 3.2.3 <u>Block diagram</u>. The block diagram shall be as specified on figure 3.

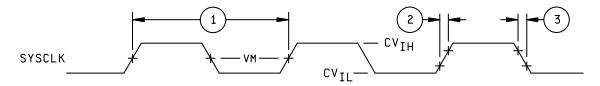

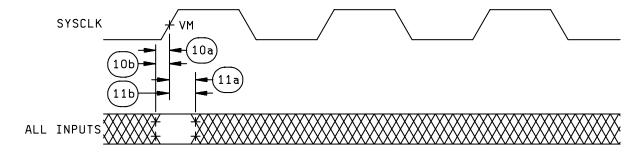

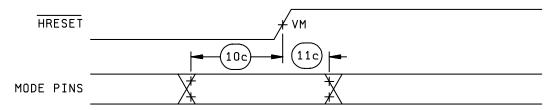

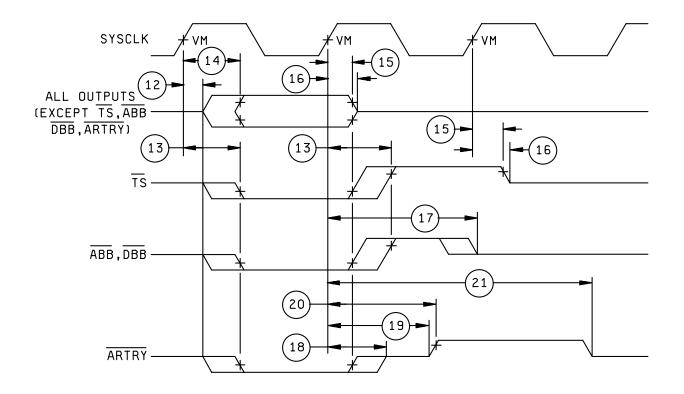

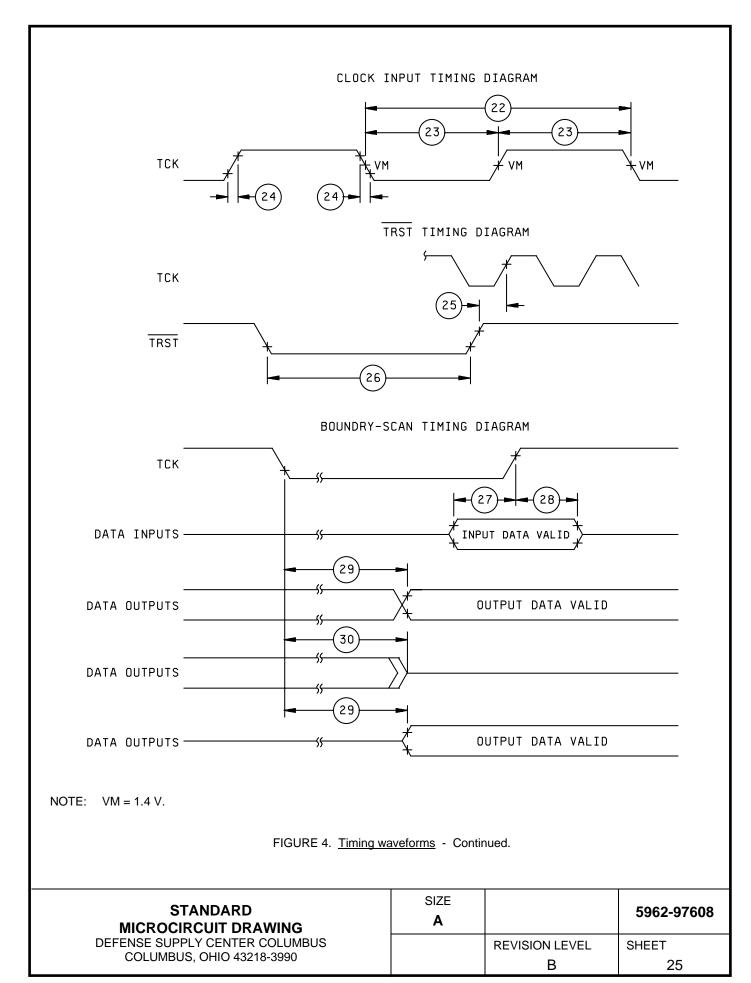

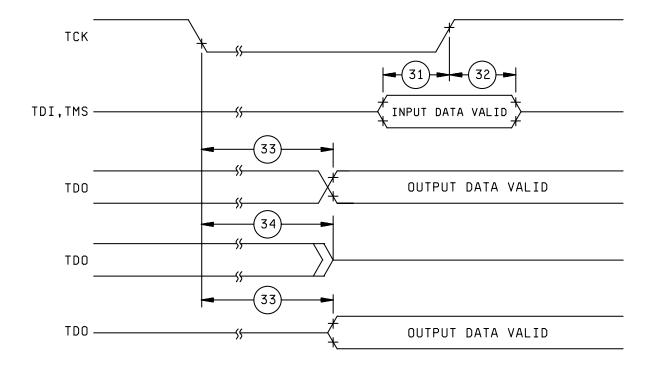

- 3.2.4 <u>Timing waveforms</u>. The timimg waveforms shall be as specified on figure 4.

- 3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table I and shall apply over the full case operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are defined in table I.

- 3.5 <u>Marking</u>. The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked. For packages where marking of the entire SMD PIN number is not feasible due to space limitations, the manufacturer has the option of not marking the "5962-" on the device. For RHA product using this option, the RHA designator shall still be marked. Marking for device classes Q and V shall be in accordance with MIL-PRF-38535. Marking for device class M shall be in accordance with MIL-PRF-38535, appendix A.

- 3.5.1 <u>Certification/compliance mark</u>. The certification mark for device classes Q and V shall be a "QML" or "Q" as required in MIL-PRF-38535. The compliance mark for device class M shall be a "C" as required in MIL-PRF-38535, appendix A.

- 3.6 <u>Certificate of compliance</u>. For device classes Q and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.6.1 herein). For device class M, a certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-HDBK-103 (see 6.6.2 herein). The certificate of compliance submitted to DSCC-VA prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device classes Q and V, the requirements of MIL-PRF-38535 and herein or for device class M, the requirements of MIL-PRF-38535, appendix A and herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required for device classes Q and V in MIL-PRF-38535 or for device class M in MIL-PRF-38535, appendix A shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 <u>Notification of change for device class M</u>. For device class M, notification to DSCC-VA of change of product (see 6.2 herein) involving devices acquired to this drawing is required for any change that affects this drawing.

- 3.9 <u>Verification and review for device class M.</u> For device class M, DSCC, DSCC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 3.10 <u>Microcircuit group assignment for device class M.</u> Device class M devices covered by this drawing shall be in microcircuit group number 105 (see MIL-PRF-38535, appendix A).

- 3.11 <u>IEEE 1149.1 compliance interface</u>. The boundary-scan interface of the device is a fully compliant implementation of the IEEE 1149.1 standard.

- 3.11.1 <u>Test access port</u>. The device has five dedicated JTAG signals which are described in the following table. The TDI and TDO scan ports are used to scan instructions as well as data into the various scan registers for JTAG operations. The scan operation is controlled by the test access port (TAP) controller which in turn is controlled by the TMS input sequence. The scan data is latched in at the rising edge of TCK.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-97608 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS. OHIO 43218-3990 |                  | REVISION LEVEL | SHEET      |

| COLUMBOS, OFIIO 43218-3990                                  |                  | В              | 5          |

### IEEE interface pin descriptions

| Signal name | Input/Output | Weak pullup<br>provided | IEEE 1149.1 function       |

|-------------|--------------|-------------------------|----------------------------|

| TDI         | Input        | Yes                     | Serial scan input signal   |

| TDO         | Output       | No                      | Serial scan output signal  |

| TMS         | Input        | Yes                     | TAP controller mode signal |

| TCK         | Input        | Yes                     | Scan clock                 |

| TRST        | Input        | Yes                     | TAP controller reset       |

TRST is a JTAG optional signal which is used to reset the TAP controller asynchronously. The TRST signal assures that the JTAG logic does not interfere with the normal operation of the chip, and can be asserted coincident with the HRESET.

- 3.11.2 <u>TAP controller</u>. The TAP (Tap Access Port) controller is a state machine that controls the JTAG scan protocol. The TAP controller implements 16 states specified by the IEEE 1149.1 specification. The TAP controller state machine is clocked by TCK and the state transitions are controlled by the TMS input.

- 3.11.3 <u>JTAG instructions</u>. The device supports the three required JTAG instructions: BYPASS, SAMPLE/PRELOAD, and EXTEST which are controlled by an 8-bit instruction register. These instructions are scanned in serially (LSB first) via the TDI pin. The table of the JTAG instructions for the device is given below.

#### JTAG instructions

| Instruction    | Encoding | Test data register accessed |  |

|----------------|----------|-----------------------------|--|

| BYPASS         | 11111111 | Bypass register             |  |

| SAMPLE/PRELOAD | 11000000 | Boundary-scan register      |  |

| EXTEST         | 00000000 | Boundary-scan register      |  |

<u>The BYPASS instruction</u>. The bypass register contains a single shift-register stage and is used to provide a minimum-length serial path between the TDI and the TDO pins of a component when no test operation of that component is required. This allows more rapid movement of test data to and from other components on a board that are required to perform test operations.

<u>The SAMPLE/PRELOAD instruction</u>. The mandatory SAMPLE/PRELOAD instruction allows a snapshot of the normal operation of the component to be taken and examined. It also allows data values to be loaded onto the latched parallel outputs of the boundary-scan shift register prior to selection of the other boundary-scan test instructions.

<u>The EXTEST instruction</u>. The mandatory EXTEST instruction allows testing of off-chip circuitry and board level interconnections. Data would typically be loaded onto the latched parallel outputs of boundary-scan shift-register stages using the SAMPLE/PRELOAD instruction prior to selection of the EXTEST instruction.

NOTE: Following use of the EXTEST instruction, the on-chip system logic may be in an indeterminate state that will persist until a system reset is applied. Therefore, the on-chip system logic may need to be reset on return to normal (i.e., nontest) operation.

|   | STANDARD                       |  |  |  |  |

|---|--------------------------------|--|--|--|--|

|   | MICROCIRCUIT DRAWING           |  |  |  |  |

| [ | DEFENSE SUPPLY CENTER COLUMBUS |  |  |  |  |

|   | COLUMBUS, OHIO 43218-3990      |  |  |  |  |

| SIZE<br><b>A</b> |                     | 5962-97608 |

|------------------|---------------------|------------|

|                  | REVISION LEVEL<br>B | SHEET<br>6 |

|                  |                     |            |

|                                                      |                  | TABLE I. Electrical performan                           | nce charact | teristics. |     |      |      |

|------------------------------------------------------|------------------|---------------------------------------------------------|-------------|------------|-----|------|------|

| Test                                                 | Symbol           |                                                         | Device      | Group A    | Lin | nits | Unit |

|                                                      |                  | $-55$ °C ≤ $T_C$ ≤ $+125$ °C unless otherwise specified | type        | Subgroups  | Min | Max  |      |

| Input high voltage (all Inputs except                | V <sub>IH</sub>  |                                                         | 01-04       | 1, 2, 3    | 2.4 | 5.5  | V    |

| SYSCLK)                                              |                  |                                                         | 05-09       |            | 2.0 | 5.5  |      |

| Input low voltage (all<br>Inputs except<br>SYSCLK)   | V <sub>IL</sub>  |                                                         | All         | 1, 2, 3    | 0.0 | 0.8  |      |

| SYSCLK input high voltage                            | CV <sub>IH</sub> |                                                         | All         | 1, 2, 3    | 2.4 | 5.5  | V    |

| SYSCLK input low voltage                             | CV <sub>IL</sub> |                                                         | All         | 1, 2, 3    | 0.0 | 0.4  |      |

| Output high voltage                                  | V <sub>OH</sub>  | I <sub>OH</sub> = -9 mA                                 | All         |            | 2.4 |      | V    |

| Output low voltage                                   | V <sub>OL</sub>  | I <sub>OL</sub> = 14 mA                                 | All         | 1, 2, 3    |     | 0.4  |      |

| Input leakage current                                | I <sub>IN</sub>  | V <sub>IN</sub> = 3.465 V                               | 01-04       | 1, 2, 3    |     | 10   | μА   |

| <u>2</u> /                                           |                  | V <sub>IN</sub> = 5.5 V                                 |             |            |     | 245  |      |

|                                                      |                  | V <sub>IN</sub> = 3.465 V                               | 05-09       | 1, 2, 3    |     | 30   |      |

|                                                      |                  | V <sub>IN</sub> = 5.5 V                                 |             |            |     | 300  |      |

| High-Z (off-state)                                   | I <sub>TSI</sub> | V <sub>IN</sub> = 3.465 V                               | 01-04       | 1, 2, 3    |     | 10   | μА   |

| leakage current <u>2</u> /                           |                  | V <sub>IN</sub> = 5.5 V                                 |             | 1, 2, 3    |     | 245  |      |

|                                                      |                  | V <sub>IN</sub> = 3.465 V                               | 05-09       | 1, 2, 3    |     | 30   |      |

|                                                      |                  | V <sub>IN</sub> = 5.5 V                                 |             |            |     | 300  |      |

| Input capacitance (excludes TS, ABB, DBB, and ARTRY) | C <sub>IN1</sub> | V <sub>IN</sub> = 0.0 V, f = 1 MHz<br>See 4.4.1c        | All         | 4          |     | 10.0 | pF   |

| Input capacitance (for TS, ABB, DBB, and ARTRY)      | C <sub>IN2</sub> | V <sub>IN</sub> = 0.0 V, f = 1 MHz<br>See 4.4.1c        | All         | 4          |     | 15.0 | pF   |

| Functional test                                      |                  | See 4.4.1b                                              | All         | 7, 8       |     |      |      |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-97608 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |                  | B              | 7          |

|                                     | TAB  | LE I. Electrical performance cha                           | racteristics | - Continued |       |       |      |

|-------------------------------------|------|------------------------------------------------------------|--------------|-------------|-------|-------|------|

| Test                                | Test | Test conditions 1/                                         | Device       | Group A     | Lim   | nits  | Unit |

|                                     | no.  | -55°C ≤ T <sub>C</sub> ≤ +125°C unless otherwise specified | type         | Subgroups   | Min   | Max   |      |

|                                     |      | Clock AC timing spec                                       | ifications   |             |       |       |      |

| Processor frequency                 |      | <u>3</u> /                                                 | 01           | 9, 10, 11   | 40    | 80    | MHz  |

|                                     |      |                                                            | 02           |             | 50    | 100   |      |

|                                     |      |                                                            | 03           |             | 60    | 120   |      |

|                                     |      |                                                            | 04           |             | 60    | 133.3 |      |

|                                     |      |                                                            | 05           |             | 150   | 166   |      |

|                                     |      |                                                            | 06           |             | 150   | 200   |      |

|                                     |      |                                                            | 07           |             | 180   | 233   |      |

|                                     |      |                                                            | 08           |             | 180   | 266   |      |

|                                     |      |                                                            | 09           |             | 180   | 300   |      |

| VCO frequency                       |      | <u>3</u> /                                                 | 01           | 9, 10, 11   | 80    | 200   | MHz  |

|                                     |      |                                                            | 02           |             | 100   | 200   |      |

|                                     |      |                                                            | 03           |             | 120   | 240   |      |

|                                     |      |                                                            | 04           |             | 133.3 | 266.6 |      |

|                                     |      |                                                            | 05           |             | 300   | 332   |      |

|                                     |      |                                                            | 06           |             | 300   | 400   |      |

|                                     |      |                                                            | 07           |             | 360   | 466   |      |

|                                     |      |                                                            | 08           |             | 360   | 532   |      |

|                                     |      |                                                            | 09           |             | 360   | 600   |      |

| SYSCLK (bus)                        |      |                                                            | 01-04        | 9, 10, 11   | 16.67 | 66.67 | MHz  |

| frequency                           |      |                                                            | 05           |             | 25    | 66.7  |      |

|                                     |      |                                                            | 06           |             | 33.3  | 66.7  |      |

|                                     |      |                                                            | 07-09        |             | 33.3  | 75    |      |

| SYSCLK cycle time                   | 1    |                                                            | 01-04        | 9, 10, 11   | 15.0  | 60    | ns   |

|                                     |      |                                                            | 05           |             | 15.0  | 30    |      |

|                                     |      |                                                            | 06-09        |             | 13.3  | 30    |      |

| SYSCLK rise and fall time           | 2, 3 | <u>4</u> /                                                 | All          | 9, 10, 11   |       | 2.0   | ns   |

| SYSCLK duty cycle measured at 1.4 V | 4    | <u>5</u> /                                                 | All          | 9, 10, 11   | 40.0  | 60.0  | %    |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-97608 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |                  | B              | 8          |

|                                                                                   |        | BLE I. Electrical performance cha                       |                    | - Continued. |                      |       |        |

|-----------------------------------------------------------------------------------|--------|---------------------------------------------------------|--------------------|--------------|----------------------|-------|--------|

| Test                                                                              | Test   | Test conditions 1/                                      | Device             | Group A      | Lim                  | its   | Unit   |

|                                                                                   | no.    | $-55$ °C ≤ $T_C$ ≤ $+125$ °C unless otherwise specified | Type               | Subgroups    | Min                  | Max   |        |

|                                                                                   |        | Clock AC timing specificatio                            | ns - Contir        | nued.        |                      |       |        |

| SYSCLK jitter                                                                     | 8      | <u>6</u> /                                              | All                | 9, 10, 11    |                      | ±150  | ps     |

| Device internal PLL relock time                                                   | 9      | <u>5</u> / <u>7</u> /                                   | All                | 9, 10, 11    |                      | 100   | μS     |

|                                                                                   |        | Input AC timing specific                                | cations <u>8</u> / |              |                      |       |        |

| Address/data/transfer<br>attribute inputs valid<br>to SYSCLK (input               | 10a    | <u>9</u> /                                              | 01-04              | 9, 10, 11    | 4.0                  |       | ns     |

| setup)                                                                            |        |                                                         | 05-09              |              | 2.5                  |       |        |

| All other inputs valid                                                            | 10b    | <u>10</u> /                                             | 01-04              | 9, 10, 11    | 5.0                  |       | ns     |

| to SYSCLK (input setup)                                                           |        |                                                         | 05, 06             |              | 4.0                  |       |        |

|                                                                                   |        |                                                         | 07-09              |              | 3.5                  |       |        |

| Mode select inputs valid to HRESET (input setup) (for DRTRY, QACK, and TLBISYNC)  | 10c    | <u>11</u> / <u>12</u> / <u>13</u> / <u>14</u> /         | All                | 9, 10, 11    | 8 x t <sub>SYS</sub> |       | ns     |

| SYSCLK to address/<br>data/transfer<br>attribute inputs<br>invalid (input hold)   | 11a    | 9/                                                      | All                | 9, 10, 11    | 1.0                  |       | ns     |

| SYSCLK to all other inputs invalid (input hold)                                   | 11b    | <u>10</u> /                                             | All                | 9, 10, 11    | 1.0                  |       | ns     |

| HRESET to mode select inputs invalid (input hold) (for DRTRY, QACK, and TLBISYNC) | 11c    | <u>11</u> / <u>13</u> / <u>14</u> /                     | All                | 9, 10, 11    | 0.0                  |       | ns     |

|                                                                                   |        | Output AC timing specifica                              | tions 15/          | 16/          |                      |       |        |

| SYSCLK to output<br>driven (output enable<br>time)                                | 12     | C <sub>L</sub> = 50 pF                                  | All                | 9, 10, 11    | 1.0                  |       | ns     |

| SYSCLK to output valid (5.5 V to 0.8 V -                                          | 13a    | C <sub>L</sub> = 50 pF <u>17</u> /                      | 01-04              | 9, 10, 11    |                      | 11.0  | ns     |

| TS, ABB, ARTRY, DBB)                                                              |        |                                                         | 05-09              |              |                      | 9.0   |        |

| See footnotes at end of ta                                                        | ble.   |                                                         |                    |              |                      |       |        |

|                                                                                   | TANDAF |                                                         | SIZE<br><b>A</b>   |              |                      | 5962- | -97608 |

| MICROCIRCUIT DRAWING DEFENSE SUPPLY CENTER COLUMBUS COLUMBUS, OHIO 43218-3990     |        | ER COLUMBUS                                             |                    | REVISION     | I LEVEL<br>B         | SHEET | 9      |

|                                          | TA       | BLE I. Electrical performance cha                          | <u>aracteristics</u> | ¿ - Continued.            |                               |      |                  |

|------------------------------------------|----------|------------------------------------------------------------|----------------------|---------------------------|-------------------------------|------|------------------|

| Test                                     | Test     | Test conditions 1/                                         | Device               | Group A                   | Lim                           | nits | Unit             |

|                                          | no.      | -55°C ≤ T <sub>C</sub> ≤ +125°C unless otherwise specified | type                 | Subgroups -               | Min                           | Max  | ļ                |