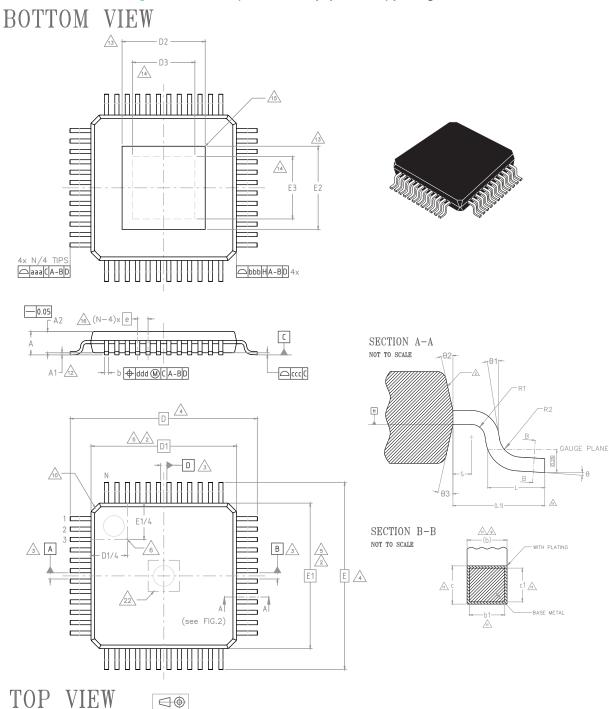

# Automotive 3-Phase motor gate driver unit

## TQFP48 (exposed pad down)

## **Features**

- Full ISO26262 compliant, ASIL-D systems ready

- VDH motor supply voltage range from 4.5 V to 75 V for working in single (12 V systems), double (24 V systems) and 48 V battery applications

- 3.3 V internal supply voltage generated from 5 V on VDD pin

- Digital I/O compatible to 3.3 V/5 V logics

- 6 separate N-channel FET pre-drivers:

- dedicated source connection to each FET

- the device can withstand -14 V to 95 V on motor connection pins

- 0% to 100% duty cycle operation support

- dedicated PWM input pin for each gate driver

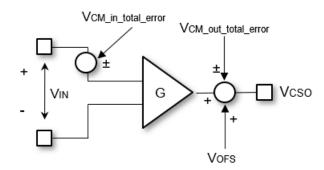

- 3 differential high accuracy current monitors for ground referred current measurements:

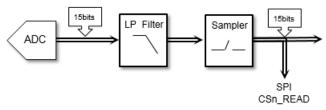

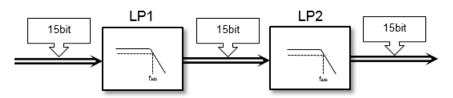

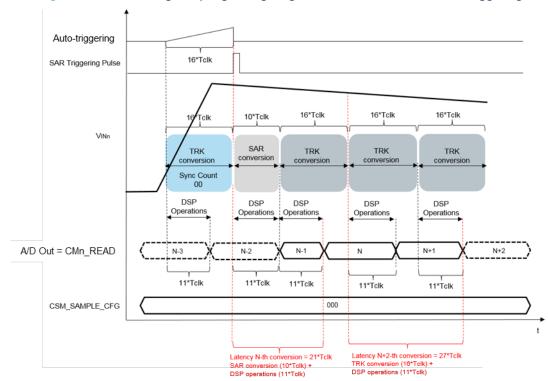

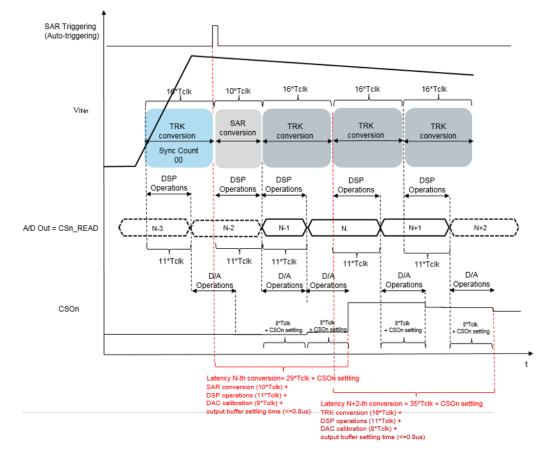

- ADC/DAC architecture

- SPI adjustable Gain Factor and Output Offset

- built-in error calibration

- the device can withstand -14 V to 6 V on input sensing pins

- SPI readable current measurement

- 0 to 4.6 V DAC output dynamic range

- 3 real time phase voltage monitor channels:

- SPI programmable phase voltage feedback;

- SPI readable phase duty cycle measurement;

- 32-bit 10 MHz SPI interface with 5-bit CRC and 1bit frame counter for internal setting, self-test and full diagnostics

- Protection and diagnostic:

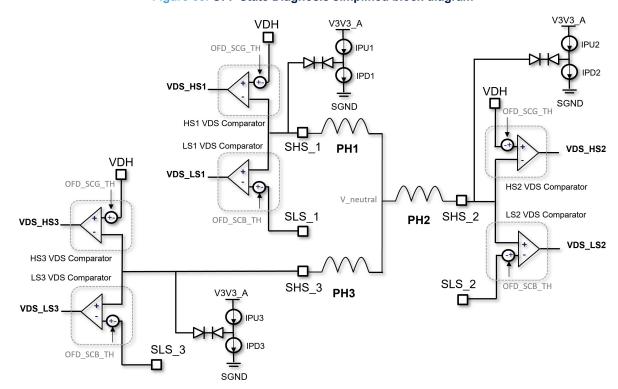

- SPI programmable VDS diagnostic and protection in on-state

- SPI programmable Dead Time protection

- SPI programmable Shoot-through diagnostic and protection

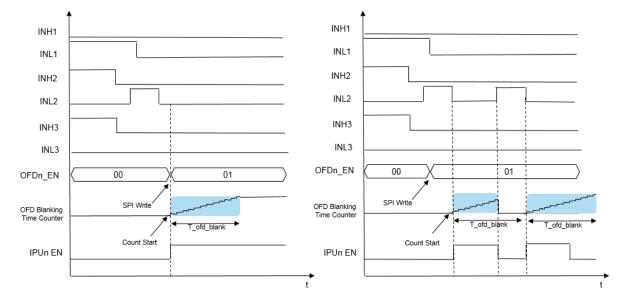

- Open load, short to GND and short to battery diagnostic in off-state

- Over-temperature diagnostic and protection with SPI programmable warning flag

- SPI readable Tj measurement

- Ground loss diagnostic

- System clock monitoring

- Power supply pins VDD, VDH, VBP over-voltage and under-voltage diagnostic

- FET driver supply VPRE and VCP under-voltage and over-voltage diagnostic

- SPI Window Watchdog

- Fault status flag output

# Product status link L9908

| Product summary |              |           |  |  |  |  |  |

|-----------------|--------------|-----------|--|--|--|--|--|

| Order<br>code   | Package      | Packing   |  |  |  |  |  |

| L9908           | TQFP48 (exp. | Tray      |  |  |  |  |  |

| L9908-TR        | pad down)    | Tape&Reel |  |  |  |  |  |

## **Application**

- · EPS Electronic Power Steering

- HVAC Blowers Heating, ventilation, and air conditioning

- · Engine Cooling Fans

- · Electronic Brake Booster

- EWP, EFP, EOP

## **Description**

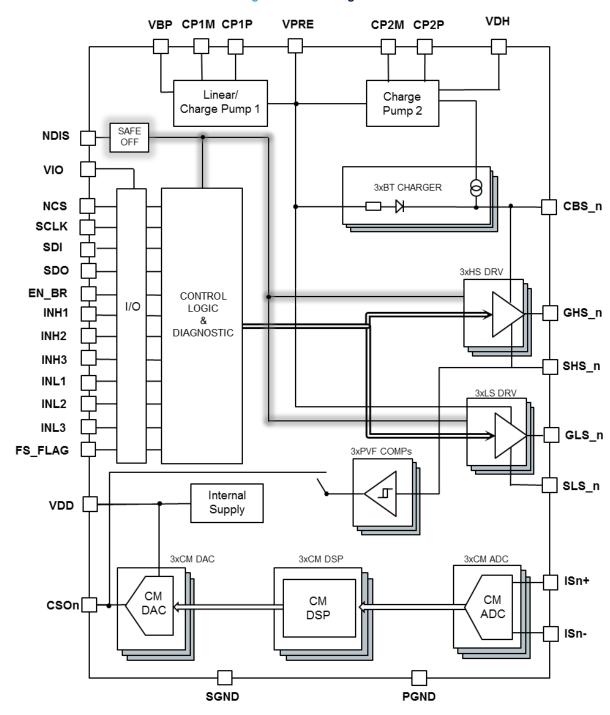

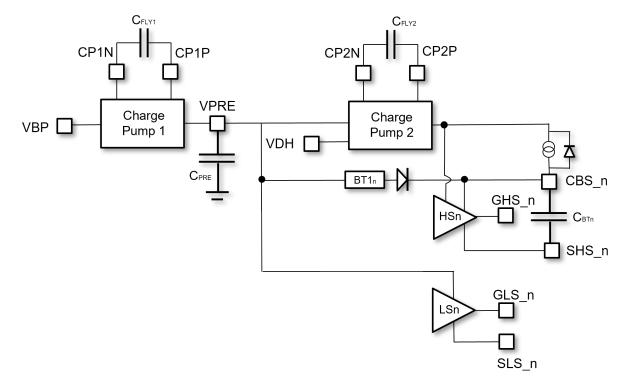

L9908 is a gate driver unit (GDU) for controlling 6 N-channel FETs for brushless motors in automotive applications.

Each one of the 3 half bridge drivers channels (HS/LS couples) can be independently configured allowing different load driving and is able to withstand -14 V to 95 V excursion on motor`s pins.

Through 6 dedicated parallel inputs the pre-driver stages can be controlled independently supporting duty cycle operations from 0% to 100% and allowing to implement all kinds of electric motor control strategy. A dedicated combination of regulators, charge pumps and bootstrap circuits allows L9908 to be suitable to operate in passenger, commercial or hybrid vehicles.

Safe operation of half bridges is ensured by shoot-through diagnosis, dead-time, short to battery, short to ground and open load detection plus a real time phase voltage monitoring.

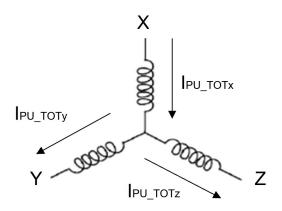

L9908 is equipped with 3 independent high accuracy current monitor channels with SPI-configurable input differential voltage ranges for ground referenced current measurements, with 5 V/3.3 V output dynamic range compatibility.

L9908 implements diagnostics on external and internal supply, ground level, internal temperature.

A 32-bit out of frame SPI-slave interface is implemented for communication up to 10 MHz between L9908 and uC. SPI communication is safe-guarded by 5-bit CRC, 1bit frame counter, frame length check and an SPI-configurable Window Watchdog.

DS13546 - Rev 3 page 2/153

# 1 Block diagram and pin description

Figure 1. Block diagram

FS\_FLAG NH3 N INL2 NL3 VPRE VBP 42 41 39 40 1 NCS CP2M 2 SCLK 35 CP2P 3 34 SDI VDH SDO 4 33 SHS\_1 VIO 5 32 GHS\_1 6 31 CSO3/PVF CBS\_1 7 30 CSO2 SHS\_2 8 29 CSO1 GHS\_2 9 28 VDD CBS\_2 10 27 SGND SHS\_3 11 26 EN\_BR GHS\_3 12 NDIS 25 CBS\_3 15 16 17 18 19 20 21 22 23 24 SLS\_3 SLS\_2 GIS\_1 SLS\_1 S1+ 53 8 52 <u>8</u>2 S1-

Figure 2. Pin connection diagram (top view)

Legenda: I = Input, O = Output, P = Power Supply, G = Ground, I/O = Input/Output

Table 1. Pin list description

| Pin# | Pin name | Description                                                                         | Pin type | Class |

|------|----------|-------------------------------------------------------------------------------------|----------|-------|

| 1    | NCS      | SPI Chip Select Input (Active LOW)                                                  | I        | Local |

| 2    | SCLK     | SPI Serial Clock Input                                                              | I        | Local |

| 3    | SDI      | SPI Serial Data Input                                                               | I        | Local |

| 4    | SDO      | SPI Serial Data Output                                                              | 0        | Local |

| 5    | VIO      | Power supply for digital output                                                     | Р        | Local |

| 6    | CSO3/PVM | Current monitor 3 analog output. Phase voltage feedback output                      | 0        | Local |

| 7    | CSO2     | Current monitor 2 analog output                                                     | 0        | Local |

| 8    | CSO1     | Current monitor 1 analog output                                                     | 0        | Local |

| 9    | VDD      | Power supply input for internal circuitry and current monitors analog output (CSOn) | Р        | Local |

| 10   | SGND     | Signal Ground (Analog, Digital, Reference)                                          | G        | Local |

| 11   | EN_BR    | Bridge Enable Input (Active HIGH)                                                   | l        | Local |

DS13546 - Rev 3 page 4/153

| Pin # | Pin name | Description                                                         | Pin type | Class  |

|-------|----------|---------------------------------------------------------------------|----------|--------|

| 12    | NDIS     | Safe switch-off activation Input (Active LOW)                       | I        | Local  |

| 13    | IS3-     | Current monitor 3 negative input                                    | I        | Local  |

| 14    | IS3+     | Current monitor 3 positive input                                    | I        | Local  |

| 15    | IS2-     | Current monitor 2 negative input                                    | I        | Local  |

| 16    | IS2+     | Current monitor 2 positive input                                    | 1        | Local  |

| 17    | IS1-     | Current monitor 1 negative input                                    | I        | Local  |

| 18    | IS1+     | Current monitor 1 positive input                                    | I        | Local  |

| 19    | SLS_3    | Source connection of LS FET, phase 3                                | I/O      | Local  |

| 20    | GLS_3    | Gate connection of LS FET, phase 3                                  | I/O      | Local  |

| 21    | SLS_2    | Source connection of LS FET, phase 2                                | I/O      | Local  |

| 22    | GLS_2    | Gate connection of LS FET, phase 2                                  | I/O      | Local  |

| 23    | SLS_1    | Source connection of LS FET, phase 1                                | I/O      | Local  |

| 24    | GLS_1    | Gate connection of LS FET, phase 1                                  | I/O      | Local  |

| 25    | CBS_3    | Bootstrap capacitor of HS, phase 3                                  | I/O      | Local  |

| 26    | GHS_3    | Gate connection of HS FET, phase 3                                  | I/O      | Local  |

| 27    | SHS_3    | Source connection of HS FET, phase 3                                | I/O      | Global |

| 28    | CBS_2    | Bootstrap capacitor of HS, phase 2                                  | I/O      | Local  |

| 29    | GHS_2    | Gate connection of HS FET, phase 2                                  | I/O      | Local  |

| 30    | SHS_2    | Source connection of HS FET, phase 2                                | I/O      | Global |

| 31    | CBS_1    | Bootstrap capacitor of HS, phase 1                                  | I/O      | Local  |

| 32    | GHS_1    | Gate connection of HS FET, phase 1                                  | I/O      | Local  |

| 33    | SHS_1    | Source connection of HS FET, phase 1                                | I/O      | Global |

| 34    | VDH      | Drain connection of HS FETs                                         | Р        | Global |

| 35    | CP2P     | Charge Pump 2 positive input of fly capacitance                     | I/O      | Local  |

| 36    | CP2M     | Charge Pump 2 negative input of fly capacitance                     | I/O      | Local  |

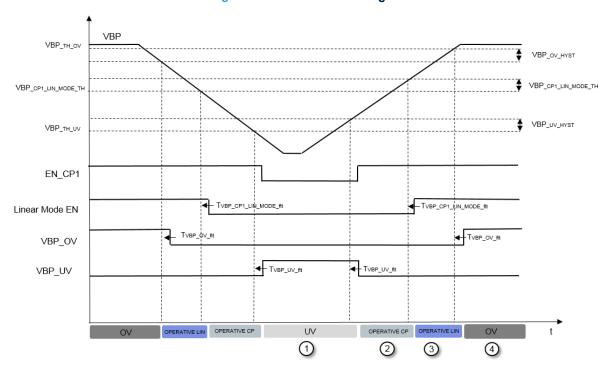

| 37    | VBP      | Pre-regulation stage power supply                                   | Р        | Global |

| 38    | CP1M     | Charge Pump 1 negative input of fly capacitance                     | I/O      | Local  |

| 39    | PGND     | Power Ground (Charge Pump 1 and 2)                                  | G        | Local  |

| 40    | CP1P     | Charge Pump 1 positive input of fly capacitance                     | I/O      | Local  |

| 41    | VPRE     | Pre-regulated voltage for HS/LS Vgs driving                         | I/O      | Local  |

| 42    | INH3     | PWM command for HS, phase 3 (Active HIGH)                           | I        | Local  |

| 43    | INH2     | PWM command for HS, phase 2 (Active HIGH)                           | I        | Local  |

| 44    | INH1     | PWM command for HS, phase 1 (Active HIGH)                           | I        | Local  |

| 45    | INL3     | PWM command for LS, phase 3 (Active HIGH)                           | I        | Local  |

| 46    | INL2     | PWM command for LS, phase 2 (Active HIGH)                           | I        | Local  |

| 47    | INL1     | PWM command for LS, phase 1 (Active HIGH)                           | I        | Local  |

| 48    | FS_FLAG  | Fault status flag output (Active LOW)                               | 0        | Local  |

|       | Exp. PAD | Cooling pad not electrically connected. Connect to GND plane on PCB |          |        |

Safety Related pin NDIS and EN\_BR have the following characteristics:

# Table 2. Safety related digital input pins functional partitioning

|   | Pins  | Default State                          | Description                             |  |  |  |  |  |

|---|-------|----------------------------------------|-----------------------------------------|--|--|--|--|--|

|   | NDIS  | Type B – Internal Resistance Pull-down | SPI Pin (SPI communication related pin) |  |  |  |  |  |

| Е | EN_BR | Type B – Internal Resistance Pull-down | SPI Pin (SPI communication related pin) |  |  |  |  |  |

Table 3. NDIS and EN\_BR electrical characteristics

| Symbol        | Parameter               | Test Condition | Min  | Тур | Max | Unit | Notes          |

|---------------|-------------------------|----------------|------|-----|-----|------|----------------|

| NDIS_II_th    | NDIS Input Low Level    |                | -0.3 | -   | 0.8 | V    | -              |

| NDIS_hI_th    | NDIS Input High Level   |                | 2    | -   | 65  | V    | -              |

| T_ndis_flt    | NDIS filtering time     |                | 1    | 2.5 | 5   | μs   | Analog filter  |

| NDIS_in_ipd   | NDIS Pull Down Current  | NDIS = VIO     | -65  | -40 | -15 | μA   | -              |

| EN_BR_II_th   | EN_BR Input Low Level   |                | -0.3 | -   | 0.8 | V    | -              |

| EN_BR _hl_th  | EN_BR Input High Level  |                | 2    | -   | 65  | V    | -              |

| T_en_br_flt   | EN_BR filtering time    |                | 1    | 2.5 | 5   | μs   | Digital filter |

| EN_BR _in_ipd | EN_BR Pull Down Current | EN_BR = VIO    | -65  | -40 | -15 | μA   | -              |

The state of Safety control pins EN\_BR and NDIS is echoed into dedicated SPI readable bits **EN\_BR\_ECHO** and **NDIS\_ECHO** in the register **GEN\_STATUS2**.

DS13546 - Rev 3 page 6/153

# 2 Absolute maximum ratings

In the following section the voltage ranges of each pin are described by dividing them into three categories: Functional Operating Range, Parametrical Operating Range and Absolute maximum rating.

Functional Functional Parametrical Permanent Permanent Critical UV Critical ov Operating Operating Operating Damage Damage Range Range Range Maximum Operating Range Absolute Maximum Rating

Figure 3. Pin voltage ranges

# 2.1 Maximum Operating Range (MOR)

### 2.1.1 Functional Operating Range

Within these operating ranges the part operates as specified in the circuit description, electrical characteristics are guaranteed only in the parametrical operating range, between these two ranges parametrical deviation may occur. The device may not operate properly if functional operating range conditions are exceeded. Once taken beyond the functional operative ratings and returned back within, the part will recover with no damage or degradation (provided that AMR range is not exceeded). All analog and digital voltages are related to the potential at signal ground SGND. All currents are assumed to be positive when current flows into the pin.

| Symbol          | Parameter                                                                              | Min           | Тур | Max     | Unit | Notes             |

|-----------------|----------------------------------------------------------------------------------------|---------------|-----|---------|------|-------------------|

|                 | Powe                                                                                   | er Supply     |     |         |      |                   |

| VBP_MOR         | VBP: voltage range                                                                     | VBP UV        | -   | VBP OV  | V    | Thermally limited |

| VBP_MOR_PU      | VBP: voltage range for power up                                                        | VBP UV + HYST | -   |         | V    | Power-Up          |

| VDH_MOR         | VDH: voltage range                                                                     | VDH UV        | -   | VDH OV  | V    | -                 |

| VDH_MOR_PU      | VDH: voltage range for power up                                                        | VDH UV + HYST | -   |         | V    | Power-Up          |

| VDD_MOR         | VDD: voltage range                                                                     | VDD UV        | -   | VDD OV  | V    | -                 |

| VDD_MOR_PU      | VDD: voltage range for power up                                                        | VDD UV + HYST | -   |         | V    | Power-Up          |

| VIO_MOR         | VIO: voltage range                                                                     | 2.5           | -   | 5.5     | V    | -                 |

|                 | Gate Dr                                                                                | iver Supply   |     |         |      |                   |

| d_CP1P_CP1M_MOR | CP1P - CP1M: Charge<br>Pump1 external<br>capacitance terminals<br>differential voltage | VPRE UV       | -   | VPRE OV | V    | -                 |

| VPRE_MOR        | VPRE: voltage range                                                                    | VPRE UV       | -   | VPRE OV | V    | -                 |

| d_CP2P_CP2M_MOR | CP2P – CP2M: Charge<br>Pump2 external<br>capacitance terminals<br>differential voltage | VPRE UV       | -   | VPRE OV | V    | -                 |

Table 4. Functional operating conditions

Downloaded from Arrow.com.

| Symbol                  | Parameter                                                            | Min                   | Тур | Max                   | Unit | Notes                                                         |

|-------------------------|----------------------------------------------------------------------|-----------------------|-----|-----------------------|------|---------------------------------------------------------------|

|                         | Gate                                                                 | Drivers               |     |                       |      |                                                               |

| d_CBSN_SHSN_MOR_BT1_MOR | CBS_n - SHS_n:<br>differential voltage<br>between CBS_n and<br>SHS_n | VPRE UV               | -   | VPRE OV               | V    | Charge<br>through BT<br>charge limiter<br>1 only<br>[n=1,2,3] |

| d_CBSN_SHSN_MOR_BT2_MOR | CBS_n - SHS_n:<br>differential voltage<br>between CBS_n and<br>SHS_n | BT_lim2_vlim<br>(MIN) | -   | BT_lim2_vlim<br>(MAX) | V    | Charge<br>through BT<br>charge limiter<br>2 only<br>[n=1,2,3] |

| d_GHSN_SHSN_MOR         | GHS_n - SHS_n:<br>differential voltage<br>between GHS_n and<br>SHS_n | 0                     | -   | CBS_n-SHS_n           | V    | [n=1,2,3]                                                     |

| SHSN_MOR                | SHS_n: voltage range                                                 | -12                   | -   | VDH +12               | V    | [n=1,2,3]                                                     |

| d_GLSN_SLSN_MOR         | GLS_n - SLS_n:<br>differential voltage<br>between GLS_n and<br>SLS_n | 0                     | -   | VPRE-SLS_n            | V    | [n=1,2,3]                                                     |

| d_SLSN_MOR              | SLS_n: voltage range                                                 | -12                   | -   | 2                     | V    | [n=1,2,3]                                                     |

|                         | Curren                                                               | t Monitors            |     |                       |      |                                                               |

| ISN_MOR                 | ISn+ – ISn-: differential voltage between ISn+ and IS-n              | -0.3                  | -   | 0.3                   | V    | [n=1,2,3]                                                     |

| ISN_MOR                 | ISn+/ISn-: common mode voltage range                                 | -2                    | -   | 2                     | V    | [n=1,2,3]                                                     |

| CSON_MOR                | CSOn: voltage range                                                  | 0                     | -   | VDD-0.4               | V    | [n=1,2,3]                                                     |

|                         | Dig                                                                  | jital I/O             |     |                       |      |                                                               |

| DO_MOR                  | SDO, PVM, FS_FLAG: voltage range                                     | 0                     | -   | VIO                   | V    | -                                                             |

| DI_MOR                  | NCS, SCLK, SDI,<br>EN_BR, NDIS, INHn,<br>INLn: voltage range         | 0                     | -   | VIO                   | V    | [n=1,2,3]                                                     |

Note:

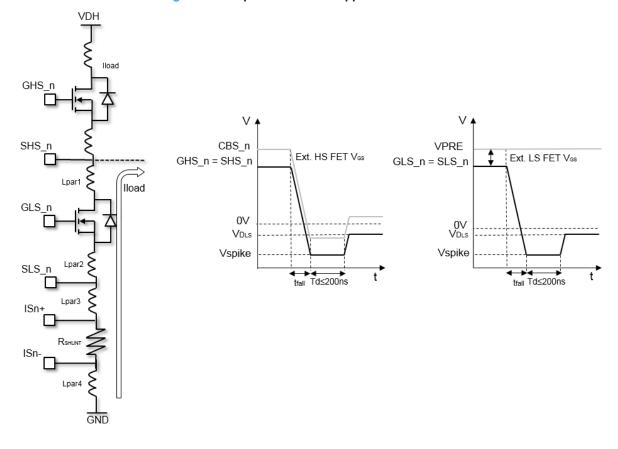

undershoot spikes at motor's phase (SHS\_n) take place when the high side is switched off and the load current must flow through the low-side freewheeling diode.

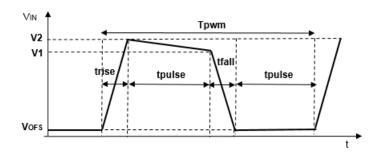

Figure 4. 14 V pulse scenario - applicative condition

The negative peak voltage reached during such a transition can be described by the following formula:

$$SHS_{n(peak)} = V_{d\_peak} + (L_{PAR\_TOT}) \frac{dI_{LOAD}}{t_{fall}} + (R_{shunt} + R_{PAR\_TOT}) I_{load}$$

$$SHS_{n(peak)} \approx (L_{PAR\_TOT}) \frac{dI_{LOAD}}{t_{fall}}$$

(2)

$$SHS_{n(peak)} \approx \left(L_{PAR\_TOT}\right) \frac{dI_{LOAD}}{t_{fall}}$$

(2)

The first term Vd peak is the transient peak voltage of the LS FET body diode, the second is due to transient response of the parasitic inductances between SHS\_n and GND while the third is related to path resistance drop. Given the maximum current conducted, the application shall limit the maximum undershoot peak voltage by minimizing the ratio:

$$\frac{L_{PAR\_TOT}}{t_{fall}} \tag{3}$$

(Ex: if Iload = 100 A then  $L_{PAR}$  TOT = 4 nH then  $t_{fall}$  must be kept higher than 33 ns)

The above-mentioned considerations also apply to SHS in positive pulse which takes place when the inverter is working in generator mode.

#### 2.1.2 **Parametrical Operating Range**

Within these operating ranges the part operates as specified and without parameter deviations. The device may show parameters deviation if parametrical operating conditions are exceeded.

Once taken beyond the operative ratings and returned back within, the part will recover with no damage or degradation (provided that AMR range is not exceeded). All analog and digital voltages are related to the potential at signal ground SGND. All currents are assumed to be positive when current flows into the pin.

DS13546 - Rev 3 page 9/153

Table 5. Parametrical operating conditions

| Symbol           | Parameter                                   | Test Condition            | Min  | Тур | Max  | Unit | Notes                    |

|------------------|---------------------------------------------|---------------------------|------|-----|------|------|--------------------------|

|                  | Powe                                        | er Supply                 |      |     |      |      |                          |

| VBP_MOR_PAR      | VBP: voltage range                          | -                         | 4.5  | -   | 36   | V    | -                        |

| VBP_MOR_PAR_EXT1 | VBP: extended voltage range 1               | t ≤ 15 min<br>Tamb = 25°C | 36   | -   | 48   | V    | Jump Start Pulse         |

| VBP_MOR_PAR_EXT2 | VBP: extended voltage range 2               | t ≤ 400 ms<br>Tamb = 25°C | 48   | -   | 60   | V    | Load Dump Pulse          |

| VDD_MOR_PAR_CSON | VDD: voltage range (CSOn related parameter) | -                         | 4.85 | 5   | 5.15 | V    | -                        |

| VDD_MOR_PAR      | VDD: voltage range                          | -                         | 4. 5 | 5   | 5.5  | V    | -                        |

| VIO_MOR_PAR      | VIO: voltage range                          | -                         | 2.5  | -   | 5.5  | V    | -                        |

| VPRE_MOR_PAR     | VPRE: voltage range                         | -                         | 7    | -   | 15   | V    | -                        |

| VDH_MOR_PAR      | VDH: voltage range                          | -                         | 4.5  | -   | 52   | V    | -                        |

| VDH_MOR_PAR_EXT1 | VDH: extended voltage range 1               | t ≤ 60 min<br>Tamb = 25°C | 52   | -   | 60   | V    | Long Term<br>Overvoltage |

| VDH_MOR_PAR_EXT2 | VDH: extended voltage range 2               | t ≤ 40 ms<br>Tamb = 25°C  | 60   | -   | 70   | V    | Transient Overvoltage    |

Note:

All parameters are guaranteed and tested, in the voltage ranges reported above in Table 5 unless otherwise specified. Where not specified the parametrical operating range equals the functional operating range.

# 2.2 Absolute Maximum Ratings (AMR)

Maximum ratings are absolute ratings; exceeding any one of these values may cause permanent damage to the integrated circuit. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. All analog and digital voltages are related to the potential at signal ground SGND. All currents are assumed to be positive when current flows into the pin.

Table 6. Absolute maximum ratings

| Symbol        | Parameter                                          | Test Condition               | Min  | Тур | Max               | Unit | Notes                          |  |  |

|---------------|----------------------------------------------------|------------------------------|------|-----|-------------------|------|--------------------------------|--|--|

|               | Power Supply                                       |                              |      |     |                   |      |                                |  |  |

| VBP_AMR_DC    | VBP: DC voltage range                              | -                            | -0.3 | -   | 65 <sup>(1)</sup> | V    | -                              |  |  |

| VBP_AMR_AC    | VBP: transient voltage range                       | t ≤ 400 ns;<br>IVBP ≤ 500 mA | -1   | -   | 65 <sup>(1)</sup> | V    | Not subject to production test |  |  |

| VDH_AMR_DC    | VDH: DC voltage range.                             |                              | -0.3 | -   | 75 <sup>(2)</sup> | V    |                                |  |  |

| VDH_AMR_AC    | VDH: transient voltage range.                      | t ≤ 400 ns;<br>IVDH ≤ 500 mA | -1   | -   | 90                | V    | Not subject to production test |  |  |

| d_VDH_VBP_AMR | VDH - VBP Differential voltage between VDH and VBP | -                            | -65  | -   | 75                | V    | -                              |  |  |

| VDD_AMR       | VDD: voltage range                                 | -                            | -0.3 | -   | 20                | V    | -                              |  |  |

| VIO_AMR       | VIO: voltage range                                 | -                            | -0.3 | -   | 20                | V    | -                              |  |  |

|               | Gate Dr                                            | iver Supply                  |      |     |                   |      |                                |  |  |

| CP1M_AMR      | CP1M: voltage range                                |                              | -0.3 | -   | 65                | V    | -                              |  |  |

DS13546 - Rev 3 page 10/153

| Symbol              | Parameter                                                                                | Test Condition                       | Min                      | Тур | Max    | Unit | Notes                                          |

|---------------------|------------------------------------------------------------------------------------------|--------------------------------------|--------------------------|-----|--------|------|------------------------------------------------|

| d_VBP_CP1M_AMR      | VBP - CP1M: Charge Pump1<br>external differential voltage<br>between VBP and CP1M        | -                                    | -0.3                     | -   | 65     | V    | -                                              |

| CP1P_AMR            | CP1P: voltage range                                                                      | -                                    | -0.3                     | -   | 20     | V    | -                                              |

| d_CP1P_CP1M_AMR     | CP1P - CP1M: Charge<br>Pump1 external capacitance<br>terminals differential voltage      | -                                    | -65                      | -   | 20     | V    | -                                              |

| d_VBP_CP1P_AMR      | VBP - CP1P: Charge Pump1<br>external differential voltage<br>between VBP and CP1P        | -                                    | -20                      | -   | 65     | V    | -                                              |

| d_VPRE_CP1P_AMR     | VPRE – CP1P: Charge<br>Pump1 external differential<br>voltage between VPRE and<br>CP1P   | -                                    | -0.3                     | -   | 20     | V    | -                                              |

| VPRE_AMR            | VPRE: voltage range                                                                      | -                                    | -0.3                     | -   | 20     | V    | -                                              |

| CP2M_AMR            | CP2M: voltage range                                                                      | -                                    | -0.3                     | -   | 75     | V    | -                                              |

| d_VPRE_CP2M_AMR     | VPRE – CP2M: Charge<br>Pump2 external differential<br>voltage between VPRE and<br>CP2M   | -                                    | -75                      | -   | 20     | V    | -                                              |

| CP2P_AMR            | CP2P: voltage range                                                                      | -                                    | -0.3                     | -   | 95     | V    | -                                              |

| d_CP2P_CP2M_AMR     | CP2P – CP2M: Charge<br>Pump2 external capacitance<br>terminals differential voltage      | -                                    | -20                      | -   | 75     | V    | -                                              |

| d_VPRE_CP2P_AMR     | VPRE – CP2P: Charge<br>Pump2 external differential<br>voltage between VPRE and<br>CP2P   | -                                    | -75                      | -   | 20     | V    | -                                              |

| d_VDH_CP2P_AMR      | VDH – CP2P: Charge Pump2<br>external differential voltage<br>between VDH and CP2P        | -                                    | -95                      | _   | 0.3    | V    | -                                              |

| d_VDH_VPRE_SHSN_AMR | VDH+VPRE-SHS_n:<br>constraint on simultaneous<br>voltage on VDH, VPRE and<br>SHS_n/GHS_n | -                                    | -                        | -   | 100(3) | V    | [n=1,2,3]<br>Application<br>information        |

|                     | Gate                                                                                     | Drivers                              |                          |     |        |      |                                                |

| CBS_AMR_DC_RES      | CBS_n: DC voltage range in RESET                                                         | VDD < VDD UV +<br>HYST               | -0.3                     | -   | 95     | V    | [n=1,2,3]                                      |

| CBS_AMR_DC          | CBS_n: DC voltage range                                                                  | VDD≥VDD UV +<br>HYST                 | <b>-7</b> <sup>(1)</sup> | -   | 95     | V    | [n=1,2,3]                                      |

| CBS_AMR_AC          | CBS_n: transient voltage range                                                           | VDD ≥ VDD UV +<br>HYST<br>t ≤ 200 ns | -14 <sup>(1)</sup>       | _   | 95     | V    | [n=1,2,3] Not<br>subject to<br>production test |

| d_CBSN_CP2P_AMR     | CBS_n - CP2P: differential voltage between CBS_n and CP2P terminals                      | -                                    | -95                      | -   | 20     | V    | [n=1,2,3]                                      |

| GHS_N_AMR_DC_RES    | GHS_n: DC voltage range in RESET                                                         | VDD < VDD UV +<br>HYST               | -0.3                     | -   | 95     | V    | [n=1,2,3]                                      |

| GHS_N_AMR_DC        | GHS_n: DC voltage range                                                                  | VDD ≥ VDD UV +<br>HYST               | -7                       | -   | 95     | V    | [n=1,2,3]                                      |

| GHS_N_AMR_AC        | GHS_n: transient voltage range                                                           | VDD ≥ VDD UV +<br>HYST<br>t ≤ 200 ns | -14                      | -   | 95     | V    | [n=1,2,3] Not<br>subject to<br>production test |

DS13546 - Rev 3 page 11/153

| Symbol             | Parameter                                                             | Test Condition                       | Min              | Тур | Max | Unit | Notes                                          |

|--------------------|-----------------------------------------------------------------------|--------------------------------------|------------------|-----|-----|------|------------------------------------------------|

| SHS_N_AMR_DC_RES   | SHS_n: DC voltage range in RESET                                      | VDD < VDD UV +<br>HYST               | -0.3             | -   | 95  | ٧    | [n=1,2,3]                                      |

| SHS_N_AMR_DC       | SHS_n: DC voltage range                                               | VDD ≥ VDD UV +<br>HYST               | -7               | -   | 75  | V    | [n=1,2,3]                                      |

| SHS_N_AMR_AC       | SHS_n: transient voltage range                                        | VDD ≥ VDD UV +<br>HYST<br>t ≤ 200 ns | -14              | -   | 95  | V    | [n=1,2,3] Not<br>subject to<br>production test |

| SHS_N_AMR_SR       | SHS_n: transient slew rate                                            | SR ≤ 1V/ns                           | -                | -   | 20  | V    | [n=1,2,3] Not<br>subject to<br>production test |

| d_CBSN_GHSN_AMR    | CBS_n - GHS_n: differential voltage between CBS_n and GHS_n terminals | -                                    | -0.3             | -   | 20  | V    | [n=1,2,3]                                      |

| d_CBSN_SHSN_AMR    | CBS_n - SHS_n: Differential voltage between CBS_n and SHS_n           | -                                    | -0.3             | -   | 20  | V    | [n=1,2,3]                                      |

| d_GHSN_SHSN_AMR_DC | GHS _n - SHS_n: Differential DC voltage between GHS_n and SHS_n       | -                                    | -0.3             | -   | 20  | V    | [n=1,2,3]                                      |

| d_GHSN_SHSN_AMR_AC | GHS_n - SHS_n: Differential transient voltage between GHS_n and SHS_n | t ≤ 200 ns; IGHS_n<br>≤ - 2A         | -2               | -   | 20  | V    | [n=1,2,3] Not<br>subject to<br>production test |

| d_VDH_SHSN_AMR_RES | VDH - SHS_n: Differential voltage between VDH and SHS_n in RESET      | VDD < VDD UV +<br>HYST               | -0.3             | -   | 95  | V    | -                                              |

| d_VDH_SHSN_AMR     | VDH - SHS_n: Differential voltage between VDH and SHS_n               | VDD ≥ VDD UV +<br>HYST               | -14              | -   | 95  | V    | [n=1,2,3]                                      |

| GLS_N_AMR_RES      | GLS_n: DC voltage range in RESET                                      | VDD < VDD UV +<br>HYST               | -0.3             | -   | 95  | V    | [n=1,2,3]                                      |

| GLS_N_AMR          | GLS_n: DC voltage range                                               | VDD ≥ VDD UV +<br>HYST               | -7               | -   | 20  | V    | [n=1,2,3]                                      |

| GLS_N_AMR_AC       | GLS_n: transient voltage range                                        | VDD ≥ VDD UV +<br>HYST<br>t ≤ 200 ns | -14              | -   | 20  | V    | [n=1,2,3] Not<br>subject to<br>production test |

| SLS_N_AMR_DC_RES   | SLS_n: DC voltage range in RESET                                      | VDD < VDD UV +<br>HYST               | -0.3             | -   | 95  | V    | [n=1,2,3]                                      |

| SLS_N_AMR_DC       | SLS_n: DC voltage range                                               | VDD ≥ VDD UV +<br>HYST               | -7               | -   | 20  | V    | [n=1,2,3]                                      |

| SLS_N_AMR_AC       | SLS_n: transient voltage range                                        | VDD ≥ VDD UV +<br>HYST<br>t ≤ 200 ns | -14              | -   | 20  | V    | [n=1,2,3] Not<br>subject to<br>production test |

| d_VPRE_GLSN_AMR    | VPRE - GLS_n: Differential voltage between VPRE and GLS_n             | -                                    | -0.3             | -   | 35  | V    | [n=1,2,3]                                      |

| d_VPRE_SLSN_AMR    | VPRE - SLS_n: Differential voltage between VPRE and SLS_n             | -                                    | -0.3             | -   | 35  | V    | [n=1,2,3]                                      |

| d_GLSN_SLSN_AMR_DC | GLS_n - SLS_n: Differential voltage between GLS_n and SLS_n           | -                                    | 0 <sup>(1)</sup> | -   | 20  | V    | [n=1,2,3]                                      |

DS13546 - Rev 3 page 12/153

| Symbol             | Parameter                                                                  | Test Condition                       | Min               | Тур | Max | Unit | Notes                                          |

|--------------------|----------------------------------------------------------------------------|--------------------------------------|-------------------|-----|-----|------|------------------------------------------------|

| d_GLSN_SLSN_AMR_AC | GLS_n - SLS_n: Differential voltage between GLS_n and SLS_n                | t ≤ 200 ns; IGLS_n<br>≤ - 2 A        | -2 <sup>(1)</sup> | -   | 20  | V    | [n=1,2,3] Not<br>subject to<br>production test |

|                    | Currer                                                                     | nt Monitors                          |                   |     |     |      |                                                |

| IS_AMR_DC_RES      | ISn+/ISn-: DC voltage range in RESET                                       | VDD < VDD UV +<br>HYST               | -0.3              | -   | 20  | V    | [n=1,2,3]                                      |

| IS_AMR_DC          | ISn+/ISn-: DC common mode voltage range                                    | VDD ≥ VDD UV +<br>HYST               | -7                | -   | 20  | V    | [n=1,2,3]                                      |

| IS_AMR_AC          | ISn+/ISn-: transient common mode voltage range                             | VDD ≥ VDD UV +<br>HYST<br>t ≤ 200 ns | -14               | -   | 20  | V    | [n=1,2,3] Not<br>subject to<br>production test |

| d_ISMPN_ISMN_AMR   | ISn+ - ISn-: Differential voltage between ISn+ and ISn-                    | -                                    | -5                | -   | 5   | V    | [n=1,2,3]                                      |

| d_VPRE_IS_AMR      | VPRE - ISn+/ISn: Differential voltage between VPRE and ISn+/ISn            | -                                    | 0                 | -   | 40  | V    | [n=1,2,3] Not<br>subject to<br>production test |

| IS_AMR_SR          | ISn+/ISn-: common mode transient slew rate                                 | SR ≤ 1V/ns                           | -                 | -   | 20  | V    | [n=1,2,3] Not<br>subject to<br>production test |

| CSON_AMR           | CSOn: voltage range                                                        | -                                    | -0.3              | -   | 20  | V    | [n=1,2,3]                                      |

| d_VIO_CSON_AMR     | VIO – CSOn: differential voltage between VIO supply and CSOn outputs       | -                                    | -0.3              | -   | 20  | V    | [n=1,2,3]                                      |

|                    | SPI                                                                        | Interface                            |                   |     |     |      |                                                |

| NCS_AMR            | NCS: voltage range                                                         | -                                    | -0.3              | -   | 20  | V    | -                                              |

| SCLK_AMR           | SCLK: voltage range                                                        | -                                    | -0.3              | -   | 20  | V    | -                                              |

| SDI_AMR            | SDI: voltage range                                                         | -                                    | -0.3              | -   | 20  | V    | -                                              |

| SDO_AMR            | SDO: voltage range                                                         | -                                    | -0.3              | -   | 20  | V    | -                                              |

|                    | Diç                                                                        | gital I/O                            |                   |     |     |      |                                                |

| d_VIO_SDO_AMR      | VIO – SDO: differential voltage between VIO supply and SDO outputs         | -                                    | -0.3              | -   | 20  | V    | -                                              |

| d_VIO_PVF_AMR      | VIO – PVF: differential voltage between VIO supply and PVF outputs         | -                                    | -20               | -   | 20  | V    | -                                              |

| d_VIO_FSFLAG_AMR   | VIO – FS_FLAG: differential voltage between VIO supply and FS_FLAG outputs | -                                    | -0.3              | -   | 20  | V    | -                                              |

| PVF_AMR            | PVF: voltage range                                                         | -                                    | -0.3              | -   | 20  | V    | -                                              |

| FS_FLAG            | FS_FLAG: voltage range                                                     | -                                    | -0.3              | -   | 20  | ٧    | -                                              |

| INHN_AMR           | INHn: voltage range                                                        | -                                    | -0.3              | -   | 20  | V    | [n=1,2,3]                                      |

| INLN_AMR           | INLn: voltage range                                                        | -                                    | -0.3              | -   | 20  | V    | [n=1,2,3]                                      |

| EN_BR _AMR         | EN_BR: voltage range                                                       | -                                    | -0.3              | -   | 65  | V    | -                                              |

| NDIS _AMR          | NDIS: voltage range                                                        | -                                    | -0.3              | -   | 65  | V    | -                                              |

|                    | Gı                                                                         | ounds                                |                   |     |     |      |                                                |

| GND_AMR            | SGND, PGND                                                                 | _                                    | -0.6              | _   | 0.6 | V    | -                                              |

<sup>1. 36</sup> V AMR over life-time. 48 V ≥ AMR ≥ 36 V for Jump Start transient pulse E-02 as defined in LV 124 standard and AMR ≥ 48 V for Load Dump Test B transient pulse as defined in ISO 16750-2 standard.

page 13/153

mA

100

- 2. 52 V AMR over life-time. 60 V ≥ AMR ≥ 52 V for E48-01a transient pulse, AMR ≥ 60 V for E48-02 transients pulse as defined in VDA\_320/LV 148 standard.

- 3. The maximum voltage drop experienced by internal structures has to be limited to 100V in order to avoid damages. The HS pre-driver stage may experience together the maximum voltage and the minimum voltage all over L9908 respectively imposed by CP2 output voltage or CBS\_n and SHS\_n negative pulses. HS pre-driver then must be protected by ensuring that the absolute maximum voltage on CP2 or on CBS\_n never takes place simultaneously with the absolute minimum voltage on SHS\_n so that: VDH \* VPRE SHS\_n ≤ 100 W

Note:

Integrated protection and diagnostics are designed to prevent device damage under the fault conditions defined in the functional description. Fault conditions are considered to be out of normal operating range. Protection functions are not designed for a continuous repetitive operation.

# 2.3 ESD resistivity

**Symbol Parameter Test Condition** Min Тур Max Unit **Notes** HBM\_LOC\_ESD HBM (Local Pins)(1) All pins(2) -2 \_ 2 kV Class 2 HBM\_GLO\_ESD VBP, VDH, SHS\_n Class 3A HBM (Global Pins)(1) -4 4 kV CDM\_ESD CDM (1) All pins -500 \_ 500 ٧ Class C3 CDM (1) CDM\_COR\_ESD -750 750 V Class C4 Corner pins

All pins

-100

Table 7. ESD resistivity (pin level)

1. According to AEC-Q100-011

LUT

2. Pins are all GND connected together.

Latch Up (3)

3. According to AEC-Q100-004

# 2.4 Temperature ranges and thermal data

Table 8. Temperature ranges and thermal data

| Symbol                             | Parameter                                  | Min | Тур | Max | Unit | Notes                                       |

|------------------------------------|--------------------------------------------|-----|-----|-----|------|---------------------------------------------|

| T <sub>amb</sub>                   | Operating temperature (ECU environment)    | -40 | -   | 150 | °C   | -                                           |

| T <sub>j</sub> <sup>(1)</sup>      | Operating junction temperature             | -40 | -   | 150 | °C   | -                                           |

| Tj                                 | Extended operating junction temperature    | -40 | -   | 175 | °C   | 200h over life time                         |

| T <sub>sto</sub>                   | Storage temperature                        | -55 | -   | 150 | °C   |                                             |

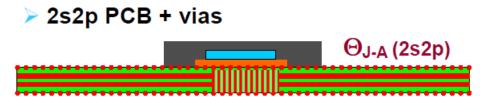

| R <sub>thJ-A</sub> <sup>(2)</sup>  | Thermal resistance junction-to-ambient     | -   | 31  | -   | °C/W | Homogeneous internal power distribution (3) |

| R <sub>Thj-cb</sub> <sup>(2)</sup> | Thermal resistance junction-to-case-bottom | -   | 2.1 | -   | °C/W | Homogeneous internal power distribution     |

- All parameters are guaranteed and tested, in the temperature range T<sub>j</sub>-40 ÷ 150°C unless otherwise specified. The

device is still operative and functional at higher temperatures (up to T<sub>j</sub> 175°C). Device functionality at high temperature is

guaranteed by bench validation, electrical parameters are guaranteed by correlation with ATE tests at reduced temperature

and adjusted limits (if needed).

- 2. Not subject to production test, guaranteed by design.

- 3.  $R_{thJA}$  value is retrieved according to Jedec JESD51-2,-5,-7 guideline with a 2s2p board.

DS13546 - Rev 3 page 14/153

Figure 5. 2s2p PCB with thermal vias

Note:

In "2s2p", the "s" suffix stands for "Signal" and the number before indicates how many PCB layers are dedicated to signal wires. The "p" suffix stands for "Power" and the number before indicates how many PCB layers are dedicated to power planes.

DS13546 - Rev 3 page 15/153

# 3 Current consumption

Table 9. Quiescent current consumption in reset mode

| Symbol  | Parameter                                   | Test Condition                                                                 | Min | Тур | Max | Unit |

|---------|---------------------------------------------|--------------------------------------------------------------------------------|-----|-----|-----|------|

| IQ_VBP1 | Quiescent consumption for VBP in reset mode | VBP = 14 V, -40° ≤ $T_j$ ≤ 25°C VDD = 0 V                                      | -   | 0.5 | 15  | μA   |

| IQ_VBP2 | Quiescent consumption for VBP in reset mode | VBP = 14 V, 25°C < $T_j \le 150$ °C<br>VDD = 0 V                               | -   | 1.3 | 15  | μA   |

| IQ_VBP3 | Quiescent consumption for VBP in reset mode | VBP = 60 V, $-40$ °C $\leq$ T $_{j}$ $\leq$ 25°C VDD = 0 V                     | -   | 2.2 | 15  | μA   |

| IQ_VBP4 | Quiescent consumption for VBP in reset mode | VBP = 60 V, 25°C < $T_j \le 150$ °C<br>VDD = 0 V                               | -   | 4.6 | 15  | μA   |

| IQ_VDH1 | Quiescent consumption for VDH in reset mode | VDH = 14 V, $-40$ °C $\leq T_j \leq 25$ °C<br>VDD = 0 V                        | -   | 0.3 | 15  | μA   |

| IQ_VDH2 | Quiescent consumption for VDH in reset mode | VDH = 14 V, 25°C $<$ T $_{j}$ ≤ 150°C VDD = 0 V                                | -   | 1   | 15  | μA   |

| IQ_VDH3 | Quiescent consumption for VDH in reset mode | VDH = 60 V, $40^{\circ}$ C $\leq$ T $_{j}$ $\leq$ 25 $^{\circ}$ C<br>VDD = 0 V | -   | 0.8 | 15  | μA   |

| IQ_VDH4 | Quiescent consumption for VDH in reset mode | VDH = 60 V, 25°C <t<sup>j ≤ 150°C<br/>VDD = 0 V</t<sup>                        | -   | 2.5 | 15  | μA   |

| IQ_VIO1 | Quiescent consumption for VIO in reset mode | VIO = 5 V, $-40^{\circ}$ C $\leq$ T $_{j}$ $\leq$ 25 $^{\circ}$ C<br>VDD = 0 V | -   | 5   | 15  | μA   |

| IQ_VIO2 | Quiescent consumption for VIO in reset mode | VIO = 5 V, $25^{\circ}$ C < $T_j \le 150^{\circ}$ C<br>VDD = 0 V               | -   | 6   | 15  | μA   |

Table 10. Mean current consumptions in normal mode

| Symbol       | Parameter                                       | Test Condition                                           | Min | Тур | Max | Unit |

|--------------|-------------------------------------------------|----------------------------------------------------------|-----|-----|-----|------|

|              |                                                 | VBP = 14 V, -40°C ≤ T <sub>j</sub> ≤ 25°C                |     |     |     |      |

| INORMAL_VBP1 | Mean Current consumption for VBP in normal mode | Default Configuration and HBn_DIS=0 INLn=INHn=0, SHS_n=0 | -   | 2.5 | 20  | mA   |

|              |                                                 | [n=1,2,3]                                                |     |     |     |      |

|              |                                                 | VBP = 14 V, 25°C < T <sub>j</sub> ≤ 150°C                |     |     |     |      |

| INORMAL_VBP2 | Mean Current consumption for VBP in normal mode | Default Configuration and HBn_DIS=0 INLn=INHn=0, SHS_n=0 | -   | 2.5 | 20  | mA   |

|              |                                                 | [n=1,2,3]                                                |     |     |     |      |

|              |                                                 | VBP = 60 V, -40°C ≤ T <sub>j</sub> < 25°C                |     |     |     |      |

| INORMAL_VBP3 | Mean Current consumption for VBP in normal mode | Default Configuration and HBn_DIS=0 INLn=INHn=0, SHS_n=0 | -   | 2.5 | 20  | mA   |

|              |                                                 | [n=1,2,3]                                                |     |     |     |      |

|              |                                                 | VBP = 60 V, 25°C < T <sub>j</sub> ≤ 150°C                |     |     |     |      |

| INORMAL_VBP4 | Mean Current consumption for VBP in normal mode | Default Configuration and HBn_DIS=0 INLn=INHn=0, SHS_n=0 | -   | 2.5 | 20  | mA   |

|              |                                                 | [n=1,2,3]                                                |     |     |     |      |

DS13546 - Rev 3 page 16/153

| Symbol       | Parameter                                       | Test Condition                                                                   | Min | Тур | Max | Unit |

|--------------|-------------------------------------------------|----------------------------------------------------------------------------------|-----|-----|-----|------|

|              |                                                 | VDH = 14 V, -40°C ≤ T <sub>j</sub> ≤ 25°C                                        |     |     |     |      |

| INORMAL_VDH1 | Mean Current consumption for VDH in normal mode | Default Configuration and HBn_DIS=0 INLn=INHn=0, SHS_n=0                         | -   | 3.5 | 15  | mA   |

|              |                                                 | [n=1,2,3]                                                                        |     |     |     |      |

|              |                                                 | VDH = 14 V, 25°C < T <sub>j</sub> ≤ 150°C                                        |     |     |     |      |

| INORMAL_VDH2 | Mean Current consumption for VDH in normal mode | Default Configuration and HBn_DIS=0 INLn=INHn=0, SHS_n=0                         | -   | 3.5 | 15  | mA   |

|              |                                                 | [n=1,2,3]                                                                        |     |     |     |      |

|              |                                                 | VDH = 60 V, -40°C ≤ $T_j$ ≤ 25°C                                                 |     |     |     |      |

| INORMAL_VDH3 | Mean Current consumption for VDH in normal mode | Default Configuration and HBn_DIS=0 INLn=INHn=0, SHS_n=0                         | -   | 3.5 | 15  | mA   |

|              |                                                 | [n=1,2,3]                                                                        |     |     |     |      |

|              |                                                 | VDH = 60 V, 25°C < T <sub>j</sub> ≤ 150°C                                        |     |     |     |      |

| INORMAL_VDH4 | Mean Current consumption for VDH in normal mode | Default Configuration and HBn_DIS=0 INLn=INHn=0, SHS_n=0                         | -   | 3.5 | 15  | mA   |

|              |                                                 | [n=1,2,3]                                                                        |     |     |     |      |

|              |                                                 | VDD = 5.5 V, -40°C ≤ T <sub>j</sub> ≤ 25°C                                       |     |     |     |      |

| INORMAL_VDD1 | Mean Current consumption for VDD in normal mode | Default Configuration and HBn_DIS=0 INLn=INHn=0, SHS_n=0                         | -   | 23  | 40  | mA   |

|              |                                                 | [n=1,2,3]                                                                        |     |     |     |      |

|              |                                                 | VDD = 5.5 V, 25°C < T <sub>j</sub> ≤ 150°C                                       |     |     |     |      |

| INORMAL_VDD2 | Mean Current consumption for VDD in normal mode | Default Configuration and HBn_DIS=0 INLn=INHn=0, SHS_n=0                         | -   | 25  | 40  | mA   |

|              |                                                 | [n=1,2,3]                                                                        |     |     |     |      |

|              |                                                 | $VIO = 5 \text{ V}, -40^{\circ}\text{C} \le \text{T}_{j} \le 25^{\circ}\text{C}$ |     |     |     |      |

| INORMAL_VIO1 | Mean Current consumption for VIO in normal mode | Default Configuration and HBn_DIS=0 INLn=INHn=0, SHS_n=0                         | -   | 2   | 4   | mA   |

|              |                                                 | [n=1,2,3]                                                                        |     |     |     |      |

|              |                                                 | VIO = 5 V, 25°C < T <sub>j</sub> ≤ 150°C                                         |     |     |     |      |

| NORMAL_VIO2  | Mean Current consumption for VIO in normal mode | Default Configuration and HBn_DIS=0 INLn=INHn=0, SHS_n=0                         | -   | 2.5 | 4   | mA   |

|              |                                                 | [n=1,2,3]                                                                        |     |     |     |      |

DS13546 - Rev 3

Downloaded from Arrow.com. page 17/153

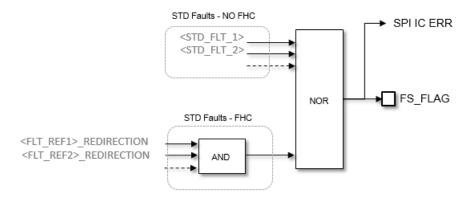

# 4 Functional safety

#### 4.1 Safe states

To reach the safety requirements of the system, the following safe states are supported by L9908, with a different associated priority level:

- SAFE-OFF due to CLK1 TIME OUT or NDIS='0'. Priority Level = 1

- SAFE-HIZ. Priority Level = 2

- SAFE-OFF due to STD Fault detection except INT\_RST or Configurable fault with related FRC set as 00.

Priority Level = 3

- SAFE-DIS. Priority Level = 4

In case of simultaneous safe state activation requests with different safe states required, the safe state reached by L9908 is determined by the highest priority level.

Note:

- Priority is descending, 1 = higher priority.

- SAFE OFF by NDIS assertion has the highest priority all over.

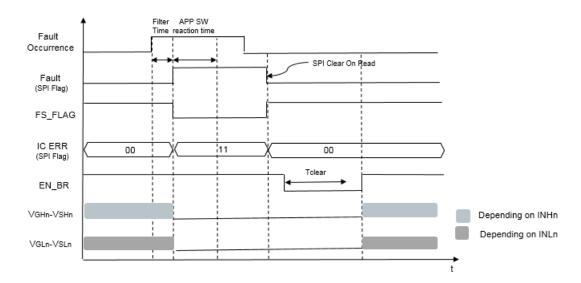

#### 4.1.1 SAFE-OFF

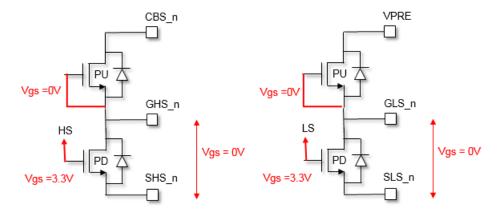

When SAFE-OFF is active the gate driver unit is disabled by forcing the three Half Bridges in a tristate mode so that VGHS\_n-VSHS\_n = 0 V actively, VGLS\_n-VSLS\_n = HIZ and by disabling the Gate Drive Supply block (CP1 EN = CP2 EN = 0).

SAFE-OFF is activated by default if the following conditions are verified:

- STD Fault detection except INT\_RST

- CLK1\_TIME\_OUT

- · Configurable fault with related FRC set as 00

- NDIS = 0

### 4.1.2 SAFE-DIS

When SAFE-DIS is active the gate driver unit is disabled by forcing the three Half Bridges in a tristate mode so that VGHS n-VSHS n and VGLS n-VSLSn are kept tight to 0 V actively.

SAFE-DIS is activated by default if the following conditions are verified:

- VPRE UV fault detection

- Configurable fault with related FRC set as 01

- EN\_BR = 0

#### 4.1.3 SAFE-HIZ

When SAFE-HIZ is active the gate driver unit is disabled by forcing the driver output in a tristate mode so that VGHS\_n-VSHS\_n and VGLS\_n-VSLSn = HIZ.

SAFE-HIZ is activated by default if the following conditions are verified:

- Fault detection which generates INT\_RST

- SW RST

- No STD faults present & HBn\_DIS = 0 [n = 1,2,3] & STD DRV\_HIZ = 1

DS13546 - Rev 3 page 18/153

### 4.2 Safe state activation

Depending on the safe state its activation is performed through one between two separate paths.

Main Logic CP1 DRV\_HIZ CP2 EN\_BR Disable Logics SAFE\_SW\_ECHO CLK1\_TIME\_OUT ΗV HV ΗV ΗV Safe NDIS Switch-off ΗV HΥ Damage Protected Activation Path Logic Activation Path

Figure 6. Safe states activation paths

Logic activation path: safe state activation is carried out entirely by the main logic.

This path is used to develop:

- SAFE HIZ (except if determined by CLK1\_TIME\_OUT)

- SAFE DIS

- SAFE OFF

Damage protected activation path: in case of device failure where internal main logic integrity is compromised L9908 implements an isolated Safe Switch Off structure which allows to activate an isolated Safe Switch Off structure which can be activated through a separated path.

This path is used to develop:

- SAFE OFF (only if determined by NDIS = 0)

- CLK1\_TIME\_OUT

The Safe State activation through the damage protected path is signaled by setting the dedicated SPI read only bit SAFE\_STATE (GEN\_STATUS1[2]).

DS13546 - Rev 3 page 19/153

V3V3 DIG NDIS pin ECHO (to Main Logic) V3V3\_SAFE V3V3 DIG NDIS - $\prod$ SAFE HIZ ECHO GND (to Main Logic) GND V3V3\_SAFE GND POR\_DIG HSn Gate DRV LSn Gate DRV VGHS\_n-VSHS\_n=0 VGLS\_n-VSLS\_n=0 I V3V3\_SAFE EN\_CP GND OR V3V3\_SAFE CLK1\_ERR or SW OFF Self Test GND GND П GND V3V3\_DIG UV (from Main Logic) GND V3V3 DIG V3V3\_SAFE V3V3\_DIG V3V3\_SAFE V3V3\_SAFE V3V3\_DIG OV GND

Figure 7. Damage protected activation simplified structure

DS13546 - Rev 3 page 20/153

# 5 Functional description

## 5.1 Internal supply

#### 5.1.1 VDD power supply

The internal supply rails for analog and digital circuitries on L9908 are generated from the VDD pin which is the main power input. Additionally VDD is used as reference voltage for Current Measurement Analog output (CSO Buffers).

### 5.1.2 Internal supply monitor

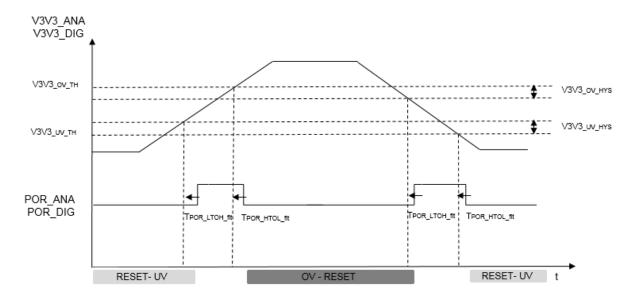

Each internal supply voltage level (V3V3\_ANA/DIG) is monitored by means of a dedicated UV and an OV diagnosis. Abnormal behavior on internal supply level will cause the generation of a POR (Power on Reset) event that consequently sends L9908 into a RESET state. Hysteresis on thresholds and filtering time are implemented. If V3V3\_ANA/DIG  $\leq$  V3V3\_uv\_th occurs for an interval longer than T\_por\_htol\_flt, INT\_RST flag is set. The error flag remains set until the failure condition is removed and the flag is cleared by an SPI command. POR\_ANA/DIG is set low and internal reset is triggered.

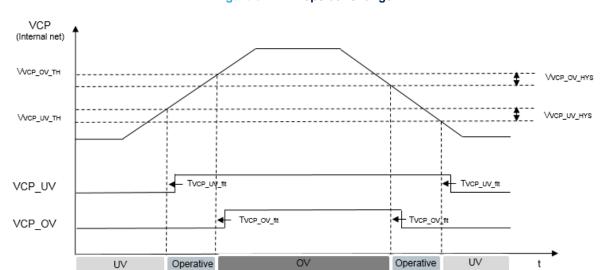

If V3V3\_ANA/DIG ≥ V3V3\_ov\_th occurs for an interval longer than T\_por\_htol\_flt, INT\_RST flag is set. The error flag remains set until the failure condition is removed and the flag is cleared by an SPI command. POR\_ ANA/DIG is set low and internal reset is triggered. OV/UV Resets related to V3V3 internal reference are represented in Figure 8.

The internal supply monitor is safety relevant and then a self-check procedure is implemented.

Note:

All parameters are guaranteed and tested in the voltage ranges specified in Table 5 unless otherwise specified. Where not specified parametrical operating range equals functional operating range.

Table 11. Internal power supply electrical characteristics

| Symbol         | Parameter                              | Min   | Тур  | Max   | Unit | Notes                         |

|----------------|----------------------------------------|-------|------|-------|------|-------------------------------|

| VBG_vout       | Bandgap output voltage                 | 1.188 | 1.2  | 1.212 | V    | -                             |

| V3V3_vout      | V3V3_ANA/DIG output voltage            | 3.2   | 3.3  | 3.34  | V    | -                             |

| V3V3_uv_th     | V3V3_ANA/DIG under-voltage threshold   | 2.65  | 2.73 | 2.93  | V    | Comparator output Low to High |

| V3V3_uv_hys    | V3V3_ANA/DIG under-voltage hysteresis  | 35    | 45   | 56    | mV   | -                             |

| V3V3_ov_th     | V3V3_ANA/DIG over-voltage threshold    | 3.6   | 3.7  | 3.9   | V    | Comparator output Low to High |

| V3V3_ov_hys    | V3V3_ANA/DIG over-voltage hysteresis   | -     | 0    | -     | mV   | -                             |

| V3V3_pre_vout  | V3V3_PRE output voltage                | 2.7   | 3.35 | 3.55  | V    | -                             |

| T_por_ltoh_flt | POR_V3V3 Low to High state filter time | 3.2   | 4.8  | 7.3   | μs   | Analog filter                 |

| T_por_htol_flt | POR_V3V3 High to Low state filter time | 5.4   | 8.3  | 13.5  | μs   | Analog filter                 |

DS13546 - Rev 3 page 21/153

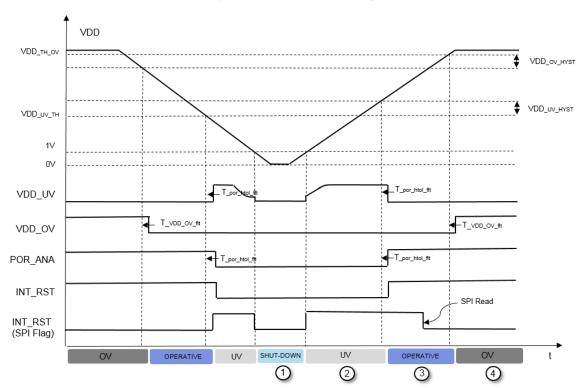

Figure 8. Internal supply operative range

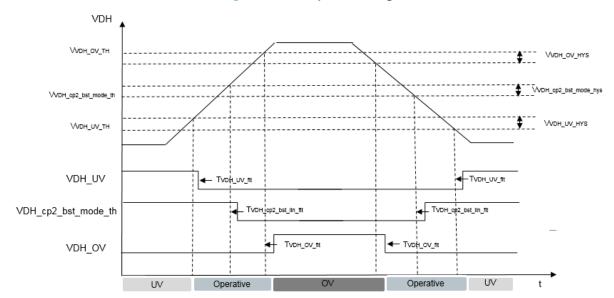

#### 5.1.3 VDD monitor

VDD voltage level is monitored by means of dedicated UV and an OV diagnosis. Hysteresis on thresholds and filtering time are implemented.

If VDD ≤ VDD\_uv\_th occurs for an interval longer than T\_por\_htol\_flt, INT\_RST flag is set. The error flag remains set until the failure condition is removed and the flag is cleared by SPI command. POR\_ANA is set low and internal reset is triggered.

If  $VDD \ge VDD_ov_th$  occurs for an interval longer than  $T_vdd_ov$ ,  $VDD_ov_th$  occurs for an interval longer than  $T_vdd_ov$ ,  $VDD_ov_th$  flag is set. The error flag remains set until the failure condition is removed and the flag is cleared by SPI command.

Device's functional ranges related to VDD level are represented in Figure 9.

The operative VDD monitor is safety relevant and then a self-check procedure is implemented.

Note:

All parameters are guaranteed and tested in the voltage ranges reported in Table 5 unless otherwise specified. Where not specified the parametrical operating range equals the functional operating range.

Table 12. VDD monitor electrical characteristics

| Symbol       | Parameter                              | Min  | Тур  | Max  | Unit | Notes                         |

|--------------|----------------------------------------|------|------|------|------|-------------------------------|

| VDD_uv_th    | VDD under-voltage threshold            | 3.95 | 4.05 | 4.15 | V    | Comparator output Low to High |

| VDD_uv_hys   | VDD under-voltage hysteresis           | 135  | -    | 165  | mV   |                               |

| VDD_ov_th    | VDD over-voltage threshold             | 5.5  | -    | 6    | V    | Comparator output Low to High |

| VDD_ov_hys   | VDD over-voltage hysteresis            | 120  | 170  | 220  | mV   |                               |

| T_vdd_ov_flt | VDD over-voltage detection filter time | 1    | -    | 5    | μs   | Digital filter                |

DS13546 - Rev 3 page 22/153

## 5.1.3.1 VDD functional ranges

Figure 9. VDD functional ranges

#### Where:

- 1. 0V ≤ VDD ≤ 1V

- L9908 is shut-down. Internal supply and reference voltage/currents levels are shutdown.

- 2.  $1V \le VDD \le VDD_uv_th + VDD_uv_hyst$

VDD is in under-voltage and L9908 is sent into RESET mode. Internal supply and reference voltage/currents levels are degraded. Internal registers are under reset.

- 3.  $VDD_uv_th \le VDD \le VDD_ov_th$

- Internal supply and reference voltage/currents are available. Internal registers are out of reset. (if no STD faults are detected and NDIS='1' the device is in NORMAL mode).

- 4. VDD\_ov\_th ≤ VDD

VDD is in over-voltage and L9908 sent into safe state. The internal supply and reference voltage/currents are available. Internal registers are out of reset.

DS13546 - Rev 3 page 23/153

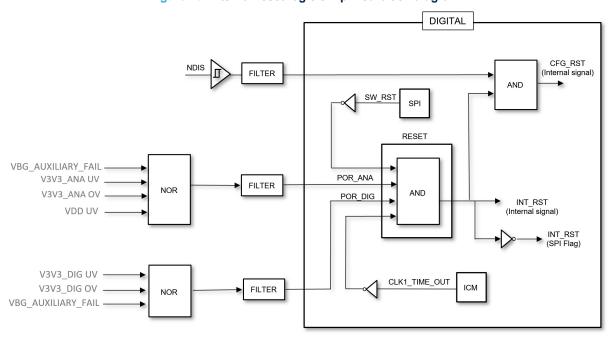

# 5.2 Internal resets (INT\_RST, CFG\_RST)

L9908 implements two different reset states following two different reset signals INT\_RST and CFG\_RST.

• INT\_RST (active LOW) is the main internal reset signal; when active it resets the whole logic system. This signal is generated via the reset logic by supervising Internal Supply Monitor, VDD Monitor and ICM outputs: if a fault is verified the internal reset is activated.

The internal INT\_RST can be alternatively triggered through an activation key written into a dedicated SPI register SW\_RESET\_KEY.

Table 13. SW reset activation register

| SW_RESET_KEY <7:0> | Description         |

|--------------------|---------------------|

| 0xCC               | SW Reset Activation |

CFG\_RST (active LOW) is the reset signal configuration register.

This signal is generated via the reset logic by supervising the NDIS pin status level: if a '0' logic level is detected for a time interval greater than T\_ndis\_flt the reset is activated.

Table 14. Internal resets sources and filtering

| Condition            | Action              | Filter timer for Reset |

|----------------------|---------------------|------------------------|

| NDIS='0'             | CFG_RST=0           | T_ndis_flt             |

| UV on V3V3_ANA       | CFG_RST=0 INT_RST=0 | T_por_ltoh_flt         |

| UV on V3V3_DIG       | CFG_RST=0 INT_RST=0 | T_por_ltoh_flt         |

| OV on V3V3_ANA       | CFG_RST=0 INT_RST=0 | T_por_ltoh_flt         |

| OV on V3V3_DIG       | CFG_RST=0 INT_RST=0 | T_por_ltoh_flt         |

| UV on BG MAIN        | CFG_RST=0 INT_RST=0 | T_por_ltoh_flt         |

| UV on BG AUXILIARY   | CFG_RST=0 INT_RST=0 | T_por_ltoh_flt         |

| UV on VDD            | CFG_RST=0 INT_RST=0 | T_por_ltoh_flt         |

| CLK1 timeout (stuck) | CFG_RST=0 INT_RST=0 | ICM Timeout            |

| SW Reset SPI frame   | CFG_RST=0 INT_RST=0 | NA                     |

DS13546 - Rev 3 page 24/153

Figure 10. Internal reset logic simplified block diagram

DS13546 - Rev 3 page 25/153

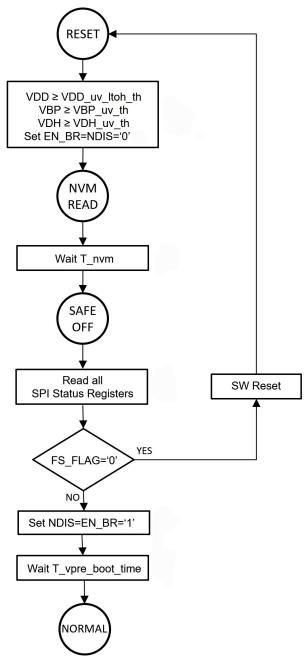

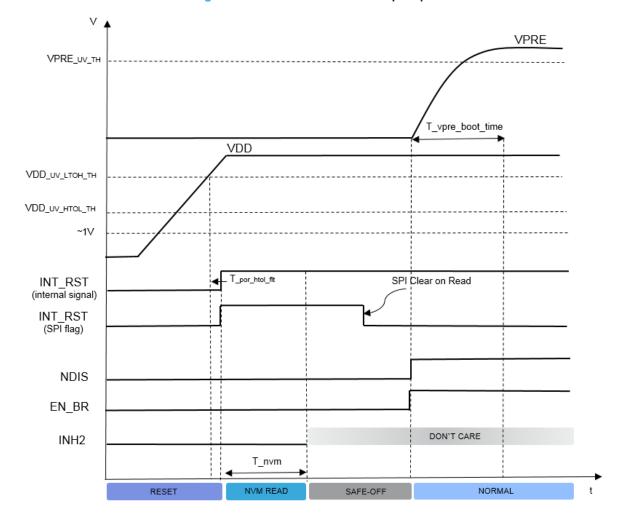

# 5.3 Device operation state machine

INT RST=1 INT\_RST=0 (Internal Signal) (Internal Signal) 1 RESET 2 STD Fault NVM READ MODE CONFIG Access 6 NVM CRC Check End & No STD CONFIG SPI Clear on Read → EN\_BR rising edge NVM Data Deploy End MODE (3) NORMAL CONFIG Leave or 4 CONFIG Timeout Expired MODE SAFE OFF NDIS=0 MODE STD Fault SELF TEST Access BIST\_STATUS=10 or SELF TEST Timeout Expired (5) SELF TEST BIST\_STATUS=11 MODE

Figure 11. Device operational state machine

#### Where:

#### RESET MODE

Internal supply and reference voltage/currents levels are degraded or shutdown. Main logic is under reset (INT RST = '0', Internal signal). All functions are disabled:

- Gate Driver Supply stage and Half Bridge Gate Drivers stage are shutdown (SAFE-HIZ)

- Current Monitors chains and monitoring units are shutdown

- SPI Read/Write operations are not available

The device persists in this state as long as INT\_RST='0' (Internal signal).

DS13546 - Rev 3 page 26/153

#### 2. NVM READ MODE

Internal supply and reference voltage/currents are available possibly exceeding spec parametrical ranges. Main logic is out of reset (INT\_RST = '1', Internal signal). Main functions are disabled:

- Gate Driver Supply stage disabled

- Half Bridge Gate Drivers stages are in HIZ mode while LS Half Bridge Gate Drivers stages are shutdown (SAFE-HIZ)

- Current Monitors chains and monitoring units are disabled

- SPI Read is available while SPI Write is disabled

In this mode a CRC check on NVM data is first performed:

- If no CRC error is detected the NVM content is deployed into main logic register

- If a CRC error is detected the related main logic registers are reset to default values (all '0') and NVM\_CRC\_FAIL flag is set to '1'

Note: All parameters are guaranteed and tested in the voltage ranges reported in Table 5 unless otherwise specified. Where not specified the parametrical operating range equals the functional operating range.

Table 15. Power up/down timings

| Symbol | Parameter                      | Min | Тур | Max | Unit | Notes                          |

|--------|--------------------------------|-----|-----|-----|------|--------------------------------|

| T_nvm  | NVM data deploy & CRC duration | -   | -   | 2   | ms   | Not subject to production test |

#### NORMAL MODE

Internal supply and reference voltage/currents are available and within spec ranges. Main logic is out of reset (INT RST = '1', Internal signal). Main functions:

- Half Bridge Gate Drivers status depends on disable logic assessment (Functional or SAFE DIS)

- Gate Driver Supply stage status depends on configuration

- Current Monitors chains and monitoring units status depend on configuration

- SPI Read/Write operations are available

### 4. SAFE OFF MODE

Internal supply and reference voltage/currents are available and within spec ranges. Main logic is out of reset (INT\_RST = '1', Internal signal). Main functions:

- Gate Driver Supply stage is disabled

- HS and LS state are in SAFE OFF or SAFE HIZ depending on fault reaction as described in Table 17

- Current Monitors chains and monitoring units status depend on configuration

- SPI Read/Write operations are available

#### 5. SELF TEST MODE

Internal supply and reference voltage/currents are available and within spec ranges. Main logic is out of reset (INT RST = '1', Internal signal). Main functions:

- Gate Driver Supply stage depends on disable logic assessment

- Half Bridge Gate Drivers are disabled (SAFE-DIS)

- Current Monitors chains and monitoring units status depend on configuration

- SPI Read is available while SPI Write is disabled

#### CONFIG MODE

Internal supply and reference voltage/currents are available and within spec ranges. Main logic is out of reset (INT\_RST = '1', Internal signal). Main functions:

- Half Bridge Gate Drivers status depends on disable logic assessment (Functional or SAFE\_DIS)

- Gate Driver Supply stage status depends on configuration

- Current Monitors chains and monitoring units status depend on configuration

- SPI Read/Write operations are available

Three SPI readable flags are present to read-back the operational state machine status according to the following table:

DS13546 - Rev 3 page 27/153

**RESET Mode**

**RESET Mode**

| OPERATION_MODE2 | OPERATION_MODE1 | OPERATION_MODE0 | Description    |

|-----------------|-----------------|-----------------|----------------|

| 0               | 0               | 0               | RESET Mode     |

| 0               | 0               | 1               | NVM Read Mode  |

| 0               | 1               | 0               | SAFE OFF Mode  |

| 0               | 1               | 1               | NORMAL Mode    |

| 1               | 0               | 0               | CFG Mode       |

| 1               | 0               | 1               | SELF TEST Mode |

Table 16. Operation mode status bits

Table 17. Device operation modes summary

1

1

| Operation Mode | Logic Core | Gate Driver<br>Supply | HS/LS Pre-drivers     | Current Monitors | Diagnosis     | SPI Access |

|----------------|------------|-----------------------|-----------------------|------------------|---------------|------------|

| RESET          | Reset      | Disabled              | SAFE_HIZ              | Disabled         | Disabled      | Disabled   |

| NVM READ       | Functional | Disabled              | SAFE_HIZ              | Disabled         | Disabled      | Read       |

| SELF TEST      | Functional | As configured         | SAFE_DIS              | As configured    | As configured | Read       |

| SAFE OFF       | Functional | Disabled              | SAFE_OFF/<br>SAFE_HIZ | Disabled         | As configured | Read/Write |

| CONFIG         | Functional | As configured         | Functional/SAFE_DIS   | As configured    | As configured | Read/Write |

| NORMAL         | Functional | As configured         | Functional/SAFE_DIS   | As configured    | As configured | Read/Write |

# 5.4 Configuration mode

1

1

The L9908 default configuration can be modified by properly writing the SPI configuration registers.

Configuration registers are divided into three categories depending on their functional safety relevance:

- Safety Relevant Registers (SRR): the content of these registers is protected by a two-step LOCK mechanism: CONFIG mode access procedure and a masking related to Half Bridges status (EN\_BR = 0 or HBn\_DIS = 1 with n = 1, 2, 3). The content is then protected by a cyclic 5-bit CRC check.

- Safety Latent Registers (SLR): the content of these registers is protected by a one-step LOCK mechanism: CONFIG mode access procedure. The content has no CRC protection.

- Non-safety Registers (NSR): the content of these registers can be accessed directly in NORMAL Mode and has no CRC protection.

Correct SRR modification is safety relevant and then a CRC check on their bit is performed continuously by a dedicated state machine. CRC check is performed sequentially over the 11 bits content of shadow register, LSB first. The 5-bit CRC is calculated using the following polynomial expression over bit 5-15:

$$g(x) = x^5 + x^2 + 1 \tag{4}$$

The initial value to be used is 11111 (0x1F).

#### Example:

- Input word: [000.0000.0100] (0x004)

- Computed CRC: [0.1011] (0XB)

- Resulting frame: [0000.0000.1000.1011] (0X8B)

If a CRC violation on one or more SRR the SR\_CRC\_FAIL flag is set. The error flag remains set until the failure condition is removed and the flag is cleared by the SPI command.

DS13546 - Rev 3 page 28/153

#### 5.4.1 Configuration mode activation

An accidental SRR and SLR change must be avoided therefore a finite state machine is implemented to access the CONFIG mode.

The CONFIG mode access state machine is composed by 2 sequential states, the passage from a state to the next one is carried out by the acknowledgment of a dedicated UNLOCK frames sequence to be written in the SPI register CFG\_EN\_UNLOCK (UNLOCK1 key: 0x55 → UNLOCK2 key: 0x33).

The correct completion of the CONFIG Mode procedure gives access to SLR. Access to SRR is further masked until EN BR = 0 or HBn DIS = 1 [n = 1, 2, 3].

Table 18. CONFIG mode activation register

| CFG_EN_UNLOCK <7:0> | Description        |

|---------------------|--------------------|

| 0x55 → 0x33         | CONFIG Mode Access |

| 0xAA                | CONFIG Mode Exit   |

Note:

- SRR and SLR configuration will become effective the next clock cycle after the completed writing operation.

- Write attempts on SRR and SLR are ignored as long as the previous requirements aren't met.

- Write attempts on Read Only (RO) registers are ignored, no matter if the register is NSR, SLR or SRR.

Wrong UNLOCK

SPI Frame 1

UNLOCK

SPI Frame 1

Partial CFG MODE

UNLOCK

SPI Frame 2

CFG Timeout or

CFG LOCK SPI Frame

CONFIG

MODE

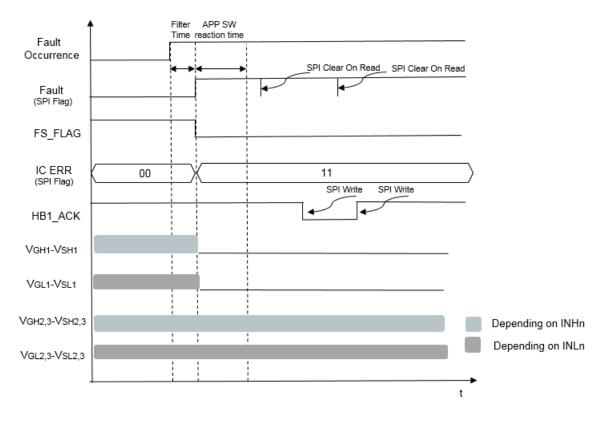

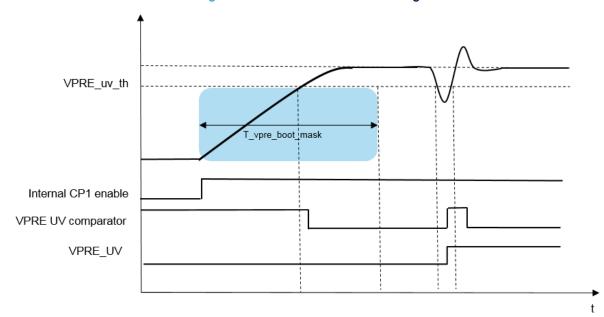

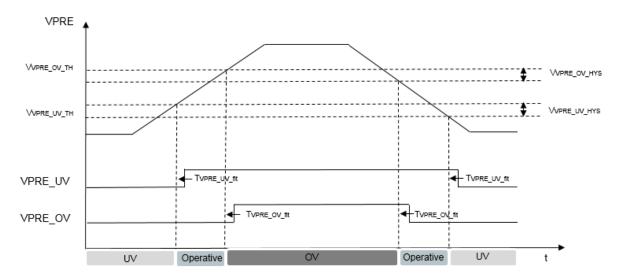

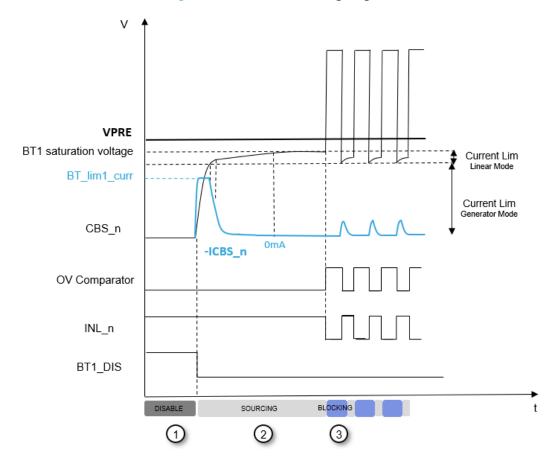

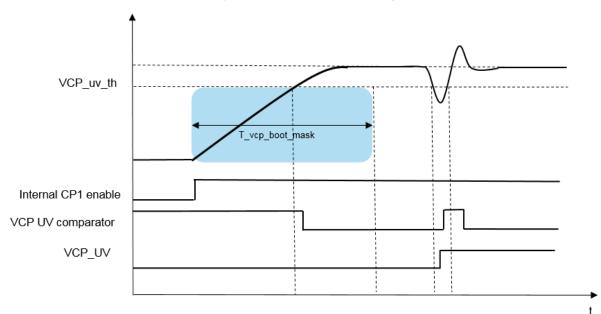

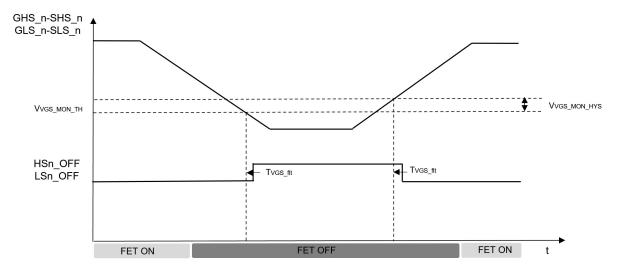

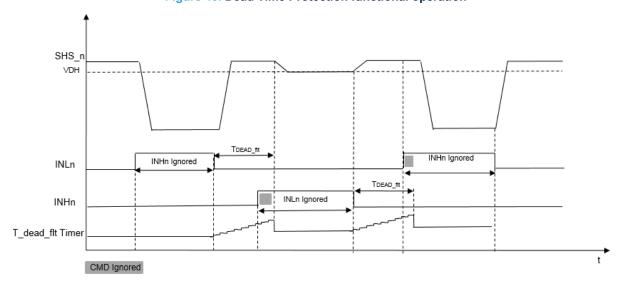

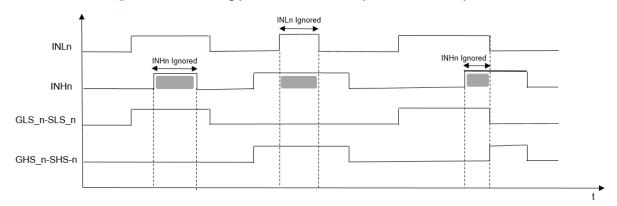

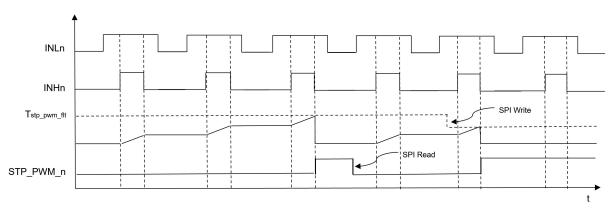

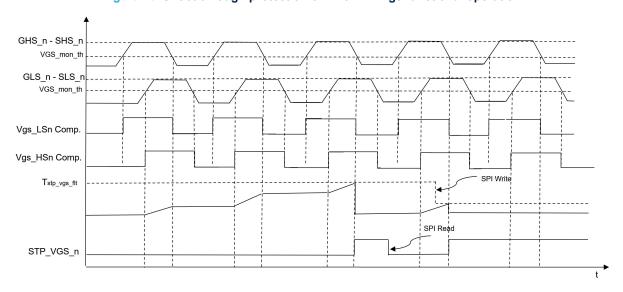

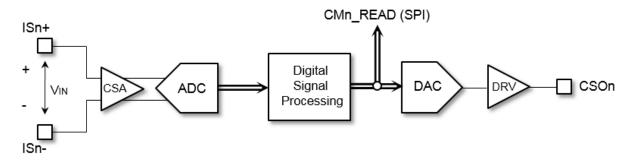

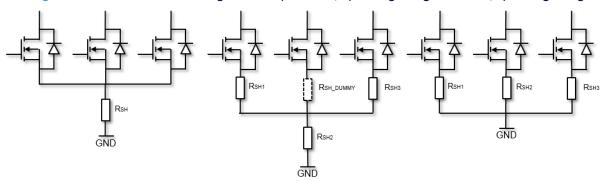

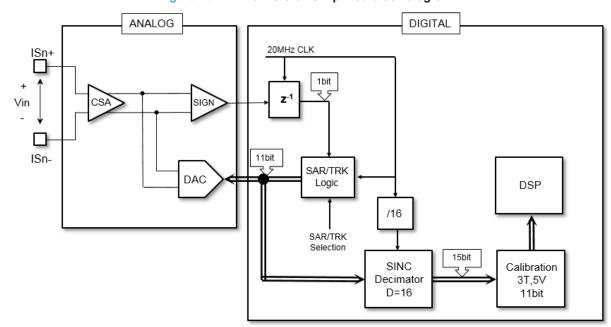

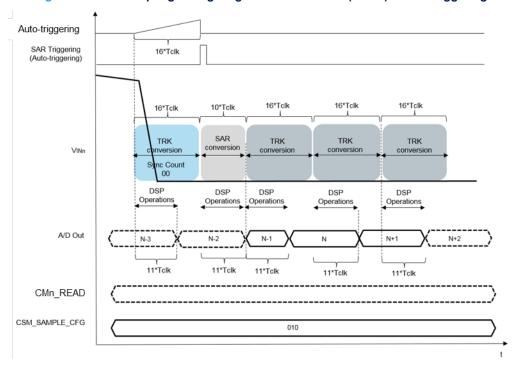

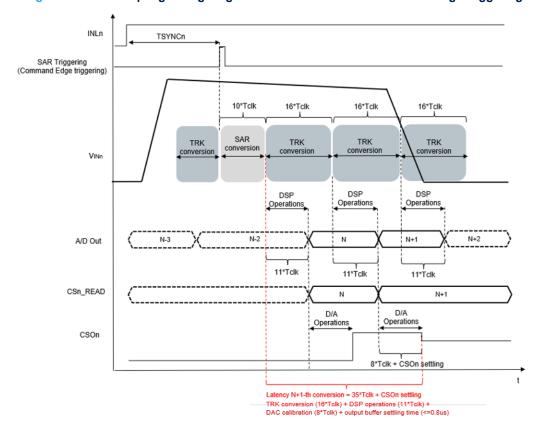

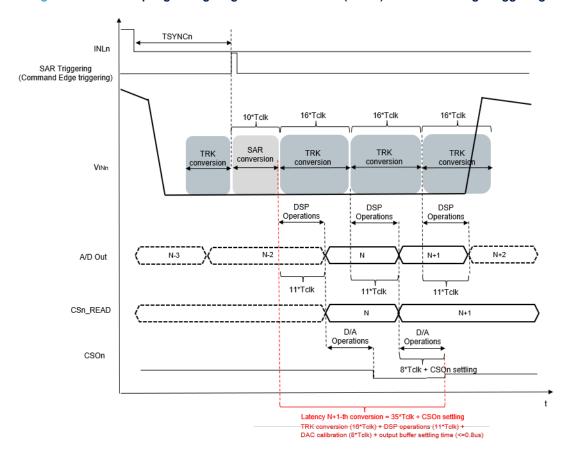

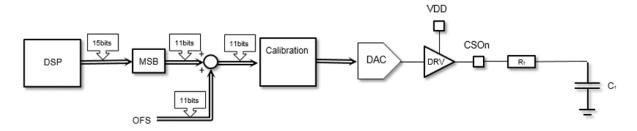

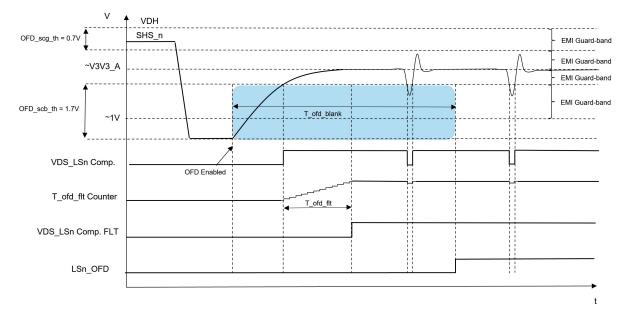

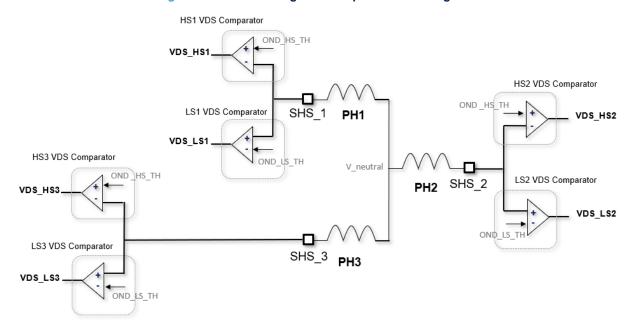

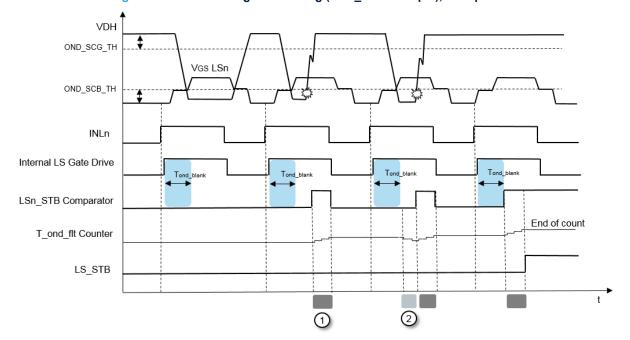

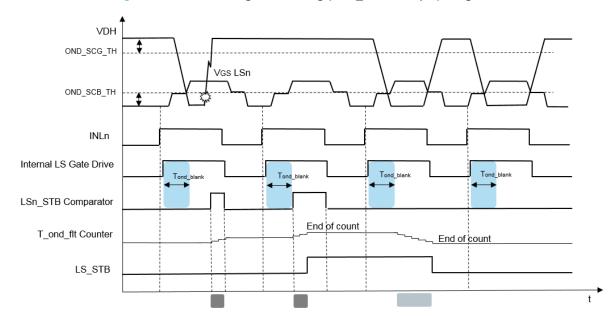

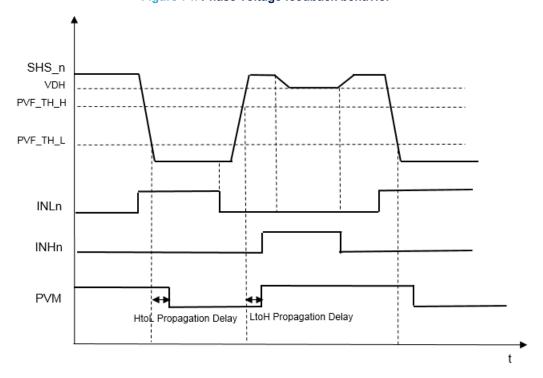

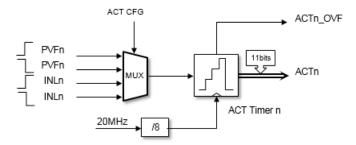

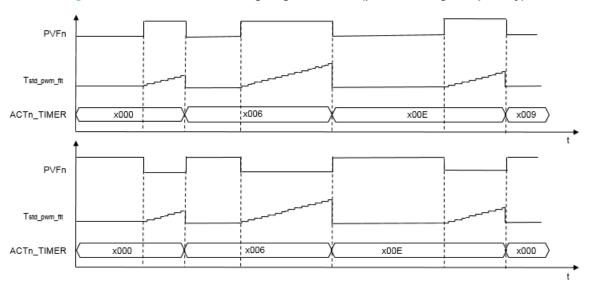

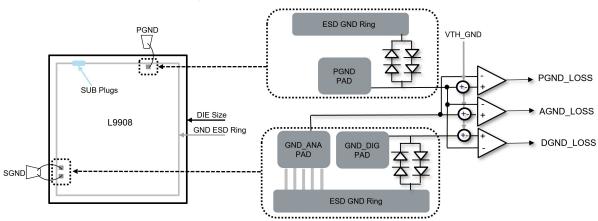

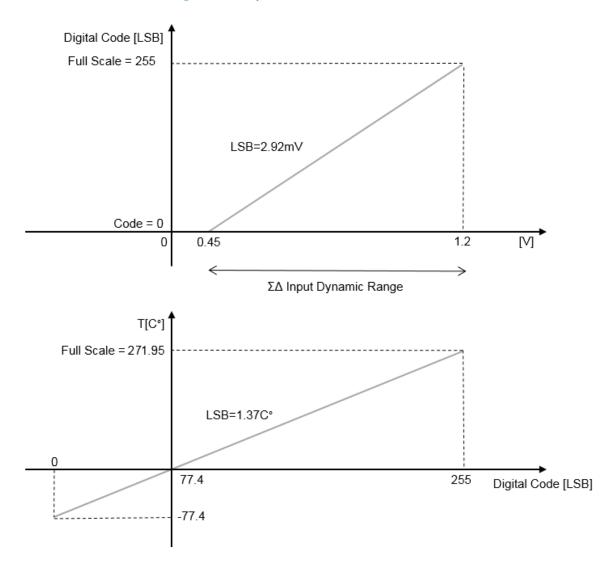

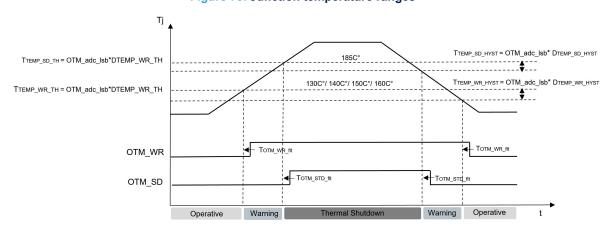

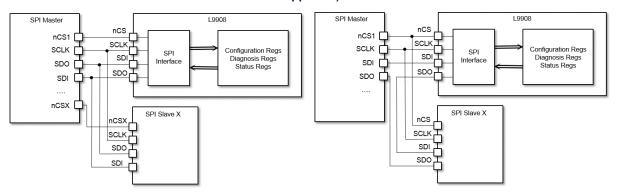

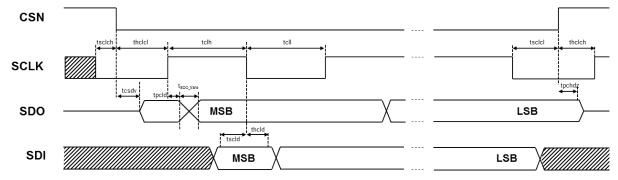

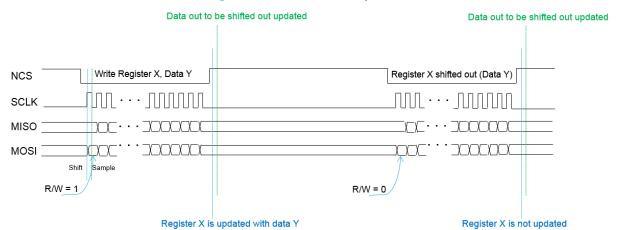

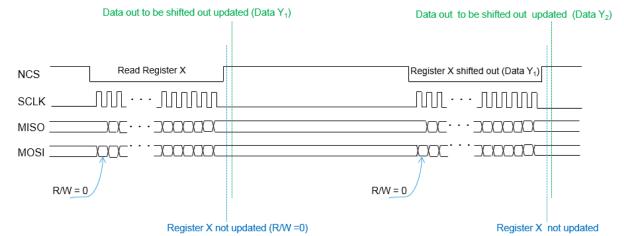

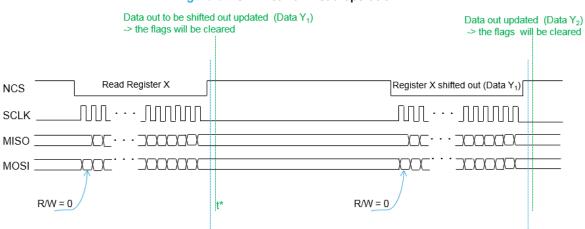

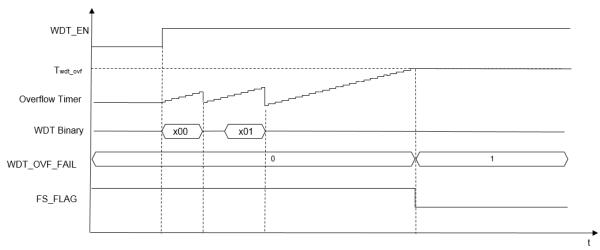

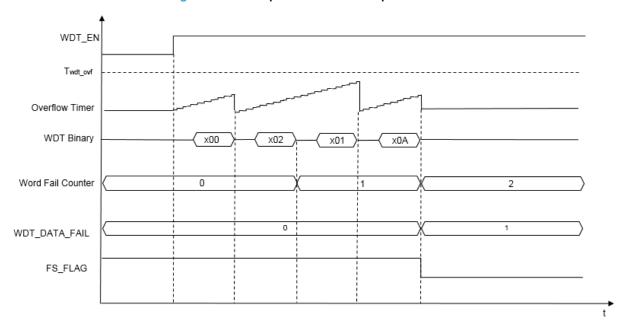

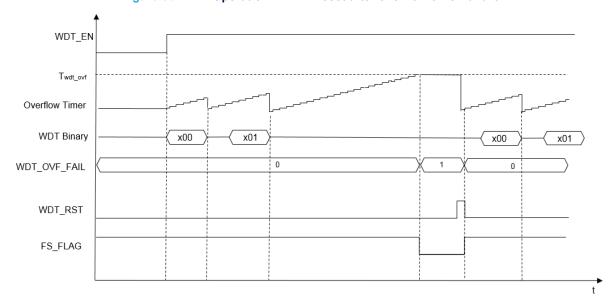

Figure 12. CONFIG mode state machine