# High Speed Dual MOSFET Drivers

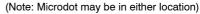

The MC34151/MC33151 are dual inverting high speed drivers specifically designed for applications that require low current digital circuitry to drive large capacitive loads with high slew rates. These devices feature low input current making them CMOS and LSTTL logic compatible, input hysteresis for fast output switching that is independent of input transition time, and two high current totem pole outputs ideally suited for driving power MOSFETs. Also included is an undervoltage lockout with hysteresis to prevent erratic system operation at low supply voltages.

Typical applications include switching power supplies, dc to dc converters, capacitor charge pump voltage doublers/inverters, and motor controllers.

These devices are available in dual-in-line and surface mount packages.

### Features

- Two Independent Channels with 1.5 A Totem Pole Output

- Output Rise and Fall Times of 15 ns with 1000 pF Load

- CMOS/LSTTL Compatible Inputs with Hysteresis

- Undervoltage Lockout with Hysteresis

- Low Standby Current

- Efficient High Frequency Operation

- Enhanced System Performance with Common Switching Regulator Control ICs

- Pin Out Equivalent to DS0026 and MMH0026

- These are Pb-Free and Halide-Free Devices

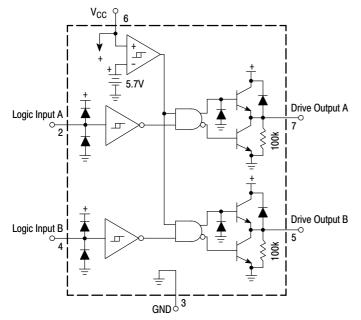

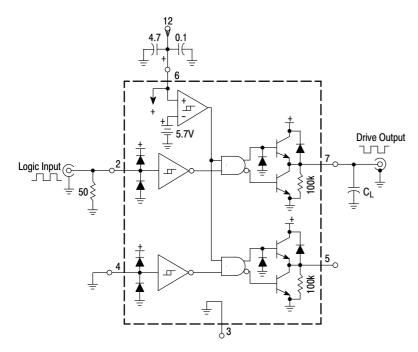

Figure 1. Representative Block Diagram

# **ON Semiconductor®**

http://onsemi.com

# **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 10 of this data sheet.

Downloaded from Arrow.com.

### **MAXIMUM RATINGS**

| Rating                                                                                                                                                                                                                                                                                                   | Symbol                                                                   | Value                                 | Unit                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------|------------------------|

| Power Supply Voltage                                                                                                                                                                                                                                                                                     | V <sub>CC</sub>                                                          | 20                                    | V                      |

| Logic Inputs (Note 1)                                                                                                                                                                                                                                                                                    | V <sub>in</sub>                                                          | –0.3 to $V_{CC}$                      | V                      |

| Drive Outputs (Note 2)<br>Totem Pole Sink or Source Current<br>Diode Clamp Current (Drive Output to V <sub>CC</sub> )                                                                                                                                                                                    | l <sub>O</sub><br>I <sub>O(clamp)</sub>                                  | 1.5<br>1.0                            | A                      |

| Power Dissipation and Thermal Characteristics<br>D Suffix SOIC-8 Package Case 751<br>Maximum Power Dissipation @ $T_A = 50^{\circ}C$<br>Thermal Resistance, Junction-to-Air<br>P Suffix 8-Pin Package Case 626<br>Maximum Power Dissipation @ $T_A = 50^{\circ}C$<br>Thermal Resistance, Junction-to-Air | P <sub>D</sub><br>R <sub>0JA</sub><br>P <sub>D</sub><br>R <sub>0JA</sub> | 0.56<br>180<br>1.0<br>100             | ₩<br>°C/₩<br>₩<br>°C/₩ |

| Operating Junction Temperature                                                                                                                                                                                                                                                                           | Т <sub>Ј</sub>                                                           | +150                                  | °C                     |

| Operating Ambient Temperature<br>MC34151<br>MC33151<br>MC33151V                                                                                                                                                                                                                                          | T <sub>A</sub>                                                           | 0 to +70<br>-40 to +85<br>-40 to +125 | °C                     |

| Storage Temperature Range                                                                                                                                                                                                                                                                                | T <sub>stg</sub>                                                         | -65 to +150                           | °C                     |

| Electrostatic Discharge Sensitivity (ESD) (Note 3)<br>Human Body Model (HBM)<br>Machine Model (MM)<br>Charged Device Model (CDM)                                                                                                                                                                         | ESD                                                                      | 2000<br>200<br>1500                   | V                      |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

For optimum switching speed, the maximum input voltage should be limited to 10 V or V<sub>CC</sub>, whichever is less.

Maximum package power dissipation limits must be observed.

ESD protection per JEDEC Standard JESD22–A114–F for HBM per JEDEC Standard JESD22–A115–A for MM

per JEDEC Standard JESD22-C101D for CDM.

**ELECTRICAL CHARACTERISTICS** ( $V_{CC}$  = 12 V, for typical values  $T_A$  = 25°C, for min/max values  $T_A$  is the only operating ambient temperature range that applies [Note 3], unless otherwise noted.)

|                                            | Characteristics                      | Symbol                   | Min  | Тур  | Max | Unit |

|--------------------------------------------|--------------------------------------|--------------------------|------|------|-----|------|

| LOGIC INPUTS                               |                                      |                          |      |      |     |      |

| Input Threshold Voltage -                  | Output Transition High to Low State  | V <sub>IH</sub>          | -    | 1.75 | 2.6 | V    |

|                                            | Output Transition Low to High State  | V <sub>IL</sub>          | 0.8  | 1.58 | -   |      |

| Input Current – High State (VIH =          | = 2.6 V)                             | IIH                      | -    | 200  | 500 | μA   |

| – Low State (V <sub>IL</sub> =             | 0.8 V)                               | ۱ <sub>۱L</sub>          | -    | 20   | 100 |      |

| DRIVE OUTPUT                               |                                      |                          |      |      |     |      |

| Output Voltage - Low State (ISir           | <sub>lk</sub> = 10 mA)               | V <sub>OL</sub>          | -    | 0.8  | 1.2 | V    |

| (I <sub>Sir</sub>                          | <sub>lk</sub> = 50 mA)               |                          | -    | 1.1  | 1.5 |      |

| (I <sub>Sir</sub>                          | <sub>lk</sub> = 400 mA)              |                          | -    | 1.7  | 2.5 |      |

| – High State (I <sub>So</sub>              | <sub>urce</sub> = 10 mA)             | V <sub>OH</sub>          | 10.5 | 11.2 | -   |      |

|                                            | <sub>urce</sub> = 50 mA)             |                          | 10.4 | 11.1 | -   |      |

|                                            | <sub>urce</sub> = 400 mA)            |                          | 9.5  | 10.9 | -   |      |

| Output Pulldown Resistor                   |                                      | R <sub>PD</sub>          | -    | 100  | -   | kΩ   |

| SWITCHING CHARACTERISTIC                   | <b>S</b> (T <sub>A</sub> = 25°C)     | -                        |      |      | -   | -    |

| Propagation Delay (10% Input to            | 10% Output, C <sub>L</sub> = 1.0 nF) |                          |      |      |     | ns   |

| Logic Input to Drive Output Ris            | Se                                   | t <sub>PLH(in/out)</sub> | -    | 35   | 100 |      |

| Logic Input to Drive Output Fa             | II                                   | tPHL(in/out)             | -    | 36   | 100 |      |

| Drive Output Rise Time (10% to             | 90%) C <sub>L</sub> = 1.0 nF         | tr                       | _    | 14   | 30  | ns   |

|                                            | $C_L = 2.5 \text{ nF}$               |                          | -    | 31   | -   |      |

| Drive Output Fall Time (90% to 1           | 0%) C <sub>L</sub> = 1.0 nF          | t <sub>f</sub>           | -    | 16   | 30  | ns   |

|                                            | $C_{L} = 2.5 \text{ nF}$             |                          | -    | 32   | -   |      |

| TOTAL DEVICE                               |                                      |                          |      |      |     |      |

| Power Supply Current                       |                                      | I <sub>CC</sub>          |      |      |     | mA   |

| Standby (Logic Inputs Ground               | ed)                                  |                          | -    | 6.0  | 10  |      |

| Operating (C <sub>L</sub> = 1.0 nF Drive 0 | Dutputs 1 and 2, f = 100 kHz)        |                          | -    | 10.5 | 15  |      |

|                                            |                                      | V <sub>CC</sub>          | 6.5  |      | 18  | V    |

2. Maximum package power dissipation limits must be observed. 3.  $T_{low} = 0^{\circ}C$  for MC34151  $T_{high} = +70^{\circ}C$  for MC34151  $-40^{\circ}C$  for MC33151  $+85^{\circ}C$  for MC33151

5.0 V Logic Input  $t_r, t_f \leq 10 \text{ ns}$ 0 V  $t_{PHL}$ 90%  $t_{PLH}$   $t_{PLH}$   $t_{PLH}$  $t_{r}, t_{r} \leq 10^{\circ}$

Figure 2. Switching Characteristics Test Circuit

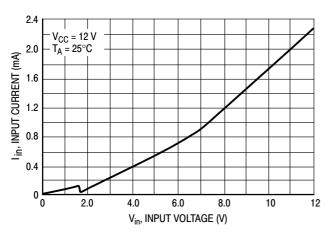

Figure 4. Logic Input Current versus Input Voltage

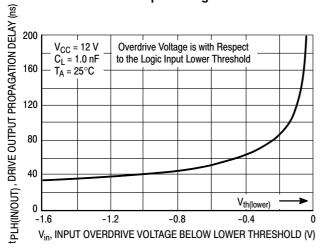

Figure 6. Drive Output Low-to-High Propagation Delay versus Logic Overdrive Voltage

Figure 3. Switching Waveform Definitions

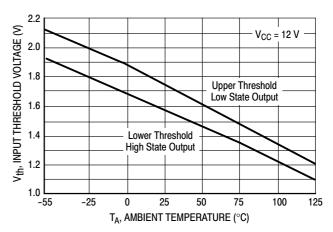

Figure 5. Logic Input Threshold Voltage versus Temperature

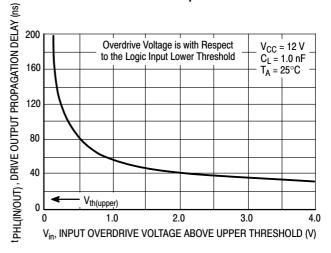

Figure 7. Drive Output High-to-Low Propagation Delay versus Logic Input Overdrive Voltage

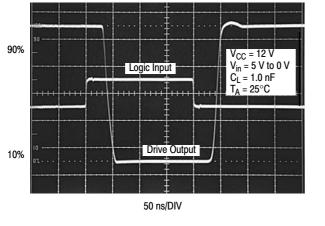

Figure 8. Propagation Delay

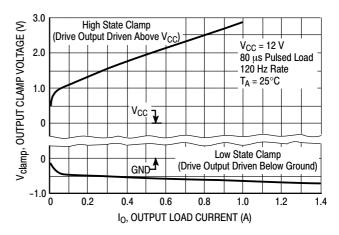

Figure 9. Drive Output Clamp Voltage versus Clamp Current

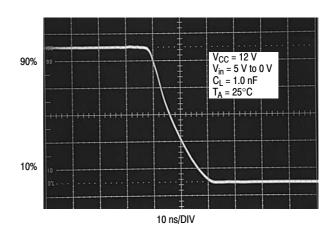

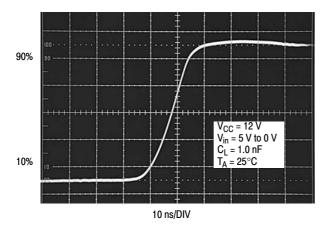

Figure 13. Drive Output Fall Time

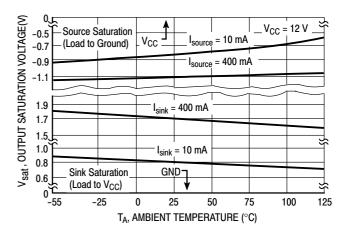

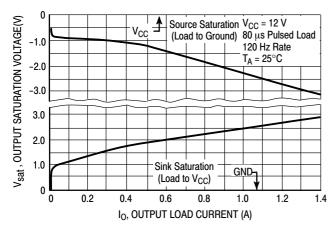

Figure 10. Drive Output Saturation Voltage versus Load Current

Figure 12. Drive Output Rise Time

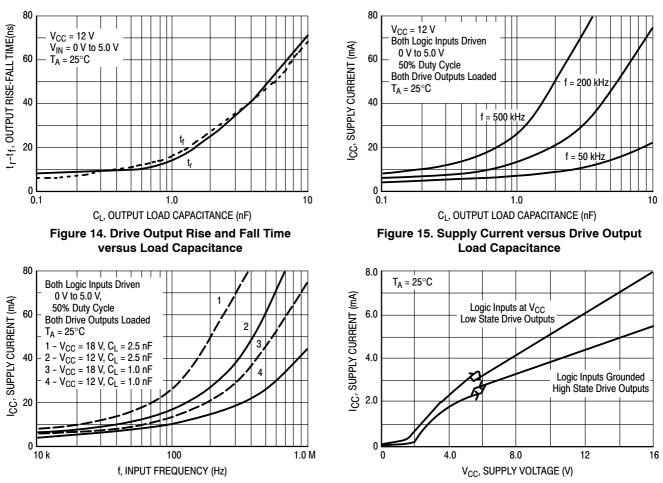

Figure 16. Supply Current versus Input Frequency

Figure 17. Supply Current versus Supply Voltage

#### Description

The MC34151 is a dual inverting high speed driver specifically designed to interface low current digital circuitry with power MOSFETs. This device is constructed with Schottky clamped Bipolar Analog technology which offers a high degree of performance and ruggedness in hostile industrial environments.

#### Input Stage

The Logic Inputs have 170 mV of hysteresis with the input threshold centered at 1.67 V. The input thresholds are insensitive to  $V_{CC}$  making this device directly compatible with CMOS and LSTTL logic families over its entire operating voltage range. Input hysteresis provides fast output switching that is independent of the input signal transition time, preventing output oscillations as the input thresholds are crossed. The inputs are designed to accept a signal amplitude ranging from ground to  $V_{CC}$ . This allows the output of one channel to directly drive the input of a second channel for master–slave operation. Each input has a 30 k $\Omega$  pulldown resistor so that an unconnected open input will cause the associated Drive Output to be in a known high state.

# Output Stage

**APPLICATIONS INFORMATION**

Each totem pole Drive Output is capable of sourcing and sinking up to 1.5 A with a typical 'on' resistance of 2.4  $\Omega$  at 1.0 A. The low 'on' resistance allows high output currents to be attained at a lower  $V_{CC}$  than with comparative CMOS drivers. Each output has a 100 k $\Omega$  pulldown resistor to keep the MOSFET gate low when  $V_{CC}$  is less than 1.4 V. No over current or thermal protection has been designed into the device, so output shorting to  $V_{CC}$  or ground must be avoided.

Parasitic inductance in series with the load will cause the driver outputs to ring above  $V_{CC}$  during the turn-on transition, and below ground during the turn-off transition. With CMOS drivers, this mode of operation can cause a destructive output latchup condition. The MC34151 is immune to output latchup. The Drive Outputs contain an internal diode to  $V_{CC}$  for clamping positive voltage transients. When operating with  $V_{CC}$  at 18 V, proper power supply bypassing must be observed to prevent the output ringing from exceeding the maximum 20 V device rating. Negative output transients are clamped by the internal NPN pullup transistor. Since full supply voltage is applied across

the NPN pullup during the negative output transient, power dissipation at high frequencies can become excessive. Figures 20, 21, and 22 show a method of using external Schottky diode clamps to reduce driver power dissipation.

#### **Undervoltage Lockout**

An undervoltage lockout with hysteresis prevents erratic system operation at low supply voltages. The UVLO forces the Drive Outputs into a low state as  $V_{CC}$  rises from 1.4 V to the 5.8 V upper threshold. The lower UVLO threshold is 5.3 V, yielding about 500 mV of hysteresis.

#### **Power Dissipation**

Circuit performance and long term reliability are enhanced with reduced die temperature. Die temperature increase is directly related to the power that the integrated circuit must dissipate and the total thermal resistance from the junction to ambient. The formula for calculating the junction temperature with the package in free air is:

where:

$T_J$  = Junction Temperature  $T_A$  = Ambient Temperature  $P_D$  = Power Dissipation

$T_J = T_A + P_D (R_{\theta JA})$

$R_{\theta JA}$  = Thermal Resistance Junction to Ambient

There are three basic components that make up total power to be dissipated when driving a capacitive load with respect to ground. They are:

where:

$P_{D} = P_Q + P_C + P_T$  $P_Q = Quiescent Power Dissipation$

$P_C$  = Capacitive Load Power Dissipation

$P_T$  = Transition Power Dissipation

The quiescent power supply current depends on the supply voltage and duty cycle as shown in Figure 17. The device's quiescent power dissipation is:

$$P_{Q} = V_{CC} \quad (I_{CCL} (1-D) + I_{CCH} (D))$$

where:

I<sub>CCL</sub> = Supply Current with Low State Drive Outputs

- I<sub>CCH</sub> = Supply Current with High State Drive Outputs

- D = Output Duty Cycle

The capacitive load power dissipation is directly related to the load capacitance value, frequency, and Drive Output voltage swing. The capacitive load power dissipation per driver is:

$\begin{array}{rcl} P_{C} = & V_{CC} \left( V_{OH} - V_{OL} \right) C_{L} f \\ \text{where:} & V_{OH} = & \text{High State Drive Output Voltage} \\ & V_{OL} = & \text{Low State Drive Output Voltage} \\ & C_{L} = & \text{Load Capacitance} \\ & f = & \text{frequency} \end{array}$

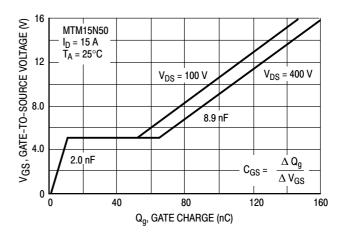

When driving a MOSFET, the calculation of capacitive load power  $P_C$  is somewhat complicated by the changing gate to source capacitance  $C_{GS}$  as the device switches. To aid in this calculation, power MOSFET manufacturers provide

gate charge information on their data sheets. Figure 18 shows a curve of gate voltage versus gate charge for the ON Semiconductor MTM15N50. Note that there are three distinct slopes to the curve representing different input capacitance values. To completely switch the MOSFET 'on', the gate must be brought to 10 V with respect to the source. The graph shows that a gate charge  $Q_g$  of 110 nC is required when operating the MOSFET with a drain to source voltage  $V_{DS}$  of 400 V.

Figure 18. Gate-To-Source Voltage versus Gate Charge

The capacitive load power dissipation is directly related to the required gate charge, and operating frequency. The capacitive load power dissipation per driver is:

$$P_{C(MOSFET)} = V_C Q_g f$$

The flat region from 10 nC to 55 nC is caused by the drain-to-gate Miller capacitance, occurring while the MOSFET is in the linear region dissipating substantial amounts of power. The high output current capability of the MC34151 is able to quickly deliver the required gate charge for fast power efficient MOSFET switching. By operating the MC34151 at a higher  $V_{CC}$ , additional charge can be provided to bring the gate above 10 V. This will reduce the 'on' resistance of the MOSFET at the expense of higher driver dissipation at a given operating frequency.

The transition power dissipation is due to extremely short simultaneous conduction of internal circuit nodes when the Drive Outputs change state. The transition power dissipation per driver is approximately:

> $P_T = V_{CC}$  (1.08  $V_{CC}$  C<sub>L</sub> f – 8 y 10<sup>-4</sup>)  $P_T$  must be greater than zero.

Switching time characterization of the MC34151 is performed with fixed capacitive loads. Figure 14 shows that for small capacitance loads, the switching speed is limited by transistor turn–on/off time and the slew rate of the internal nodes. For large capacitance loads, the switching speed is limited by the maximum output current capability of the integrated circuit.

# LAYOUT CONSIDERATIONS

High frequency printed circuit layout techniques are imperative to prevent excessive output ringing and overshoot. **Do not attempt to construct the driver circuit on wire-wrap or plug-in prototype boards.** When driving large capacitive loads, the printed circuit board must contain a low inductance ground plane to minimize the voltage spikes induced by the high ground ripple currents. All high current loops should be kept as short as possible using heavy copper runs to provide a low impedance high frequency path. For

The MC34151 greatly enhances the drive capabilities of common switching regulators and CMOS/TTL logic devices.

#### Figure 19. Enhanced System Performance with Common Switching Regulators

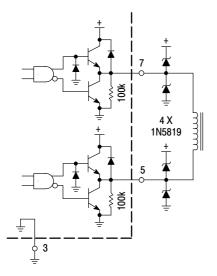

Output Schottky diodes are recommended when driving inductive loads at high frequencies. The diodes reduce the driver's power dissipation by preventing the output pins from being driven above  $V_{CC}$  and below ground.

#### Figure 21. Direct Transformer Drive

optimum drive performance, it is recommended that the initial circuit design contains dual power supply bypass capacitors connected with short leads as close to the  $V_{CC}$  pin and ground as the layout will permit. Suggested capacitors are a low inductance 0.1  $\mu$ F ceramic in parallel with a 4.7  $\mu$ F tantalum. Additional bypass capacitors may be required depending upon Drive Output loading and circuit layout.

Proper printed circuit board layout is extremely critical and cannot be over emphasized.

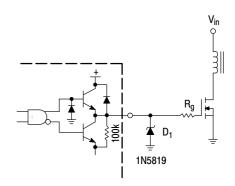

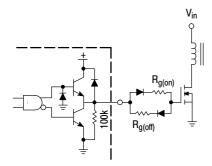

Series gate resistor  $R_g$  may be needed to damp high frequency parasitic oscillations caused by the MOSFET input capacitance and any series wiring inductance in the gate-source circuit.  $R_g$  will decrease the MOSFET switching speed. Schottky diode  $\mathsf{D}_1$  can reduce the driver's power dissipation due to excessive ringing, by preventing the output pin from being driven below ground.

#### Figure 20. MOSFET Parasitic Oscillations

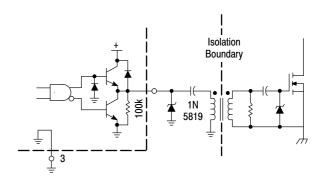

#### Figure 22. Isolated MOSFET Drive

In noise sensitive applications, both conducted and radiated EMI can be reduced significantly by controlling the MOSFET's turn-on and turn-off times.

# Figure 23. Controlled MOSFET Drive

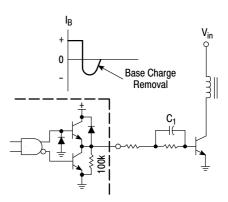

The totem-pole outputs can furnish negative base current for enhanced transistor turn-off, with the addition of capacitor  $C_{1.}$

Figure 24. Bipolar Transistor Drive

The capacitor's equivalent series resistance limits the Drive Output Current to 1.5 A. An additional series resistor may be required when using tantalum or other low ESR capacitors.

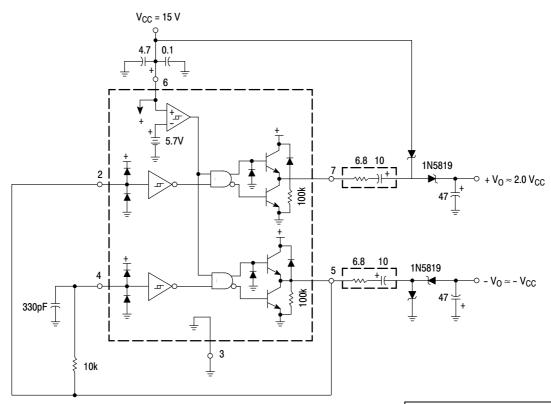

Figure 25. Dual Charge Pump Converter

| Output Load Regulation |                     |                     |  |

|------------------------|---------------------|---------------------|--|

| I <sub>O</sub> (mA)    | +V <sub>0</sub> (V) | -V <sub>0</sub> (V) |  |

| 0                      | 27.7                | -13.3               |  |

| 1.0                    | 27.4                | -12.9               |  |

| 10                     | 26.4                | -11.9               |  |

| 20                     | 25.5                | -11.2               |  |

| 30                     | 24.6                | -10.5               |  |

| 50                     | 22.6                | -9.4                |  |

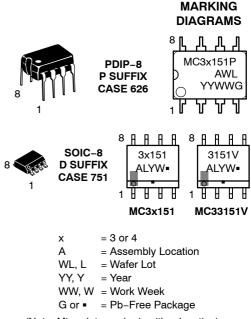

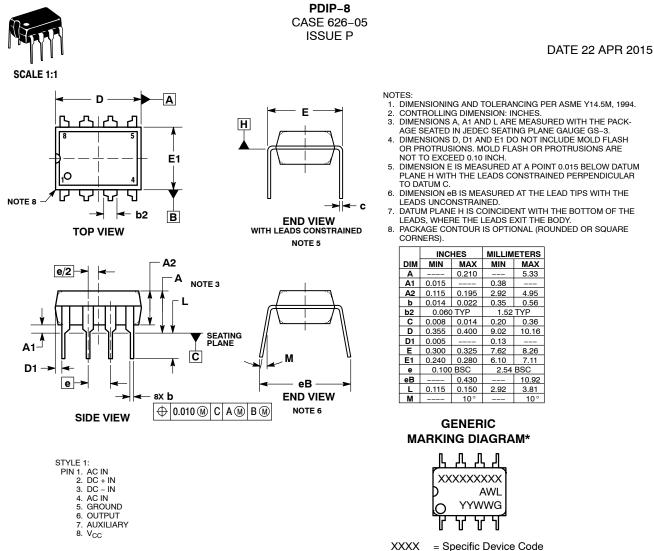

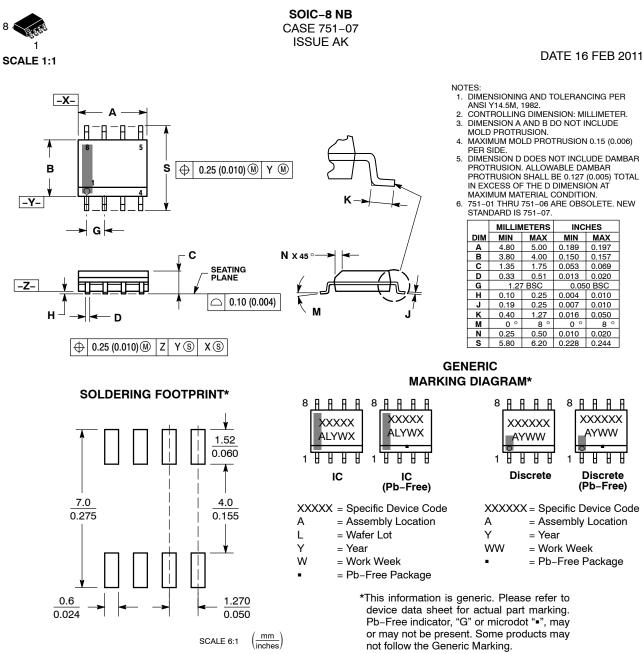

# **ORDERING INFORMATION**

| Device       | Package             | Shipping <sup>†</sup> |

|--------------|---------------------|-----------------------|

| MC34151DG    | SOIC-8<br>(Pb-Free) | 98 Units / Rail       |

| MC34151DR2G  | SOIC-8<br>(Pb-Free) | 2500 Tape & Reel      |

| MC34151PG    | PDIP-8<br>(Pb-Free) | 50 Units / Rail       |

| MC33151DG    | SOIC-8<br>(Pb-Free) | 98 Units / Rail       |

| MC33151DR2G  | SOIC-8<br>(Pb-Free) | 2500 Tape & Reel      |

| MC33151PG    | PDIP-8<br>(Pb-Free) | 50 Units / Rail       |

| MC33151VDR2G | SOIC-8<br>(Pb-Free) | 2500 Tape & Reel      |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

A = Assembly Location

- WL = Wafer Lot

- YY = Year

- WW = Work Week G = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ■", may or may not be present.

© Semiconductor Components Industries, LLC, 2019

# onsemí

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

# STYLES ON PAGE 2

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 98ASB42564B      | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PTION: SOIC-8 NB |                                                                                                                                                                                     | PAGE 1 OF 2 |  |  |

| onsemi and ONSEMi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights or the rights of others. |                  |                                                                                                                                                                                     |             |  |  |

#### SOIC-8 NB CASE 751-07 **ISSUE AK**

ŝ

ę

ŝ

S

STYLE 1: PIN 1. EMITTER COLLECTOR 2. COLLECTOR З. 4. EMITTER EMITTER 5. BASE 6. 7 BASE EMITTER 8. STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN DRAIN 4. GATE 5. 6. GATE SOURCE 7. 8. SOURCE STYLE 9: PIN 1. EMITTER, COMMON COLLECTOR, DIE #1 COLLECTOR, DIE #2 2. З. EMITTER, COMMON 4. 5. EMITTER, COMMON 6 BASE, DIE #2 BASE, DIE #1 7. 8. EMITTER, COMMON STYLE 13: PIN 1. N.C. 2. SOURCE 3 GATE 4. 5. DRAIN 6. DRAIN DRAIN 7. DRAIN 8. STYLE 17: PIN 1. VCC 2. V2OUT V10UT З. TXE 4. 5. RXE 6. VFF 7. GND 8. ACC STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3 CATHODE 3 CATHODE 4 4. 5. CATHODE 5 6. COMMON ANODE COMMON ANODE 7. 8. CATHODE 6 STYLE 25: PIN 1. VIN 2 N/C З. REXT 4. GND 5. IOUT 6. IOUT IOUT 7. 8. IOUT STYLE 29: BASE, DIE #1 PIN 1. 2 EMITTER, #1 BASE, #2 З. EMITTER, #2 4. 5 COLLECTOR, #2 COLLECTOR, #2

STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 COLLECTOR, #2 3. 4 COLLECTOR, #2 BASE, #2 5. EMITTER, #2 6. 7 BASE #1 EMITTER, #1 8. STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN SOURCE 4. SOURCE 5. 6. GATE GATE 7. 8. SOURCE STYLE 10: GROUND PIN 1. BIAS 1 OUTPUT 2. З. GROUND 4. 5. GROUND 6. BIAS 2 INPUT 7. 8. GROUND STYLE 14: PIN 1. N-SOURCE 2. N-GATE P-SOURCE 3 P-GATE 4. P-DRAIN 5. 6. P-DRAIN N-DRAIN 7. N-DRAIN 8. STYLE 18: PIN 1. ANODE 2. ANODE SOURCE 3. GATE 4. 5. DRAIN 6 DRAIN CATHODE 7. CATHODE 8. STYLE 22: PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC COMMON CATHODE/VCC 3 I/O LINE 3 4. 5. COMMON ANODE/GND 6. I/O LINE 4 7. I/O LINE 5 COMMON ANODE/GND 8. STYLE 26: PIN 1. GND 2 dv/dt ENABLE З. 4. ILIMIT 5. SOURCE SOURCE 6. SOURCE 7. 8. VCC STYLE 30: PIN 1. DRAIN 1 2. DRAIN 1 GATE 2 З. SOURCE 2 4. SOURCE 1/DRAIN 2 SOURCE 1/DRAIN 2 5. 6.

| 2.  <br>3.  <br>4.  <br>5.  <br>6.  <br>7.                  | DRAIN, DIE #1<br>DRAIN, #1<br>DRAIN, #2<br>DRAIN, #2<br>GATE, #2<br>GATE, #2<br>GATE, #1<br>SOURCE, #1                                  |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 2.  <br>3<br>4. (<br>5.  <br>6. (<br>7. )                   | NPUT<br>EXTERNAL BYPASS<br>THIRD STAGE SOURCE<br>GROUND<br>DRAIN<br>SATE 3<br>SECOND STAGE Vd<br>FIRST STAGE Vd                         |

| 2. (<br>3. 5<br>4. (<br>5. 1<br>6. 1<br>7. 1                | Source 1<br>Gate 1<br>Source 2<br>Gate 2<br>Drain 2<br>Drain 2<br>Drain 1<br>Drain 1                                                    |

| 2. /<br>3. /<br>4. /<br>5. ()<br>6. ()<br>7. ()             | NODE 1<br>NODE 1<br>NODE 1<br>NODE 1<br>SATHODE, COMMON<br>SATHODE, COMMON<br>SATHODE, COMMON                                           |

| 2.<br>3.<br>4.<br>5.<br>6.<br>7.<br>8.                      | SOURCE 1<br>GATE 1<br>SOURCE 2<br>GATE 2<br>DRAIN 2<br>MIRROR 2<br>DRAIN 1<br>MIRROR 1                                                  |

| 2.<br>3.<br>4.<br>5.<br>6.<br>7.                            | :<br>Line 1 in<br>Common Anode/Gnd<br>Common Anode/Gnd<br>Line 2 in<br>Line 2 out<br>Common Anode/Gnd<br>Common Anode/Gnd<br>Line 1 out |

| STYLE 2<br>PIN 1.<br>2.<br>3.<br>4.<br>5.<br>6.<br>7.<br>8. | 7:<br>ILIMIT<br>OVLO<br>UVLO<br>IINPUT+<br>SOURCE<br>SOURCE<br>SOURCE<br>DRAIN                                                          |

#### DATE 16 FEB 2011

STYLE 4: PIN 1. 2. ANODE ANODE ANODE З. 4. ANODE ANODE 5. 6. ANODE 7 ANODE COMMON CATHODE 8. STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 BASE #2 3. COLLECTOR, #2 4. COLLECTOR, #2 5. 6. EMITTER, #2 EMITTER, #1 7. 8. COLLECTOR, #1 STYLE 12: PIN 1. SOURCE SOURCE 2. 3. GATE 4. 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 16: PIN 1. EMITTER, DIE #1 2. BASE, DIE #1 EMITTER, DIE #2 3 BASE, DIE #2 4. 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 COLLECTOR, DIE #1 7. COLLECTOR, DIE #1 8. STYLE 20: PIN 1. SOURCE (N) GATE (N) SOURCE (P) 2. 3. 4. GATE (P) 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 24: PIN 1. BASE EMITTER 2. 3 COLLECTOR/ANODE COLLECTOR/ANODE 4. 5. CATHODE 6. CATHODE COLLECTOR/ANODE 7. 8. COLLECTOR/ANODE STYLE 28: PIN 1. SW\_TO\_GND 2. DASIC OFF DASIC\_SW\_DET 3. 4. GND 5. 6. V MON VBULK 7. VBULK 8 VIN

| DOCUMENT NUMBER:                                                                                                                                                         | 98ASB42564B Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |             |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|--|

| DESCRIPTION:                                                                                                                                                             | SOIC-8 NB                                                                                                                                                                                       |  | PAGE 2 OF 2 |  |

| onsemi and ONSEMi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves |                                                                                                                                                                                                 |  |             |  |

SOURCE 1/DRAIN 2

7.

8 GATE 1

the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

6.

7.

8

COLLECTOR, #1

COLLECTOR, #1

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent\_Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at <u>www.onsemi.com/support/sales</u>