# Platform Manager 2 Evaluation Board User Guide

EB93 Version 1.0, June 2015

### Introduction

Thank you for choosing the Lattice Semiconductor Platform Manager 2 Evaluation Board!

The Platform Manager 2 evaluation board is used to demonstrate, evaluate and design using the Platform Manager 2 (LPTM21) device and the Hardware Management Expander (L-ASC10) device. The board is pre-programmed with a demo design that highlights the features and flexibility of the LPTM21 and L-ASC10 devices. This demo operates on the board without any other software or hardware as described in the **QuickSTART Guide** that is included with the board. However, a more complete evaluation can be accomplished using the I<sup>2</sup>C demo / debugging software which is available from the Lattice website. This software and the demo design can be used to evaluate the following features provided by the Platform Manager 2 devices: Power Management (Power Sequencing, Voltage Monitoring, Trimming, Margining), Thermal Management (Temperature Monitoring, Fan Control, Power Control) and Control Plane (Reset Control, Fault Logging). The use of the software with the demo design is fully described in the user guide which is included with the software zip file: UG59, *Platform Manager 2 PC Demo Design and GUI User's Guide*.

### The QuickSTART Guide

Please use the Platform Manager 2 Board QuickSTART Guide to get started. The QuickSTART Guide provides a "fast path" for working with the Platform Manager 2 evaluation board and the pre-programmed demo. This user's guide augments the QuickSTART Guide by providing detailed descriptions of the on board circuits that support both the demo and customer evaluation designs.

#### **Features**

The Platform Manager 2 evaluation board has been designed to demonstrate and evaluate the following applications:

- Supply Voltage monitoring, sequencing, trimming, VID, and control.

- Current sensing, monitoring and control.

- Temperature sensing, monitoring and control.

- 3-Wire, 4 Wire Fan Control.

- · Fault logging to internal UFM or external SPI Flash.

- Scalable monitoring and control of voltages, currents, temperatures.

- · Field upgrades via background programming and dual boot.

- · GPIO control and expansion.

The Platform Manager 2 evaluation board also allows the user to quickly learn, evaluate, develop and test their own designs using the LPTM21, L-ASC10 and surrounding circuits and components.

The Platform Manager 2 evaluation board contains the following on-board components and circuits to support the demo design and customer developed designs:

#### Integrated Circuits

- LPTM21 FTBGA-237 Platform Manager 2 [U1]

- L-ASC10 QFN-48 Hardware Expander [U4]

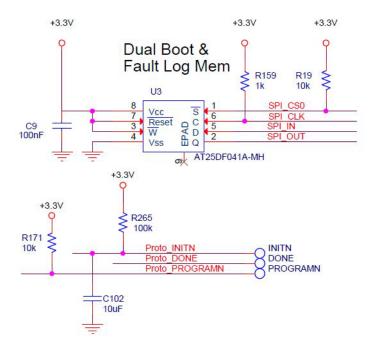

- AT25DF041AMH -SPI Flash Memory [U3]

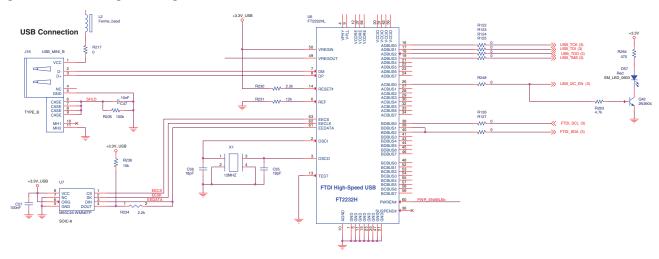

- FT2232HL- USB Driver [U6]

- 93C46-WMN6TP EEPROM Memory [U7]

- NCP1117-LDO [U8]

- LD6836-LDO [U9]

- FSA4157 Analog Switch-SPDT [U10, U11]

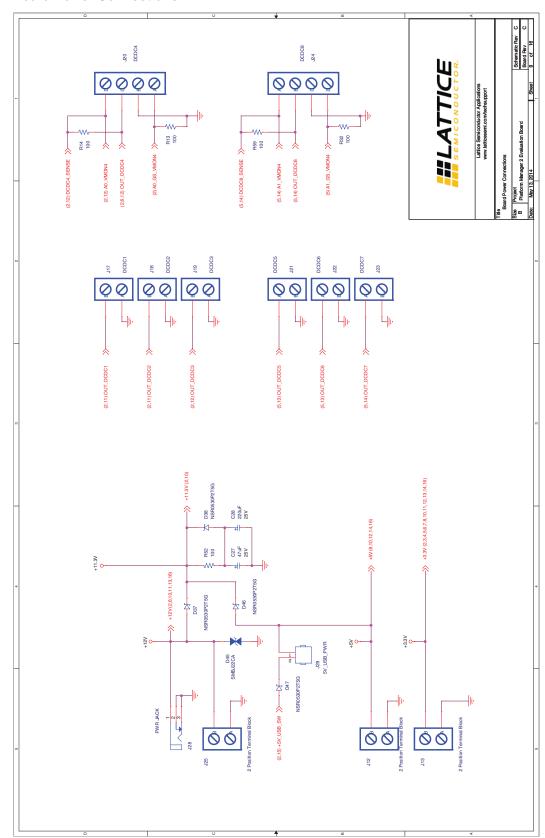

### Power Supplies, Connections and Switches

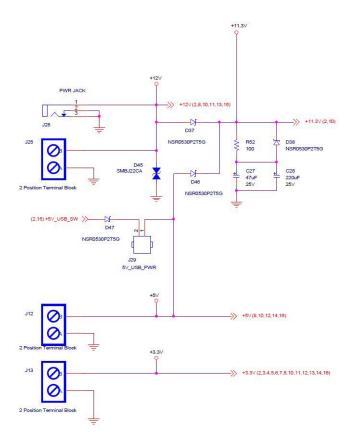

- External 12 V Supply Connector –Coaxial Power Jack [J28]

- External 12 V Supply Connector Two position Terminal [J25]

- External 5 V Supply Connector Two position Terminal [J12]

- External 3 V Supply Connector Two position Terminal [J13]

- +5 V to 2.5 V Trim-able DCDC Converter [DCDC3, DCDC7]

- +5 V to 1.2 V Trim-able DCDC Converter [DCDC4, DCDC8]

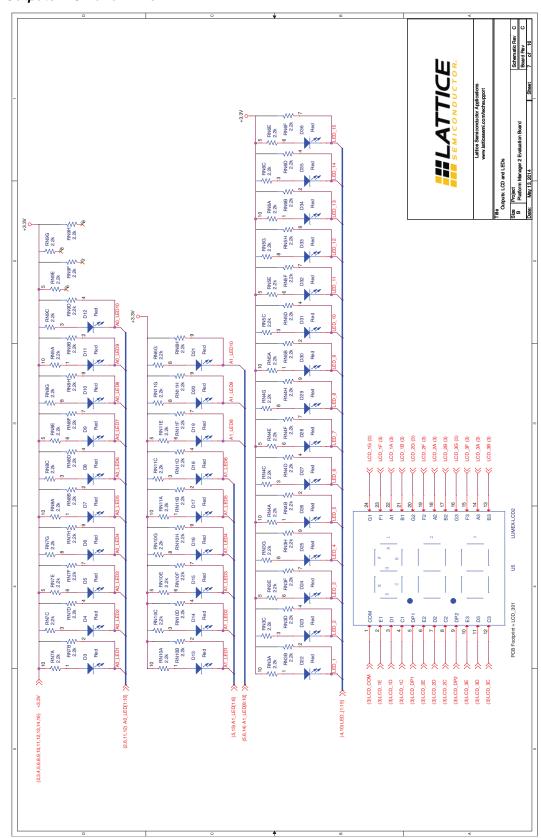

#### LEDs and LCD Display

- Blue USB Power LED [D42]

- Green +3.3 V Power LED [D44]

- Red LPTM21 (U1 ASC) Output LEDs [D3-D12]

- Red LPTM21 (U1 FPGA) Output LEDs[D22-D36]

- Red L-ASC10 (U4) Output LEDs [D13-D21]

- 3-Digit LCD Display [U5]

- Red ASC # 2 Interface Power LED [D39]

- Red ASC # 3 Interface Power LED [D40]

- Green DC-DC # 3 Power LED [D51]

- Green DC-DC # 4 Power LED [D52]

- Green DC-DC # 7 Power LED [D55]

- Green DC-DC # 8 Power LED [D56]

## • Switches, Sliders, Buttons, Sensors and Jumpers

- VID\_A 8-position DIP Switch [SW6]

- Restart Push Button Switch [SW4]

- Demo control Push Button Switch [SW1-SW3, SW5]

- Slide Potentiometer [R34, R36, R39, R41]

- Temperature Sensor [Q4, Q6, Q7]

- Temperature Sensor [Q5-with artificial load power resistor]

- 3.3 V supply select Jumper [J1, J3, J4]

- Reset select Jumper [J5]

- Fan Supply Select [J6, J8]

- Enable ASC program Jumper [J31, J32]

- MOSFET Drive Select [J30]

- 5 V supply select jumper [J29]

#### Connectors and Interfaces

- JTAG connector [J2]

- I<sup>2</sup>C/SPI connector [J26]

- External FAN connectors [J7, J9, J10, J11]

- Two Position Screw connector for off board load for DCDC3 and DCDC7 [J19, J23]

- Four position screw connector for off board load for DCDC4 and DCDC8 [J20, J24]

- USB B-mini Connector [J16]

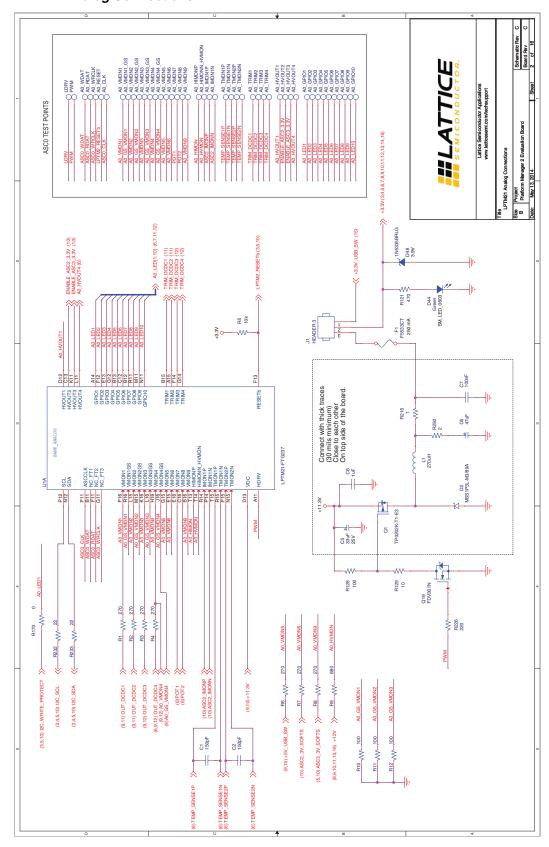

- DSUB 25 Expandable Architecture Connectors for ASC Breakout Board [J14, J15]

- Probe and Test Points

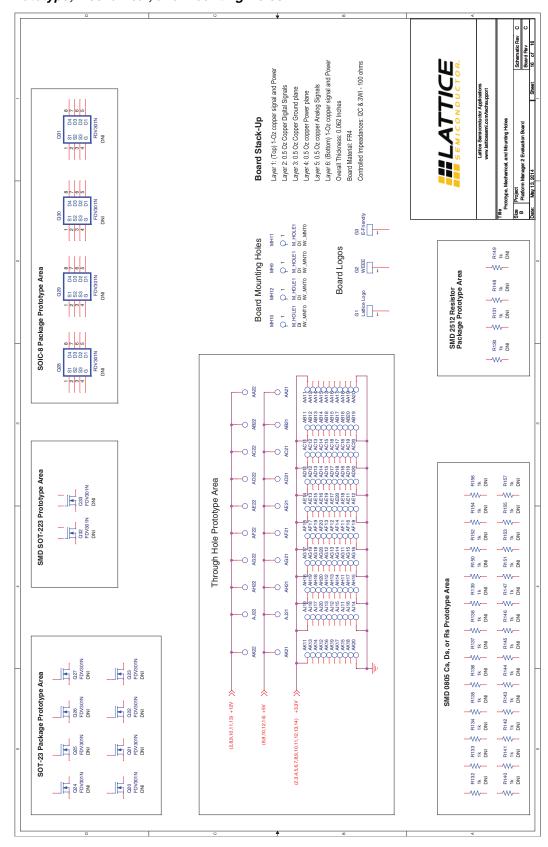

#### User Prototyping Area

- 12 x 10 through-Hole array with +12 V, +5 V, +3.3 V, and GND buses

- 24 SMD 0805 footprints

- 8 SMD SOT-23 footprints

- 4 SMD 2512 footprints

- 4 SMD SOIC-8 footprints

- 2 SMD SOT-223 footprints

# **Mechanical Specifications**

Dimensions: 7 in. [L] x 6 in. [W] x 1 in. [H]

# **Environmental Specifications**

The evaluation board must be stored between -40 °C and 100 °C. The recommended operating temperature is between 0 °C and 55 °C.

# **Electrical Specifications**

- 12 V Input +/- 15% @ 50 mA typical.

- 5 V Input +/- 10% @ 110 mA typical.

- 3.3 V Input +/- 5% @ 150 mA typical.

- 12 V Maximum Current 10 A when using an off board supply and load.

- 5 V Maximum Current 10 A when using an off board supply and load.

- 3.3 V Maximum Current 5 A when using an off board supply and load.

# **Software Requirements**

The pre-loaded demo design on the Platform Manager 2 evaluation board can operate without the need to install any special software and can be powered using any standard USB port. All control and status information is available on the board using switches, push-buttons, potentiometers, LEDs and the LCD display, as described in the QuickSTART Guide that was mentioned in the introduction. In order to create and program custom designs or program reference or demo designs, Lattice Diamond 3.4 or later software is required along with a corresponding license. Within Lattice Diamond<sup>®</sup>, Platform Designer is a custom tool that is used to create, edit, and build Platform Manager 2 designs.

# **Platform Designer Tool-Software**

The Platform Designer tool provides an integrated design environment that simplifies building and editing Platform Manager 2 designs. It supports all of the following and more: implement the hardware management algorithm, check design rules, compile the design, generate stimulus files, simulate the design, assign pins, and finally generate the JEDEC files used to program and configure the device on the circuit board. Platform Designer also supports the importing of an HDL file to integrate other desired functions.

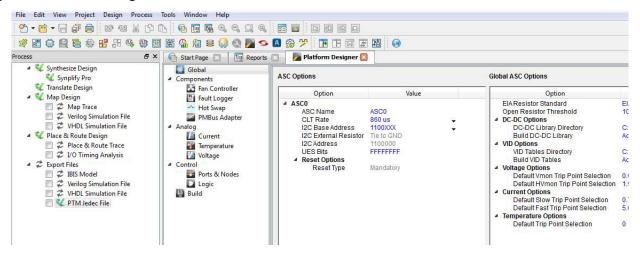

Figure 1. Platform Designer Software

As shown in Figure 1, the Platform Designer tool contains five main sections: Global, Analog, Components, Control, and Build. Each of the five sections is briefly described below.

- Global ASC Options and Device Options views are used for configuring global settings for the ASC and the

device.

- Analog Current, Temperature, and Voltage views are used for configuring the built-in monitoring circuits for these signals.

- Components Fan Controller, Fault Logger, Hot Swap, and PMBus Adapter views are used to configure and instantiate built-in IPs for these functions.

- Control Ports and Nodes and Logic views are used to name and assign I/O for the design; and to develop and/ or import the control logic.

- Build DRC, Compile, Pin Assignment, Generate Jedec, Generate Stimulus, and Export Configuration Report buttons are used for checking design rules, and building the design. A summary view shows the usage and consumption of the design resources available.

# Platform Manager 2 I<sup>2</sup>C GUI - Software

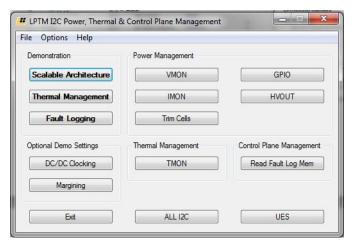

The Platform Manager 2 I<sup>2</sup>C GUI software and User's Guide can be downloaded from the Lattice website. This software is provided license free and is used to enhance the demo experience and as a hardware debugging tool; the main interface is shown in Figure 2. The Demonstration buttons are used in conjunction with the default demo. The Power Management, Thermal Management, and Control Plane Management buttons can be used independently of the demo and can also be used with customer board designs (provided an FTDI based USB to I<sup>2</sup>C interface is used).

Figure 2. Platform Manager 2 I'C GUI Software

# **Platform Manager 2 Evaluation Board**

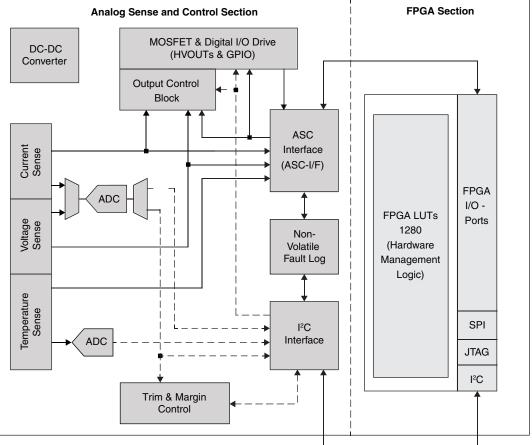

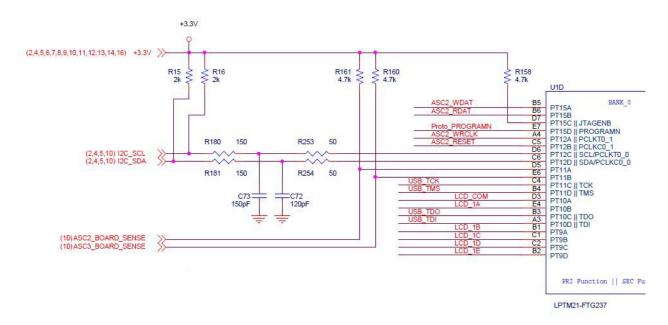

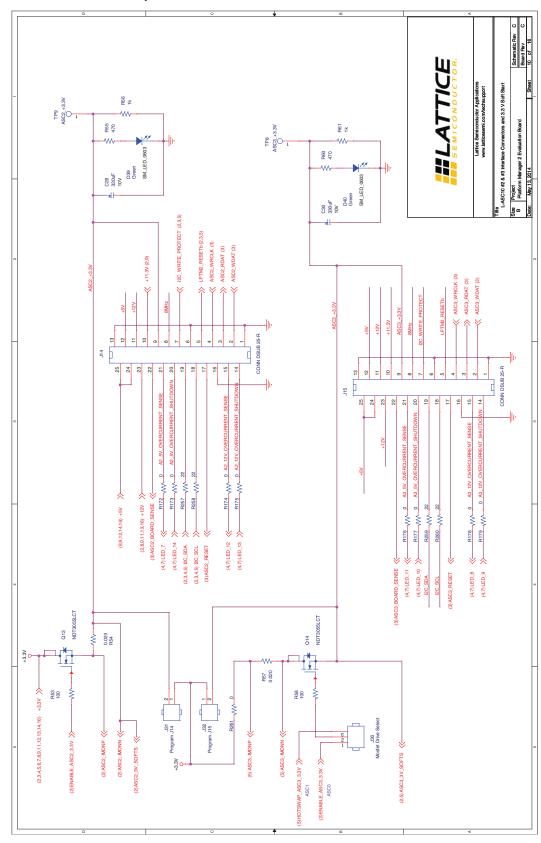

### LPTM21-Platform Manager 2-Device

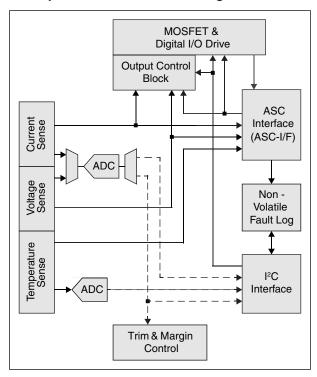

As shown in Figure 3, the Lattice Platform Manager 2 device is a fast-reacting, programmable logic based hardware management controller. Platform Manager 2 is an integrated solution combining analog sense and control elements with scalable programmable logic resources. This unique approach allows Platform Manager 2 to integrate Power Management (Power Sequencing, Voltage Monitoring, Trimming and Margining), Thermal Management (Temperature Monitoring, Fan Control, Power Control), and Control Plane functions (System Configuration, I/O Expansion, etc.) as a single device.

Architecturally, the Platform Manager 2 device can be divided into two sections – Analog Sense and Control and FPGA. The Analog Sense and Control (ASC) section provides three types of analog sense channels: voltage (nine

standard channels and one high voltage channel), current (one standard voltage and one high voltage) and temperature (two external and one internal).

Each of the analog sense channels is monitored through two independently programmable comparators to support both high/low and in-bounds/out-of-bounds (window-compare) monitor functions. In addition, each of the current sense channels provides a fast fault detect (one µs response time) for detecting short circuit events. The temperature sense channels can be configured to work with different external transistor or diode configurations.

The Analog Sense and Control section also provides ten general purpose 5 V tolerant open-drain digital input/out-put pins that can be used for controlling DC-DC converters, low-drop-out regulators (LDOs) and opto-couplers, as well as for general purpose logic interface functions. In addition, four high-voltage charge pumped outputs (HVOUT1-HVOUT4) may be configured as high-voltage MOSFET drivers to control high-side MOSFET switches. These HVOUT outputs can also be programmed as static output signals or as switched outputs (to support external charge pump implementation) operating at a dedicated duty cycle and frequency.

The ASC section incorporates four TRIM outputs for controlling the output voltages of DC-DC converters. Each power supply output voltage can be maintained typically within 0.5% tolerance across various load conditions using the Digital Closed Loop Control mode of the trimming block.

The internal 10-bit A/D converter can be used to measure the voltage and current through the I<sup>2</sup>C bus. The ADC is also used in the digital closed loop control mode of the trimming block.

The ASC section also provides the capability of logging up to 16 status records into its nonvolatile EEPROM memory. Each record includes voltage, current and temperature monitor signals along with digital input and output levels.

The ASC section includes an output control block (OCB) which allows certain inputs and control signals a direct connection to the digital outputs or HVOUTs, bypassing the ASC-I/F for a faster response. The OCB is used to connect the fast current fault detect signal to an FPGA input directly. It also supports functions such as Hot Swap with a programmable hysteretic controller.

The FPGA section contains non-volatile low cost programmable logic of 1280 Look-Up Tables (LUTs). In addition to the LUT-based logic, the FPGA section features Embedded Block RAM (EBR), Distributed RAM, User Flash Memory (UFM), flexible I/Os, and hardened versions of commonly used functions such as SPI controller, I<sup>2</sup>C controller and Timer/counter. The FPGA I/Os offer enhanced features such as drive strength control, slew rate control, buskeeper latches, internal pull-up or pull-down resistors, and open-drain outputs. These features are controllable on a "per-pin" basis.

The power management, thermal management and control plane logic functions are implemented in the FPGA section of Platform Manager 2. The FPGA receives the analog comparator values and inputs from the ASC section and sends output commands to the ASC section through the dedicated ASC-interface (ASC-I/F) high-speed, reliable serial channel. The FPGA hardware management functions are implemented using the Platform Designer tool inside Lattice Diamond software. The Platform Designer tool includes an easy to use sequence and monitor logic builder tool and a set of pre-engineered components for functions like time-stamped fault logging, voltage by identification (VID), and fan control.

The Platform Manager 2 is designed to enable seamless scaling of the number of voltage, current and temperature sense channels in the system by adding external Analog Sense and Control (ASC) Hardware Management Expanders. The algorithm implemented within the FPGA can access and control these external ASCs through the dedicated ASC-I/F. Larger systems with up to eight ASC devices can be created by using a MachXO2 FPGA in place of the Platform Manager 2 device. The companion devices are connected in a scalable, star topology to Platform Manager 2 or MachXO2.

The Platform Manager 2 has an I<sup>2</sup>C interface which is used by the FPGA section for ASC interface configuration. The I<sup>2</sup>C interface also provides the mechanism for parameter measurement or I/O control or status. For example, voltage trim targets can be set over the I<sup>2</sup>C bus and measured voltage, current, or temperature values can be read over the I<sup>2</sup>C bus.

The Platform Manager 2 device can be programmed in-system through JTAG or I<sup>2</sup>C interfaces. The configuration is stored in on-chip non-volatile memory. Upon power-on, the FPGA section configuration is transferred to the on-chip SRAM and the device operates from SRAM. It is possible to update the non-volatile memory content in the background without interrupting the system operation. For additional details please see DS1043, Platform Manager 2 Data Sheet.

Figure 3. Platform Manager 2 Block Diagram

Analog Sense and Contr

# L-ASC10-Hardware Expander-Device

As shown in Figure 4, The L-ASC10 (Analog Sense and Control - 10 rail) is a Hardware Management (Power, Thermal, and Control Plane Management) Expander designed to be used with Platform Manager 2 or MachXO2 FPGAs to implement the Hardware Management Control function in a circuit board. The L-ASC10 (referred to as ASC) enables seamless scaling of power supply voltage and current monitoring, temperature monitoring, sequence and margin control channels. The ASC includes dedicated interfaces supporting the exchange of monitor signal status and output control signals with these centralized hardware management controllers. Up to eight ASC devices can be used to implement a hardware management system.

The ASC provides three types of analog sense channels: voltage (nine standard channels and one high voltage channel), current (one standard voltage and one high voltage), and temperature (two external and one internal) as shown in Figure 2.

Each of the analog sense channels is monitored through two independently programmable comparators to support both high/low and in-bounds/out-of-bounds (window-compare) monitor functions. The current sense channels feature a programmable gain amplifier and a fast fault detect (<1 µs response time) for detecting short circuit events. The temperature sense channels can be configured to work with different external transistor or diode configurations.

Nine general purpose 5 V tolerant open-drain digital input/output pins are provided that can be used in a system for controlling DC-DC converters, low-drop-out regulators (LDOs) and optocouplers, as well as for supervisory and general purpose logic interface functions. Four high-voltage charge pumped outputs (HVOUT1-HVOUT4) may be configured as high-voltage MOSFET drivers to control high-side MOSFET switches. These HVOUT outputs can also be programmed as static output signals or as switched outputs (to support external charge pump implementation) operating at a dedicated duty cycle and frequency.

The ASC device incorporates four TRIM outputs for controlling the output voltages of DC-DC converters. Each power supply output voltage can be maintained typically within 0.5% tolerance across various load conditions using the Digital Closed Loop Control mode.

The internal 10-bit A/D converter can be used to monitor the voltage and current through the I<sup>2</sup>C bus. The ADC is also used in the digital closed loop control mode of the trimming block.

The ASC also provides the capability of logging up to 16 status records into the on-chip nonvolatile EEPROM memory. Each record includes voltage, current and temperature monitor signals along with digital input and output levels.

The dedicated ASC Interface (ASC-I/F) is a reliable serial channel used to communicate with a Platform Manager 2 or a MachXO2 FPGA in a scalable star topology. The centralized control algorithm in the FPGA monitors signal status and controls output behavior via this ASC-I/F. The ASC I<sup>2</sup>C interface is used by the FPGA or an external microcontroller for ASC background programming, interface configuration, and additional data transfer such as parameter measurement or I/O control or status. For example, voltage trim targets can be set over the I<sup>2</sup>C bus and measured voltage, current, or temperature values can be read over the I<sup>2</sup>C bus.

The ASC also includes an on-chip output control block (OCB) which allows certain alarms and control signals a direct connection to the GPIOs or HVOUTs, bypassing the ASC-I/F for a faster response. The OCB is used to connect the fast current fault detect signal to an FPGA input directly. It also supports functions like Hot Swap with a programmable hysteretic controller. For additional details please see DS1042, L-ASC10 Data Sheet.

Figure 4. Hardware Management Expander L-ASC10 Block Diagram

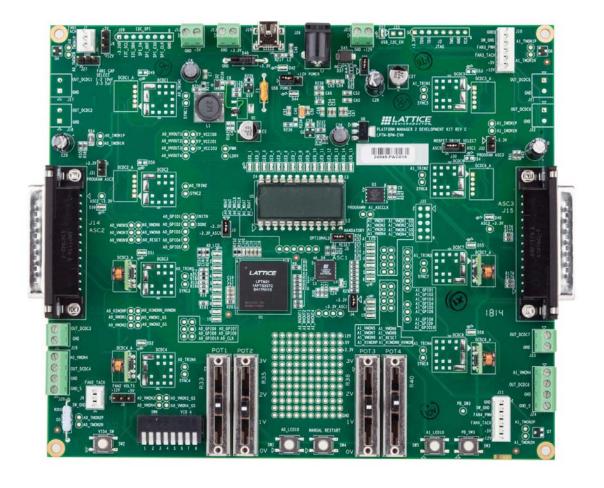

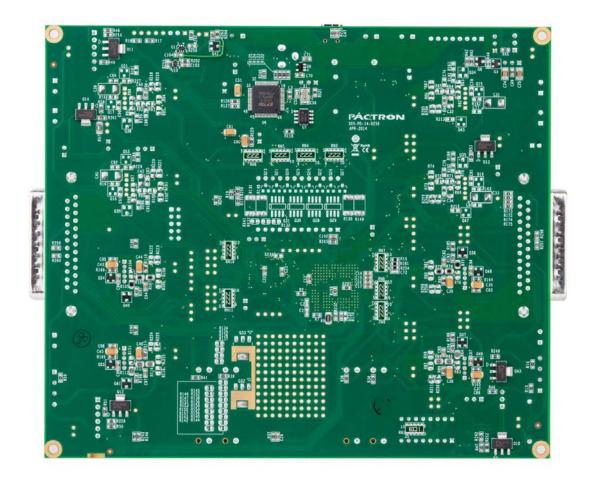

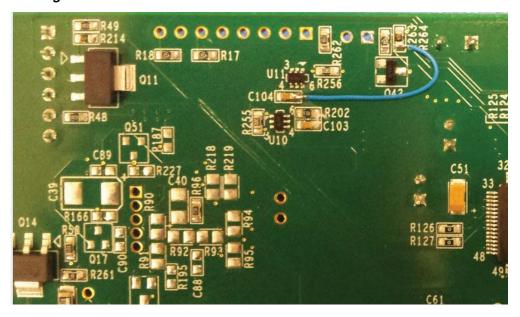

# **Platform Manager 2 Board Photos**

Photographs of the top and bottom of Platform Manager 2 Board are shown in Figure 5 and Figure 6 below. Component location references are relative to the top of the board with the silk screen text in the readable orientation (as shown in the photo).

Figure 5. Platform Manager 2 Evaluation Board – Top View

Figure 6. Platform Manager 2 Evaluation Board – Bottom View

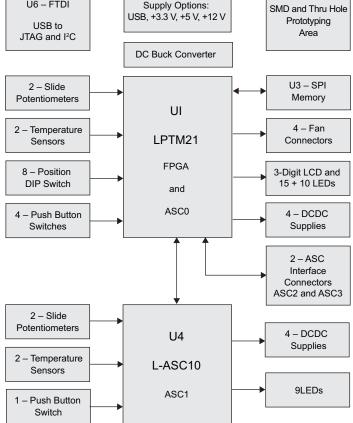

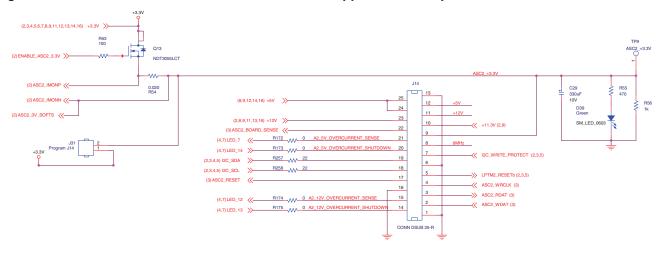

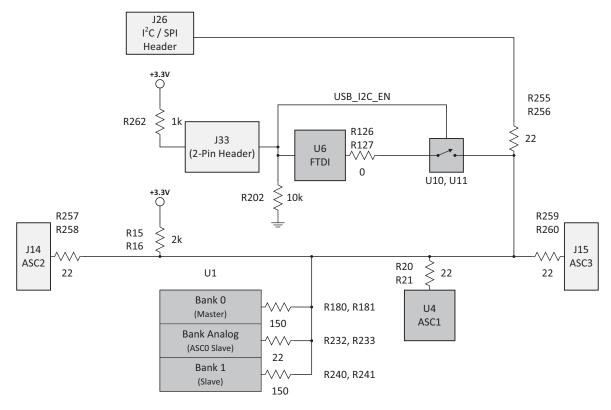

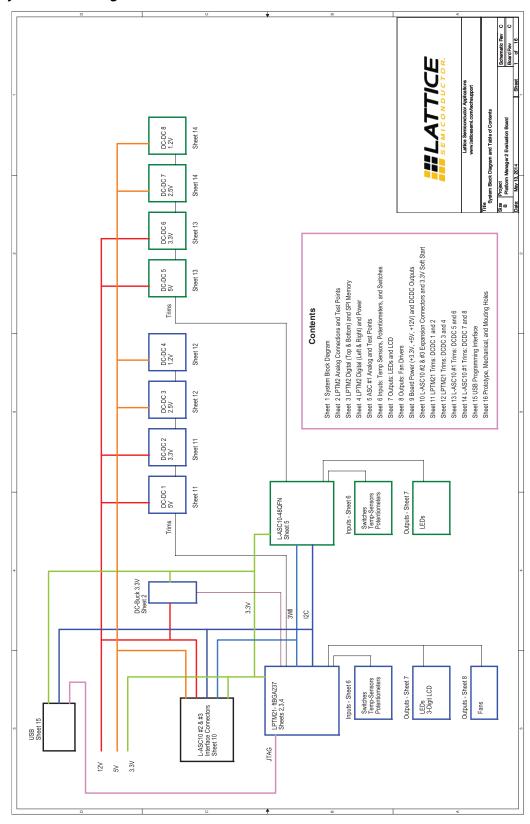

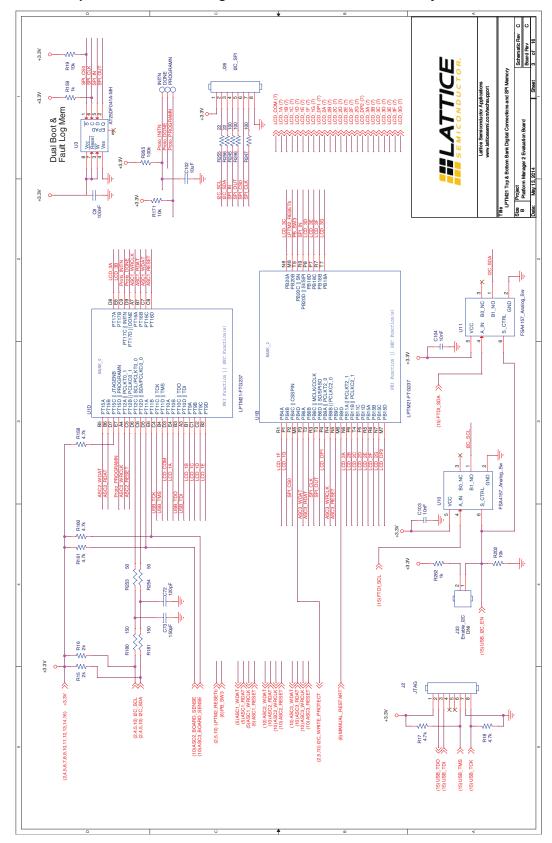

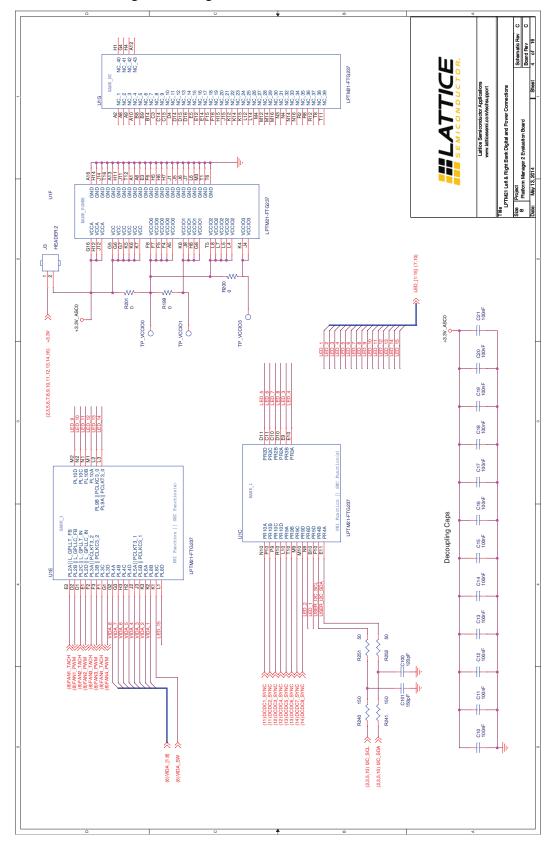

# Platform Manager 2 Board – Architecture Overview

In this section, the Platform Manager 2 evaluation board is described at the top level. It identifies the main hard-ware components on the board and briefly describes their functions. Because many of these elements are described in much more detail in the various Operational Description sections that follow, this section is just a short overview. Refer to the appropriate Operational Description Section for more details on each block. A block diagram of the overall system architecture of the Platform Manager 2 evaluation board is shown in Figure 7. Not all blocks are used by the demo but are provided to evaluate other features of the Platform Manager devices.

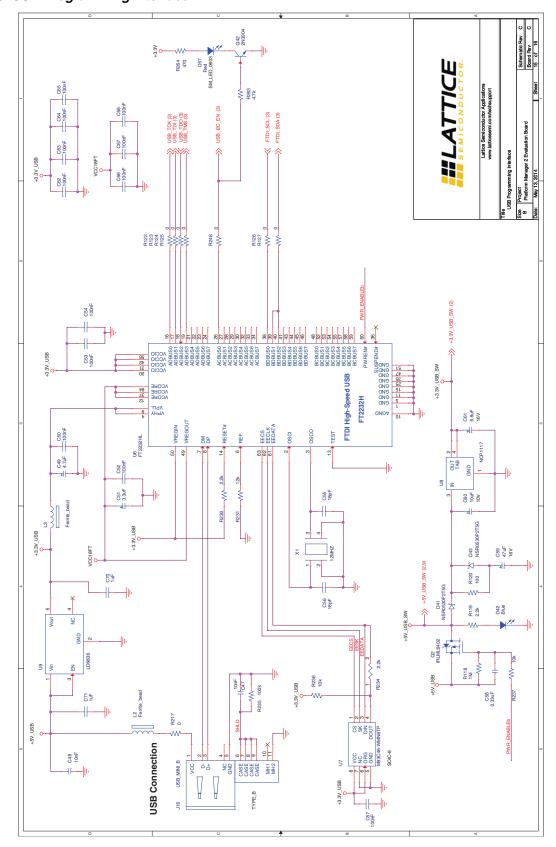

U6 – FTDI Supply Options: USB, +3.3 V, +5 V, +12 V

Figure 7. Platform Manager 2 Evaluation Board – Block Diagram

As discussed earlier the LPTM21 (U1) and L-ASC10 (U4) are the Platform Manager 2 devices that are highlighted on this board. Both are connected to a variety of input and output circuits that can be used in demos and customer evaluations.

**LPTM21** (U1) is the primary Platform Manager 2 device. It is referred to as ASC0 in this document when discussing the analog features and as LPTM21 or FPGA when the focus is on the programmable logic.

**L-ASC10** (U4) is the secondary Platform Manager 2 device that expands the hardware control and monitoring of LPTM21 (U1).

**SPI Memory** (U3) is used for Dual Boot and fault logging.

**FTDI USB Interface** (U6) is used for programming the Platform Manager devices and to access the I<sup>2</sup>C bus from USB.

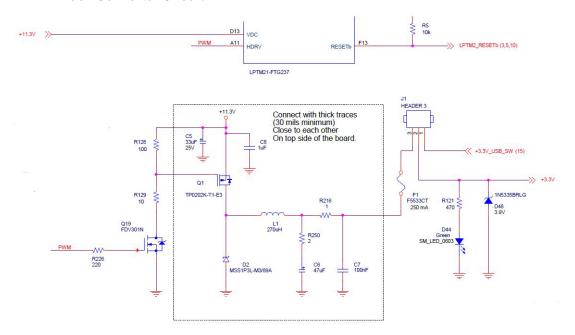

**DC Buck Converter** is used to power the board from an optional +12 V supply.

**Slide Potentiometers** are used to demonstrate voltage monitoring; they simulate power supplies and can be used to generate either over or under voltage faults.

**Temperature Sensors** are used to demonstrate temperature monitoring.

8-Position DIP Switch interfaces with the FPGA and can be used for a variety of uses.

Push Button Switches are connected to ASC GPIO and FPGA pins for a variety of uses.

Fan Connectors are used with off board fans.

**LCD Display** is a three digit seven segment display that is connected to the FPGA for a variety of uses.

**LED Indicators** are distributed to the ASC GPIO pins and some FPGA pins for user defined functions.

**DC-DC Supplies** can be enabled, monitored, trimmed, and controlled be VID.

**ASC Interface Connectors** are provided to connect additional ASC Evaluation boards to expand the level of hardware control and monitoring.

# **Operational Description**

Platform Manager 2 evaluation board supports the demonstration of multiple features, the details of which are described in this part of user guide. Each of the following sections covers a specific Platform Manager 2 feature with a focus on the associated circuitry and signals. Some sections are independent while others are combined to implement the complete Platform Manager 2 solution. The operational sections are organized as follows:

- · Voltage Monitor

- Temperature Sense

- · Current Monitor

- Hot Swap

- Fan Control

- Fault Logging

- Closed Loop Trim

- VID

- Programming and Configuration

- Dual Boot

- 12 V Buck Converter

- Power Supplies

- ASC Interface

- I<sup>2</sup>C Bus

- Miscellaneous

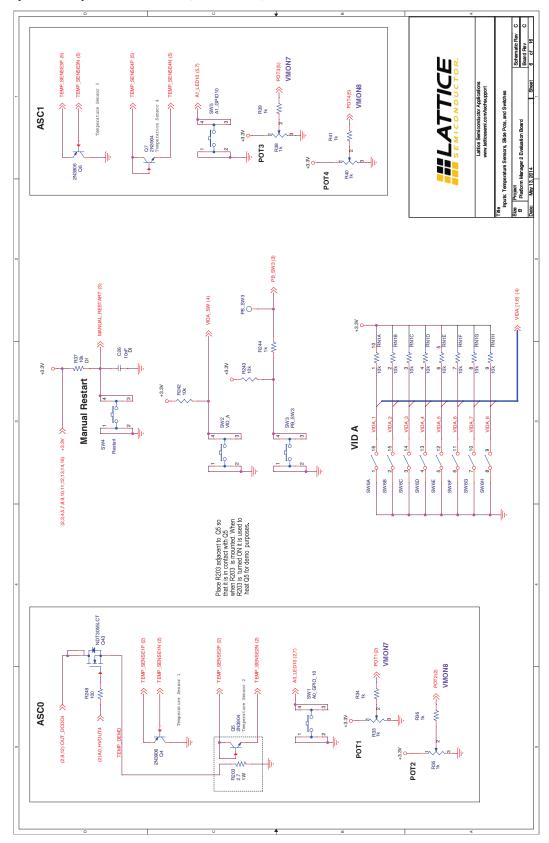

### **Voltage Monitor Operation**

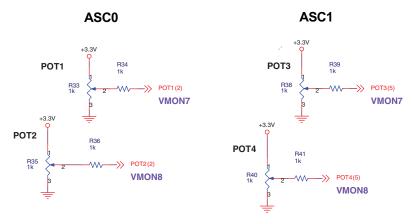

One of the key features of the Platform Manager 2 device is the ability to accurately monitor Voltages. The evaluation board has four slide potentiometers connected to Voltage Monitor inputs (VMONs). These potentiometers function as pseudo power supplies for the demo design and for evaluation of Voltage Monitoring. Most of the VMONs on the evaluation board have a low value series resistors connected to the on board source such as the DC-DC outputs, on-board supplies, and the potentiometers. These series resistors are only needed for the evaluation board so that the VMON test points can be driven from off-board sources without damage to either the onboard circuits or the off-board source and without the need to modify the board. Table 1 lists the components and signals associated with Voltage Monitoring.

Table 1. Components and Signals for Voltage Monitoring

| Component / Signals                                | Ref. Des.                       | Schematic<br>Sheet | Description                                                                                                                                    |

|----------------------------------------------------|---------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Components                                         |                                 |                    |                                                                                                                                                |

| Slider Potentiometers <sup>1</sup> (POT1 and POT2) | R33, R35                        | 6                  | 1 kOhm slider potentiometer: provides a variable Voltage from zero to 3.3 V. Connected to VMON7 and VMON8 of U1 with a 1 kOhm series resistor. |

| Series Resistors <sup>2</sup>                      | R34, R36                        | 6                  | 1 kOhm resistor.                                                                                                                               |

| Slider Potentiometers <sup>1</sup> (POT3 and POT4) | R39, R41                        | 6                  | 1 kOhm slider potentiometer: provides a variable Voltage from zero to 3.3 V. Connected to VMON7 and VMON8 of U4 with a 1 kOhm series resistor. |

| Series Resistors <sup>2</sup>                      | R39, R41                        | 6                  | 1 kOhm resistor.                                                                                                                               |

| Series Resistors <sup>2</sup>                      | R1, R2, R3, R4,<br>R6, R7, R8   | 2                  | 270 Ohm resistor.                                                                                                                              |

| Series Resistor <sup>2</sup>                       | R9                              | 2                  | 680 Ohm resistor.                                                                                                                              |

| Ground Sense Resistors <sup>2</sup>                | R10, R11, R12                   | 2                  | 100 Ohm resistor.                                                                                                                              |

| Ground Sense Resistor <sup>2</sup>                 | R13                             | 9                  | 100 Ohm resistor.                                                                                                                              |

| Series Resistors <sup>2</sup>                      | R23, R24, R25,<br>R26, R28, R29 | 5                  | 270 Ohm resistor.                                                                                                                              |

| Ground Sense Resistors <sup>2</sup>                | R29, R30, R31                   | 5                  | 100 Ohm resistor.                                                                                                                              |

| Ground Sense Resistor <sup>2</sup>                 | R32                             | 9                  | 100 Ohm resistor.                                                                                                                              |

| Signals                                            | 1                               |                    |                                                                                                                                                |

| A0_VMON1 - A0_VMON9                                |                                 | 2                  | ASC0 VMON inputs (9)                                                                                                                           |

| A0_GS_VMON1 -<br>A0_GS_VMON4                       |                                 | 2                  | ASC0 VMON Ground Sense inputs (4) pulled to ground with 100 Ohm resistors. Can be connected to low side of a differential source.              |

| A0_HVMON                                           |                                 | 2                  | ASC0 High Voltage VMON input.                                                                                                                  |

| A1_VMON1 – A1_VMON9                                |                                 | 5                  | ASC1 VMON inputs (9)                                                                                                                           |

| A1_GS_VMON1 -<br>A1_GS_VMON4                       |                                 | 5                  | ASC1 VMON Ground Sense inputs (4) pulled to ground with 100 Ohm resistors. Can be connected to low side of a differential source.              |

| A1_HVMON                                           |                                 | 5                  | ASC1 High Voltage VMON input.                                                                                                                  |

<sup>1.</sup> Not required for customer designs; this is only needed to support demonstrations on the evaluation board.

<sup>2.</sup> Not required for customer designs; allows driving test points with an off-board Voltage source without adding or removing components or damaging on board circuitry.

Figure 8. Voltage Monitor POT Circuits

The four slide potentiometers shown in Figure 8 provide a variable Voltage source from zero to +3.3 V. POT1 and POT2 are connected to LPTM21 (U1) while POT3 and POT4 are connected to L-ASC10 (U4).

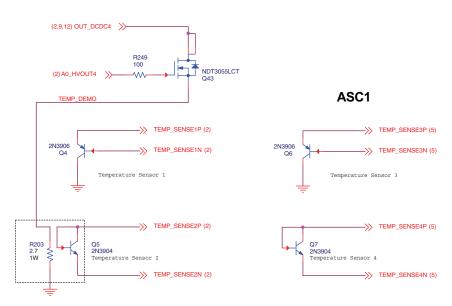

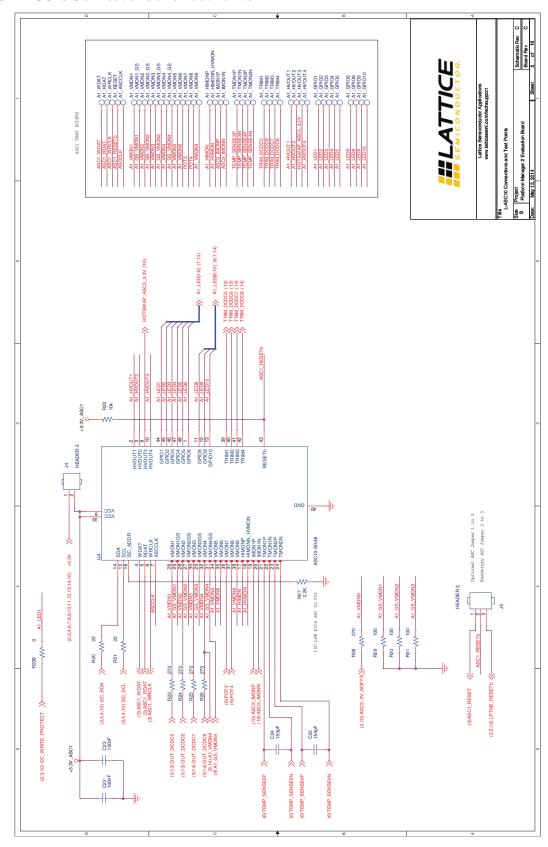

### **Temperature Monitor Operation**

Another key feature of the Platform Manager 2 device is the ability to sense and monitor temperatures. Each device can support up to two external temperature sensors and one internal. The external sensors are diode configured bipolar transistors that are connected to the TMON (temperature monitor) inputs of LPTM21 and L-ASC10 (U1 and U4). Table 2 lists the components and signals on the Platform Manager 2 evaluation board to demonstrate temperature sensing and monitoring operation.

Table 2. Components and Signals for Temperature Sense and Monitor

| Component / Signals              | Ref. Des.           | Schematic<br>Sheet | Description                                                                                                                                        |

|----------------------------------|---------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Components                       |                     |                    |                                                                                                                                                    |

| Temperature Sensor 1             | Q4                  | 9                  | 2N3906 PNP Transistor, Diode-configured (Beta Compensated) differential temperature sensor. Connected to TMON1 inputs of LPTM21 U1.                |

| Temperature Sensor 2             | Q5                  | 9                  | 2N3904 NPN Transistor, Diode- configured (Differential NPN) temperature sensor. Connected to TMON2 inputs of LPTM21 U1.                            |

| Temperature Sensor 3             | Q6                  | 9                  | 2N3906 PNP Transistor Diode- configured (Beta Compensated) differential temperature sensor. Connected to TMON1 inputs of L-ASC10 U4.               |

| Temperature Sensor 4             | Q7                  | 9                  | 2N3904 NPN Transistor Diode- configured (Differential NPN) temperature sensor. Connected to TMON2 inputs of L-ASC10 U4.                            |

| Heater (Pseudo IC) <sup>1</sup>  | R203                | 9                  | 2.7 Ohm 1 W power resistor is mounted over Q5 for demo purposes. The amount of heat generated depends on the output of DCDC4 and the state of Q43. |

| Heater Power Switch <sup>1</sup> | Q43                 | 9                  | Connects the output of DCDC4 to the heater (R203) when A0_HVOUT is active.                                                                         |

| Sensor Filter Capacitors         | C1, C2, C24,<br>C25 | 2 and 5            | 150 pF Input filter capacitors for temperature monitoring signals to reject external noise. Located near U1 and U4.                                |

| Component / Signals            | Ref. Des. | Schematic<br>Sheet | Description                                                                                                                                                        |

|--------------------------------|-----------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signals                        |           |                    |                                                                                                                                                                    |

| TEMP_SENSE1P /<br>TEMP_SENSE1N |           | 2 and 6            | Differential temperature sensor inputs to TMON1 of LPTM21 U1.                                                                                                      |

| TEMP_SENSE2P /<br>TEMP_SENSE2N |           | 2 and 6            | Differential temperature sensor inputs to TMON2 of LPTM21 U1.                                                                                                      |

| TEMP_SENSE3P /<br>TEMP_SENSE3N |           | 5 and 6            | Differential temperature sensor inputs to TMON1 of L-ASC10 U4.                                                                                                     |

| TEMP_SENSE4P /<br>TEMP_SENSE4N |           | 5 and 6            | Differential temperature sensor inputs to TMON2 of L-ASC10 U4.                                                                                                     |

| A0_HVOUT4                      |           | 2 and 6            | HVOUT output from LPTM21 to turn on/off transistor (Q43) in order to control the current flowing into resistor (R203) which provides temperature for demo purpose. |

<sup>1.</sup> Not required for customer designs; this is only needed to support demonstrations on the evaluation board.

Figure 9. Temperature Monitor Circuits

#### ASC<sub>0</sub>

On the Platform Manager 2 evaluation board there are four external temperature sensors as shown in Figure 9. Two sensors (Q4 and Q5) are connected to LPTM21 (U1) and two sensors (Q6 and Q7) are connected to L-ASC10 (U4). The evaluation board demonstrates two different configurations for the temperature sensors. Q5 and Q7 are configured as *Differential NPN* diodes while; Q4 and Q6 are configured as *Beta Compensated PNP* diodes. The *Beta Compensated PNP* configuration is similar to a substrate diode connection and is able to take advantage of the Platform Manager 2 built-in beta compensation for more accurate temperature monitoring. All of the temperature sensors have filter capacitors connected across the differential signals to improve noise-immunity and they are located close to the Platform Manager 2 devices (U1 and U4). All of the temperature sensors have test points nearby to support off-board sensors after the on-board sensor has been removed.

The circuit in Figure 9 shows a power resistor (R203) mounted thermally close to sensor 2 (Q5). This 1-watt power resistor is a pseudo IC load to demonstrate thermal management in the demo design. The resistor is powered when both the MOSFET switch (Q43) is biased ON and DCDC4 is enabled. Q43 is turned on when HVOUT4 of LPTM21 (U1) is turned ON; HVOUT4 needs to be in Charge Pump mode with the following settings: 8 V, 100 uA source, 3000 uA sink, and static mode. Using the Platform Manager 2 I<sup>2</sup>C GUI with the demo, the output of DCDC4

can be adjusted or fan #2 can be controlled (or both) in order to reduce the power and lower the temperature of the sensor. For details on using the demo and GUI please refer to the Platform Manager 2 I<sup>2</sup>C Demo Design and GUI User's Guide. For additional information regarding temperature monitoring please refer to TN1278, Temperature Monitoring and Fan Control with Platform Manager 2.

### **Current Monitoring Operation**

Another key feature of the Platform Manager 2 device is the ability to monitor current. Each device has two current monitoring (IMON) inputs and each input has two pins that connect to an external current sensing resistor. One current sensing input is designed to monitor current at high voltage (12 V typical) and shares a pin with the high voltage VMON (HIMONN\_HVMON). The second current sensing input is designed to monitor lower voltage (5 V typical or lower) currents. Table 3 lists the components and signals associated with current monitoring operation on the Platform Manager 2 board.

Table 3. Components and Signals for Current Monitoring Operation

| Component / Signals              | Ref. Des. | Schematic<br>Sheet | Description                                                                                        |

|----------------------------------|-----------|--------------------|----------------------------------------------------------------------------------------------------|

| Components                       | 1         | 1                  |                                                                                                    |

| Current sense resistor           | R54       | 10                 | 20 milli-Ohm ¼ W Resistor for load side current monitoring with IMON1 inputs of LPTM21 (U1).       |

| Current sense resistor           | R57       | 10                 | 20 milli-Ohm ¼ W Resistor for supply side current monitoring with IMON1 inputs of L-ASC10 (U4).    |

| Isolation Resistor               | R261      | 10                 | Zero Ohm Resistor isolates the ASC3_IMONP net from the +3.3 V supply net to support Kelvin layout. |

| Test Connector <sup>1</sup>      | J31, J32  | 10                 | Connect an external load resistor between pin 2 and ground to provide a measurable current.        |

| Power Switch MOSFET <sup>1</sup> | Q13, Q14  | 10                 | N-Channel Power MOSFET, used to enable power to loads either on/off or Hot Swap mode.              |

| Signals                          |           | 1                  |                                                                                                    |

| ASC2_IMONP<br>ASC2_IMONN         |           | 2, 10              | The current monitoring signals to LPTM21 (U1) connected across the current sense resistor R54.     |

| ASC3_IMONP<br>ASC3_IMONN         |           | 5, 10              | The current monitoring signals to L-ASC10 (U4) connected across the current sense resistor R57.    |

<sup>1.</sup> Not required for customer designs; this is only needed to support demonstrations on the evaluation board.

Figure 10. ASC0 IMON1 Monitors ASC2 Current and Supports Hot Swap Circuits

The current sense resistor (R54) shown in Figure 10 is used to monitor the current through power switch MOSFET (Q13). When Q13 is turned on, +3.3 V is supplied to loads both on and off board and R54 is used to monitor the combined load current. The signals ASC2\_IMONP and ASC2\_IMONN are connected to R54 using Kelvin connections and differential signaling layout techniques to maximize the current sensing accuracy at the IMON1 inputs of U1 (sheet 2). The signals are named because they can be used to monitor off board current drawn by the ASC2 interface connector J14.

The N-channel MOSFET (Q13) is controlled by the HVOUT2 of U1 (sheet 2) either on/off control or Hot Swap based on the design. The gate resistor (R53) is mounted physically close to Q13 to minimize parasitic oscillations. The programming jumper (J31) by-passes Q13 when installed to support programming ASC2 via J14; the jumper should be removed for Hot Swap operation.

The on-board loads consist of the following components: C29, D39, R55, and R56. While they provide a path to ground for Q13 and R54, they are not designed to provide a significant load. Alternatively, an external load resistor can be attached between pin 2 of J31 and ground to provide a more significant load to be measured. The external load resistor should draw less than 200 mA when the board is powered by USB and less than 3 A when the board is powered from a bench supply connected to J12 (sheet 9). The function of LED D39 and bias resistor R55 is to indicate that +3.3 V is available for the ASC2 interface connector. R56 is designed to discharge the Hot Swap load capacitor C29 when power is removed. The Hot Swap load capacitor C29 only draws current when it is charging up which is discussed in the Hot Swap Operation section.

(S) ASC3\_NONE (C) ENAMEL MCS\_3.9V )

(A) (LID\_11 (C) ENAMEL MCS\_3.9V )

(B) (LID\_11 (C) ENAMEL MCS\_3.9V )

(C) (LID\_11 (C) ENAMEL ENAMEL MCS\_3.9V )

(C) (LID\_11 (C) ENAMEL ENAM

Figure 11. ASC1 IMON1 Monitors ASC3 Current and Supports Hot Swap Circuits

The current sense resistor (R57) shown in Figure 11 is used to monitor the current through the power switch MOS-FET (Q14). When Q14 is turned on, +3.3 V is supplied to loads both on and off board and R57 is used to monitor the combined load current. The signals ASC3\_IMONP and ASC3\_IMONN are connected to R57 using Kelvin connections and differential signaling layout techniques to maximize the current sensing accuracy at the IMON1 inputs of U4 (sheet 5). The signals ASC3\_IMONP and ASC3\_IMONN are named because they can be used to monitor off board current drawn by the ASC3 interface connector J15. Since R57 is used to monitor the current on the high (or supply side), a zero Ohm jumper (R261) is used to generate a sensing net that is isolated from the power net. This separate net supports differential signal layout from the sensing resistor to the IMON inputs.

The N-channel MOSFET (Q14) can be controlled by either HVOUT3 of U1 (sheet 2) for simple on/off control or HVOUT3 of U4 (sheet 5) for Hot Swap control, based on the position of a jumper (J30). Hot Swap is only supported when the current sense and MOSFET control are connected to the same ASC; in this case ASC1 (U4). The gate resistor (R58) is mounted physically close to Q14 to minimize parasitic oscillations. The programming jumper (J32) by-passes Q14 when installed to support programming ASC3 via J15; the jumper should be removed for Hot Swap operation.

The on-board loads consist of the following components: C30, D40, R60, and R61. While they provide a path to ground for Q14 and R57, they are not designed to provide a significant load. Alternatively, one can attach a load resistor between pin 2 of J32 and ground to provide a load to be measured. The resistor should draw less than 200 mA when the board is powered by USB and less than 3 A when the board is powered from a bench supply connected to J12 (sheet 9). The function of LED D40 and bias resistor R60 is to indicate that +3.3 V is available for the ASC3 interface connector. R61 is designed to discharge the Hot Swap load capacitor C30 when power is removed. The Hot Swap load capacitor C30 only draws current when it is charging up which is discussed in the Hot Swap Operation section.

### **Hot Swap Operation**

The Hot Swap operation can be demonstrated on the Platform Manager 2 evaluation board using the IMON1 current sense inputs and the HVOUT MOSFET driver outputs. The default demo does not include Hot Swap operation. However, this section is provided for future demos and customer evaluations. Table 4 lists the components and signals associated with the Hot Swap operation on the Platform Manager 2 evaluation board

Table 4. Components and Signals for Hot Swap Operation

| Component / Signals              | Ref. Des. | Schematic<br>Sheet | Description                                                                                                           |

|----------------------------------|-----------|--------------------|-----------------------------------------------------------------------------------------------------------------------|

| Components                       | l l       |                    |                                                                                                                       |

| Current sense resistor           | R54       | 10                 | 20 milli-Ohm ¼ W Resistor for load side current monitoring with IMON1 inputs of LPTM21 (U1).                          |

| Current sense resistor           | R57       | 10                 | 20 milli-Ohm ¼ W Resistor for supply side current monitoring with IMON1 inputs of L-ASC10 (U4).                       |

| Isolation Resistor               | R261      | 10                 | Zero Ohm Resistor isolates the ASC3_IMONP net from the +3.3V supply net to support Kelvin layout.                     |

| Gate Resistors                   | R53, R58  | 10                 | 100 Ohm Resistor to reduce parasitic MOSFET oscillations on Q13 and Q14.                                              |

| LED Bias Resistors               | R55, R60  | 10                 | 470 Ohm Resistors to limit the current in LEDs D39 and D40.                                                           |

| MOSFET Switch                    | Q13       | 10                 | N-Channel MOSFET Supply-side hot-swap switch supplies power to load capacitor C29 and ASC2 interface connector (J14). |

| MOSFET Switch                    | Q14       | 10                 | N-Channel MOSFET Load-side hot-swap switch supplies power to load capacitor C30 and ASC3 interface connector (J15).   |

| LEDs                             | D39, D40  | 10                 | LEDs Green, indicate when hot-swap power is on or programming jumpers are in place.                                   |

| Load Capacitors <sup>1</sup>     | C29, C30  | 10                 | 330 uF 10 V Bulk capacitance emulates a hot-swap load.                                                                |

| Discharge Resistors <sup>1</sup> | R56, R61  | 10                 | 1 kOhm Resistor discharges load capacitor between hot-swaps.                                                          |

| Three-Pin Header <sup>1</sup>    | J30       | 10                 |                                                                                                                       |

| 2-Pin Header <sup>1</sup>        | J31, J32  | 10                 | Install jumper to bypass hot-swap circuits and provide power during programming of ASC2 and/or ASC3.                  |

|                     |            | 0-1                |                                                                                                                       |

|---------------------|------------|--------------------|-----------------------------------------------------------------------------------------------------------------------|

| Component / Signals | Ref. Des.  | Schematic<br>Sheet | Description                                                                                                           |

| Signals             | 11011 2001 | Onoot              | Бесеприон                                                                                                             |

|                     |            | 0.10               | LIVOLITO signal frage LDTMO1 (LI1) to control O10                                                                     |

| ENABLE_ASC2_3.3V    |            | 2, 10              | HVOUT2 signal from LPTM21 (U1) to control Q13. Can be used in hot-swap or simply as on/off control.                   |

| ENABLE_ASC3_3.3V    |            |                    | HVOUT3 signal from LPTM21 (U1) to control Q13. For use as on/off control when L-ASC10 (U4) is powered down.           |

| HOTSWAP_ASC3_3.3V   |            | 5, 10              | HVOUT3 signal from L-ASC10 (U4) to control Q14. Can be used in hot-swap or simply as on/off control.                  |

| ASC2_IMONP          |            |                    |                                                                                                                       |

| ASC2_IMONN          |            | 2, 10              | The current monitoring signals to LPTM21 (U1) connected across the current sense resistor R54.                        |

| ASC3_IMONP          |            |                    |                                                                                                                       |

| ASC3_IMONN          |            | 5, 10              | The current monitoring signals to L-ASC10 (U4) connected across the current sense resistor R57.                       |

| ASC2_3V_SOFTS       |            | 2, 10              | Voltage monitoring signal for Hot Swap or sequencing connected to VMON6 of LPTM21 (U1).                               |

| ASC3_3V_SOFTS       |            | 5, 10              | Voltage monitoring signal connected to VMON9 of LPTM21 (U1) for sequencing and VMON9 of L-ASC10 (U4) for Hot Swap.    |

| ASC2_+3.3V          | TP9        | 10                 | Hot-swap power bus for ASC2 interface connector (J14) and loads. Test point on board is labeled with the signal name. |

| ASC3_+3.3V          | TP8        | 10                 | Hot-swap power bus for ASC3 interface connector (J15) and loads. Test point on board is labeled with the signal name. |

<sup>1.</sup> Not required for customer designs; this is only needed to support demonstrations on the evaluation board.

There are two Hot Swap circuits provided on the Platform Manager 2 evaluation board; one is controlled LPTM21 U1 and the other is controlled by L-ASC10 U4. The supporting Hot Swap circuitry for U1 is shown in Figure 10 and for U4 in Figure 11. Neither Hot Swap circuit is used in the default demo but, they are described for future demos and customer evaluations.

The circuit in Figure 10 illustrates a Supply based Hot Swap with the MOSFET Q13 connected between the supply and the current sensing resistor R54. The N type MOSFET Q13 is controlled by HVOUT2 of LPTM21 (sheet 2) and the gate resistor R53 is located physically close to Q13 to reduce turn on oscillations. The signals ASC2\_IMONP and ASC2\_IMONN are connected to R54 using Kelvin connections and differential signaling layout techniques to maximize the current sensing accuracy at the IMON1 inputs of LPTM21 (sheet 2). The signal ASC2\_3V\_SOFTS can be used by the Hot Swap function to monitor the load capacitor C29 voltage and is connected to VMON6 of LPTM21 using R7 (sheet 2). The Hot Swap function monitors the load capacitor C29 voltage for the following reasons: 1) to see that C29 is charging up and there is not a short or open in the circuit, 2) see that C29 has reached a voltage where a higher current limit can be used, 3) to know when C29 is close to the supply value – Hot Swap is complete. When Hot Swap is disabled R56 provides a discharge path for C29 to prepare the circuit for a subsequent Hot Swaps. LED D39 and bias resistor R55 gives a visual indication that the Hot Swap process is complete.

The circuit In Figure 11 illustrates a Load based Hot Swap with the MOSFET Q13 connected between the current sensing resistor R74 and the load. The N type MOSFET Q14 is controlled by HVOUT3 of L-ASC10 (sheet 5) and the gate resistor R58 is located physically close to Q14 to reduce turn on oscillations. The signals ASC3\_IMONP and ASC3\_IMONN are connected to R57 using Kelvin connections and differential signaling layout techniques to maximize the current sensing accuracy at the IMON1 inputs of L-ASC10 (sheet 5). The signal ASC3\_3V\_SOFTS is used by the Hot Swap function to monitor the load capacitor C30 voltage and is connected to VMON9 of L-ASC10 using R28 (sheet 5). The Hot Swap function monitors the load capacitor C30 voltage for the following reasons: 1) to see that C30 is charging up and there is not a short or open in the circuit, 2) see that C30 has reached a voltage

where a higher current limit can be used, 3) to know when C30 is close to the supply value – Hot Swap is complete. When Hot Swap is disabled R61 provides a discharge path for C30 to prepare the circuit for a subsequent Hot Swaps. LED D40 and bias resistor R60 gives a visual indication that the Hot Swap process is complete.

Note the series resistors R7 (sheet 2) and R28 (sheet 5) are not required for Hot Swap or VMON operation; in a typical design the VMON input is connected directly to the Voltage source being monitored. The value of the series resistor (270 Ohms) is a compromise; it is low enough that the voltage sensing accuracy during Hot Swap is not affected but, it is also high enough that another supply can be connected directly to VMON test point without significant current flowing between the supplies. The function of R7 and R28 is to support prototype circuits that may be built using the Platform Manager 2 evaluation board without having to remove components or cut traces.

For Hot Swap operation the Platform Designer tool must be used to configure ASC0 and ASC1 (U1 and U4) so that the HVOUT output is controlled by the status of the IMON1 inputs. This internal connection provides hysteretic control such that the MOSFET is modulated to restrict the current below the IMON1 trip point. If the sensed current is below the trip point then the MOSFET bias is increased; and if the sensed current exceeds the trip point then the MOSFET bias is reduced. For additional information please see the Hot Swap Application Note.

Note that for the Hot Swap operation to work properly, no significant off board load should be enabled or attached to J31 or J32 or the ASC interface connectors J14 and J15. A significant load would draw more than 20% of the Hot Swap current. Also J30 should be in the ASC1 position.

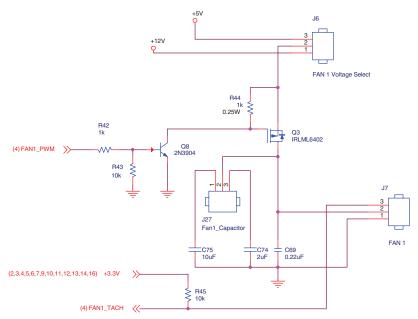

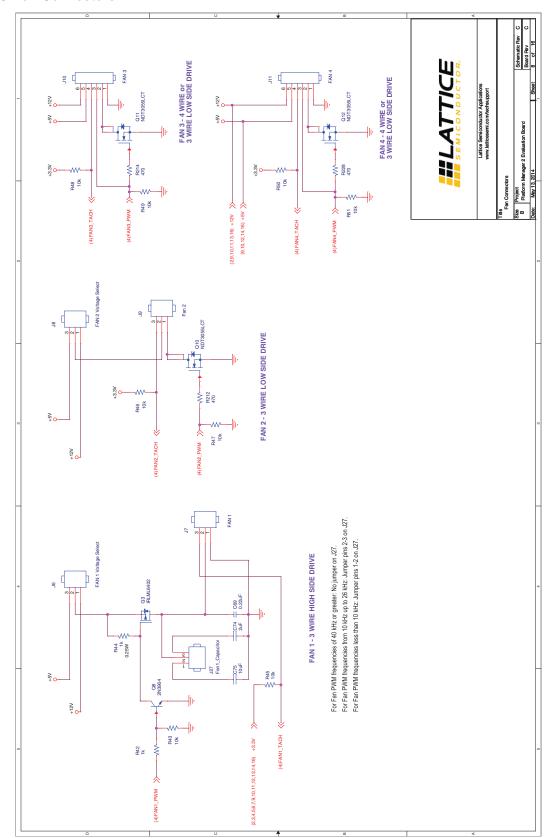

## **Fan Control Operation**

The Platform Manager 2 evaluation board provides four channels of fan control for a variety of thermal management demos and the kit includes a loose un-mounted 5 V 3-wire fan. Table 5 lists the components and signals associated with fan control operation of the Platform Manager 2 board.

Table 5. Components and Signals for Fan Control Operation

| Component / Signals               | Ref. Des. | Schematic<br>Sheet                                                                                            | Description                                                                                                           |

|-----------------------------------|-----------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Components                        |           |                                                                                                               |                                                                                                                       |

| 5V 3-Wire Fan                     |           |                                                                                                               | Not mounted on the board but, included with the kit for various demos. Has a 3x1 connector for use with FAN1 or FAN2. |

| 3x1 Header                        | J7, J9    | 8                                                                                                             | Headers to connect external 3 Wire fans. (FAN1 and FAN2). Supports both +5 V and +12 V fans.                          |

| 6x1 Header                        | J10, J11  | 8 Headers to connect external fans (FAN3 and FAN4). Supports both +5 V and +12 V also 3-wire and 4-wire fans. |                                                                                                                       |

| 3x1 Header1                       | J6, J8    | 8                                                                                                             | Headers to select from either +5 V or +12 V supply for FAN1 and FAN2.                                                 |

| 3x1 Header1                       | J27       | 8                                                                                                             | Provides options to connect various filter capacitors to the supply pin of FAN1.                                      |

| High-Side Drive Filter Capacitor2 | C69       | 8                                                                                                             | 0.22 uF capacitor – Default filter for PWM frequencies 40 kHz or more. No jumper on J27.                              |

| High-Side Drive Filter Capacitor2 | C74       | 8                                                                                                             | 2.0 uF capacitor – Optional filter for PWM frequencies between 10 kHz and 26 kHz. Jumper pins 2-3 on J27.             |

| High-Side Drive Filter Capacitor2 | C75       | 8                                                                                                             | 10 uF capacitor – Optional filter for PWM frequencies below 10 kHz. Jumper pins 1-2 on J27.                           |

| NPN Transistor – SOT-23           | Q8        | 8                                                                                                             | 2N3904 NPN Transistor inverts the FAN1_PWM signal from LPTM21 U1 and shifts the drive level up to +12 V.              |

| P-Channel MOSFET - SOT-23         | Q3        | 8                                                                                                             | IRLML6402 P-Channel MOSFET provides high-side switching for FAN1 based on the inverted (by Q8) FAN1_PWM signal.       |

# **Platform Manager 2 Evaluation Board**

| Component / Signals        | Ref. Des.             | Schematic<br>Sheet | Description                                                                                                                                                         |

|----------------------------|-----------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N-Channel MOSFET - SOT-235 | Q10, Q11, Q12         | 8                  | NDT3055LCT – N-Channel MOSFET provides low-<br>side drive based on PWM signal from LPTM21 U1.                                                                       |

| Gate Resistor              | R212, R214,<br>R228   | 8                  | 470 Ohm resistor to isolate the MOSFET input capacitance from the LPTM21 I/O bank to minimize ground and supply bounce. Also suppresses MOSFET turnon oscillations. |

| Gate Pull Down Resistor    | R47, R49, R51         | 8                  | 10k Ohm resistor to keep MOSFETs turned off by default.                                                                                                             |

| Gate Pull Up Resistor      | R44                   | 8                  | 1 kOhm ¼ W Resistor to provide a fast turn-off of Q3. The power rating is required for operation at +12 V.                                                          |

| Tach Pull Up Resistor      | R45, R46, R48,<br>R50 | 8                  | 10 kOhm resistor to bias the open-drain tachometer feedback signal from the fans.                                                                                   |

| Base Pull Down Resistor    | R43                   | 8                  | 10 kOhm resistor to keep Q8 turned off by default.                                                                                                                  |

| Base Bias Resistor         | R42                   | 8                  | 1 kOhm resistor to limit the current from the LPTM21 U1 output when turning on Q8.                                                                                  |

| Signals                    | 1                     |                    |                                                                                                                                                                     |

| FAN1_PWM,                  |                       |                    |                                                                                                                                                                     |

| FAN2_PWM,                  |                       |                    |                                                                                                                                                                     |

| FAN3_PWM,                  |                       |                    |                                                                                                                                                                     |

| FAN4_PWM                   |                       | 4, 8               | The PWM signals to control the fan speed, FPGA output from LPTM21 U1.                                                                                               |

| FAN1_TACH,                 |                       |                    |                                                                                                                                                                     |

| FAN2_TACH,                 |                       |                    |                                                                                                                                                                     |

| FAN3_TACH,                 |                       |                    |                                                                                                                                                                     |

| FAN4_TACH                  |                       | 4, 8               | The Tachometer or fault signal from fan to FPGA input of LPTM21 U1.                                                                                                 |

- 1. Not required for customer designs; this is only needed to support demonstrations on the evaluation board.

- 2. Actual values may vary for customer designs; several values are provided to support demonstrations on the evaluation board.

The control circuit shown in Figure 12 for Fan 1 is the most complex fan drive circuit on the board. This is to support a wide variety of design evaluations. High-side drive is implemented for Fan 1 using Q3 to modulate the supply to the fan. The FAN1\_PWM signal from LPTM21 (U1) is inverted and level shifted by Q8. The low impedance (1 kOhm) of R44 is needed to turn Q3 off quickly and because of operation at +12 V the ½ watt package is required. The high-side drive benefits from having a filter capacitor in the circuit and J27 provides the means to change the filter value based on the PWM frequency. The PWM frequency is selected in Platform Designer Fan Component view. A jumper needs to be installed on J6 to select the fan supply voltage. +5 V can be provided by the USB cable to power the included fan. Alternatively +5 V can be supplied from J12, J14, or J15 (sheets 9 and 10) based on type of evaluation being done. If a +12 V fan is used the voltage must be supplied from an off-board supply via J28, J25, J14, or J15 (sheets 9 and 10) because +12 V is not generated from the USB +5 V. The 10k pull-up resistor (R45) is connected to +3.3 V to provide bias for fans that have an open-drain tachometer or fault output and to interface with the LPTM21 (U1) FPGA inputs.

Figure 12. Fan 1 PWM Control Circuit

**FAN 1 - 3 WIRE HIGH SIDE DRIVE**

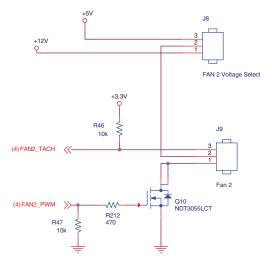

The control circuit shown in Figure 13 for Fan 2 provides a low-side drive circuit where Q10 modulates the ground connection to the fan. The signal FAN2\_PWM comes from the FPGA output of LPTM21 (U1) through a series resistor (R212). The series resistor minimizes both the capacitive loading on the LPTM21 outputs and the tendency for Q10 to oscillate during turn-on; it is located physically close to Q10 on the board. The pull-down resistor R17 keeps the MOSFET Q10 turned off by default. A jumper needs to be installed on J8 to select the fan supply voltage. +5 V can be provided by the USB cable to power the included fan. Alternatively +5 V can be supplied from J12, J14, or J15 (sheets 9 and 10) based on type of evaluation being done. If a +12 V fan is used the voltage must be supplied from an off-board supply via J28, J25, J14, or J15 (sheets 9 and 10) because +12 V is not generated from the USB +5 V. The 10 kOhm pull-up resistor (R47) is connected to +3.3 V to provide bias for fans that have an open-drain tachometer or fault output and to interface with the LPTM21 (U1) FPGA inputs.

Figure 13. Fan 2 PWM Control Circuit

**FAN 2 - 3 WIRE LOW SIDE DRIVE**

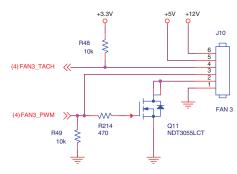

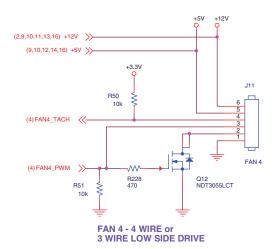

Figure 14. Fans 3 and 4 PWM Control Circuits

FAN 3 - 4 WIRE or 3 WIRE LOW SIDE DRIVE

The control circuits shown in Figure 14 for Fan 3 and 4 provide low-side drive for both fans; Q11 modulates the ground connection for Fan 3 based on the FAN3\_PWM signal and Q12 modulates the ground connection for Fan 4 based on the FAN4\_PWM signal. Both signals come from LPTM21 (U1) FPGA outputs and use series resistors of 470 Ohms (R214 and R228) to minimize the capacitive loading. The series resistors are also mounted physically close to the MOSFETs (Q11 and Q12) to minimize parasitic oscillations. Both circuits have 10 kOhm pull-down resistors to keep the MOSFETs turned off by default. Unlike Fans 1 and 2 there is not a separate jumper to select the fan supply voltage; both the +5 V and +12 V supplies are available on the six-pin headers (J10 and J11) so that the fan connector can be wired to select the supply voltage. The six-pin headers also provide the PWM signals directly on pin three to support 4-wire fans. Both fan circuits have 10 kOhm pull-up resistors to +3.3 V on the TACH signals to support fans with open-drain tachometer outputs and to interface with the LPTM21 (U1) FPGA inputs.

The Platform Designer tool has a configurable Fan Controller component which can be implemented within the LPTM21 (U1). The fan controller can be configured to work with 2-wire, 3-wire, or 4-wire fans, and a maximum of sixteen fans can be controlled. The fan controller IP generates a pulse width modulated (PWM) signal, which is used to control the speed of the fan. It also monitors the tachometer input from the fan to detect a faulty condition. For additional information regarding fan control please refer to TN1278, Temperature Monitoring and Fan Control with Platform Manager 2.

### **Fault Logging Operation**

One of the main features of any Platform Manager is the ability to log faults in non-volatile memory for later retrieval and analysis. The Platform Manager 2 evaluation board supports three methods of fault logging: 1) internal L-ASC10 storage only, 2) internal LPTM21 storage, and 3) external storage in SPI flash memory. The board also provides hold-up circuits so the Platform Manager 2 has time to log faults in the event of a primary supply failure. Table 6 lists the components and signals associated with Fault Logging operation of the Platform Manager 2 evaluation board.

Table 6. Components and Signals for Fault Logging OperationComponents and Signals for Fan Control Operation

| Component / Signals    | Ref. Des. | Schematic<br>Sheet | Description                                                                                                                                                           |

|------------------------|-----------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Components             |           | 1                  |                                                                                                                                                                       |

| 4 MB Flash Memory      | U3        | 3                  | SPI Flash memory to store Fault log data from LPTM21. LPTM21 has built-in SPI master which enables data transfer. This is the same memory that is used for Dual Boot. |

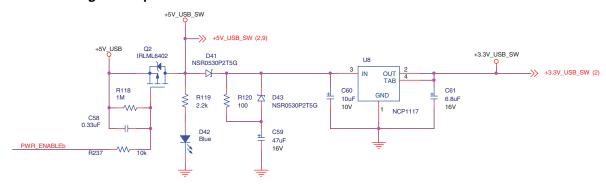

| 5 V Blocking Diode     | D41       | 15                 | Schottky Diode. Prevents external loads or supply from draining the hold-up capacitor.                                                                                |

| 5 V Passing Diode      | D43       | 15                 | Schottky Diode. Allows the hold-up capacitor to provide full current to down-stream supply.                                                                           |

| 5 V Hold-up Capacitor  | C59       | 15                 | 47uF Capacitor. Keeps U1, U3, and U4 alive after +5 V power outage to store faults.                                                                                   |

| 5 V Charging Resistor  | R120      | 15                 | 100 Ohm Resistor. Prevents large in-rush current charging the hold-up capacitor at power up.                                                                          |

| 12 V Blocking Diode    | D37       | 9                  | Schottky Diode. Prevents external loads or supply from draining the hold-up capacitor.                                                                                |

| 12 V Passing Diode     | D38       | 9                  | Schottky Diode. Allows the hold-up capacitor to provide full current to down-stream supply.                                                                           |

| 12 V Hold-up Capacitor | C27, C28  | 9                  | 47 uF and 220 uF Capacitors. Keeps U1, U3, and U4 alive after +12 V power outage to store faults.                                                                     |

| 12 V Charging Resistor | R52       | 9                  | 100 Ohm Resistor. Prevents large in-rush current charging the hold-up capacitor at power up.                                                                          |

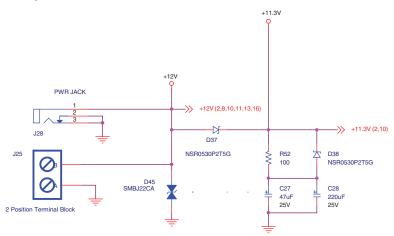

Figure 15 shows the hold-up circuit for the USB +5 V supply. If the USB +5 V supply suddenly fails, this hold-up circuit will power the Platform Manager 2 and flash memory long enough to store the fault. The USB +5 V can fail for several of the following reasons: the USB cable is unplugged, the USB hub is powered down, the FTDI (U6) device is told to power down and Q2 is turned off. The signal +5V\_USB\_SW is connected to VMON5 of LPTM21 (U1 on sheet 2) for early detection of a 5 V fault. Small signal Schottky diodes are used for the blocking and passing diodes as the power required for the Platform Manager 2 and flash memory is fairly low. The size of the hold-up capacitor (C59) should be increased for fault logging support if significant loads are added to the +3.3 V supply. The charging resistor (R120) prevents large in-rush currents when the supply is connected or turned on.

Figure 15. Fault Log Hold-Up Circuit for 5 V

Figure 16 shows the hold-up circuit for the +12 V supply; it is similar to the 5 V circuit described above. The +12 V supply is monitored by the HIMONN\_HVMON pin of the LPTM21 (U1 on sheet 2) for early detection of supply failure. The small signal Schottky diodes are used for blocking and passing the charge on the hold-up capacitors (C27 and C28). The charging resistor R52 prevents large in-rush currents when the supply is connected or turned on.

Figure 16. Fault Log Hold-Up Circuit for 12V

Both the LPTM21 and L-ASC10 devices have non-volatile EEPROM and volatile registers available to store fault log data. In addition, the LPTM21 device can store fault log data either internally in the User Flash Memory (UFM) of the FPGA section of U1 or externally in the SPI Flash Memory (U3). The Platform Manager 2 evaluation board has an external SPI 4 MB flash (U3) connected to the LPTM21 SPI interface to communicate with the memory as shown in Figure 21. This memory can be used for both Dual Boot and Fault Logging. The Platform Designer tool has a Fault Logging component which is used to configure what is logged and how it is stored. For additional information regarding fault logging please refer to TN1277, Fault Logging Using Platform Manager 2.

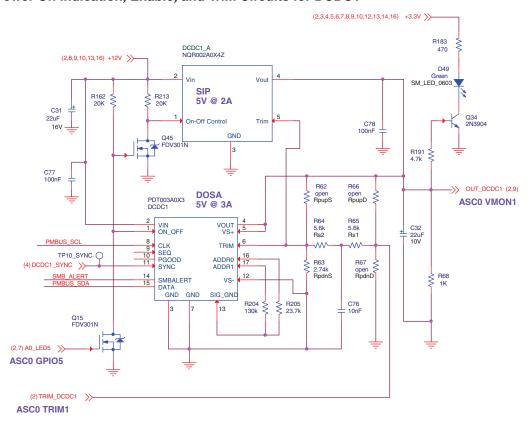

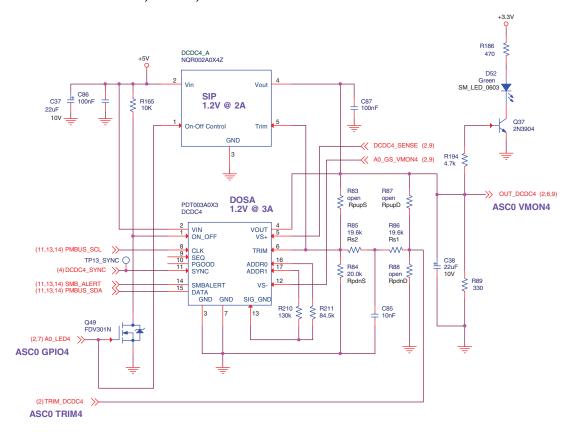

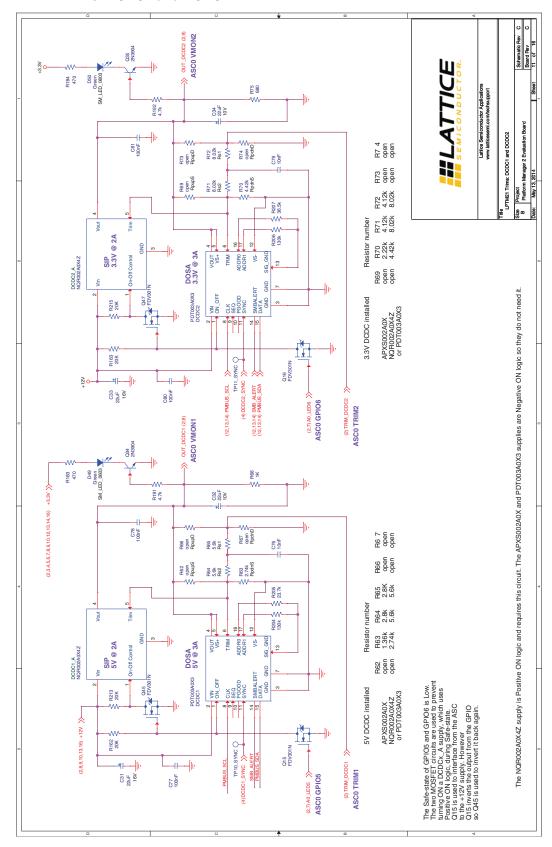

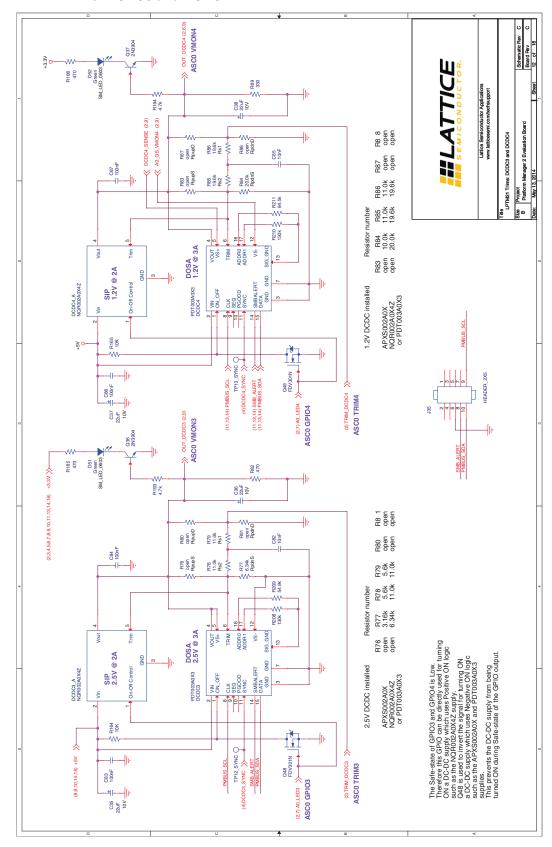

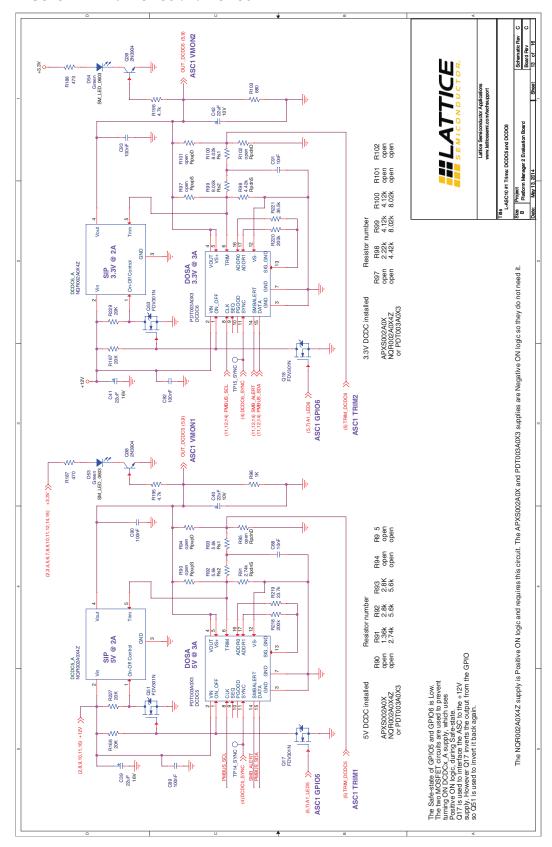

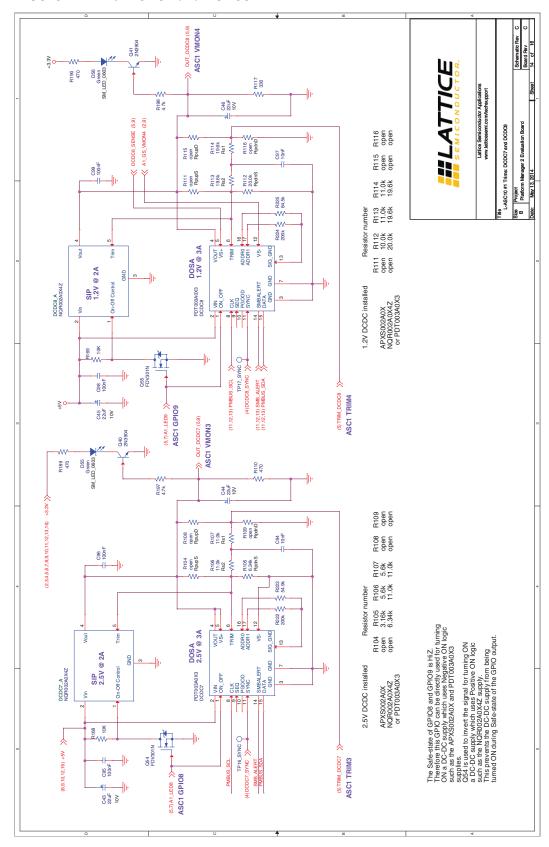

# **Close Loop Trim Operation**

A differentiating feature of the Platform Manager 2 is the Closed Loop Trim (CLT) feature which is used to accurately trim and margin power supplies. The Platform Manager 2 evaluation board provides CLT circuits for up to eight DC-DC power supplies; four (DCDC1 – DCDC4) are controlled by LPTM21 (U1) and four (DCDC5 – DCDC8) are controlled by L-ASC10 (U4). Table 7 lists the installed components and signals associated with CLT operation on the Platform Manager 2 evaluation board.

Table 7. Installed Components and Signals for Closed Loop Trim Operation

| Component / Signals                        | Ref. Des.                                 | Schematic<br>Sheet | Description                                                                           |

|--------------------------------------------|-------------------------------------------|--------------------|---------------------------------------------------------------------------------------|

| Components                                 |                                           |                    |                                                                                       |

| DC-DC Converter                            | DCDC3, DCDC4                              | 12                 | Dual-footprint +5 V input adjustable output power supply. NQR002A0X4Z SIP installed.  |

| DC-DC Converter                            | DCDC7, DCDC8                              | 14                 | Dual-footprint +5 V input adjustable output power supply. NQR002A0X4Z SIP installed.  |

| N-Channel MOSFET - SOT-23                  | Q48,Q49,<br>Q54,Q55                       | 12, 14             | FDV301N N-Channel MOSFET. Inverts the DC-DC enable signal from ASC GPIO for SIP.      |

| Green LED                                  | D51, D52, D55,<br>D56                     | 12, 14             | LED to indicate output of DC-DC is active.                                            |

| LED Bias Resistor                          | R185,R186,<br>R189, R190                  | 12, 14             | 470 Ohm resistor limits the LED current.                                              |

| NPN Transistor – SOT-23                    | Q36,Q37,Q40,<br>Q41                       | 12, 14             | 2N3904 NPN Transistor drives LED on when DC-DC output is active.                      |

| NPN Bias Resistor                          | R193, R194,<br>R197, R198                 | 12, 14             | 4.7 kOhm resistor limits the base current of NPN transistor.                          |

| Tantalum Cap 1                             | C35, C37, C43,<br>C45                     | 12, 14             | 22 uF, 10 V capacitor +5 V DC-DC input filter.                                        |

| Ceramic Bypass Cap                         | C83, C84, C86,<br>C87,C95,C96,<br>C98,C99 | 12, 14             | 100 nF 16 V capacitor +5 V DC-DC input and output filter.                             |

| Tantalum Cap <sup>1</sup>                  | C36, C38, C44,<br>C46                     | 12, 14             | 22 uF, 10 V capacitor +5 V DC-DC output filter.                                       |

| DC-DC Output Load Resistor <sup>1</sup>    | R82, R89,<br>R110,R117                    | 12, 14             | 470 and 330 Ohm resistors pull DC-DC output down to zero when disabled.               |

| DC-DC 3 Trim Resistors <sup>1</sup>        | R76 – R81                                 | 12                 | Resistor values based on Platform Designer Trim Calculator. Three installed.          |

| DC-DC 4 Trim Resistors <sup>1</sup>        | R83 – R88                                 | 12                 | Resistor values based on Platform Designer Trim Calculator. Three installed.          |

| DC-DC 7 Trim Resistors <sup>1</sup>        | R104 – R109                               | 14                 | Resistor values based on Platform Designer Trim Calculator. Three installed.          |

| DC-DC 8 Trim Resistors <sup>1</sup>        | R111 – R116                               | 14                 | Resistor values based on Platform Designer Trim Calculator. Three installed.          |

| Ceramic Cap <sup>1</sup>                   | C82, C85, C94,<br>C97                     | 12, 14             | 10 nF 10 V capacitor: trim network filter.                                            |

| Phoenix 2-Terminal Connector DC-DC 3 and 7 | J19, J23                                  | 9                  | Wire to board connectors to apply off-board loads to DC-DC.                           |

| Phoenix 4-Terminal Connector DC-DC 4 and 8 | J20, J24                                  | 9                  | Wire to board connectors to apply off-board loads to DC-DC with remote sensing.       |

| Ground Sense Resistor                      | R13, R32                                  | 9                  | 100 Ohm resistor: default ground sense connection when off-board sensing is not used. |

| VMON Series Resistor                       | R14, R59                                  | 9                  | 100 Ohm resistor: default VMON connection when off-board sensing is not used.         |

# **Platform Manager 2 Evaluation Board**

| Component / Signals                | Ref. Des. | Schematic<br>Sheet | Description                                                                                                                                     |

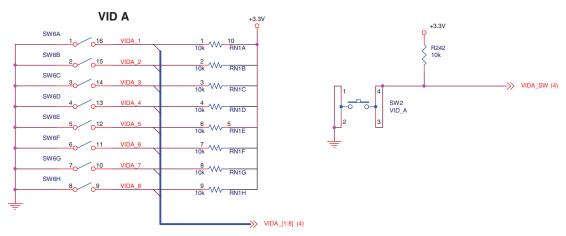

|------------------------------------|-----------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|