## LTC4266 IEEE 802.3at PoE Quad PSE Controller

### DESCRIPTION

Demonstration circuit DC1366B features the LTC®4266, a quad network power controller with  $I^2C^{\otimes}$  interface, designed for use in IEEE 802.3at compliant Power Sourcing Equipment (PSE). Integrated into a tiny 5mm × 7mm 38-pin QFN package are four independent channels controlling external N-channel power MOSFETs. Each port features:

- Reliable 4-Point PD Detection

- Selectable 1 or 2-Event Classification

- Inrush Current Limiting

- Extremely Fast Short-Circuit Protection with Programmable Foldback Current Threshold

- Programmable Cutoff Current Threshold for Class Power Enforcement

- Voltage and Current Readback

- DC Disconnect Sensing

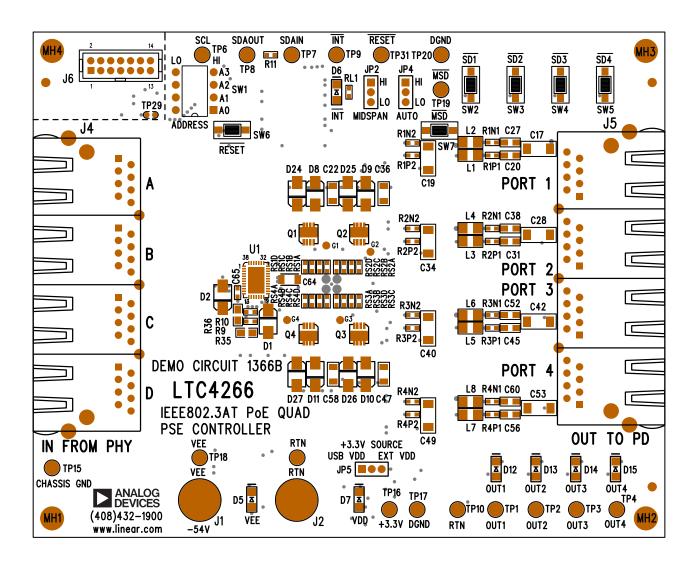

The DC1366B is configured like a midspan PSE with two RJ45 connectors for each port such that gigabit Ethernet data can pass through the board at full line rates while DC power is injected by the LTC4266 on the OUT TO PD side of the board.

Often one of the most challenging aspects of designing a PSE system is the power management software; Analog Devices makes the job easier with the fully-featured LTC4266 register set and a QuikEval™ GUI software application. The GUI allows the user full and easy access to the LTC4266 register set with detailed contextual help info.

LTC4266 example software is available only under a non-disclosure agreement (NDA).

The DC1366B has increased surge protection and more compact Hot Swap MOSFETs over the DC1366A. The DC1366B is Ethernet Alliance™ certified.

Design files for this circuit board are available.

DC1366B

## **QUICK START PROCEDURE**

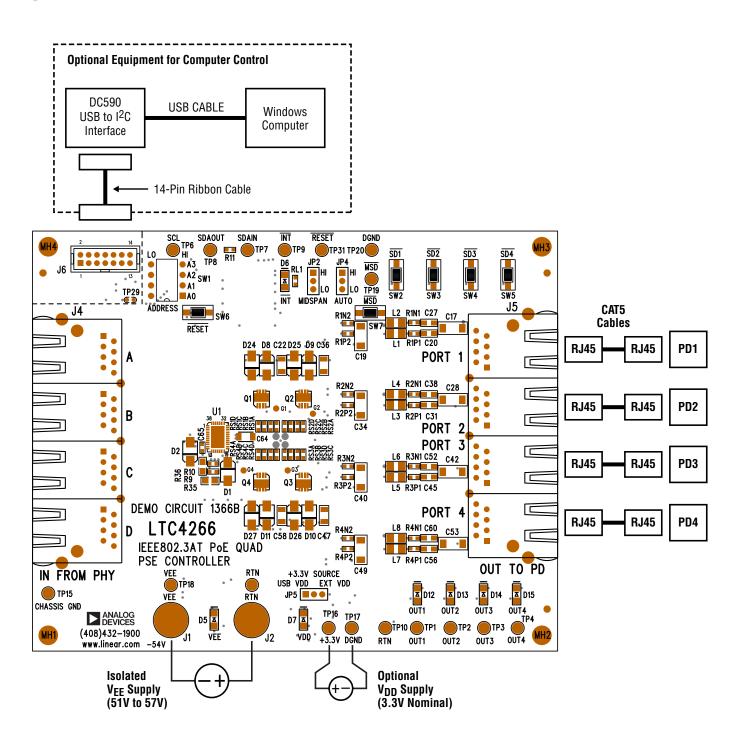

Figure 1 shows the basic setup. The LTC4266 requires two power supply rails:  $V_{DD}$  (nominally 3.3V) and  $V_{EE}$  (nominally –54V). The  $V_{DD}$  supply can be provided by a DC590 board or an external bench supply.

When running QuikEval on a Windows computer, the DC590 is used to interface a USB port on the PC to the  $I^2C$  bus on the DC1366B. The DC590 also provides optoisolation of the  $I^2C$  bus, and an isolated 3.3V supply to run the LTC4266; the user need only provide the  $V_{FF}$  supply.

Alternatively, the user can omit the DC590 and connect an  $I^2C$  master device to the DC1366B. If the DC590 is omitted then a bench power supply must provide  $V_{DD}$ .

For applications where  $I^2C$  control is not required, the LTC4266 features an AUTO mode allowing it to operate completely autonomously.

Choose one of the setup procedures shown on the next page, depending on whether or not the QuikEval GUI application software is required.

### Setup Procedure to Run the QuikEval GUI Software

- Install the GUI software on the PC according to the instructions in the README.txt file included with the GUI software.

- On the DC590:

- a. Set both sides (ISO and SW) of JP5 to ON.

- b. Set JP6 to 3.3V.

- 3. Connect the DC590 to the PC with a standard USB A-B cable.

- a. Verify the computer recognized the USB device. (The first time the DC590 is connected the Hardware Wizard may ask for help to locate the driver. Direct it to the location specified in the README.txt that came with the GUI software.)

- b. Verify the ISO PWR LED on the DC590 is lit.

- 4. On the DC1366B board:

- a. Set JP5 to the USB  $V_{DD}$  position.

- b. Set JP3 to the TIE position.

- c. Set JP4 (AUTO) to the HI position.

- d. If midspan operation is desired set JP2 to HI, for endpoint set to LO.

- 5. Connect the DC590 to the DC1366B with the 14-conductor ribbon cable supplied with the DC1366B. Verify the  $V_{DD}$  LED on the DC1366B is lit.

- 6. Before connecting the main power supply to the DC1366B verify the voltage is between 51V and 57V, and that the main supply is turned off.

- 7. Connect the main power supply to the DC1366B with two banana patch cords as shown in Figure 1. Verify the polarity is correct before turning on the power; positive goes to RTN and negative to  $V_{\text{EE}}$ .

- 8. Turn on the main power supply and verify the  $V_{\text{EE}}$  LED on the DC1366B is lit.

- Connect PDs to any of the ports on the OUT to PD side of the DC1366B and verify they turn on by the respective OUTn LED.

- 10. Launch QuikEval.

## **QUICK START PROCEDURE**

### Setup Procedure without the DC590

- 1. On the DC1366B:

- a. Set JP5 to EXT V<sub>DD</sub>.

- b. Set JP4 (AUTO) to the HI position.

- c. If midspan operation is desired set JP2 to HI, for endpoint set to LO.

- Connect a 3.3V power supply across +3.3V and DGND test points as shown in Figure 1. Turn on the 3.3V supply and verify the V<sub>DD</sub> LED on the DC1366B is lit.

- 3. Before connecting the main power supply to the DC1366B verify the voltage is between 51V and 57V, and that the main supply is turned off.

- 4. Connect the main power supply to the DC1366B with two banana patch cords as shown in Figure 1. Verify the polarity is correct before turning on the power; positive goes to RTN and negative to  $V_{EE}$ .

- 5. Turn on the main power supply and verify the  $V_{\text{EE}}$  LED on the DC1366B is lit.

- 6. Connect PDs to any of the ports on the OUT TO PD side of the DC1366B and verify they turn on by the respective OUTn LED.

## **QUICK START PROCEDURE**

Figure 1. DC1366B Setup

### **OPERATION**

#### Introduction

The DC1366B demonstrates the features and capabilities of the LTC4266, a quad controller for IEEE802.3at Power Sourcing Equipment (PSE). The DC1366B provides a quick and simple, fully compliant PSE solution requiring only a  $V_{EE}$  supply when used in conjunction with the DC590 USB-to- $I_{EE}$ 0 interface board.

#### **Supply Voltages**

The IEEE802.3at standard requires the port output voltage of a type 2 PSE to be in the range of 50V to 57V. The positive side is RTN and the negative side is  $V_{EE}$ . The  $V_{EE}$  supply voltage should be in this range for the sake of compliance; however, the LTC4266 is capable of operating with  $V_{EE}$  down to 30V, the max undervoltage lockout (UVLO) threshold.

Make sure to choose a  $V_{EE}$  supply with enough power to sustain all four ports at maximum load; if the total load is too great for the power supply its voltage may drop below the UVLO threshold, resetting the LTC4266 and shutting off all the ports. The worst case is when all four PDs are class 4: each class 4 PD may draw up to 600mA, totaling 2.4A. Therefore a  $V_{EE}$  supply rated for at least 2.6A is recommended.

The  $V_{DD}$  supply should nominally be 3.3V but the LTC4266 is capable of operating over the range of 3.0V to 4.3V. (The UVLO threshold for the  $V_{DD}$  supply is typically 2.2V.) The LTC4266 chip typically draws only 1.1mA from the  $V_{DD}$  supply; however, LEDs and other components on the DC1366B board also draw current from  $V_{DD}$ , so the total load is typically 9mA to 26mA at 3.3V depending on which LEDs are lit.

## **V<sub>DD</sub>** to DGND Configurations

The DC1366B, LTC4266  $V_{DD}$  supply can be configured in one of two ways. The default DC1366B configuration ties the LTC4266  $V_{DD}$  pin to the AGND pin through a 0 0hm resistor R10. The DGND pin is at -3.3V below the AGND pin. The DC1366B can also be configured for a +3.3V at  $V_{DD}$  relative to AGND by removing R10 and installing a  $0\Omega$  resistor at R9. This ties the LTC4266 DGND pin and AGND pin.

#### **Modes of Operation**

The LTC4266 has four modes of operation:

- Shutdown: Ports are shutdown, detection and classification cycles are disabled.

- Manual: The port does not advance automatically from detection to classification, to power on. It waits for instructions from a host controller via the I<sup>2</sup>C interface.

- Semiauto: The port automatically advances to classification after detecting a PD, but does not turn on power to the PD until told to do so by from a host controller via the I<sup>2</sup>C interface.

- AUTO Pin High: The LTC4266 operates autonomously.

#### **AUTO Pin**

The AUTO pin determines several aspects of the LTC4266 initial behavior. AUTO is sensed by the LTC4266 at power up and after a reset.

If the AUTO pin is high then:

- All ports come up in AUTO pin high mode. Any valid PD will be turned on without software intervention.

- The current-sense resistors are assumed to be  $0.25\Omega$  (which they are on the DC1366B).

- High power is enabled. After the LTC4266 classifies a PD it applies power and automatically sets I<sub>CUT</sub> and I<sub>LIM</sub> appropriately for the class. With high-power enabled a class 4 PD will be able to draw up to 600mA without being cut off.

If the AUTO pin is low then:

- All ports come up in shutdown mode. A host controller must take action in order to power up any PDs.

- The current-sense resistors are assumed to be  $0.50\Omega$ ; a host controller must change this to  $0.25\Omega$  for correct operation of the DC1366B.

- High power is disabled and is enabled by a host controller.

### **OPERATION**

#### Endpoint vs. Midspan

The LTC4266 can be configured either for endpoint or midspan operation without software intervention by setting the MID pin high or low respectively. (You must reset the LTC4266 or cycle the power for the MID pin to be sensed.) The only difference in the behavior of the LTC4266 is that the detection back-off timer is enabled when midspan operation is selected.

Each port can be configured individually as either endspan or midspan via I<sup>2</sup>C commands.

The DC1366B is wired for Alternative-A, MDI-X (power is injected on the data pairs of the CAT5/6e cable; positive on pins 3 and 6 of the RJ45 connector, and negative on pins 1 and 2). The original 802.3af standard required all midspans to use Alternative-B, but 802.3at allows midspans to use Alternative-A.

### **Disconnect Sensing**

The LTC4266 employs DC disconnect sensing only. For the sake of software backward compatibility with the older LTC4259, the LTC4266 includes register bits for enabling AC disconnect sensing, but these bits simply enable the DC disconnect sensing.

#### **Pushbutton Switches**

The DC1366B includes several pushbutton switches to facilitate experimentation with the LTC4266.

- The RESET button (SW6) resets all ports just as if the power supplies were cycled.

- The Masked Shutdown (MSD) button (SW7) will turn off any ports that have their corresponding mask bit set in the MSD register.

- Each port has an individual shut down switch (SW2 through SW5 for ports 1 through 4 respectively).

#### **Masked Shutdown**

The MSD register can be used to pre-assign low-priority to selected ports so they can be shut down quickly when needed.

A PSE system design can utilize the MSD feature in various ways. For example, a PSE system may include a circuit that monitors the  $V_{EE}$  supply; if it becomes overloaded and the voltage begins to sag, the system can dump low-priority ports by asserting the  $\overline{\text{MSD}}$  pin. Shedding excess load quickly may allow the  $V_{EE}$  voltage to recover before it reaches the UVLO threshold, thus avoiding shutting down higher-priority ports.

## I<sup>2</sup>C Addressing

The 7-bit  $I^2C$  address of the LTC4266 is  $010A_3A_2A_1A_0b$ , where  $A_3$  through  $A_0$  are determined by pins AD3 through AD0 respectively. On the DC1366B these pins are controlled by the quad DIP switch, SW1. The LTC4266 has internal pull-up resistors on these pins, so with all four switches of SW1 open the address will be 0101111b.

All LTC4266 chips also respond to the global address 0110000b regardless of the state of their AD3-AD0 pins.

#### I<sup>2</sup>C Bus Lines

The LTC4266 has separate pins for SDAIN and SDAOUT to facilitate the use of opto-couplers. The DC1366B provides test points for both SDAIN and SDAOUT to make it easy to connect to any type of breadboard or development tools. The DC1366B ties SDAIN and SDAOUT with shunt R11.

The DC590 includes pull-up resistors on the SDA and SCL lines, while the DC1366B board has none. If the DC590 board is replaced by a different I<sup>2</sup>C master, the user must make sure there are appropriate pull-up resistors on SDA and SCL.

#### Interrupts

The LTC4266 includes an open-drain interrupt line for signaling the host controller when it needs service. This signal can be accessed on the DC1366B at the INT test point. An LED is also included to indicate an interrupt.

#### **Connecting Multiple DC1366B Boards**

To use multiple DC1366B on a common I<sup>2</sup>C bus, simply connect their J6 connectors together with ribbon cable (14-conductor, 1mm pitch).

Rev B

### **OPERATION**

Up to sixteen DC1366B can be controlled by a single I<sup>2</sup>C master. Remember to set each board to a different I<sup>2</sup>C address using the DIP switch.

The DC590 cannot supply enough current on  $V_{DD}$  for more than five or six DC1366B boards; an external  $V_{DD}$  power supply is recommended if more than five DC1366B boards are connected together.

If a large number of DC1366B boards are connected to a single  $V_{\text{EE}}$  supply, be aware that banana patch cords are only rated for approximately 14A. To avoid exceeding the ampacity of the patch cords, the boards should be connected in a star configuration rather than connecting the boards in a chain.

#### QuikEval GUI Software

The QuikEval GUI application software is a powerful tool for learning the LTC4266 registers. Also available is the LTC4266NDASI software interface data sheet that provides further details on these registers.

### Surge Protection

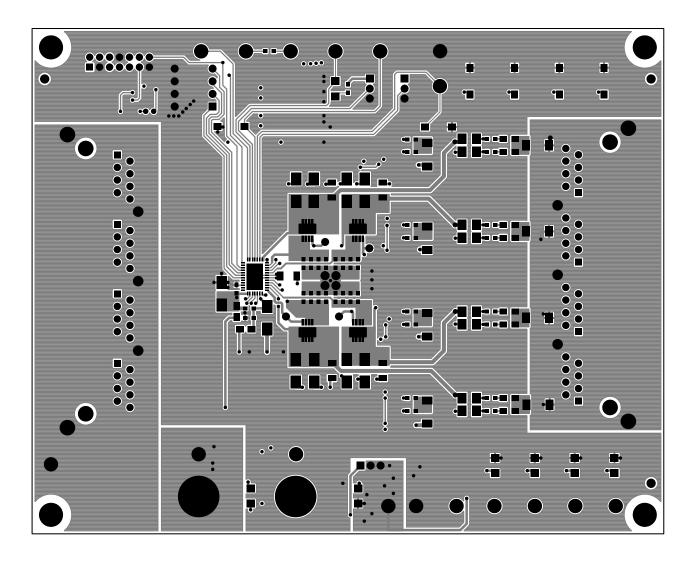

Ethernet ports can be subject to significant cable surge events. To keep PoE voltages below a safe level and protect the application against damage, protection components are required at the main supply, at the LTC4266 supply pins and at each port.

Bulk transient voltage suppression devices and bulk capacitance are required across the main PoE supply and should be sized to accommodate system level surge requirements. The DC1366B diode D18 and capacitor C2 are example components for this protection at the main PoE supply.

Each LTC4266 requires a  $10\Omega$ , 0805 resistor (R35) in series from supply AGND to the LTC4266 AGND pin. Across the LTC4266 AGND pin and V<sub>EE</sub> pin are an SMAJ58A, 58V TVS (D1) and a  $1\mu$ F, 100V bypass capacitor (C64). These components must be placed close to the LTC4266 pins.

Each port requires a pair of S1B clamp diodes: one from OUTn to supply AGND and one from OUTn to supply  $V_{EE}$ . The diodes at the ports steer harmful surges into the supply rails where they are absorbed by the surge suppressors and the  $V_{EE}$  bypass capacitance. The layout of these paths must be low impedance.

Finally, the  $V_{DD}$  logic supply and logic pins may also require additional surge protection. Components D23, C16, R36, D2, and C65 demonstrate surge protection for  $V_{DD}$  to DGND. For a positive  $V_{DD}$  configuration where  $V_{DD}$  is +3.3V above AGND and DGND is tied to AGND, the DC1366B has place holders at D28 and C66 for a 64V TVS and high voltage capacitance from  $V_{DD}$  to  $V_{EE}$ .

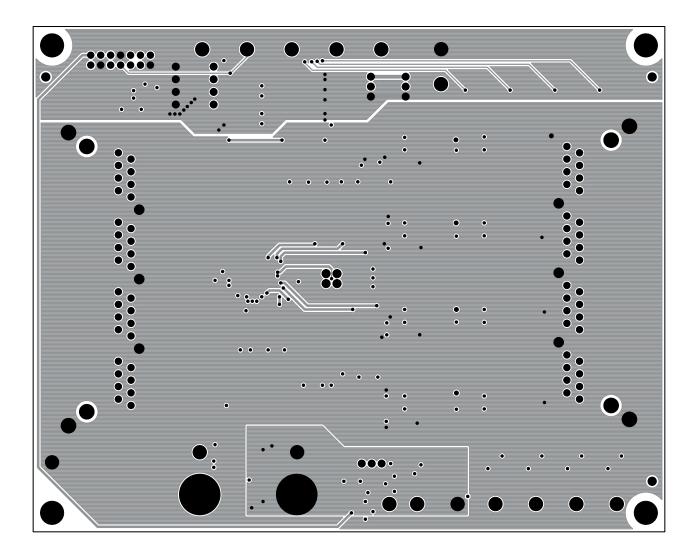

**Top Assembly**

Layer 1

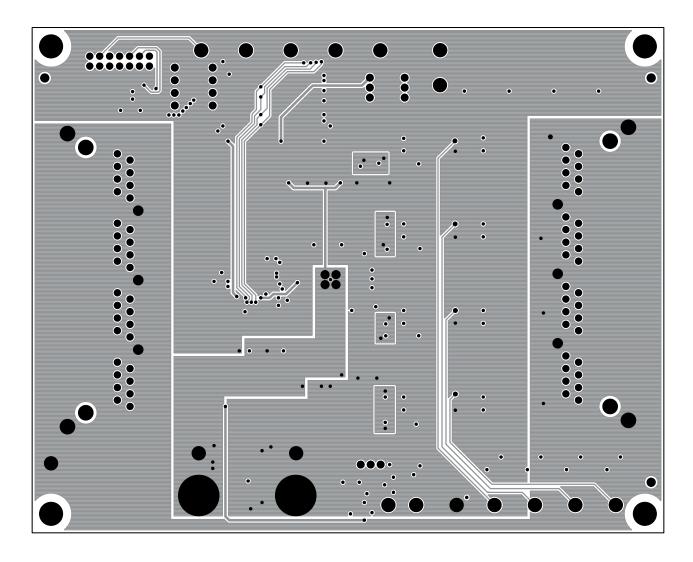

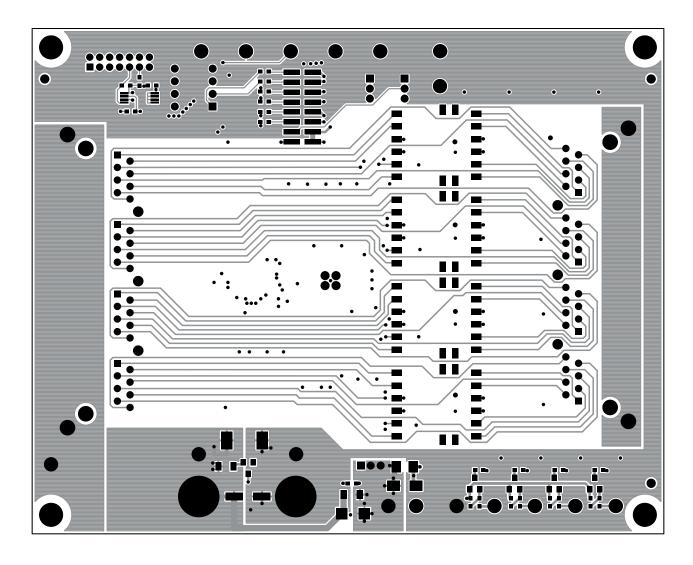

Layer 2

Layer 3

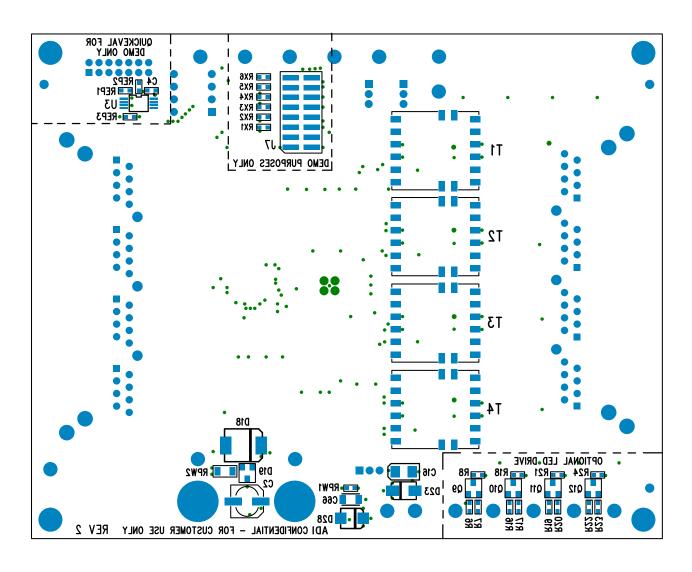

Layer 4

**Bottom Assembly**

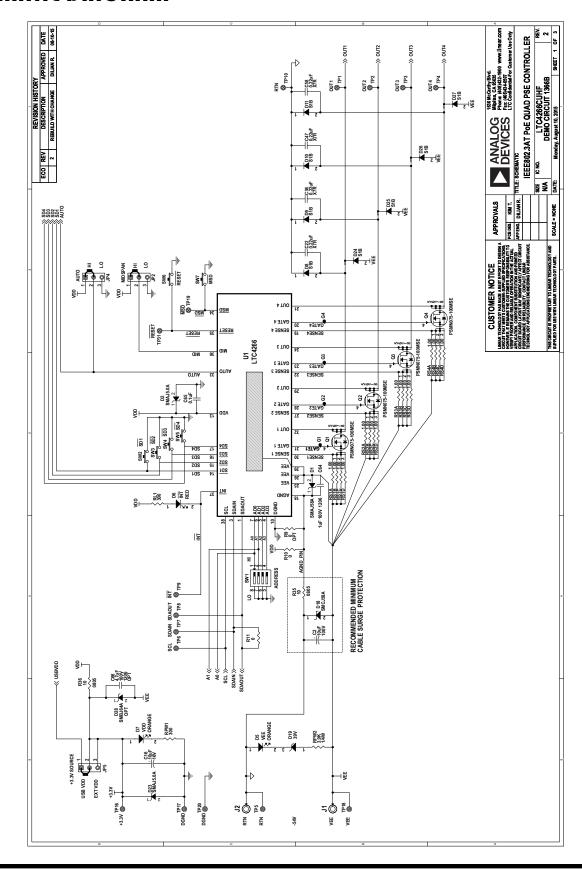

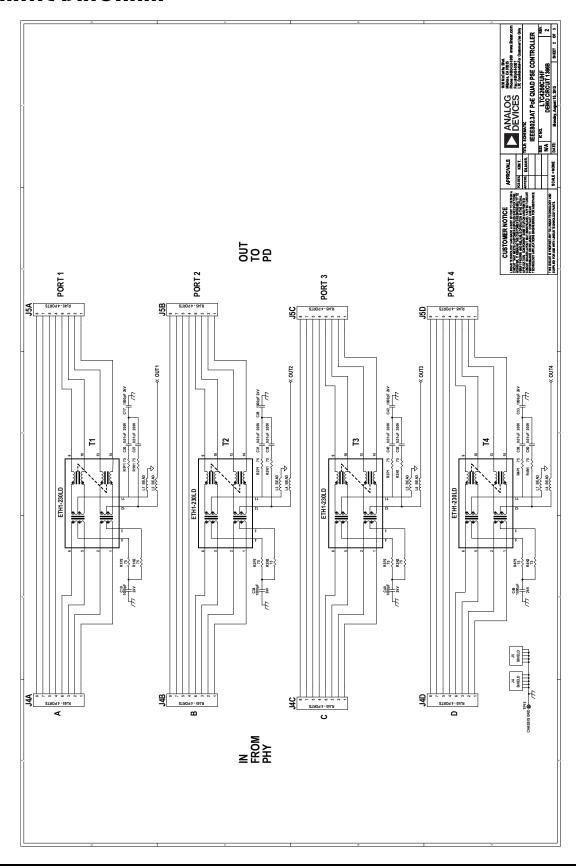

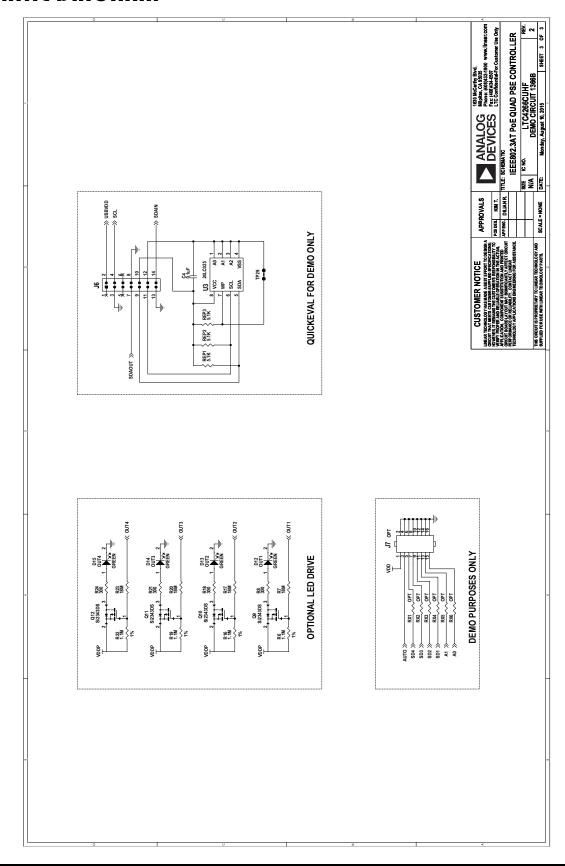

## **SCHEMATIC DIAGRAM**

## **SCHEMATIC DIAGRAM**

## **SCHEMATIC DIAGRAM**

## **REVISION HISTORY**

| REV | DATE  | DESCRIPTION                                                                                    | PAGE NUMBER |

|-----|-------|------------------------------------------------------------------------------------------------|-------------|

| Α   | 12/15 | Replaced Q1-Q4 with NXP PSMN075-100MSE, LFPAK33 package.                                       |             |

|     |       | Replaced SDAIN/SDAOUT jumper, JP3, tie option with resistor shunt R11.                         |             |

|     |       | Changed diode D18 to SMCJ58A, 58V TVS.                                                         |             |

|     |       | Removed 3.3V LDO, U2.                                                                          |             |

|     |       | Added AGND pin surge protection $10\Omega$ resistor R35, moved logic pull-ups to $V_{DD}$ pin. |             |

|     |       | Added $V_{DD}$ pin surge protection $10\Omega$ resistor R36.                                   |             |

|     |       | Added SMAJ5.0A, 5V TVS, D2, across LTC4266 V <sub>DD</sub> and DGND pins.                      |             |

|     |       | Changed diode D23 to SMAJ5.0A, 5V TVS.                                                         |             |

|     |       | Renamed board logic ground to DGND, moved logic ground connections to DGND.                    |             |

|     |       | Renamed V <sub>EE</sub> high side supply connection to RTN.                                    |             |

|     |       | Added R10, V <sub>DD</sub> pin shunt to AGND pin, and R9, DGND pin shunt option to AGND pin.   |             |

|     |       | Moved LED pull-up to +3.3V.                                                                    |             |

| В   | 11/18 | Ethernet Alliance certification logo added.                                                    | 1           |

## DEMO MANUAL DC1366B

#### **FSD Caution**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

#### **Legal Terms and Conditions**

By using the evaluation board discussed herein (together with any tools, components documentation or support materials, the "Evaluation Board"), you are agreeing to be bound by the terms and conditions set forth below ("Agreement") unless you have purchased the Evaluation Board, in which case the Analog Devices Standard Terms and Conditions of Sale shall govern. Do not use the Evaluation Board until you have read and agreed to the Agreement. Your use of the Evaluation Board shall signify your acceptance of the Agreement. This Agreement is made by and between you ("Customer") and Analog Devices, Inc. ("ADI"), with its principal place of business at One Technology Way, Norwood, MA 02062, USA. Subject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal, temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board FOR EVALUATION PURPOSES ONLY. Customer understands and agrees that the Evaluation Board is provided for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board for any other purpose. Furthermore, the license granted is expressly made subject to the following additional limitations: Customer shall not (i) rent, lease, display, sell, transfer, assign, sublicense, or distribute the Evaluation Board; and (ii) permit any Third Party to access the Evaluation Board. As used herein, the term "Third Party" includes any entity other than ADI, Customer, their employees, affiliates and in-house consultants. The Evaluation Board is NOT sold to Customer; all rights not expressly granted herein, including ownership of the Evaluation Board, are reserved by ADI. CONFIDENTIALITY. This Agreement and the Evaluation Board shall all be considered the confidential and proprietary information of ADI. Customer may not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of use of the Evaluation Board or termination of this Agreement, Customer agrees to promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer shall inform ADI of any occurred damages or any modifications or alterations it makes to the Evaluation Board, including but not limited to soldering or any other activity that affects the material content of the Evaluation Board. Modifications to the Evaluation Board must comply with applicable law, including but not limited to the RoHS Directive. TERMINATION. ADI may terminate this Agreement at any time upon giving written notice to Customer agrees to return to ADI the Evaluation Board at that time. LIMITATION OF LIABILITY. THE EVALUATION BOARD PROVIDED HEREUNDER IS PROVIDED "AS IS" AND ADI MAKES NO WARRANTIES OR REPRESENTATIONS OF ANY KIND WITH RESPECT TO IT. ADI SPECIFICALLY DISCLAIMS ANY REPRESENTATIONS, ENDORSEMENTS, GUARANTEES, OR WARRANTIES, EXPRESS OR IMPLIED, RELATED TO THE EVALUATION BOARD INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, TITLE, FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS. IN NO EVENT WILL ADI AND ITS LICENSORS BE LIABLE FOR ANY INCIDENTAL, SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES RESULTING FROM CUSTOMER'S POSSESSION OR USE OF THE EVALUATION BOARD, INCLUDING BUT NOT LIMITED TO LOST PROFITS. DELAY COSTS. LABOR COSTS OR LOSS OF GOODWILL. ADI'S TOTAL LIABILITY FROM ANY AND ALL CAUSES SHALL BE LIMITED TO THE AMOUNT OF ONE HUNDRED US DOLLARS (\$100.00). EXPORT. Customer agrees that it will not directly export the Evaluation Board to another country, and that it will comply with all applicable United States federal laws and regulations relating to exports. GOVERNING LAW. This Agreement shall be governed by and construed in accordance with the substantive laws of the Commonwealth of Massachusetts (excluding conflict of law rules). Any legal action regarding this Agreement will be heard in the state or federal courts having jurisdiction in Suffolk County, Massachusetts, and Customer hereby submits to the personal jurisdiction and venue of such courts. The United Nations Convention on Contracts for the International Sale of Goods shall not apply to this Agreement and is expressly disclaimed.

Rev B