#### **CMOSIC**

# **On-Screen Display Controller**

http://onsemi.com

#### Overview

The LC74736PT is an on-screen display CMOS IC that displays characters and patterns on a TV screen under the control of a microcontroller.

For QVGA display, the LC74736PT supports the use of both a  $16 \times 16$  dot character font and a  $16 \times 16$  dot graphic font with 16 colors.

For WVGA display, the LC74736PT supports the use of both a  $24 \times 32$  dot character font and a  $24 \times 32$  dot graphic font with 16 colors.

The LC74736PT can also implement extremely varied displays by the use of an external ROM.

The LC74736PT supports both QVGA (480×234) and WVGA (800×480).

#### **Features**

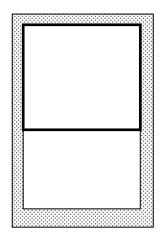

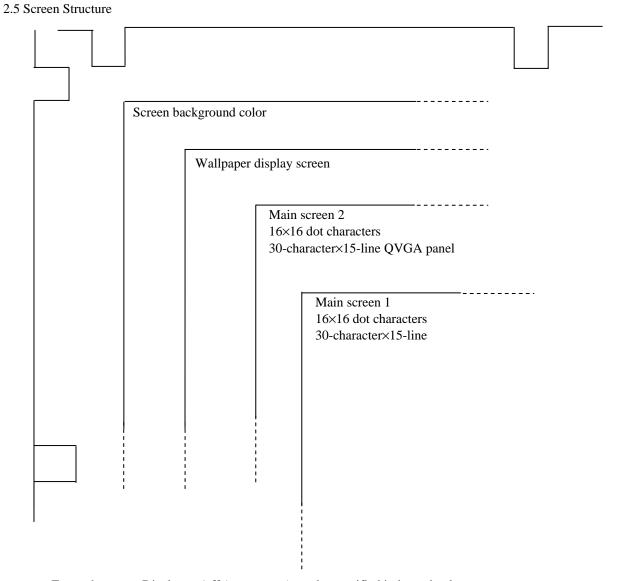

(1) Screen structure

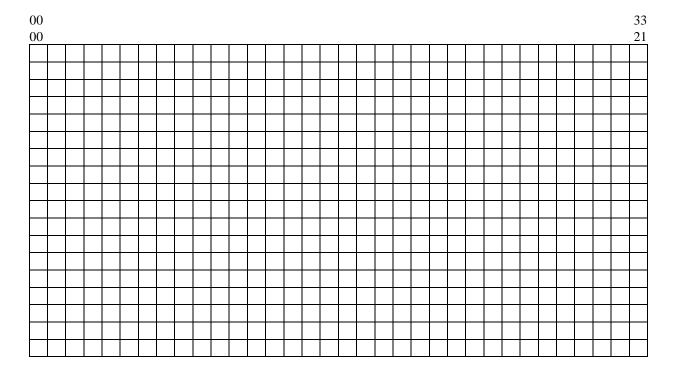

Main: 2 screens (1 screen for WVGA display)

30 characters×15 lines (up to 450 characters) on a QVGA panel

33 characters×15 lines (up to 495 characters) on a WVGA panel

(Up to 34 characters×18 lines)

Wallpaper display screen:

QVGA mode: maximum Permanent repetition of a 4×4 (horizontal×vertical) character pattern Permanent repetition of a 2×2 (horizontal×vertical) character pattern

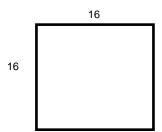

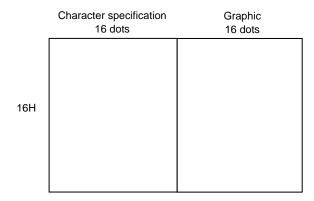

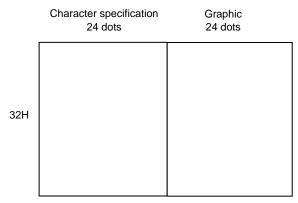

#### (2) Character structure

QVGA mode: About 9MHz

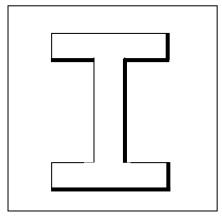

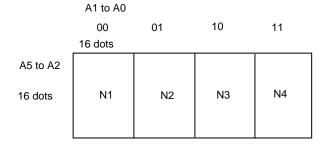

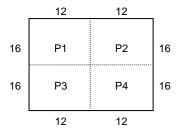

16 dots (horizontal) ×16 dots (vertical): Character display 16 dots (horizontal) ×16 dots (vertical): Graphic glyph display

WVGA mode: About 33.2MHz

24 dots (horizontal) ×32 dots (vertical): Character display 24 dots (horizontal) ×32 dots (vertical): Graphic glyph display

Character display clock:

LC oscillator (about 10MHz)

External clock signal input (up to 40MHz)

Built-in PLL (VCO) (7 to 40MHz)

#### (3) Number of characters

QVGA mode

Up to 16384 characters when an external 16-bit 16M ROM is used.

#### WVGA mode

Up to 4096 characters when an external 16-bit 16M ROM is used.

No internal ROM

Internal character RAM QVGA: 4 characters, WVGA: 1 character

(4) Character sizes: Four horizontal sizes  $(1\times, 2\times, 3\times, \text{ and } 4\times)$

Four vertical sizes  $(1\times, 2\times, 3\times, \text{ and } 4\times)$

(The character size is specified in line units.)

(5) Display start positions: 1024 positions in the horizontal direction and 512 positions in the vertical direction.

Setting units: Horizontal: 1 dot (in screen units)

Vertical: 1 dot (in screen units)

- (6) Display functions

- Blinking specification (in character units)

Period: 1/64, 1/32, and 1/16 of the vertical sync signal (in screen units)

Duty: Fixed at 50%

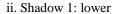

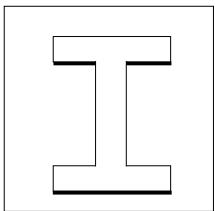

• Box (raised or recessed) display

Raised/recessed specification

Left: Off/on specification

Right: Off/on specification

Top: Off/on specification

Bottom: Off/on specification

(in character units)

(in character units)

(in character units)

- Border specification (in line units): Only valid with glyphs from the character font.

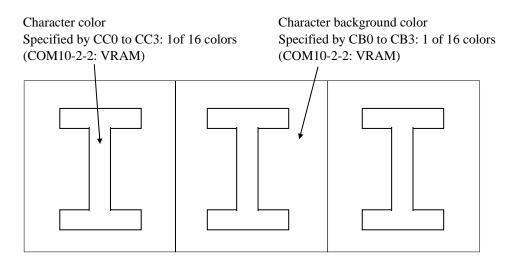

- (7) Color specification

#### Character

Character color (in character units):

1 of 16 colors can be specified.

Character background color (in character units):

1 of 16 colors can be specified.

• Border color (in line units): 1 of 16 colors can be specified.

#### Graphic

• 16 types can be specified by ROM data

#### Graphic 2

• 16 types can be specified by ROM data 1 color type can be changed.

#### Graphic 3

- 16 types can be specified by ROM data 1 color table type can be changed.

- Box (raised or recessed) color (line units): 1 of 16 colors can be specified.

- Background color (screen units): 1 of 16 colors can be specified.

- (8) Color table (palette)

- Sixteen colors can be selected from a set of 4096 colors (One of which is specified to be transparent.)

- Number of color tables: 4. This allows up to 64 colors to be displayed at the same time.

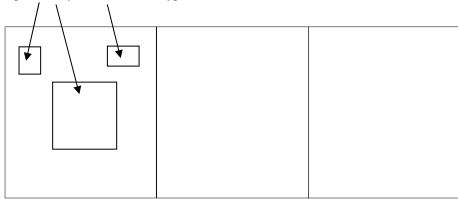

- (9) Wallpaper screen (Graphics glyphs only)

Wallpaper display: Repeated display under the main screen

(up to 4 characters horizontally by 4 characters vertically).

Sprite character display: Displayed above the main screen

(up to 4 characters horizontally by 4 characters vertically).

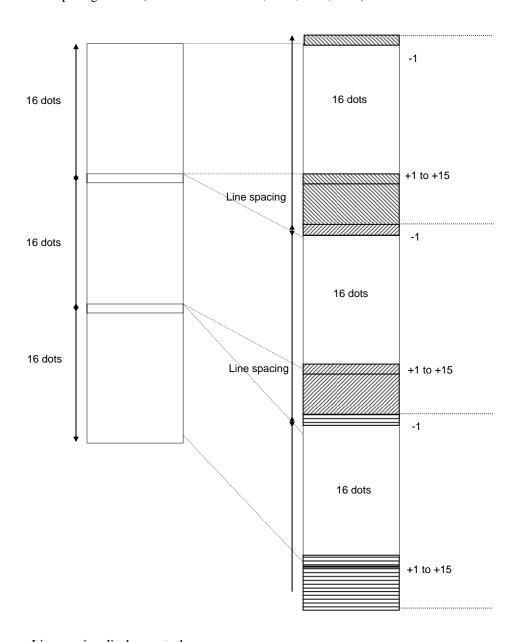

(10) Line spacing control

0-15 scan lines (in line units)

(11) Output

Analog RGB output (to 20MHz)

Digital RGB output (4 bits per color)

BLK (OSD display period signal)

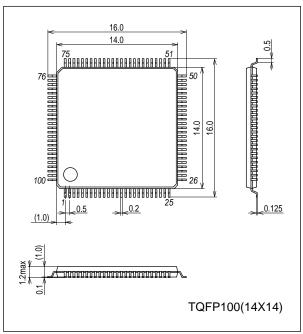

Package: TQFP100 Voltage: 3.3V

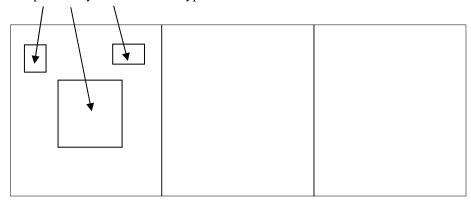

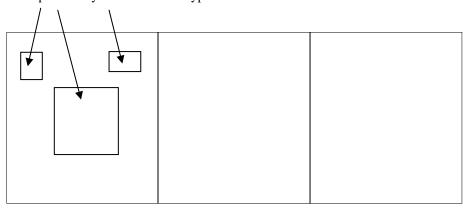

## **Package Dimensions**

unit: mm (typ)

3274

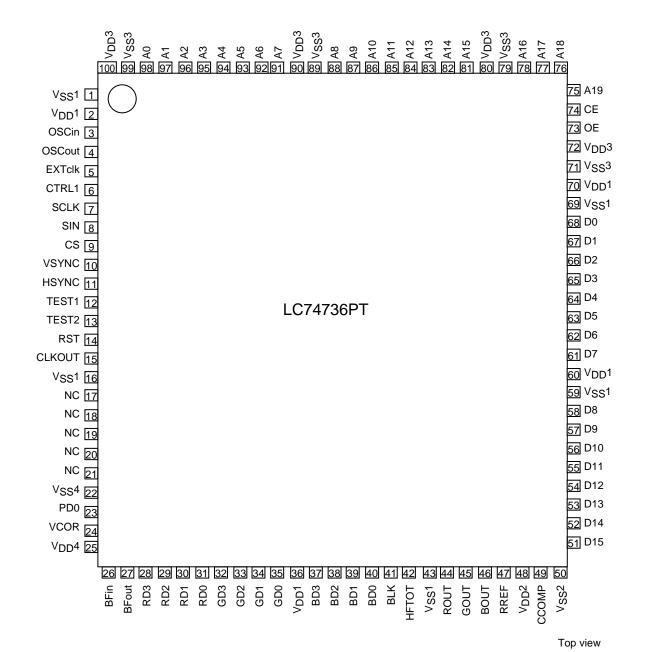

#### **Pin Assignment**

# **Pin Functions**

| Pin No. | Symbol            | Туре                           | Functional description                                                        |

|---------|-------------------|--------------------------------|-------------------------------------------------------------------------------|

| 1       | V <sub>SS</sub> 1 | Ground                         | Connect a ground to this pin. (Digital system ground)                         |

| 2       | V <sub>DD</sub> 1 | Power supply (+3.3V)           | Digital system power supply: +3.3V                                            |

| 3       | OSCin             | LC oscillator                  | Connect to the character output dot clock generator oscillator coil and       |

| 4       | OSCout            | _                              | capacitor.                                                                    |

| 5       | EXTclk            | External clock signal input    | Receives an external clock signal.                                            |

| 9       | EXTOR             | External clock signal input    | Capacitor coupling, 50% duty cycle, 0.5Vp-p or higher                         |

| 6       | CTRL1             | OSCin oscillator input control | Switches between external clock input mode and LC oscillator mode.            |

|         |                   |                                | Low: LC oscillator, high: external clock input MORE+                          |

|         |                   |                                | OR control with MORE+ command                                                 |

| 7       | SCLK              | Clock input                    | Clock input for the serial data input system                                  |

|         |                   |                                | MORE+ (This input has hysteresis characteristics.)                            |

| 8       | SIN               | Data input                     | Serial data input                                                             |

|         | CS                | Forthern                       | MORE+ (This input has hysteresis characteristics.)                            |

| 9       | CS                | Enable input                   | Enable input for the serial data input system. Serial data input is enabled   |

|         |                   |                                | when this pin is set low.  MORE+ (This input has hysteresis characteristics.) |

| 10      | VSYNC             | Vertical sync signal input     | Vertical sync signal input                                                    |

| . •     |                   |                                | MORE+ (This input has hysteresis characteristics.)                            |

| 11      | HSYNC             | Horizontal sync signal input   | Horizontal sync signal input                                                  |

|         |                   |                                | MORE+ (This input has hysteresis characteristics.)                            |

| 12      | TEST1             | Test mode control 1            | Test mode control 1                                                           |

|         |                   |                                | Low: normal operation, high: test mode MORE+                                  |

| 13      | TEST2             | Test mode control 2            | Test mode control 2                                                           |

|         |                   |                                | Low: normal operation, high: test mode (scan mode) MORE+                      |

| 14      | RST               | Reset input                    | System reset input                                                            |

| 45      | CLKOUT            | Clark systems                  | MORE+ (This input has hysteresis characteristics.)                            |

| 15      | CLKOUT            | Clock output                   | Clock output                                                                  |

| 16      | V <sub>SS</sub> 1 | Ground                         | Connect a ground to this pin. (Digital system ground)                         |

| 17      | NC                |                                |                                                                               |

| 18      | NC                |                                |                                                                               |

| 19      | NC                |                                |                                                                               |

| 20      | NC                |                                |                                                                               |

| 21      | NC                |                                |                                                                               |

| 22      | V <sub>SS</sub> 4 | Ground                         | Connect a ground tro this pin. (PLL system power supply)                      |

| 23      | PD0               | PLL charge pump output         | Charge pump output                                                            |

|         |                   |                                | Connect a LPF (lug lead filter) to this pin.                                  |

|         |                   | PLL VCO control voltage input  | Voltage input for internal VCO control                                        |

| 24      | VCOR              | VCO variable range adjustment  | Used to adjust variable voltage range of internal VCO.                        |

|         |                   |                                | Connect a resistor to this pin.                                               |

| 25      | V <sub>DD</sub> 4 | Power supply (+3.3V)           | PLL system power supply: +3.3V                                                |

| 26      | BFin              | Amplifier input                | Oscillation input for external VCO                                            |

| 27      | BFout             | Amplifier output               | Oscillation output for external VCO                                           |

| 28      | RD3               | Rout output: bit 3             | Rout output                                                                   |

| 29      | RD2               | Rout output: bit 2             | This is a 4-bit digital output with values from 0000 to 1111.                 |

| 30      | RD1               | Rout output: bit 1             |                                                                               |

| 31      | RD0               | Rout output: bit 0             |                                                                               |

| 32      | GD3               | Gout output: bit 3             | Gout output                                                                   |

| 33      | GD2               | Gout output: bit 2             | This is a 4-bit digital output with values from 0000 to 1111.                 |

| 34      | GD1               | Gout output: bit 1             |                                                                               |

|         |                   | -                              |                                                                               |

| 35      | GD0               | Gout output: bit 0             | Digital system assure to 2007                                                 |

| 36      | V <sub>DD</sub> 1 | Power supply (+3.3V)           | Digital system power supply: +3.3V                                            |

Continued from preceding page.

| Pin No. | n preceding page<br>Symbol | Type                                  | Functional description                                            |

|---------|----------------------------|---------------------------------------|-------------------------------------------------------------------|

| 37      | BD3                        | Bout output: bit 3                    | Bout output                                                       |

| 38      | BD2                        | Bout output: bit 2                    | This is a 4-bit digital output with values from 0000 to 1111.     |

| 39      | BD1                        | Bout output: bit 1                    |                                                                   |

| 40      | BD0                        | Bout output: bit 0                    |                                                                   |

| 41      | BLK                        | Blanking signal output                | This signal indicates the OSD display period.                     |

| 42      | HFTOT                      | Halftone control signal output        | OSD halftone period control signal                                |

|         |                            |                                       | Synthesized in the next stage IC.                                 |

| 43      | V <sub>SS</sub> 1          | Ground                                | Connect a ground to this pin. (Digital system ground)             |

| 44      | Rout                       | Rout output: analog                   | D/A converter (4 bits) output. Connect a resistor Ro to this pin. |

| 45      | Gout                       | Gout output: analog                   | D/A converter (4 bits) output. Connect a resistor Ro to this pin. |

| 46      | Bout                       | Bout output: analog                   | D/A converter (4 bits) output. Connect a resistor Ro to this pin. |

| 47      | RREF                       | Reference resistor connection         | Connect a reference register to this pin.                         |

| 48      | V <sub>DD</sub> 2          | Power supply (+3.3V)                  | D/A converter power supply: +3.3V                                 |

| 49      | CCOMP                      | Phase correction capacitor connection | Capacitor connection: 1.5µF                                       |

| 50      | V <sub>SS</sub> 2          | Ground                                | Connect a ground to this pin. (D/A converter ground)              |

| 51      | D15                        | Data input 15                         | ROM data input 15. MORE+ [MSB]                                    |

| 52      | D14                        | Data input 14                         | ROM data input 14. MORE+                                          |

| 53      | D13                        | Data input 13                         | ROM data input 13. MORE+                                          |

| 54      | D12                        | Data input 12                         | ROM data input 12. MORE+                                          |

| 55      | D11                        | Data input 11                         | ROM data input 11. MORE+ [MSB]                                    |

| 56      | D10                        | Data input 10                         | ROM data input 10. MORE+                                          |

| 57      | D9                         | Data input 9                          | ROM data input 9. MORE+                                           |

| 58      | D8                         | Data input 8                          | ROM data input 8. MORE+                                           |

| 59      | V <sub>SS</sub> 1          | Ground                                | Connect a ground to this pin. (Digital system ground)             |

| 60      | V <sub>DD</sub> 1          | Power supply (+3.3V)                  | Digital system power supply: +3.3V                                |

| 61      | D7                         | Data input 7                          | ROM data input 7. MORE+                                           |

| 62      | D6                         | Data input 6                          | ROM data input 6. MORE+                                           |

| 63      | D5                         | Data input 5                          | ROM data input 5. MORE+                                           |

| 64      | D4                         | Data input 4                          | ROM data input 4. MORE+                                           |

| 65      | D3                         | Data input 3                          | ROM data input 3. MORE+                                           |

| 66      | D2                         | Data input 2                          | ROM data input 2. MORE+                                           |

| 67      | D1                         | Data input 1                          | ROM data input 1. MORE+                                           |

| 68      | D0                         | Data input 0                          | ROM data input 0. MORE+ [LSB][LSB]                                |

| 69      | V <sub>SS</sub> 1          | Ground                                | Connect a ground to this pin. (Digital system ground)             |

| 70      | V <sub>DD</sub> 1          | Power supply (+3.3V)                  | Power supply: (+3.3V: Digital system)                             |

| 71      | V <sub>SS</sub> 3          | Ground                                | Connect a ground to this pin. (External ROM output system ground) |

| 72      | V <sub>DD</sub> 3          | Power supply (+3.3 or +5.5V)          | Power supply (External ROM output system power supply)            |

| 73      | ŌĒ                         | Output enable                         | ROM output enable output. This is an active low output.           |

| 74      | CE                         | Chip enable                           | ROM chip enable output. This is an active low output.             |

| 75      | A19                        | Address output 19                     | ROM address output 19                                             |

| 76      | A18                        | Address output 18                     | ROM address output 18                                             |

| 77      | A17                        | Address output 17                     | ROM address output 17                                             |

| 78      | A16                        | Address output 16                     | ROM address output 16                                             |

| 79      | V <sub>SS</sub> 3          | Ground                                | Connect a ground to this pin. (External ROM output system ground) |

| 80      | V <sub>DD</sub> 3          | Power supply (+3.3 or +5.5V)          | Power supply (External ROM output system power supply)            |

| 81      | A15                        | Address output 15                     | ROM address output 15                                             |

| 82      | A14                        | Address output 14                     | ROM address output 14                                             |

| 83      | A13                        | Address output 13                     | ROM address output 13                                             |

| 84      | A12                        | Address output 12                     | ROM address output 12                                             |

| ٠.      | ···-                       |                                       |                                                                   |

Continued from preceding page.

| Pin No. | Symbol            | Туре                         | Functional description                                            |

|---------|-------------------|------------------------------|-------------------------------------------------------------------|

| 86      | A10               | Address output 10            | ROM address output 10                                             |

| 87      | A9                | Address output 9             | ROM address output 9                                              |

| 88      | A8                | Address output 8             | ROM address output 8                                              |

| 89      | V <sub>SS</sub> 3 | Ground                       | Connect a ground to this pin. (External ROM output system ground) |

| 90      | V <sub>DD</sub> 3 | Power supply (+3.3 or +5.5V) | Power supply (External ROM output system power supply)            |

| 91      | A7                | Address output 7             | ROM address output 7                                              |

| 92      | A6                | Address output 6             | ROM address output 6                                              |

| 93      | A5                | Address output 5             | ROM address output 5                                              |

| 94      | A4                | Address output 4             | ROM address output 4                                              |

| 95      | А3                | Address output 3             | ROM address output 3                                              |

| 96      | A2                | Address output 2             | ROM address output 2                                              |

| 97      | A1                | Address output 1             | ROM address output 1                                              |

| 98      | A0                | Address output 0             | ROM address output 0                                              |

| 99      | V <sub>SS</sub> 3 | Ground                       | Connect a ground to this pin. (External ROM output system ground) |

| 100     | V <sub>DD</sub> 3 | Power supply (+3.3 or +5.5V) | Power supply (External ROM output system power supply)            |

## **Specifications**

## Absolute Maximum Ratings at Ta=25°C

| Parameter                 | Symbol             | Conditions                                             | Ratings                                       | Unit |

|---------------------------|--------------------|--------------------------------------------------------|-----------------------------------------------|------|

| Supply voltage            | V <sub>DD</sub> 1  | $V_{DD}1, V_{DD}2$ , and $V_{DD}4$                     | V <sub>SS</sub> -0.3 to V <sub>SS</sub> +4.6  | V    |

|                           | V <sub>DD</sub> 3  | V <sub>DD</sub> 3                                      | V <sub>SS</sub> -0.3 to V <sub>SS</sub> +6.0  | V    |

| Input voltage             | $V_{IN}$           | All input pins                                         | V <sub>SS</sub> -0.3 to V <sub>DD</sub> 1+0.3 | V    |

| Output voltage            | V <sub>OUT</sub> 1 | RD3 to RD0, GD3 to GD0, BD3 to BD0, BLK, HFTOT outputs | V <sub>SS</sub> -0.3 to V <sub>DD</sub> 1+0.3 | V    |

|                           | V <sub>OUT</sub> 2 | A0 to 19, CE, OE outputs                               | V <sub>SS</sub> -0.3 to V <sub>DD</sub> 3+0.3 | V    |

| Maximum power dissipation | Pd max             |                                                        | 275                                           | mW   |

| Operating temperature     | Topr               |                                                        | -40 to +85                                    | °C   |

| Storage temperature       | Tstg               |                                                        | -40 to +125                                   | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

## **Recommended Operating Conditions**

| Down store                         | O. make all       | Condition -                                                               |                      | Ratings |                      | l lais |

|------------------------------------|-------------------|---------------------------------------------------------------------------|----------------------|---------|----------------------|--------|

| Parameter                          | Symbol            | Conditions                                                                | min                  | typ     | max                  | Unit   |

| Supply voltage                     | V <sub>DD</sub> 1 | V <sub>DD</sub> 1, 2, and V <sub>DD</sub> 4                               | 3.0                  | 3.3     | 3.6                  | V      |

|                                    | V <sub>DD</sub> 3 | V <sub>DD</sub> 3                                                         | 3.0                  | 3.3     | 5.5                  | V      |

| Input high-level voltage           | V <sub>IH</sub> 1 | CTRL1, TEST1, TEST2                                                       | 0.7V <sub>DD</sub> 1 |         | 5.5                  | V      |

|                                    | V <sub>IH</sub> 2 | SCLK, SIN, $\overline{\text{CS}}$ , VSYNC, HSYNC, $\overline{\text{RST}}$ | 0.8V <sub>DD</sub> 1 |         | 5.5                  | V      |

|                                    | V <sub>IH</sub> 3 | D0 to D15                                                                 | 0.7V <sub>DD</sub> 1 |         | 5.5                  | V      |

| Input low-level voltage            | V <sub>IL</sub> 1 | CTRL1, TEST1, TEST2                                                       | V <sub>SS</sub> -0.3 |         | 0.3V <sub>DD</sub> 1 | V      |

|                                    | V <sub>IL</sub> 2 | SCLK, SIN, $\overline{\text{CS}}$ , VSYNC, HSYNC, $\overline{\text{RST}}$ | V <sub>SS</sub> -0.3 |         | 0.2V <sub>DD</sub> 1 | V      |

|                                    | V <sub>IH</sub> 3 | D0 to D11                                                                 | V <sub>SS</sub> -0.3 |         | 0.3V <sub>DD</sub> 1 | V      |

| Oscillator frequency (LC)          | FOSC1             | OSCin and OSCout oscillator pins (LC oscillator)                          |                      | 10      |                      | MHz    |

| External clock input               | FOSC2             | OSCin, V <sub>DD</sub> 1 = 3.3V                                           |                      | 33      | 40                   | MHz    |

|                                    | V <sub>IN</sub> 1 | V <sub>DD</sub> 1 = 3.3V CTRL1 = high                                     | 0.5                  |         | 3.3                  | Vp-p   |

| Oscillator frequency (VCO)         | FOSC3             | VCO oscillator (internal)                                                 | 7                    |         | 40                   | MHz    |

| D/A converter (4-bit, 3 ch)        | Vrefda            | Reference voltage                                                         |                      | 1.1     |                      | V      |

| When maximum output voltage = 0.7V | Rfda              | Output load resistance<br>ROUT, GOUT, BOUT                                | 120                  |         | 225                  | Ω      |

|                                    | Rref              | Reference load resistance, RREF                                           |                      | 1100    |                      | Ω      |

# **Electrical Characteristics** at Ta = -40 to +85°C, $V_{DD} = 3.3V$ unless otherwise specified

| Dorometer                 | Cumbal                       | Pin                                                            | Conditions                                          |                           | Ratings |     | Unit |

|---------------------------|------------------------------|----------------------------------------------------------------|-----------------------------------------------------|---------------------------|---------|-----|------|

| Parameter                 | Symbol                       | Pin                                                            | Conditions                                          | min                       | typ     | max | Unit |

| Output high-level voltage | V <sub>OH</sub> 1            | RD3 to RD0, GD3 to GD0, BD3 to BD0, BLK, and HFTOT outputs     | $V_{DD}1 = 3.0V$<br>$I_{OH}1 = -8mA$                | V <sub>DD</sub> 1<br>-0.8 |         |     | V    |

|                           | V <sub>OH</sub> <sup>2</sup> | A0 to A19, $\overline{\text{CE}}$ , and $\overline{\text{OE}}$ | $V_{DD}3 = 3.0V$<br>$I_{OH}2 = -8mA$                | V <sub>DD</sub> 3<br>-0.8 |         |     | V    |

|                           | VOH3                         | A0 to A19, $\overline{\text{CE}}$ , and $\overline{\text{OE}}$ | $V_{DD}3 = 4.5V$<br>$I_{OH}3 = -8mA$                | V <sub>DD</sub> 3<br>-0.8 |         |     | V    |

| Output low-level voltage  | V <sub>OL</sub> 1            | RD3 to RD0, GD3 to GD0, BD3 to BD0, BLK, and HFTOT outputs     | V <sub>DD</sub> 1 = 3.0V<br>I <sub>OL</sub> 1 = 8mA |                           |         | 0.4 | V    |

|                           | V <sub>OL</sub> 2            | A0 to A19, $\overline{\text{CE}}$ , and $\overline{\text{OE}}$ | $V_{DD}3 = 3.0V$ $I_{OL}2 = 8mA$                    |                           |         | 0.4 | V    |

|                           | V <sub>OL</sub> 3            | A0 to A19, CE, and OE                                          | V <sub>DD</sub> 3 = 4.5V<br>I <sub>OL</sub> 3 = 8mA |                           |         | 0.4 | V    |

| Input current             | I <sub>IH</sub> 1            | CTRL1, TEST1, TEST2 SCLK, SIN, CS, VSYNC, HSYNC, RST           | $V_{IN} = V_{DD}1$                                  |                           |         | 10  | μА   |

|                           | I <sub>IH</sub> 2            | D0 to D15                                                      | $V_{IN} = V_{DD}3$                                  |                           |         | 10  | μΑ   |

|                           | I <sub>IL</sub> 1            | CTRL1, TEST1, TEST2<br>SCLK, SIN, CS, VSYNC, HSYNC             | V <sub>IN</sub> = V <sub>SS</sub>                   | -10                       |         |     | μΑ   |

|                           | I <sub>IL</sub> 2            | D0 to D15                                                      | V <sub>IN</sub> = V <sub>SS</sub>                   | -10                       |         |     | μΑ   |

| Operating current drain   | I <sub>DD</sub> 1            | V <sub>DD</sub> 1                                              | All outputs open OSCin: 20MHz                       |                           |         | 25  | mA   |

|                           | $I_{DD}^2$                   | V <sub>DD</sub> 2                                              | D/A on                                              |                           |         | 22  | mA   |

|                           | I <sub>DD</sub> 3            | V <sub>DD</sub> 3                                              |                                                     |                           |         | 10  | mA   |

|                           | I <sub>DD</sub> 4            | V <sub>DD</sub> 4                                              | VCO on                                              |                           |         | 22  | mA   |

| D/A converter             | CLK                          | Clock frequency                                                |                                                     |                           |         | 20  | MHz  |

|                           | V max                        | Maximum output voltage                                         | V <sub>DD</sub> 2 = 3.3V                            | 0.25                      |         | 1.5 | V    |

|                           | V min0                       | Minimum output voltage                                         | V <sub>DD</sub> 2 = 3.3V                            |                           | 0       |     | V    |

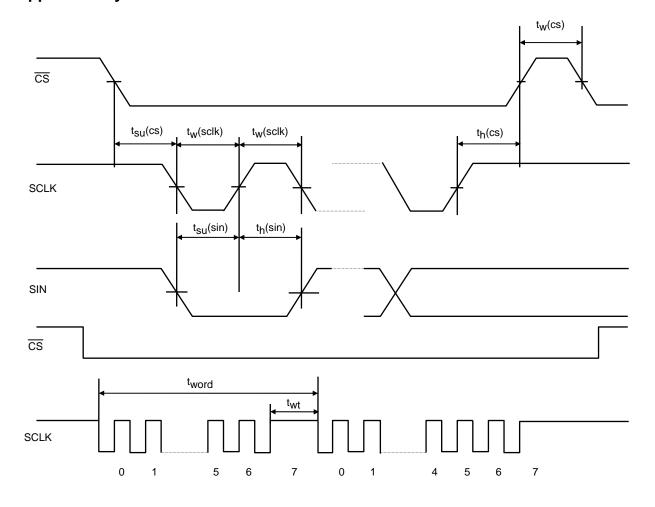

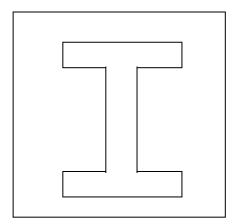

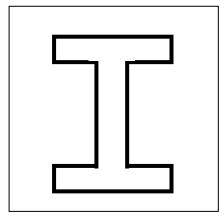

# **Timing Characteristics**

**OSD Write** (See figure 1.) at Ta = -40 to  $+85^{\circ}C$ ,  $V_{DD}1 = 3.3V \pm 0.3V$

| Danamatan                 | Occaditions           |                                  | l lada |     |     |      |

|---------------------------|-----------------------|----------------------------------|--------|-----|-----|------|

| Parameter                 | Symbol                | Conditions                       | min    | typ | max | Unit |

| Minimum input pulse width | t <sub>W</sub> (sclk) | SCLK                             | 200    |     |     | ns   |

|                           | t <sub>W</sub> (cs)   | CS (The period CS is high)       | 1      |     |     | μs   |

| Data setup time           | t <sub>su</sub> (cs)  | <u>cs</u>                        | 200    |     |     | ns   |

|                           | t <sub>SU</sub> (sin) | SIN                              | 200    |     |     | ns   |

| Data hold time            | t <sub>h</sub> (cs)   | <u>cs</u>                        | 2      |     |     | μs   |

|                           | t <sub>h</sub> (sin)  | SIN                              | 200    |     |     | ns   |

| One word write time       | tword                 | The time to write 8 bits of data | 4.2    |     |     | μs   |

|                           | t <sub>wt</sub>       | RAM data write time              | 1      |     |     | μs   |

# **Supplementary Materials**

Figure 1 OSD Serial Data Input Timing

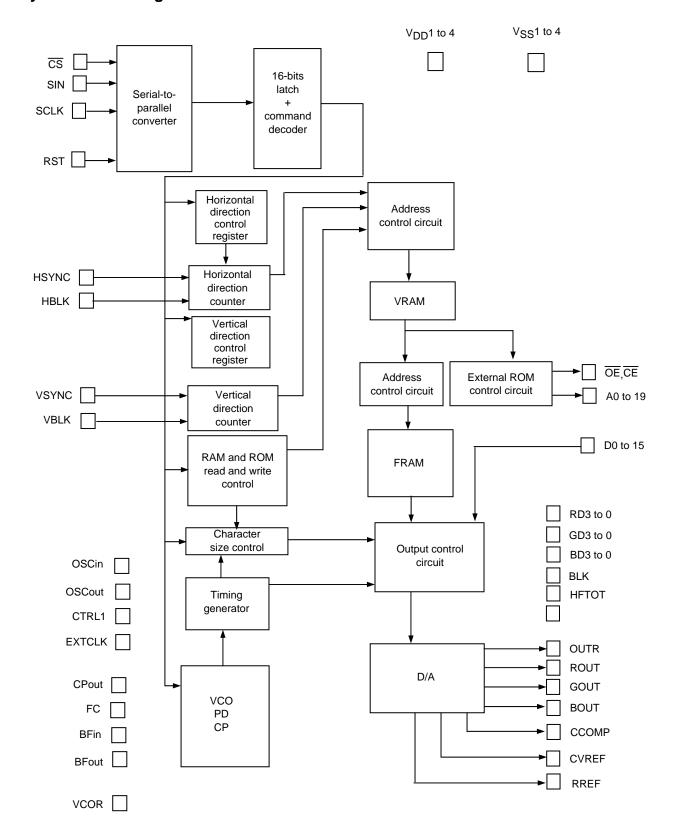

# **System Block Diagram**

## **Display Control Commands**

The display control commands have serial input format that consists of 8-bit units transmitted LSB first. A commands consists of a command identification code in the first byte and data in the second and following bytes. Both a first byte and a second byte (16 bits) must be transmitted for each command. Commands 10, 11, 12, 6C1, and 701 set the IC to continuous write mode. (Continuous write mode is cleared by setting the CS pin high.)

Display Control Command Table

| Display Control Command Table | 2                                            |   |   |   |   |   |       |        |             |      |      |     |     |     |     |      |  |  |

|-------------------------------|----------------------------------------------|---|---|---|---|---|-------|--------|-------------|------|------|-----|-----|-----|-----|------|--|--|

|                               | First byte  Command identification code data |   |   |   |   |   |       |        | Second byte |      |      |     |     |     |     |      |  |  |

| Command                       |                                              |   |   |   |   | 1 | 1     | Da     | ata         |      |      | 1   |     |     |     |      |  |  |

|                               | 7                                            | 6 | 5 | 4 | 3 | 2 | 1     | 0      | 7           | 6    | 5    | 4   | 3   | 2   | 1   | 0    |  |  |

| COMMAND00                     | 1                                            | 0 | 0 | 0 | 0 | 0 | 0     | 0      | 0           | 0    | 0    | V14 | V13 | V12 | V11 | V10  |  |  |

| (Write address) Main 1: V     |                                              |   |   |   |   |   |       |        |             |      |      |     |     |     |     |      |  |  |

| COMMAND01                     | 1                                            | 0 | 0 | 0 | 0 | 0 | 1     | 0      | 0           | 0    | H15  | H14 | H13 | H12 | H11 | H10  |  |  |

| (Write address) Main 1: H     |                                              |   |   |   |   |   |       |        |             |      |      |     |     |     |     |      |  |  |

| COMMAND02                     | 1                                            | 0 | 0 | 0 | 0 | 1 | 0     | 0      | 0           | 0    | 0    | V24 | V23 | V22 | V21 | V20  |  |  |

| (Write address) Main 2: V     |                                              |   |   |   |   |   |       |        |             |      |      |     |     |     |     |      |  |  |

| COMMAND03                     | 1                                            | 0 | 0 | 0 | 0 | 1 | 1     | 0      | 0           | 0    | H25  | H24 | H23 | H22 | H21 | H20  |  |  |

| (Write address) Main 2: H     |                                              |   |   |   |   |   |       |        |             |      |      |     |     |     |     |      |  |  |

| COMMAND04                     | 1                                            | 0 | 0 | 0 | 1 | 0 | 0     | 0      | SV1         | SV0  | 0    | 0   | 0   | 0   | SH1 | SH0  |  |  |

| (Write address) Sub           |                                              |   |   |   |   |   |       |        |             |      |      |     |     |     |     |      |  |  |

| COMMAND10                     | 1                                            | 0 | 0 | 1 | 0 | 0 | RM2 F | RM1[1] | HF1         | HF0  | at   | BXS | BXL | BXR | BXU | BXD  |  |  |

| (Character write) Main 1      |                                              |   |   |   |   |   |       | [2]    | СВЗ         | CB2  | CB1  | CB0 | CC3 | CC2 | CC1 | CC0  |  |  |

|                               |                                              |   |   |   |   |   |       | [3]    | 0           | CTB1 | CTB0 | I/E | MG1 | MG0 | RO1 | RO0  |  |  |

|                               |                                              |   |   |   |   |   |       | [4]    | 0           | 0    | C13  | C12 | C11 | C10 | C9  | C8   |  |  |

|                               |                                              |   |   |   |   |   |       | [5]    | C7          | C6   | C5   | C4  | C3  | C2  | C1  | C0   |  |  |

| COMMAND11                     | 1                                            | 0 | 0 | 1 | 0 | 1 | RM2 F | RM1[1] | HF1         | HF0  | at   | BXS | BXL | BXR | BXU | BXD  |  |  |

| (Character write) Main 2      |                                              |   |   |   |   |   |       | [2]    | СВЗ         | CB2  | CB1  | CB0 | CC3 | CC2 | CC1 | CC0  |  |  |

|                               |                                              |   |   |   |   |   |       | [3]    | 0           | CTB1 | CTB0 | I/E | MG1 | MG0 | RO1 | RO0  |  |  |

|                               |                                              |   |   |   |   |   |       | [4]    | 0           | 0    | C13  | C12 | C11 | C10 | C9  | C8   |  |  |

|                               |                                              |   |   |   |   |   |       | [5]    | C7          | C6   | C5   | C4  | C3  | C2  | C1  | C0   |  |  |

| COMMAND12                     | 1                                            | 0 | 0 | 1 | 1 | 0 | RM2 F | RM1[1] | 0           | 0    | 0    | 0   | 0   | 0   | 0   | 0    |  |  |

| (Character write) Sub         |                                              |   |   |   |   |   |       | [2]    | 0           | 0    | 0    | 0   | 0   | 0   | 0   | 0    |  |  |

|                               |                                              |   |   |   |   |   |       | [3]    | 0           | CTB1 | CTB0 | I/E | MG1 | MG0 | RO1 | RO0  |  |  |

|                               |                                              |   |   |   |   |   |       | [4]    | 0           | 0    | C13  | C12 | C11 | C10 | C9  | C8   |  |  |

|                               |                                              |   |   |   |   |   |       | [5]    | C7          | C6   | C5   | C4  | C3  | C2  | C1  | C0   |  |  |

| COMMAND20                     | 1                                            | 0 | 1 | 0 | 0 | 0 | 0     | 0      | TST         | TST  | SYS  | FRM | СТ  | SRM | MRM | MRM  |  |  |

| (System control)              |                                              |   |   |   |   |   |       |        | MD2         | MD1  | RST  | ERS | ERS | ERS | ER2 | ERS1 |  |  |

| COMMAND21                     | 1                                            | 0 | 1 | 0 | 0 | 0 | 0     | 1      | BK          | ВК   | BK   | BK  | DSP | DSP | DSP | DSP  |  |  |

| (Display control)             |                                              |   |   |   |   |   |       |        | 12          | 02   | 11   | 01  | BG  | GS  | GM2 | GM1  |  |  |

| COMMAND22                     | 1                                            | 0 | 1 | 0 | 0 | 0 | 1     | 0      | 0           | BLOP | BLO  | BLO | BLO | CKP | VIP | HIP  |  |  |

| (I/O polarity control 1)      |                                              |   |   |   |   |   |       |        |             |      | 2    | 1   | 0   |     |     |      |  |  |

| COMMAND23                     | 1                                            | 0 | 1 | 0 | 0 | 0 | 1     | 1      | DPM         | DPM  | BGC  | BGC | BGC | BGC | BGC | BGC  |  |  |

| (Screen background color)     |                                              |   |   |   |   |   |       |        | HC1         | HC0  | T1   | T0  | 3   | 2   | 1   | 0    |  |  |

| COMMAND24                     | 1                                            | 0 | 1 | 0 | 0 | 1 | 0     | 0      | DPM         | DPM  | DA   | SBG | GD  | GD  | GD  | СКОР |  |  |

| (I/O polarity control 2)      |                                              |   |   |   |   |   |       |        | MD          | VC   | SEL  | SL  | 2   | 1   | 0   |      |  |  |

Continued from preceding page.

| Continued from preceding page.              |   |   |      | Fi      | rst byte  | 9      |        |     |     |     |     | Secon | d byte |     |     |     |

|---------------------------------------------|---|---|------|---------|-----------|--------|--------|-----|-----|-----|-----|-------|--------|-----|-----|-----|

| Command                                     |   | C | omma | nd ider | ntificati | on cod | e data |     |     |     |     | Da    | ata    |     |     |     |

|                                             | 7 | 6 | 5    | 4       | 3         | 2      | 1      | 0   | 7   | 6   | 5   | 4     | 3      | 2   | 1   | 0   |

| COMMAND25                                   | 1 | 0 | 1    | 0       | 0         | 1      | 0      | 1   | CEH | ток | VI  | LCS   | ОТМ    | OTM | LCS | LCS |

| (Output control 1)                          |   |   |      |         |           |        |        |     | SL  | SL  | PSL | SP2   | 1      | 0   | STP | OFF |

| COMMAND26                                   | 1 | 0 | 1    | 0       | 0         | 1      | 1      | 0   | HF  | TBL | KBL | BL    | BL     | OTM | ROT | DOT |

| (Output control 2)                          |   |   |      |         |           |        |        |     | OFF | OFF | 2   | 1     | 0      | 2   | OFF | OFF |

| COMMAND27                                   | 1 | 0 | 1    | 0       | 0         | 1      | 1      | 1   | 0   | HFT | HFT | HFT   | TOK    | TOK | TOK | TOK |

| (Output control 3)                          |   |   |      |         |           |        |        |     |     | 2   | 1   | 0     | CB4    | CB3 | CB2 | CB1 |

| COMMAND28                                   | 1 | 0 | 1    | 0       | 1         | 0      | 0      | 0   | HPG | HPS | HPM | HPM   | VPG    | VPS | VPM | VPM |

| (Output control 4)                          |   |   |      |         |           |        |        |     | 9   | 9   | 29  | 19    | 8      | 8   | 28  | 18  |

| COMMAND29                                   | 1 | 0 | 1    | 0       | 1         | 0      | 0      | 1   | 0   | SVH | SVH | SHH   | SHH    | 0   | 0   | ML  |

| (Output control 5)                          |   |   |      |         |           |        |        |     |     | 1   | 0   | 1     | 0      |     |     | СН  |

| COMMAND2A                                   | 1 | 0 | 1    | 0       | 1         | 0      | 1      | 0   | 0   | HIN | HI  | HI    | VI     | VI  | 0   | 0   |

| (Display area control 1)                    |   |   |      |         |           |        |        |     |     | DIN | D1  | D0    | D1     | D0  |     |     |

| COMMAND30                                   | 1 | 0 | 1    | 1       | 0         | 0      | 0      | 0   | VPM | VPM | VPM | VPM   | VPM    | VPM | VPM | VPM |

| (Vertical display start position: main 1)   |   |   |      |         |           |        |        |     | 17  | 16  | 15  | 14    | 1      | 12  | 11  | 10  |

| COMMAND31                                   | 1 | 0 | 1    | 1       | 0         | 0      | 1      | НРМ | HPM | HPM | HPM | HPM   | HPM    | HPM | HPM | HPM |

| (Horizontal display start position: main 1) |   |   |      |         |           |        |        | 18  | 17  | 16  | 15  | 14    | 13     | 12  | 11  | 10  |

| COMMAND32                                   | 1 | 0 | 1    | 1       | 0         | 1      | 0      | 0   | VPM | VPM | VPM | VPM   | VPM    | VPM | VPM | VPM |

| (Vertical display start position: main 2)   |   |   |      |         |           |        |        |     | 27  | 26  | 25  | 24    | 23     | 22  | 21  | 20  |

| COMMAND33                                   | 1 | 0 | 1    | 1       | 0         | 1      | 1      | НРМ | HPM | HPM | HPM | HPM   | HPM    | HPM | HPM | HPM |

| (Horizontal display start position: main 2) |   |   |      |         |           |        |        | 28  | 27  | 26  | 25  | 24    | 23     | 22  | 21  | 20  |

| COMMAND34                                   | 1 | 0 | 1    | 1       | 1         | 0      | 0      | 0   | VPS | VPS | VPS | VPS   | VPS    | VPS | VPS | VPS |

| (Vertical display start positions: sub)     |   |   |      |         |           |        |        |     | 7   | 6   | 5   | 4     | 3      | 2   | 1   | 0   |

| COMMAND35                                   | 1 | 0 | 1    | 1       | 1         | 0      | 1      | HPS | HPS | HPS | HPS | HPS   | HPS    | HPS | HPS | HPS |

| (Horizontal display start position: sub)    |   |   |      |         |           |        |        | 8   | 7   | 6   | 5   | 4     | 3      | 2   | 1   | 0   |

| COMMAND36                                   | 1 | 0 | 1    | 1       | 1         | 1      | 0      | 0   | VPG | VPG | VPG | VPG   | VPG    | VPG | VPG | VPG |

| (Vertical display start positions: screen)  |   |   |      |         |           |        |        |     | 7   | 6   | 5   | 4     | 3      | 2   | 1   | 0   |

| COMMAND37                                   | 1 | 0 | 1    | 1       | 1         | 1      | 1      | HPG | HPG | HPG | HPG | HPG   | HPG    | HPG | HPG | HPG |

| (Horizontal display start position: screen) |   |   |      |         |           |        |        | 8   | 7   | 6   | 5   | 4     | 3      | 2   | 1   | 0   |

Continued from preceding page.

| Continued from preceding page.            |   |   |     |     |     | Fir  | rst byt  | е   |     |        |   |   |     |     |     | Secor | nd byte |      |      |      |

|-------------------------------------------|---|---|-----|-----|-----|------|----------|-----|-----|--------|---|---|-----|-----|-----|-------|---------|------|------|------|

| Command                                   |   | C | Com | nma | and | ider | ntificat | ior | cod | e data |   |   |     |     |     | Da    | ata     |      |      |      |

|                                           | 7 | 6 |     | 5   |     | 4    | 3        |     | 2   | 1      |   | 0 | 7   | 6   | 5   | 4     | 3       | 2    | 1    | 0    |

| COMMAND40                                 | 1 | 1 |     | 0   |     | 0    | 0        |     | 0   | 0      |   | 0 | 0   | 0   | 0   | 0     | SZV1    | SZV0 | SZH1 | SZH0 |

| (Character size control)                  |   |   |     |     |     |      |          |     |     |        |   |   |     |     |     |       |         |      |      |      |

| COMMAND41 main 1                          | 1 | 1 |     | 0   |     | 0    | 0        |     | 0   | 0      |   | 1 | LSZ | LSZ | LSZ | LSZ   | LSZ     | LSZ  | LSZ  | LSZ  |

| (Character size control: line setting U)  |   |   |     |     |     |      |          |     |     |        |   |   | 7   | 6   | 5   | 4     | 3       | 2    | 1    | 0    |

| COMMAND42 main 1                          | 1 | 1 |     | 0   |     | 0    | 0        |     | 0   | 1      | ( | 0 | LSZ | LSZ | LSZ | LSZ   | LSZ     | LSZ  | LSZ  | LSZ  |

| (Character size control: line setting D)  |   |   |     |     |     |      |          |     |     |        |   |   | 15  | 14  | 13  | 12    | 11      | 10   | 9    | 8    |

| COMMAND43 main 1                          | 1 | 1 |     | 0   |     | 0    | 0        |     | 0   | 1      |   | 1 | 0   | 0   | 0   | 0     | 0       | 0    | LSZ  | LSZ  |

| (Character size control: line setting D2) |   |   |     |     |     |      |          |     |     |        |   |   |     |     |     |       |         |      | 17   | 16   |

| COMMAND44 main 2                          | 1 | 1 |     | 0   |     | 0    | 0        |     | 1   | 0      | ( | 0 | LSZ | LSZ | LSZ | LSZ   | LSZ     | LSZ  | LSZ  | LSZ  |

| (Character size control: line setting U)  |   |   |     |     |     |      |          |     |     |        |   |   | 7   | 6   | 5   | 4     | 3       | 2    | 1    | 0    |

| COMMAND45 main 2                          | 1 | 1 |     | 0   |     | 0    | 0        |     | 1   | 0      |   | 1 | LSZ | LSZ | LSZ | LSZ   | LSZ     | LSZ  | LSZ  | LSZ  |

| (Character size control: line setting D)  |   |   |     |     |     |      |          |     |     |        |   |   | 15  | 14  | 13  | 12    | 11      | 10   | 9    | 8    |

| COMMAND46 main 2                          | 1 | 1 |     | 0   |     | 0    | 0        |     | 1   | 1      | ( | 0 | 0   | 0   | 0   | 0     | 0       | 0    | LSZ  | LSZ  |

| (Character size control: line setting D2) |   |   |     |     |     |      |          |     |     |        |   |   |     |     |     |       |         |      | 17   | 16   |

| COMMAND50                                 | 1 | 1 |     | 0   |     | 1    | 0        |     | 0   | 0      |   | 0 | BXL | BXL | BXU | BXU   | BXU     | BXU  | BXU  | BXU  |

| (BOX control U)                           |   |   |     |     |     |      |          |     |     |        |   |   | W1  | W0  | CT1 | CT0   | C3      | C2   | C1   | C0   |

| COMMAND51                                 | 1 | 1 |     | 0   |     | 1    | 0        |     | 0   | 0      |   | 1 | BXR | BXR | BXD | BXD   | BXD     | BXD  | BXD  | BXD  |

| (BOX control D)                           |   |   |     |     |     |      |          |     |     |        |   |   | W1  | W0  | CT1 | СТО   | C3      | C2   | C1   | C0   |

| COMMAND52 main 1                          | 1 | 1 |     | 0   |     | 1    | 0        |     | 0   | 1      |   | 0 | LBX | LBX | LBX | LBX   | LBX     | LBX  | LBX  | LBX  |

| (BOX control: line setting U)             |   |   |     |     |     |      |          |     |     |        |   |   | 7   | 6   | 5   | 4     | 3       | 2    | 1    | 0    |

| COMMAND53 main 1                          | 1 | 1 |     | 0   |     | 1    | 0        |     | 0   | 1      |   | 1 | LBX | LBX | LBX | LBX   | LBX     | LBX  | LBX  | LBX  |

| (BOX control: line setting D)             |   |   |     |     |     |      |          |     |     |        |   |   | 15  | 14  | 13  | 12    | 11      | 10   | 9    | 8    |

| COMMAND54 main 1                          | 1 | 1 |     | 0   |     | 1    | 0        |     | 1   | 0      | ( | 0 | 0   | 0   | 0   | 0     | 0       | 0    | LBX  | LBX  |

| (BOX control: line setting D2)            |   |   |     |     |     |      |          |     |     |        |   |   |     |     |     |       |         |      | 17   | 16   |

| COMMAND55 main 2                          | 1 | 1 |     | 0   | _   | 1    | 0        |     | 1   | 0      |   | 1 | LBX | LBX | LBX | LBX   | LBX     | LBX  | LBX  | LBX  |

| (BOX control: line setting U)             |   |   |     |     |     |      |          |     |     |        |   |   | 7   | 6   | 5   | 4     | 3       | 2    | 1    | 0    |

| COMMAND56 main 2                          | 1 | 1 |     | 0   |     | 1    | 0        |     | 1   | 1      | - | 0 | LBX | LBX | LBX | LBX   | LBX     | LBX  | LBX  | LBX  |

| (BOX control: line setting D)             |   |   |     |     |     |      |          |     |     |        |   |   | 15  | 14  | 13  | 12    | 11      | 10   | 9    | 8    |

| COMMAND57 main 2                          | 1 | 1 |     | 0   |     | 1    | 0        |     | 1   | 1      |   | 1 | 0   | 0   | 0   | 0     | 0       | 0    | LBX  | LBX  |

| (BOX control: line setting D2)            |   |   |     |     |     |      |          |     |     |        |   |   |     |     |     |       |         |      | 17   | 16   |

Continued from preceding page.

|                                         |   |    |      | Fii     | rst byt  | е       |        |        |     |      |     | Secor | d byte |     |      |      |

|-----------------------------------------|---|----|------|---------|----------|---------|--------|--------|-----|------|-----|-------|--------|-----|------|------|

| Command                                 |   | Co | omma | nd ider | ntificat | ion cod | e data |        |     | 1    |     | Da    | ata    |     |      |      |

|                                         | 7 | 6  | 5    | 4       | 3        | 2       | 1      | 0      | 7   | 6    | 5   | 4     | 3      | 2   | 1    | 0    |

| COMMAND58                               | 1 | 1  | 0    | 1       | 1        | 0       | 0      | 0      | 0   | GYB  | GS  | GS    | GY     | GY  | GY   | GY   |

| (Line spacing control 1)                |   |    |      |         |          |         |        |        |     | CK   | 1   | 0     | 3      | 2   | 1    | 0    |

| COMMAND59                               | 1 | 1  | 0    | 1       | 1        | 0       | 0      | 1      | BXD | BXU  | GYH | вхн   | FCH    | вхс | вхс  | BXC  |

| (Line spacing control 2)                |   |    |      |         |          |         |        |        | W   | W    | SL  | SL    | SL     | 3   | 2    | 1    |

| COMMAND5A main 1                        | 1 | 1  | 0    | 1       | 1        | 0       | 1      | 0      | LGY | LGY  | LGY | LGY   | LGY    | LGY | LGY  | LGY  |

| (Line spacing control: line setting U)  |   |    |      |         |          |         |        |        | 7   | 6    | 5   | 4     | 3      | 2   | 1    | 0    |

| COMMAND5B main 1                        | 1 | 1  | 0    | 1       | 1        | 0       | 1      | 1      | LGY | LGY  | LGY | LGY   | LGY    | LGY | LGY  | LGY  |

| (Line spacing control: line setting U)  |   |    |      |         |          |         |        |        | 15  | 14   | 13  | 12    | 11     | 10  | 9    | 8    |

| COMMAND5C main 1                        | 1 | 1  | 0    | 1       | 1        | 1       | 0      | 0      | 0   | 0    | 0   | 0     | 0      | 0   | LGY  | LGY  |

| (Line spacing control: line setting D2) |   |    |      |         |          |         |        |        |     |      |     |       |        |     | 17   | 16   |

| COMMAND5D main 2                        | 1 | 1  | 0    | 1       | 1        | 1       | 0      | 1      | LGY | LGY  | LGY | LGY   | LGY    | LGY | LGY  | LGY  |

| (Line spacing control: line setting U)  | - |    | -    |         |          |         | -      | ·      | 7   | 6    | 5   | 4     | 3      | 2   | 1    | 0    |

| COMMAND5E main 2                        | 1 | 1  | 0    | 1       | 1        | 1       | 1      | 0      | LGY | LGY  | LGY | LGY   | LGY    | LGY | LGY  | LGY  |

| (Line spacing control: line setting D)  | ' | '  | J    | ,       | '        | ,       |        | J      | 15  | 14   | 13  | 12    | 11     | 10  | 9    | 8    |

| COMMAND5F main 2                        | 1 | 1  | 0    | 1       | 1        | 1       | 1      | 1      | 0   | 0    | 0   | 0     | 0      | 0   | LGY  | LGY  |

| (Line spacing control: line setting D2) | ' | '  | U    | '       | '        | '       | '      | '      | U   | U    | U   | U     | U      | U   | 17   | 16   |

| COMMAND60                               | 1 | 1  | 1    | 0       | 0        | 0       | 0      | 0      | BLK | BLK  | EGC | EGC   | EGC    | EGC | EGC  | EGC  |

|                                         | 1 | '  | ļ    | U       | U        | U       | U      | U      | DLN | DLN  |     |       |        |     |      |      |

| (Border control)                        | _ |    |      |         | _        |         |        |        | 150 | 1.50 | T1  | T0    | 3      | 2   | 1    | 0    |

| COMMAND61 main 1                        | 1 | 1  | 1    | 0       | 0        | 0       | 0      | 1      | LFC | LFC  | LFC | LFC   | LFC    | LFC | LFC  | LFC  |

| (Border control: line setting U)        |   |    |      |         | _        |         |        |        | 7   | 6    | 5   | 4     | 3      | 2   | 1    | 0    |

| COMMAND62 main 1                        | 1 | 1  | 1    | 0       | 0        | 0       | 1      | 0      | LFC | LFC  | LFC | LFC   | LFC    | LFC | LFC  | LFC  |

| (Border control: line setting D)        |   |    |      |         |          | _       |        |        | 15  | 14   | 13  | 12    | 11     | 10  | 9    | 8    |

| COMMAND63 main 1                        | 1 | 1  | 1    | 0       | 0        | 0       | 1      | 1      | 0   | 0    | 0   | 0     | 0      | 0   | LFC  | LFC  |

| (Border control: line setting D2)       |   |    |      |         |          |         |        |        |     |      |     |       |        |     | 17   | 16   |

| COMMAND64 main 2                        | 1 | 1  | 1    | 0       | 0        | 1       | 0      | 0      | LFC | LFC  | LFC | LFC   | LFC    | LFC | LFC  | LFC  |

| (Border control: line setting U)        |   |    |      |         |          |         |        |        | 7   | 6    | 5   | 4     | 3      | 2   | 1    | 0    |

| COMMAND65 main 2                        | 1 | 1  | 1    | 0       | 0        | 1       | 0      | 1      | LFC | LFC  | LFC | LFC   | LFC    | LFC | LFC  | LFC  |

| (Border control: line setting D)        |   |    |      |         |          |         |        |        | 15  | 14   | 13  | 12    | 11     | 10  | 9    | 8    |

| COMMAND66 main 2                        | 1 | 1  | 1    | 0       | 0        | 1       | 1      | 0      | 0   | 0    | 0   | 0     | 0      | 0   | LFC  | LFC  |

| (Border control: line setting D2)       |   |    |      |         |          |         |        |        |     |      |     |       |        |     | 17   | 16   |

| COMMAND67                               | 1 | 1  | 1    | 0       | 0        | 1       | 1      | 1      | EVO | LC   | ECK | VCO   | VCS    | VCS | CKSL | CKSL |

| (PLL control 1)                         |   |    |      |         |          |         |        |        | OFF | OFF  | OFF | OFF   | 1      | 0   | 1    | 0    |

| COMMAND68                               | 1 | 1  | 1    | 0       | 1        | 0       | 0      | 0      | 0   | 0    | 0   | DIV   | DIV    | DIV | DIV  | DIV  |

| (PLL control 2)                         |   |    |      |         |          |         |        |        |     |      |     | 12    | 11     | 10  | 9    | 8    |

| COMMAND69                               | 1 | 1  | 1    | 0       | 1        | 0       | 0      | 1      | DIV | DIV  | DIV | DIV   | DIV    | DIV | DIV  | DIV  |

| (PLL control 3)                         |   |    |      |         |          |         |        |        | 7   | 6    | 5   | 4     | 3      | 2   | 1    | 0    |

| COMMAND6A                               | 1 | 1  | 1    | 0       | 1        | 0       | 1      | 0      | 0   | HD   | DZ  | DZ    | HR     | DID | DID  | DID  |

| (PLL control 5)                         |   |    |      |         |          |         |        |        |     | SL   | 1   | 0     | SL     | 2   | 1    | 0    |

| COMMAND6C0                              | 1 | 1  | 1    | 0       | 1        | 1       | 0      | 0      | 0   | 0    | CTN | CTN   | СТА    | СТА | СТА  | СТА  |

| (Write address)                         |   |    |      |         |          |         |        |        |     |      | 1   | 0     | 3      | 2   | 1    | 0    |

| Color table                             | L |    |      |         | L        |         |        |        | L   |      |     |       |        |     |      |      |

| COMMAND6C1                              | 1 | 1  | 1    | 0       | 1        | 1       | 1      | RM3[1] | 0   | 0    | HFT | TOK   | TB3    | TB2 | TB1  | TB0  |

| (Data write)                            |   |    |      |         |          |         |        | [2]    | TG3 | TG2  | TG1 | TG0   | TR3    | TR2 | TR1  | TR0  |

|                                         |   |    |      |         |          |         |        |        |     |      |     |       |        |     |      |      |

Continued from preceding page.

|                               |   |   |      | Fir     | st byte     | !      |        |        |      |     |      | Secon | d byte |     |     |     |  |  |

|-------------------------------|---|---|------|---------|-------------|--------|--------|--------|------|-----|------|-------|--------|-----|-----|-----|--|--|

| Command                       |   | C | omma | nd ider | ntification | on cod | e data |        | Data |     |      |       |        |     |     |     |  |  |

|                               | 7 | 6 | 5    | 4       | 3           | 2      | 1      | 0      | 7    | 6   | 5    | 4     | 3      | 2   | 1   | 0   |  |  |

| COMMAND700                    | 1 | 1 | 1    | 1       | 0           | 0      | 0      | 0      | FAD  | FAD | FRN  | FRN   | FVA    | FVA | FVA | FVA |  |  |

| (character ram1) writeaddress |   |   |      |         |             |        |        |        | 1    | 0   | 1    | 0     | 3      | 2   | 1   | 0   |  |  |

| COMMAND701                    | 1 | 1 | 1    | 1       | 0           | 0      | 1      | RM3[1] | D15  | D14 | D13  | D12   | D11    | D10 | D9  | D8  |  |  |

| (character ram2) write        |   |   |      |         |             |        |        | [2]    | D7   | D6  | D5   | D4    | D3     | D2  | D1  | D0  |  |  |

| COMMAND710                    | 1 | 1 | 1    | 1       | 0           | 1      | 0      | 0      | 0    | 0   | СКО  | СКО   | WFC    | WRA | WRA | WRA |  |  |

| (WVGA ROM)                    |   |   |      |         |             |        |        |        |      |     | S1   | S0    | MD     | M2  | M1  | M0  |  |  |

| COMMAND711                    | 1 | 1 | 1    | 1       | 0           | 1      | 0      | 1      | RSTB | 0   | VCRS | VCRS  | CP     | 0   | СР  | СР  |  |  |

| (PLL control 6)               |   |   |      |         |             |        |        |        |      |     |      | 1     | 0      | X2  | l11 | 10  |  |  |

| COMMAND712                    | 1 | 1 | 1    | 1       | 0           | 1      | 1      | 0      | 0    | STB | RES  | SCP   | DIV    | GAN | GAN | GAN |  |  |

| (PLL control 7)               |   |   |      |         |             |        |        |        |      | СР  | CP   | СР    | ECP    | 2   | 1   | 0   |  |  |

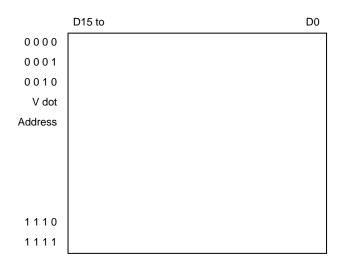

#### 1 COMMAND00 (Main screen 1: horizontal write address setting command)

(1) First byte

| DAO to 7 |                   |   | Content                                               | Neter |

|----------|-------------------|---|-------------------------------------------------------|-------|

| DAU to 7 | DA0 to 7 Register |   | Function                                              | Notes |

| 7        | -                 | 1 | Command 0 identification code                         |       |

| 6        | -                 | 0 | Main screen 1 memory horizontal write address setting |       |

| 5        | -                 | 0 |                                                       |       |

| 4        | -                 | 0 |                                                       |       |

| 3        | -                 | 0 | Sub-identification code: 0                            |       |

| 2        | -                 | 0 |                                                       |       |

| 1        | -                 | 0 |                                                       |       |

| 0        | -                 | 0 |                                                       |       |

| DAG 4- 7          | DA0 to 7 Register |       | Content                           | Notes                              |  |

|-------------------|-------------------|-------|-----------------------------------|------------------------------------|--|

| DA0 to 7 Register |                   | State | Function                          | Notes                              |  |

| 7                 | -                 | 0     |                                   |                                    |  |

| 6                 | -                 | 0     |                                   |                                    |  |

| 5                 | -                 | 0     |                                   |                                    |  |

| 4                 | V14               | 0     | Main screen 1 memory line address | COM24-2: Line number specification |  |

|                   | [MSB]             | 1     | (0 to 11, hexadecimal)            |                                    |  |

| 3                 | V13               | 0     | 15 lines: 0E (hexadecimal)        |                                    |  |

|                   |                   | 1     | 18 lines: 11 (hexadecimal)        |                                    |  |

| 2                 | V12               | 0     |                                   |                                    |  |

|                   |                   | 1     |                                   |                                    |  |

| 1                 | V11               | 0     |                                   |                                    |  |

|                   |                   | 1     |                                   |                                    |  |

| 0                 | V10               | 0     |                                   |                                    |  |

|                   | [LSB]             | 1     |                                   |                                    |  |

<sup>\*:</sup> This resistor is set to the all bits zero state when the IC is reset by the  $\overline{RST}$  pin.

#### 2 COMMAND01 (Main screen 1: vertical write address setting command)

#### (1) First byte

| DA0 to 7 Register |          |       | Content                                             | Notes |

|-------------------|----------|-------|-----------------------------------------------------|-------|

| DA0 to 7          | Register | State | Function                                            | Notes |

| 7                 | -        | 1     | Command 0 identification code                       |       |

| 6                 | -        | 0     | Main screen 1 memory vertical write address setting |       |

| 5                 | -        | 0     |                                                     |       |

| 4                 | -        | 0     |                                                     |       |

| 3                 | -        | 0     | Sub-identification code: 1                          |       |

| 2                 | -        | 0     |                                                     |       |

| 1                 | -        | 1     |                                                     |       |

| 0                 | =        | 0     |                                                     |       |

| DA0 to 7 | Pagistar |       | Content                                                         | Notes                                   |

|----------|----------|-------|-----------------------------------------------------------------|-----------------------------------------|

| DAU IO 7 | Register | State | Function                                                        | Notes                                   |

| 7        | -        | 0     |                                                                 |                                         |

| 6        | -        | 0     |                                                                 |                                         |

| 5        | -        | 0     |                                                                 |                                         |

| 4        | H15      | 0     | Main screen 1 memory character position address                 | COM23-2: Character number specification |

|          | [MSB]    | 1     | (0 to 21, hexadecimal)                                          |                                         |

| 4        | H14      | 0     | 30 characters: 1D (hexadecimal)                                 |                                         |

|          |          | 1     | 33 characters: 20 (hexadecimal) 34 characters: 21 (hexadecimal) |                                         |

| 3        | H13      | 0     | C Total actors 2 T (Hoxadoomial)                                |                                         |

|          |          | 1     |                                                                 |                                         |

| 2        | H12      | 0     |                                                                 |                                         |

|          |          | 1     |                                                                 |                                         |

| 1        | H11      | 0     |                                                                 |                                         |

|          |          | 1     |                                                                 |                                         |

| 0        | H10      | 0     |                                                                 |                                         |

|          | [LSB]    | 1     |                                                                 |                                         |

<sup>\*:</sup> This resistor is set to the all bits zero state when the IC is reset by the RST pin.

#### 3 COMMAND02 (Main screen 2: horizontal write address setting command)

(1) First byte

| DAO to 7 Progietor |          |       | Content                                               | Nata  |

|--------------------|----------|-------|-------------------------------------------------------|-------|

| DA0 to 7           | Register | State | Function                                              | Notes |

| 7                  | -        | 1     | Command 0 identification code                         |       |

| 6                  | -        | 0     | Main screen 2 memory horizontal write address setting |       |

| 5                  | -        | 0     |                                                       |       |

| 4                  | -        | 0     |                                                       |       |

| 3                  | -        | 0     | Sub-identification code: 2                            |       |

| 2                  | -        | 1     |                                                       |       |

| 1                  | -        | 0     |                                                       |       |

| 0                  | -        | 0     |                                                       |       |

| DA0 to 7          | DA0 to 7 Register |       | Content                           | Notes                              |  |  |

|-------------------|-------------------|-------|-----------------------------------|------------------------------------|--|--|

| DAU to 7 Register |                   | State | Function                          | Notes                              |  |  |

| 7                 | -                 | 0     |                                   |                                    |  |  |

| 6                 | -                 | 0     |                                   |                                    |  |  |

| 5                 | -                 | 0     |                                   |                                    |  |  |

| 4                 | V24               | 0     | Main screen 2 memory line address | COM24-2: Line number specification |  |  |

|                   | [MSB]             | 1     | (0 to 0E, hexadecimal)            |                                    |  |  |

| 3                 | V23               | 0     | 15 lines: 0E (hexadecimal)        |                                    |  |  |

|                   |                   | 1     | 18 lines: 11 (hexadecimal)        |                                    |  |  |

| 2                 | V22               | 0     |                                   |                                    |  |  |

|                   |                   | 1     |                                   |                                    |  |  |

| 1                 | V21               | 0     |                                   |                                    |  |  |

|                   |                   | 1     |                                   |                                    |  |  |

| 0                 | V20               | 0     |                                   |                                    |  |  |

|                   | [LSB]             | 1     |                                   |                                    |  |  |

<sup>\*:</sup> This resistor is set to the all bits zero state when the IC is reset by the RST pin.

#### 4 COMMAND03 (Main screen 2: vertical write address setting command)

#### (1) First byte

| DA0 to 7 | NO to 7  |       | Content                                             | Notes |

|----------|----------|-------|-----------------------------------------------------|-------|

| DAU 10 7 | Register | State | Function                                            | Notes |

| 7        | -        | 1     | Command 0 identification code                       |       |

| 6        | -        | 0     | Main screen 2 memory vertical write address setting |       |

| 5        | -        | 0     |                                                     |       |

| 4        | -        | 0     |                                                     |       |

| 3        | -        | 0     | Sub-identification code: 3                          |       |

| 2        | -        | 1     |                                                     |       |

| 1        | -        | 1     |                                                     |       |

| 0        | -        | 0     |                                                     |       |

| DA0 to 7 | Dogistor |       | Content                                                         | Notes                                   |  |

|----------|----------|-------|-----------------------------------------------------------------|-----------------------------------------|--|

| DA0 to 7 | Register | State | Function                                                        | Notes                                   |  |

| 7        | -        | 0     |                                                                 |                                         |  |

| 6        | -        | 0     |                                                                 |                                         |  |

| 5        | -        | 0     |                                                                 |                                         |  |

| 4        | H25      | 0     | Main screen 2 memory character position address                 | COM23-3: Character number specification |  |

|          | [MSB]    | 1     | (0 to 21, hexadecimal)                                          |                                         |  |

| 4        | H24      | 0     | 30 characters: 1D (hexadecimal)                                 |                                         |  |

|          |          | 1     | 33 characters: 20 (hexadecimal) 34 characters: 21 (hexadecimal) |                                         |  |

| 3        | H23      | 0     | or characters. 21 (nexadecimal)                                 |                                         |  |

|          |          | 1     | ]                                                               |                                         |  |