**FEATURES**

# +3.3 V to +5 V Quad/Octal 10-Bit DACs

# AD7804/AD7805/AD7808/AD7809

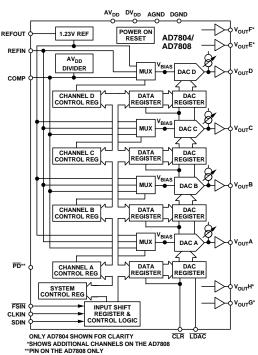

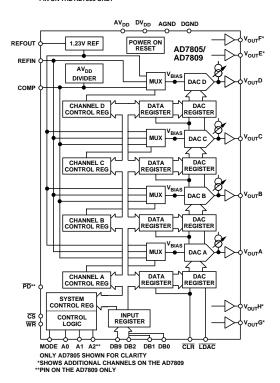

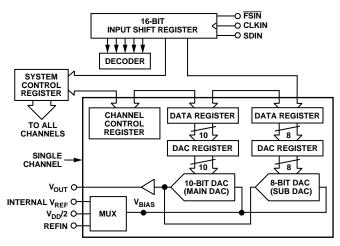

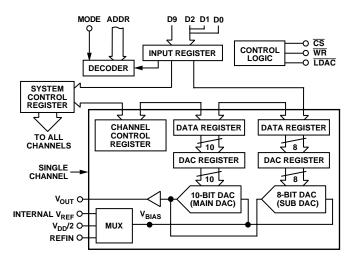

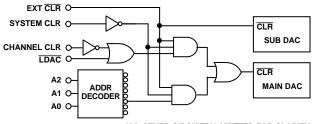

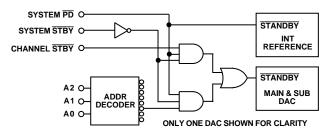

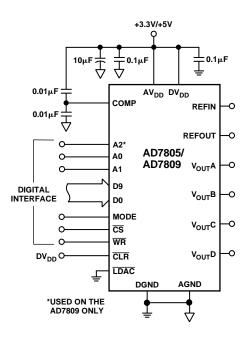

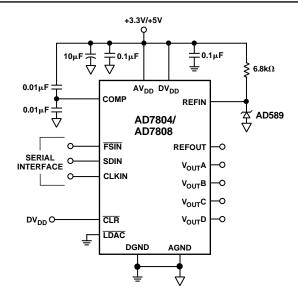

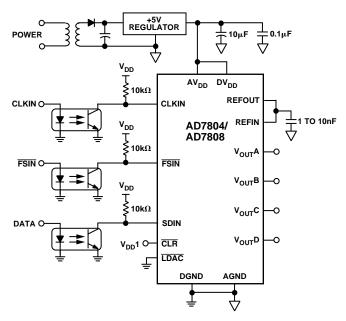

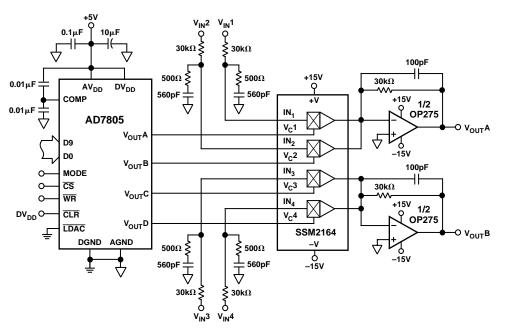

#### FUNCTIONAL BLOCK DIAGRAMS

Four 10-Bit DACs in One Package Serial and Parallel Loading Facilities Available AD7804 Quad 10-Bit Serial Loading AD7805 Quad 10-Bit Parallel Loading AD7808 Octal 10-Bit Parallel Loading +3.3 V to +5 V Operation Power-Down Mode Power-On Reset Standby Mode (All DACs/Individual DACs) Low Power All CMOS Construction 10-Bit Resolution Double Buffered DAC Registers Dual External Reference Capability APPLICATIONS Outlined Diak Drives

Optical Disk Drives Instrumentation and Communication Systems Process Control and Voltage Setpoint Control Trim Potentiometer Replacement Automatic Calibration

#### **GENERAL DESCRIPTION**

The AD7804/AD7808 are quad/octal 10-bit digital-to-analog converters, with serial load capabilities, while the AD7805/AD7809 are quad/octal 10-bit digital-to-analog converters with parallel load capabilities. These parts operate from a +3.3 V to +5 V ( $\pm 10\%$ ) power supply and incorporates an on-chip reference. These DACs provide output signals in the form of V<sub>BIAS</sub>  $\pm$  V<sub>SWING</sub> is derived internally from V<sub>BIAS</sub>. On-chip control registers include a system control register and channel control registers. The system control register has control over all DACs in the package. The channel control registers allow individual control of DACs. The complete transfer function of each individual DAC can be shifted around the V<sub>BIAS</sub> point using an on-chip Sub DAC. All DACs contain double buffered data inputs, which allow all analog outputs to be simultaneously updated using the asynchronous LDAC input.

| <b>Control Features</b>      | <b>Channels Controlled</b> | Main DAC     | Sub DAC |

|------------------------------|----------------------------|--------------|---------|

| Hardware Clear               | All                        | $\checkmark$ |         |

| System Control               |                            |              |         |

| Power Down <sup>1</sup>      | All                        |              |         |

| System Standby <sup>2</sup>  | All                        |              |         |

| System Clear                 | All                        |              |         |

| Input Coding                 | All                        |              |         |

| Channel Control              |                            |              |         |

| Channel Standby <sup>2</sup> | Selective                  |              |         |

| Channel Clear                | Selective                  |              |         |

| V <sub>BIAS</sub>            | Selective                  | $\sim$       |         |

NOTES

<sup>1</sup>Power-down function powers down all internal circuitry including the reference. <sup>2</sup>Standby functions power down all circuitry except for the reference.

#### REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 World Wide Web Site: http://www.analog.com Fax: 781/326-8703 © Analog Devices, Inc., 1998

# $\begin{array}{l} \textbf{AD7804/AD7805} \textbf{--SPECIFICATIONS} \\ \textbf{Reference} = \textbf{Internal Reference}; \ \textbf{C}_L = 100 \ \textbf{pF}; \ \textbf{R}_L = 2 \ \textbf{k} \Omega \ \textbf{to GND}. \ \textbf{Sub DAC at Midscale}. \ \textbf{All specifications T_{MIN} to T_{MAX} unless otherwise noted.} \end{array} \right)$

| Parameter                                          | B Grade <sup>1</sup>                     | C Grade <sup>1</sup>                     | Units          | Comments                                                            |

|----------------------------------------------------|------------------------------------------|------------------------------------------|----------------|---------------------------------------------------------------------|

| STATIC PERFORMANCE                                 |                                          |                                          |                |                                                                     |

| MAIN DAC                                           |                                          |                                          |                |                                                                     |

| Resolution                                         | 10                                       | 10                                       | Bits           |                                                                     |

| Relative Accuracy                                  | ±3                                       | ±3                                       | LSB max        |                                                                     |

| Gain Error                                         | ±3                                       | ±3                                       | % FSR max      |                                                                     |

| Bias Offset Error <sup>2</sup>                     | -80/+40                                  | -80/+40                                  | mV max         | DAC Code = 0.5 Full Scale                                           |

| Zero-Scale Error <sup>3</sup>                      |                                          | -VDLAS                                   | mV max         | DAC Code = $0.0$ H di Ocale<br>DAC Code = $0.0$ H for Offset Binary |

| Zero-Seale Error                                   | $\frac{-V_{BLAS}}{16}/+40$               | $\frac{-7BIAS}{16}$ / +40                | III V IIIAX    | Dife Code = 00011 for Oliset Billary                                |

| Monotonicity                                       | 9                                        | 10                                       | Bits           | and 200H for Twos Complement Coding                                 |

| Minimum Load Resistance                            | 2                                        | 2                                        | $k\Omega$ min  |                                                                     |

| SUB DAC                                            | 2                                        | 2                                        |                |                                                                     |

| Resolution                                         | 8                                        | 8                                        | Bits           |                                                                     |

| Differential Nonlinearity                          | ±0.125                                   | ±0.125                                   | LSB typ        | Refers to an LSB of the Main DAC                                    |

| Differential Nonlinearity                          |                                          |                                          |                | Refers to all LSB of the Main DAC                                   |

|                                                    | ±0.5                                     | ±0.5                                     | LSB max        |                                                                     |

| OUTPUT CHARACTERISTICS                             |                                          |                                          |                |                                                                     |

| Output Voltage Range <sup>3</sup>                  | $V_{BIAS} \pm 15/16 \times V_{BIAS}$     | $V_{BIAS} \pm 15/16 \times V_{BIAS}$     | V              | Twos Complement Coding                                              |

|                                                    | $V_{BIAS}/16$ to $31/16 \times V_{BIAS}$ | $V_{BIAS}/16$ to $31/16 \times V_{BIAS}$ | V              | Offset Binary Coding                                                |

| Voltage Output Settling Time to 10 Bits            | 4                                        | 4                                        | µs max         | Typically 1.5 µs                                                    |

| Slew Rate                                          | 2.5                                      | 2.5                                      | V/µs typ       |                                                                     |

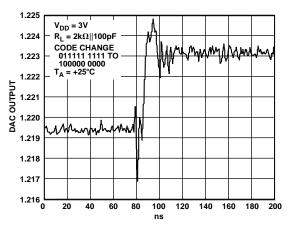

| Digital-to-Analog Glitch Impulse                   | 1                                        | 1                                        | nV-s typ       | 1 LSB Change Around the Major Carry                                 |

| Digital Feedthrough                                | 0.5                                      | 0.5                                      | nV-s typ       |                                                                     |

| Digital Crosstalk                                  | 0.5                                      | 0.5                                      | nV-s typ       |                                                                     |

| Analog Crosstalk                                   | ±0.2                                     | ±0.2                                     | LSB typ        |                                                                     |

| DC Output Impedance                                | 2                                        | 2                                        | $\Omega$ typ   |                                                                     |

| Power Supply Rejection Ratio                       | 0.002                                    | 0.002                                    | %/% typ        | $\Delta V_{ m DD} \pm 10\%$                                         |

|                                                    | 0.002                                    | 0.002                                    | 70/ 70 Lyp     | $\Delta V DD \pm 1070$                                              |

| DAC REFERENCE INPUTS                               |                                          |                                          |                |                                                                     |

| REF IN Range                                       | 1.0 to $V_{DD}/2$                        | 1.0 to $V_{DD}/2$                        | V min to V max |                                                                     |

| REF IN Input Leakage                               | ±1                                       | ±1                                       | μA max         | Typically ±1 nA                                                     |

| DIGITAL INPUTS                                     |                                          |                                          |                |                                                                     |

| Input High Voltage, $V_{IH}$ @ $V_{DD}$ = 5 V      | 2.4                                      | 2.4                                      | V min          |                                                                     |

| Input High Voltage, $V_{IH}$ @ $V_{DD}$ = 3.3 V    | 2.1                                      | 2.1                                      | V min          |                                                                     |

| Input Low Voltage, $V_{IL}$ @ $V_{DD}$ = 5 V       | 0.8                                      | 0.8                                      | V max          |                                                                     |

| Input Low Voltage, $V_{IL}$ @ $V_{DD}$ = 3.3 V     | 0.6                                      | 0.6                                      | V max          |                                                                     |

| Input Leakage Current                              | ±10                                      | μA max                                   |                |                                                                     |

| Input Capacitance                                  | 10                                       | 10                                       | pF max         |                                                                     |

| Input Coding                                       | Twos Comp/Binary                         | Twos Comp/Binary                         | -              |                                                                     |

| REFERENCE OUTPUT                                   |                                          |                                          |                |                                                                     |

| REF OUT Output Voltage                             | 1.23                                     | 1.23                                     | V nom          |                                                                     |

| REF OUT Error                                      | ±8                                       | ±8                                       | % max          |                                                                     |

| REF OUT Temperature Coefficient                    | -100                                     | -100                                     | ppm/°C typ     |                                                                     |

| REF OUT Output Impedance                           | 5                                        | 5                                        | $k\Omega$ nom  |                                                                     |

| POWER REQUIREMENTS                                 | , , , , , , , , , , , , , , , , , , ,    | 5                                        |                |                                                                     |

|                                                    | 2/5 5                                    | 2/5 5                                    | V min to V max |                                                                     |

| $V_{DD}$ (AV <sub>DD</sub> and DV <sub>DD</sub> )  | 3/5.5                                    | 3/5.5                                    | v min to v max |                                                                     |

| $I_{DD}$ (AI <sub>DD</sub> Plus DI <sub>DD</sub> ) | 10                                       | 10                                       |                | Excluding Load Currents                                             |

| Normal Mode                                        | 12                                       | 12                                       | mA max         | $V_{IH} = V_{DD}, V_{IL} = DGND$                                    |

| System Standby (SSTBY) Mode                        | 250                                      | 250                                      | μA             | $V_{IH} = V_{DD}, V_{IL} = DGND$                                    |

| Power-Down $(\overline{PD})$ Mode                  |                                          |                                          |                |                                                                     |

| @ +25°C                                            | 0.8                                      | 0.8                                      | µA max         | $V_{IH} = V_{DD}, V_{IL} = DGND$                                    |

| $T_{MIN} - T_{MAX}$                                | 1.5                                      | 1.5                                      | μA max         |                                                                     |

| Power Dissipation                                  |                                          |                                          |                | Excluding Power Dissipated in Load                                  |

| Normal Mode                                        | 66                                       | 66                                       | mW max         |                                                                     |

| System Standby (SSTBY) Mode                        | 1.38                                     | 1.38                                     | mW max         |                                                                     |

| Power-Down (PD) Mode                               |                                          |                                          |                |                                                                     |

| @ +25°C                                            | 4.4                                      | 4.4                                      | μW max         |                                                                     |

| $T_{MIN} - T_{MAX}$                                | 8.25                                     | 8.25                                     | µW max         |                                                                     |

NOTES

$^{1}$ Temperature range is  $-40^{\circ}$ C to  $+85^{\circ}$ C. <sup>2</sup>Can be minimized using the Sub DAC.

$^{3}V_{BIAS}$  is the center of the output voltage swing and can be  $V_{DD}/2$ , Internal Reference or REFIN as determined by MX1 and MX0 in the channel control register. Specifications subject to change without notice.

# $\begin{array}{l} \textbf{AD7808/AD7809} \textbf{--SPECIFICATIONS} \\ \textbf{Reference} = \textbf{Internal Reference}; \textbf{C}_L = 100 \ \textbf{pF}; \textbf{R}_L = 2 \ \textbf{k} \Omega \ \textbf{to} \ \textbf{GND}. \ \textbf{Sub DAC at Midscale}. \ \textbf{All specifications T_{MIN} to T_{MAX} unless otherwise noted.} \end{array} \right)$

| Parameter                                                 | B Grade <sup>1</sup>                     | Units              | Comments                                                            |

|-----------------------------------------------------------|------------------------------------------|--------------------|---------------------------------------------------------------------|

| STATIC PERFORMANCE                                        |                                          |                    |                                                                     |

| MAIN DAC                                                  |                                          |                    |                                                                     |

| Resolution                                                | 10                                       | Bits               |                                                                     |

| Relative Accuracy                                         | $\pm 4$                                  | LSB max            |                                                                     |

| Gain Error                                                | ±3                                       | % FSR max          |                                                                     |

| Bias Offset Error <sup>2</sup>                            | $\pm 60$                                 | mV max             | DAC Code = 0.5 Full Scale                                           |

| Zero-Scale Error                                          | ±35                                      | mV max             | DAC Code = $0.0$ H di Scale<br>DAC Code = $000$ H for Offset Binary |

| Monotonicity                                              | 9                                        | Bits               | and 200H for Twos Complement                                        |

| Minimum Load Resistance                                   | 2                                        | $k\Omega$ min      | Coding                                                              |

| SUB DAC                                                   | 2                                        | K22 11111          | Couling                                                             |

| Resolution                                                | 8                                        | Bits               |                                                                     |

|                                                           |                                          | LSB typ            | Refers to an LSB of the Main DAC                                    |

| Differential Nonlinearity                                 | $\pm 0.125 \\ \pm 0.5$                   | LSB typ<br>LSB max | Refers to an LSB of the Main DAC                                    |

| OUTPUT CHARACTERISTICS                                    | 10.5                                     |                    |                                                                     |

|                                                           | $V_{} + 15/16 \times V$                  | V                  | Two Complement Cadina                                               |

| Output Voltage Range <sup>3</sup>                         | $V_{BIAS} \pm 15/16 \times V_{BIAS}$     | V<br>V             | Twos Complement Coding                                              |

|                                                           | $V_{BIAS}/16$ to $31/16 \times V_{BIAS}$ |                    | Offset Binary Coding                                                |

| Voltage Output Settling Time to 10 Bits                   | 4                                        | µs max             | Typically 1.5 µs                                                    |

| Slew Rate                                                 | 2.5                                      | V/µs typ           |                                                                     |

| Digital-to-Analog Glitch Impulse                          | 1                                        | nV-s typ           | 1 LSB Change Around the Major Carry                                 |

| Digital Feedthrough                                       | 0.5                                      | nV-s typ           |                                                                     |

| Digital Crosstalk                                         | 0.5                                      | nV-s typ           |                                                                     |

| Analog Crosstalk                                          | $\pm 0.2$                                | LSB typ            |                                                                     |

| DC Output Impedance                                       | 2                                        | Ω typ              |                                                                     |

| Power Supply Rejection Ratio                              | 0.002                                    | %/% typ            | $\Delta V_{DD} \pm 10\%$                                            |

| DAC REFERENCE INPUTS                                      |                                          |                    |                                                                     |

| REF IN Range                                              | 1.0 to $V_{DD}/2$                        | V min to V max     |                                                                     |

| REF IN Input Leakage                                      | ±1                                       | μA max             | Typically $\pm 1$ nA                                                |

| DIGITAL INPUTS                                            |                                          | •                  |                                                                     |

| Input High Voltage, $V_{IH} @ V_{DD} = 5 V$               | 2.4                                      | V min              |                                                                     |

| Input High Voltage, $V_{IH} @ V_{DD} = 3.3 V$             | 2.1                                      | V min              |                                                                     |

|                                                           | 0.8                                      | V max              |                                                                     |

| Input Low Voltage, $V_{IL} @ V_{DD} = 5 V$                |                                          | V max              |                                                                     |

| Input Low Voltage, $V_{IL}$ @ $V_{DD}$ = 3.3 V            | 0.6                                      |                    |                                                                     |

| Input Leakage Current                                     | $\pm 10$                                 | µA max             |                                                                     |

| Input Capacitance                                         | 8                                        | pF max             |                                                                     |

| Input Coding                                              | Twos Comp/Binary                         |                    |                                                                     |

| REFERENCE OUTPUT                                          |                                          |                    |                                                                     |

| REF OUT Output Voltage                                    | 1.23                                     | V nom              |                                                                     |

| REF OUT Error                                             | $\pm 8$                                  | % max              |                                                                     |

| REF OUT Temperature Coefficient                           | -100                                     | ppm/°C typ         |                                                                     |

| REF OUT Output Impedance                                  | 5                                        | kΩ nom             |                                                                     |

| POWER REQUIREMENTS                                        |                                          |                    |                                                                     |

| $V_{DD}$ (AV <sub>DD</sub> and DV <sub>DD</sub> )         | 3/5.5                                    | V min to V max     |                                                                     |

| I <sub>DD</sub> (AI <sub>DD</sub> Plus DI <sub>DD</sub> ) |                                          |                    | Excluding Load Currents                                             |

| Normal Mode                                               | 18                                       | mA max             | $V_{IH} = V_{DD}, V_{IL} = DGND$                                    |

| System Standby (SSTBY) Mode                               | 250                                      | μA max             | $V_{IH} = V_{DD}, V_{IL} = DGND$                                    |

| Power-Down (PD) Mode                                      |                                          | r                  |                                                                     |

| @ +25°C                                                   | 1                                        | μA max             | $V_{IH} = V_{DD}, V_{IL} = DGND$                                    |

| $T_{MIN}$ T <sub>MAX</sub>                                | 3                                        | μA max             |                                                                     |

| Power Dissipation                                         |                                          | r                  | Excluding Power Dissipated in Load                                  |

| Normal Mode                                               | 99                                       | mW max             |                                                                     |

| System Standby (SSTBY) Mode                               | 1.38                                     | mW max             |                                                                     |

| Power-Down (PD) Mode                                      | 1.50                                     | 111 VY 111QA       |                                                                     |

| $(a) + 25^{\circ}C$                                       | 5.5                                      | μW max             |                                                                     |

| -                                                         | 16.5                                     | μW max             |                                                                     |

| $T_{MIN} - T_{MAX}$                                       | 10.5                                     | им шал             |                                                                     |

NOTES

<sup>1</sup>Temperature range is -40°C to +85°C.

<sup>2</sup>Can be minimized using the Sub DAC.

<sup>3</sup>V<sub>BIAS</sub> is the center of the output voltage swing and can be V<sub>DD</sub>/2, Internal Reference or REFIN as determined by MX1 and MX0 in the channel control register. Specifications subject to change without notice.

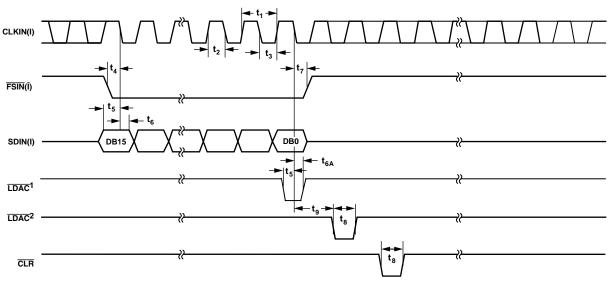

# **AD7804/AD7808 TIMING CHARACTERISTICS**<sup>1</sup> ( $V_{DD} = 3.3 V \pm 10\%$ to $5 V \pm 10\%$ ; AGND = DGND = 0 V; Reference = Internel Deference All expectitions T = to T = unless attaction and a

Internal Reference. All specifications  $T_{\text{MIN}}$  to  $T_{\text{MAX}}$  unless otherwise noted.)

| Parameter       | Limit at $T_{MIN}$ , $T_{MAX}$<br>All Versions | Units  | Description          |  |

|-----------------|------------------------------------------------|--------|----------------------|--|

| t <sub>1</sub>  | 100                                            | ns min | CLKIN Cycle Time     |  |

| t <sub>2</sub>  | 40                                             | ns min | CLKIN High Time      |  |

| t <sub>3</sub>  | 40                                             | ns min | CLKIN Low Time       |  |

| t <sub>4</sub>  | 30                                             | ns min | FSIN Setup Time      |  |

| t <sub>5</sub>  | 30                                             | ns min | Data Setup Time      |  |

| t <sub>6</sub>  | 5                                              | ns min | Data Hold Time       |  |

| t <sub>6A</sub> | 6                                              | ns min | LDAC Hold Time       |  |

| t <sub>7</sub>  | 90                                             | ns max | FSIN Hold Time       |  |

|                 | 20                                             | ns min |                      |  |

| t <sub>8</sub>  | 40                                             | ns min | LDAC, CLR Pulsewidth |  |

| t <sub>9</sub>  | 100                                            | ns min | LDAC Setup Time      |  |

NOTES

<sup>1</sup>Sample tested during initial release and after any redesign or process change that may affect this parameter. All input signals are specified with tr = tf = 5 ns and timed from a voltage of  $(V_{IL} + V_{IH})/2$ .

Specifications subject to change without notice.

<sup>1</sup>TIMING REQUIREMENTS FOR SYNCHRONOUS <u>LDAC</u> UPDATE OR <u>LDAC</u> MAY BE TIED PERMANENTLY LOW IF REQUIRED. <sup>2</sup>TIMING REQUIREMENTS FOR ASYNCHRONOUS <u>LDAC</u> UPDATE.

Figure 1. Timing Diagram for AD7804 and AD7808

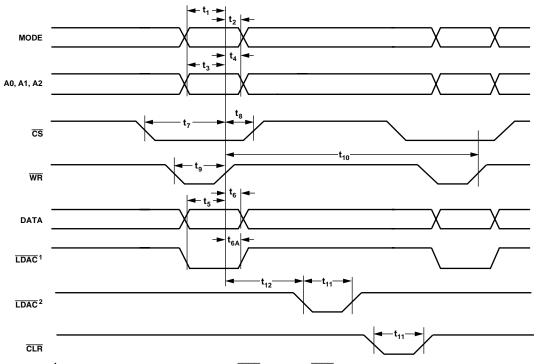

# **AD7805/AD7809 TIMING CHARACTERISTICS**<sup>1</sup> ( $V_{DD} = 3.3 V \pm 10\%$ to $5 V \pm 10\%$ ; AGND = DGND = 0 V; Reference = Internal Reference. All specifications T<sub>MIN</sub> to T<sub>MAX</sub> unless otherwise noted.)

| Parameter       | Limit at T <sub>MIN</sub> , T <sub>MAX</sub><br>All Versions | Unit   | Description                                                |

|-----------------|--------------------------------------------------------------|--------|------------------------------------------------------------|

| t <sub>1</sub>  | 25                                                           | ns min | Mode Valid to Write Setup Time                             |

| t <sub>2</sub>  | 4.5                                                          | ns min | Mode Valid to Write Hold Time                              |

| t <sub>3</sub>  | 25                                                           | ns min | Address Valid to Write Setup Time                          |

| $t_4$           | 4.5                                                          | ns min | Address Valid to Write Hold Time                           |

| t <sub>5</sub>  | 25                                                           | ns min | Data Setup Time                                            |

| t <sub>6</sub>  | 4.5                                                          | ns min | Data Hold Time                                             |

| t <sub>6A</sub> | 6                                                            | ns min | LDAC Valid to Write Hold Time                              |

| t <sub>7</sub>  | 40                                                           | ns min | Chip Select to Write Setup Time                            |

| t <sub>8</sub>  | 0                                                            | ns min | Chip Select to Write Hold Time                             |

| t <sub>9</sub>  | 40                                                           | ns min | Write Pulsewidth                                           |

| t <sub>10</sub> | 100                                                          | ns min | Time Between Successive Writes                             |

| t <sub>11</sub> | 40                                                           | ns min | $\overline{\text{LDAC}}, \overline{\text{CLR}}$ Pulsewidth |

| t <sub>12</sub> | 100                                                          | ns min | Write to LDAC Setup Time                                   |

NOTE

<sup>1</sup>Sample tested during initial release and after any redesign or process change that may affect this parameter. All input signals are specified with tr = tf = 5 ns and timed from a voltage of  $(V_{IL} + V_{IH})/2$ .

Specifications subject to change without notice.

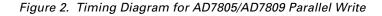

<sup>1</sup>TIMING REQUIREMENTS FOR SYNCHRONOUS LDAC UPDATE OR LDAC MAY BE TIED PERMANENTLY LOW IF REQUIRED. <sup>2</sup>TIMING REQUIREMENTS FOR ASYNCHRONOUS LDAC UPDATE.

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

$(T_A = +25^{\circ}C \text{ unless otherwise noted})$

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                 |

|----------------------------------------------------------------------------------------------------------------------|

| REF OUT to AGND $\dots -0.3$ V to + AV <sub>DD</sub>                                                                 |

| REF IN to AGND                                                                                                       |

| $V_{OUT}$ to AGND <sup>2</sup> 0.3 V to AV <sub>DD</sub> + 0.3 V                                                     |

| Input Current to Any Pin Except Supplies <sup>3</sup> $\dots \dots \pm 10 \text{ mA}$                                |

| Operating Temperature Range                                                                                          |

| AD7804/AD7805 Commercial Plastic                                                                                     |

|                                                                                                                      |

| (B, C Versions) $-40^{\circ}$ C to $+85^{\circ}$ C                                                                   |

| AD7808/AD7809 Commercial Plastic                                                                                     |

| (B, C Versions) $\dots \dots -40^{\circ}$ C to $+85^{\circ}$ C |

| Storage Temperature Range                                                                                            |

| Junction Temperature                                                                                                 |

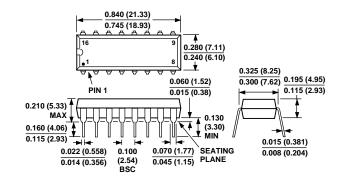

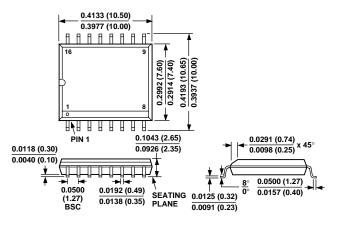

| SOIC (R-16) Package, Power Dissipation 450 mW                                                                        |

| $\theta_{IA}$ Thermal Impedance                                                                                      |

| Lead Temperature, Soldering                                                                                          |

| Vapor Phase (60 sec) +215°C                                                                                          |

| Infrared (15 sec)                                                                                                    |

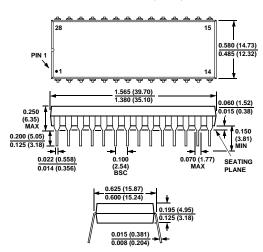

| PDIP (N-16) Package, Power Dissipation                                                                               |

| $\theta_{IA}$ Thermal Impedance                                                                                      |

| Lead Temperature, Soldering (10 sec)                                                                                 |

|                                                                                                                      |

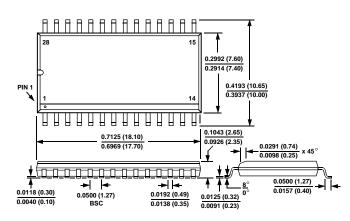

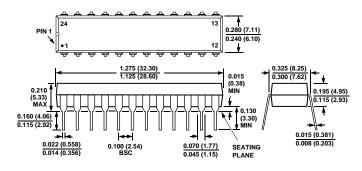

| SOIC (R-24) Package, Power Dissipation                                                                               |

| $\theta_{JA}$ Thermal Impedance                                                                                      |

| Lead Temperature, Soldering                                                                                          |

| Vapor Phase (60 sec) +215°C                                                                                          |

| Infrared (15 sec) +220°C                                                                                             |

|                                                                                                                      |

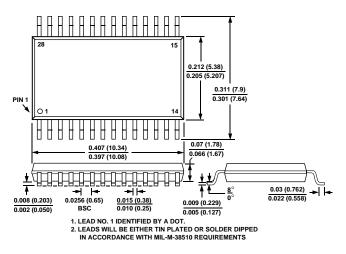

| PDIP (N-24) Package, Power Dissipation 670 mW  |

|------------------------------------------------|

| $\theta_{JA}$ Thermal Impedance 105°C/W        |

| Lead Temperature, Soldering (10 sec) +260°C    |

| SOIC (R-28) Package, Power Dissipation 875 mW  |

| $\theta_{JA}$ Thermal Impedance                |

| Lead Temperature, Soldering                    |

| Vapor Phase (60 sec) +215°C                    |

| Infrared (15 sec) +220°C                       |

| PDIP (N-28) Package, Power Dissipation 875 mW  |

| $\theta_{JA}$ Thermal Impedance                |

| Lead Temperature, Soldering (10 sec) +260°C    |

| SSOP (RS-28) Package, Power Dissipation 875 mW |

| $\theta_{JA}$ Thermal Impedance 110°C/W        |

| Lead Temperature, Soldering                    |

| Vapor Phase (60 sec) +215°C                    |

| Infrared (15 sec) +220°C                       |

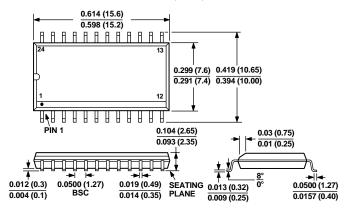

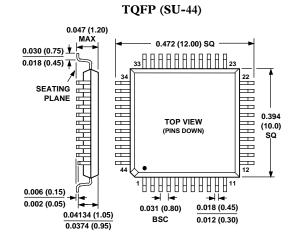

| TQFP (SU-44) Package, Power Dissipation 450 mW |

| $\theta_{JA}$ Thermal Impedance 116°C/W        |

| Lead Temperature, Soldering                    |

| Vapor Phase (60 sec) +215°C                    |

| Infrared (15 sec) +220°C                       |

|                                                |

#### NOTES

<sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>2</sup>The outputs may be shorted to voltages in this range provided the power dissipation of the package is not exceeded.

<sup>3</sup>Transient currents of up to 100 mA will not cause SCR latch-up.

| Model                                         | Supply<br>Voltage                                                            | Temperature<br>Range                                                                   | Relative<br>Accuracy                 | Package Descriptions                                                                                                | Package<br>Options            |

|-----------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------|

| AD7804BN<br>AD7804BR                          | 3.3 V to 5 V<br>3.3 V to 5 V                                                 | -40°C to +85°C<br>-40°C to +85°C                                                       | ±3 LSB<br>±3 LSB                     | 16-Lead Plastic DIP<br>16-Lead Small Outline IC                                                                     | N-16<br>R-16                  |

| AD7805BN<br>AD7805BR<br>AD7805BRS<br>AD7805CR | 3.3 V to 5 V<br>3.3 V to 5 V<br>3.3 V to 5 V<br>3.3 V to 5 V<br>3.3 V to 5 V | -40°C to +85°C<br>-40°C to +85°C<br>-40°C to +85°C<br>-40°C to +85°C<br>-40°C to +85°C | ±3 LSB<br>±3 LSB<br>±3 LSB<br>±3 LSB | 28-Lead Plastic DIP<br>28 Lead Small Outline IC<br>28-Lead Shrink Small Outline Package<br>28-Lead Small Outline IC | N-28<br>R-28<br>RS-28<br>R-28 |

| AD7808BN<br>AD7808BR<br>AD7809BST             | 3.3 V to 5 V<br>3.3 V to 5 V<br>3.3 V to 5 V<br>3.3 V to 5 V                 | -40°C to +85°C<br>-40°C to +85°C<br>-40°C to +85°C                                     | ±4 LSB<br>±4 LSB<br>±4 LSB           | 24-Lead Plastic DIP<br>24 Lead Small Outline IC<br>44-Lead Thin Plastic Quad Flatpack (TQFP)                        | N-24<br>R-24<br>SU-44         |

#### **ORDERING GUIDE**

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although these devices feature proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

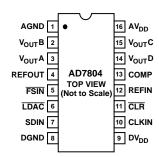

| AD7804<br>Pin No. | AD7808<br>Pin No. | Mnemonic                               | Description                                                                                                                                                                                                                                                                                                                              |  |

|-------------------|-------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1                 | 1,6               | AGND                                   | Ground reference point for analog circuitry.                                                                                                                                                                                                                                                                                             |  |

| 2, 3              | 2, 3              | V <sub>OUT</sub> B, V <sub>OUT</sub> A | Analog output voltage from the DACs.                                                                                                                                                                                                                                                                                                     |  |

| 4                 | 4                 | REFOUT                                 | Reference Output. This is a bandgap reference and is typically 1.23 V.                                                                                                                                                                                                                                                                   |  |

|                   | 5                 | PD                                     | Active low input used to put the part into low power mode reducing current consumption to $1 \ \mu$ A.                                                                                                                                                                                                                                   |  |

|                   | 7,8               | V <sub>OUT</sub> F, V <sub>OUT</sub> E | Analog output voltages from the DACs.                                                                                                                                                                                                                                                                                                    |  |

| 5                 | 9                 | FSIN                                   | Level-triggered control input (active low). This is the frame synchronization signal for the input data. When $\overline{\text{FSIN}}$ goes low, it enables the input shift register and data is transferred on the falling edges of CLKIN.                                                                                              |  |

| 6                 | 10                | LDAC                                   | $\overline{\text{LDAC}}$ Input. When this digital input is taken low, all DAC registers are simultaneously updated with the contents of the data registers. If $\overline{\text{LDAC}}$ is tied permanently low, or is low on the sixteenth falling clock edge with timing similar to that of SDIN, an automatic update will take place. |  |

| 7                 | 11                | SDIN                                   | Serial Data Input. These devices accept a 16-bit word. Data is clocked into the input shift register on the falling edge of CLKIN.                                                                                                                                                                                                       |  |

| 8                 | 12                | DGND                                   | Ground reference point for digital circuitry.                                                                                                                                                                                                                                                                                            |  |

| 9                 | 13                | DV <sub>DD</sub>                       | Digital Power Supply.                                                                                                                                                                                                                                                                                                                    |  |

| 10                | 14                | CLKIN                                  | Clock Input. Data is clocked into the input shift register on the falling edges of CLKIN. Duty Cycle should be between 40% and 60%.                                                                                                                                                                                                      |  |

| 11                | 15                | CLR                                    | Asynchronous $\overline{\text{CLR}}$ Input. When this input is taken low, all Main DAC outputs are cleared either to $V_{\text{BIAS}}$ or to $V_{\text{BIAS}}/16$ volts. All Sub DACs are also cleared and thus the transfer function of the Main DAC will remain centered around the $V_{\text{BIAS}}$ point.                           |  |

|                   | 16                | NC                                     | No Connect. This pin should be left open circuit.                                                                                                                                                                                                                                                                                        |  |

|                   | 17, 18            | V <sub>OUT</sub> H, V <sub>OUT</sub> G | Analog output voltages from the DACs.                                                                                                                                                                                                                                                                                                    |  |

| 12                | 20                | REFIN                                  | This is an external reference input for the DACs. When this reference is selected for a DAC in the control register, the analog output from the selected DAC swings around this point.                                                                                                                                                   |  |

| 13                | 21                | СОМР                                   | Compensation Pin. This pin provides an output from the internal $V_{DD}/2$ divider and is provided for ac bypass purposes only. This pin should be decoupled with 1 nF capacitors to both $AV_{DD}$ and AGND. This pin can be overdriven with an external reference, thus giving the facility for two external references on the part.   |  |

| 14, 15            | 22, 23            | V <sub>OUT</sub> D, V <sub>OUT</sub> C | Analog output voltage from the DACs.                                                                                                                                                                                                                                                                                                     |  |

| 16                | 19, 24            | AV <sub>DD</sub>                       | Analog Power Supply. +3.3 V to +5 V.                                                                                                                                                                                                                                                                                                     |  |

#### AD7804 PIN CONFIGURATION

#### AD7808 PIN CONFIGURATION

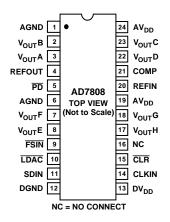

| AD7805  | AD7809         |                                        |                                                                                                                                                                                        |

|---------|----------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No. | Pin No.        | Mnemonic                               | Description                                                                                                                                                                            |

|         | 1, 11, 13,     | NC                                     | No Connect. These pins should be left open circuit.                                                                                                                                    |

|         | 20, 33         |                                        |                                                                                                                                                                                        |

| 1       | 2, 5, 39, 40   | AGND                                   | Ground reference point for analog circuitry.                                                                                                                                           |

| 2, 3    | 41, 42         | V <sub>OUT</sub> B, V <sub>OUT</sub> A | Analog output voltages from the DACs.                                                                                                                                                  |

| 4       | 43             | REFOUT                                 | Reference Output. This is a bandgap reference and is typically 1.23 V.                                                                                                                 |

| 5–10,   | 3, 4, 6, 7, 9, | DB9–DB2                                | Data Inputs. DB9 to DB2 are the 8 MSBs of the data word.                                                                                                                               |

| 12, 13  | 10, 15, 23     |                                        |                                                                                                                                                                                        |

| 19, 20  | 24, 26         | DB1, DB0                               | DB1 and DB0 function as the 2 LSBs of the 10-bit word in 10-bit parallel mode but                                                                                                      |

|         |                |                                        | have other functions when BYTE loading structure is used.                                                                                                                              |

|         | 8,12           | $\underline{V_{OUT}F}, V_{OUT}E$       | Analog output voltages from the DACs.                                                                                                                                                  |

| 11      | 14             | LDAC                                   | LDAC Input. When this digital input is taken low, all DAC registers are simultaneously                                                                                                 |

|         |                |                                        | updated with the contents of the DAC data registers. If $\overline{\text{LDAC}}$ is permanently tied low, or is                                                                        |

| 1.4     |                | DOVD                                   | low during the rising edge of $\overline{WR}$ similar to data inputs, an automatic update will take place.                                                                             |

| 14      | 16             | DGND                                   | Ground reference point for digital circuitry.                                                                                                                                          |

| 15      | 17             | DV <sub>DD</sub>                       | Digital Power Supply.                                                                                                                                                                  |

| 16      | 18             | WR                                     | Write Input $\overline{WR}$ is an active low logic input which is used in conjunction with $\overline{CS}$ and                                                                         |

| 17      | 01             | $\overline{\mathrm{CS}}$               | the address pins to write data to the relevant registers.                                                                                                                              |

| 17      | 21             |                                        | Chip Select. Active low logic input.                                                                                                                                                   |

| 18      | 19             | CLR                                    | Asynchronous $\overline{\text{CLR}}$ Input. When this input is taken low, all Main DAC outputs are                                                                                     |

|         |                |                                        | cleared either to $V_{BIAS}$ or to $V_{BIAS}/16$ volts. All Sub DACs are also cleared and thus the transfer function of the MAIN DAC will remain centered around the $V_{BIAS}$ point. |

|         | 22, 25         | V <sub>OUT</sub> H, V <sub>OUT</sub> G | Analog output voltages from the DACs.                                                                                                                                                  |

| 21, 22  | 22, 23         | A2, A1, A0                             | DAC Address Inputs. These digital inputs are used in conjunction with $\overline{\text{CS}}$ and $\overline{\text{WR}}$ to                                                             |

| 21, 22  | 21, 29, 30     | A2, A1, A0                             | determine which DAC channel control register or DAC data register is loaded from the                                                                                                   |

|         |                |                                        | input register. These address bits are don't cares when writing to the system control register.                                                                                        |

| 23      | 31             | MODE                                   | Logic Input. Logic high enables writing to the DAC data registers, a logic low enables                                                                                                 |

| 23      | 51             | MODE                                   | writing to the control registers.                                                                                                                                                      |

| 24      | 32             | REFIN                                  | This is an external reference input for the DAC. When this reference is selected for the DAC                                                                                           |

|         |                |                                        | in the control register, the analog output from the selected DAC swings around this point.                                                                                             |

| 25      | 34             | COMP                                   | Compensation Pin. This pin provides an output from the internal $V_{DD}/2$ divider and is                                                                                              |

|         |                |                                        | provided for ac bypass purposes only. This pin should be decoupled with 1 nF capacitors                                                                                                |

|         |                |                                        | to both $AV_{DD}$ and AGND. This pin can be overdriven with an external reference, thus                                                                                                |

|         |                |                                        | giving the facility for two external references on the part.                                                                                                                           |

| 26, 27  | 35, 36         | V <sub>OUT</sub> D, V <sub>OUT</sub> C | Analog output voltages from the DACs.                                                                                                                                                  |

| 28      | 28, 37, 38     | AV <sub>DD</sub>                       | Analog Power Supply.                                                                                                                                                                   |

|         | 44             | PD                                     | Active low input used to put the part into low power mode reducing current consump-                                                                                                    |

|         |                |                                        | tion to 1 µA.                                                                                                                                                                          |

#### AD7805/AD7809 PIN FUNCTION DESCRIPTIONS

#### **AD7805 PIN CONFIGURATION**

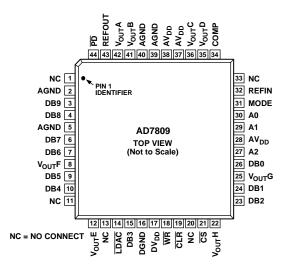

#### **AD7809 PIN CONFIGURATION**

#### TERMINOLOGY

#### **Relative Accuracy**

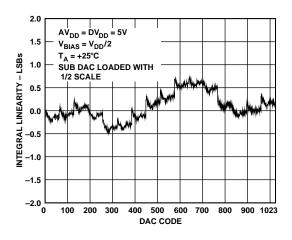

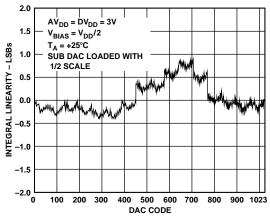

For the DACs, relative accuracy or endpoint nonlinearity is a measure of the maximum deviation, in LSBs, from a straight line passing through the endpoints of the DAC transfer function. Figures 32 and 33 show the linearity at 3 V and 5 V respectively.

#### **Differential Nonlinearity**

Differential nonlinearity is the difference between the measured change and the ideal 1 LSB change between any two adjacent codes. A specified differential nonlinearity of  $\pm 1$  LSB maximum ensures monotonicity.

#### **Bias Offset Error**

If the DACs are ideal, the output voltage of any DAC with midscale code loaded will be equal to  $V_{BIAS}$  where  $V_{BIAS}$  is selected by MX1 and MX0 in the control register. The DAC bias offset error is the difference between the actual output voltage and  $V_{BIAS}$ , expressed in mV.

#### **Gain Error**

The difference between the actual and ideal analog output range, expressed as a percent of full-scale range. It is the deviation in slope of the DAC transfer characteristic from ideal.

#### Zero-Scale Error

The zero-scale error is the actual output minus the ideal output from any DAC when zero code is loaded to the DAC. If offset binary coding is used, the code loaded is 000Hex, and if twos complement coding is used, a code of 200HEX is loaded to the DAC to calculate the zero-scale error. Zero-scale error is expressed in mV.

#### Digital-to-Analog Glitch Impulse

Digital-to-analog glitch impulse is the impulse injected into the analog output when the digital inputs change state with the DAC selected and the  $\overline{LDAC}$  used to update the DAC. It is normally specified as the area of the glitch in nV-s and is measured when the digital input code is changed by 1 LSB at the major carry transition. Regardless of whether offset binary or twos complement coding is used, the major carry transition occurs at the analog output voltage change of  $V_{BIAS}$  to  $V_{BIAS} - 1$  LSB or vice versa.

#### **Digital Feedthrough**

Digital feedthrough is a measure of the impulse injected into the analog output of a DAC from the digital inputs of the same DAC but is measured when the DAC is not updated. It is specified in nV secs and is measured with a full-scale code change on the data bus, i.e., from all 0s to all 1s and vice versa.

#### **Digital Crosstalk**

Digital crosstalk is the glitch impulse transferred to the output of one converter due to a digital code change to another DAC. It is specified in nV-s.

#### **Analog Crosstalk**

Analog crosstalk is a change in output of any DAC in response to a change in the output of one or more of the other DACs. It is measured in LSBs.

#### Power Supply Rejection Ratio (PSRR)

This specification indicates how the output of the DAC is affected by changes in the power supply voltage. Power-supply rejection ratio is quoted in terms of % change in output per % change in  $V_{DD}$  for full-scale output of the DAC.  $V_{DD}$  is varied  $\pm 10\%$ .

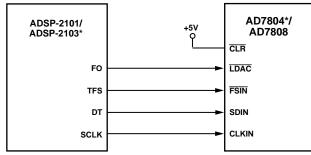

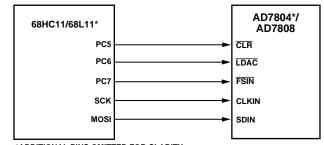

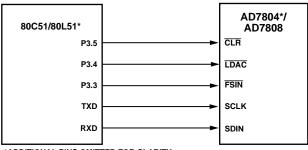

#### AD7804/AD7808 INTERFACE SECTION

The AD7804 and AD7808 are serial input devices. Three lines control the serial interface,  $\overline{\text{FSIN}}$ , CLKIN and SDIN. The timing diagram is shown in Figure 1.

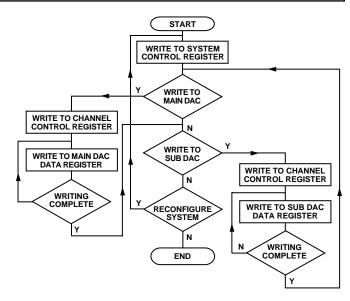

Two mode bits (MD1 and MD0) which are DB13 and DB14 of the serial word written to the AD7804/AD7808 are used to determine whether writing is to the DAC data registers or the control registers of the device. These parts contain a system control register for controlling the operation of all DACs in the package as well as a channel control register for controlling the operation of each individual DAC. Table I shows how to access these registers.

| Table I. | Register | Selection | Table for | the | AD7804/AD7808 |

|----------|----------|-----------|-----------|-----|---------------|

|----------|----------|-----------|-----------|-----|---------------|

| MD1 | MD0 | Function                                  |

|-----|-----|-------------------------------------------|

| 0   | 0   | Write enable to system control register.  |

| 0   | 1   | Write enable to channel control register. |

| 1   | X   | Write enable to DAC data registers.       |

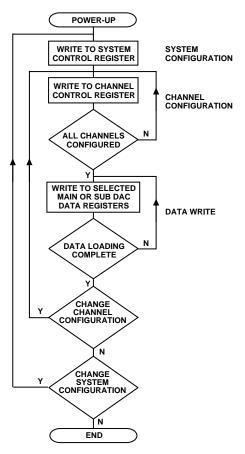

When the  $\overline{\text{FSIN}}$  input goes low, data appearing on the SDIN line is clocked into the input register on each falling edge of CLKIN. Data to be transferred to the AD7804/AD7808 is loaded MSB first. Figure 4 shows the loading sequence for the AD7804/AD7808 system control register, Figure 5 shows the sequence for the channel control register write, and Figures 6 and 7 show the sequence for loading data to the Main and Sub DAC data registers. Figure 3 shows the internal registers associated with the AD7804/AD7808 serial interface DACs. Only one DAC structure is shown for clarity.

Figure 3. AD7804/AD7808 Internal Registers

| MSB           | ;                                                                                                          |         |       |     |     |     |     |     |      |          |    |                 |       |     |      |     | LSB   |

|---------------|------------------------------------------------------------------------------------------------------------|---------|-------|-----|-----|-----|-----|-----|------|----------|----|-----------------|-------|-----|------|-----|-------|

| X             | MD0 = 0                                                                                                    | MD1 =   | = 0 X | Σ   | X Z | X I | X X | X 0 | BI   | BIN/COMP |    | $\overline{PD}$ | SSTBY | SCI | LR ( | ) X | X     |

| X = Don'      | X = Don't Care                                                                                             |         |       |     |     |     |     |     |      |          |    |                 |       |     |      |     |       |

|               | Figure 4. AD7804/AD7808 System Control Register Loading Sequence                                           |         |       |     |     |     |     |     |      |          |    |                 |       |     |      |     |       |

| DB15 (MSB) DE |                                                                                                            |         |       |     |     |     |     |     | DB0  | (LSB)    |    |                 |       |     |      |     |       |

| X             | MD0 = 1                                                                                                    | MD1 :   | = 0 A | 12* | A1  | A0  | MX  | 1 M | X0 Z | X X      | -  | X               | STBY  | CL  | R 0  | X   | X     |

|               | X = Don't Care<br>*Applicable to the AD7808 Only, and Are Don't Care Conditions when Operating the AD7804. |         |       |     |     |     |     |     |      |          |    |                 |       |     |      |     |       |

|               | Figure 5. AD7804/AD7808 Channel Control Register Loading Sequence                                          |         |       |     |     |     |     |     |      |          |    |                 |       |     |      |     |       |

| DB1           | 5 (MSB)                                                                                                    |         |       |     |     |     |     |     |      |          |    |                 | _     |     | -    | DB0 | (LSB) |

| MAI           | N/SUB N                                                                                                    | ID0 = X | MD1   | = 1 | A2* | A1  | A0  | DB9 | DB8  | DB7      | DB | DB5             | DB4   | DB3 | DB2  | DB1 | DB0   |

X = Don't Care

\*Applicable to the AD7808 Only, and Are Don't Care Conditions when Operating the AD7804.

Figure 6. AD7804/AD7808 Main DAC Data Register Loading Sequence (MAIN/SUB = 0)

| DB15 (MSB)     | )       |         |     |    |    |     |     |     |     |     |     |     |     | DB0 | (LSB) |

|----------------|---------|---------|-----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|

| MAIN/SUB       | MD0 = X | MD1 = 1 | A2* | A1 | A0 | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 | Х   | X     |

| X = Don't Care |         |         |     |    |    |     |     |     |     |     |     |     |     |     |       |

\*Applicable to the AD7808 Only, and Are Don't Care Conditions when Operating the AD7804.

Figure 7. AD7804/AD7808 Sub DAC Data Register Loading Sequence (MAIN/SUB = 1)

When the system control register is selected by writing zeros to the mode bits, MD1 and MD0 the address bits are ignored as the system control register controls all DACs in the package. When MD1 = 0 and MD0 = 1, writing is to the channel control register. Only the DAC selected by the address bits will be affected by writing to this register. Each individual DAC has a channel control register.

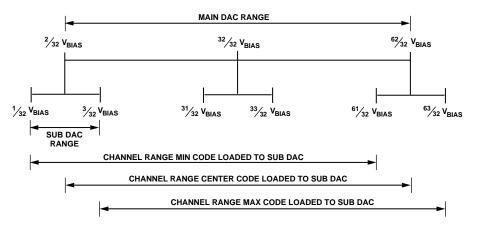

The DACs data registers are addressed by writing a one to MD1 (DB13); the condition of MD0 (DB14) does not matter when writing to the data registers. DB15 determines whether writing is to the Main DAC data register or to the Sub DAC data register. The Main DAC is 10 bits wide and the Sub DAC is 8 bits wide. Thus when writing to the Sub DAC DB1 and DB0 become don't cares. The Sub DAC is used to offset the complete transfer function of the Main DAC to be offset by  $\pm V_{BIAS}/32$ .

When the  $\overline{\text{LDAC}}$  line goes low, all DAC registers in the device are simultaneously loaded with the contents of their respective DAC data registers, and the outputs change accordingly.

Bringing the  $\overline{\text{CLR}}$  line low resets the DAC data and DAC registers. This hardware clear affects both the Main and Sub DACs. This operation sets the analog output of the Main DAC to V<sub>BIAS</sub>/16 when offset binary coding is selected and the output is set to V<sub>BIAS</sub> when twos complement coding is used. V<sub>BIAS</sub> is the output of the internal multiplexer as shown in Figure 3. The output of the Sub DAC is used to shift the transfer function of the Main DAC around the V<sub>BIAS</sub> point and the contribution from the Sub DAC is zero following an external hardware clear. Software clears affect the Main DACs only.

# AD7804/AD7808 SYSTEM CONTROL REGISTER (MD1 = 0, MD0 = 0)

The bits in this register allow control over all DACs in the package. The control bits include power down ( $\overline{PD}$ ), DAC input coding select (BIN/ $\overline{COMP}$ ), system standby (SSTBY) and a system clear (SCLR). The function of these bits is as follows:

#### Power Down (PD)

This bit in the control register is used to shut down the complete device. With a 0 in this position, the reference and all DACs are put into low power mode. Writing a 1 to this bit puts the part in the normal operating mode. When in power-down mode, the contents of all registers are retained and are valid when the device is put back into normal operation.

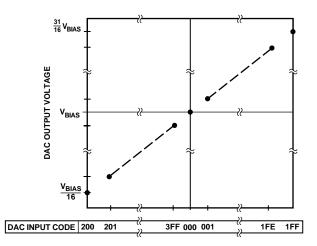

#### Coding (BIN/COMP)

This bit in the system control register allows the user to select one of two input coding schemes. The available schemes are Twos complement coding and offset binary coding. All DACs will be configured with the same input coding scheme. Writing a zero to the control register selects twos complement coding, while writing a 1 to this bit in the control register selects offset binary coding.

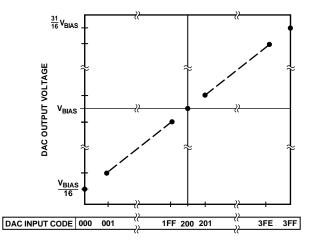

With twos complement coding selected the output voltage from the Main DAC is of the form :

$V_{OUT} = V_{BIAS} \pm V_{SWING}$

$$V_{SWING}$$

is  $\frac{15}{16} \times V_{BLAS}$

With Offset Binary coding selected the output voltage from the Main DAC ranges from:

$$V_{OUT} = \frac{V_{BLAS}}{16}$$

to  $V_{OUT} = \frac{31}{16} \times V_{BLAS}$

where

$V_{BIAS}$  can be the internal bandgap reference, the internal  $V_{DD}/2$  reference or the external REFIN as determined by MX1 and MX0 in the channel control register. A second external reference can be used if required by overdriving the  $V_{DD}/2$  reference which appears at the COMP pin.

#### System Standby (SSTBY)

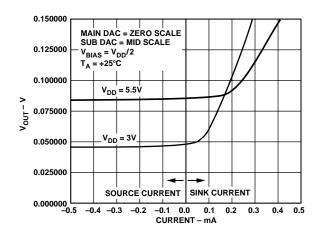

This bit allows all the DACs in the package to be put into low power mode simultaneously but the reference is not affected. Writing a one to the SSTBY bit in the system control register puts all DACs into standby mode. On writing a one to this bit all linear circuitry is switched off and the DAC outputs are connected through a high impedance to ground. The DACs come out of standby mode when a 0 is written to the SSTBY bit.

#### System Clear Function (SCLR)

This function allows the user to clear the contents of all data and DAC registers in software. Writing a one to the SCLR bit in the control register clears the DAC's outputs. A zero in this bit position puts the DAC in normal operating mode. The output of the Main DACs are cleared to one of two voltages depending on the input coding used. If twos complement coding is selected, then issuing a software clear will reset the output of the Main DAC to midscale (V<sub>BIAS</sub>). If offset binary coding is selected, the Main DAC output will be reset to V<sub>BIAS</sub> /16 following the execution of a software clear. This system clear function does not affect the Sub DAC; the Sub DAC data register retains its value during a system software clear (SCLR).

# AD7804/AD7808 CHANNEL CONTROL REGISTER (MD1 = 0, MD0 = 1)

This register allows the user to have control over individual DACs in the package. The control bits in this register include the address bits for the selected DAC, standby (STBY), individual DAC clear (CLR) and multiplexer output selection (MX1 and MX0). The function of these bits follows.

#### DAC Selection (A2, A1, A0)

Bits A2, A1 and A0 in the input registers are used to address a specific DAC. Table IIa shows the selection table for the DACs of the AD7804. Table IIb shows the selection table for the DACs of the AD7808.

Table IIa. DAC Selection Table for the AD7804

| A2 | A1 | A0 | Function       |

|----|----|----|----------------|

| X  | 0  | 0  | DAC A Selected |

| Х  | 0  | 1  | DAC B Selected |

| Х  | 1  | 0  | DAC C Selected |

| Х  | 1  | 1  | DAC D Selected |

| Table IIb. DAC Selection Table for the A | AD7808 |

|------------------------------------------|--------|

|------------------------------------------|--------|

| A2 | A1 | A0 | Function       |

|----|----|----|----------------|

| 0  | 0  | 0  | DAC A Selected |

| 0  | 0  | 1  | DAC B Selected |

| 0  | 1  | 0  | DAC C Selected |

| 0  | 1  | 1  | DAC D Selected |

| 1  | 0  | 0  | DAC E Selected |

| 1  | 0  | 1  | DAC F Selected |

| 1  | 1  | 0  | DAC G Selected |

| 1  | 1  | 1  | DAC H Selected |

#### Standby ( $\overline{STBY}$ )

This bit allows the selected DAC in the package to be put into low power mode. Writing a zero to the  $\overline{STBY}$  bit in the channel control register puts the selected DAC into standby mode. On writing a zero to this bit all linear circuitry is switched off and the DAC output is connected through a high impedance to ground. The DAC is returned to normal operation by writing a one to the  $\overline{STBY}$  bit.

#### Software Clear Function (CLR)

This function allows the user to clear the contents of the selected DAC's data in software. Writing a one to the CLR bit in the control register clears the DAC's output. A zero in the CLR bit position puts the DAC in normal operating mode. This software CLR operation clears only the Main DAC, the contents of the Sub DAC is unaffected by a CLR operation. The output of the Main DAC can be cleared to one of two places depending on the input coding used. An LDAC pulse is required to activate the channel clear function and must be applied after the bit in the channel control register is set or reset. If twos complement coding is selected, then issuing a software clear will reset the output of the Main DAC to midscale (V<sub>BIAS</sub>). If offset binary coding is selected, the Main DAC output will be reset to V<sub>BIAS</sub>/16 following the execution of a software clear.

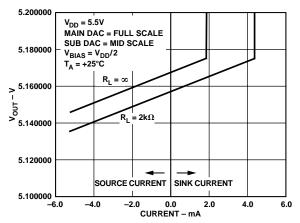

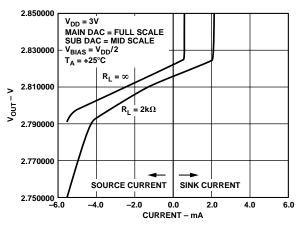

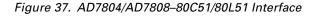

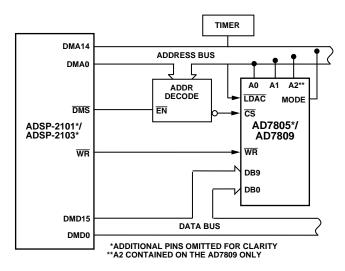

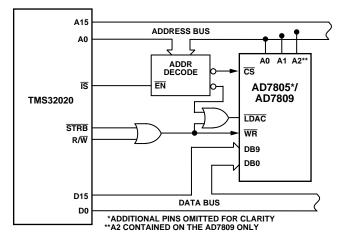

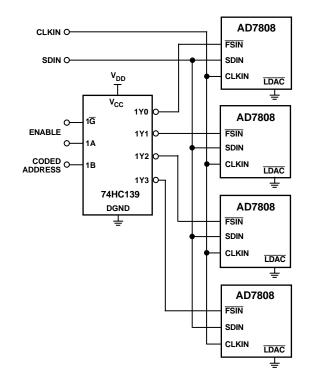

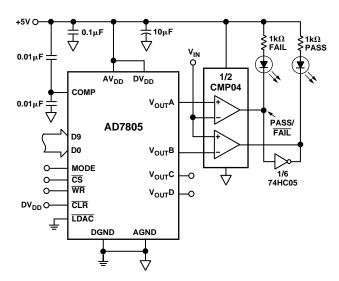

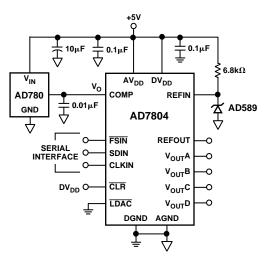

#### Multiplexer Selection (MX1, MX0)