# **SHARKY - SHARKY PRO**

User's Guide

MDX-STWBP-R01: Sharky PCB Ant.

MDX-STWBU-R01 : Sharky uFL antenna

MDX-STWBC-R01: Sharky Pro chip antenna

MDX-STWBW-R01: Sharky Pro no antenna

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Midatronics S.r.l. without notice.

Document:

SHARKY - User's Guide

2020/07/20

# **Outline**

| 1. FCC Rules 1.1. List of FCC rules                                                                                                                                                                                                                                                                                                                                                               | 8                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| 2. Introduction 2.1. Description                                                                                                                                                                                                                                                                                                                                                                  | <b>8</b>                                        |

| 3.1. BLE Technology Overview 3.2. BLE Mesh Technology overview 3.3. Thread Technology overview 3.4. STM32WB Wireless System-on-Chip 3.5. Block Diagram                                                                                                                                                                                                                                            | 10<br>10<br>12<br>13<br>15                      |

| 4. Connectors 4.1. Sharky Module 4.2. Sharky Pro Module                                                                                                                                                                                                                                                                                                                                           | <b>18</b><br>19<br>23                           |

| 5.1. Power Supply 5.2. Sharky Connections 5.2.1. Power Supply on module configuration 5.2.2. Power Supply 5.2.3. Reset Circuit 5.2.4. Boot0 pin 5.2.5. SWD - JLink-V3SET connection 5.3. Sharky Pro Connections 5.3.1. Power Supply 5.3.2. Reset Circuit 5.3.3. Boot0 pin 5.3.4. SWD - JLink-V3SET connection 5.3.5. External antenna 5.4. STLink-V3SET expansion board 5.5. Operating Conditions | 29 29 30 30 31 31 31 32 33 34 34 34 35 36 37 38 |

| 6. Board Layout 6.1. Sharky Module 6.2. Sharky Pro Module with Chip Antenna 6.3. Sharky Pro Module No Antenna 6.4. Mounting Suggestions 6.4.1. Sharky PCB Antenna                                                                                                                                                                                                                                 | 40<br>40<br>41<br>42<br>43<br>44                |

#### Document:

SHARKY - User's Guide

2020/07/20

| 6.4.2. Sharky uFL Antenna                    | 44 |

|----------------------------------------------|----|

| 6.4.3. Sharky Pro Chip Antenna               | 45 |

| 6.4.4. Sharky Pro external antenna           | 46 |

| 6.4.5. Sharky uFL Suggested Antennas         | 46 |

| 6.5. Sharky Breakout                         | 47 |

| 6.5.1. Sharky PCB/uFL antenna                | 47 |

| 6.5.2. Sharky Pro Chip Antenna               | 48 |

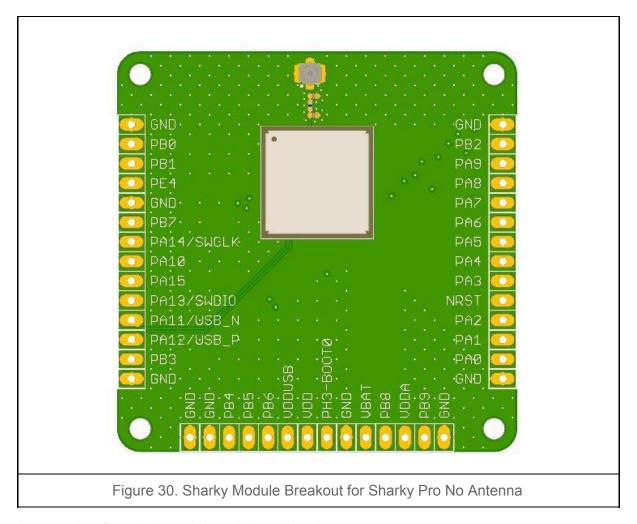

| 6.5.3. Sharky Pro No Antenna                 | 49 |

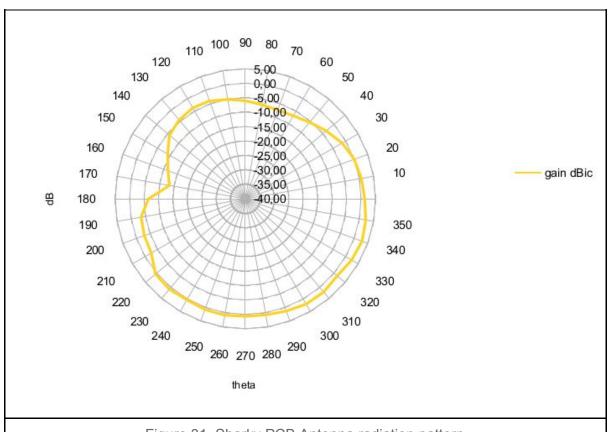

| 7. Radiation pattern plots                   | 50 |

| 7.1. Sharky PCB-Ant module                   | 50 |

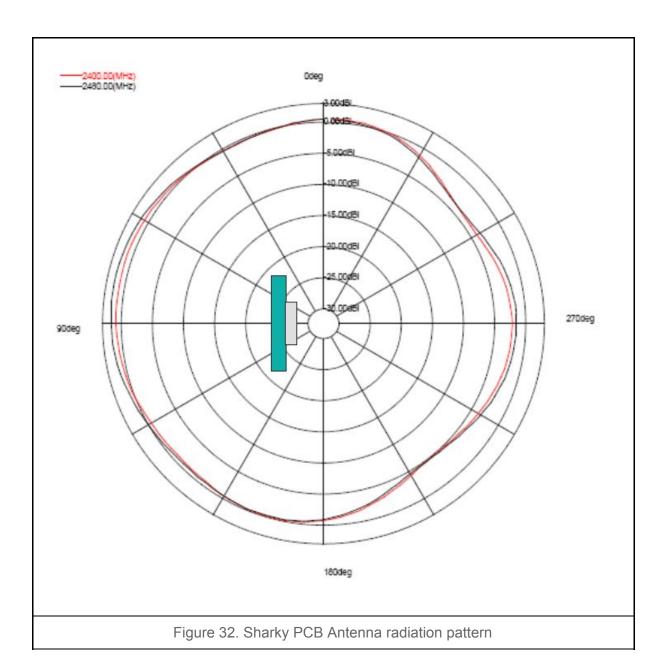

| 7.2. Sharky Pro Chip Antenna module          | 51 |

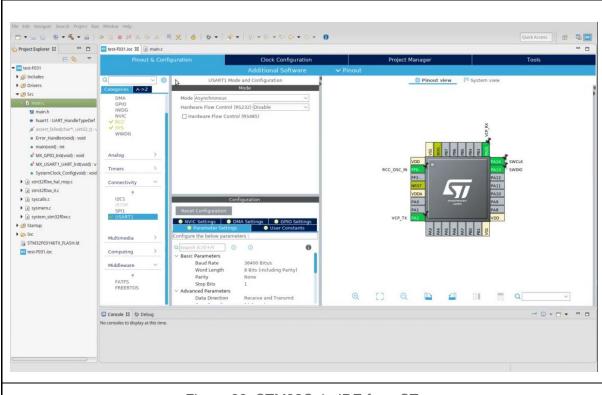

| 8. Firmware Upload                           | 52 |

| 8.1. FW upload to M4 core                    | 52 |

| 8.2. FW upload to M0+ core                   | 52 |

| 9. Software Development                      | 54 |

| 10. References and Useful Links              | 55 |

| 10.1. Data Sheets and documents              | 55 |

| 10.2. Tools                                  | 55 |

| 10.3. WebSites                               | 55 |

| 10.4. Bibliography                           | 55 |

| 11. FCC                                      | 56 |

| 11.1. Label and Compliance Information (FCC) | 56 |

Document:

SHARKY - User's Guide

2020/07/20

## Illustrations

| Figure 1. Bluetooth Scatternet topology                                  | 10 |

|--------------------------------------------------------------------------|----|

| Figure 2. BLE Star-bus Topology                                          | 11 |

| Figure 3. BLE Mesh Topology                                              | 12 |

| Figure 4. Thread Network Architecture                                    | 13 |

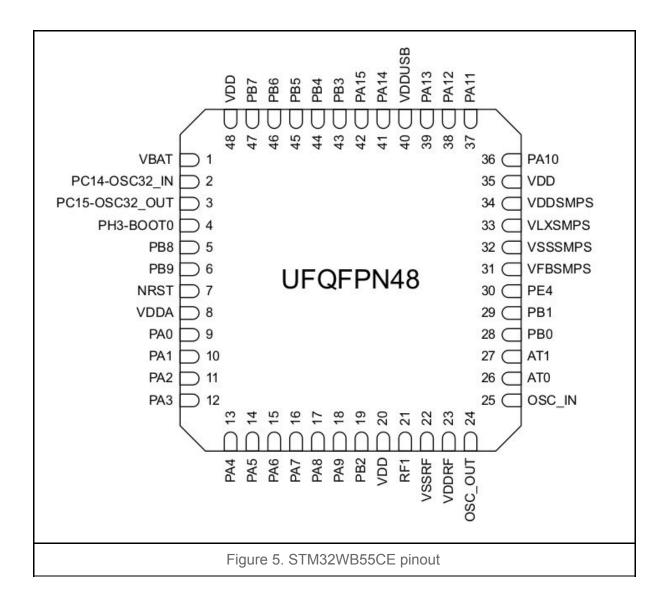

| Figure 5. STM32WB55CE pinout                                             | 16 |

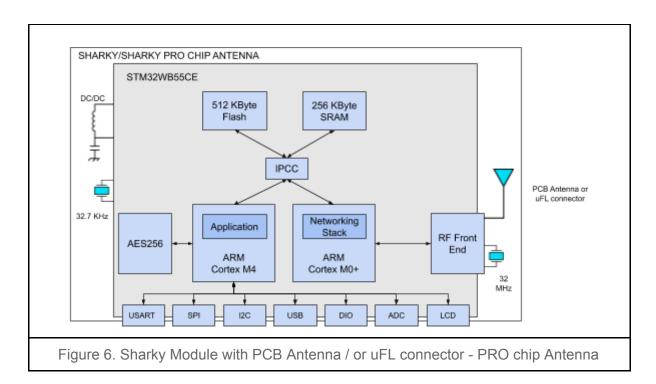

| Figure 6. Sharky Module with PCB Antenna / or uFL connector              | 17 |

| Figure 7. Sharky Pro Module with Chip Antenna / no Antenna               | 17 |

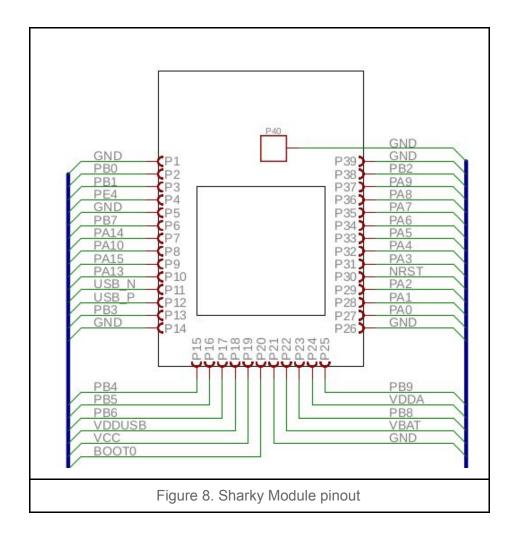

| Figure 8. Sharky Module pinout                                           | 18 |

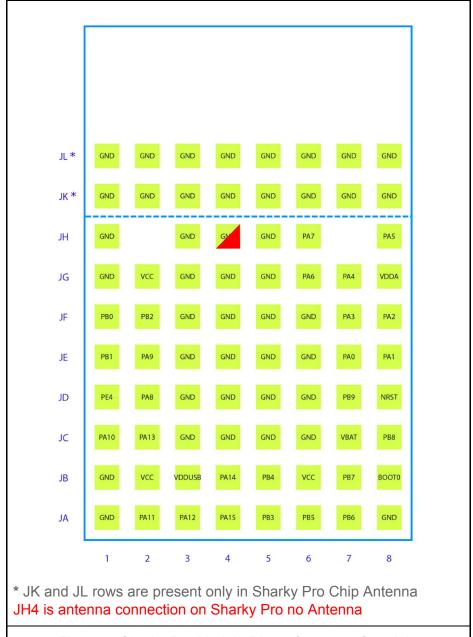

| Figure 9. Sharky Pro Module Pinout                                       | 23 |

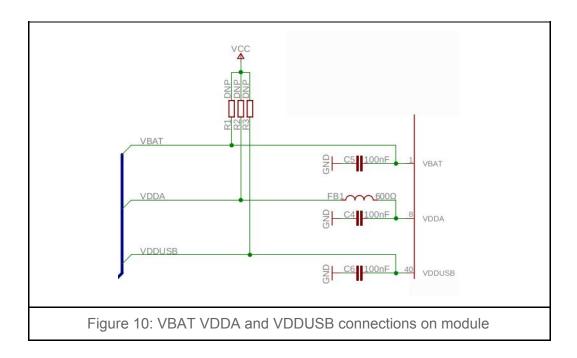

| Figure 10: VBAT VDDA and VDDUSB connections                              | 30 |

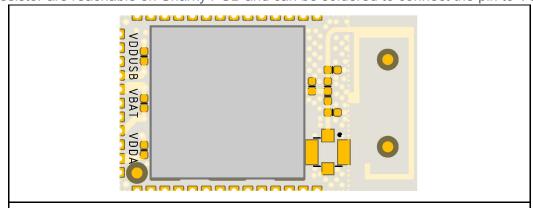

| Figure 11: VDDUSB, VBAT and VDDA resistors placement (left side of PCB)  | 30 |

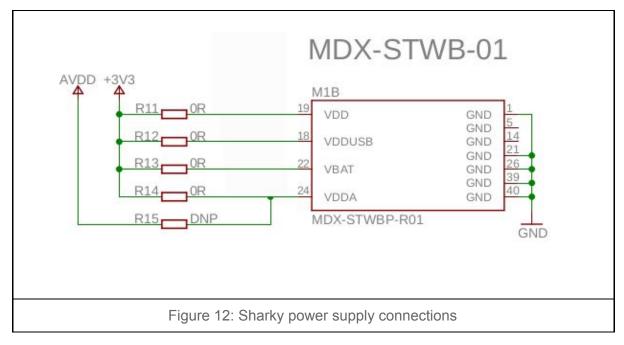

| Figure 12: Sharky power supply connections                               | 31 |

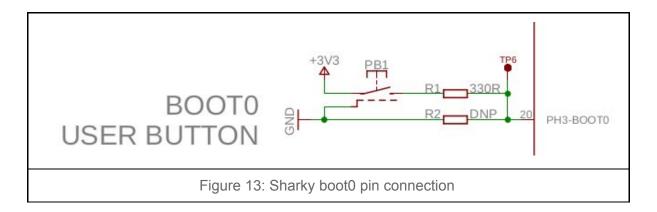

| Figure 13: Sharky boot0 pin connection                                   | 32 |

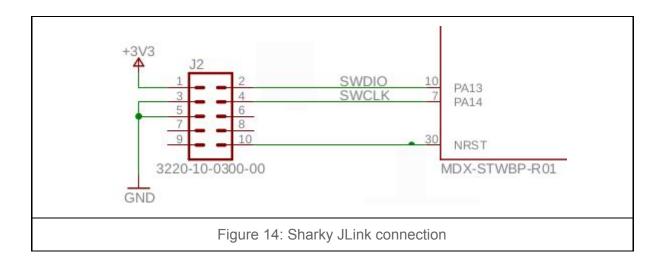

| Figure 14: Sharky JLink connection                                       | 33 |

| Figure 15: Sharky JLink with connection cable                            | 33 |

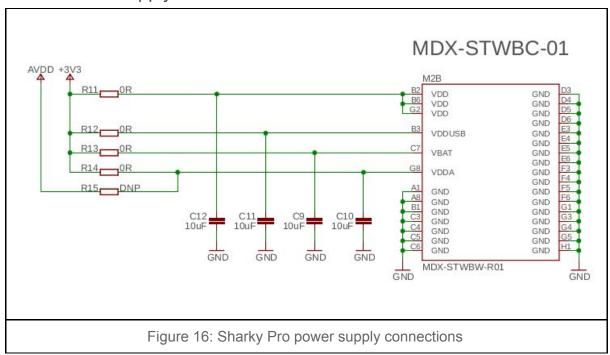

| Figure 16: Sharky Pro power supply connections                           | 34 |

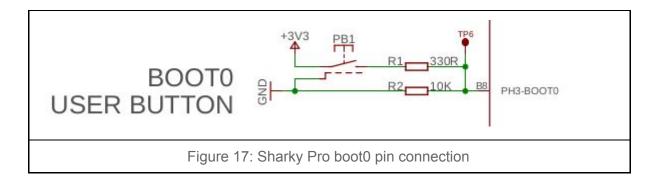

| Figure 17: Sharky Pro boot0 pin connection                               | 35 |

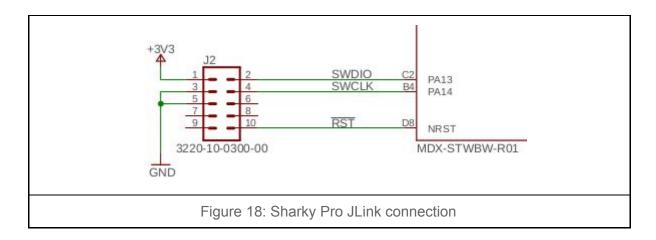

| Figure 18: Sharky Pro JLink connection                                   | 36 |

| Figure 19: Sharky Pro JLink with connection cable                        | 36 |

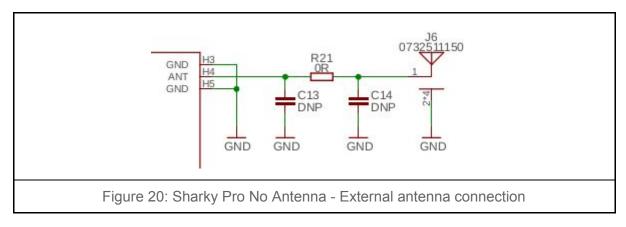

| Figure 20: Sharky Pro No Antenna - External antenna connection           | 37 |

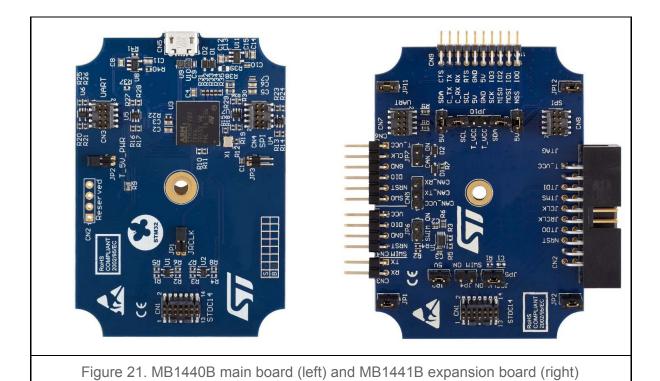

| Figure 21. MB1440B main board (left) and MB1441B expansion board (right) | 38 |

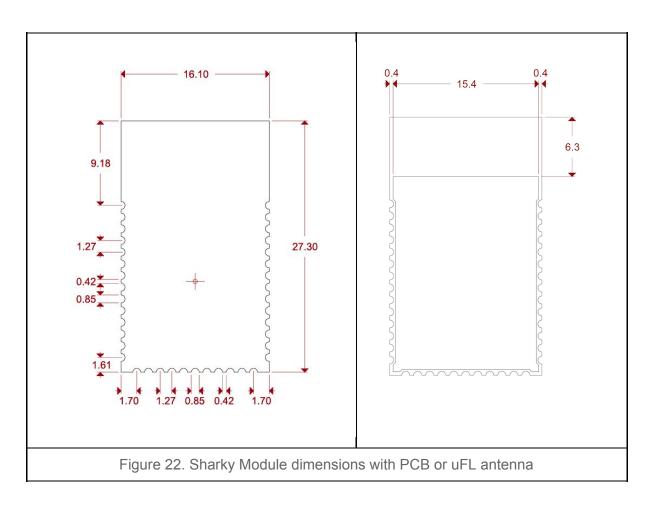

| Figure 22. Sharky Module dimensions with PCB or uFL antenna              | 40 |

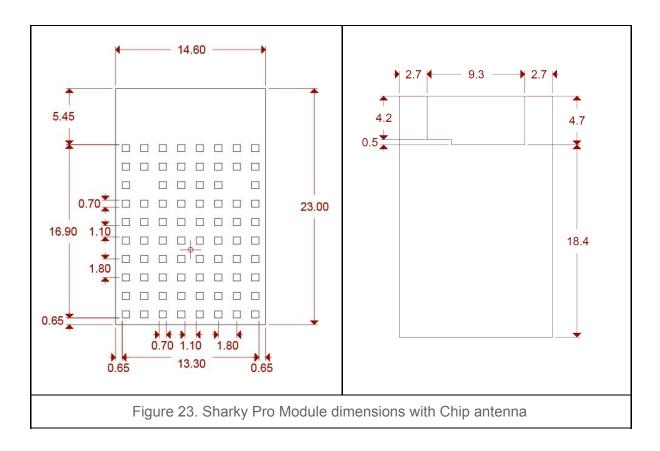

| Figure 23. Sharky Pro Module dimensions with Chip antenna                | 41 |

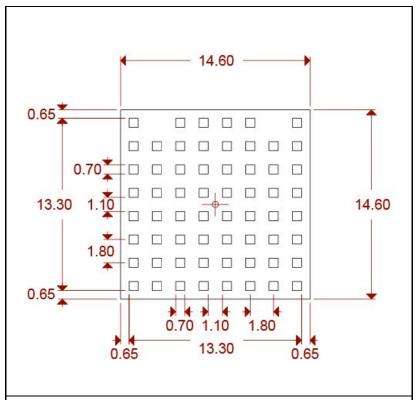

| Figure 24. Sharky Pro Module dimensions with no antenna                  | 42 |

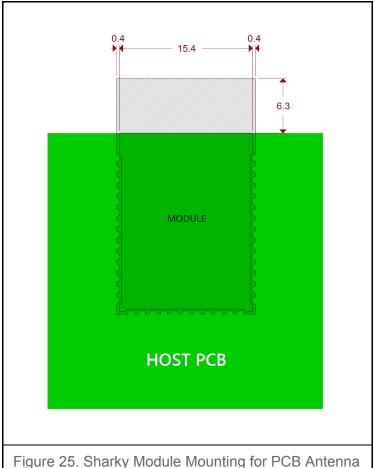

| Figure 25. Sharky Module Mounting for PCB Antenna                        | 44 |

2020/07/20

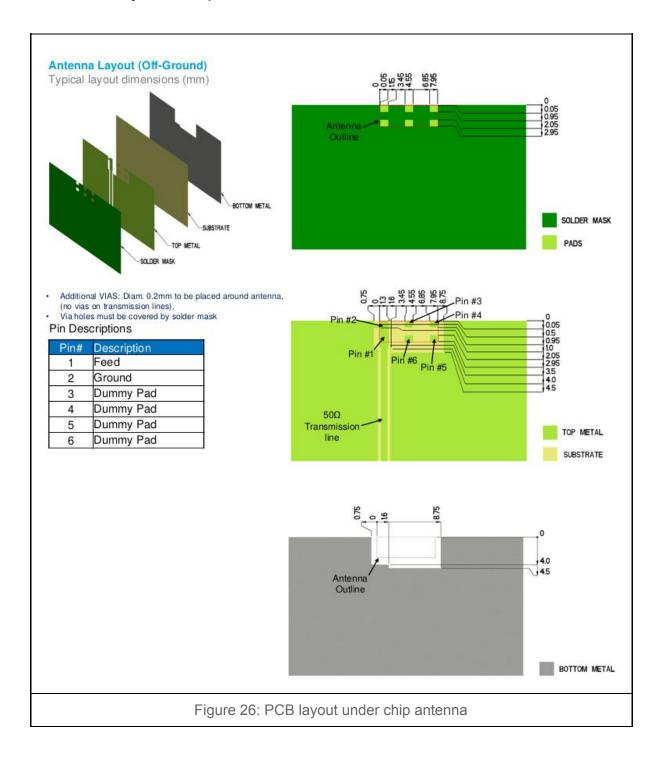

| Figure 26: PCB layout under chip antenna                                 | 45 |

|--------------------------------------------------------------------------|----|

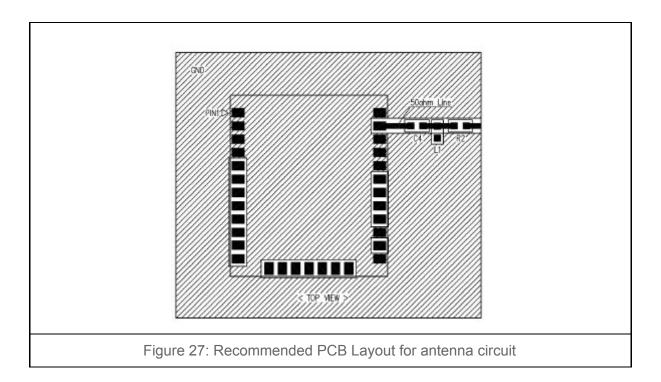

| Figure 27: Recommended PCB Layout for antenna circuit                    | 46 |

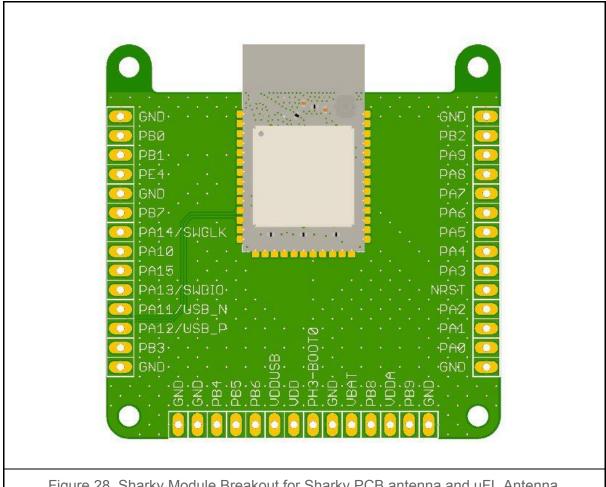

| Figure 28. Sharky Module Breakout for Sharky PCB antenna and uFL Antenna | 47 |

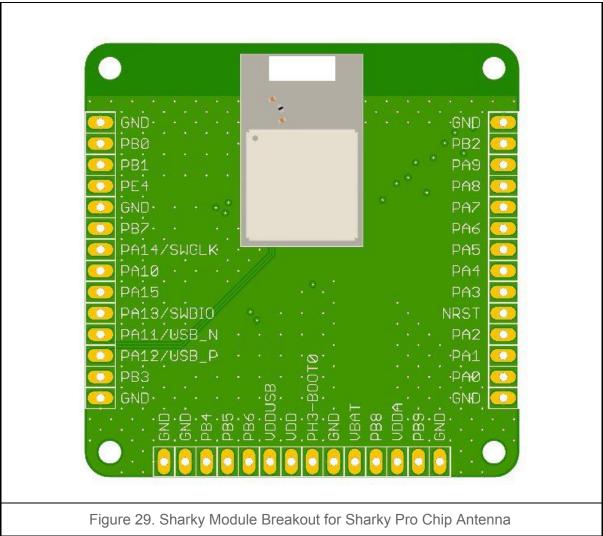

| Figure 29. Sharky Module Breakout for Sharky Pro Chip Antenna            | 48 |

| Figure 30. Sharky Module Breakout for Sharky Pro No Antenna              | 49 |

| Figure 31. Sharky PCB Antenna radiation pattern                          | 50 |

| Figure 32. Sharky PCB Antenna radiation pattern                          | 51 |

| Figure 33. Atollic TrueStudio for STM32 IDE                              | 54 |

2020/07/20

## **Tables**

| Table 1. Module internal pins | 18 |

|-------------------------------|----|

| Table 2. Sharky Pinout        | 22 |

| Table 3. Sharky Pro pinout    | 27 |

| Table 4. SWD connector CN6    | 38 |

## **Revisions**

| REVISION | DATE       | DESCRIPTION                       | STATUS | AUTHOR               | REVISER |

|----------|------------|-----------------------------------|--------|----------------------|---------|

| 1.0      | 2019/04/04 | First Release                     | Draft  | info@midatronics.com | UA-EM   |

| 1.1      | 2019/09/19 | Changed chap 9                    | Draft  | info@midatronics.com | UA-EM   |

| 1.2      | 2020/02/07 | Changed chap 3.1, 4, 5, 6         | Draft  | info@midatronics.com | UA-EM   |

| 1.3      | 2020/03/30 | Added chap 4.4                    | Draft  | info@midatronics.com | UA      |

| 1.4      | 2020/05/29 | Changes for FCC                   | Draft  | info@midatronics.com | UA      |

| 1.5      | 2020/06/11 | Updated Sharky<br>Dimension image | Draft  | info@midatronics.com | UA      |

| 1.6      | 2020/07/20 | Updated chap.<br>4.1              | Draft  | info@midatronics.com | UA      |

## **Disclaimer**

All rights strictly reserved. Reproduction in any form is not permitted without written authorization from Midatronics S.r.l.

Midatronics S.r.l. Via Zucchi 1 20900 Monza (Monza Brianza) Italy info@midatronics.com www.midatronics.com

2020/07/20

#### 1.1. List of FCC rules

The SHARKY module have received Federal Communications Commission (FCC) CFR47 Telecommunications, Part 15 Subpart C "Intentional Radiators" single-modular approval in accordance with Part 15.212 Modular Transmitter approval.

According to FCC Part 15.212 the single-modular transmitter is a completely self-contained radiofrequency transmitter device that is typically incorporated into another product, host or device and complies to all the conditions to be defined as a "single modular transmitter".

The Midatronics SHARKY Modular Transmitter is also compliant to FCC Part 15.247 insofar as it is a device using a wide band modulation inside the band 2400-2483.5 MHz with a 6dB bandwidth greater than 500kHz.

### 2. Introduction

### 2.1. Description

This document describes the Sharky modules.

Sharky is a complete family of modules that enables customer to test and integrate the new STM32WB MCU for rapid prototyping and fast time to market.

Sharky modules are based on STMicroelectronics STM32WB55CE, a dual-core MCUs with wireless support based on an Arm® Cortex®-M4 core running at 64 MHz (application processor) plus an Arm® Cortex®-M0+ core at 32 MHz (network processor).

With two totally independent cores, this innovative architecture is optimized for real-time execution (radio-related software processing).

The STM32WB55 Bluetooth 5.0-certified device offers Mesh 1.0 software support, multiple profiles and flexibility to integrate proprietary BLE stacks.

OpenThread-certified software stack is available. The radio can also run BLE/OpenThread protocols concurrently. The embedded generic MAC allows the usage of other IEEE 802.15.4 proprietary stacks like ZigBee®, or proprietary protocols, giving even more options for connecting devices to the Internet of Things (IoT).

The Sharky module is available in four versions:

- Sharky with PCB Antenna

- Sharky with uFL connector

- Sharky Pro with Chip Antenna

- Sharky Pro with no antenna

2020/07/20

Sharky modules are sold standalone or soldered on a breakout board for easy connections.

#### **Main features**

- Module size from 16.1 x 27.3 mm down to 14.6 x 14.6 mm

- Module with:

- o PCB antenna

- o uFL antenna connector

- Chip antenna

- No antenna

- Integrated BLE/OpenThread or IEEE 802.15.4 programmable networking stacks

# 3. System Overview

## 3.1. BLE Technology Overview

Bluetooth Low Energy (BLE) is the main feature of the Bluetooth specification v4.0 released in December 2009. BLE is a new protocol that allows for long-term operation of Bluetooth devices that transmit low volumes of data. BLE enables smaller form factors, better power optimization, and the ability to operate on a small power cell for several years.

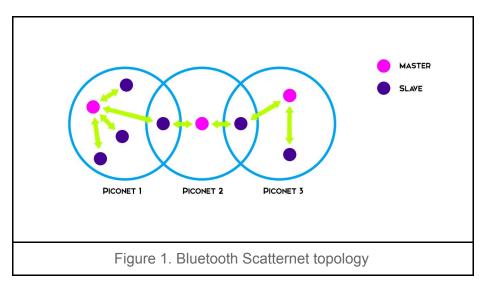

The classic Bluetooth specification defines a uniform structure for a wide range of devices that connect to each other. Bluetooth operates primarily using ad hoc piconets. A master device controls up to seven slaves per piconet; the slaves communicate with the master device but they do not communicate with each other. However, a slave device may participate in one or more piconets, essentially a collection of devices connected via Bluetooth. A summary of classic Bluetooth topology with multiple piconets, called scatternet, can be found below.

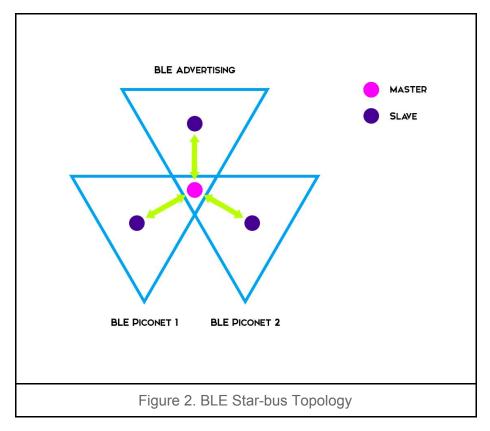

In a BLE topology, the slaves each communicate on a separate physical channel with the master. Unlike a classic Bluetooth piconet, where all slaves listen for incoming connections and therefore need to be on constant standby, a BLE slave invites connections and so is in total control of when to consume power. A BLE master, which is assumed to have less power constraints, will listen for advertisements and make connections on the back of an advertisement packet. A diagram of this can be found below.

While BLE inherits the operating spectrum and the basic structure of the communication protocol from the classic Bluetooth protocol, BLE implements a new lightweight Link Layer that provides ultra-low power idle mode operation, fast device discovery, and reliable and secure point-to-multipoint data transfers. As a result, BLE offers substantially lower peak, average, and idle-mode power consumption than classic Bluetooth. Averaged over time, BLE consumes only 10% of the power consumed by classic Bluetooth.

In addition to its ultra-low power consumption, BLE has several unique features that set it apart from other available wireless technologies, including:

- Interoperability: Like classic Bluetooth devices, BLE devices follow standards set by the Bluetooth Special Interest Group (SIG), and BLE devices from different manufacturers interoperate.

- **Robustness**: BLE uses fast frequency hopping to secure a robust transmission even in the presence of other wireless technologies.

- **Ease of Use**: BLE has been developed so that it is straightforward for designers to implement it in a variety of different applications.

- Latency: The total time to send small chunks of data is generally fewer than 6 ms, and as low as 3 ms (compared to 100 ms with classic Bluetooth).

- Range: Thanks to an increased modulation index, BLE technology offers greater range (up to 200 feet and beyond, in ideal environments) than to classic Bluetooth offers.

### 3.2. BLE Mesh Technology overview

Borrowing from the original Bluetooth specification, the Bluetooth SIG defines several profiles — specifications for how a device works in a particular application — for low energy devices. Manufacturers are expected to implement the appropriate specifications for their device in order to ensure compatibility. A device may contain implementations of multiple profiles.

Majority of current low energy application profiles is based on the generic attribute profile (GATT), a general specification for sending and receiving short pieces of data known as attributes over a low energy link. Bluetooth mesh profile is the exception to this rule as it is based on General Access Profile (GAP).

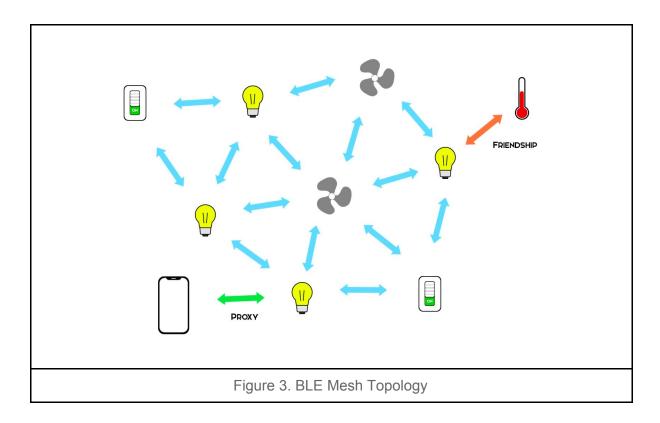

Bluetooth mesh profiles use Bluetooth Low Energy to communicate with other Bluetooth Low Energy devices in the network. Each device can pass the information forward to other Bluetooth Low Energy devices creating a "mesh" effect. For example, switching off an entire building of lights from a single smartphone.

Conceptually, the Bluetooth Mesh Standard is defined as a publish/subscribe model where publishers can publish to a certain topic and subscribers can subscribe to one or more topics of interest.

This concept is used as an inspiration for the implementation in the standard. A node in a Bluetooth Mesh network can subscribe to one or more addresses (stored in the *subscriber list*) and publish to one specific address (stored in the *publish address*).

To be able to connect these different publishers and subscribers, a mesh topology is created. The standard uses BLE advertising and scanning as an underlying technology to implement communication. To communicate in a Bluetooth Mesh network, a flooding mechanism is used. By default, a flooding mechanism ensures that each node in the network repeats incoming messages, so that they are relayed further, until the destination node is reached.

The standard uses a new type of BLE advertisement packet to communicate in a mesh network, which is only supported by devices that support both BLE and Bluetooth Mesh. Fortunately, the standard also defines a backwards compatibility feature to ensure that BLE devices which do not support Bluetooth Mesh can also be part of a Bluetooth Mesh network.

### 3.3. Thread Technology overview

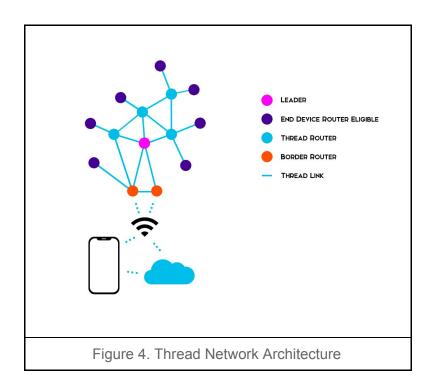

Thread is a secure, wireless mesh networking protocol. The Thread stack is an open standard that is built upon a collection of existing Institute for Electrical and Electronics Engineers (IEEE) and Internet Engineering Task Force (IETF) standards.

The Thread stack supports IPv6 addresses and provides low-cost bridging to other IP networks and is optimized for low-power/battery-backed operation, and wireless device-to-device communication. The Thread stack is designed specifically for Connected Home applications where IP-based networking is desired and a variety of application layers can be used on the stack.

2020/07/20

These are the general characteristics of the Thread stack focused on the Connected Home:

- Simple network installation, start-up, and operation: The Thread stack supports several network topologies. Installation is simple using a smartphone, tablet, or computer. Product installation codes are used to ensure only authorized devices can join the network. The simple protocols for forming and joining networks allow systems to self-configure and fix routing problems as they occur.

- Secure: Devices do not join the network unless authorized and all communications are encrypted and secure. Security is provided at the network layer and can be at the application layer. All Thread networks are encrypted using a smartphone-era authenticationscheme and Advanced Encryption Standard (AES) encryption. The security used in Thread networks is stronger than other wireless standards the Thread Group has evaluated.

- Small and large networks: Home networks vary from several to hundreds of devices. The networking layer is designed to optimize the network operation based on the expected use.

- Range: Typical devices provide sufficient range to cover a normal home. Readily

available designs with power amplifiers extend the range substantially. A

distributed spread spectrum is used at the Physical Layer (PHY) to be more

immune to interference.

- **No single point of failure**: The Thread stack is designed to provide secure and reliable operations even with the failure or loss of individual devices.

- Low power: Devices efficiently communicate to deliver an enhanced user experience with years of expected life under normal battery conditions. Devices can typically operate for several years on AA type batteries using suitable duty cycles.

- Cost-effective: Compatible chipsets and software stacks from multiple vendors are priced for mass deployment, and designed from the ground up to have extremely low-power consumption. Typical home products run in the connected home include: normally powered (lighting, appliances, HVAC, fans), powered or battery-operated (thermostats, smoke detectors, CO and CO2 detectors, security systems), and normally battery-operated (door sensors, window sensors, motion sensors, door locks).

2020/07/20

### 3.4. STM32WB Wireless System-on-Chip

The Sharky modules are based on STMicroelectronics STM32WB55CE, a dual-core MCUs with wireless support are based on an Arm® Cortex®-M4 core running at 64 MHz (application processor) plus an Arm® Cortex®-M0+ core at 32 MHz (network processor).

The STM32WB platform is an evolution of the well-known market-leading STM32L4 ultra-low-power series of MCUs. It provides the same digital and analog peripherals suitable for applications requiring extended battery life and complex functionalities.

STM32WB proposes a variety of communication assets, a practical crystal-less USB2.0 FS interface, audio support, an LCD driver, up to 72 GPIOs, an integrated SMPS for power consumption optimization, and multiple low-power modes to maximize battery life.

On top of wireless and ultra-low-power aspects, a particular focus was placed on embedding security hardware functions such as a 256-bit AES, PCROP, JTAG Fuse, PKA (elliptic curve encryption engine), and Root Secure Services (RSS). The RSS allows authenticating OTA communications, regardless of the radio stack or application.

For more informations on STM32WB visit the following site:

https://www.st.com/en/microcontrollers/stm32wb-series.html?querycriteria=productId=SS196

## 3.5. Block Diagram

SHARKY PRO NO ANTENNA STM32WB55CE DC/DC 512 KByte 256 KByte Flash SRAM IPCC 32.7 KHz Networking Application Stack RF Front AES256 End ARM ARM Cortex M4 Cortex M0+ MHz USART USB SPI I2C DIO ADC LCD Figure 7. Sharky Pro Module with no Antenna

## 4. Connectors

The following picture shows the connectors of the three Sharky types. The following MCU pins are used internally and not exposed in connector:

| PIN | NAME/FUNCTION                 | Connected to:                |  |  |  |  |

|-----|-------------------------------|------------------------------|--|--|--|--|

| 2   | PC14-OSC32_IN                 | 32.768 KHzquartz oscillator  |  |  |  |  |

| 3   | PC15-OSC32_OUT                | 32.768 KHz quartz oscillator |  |  |  |  |

| 25  | OSC_IN                        | 32 MHz quartz oscillator     |  |  |  |  |

| 24  | OSC_OUT                       | 32 MHz quartz oscillator     |  |  |  |  |

| 21  | RF1                           | 2.4 GHz Filter               |  |  |  |  |

| 26  | AT0                           | n.c.                         |  |  |  |  |

| 27  | AT1                           | n.c.                         |  |  |  |  |

| 34  | VDDSMPS                       | VCC                          |  |  |  |  |

| 33  | VLXSMPS                       | SMPS circuit                 |  |  |  |  |

| 31  | VFBSMPS                       | SMPS circuit                 |  |  |  |  |

| 32  | VSSSMPS                       | SMPS circuit                 |  |  |  |  |

| 23  | VDDRF                         | Filter Capacitors            |  |  |  |  |

| 22  | VSSRF                         | Filter Capacitors            |  |  |  |  |

| EP  | EP                            | GND                          |  |  |  |  |

|     | Table 1. Module internal pins |                              |  |  |  |  |

Doc: UG\_MDX-STWBx, Rev 1.6 pag. 18 of 57

## 4.1. Sharky Module

| Sharky<br>Pin | pin | SoC Pin | typ | str    | STM32WB55CE I/O                                                                                                               |

|---------------|-----|---------|-----|--------|-------------------------------------------------------------------------------------------------------------------------------|

| P1            |     | GND     | S   |        |                                                                                                                               |

| P2            | 28  | PB0     | I/O | TT     | COMP1_OUT, CM4_EVENTOUT, EXT_PA_TX                                                                                            |

| P3            | 29  | PB1     | I/O | TT     | LPUART1_RTS_DE, LPTIM2_IN1, CM4_EVENTOUT                                                                                      |

| P4            | 30  | PE4     | I/O | FT     | CM4_EVENTOUT                                                                                                                  |

| P5            |     | GND     | S   |        |                                                                                                                               |

| P6            | 47  | PB7     | I/O | FT_fla | LPTIM1_IN2, TIM1_BKIN, I2C1_SDA, USART1_RX, TSC_G2_IO4, LCD_SEG21, TIM17_CH1N, CM4_EVENTOUT, COMP2_INM, PVD_IN                |

| P7            | 41  | PA14    | I/O | FT_I   | JTCK-SWCLK, LPTIM1_OUT, I2C1_SMBA, LCD_SEG5, SAI1_FS_B, CM4_EVENTOUT                                                          |

| P8            | 36  | PA10    | I/O | FT_fl  | TIM1_CH3, SAI1_PDM_DI1, I2C1_SDA, USART1_RX, USB_CRS_SYNC, LCD_COM2, SAI1_SD_A, TIM17_BKIN, CM4_EVENTOUT                      |

| P9            | 42  | PA15    | I/O | FT_I   | JTDI, TIM2_CH1, TIM2_ETR, SPI1_NSS, TSC_G3_IO1, LCD_SEG17, CM4_EVENTOUT                                                       |

| P10           | 39  | PA13    | I/O | FT_u   | JTMS-SWDIO, IR_OUT, USB_NOE, SAI1_SD_B, CM4_EVENTOUT                                                                          |

| P11           | 37  | PA11    | I/O | FT_u   | TIM1_CH4, TIM1_BKIN2, SPI1_MISO, USART1_CTS, USB_DM, CM4_EVENTOUT                                                             |

| P12           | 38  | PA12    | I/O | FT_u   | TIM1_ETR, SPI1_MOSI, LPUART1_RX, USART1_RTS_DE, USB_DP, CM4_EVENTOUT                                                          |

| P13           | 43  | PB3     | I/O | FT_la  | JTDO-TRACESWO, TIM2_CH2, SPI1_SCK, USART1_RTS_DE, LCD_SEG7, SAI1_SCK_B, CM4_EVENTOUT, COMP2_INM                               |

| P14           |     | GND     | S   |        |                                                                                                                               |

| P15           | 44  | PB4     | I/O | FT_fla | NJTRST, I2C3_SDA, SPI1_MISO,<br>USART1_CTS,TSC_G2_IO1, LCD_SEG8,<br>SAI1_MCLK_B, TIM17_BKIN, CM4_EVENTOUT,<br>COMP2_INP       |

| P16           | 45  | PB5     | I/O | FT_I   | LPTIM1_IN1, I2C1_SMBA, SPI1_MOSI, USART1_CK, LPUART1_TX, TSC_G2_IO2, LCD_SEG9, COMP2_OUT, SAI1_SD_B, TIM16_BKIN, CM4_EVENTOUT |

2020/07/20

| P17 | 46 | PB6    | I/O | FT_fla | LPTIM1_ETR, I2C1_SCL, USART1_TX, TSC_G2_IO3, LCD_SEG6, SAI1_FS_B, TIM16_CH1N, MCO, CM4_EVENTOUT, COMP2_INP                              |

|-----|----|--------|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------|

| P18 | 40 | VDDUSB | S   |        |                                                                                                                                         |

| P19 |    | VCC    | S   |        |                                                                                                                                         |

| P20 | 4  | PH3    | I/O | FT     | BOOT0, CM4_EVENTOUT, LSCO                                                                                                               |

| P21 |    | GND    | S   |        |                                                                                                                                         |

| P22 | 1  | VBAT   | S   |        |                                                                                                                                         |

| P23 | 5  | PB8    | I/O | FT_fl  | TIM1_CH2N, SAI1_PDM_CK1, I2C1_SCL,<br>QUADSPI_BK1_IO1, LCD_SEG16, SAI1_MCLK_A,<br>TIM16_CH1, CM4_EVENTOUT                               |

| P24 | 8  | VDDA   | S   |        |                                                                                                                                         |

| P25 | 6  | PB9    | I/O | FT_fla | TIM1_CH3N, SAI1_PDM_DI2,<br>I2C1_SDA, SPI2_NSS, IR_OUT, TSC_G7_IO4,<br>QUADSPI_BK1_IO0, LCD_COM3, SAI1_FS_A,<br>TIM17_CH1, CM4_EVENTOUT |

| P26 |    | GND    | S   |        |                                                                                                                                         |

| P27 | 9  | PA0    | I/O | FT_a   | TIM2_CH1, COMP1_OUT, SAI1_EXTCLK, TIM2_ETR, CM4_EVENTOUT, COMP1_INM, ADC1_IN5, RTC_TAMP2/WKUP1                                          |

| P28 | 10 | PA1    | I/O | FT_la  | TIM2_CH2, I2C1_SMBA, SPI1_SCK, LCD_SEG0, CM4_EVENTOUT, COMP1_INP, ADC1_IN6                                                              |

| P29 | 11 | PA2    | I/O | FT_la  | LSCO, TIM2_CH3, LPUART1_TX, QUADSPI_BK1_NCS, LCD_SEG1, COMP2_OUT, CM4_EVENTOUT, COMP2_INM, ADC1_IN7, WKUP4/LSCO                         |

| P30 | 7  | NRST   | I/O | RST    |                                                                                                                                         |

| P31 | 12 | PA3    | I/O | FT_la  | TIM2_CH4, SAI1_PDM_CK1, LPUART1_RX,<br>QUADSPI_CLK, LCD_SEG2, SAI1_MCLK_A,<br>CM4_EVENTOUT, COMP2_INP, ADC1_IN8                         |

| P32 | 13 | PA4    | I/O | FT_a   | SPI1_NSS, SAI1_FS_B, LPTIM2_OUT, LCD_SEG5, CM4_EVENTOUT, COMP1_INM, COMP2_INM, ADC1_IN9                                                 |

| P33 | 14 | PA5    | I/O | FT_a   | TIM2_CH1, TIM2_ETR, COMP1_INM, COMP2_INM, SPI1_SCK, LPTIM2_ETR, ADC1_IN10, SAI1_SD_B, CM4_EVENTOUT                                      |

| P34 | 15 | PA6    | I/O | FT_la  | TIM1_BKIN, SPI1_MISO, LPUART1_CTS,                                                                                                      |

2020/07/20

|     |                        |     |     |        | QUADSPI_BK1_IO3, LCD_SEG3, TIM16_CH1, CM4_EVENTOUT, ADC1_IN11                                                  |  |

|-----|------------------------|-----|-----|--------|----------------------------------------------------------------------------------------------------------------|--|

| P35 | 16                     | PA7 | I/O | FT_fla | TIM1_CH1N, I2C3_SCL, SPI1_MOSI,<br>QUADSPI_BK1_IO2, ADC1_IN12, LCD_SEG4,<br>COMP2_OUT, TIM17_CH1, CM4_EVENTOUT |  |

| P36 | 17                     | PA8 | I/O | FT_la  | MCO, TIM1_CH1, SAI1_PDM_CK2, USART1_CK, LCD_COM0, SAI1_SCK_A, LPTIM2_OUT, CM4_EVENTOUT, ADC1_IN15              |  |

| P37 | 18                     | PA9 | I/O | FT_fla | TIM1_CH2, SAI1_PDM_DI2, I2C1_SCL, SPI2_SCK, COMP1_INM, ADC1_IN16, USART1_TX, LCD_COM1, SAI1_FS_A, CM4_EVENTOUT |  |

| P38 | 19                     | PB2 | I/O | FT_a   | RTC_OUT, LPTIM1_OUT, I2C3_SMBA, SPI1_NSS, LCD_VLCD, SAI1_EXTCLK, CM4_EVENTOUT, COMP1_INP                       |  |

| P39 |                        | GND | S   |        |                                                                                                                |  |

| P40 |                        | GND | S   |        |                                                                                                                |  |

|     | Table 2. Sharky Pinout |     |     |        |                                                                                                                |  |

Legend:

| Name  | Abbreviation                                                                | Definition                                         |  |  |  |

|-------|-----------------------------------------------------------------------------|----------------------------------------------------|--|--|--|

|       | S                                                                           | Supply Pin                                         |  |  |  |

| typ   | I                                                                           | Input only pin                                     |  |  |  |

|       | I/O                                                                         | Input / output pin                                 |  |  |  |

|       | FT                                                                          | 5 V tolerant I/O                                   |  |  |  |

|       | TT                                                                          | 3.6 V tolerant I/O                                 |  |  |  |

|       | RF                                                                          | RF I/O                                             |  |  |  |

|       | RST                                                                         | Bidirectional reset pin with weak pull-up resistor |  |  |  |

| str   | Option for TT or FT I/Os                                                    |                                                    |  |  |  |

|       | _f                                                                          | I/O, Fm+ capable                                   |  |  |  |

|       | _l                                                                          | I/O, with LCD function supplied by V LCD           |  |  |  |

|       | _u                                                                          | I/O, with USB function supplied by V DDUSB         |  |  |  |

|       | _a                                                                          | I/O, with Analog switch function supplied by V DDA |  |  |  |

| Notes | Unless specified, all I/Os are set as analog inputs during and after reset. |                                                    |  |  |  |

## 4.2. Sharky Pro Module

Figure 9. Sharky Pro Module Pinout from top of module

| Sharky<br>Pro Pin | pin | SoC Pin | typ | str    | STM32WB55CE I/O                                                                                                               |

|-------------------|-----|---------|-----|--------|-------------------------------------------------------------------------------------------------------------------------------|

| JA1               |     | GND     | S   |        |                                                                                                                               |

| JA2               | 37  | PA11    | I/O | FT_u   | TIM1_CH4, TIM1_BKIN2, SPI1_MISO, USART1_CTS, USB_DM, CM4_EVENTOUT                                                             |

| JA3               | 38  | PA12    | I/O | FT_u   | TIM1_ETR, SPI1_MOSI, LPUART1_RX, USART1_RTS_DE, USB_DP, CM4_EVENTOUT                                                          |

| JA4               | 42  | PA15    | I/O | FT_I   | JTDI, TIM2_CH1, TIM2_ETR, SPI1_NSS, TSC_G3_IO1, LCD_SEG17, CM4_EVENTOUT                                                       |

| JA5               | 43  | PB3     | I/O | FT_la  | JTDO-TRACESWO, TIM2_CH2, SPI1_SCK, USART1_RTS_DE, LCD_SEG7, SAI1_SCK_B, CM4_EVENTOUT, COMP2_INM                               |

| JA6               | 45  | PB5     | I/O | FT_I   | LPTIM1_IN1, I2C1_SMBA, SPI1_MOSI, USART1_CK, LPUART1_TX, TSC_G2_IO2, LCD_SEG9, COMP2_OUT, SAI1_SD_B, TIM16_BKIN, CM4_EVENTOUT |

| JA7               | 46  | PB6     | I/O | FT_fla | LPTIM1_ETR, I2C1_SCL, USART1_TX, TSC_G2_IO3, LCD_SEG6, SAI1_FS_B, TIM16_CH1N, MCO, CM4_EVENTOUT, COMP2_INP                    |

| JA8               |     | GND     | S   |        |                                                                                                                               |

| JB1               |     | GND     | S   |        |                                                                                                                               |

| JB2               |     | VCC     | S   |        |                                                                                                                               |

| JB3               | 40  | VDDUSB  | S   |        |                                                                                                                               |

| JB4               | 41  | PA14    | I/O | FT_I   | JTCK-SWCLK, LPTIM1_OUT, I2C1_SMBA, LCD_SEG5, SAI1_FS_B, CM4_EVENTOUT                                                          |

| JB5               | 44  | PB4     | I/O | FT_fla | NJTRST, I2C3_SDA, SPI1_MISO,<br>USART1_CTS,TSC_G2_IO1, LCD_SEG8,<br>SAI1_MCLK_B, TIM17_BKIN, CM4_EVENTOUT,<br>COMP2_INP       |

| JB6               |     | VCC     | S   |        |                                                                                                                               |

| JB7               | 47  | PB7     | I/O | FT_fla | LPTIM1_IN2, TIM1_BKIN, I2C1_SDA, USART1_RX, TSC_G2_IO4, LCD_SEG21, TIM17_CH1N, CM4_EVENTOUT, COMP2_INM, PVD_IN                |

| JB8               | 4   | воото   |     | FT     | PH3-BOOT0                                                                                                                     |

| JC1               | 36  | PA10    | I/O | FT_fl  | TIM1_CH3, SAI1_PDM_DI1, I2C1_SDA, USART1_RX,                                                                                  |

2020/07/20

|     |    | ı    |     | 1      |                                                                                                                                         |

|-----|----|------|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------|

|     |    |      |     |        | USB_CRS_SYNC, LCD_COM2, SAI1_SD_A, TIM17_BKIN, CM4_EVENTOUT                                                                             |

| JC2 | 39 | PA13 | I/O | FT_u   | JTMS-SWDIO, IR_OUT, USB_NOE, SAI1_SD_B, CM4_EVENTOUT                                                                                    |

| JC3 |    | GND  | S   |        |                                                                                                                                         |

| JC4 |    | GND  | S   |        |                                                                                                                                         |

| JC5 |    | GND  | S   |        |                                                                                                                                         |

| JC6 |    | GND  | S   |        |                                                                                                                                         |

| JC7 | 1  | VBAT | S   |        |                                                                                                                                         |

| JC8 | 5  | PB8  | I/O | FT_fl  | TIM1_CH2N, SAI1_PDM_CK1, I2C1_SCL,<br>QUADSPI_BK1_IO1, LCD_SEG16, SAI1_MCLK_A,<br>TIM16_CH1, CM4_EVENTOUT                               |

| JD1 | 30 | PE4  | I/O | FT     | CM4_EVENTOUT                                                                                                                            |

| JD2 | 17 | PA8  | I/O | FT_la  | MCO, TIM1_CH1, SAI1_PDM_CK2, USART1_CK, LCD_COM0, SAI1_SCK_A, LPTIM2_OUT, CM4_EVENTOUT, ADC1_IN15                                       |

| JD3 |    | GND  | S   |        |                                                                                                                                         |

| JD4 |    | GND  | S   |        |                                                                                                                                         |

| JD5 |    | GND  | S   |        |                                                                                                                                         |

| JD6 |    | GND  | S   |        |                                                                                                                                         |

| JD7 | 6  | PB9  | I/O | FT_fla | TIM1_CH3N, SAI1_PDM_DI2,<br>I2C1_SDA, SPI2_NSS, IR_OUT, TSC_G7_IO4,<br>QUADSPI_BK1_IO0, LCD_COM3, SAI1_FS_A,<br>TIM17_CH1, CM4_EVENTOUT |

| JD8 | 7  | NRST | I/O | RST    |                                                                                                                                         |

| JE1 | 29 | PB1  | I/O | TT     | LPUART1_RTS_DE, LPTIM2_IN1, CM4_EVENTOUT                                                                                                |

| JE2 | 18 | PA9  | I/O | FT_fla | TIM1_CH2, SAI1_PDM_DI2, I2C1_SCL, SPI2_SCK, COMP1_INM, ADC1_IN16, USART1_TX, LCD_COM1, SAI1_FS_A, CM4_EVENTOUT                          |

| JE3 |    | GND  | S   |        |                                                                                                                                         |

| JE4 |    | GND  | S   |        |                                                                                                                                         |

| JE5 |    | GND  | S   |        |                                                                                                                                         |

| JE6 |    | GND  | S   |        |                                                                                                                                         |

2020/07/20

| JE7 | 9  | PA0  | I/O | FT_a  | TIM2_CH1, COMP1_OUT, SAI1_EXTCLK, TIM2_ETR, CM4_EVENTOUT, COMP1_INM, ADC1_IN5, RTC_TAMP2/WKUP1                  |

|-----|----|------|-----|-------|-----------------------------------------------------------------------------------------------------------------|

| JE8 | 10 | PA1  | I/O | FT_la | TIM2_CH2, I2C1_SMBA, SPI1_SCK, LCD_SEG0, CM4_EVENTOUT, COMP1_INP, ADC1_IN6                                      |

| JF1 | 28 | PB0  | I/O | TT    | COMP1_OUT, CM4_EVENTOUT, EXT_PA_TX                                                                              |

| JF2 | 19 | PB2  | I/O | FT_a  | RTC_OUT, LPTIM1_OUT, I2C3_SMBA, SPI1_NSS, LCD_VLCD, SAI1_EXTCLK, CM4_EVENTOUT, COMP1_INP                        |

| JF3 |    | GND  | S   |       |                                                                                                                 |

| JF4 |    | GND  | S   |       |                                                                                                                 |

| JF5 |    | GND  | S   |       |                                                                                                                 |

| JF6 |    | GND  | S   |       |                                                                                                                 |

| JF7 | 12 | PA3  | I/O | FT_la | TIM2_CH4, SAI1_PDM_CK1, LPUART1_RX, QUADSPI_CLK, LCD_SEG2, SAI1_MCLK_A, CM4_EVENTOUT, COMP2_INP, ADC1_IN8       |

| JF8 | 11 | PA2  | I/O | FT_la | LSCO, TIM2_CH3, LPUART1_TX, QUADSPI_BK1_NCS, LCD_SEG1, COMP2_OUT, CM4_EVENTOUT, COMP2_INM, ADC1_IN7, WKUP4/LSCO |

| JG1 |    | GND  | S   |       |                                                                                                                 |

| JG2 |    | VCC  | S   |       |                                                                                                                 |

| JG3 |    | GND  | S   |       |                                                                                                                 |

| JG4 |    | GND  | S   |       |                                                                                                                 |

| JG5 |    | GND  | S   |       |                                                                                                                 |

| JG6 | 15 | PA6  | I/O | FT_la | TIM1_BKIN, SPI1_MISO, LPUART1_CTS,<br>QUADSPI_BK1_IO3, LCD_SEG3, TIM16_CH1,<br>CM4_EVENTOUT, ADC1_IN11          |

| JG7 | 13 | PA4  | I/O | FT_a  | SPI1_NSS, SAI1_FS_B, LPTIM2_OUT, LCD_SEG5, CM4_EVENTOUT, COMP1_INM, COMP2_INM, ADC1_IN9                         |

| JG8 | 8  | VDDA | S   |       |                                                                                                                 |

| JH1 |    | GND  | S   |       |                                                                                                                 |

| JH3 |    | GND  | S   |       |                                                                                                                 |

2020/07/20

| JH4 |                            | GND    | S   |        | Chip Antenna Version                                                                                           |  |

|-----|----------------------------|--------|-----|--------|----------------------------------------------------------------------------------------------------------------|--|

|     |                            | RF OUT | S   |        | No Antenna Version                                                                                             |  |

| JH5 |                            | GND    | S   |        |                                                                                                                |  |

| JH6 | 16                         | PA7    | I/O | FT_fla | TIM1_CH1N, I2C3_SCL, SPI1_MOSI,<br>QUADSPI_BK1_IO2, ADC1_IN12, LCD_SEG4,<br>COMP2_OUT, TIM17_CH1, CM4_EVENTOUT |  |

| JH8 | 14                         | PA5    | I/O | FT_a   | TIM2_CH1, TIM2_ETR, COMP1_INM, COMP2_INM, SPI1_SCK, LPTIM2_ETR, ADC1_IN10, SAI1_SD_B, CM4_EVENTOUT             |  |

| JK1 | (a)                        | GND    | S   |        |                                                                                                                |  |

| JK2 | (a)                        | GND    | S   |        |                                                                                                                |  |

| JK3 | (a)                        | GND    | S   |        |                                                                                                                |  |

| JK4 | (a)                        | GND    | S   |        |                                                                                                                |  |

| JK5 | (a)                        | GND    | S   |        |                                                                                                                |  |

| JK6 | (a)                        | GND    | S   |        |                                                                                                                |  |

| JK7 | (a)                        | GND    | S   |        |                                                                                                                |  |

| JK8 | (a)                        | GND    | S   |        |                                                                                                                |  |

| JI1 | (a)                        | GND    | S   |        |                                                                                                                |  |

| JL2 | (a)                        | GND    | S   |        |                                                                                                                |  |

| JL3 | (a)                        | GND    | S   |        |                                                                                                                |  |

| JL4 | (a)                        | GND    | S   |        |                                                                                                                |  |

| JL5 | (a)                        | GND    | S   |        |                                                                                                                |  |

| JL6 | (a)                        | GND    | S   |        |                                                                                                                |  |

| JL7 | (a)                        | GND    | S   |        |                                                                                                                |  |

| JL8 | (a)                        | GND    | S   |        |                                                                                                                |  |

|     | Table 3. Sharky Pro pinout |        |     |        |                                                                                                                |  |

#### Legend:

(a) These pins are present only in Sharky Pro Chip Antenna module

2020/07/20

pag. 28 of 57

| Name  | Abbreviation                                                                | Definition                                         |  |  |  |

|-------|-----------------------------------------------------------------------------|----------------------------------------------------|--|--|--|

|       | S                                                                           | Supply Pin                                         |  |  |  |

| typ   | I                                                                           | Input only pin                                     |  |  |  |

|       | I/O                                                                         | Input / output pin                                 |  |  |  |

|       | FT                                                                          | 5 V tolerant I/O                                   |  |  |  |

|       | TT                                                                          | 3.6 V tolerant I/O                                 |  |  |  |

|       | RF                                                                          | RF I/O                                             |  |  |  |

|       | RST                                                                         | Bidirectional reset pin with weak pull-up resistor |  |  |  |

| str   | Option for TT or FT I/Os                                                    |                                                    |  |  |  |

|       | _f                                                                          | I/O, Fm+ capable                                   |  |  |  |

|       | _l                                                                          | I/O, with LCD function supplied by V LCD           |  |  |  |

|       | _u                                                                          | I/O, with USB function supplied by V DDUSB         |  |  |  |

|       | _a                                                                          | I/O, with Analog switch function supplied by V DDA |  |  |  |

| Notes | Unless specified, all I/Os are set as analog inputs during and after reset. |                                                    |  |  |  |

SHARKY - User's Guide

2020/07/20

# 5. Usage

This chapter describes how to connect, configure and interact with the Sharky and Sharky Pro modules.

### 5.1. Power Supply

Sharky and Sharky PRO modules are powered by:

- VCC/VDD pins, from 1.71 V to 3.6 V

- VDDA pin, from 1.62 V (ADCs/COMPs) to 2.4 V (VREFBUF) to 3.6 V.

VDDA is the external analog power supply for A/D converters, D/A converters, voltage reference buffer, operational amplifiers and comparators. The VDDA voltage level is independent from the VDD voltage and should preferably be connected to VDD when these peripherals are not used.

VDDUSB = 3.0 V to 3.6 V

VDDUSB is the external independent power supply for USB transceivers. The VDDUSB voltage level is independent from the VDD voltage and should preferably be connected to VDD when the USB is not used.

VBAT = 1.55 V to 3.6 V

VBAT is the power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when VDD is not present.

During power up and power down, the following power sequence is required:

- When VDD < 1 V, the other power supplies (VDDA, VDDUSB and V LCD) must</li> remain below VDD + 0.3 V. During the power down VDD can temporarily become lower than the other supplies only if the energy provided to the MCU remains below 1 mJ. This allows the external decoupling capacitors to discharge with different time constants.

- When VDD ≥ 1 V, all power supplies become independent.

An embedded linear voltage regulator is used to supply the internal digital power VCORE. VCORE is the power supply for digital peripherals, SRAM1 and SRAM2. The Flash memory is supplied by VCORE and VDD.

## 5.2. Sharky Connections

### 5.2.1. Power Supply on module configuration

In the Sharky module VBAT, VDDA and VDDUSB can be connected to VCC soldering 0402 size, zero ohm resistors on the module.

The resistor are reachable on Sharky PCB and can be soldered to connect the pin to VCC:

Figure 11: VDDUSB, VBAT and VDDA resistors placement (left side of PCB)

### 5.2.2. Power Supply

VDD, VDDUSB and VBAT must be connected to power supply. Optionally VDDA can be connected to power supply or to an external AVDD level.

#### 5.2.3. Reset Circuit

Reset pin is already pulled up internally in the STM32WB. From ST datasheet:

#### 6.3.18 NRST pin characteristics

The NRST pin input driver uses the CMOS technology. It is connected to a permanent pull-up resistor,  $R_{\rm PU}$ .

So NRST pin can be directly connected to the NRST signal of JLink V3SET

### 5.2.4. Boot0 pin

Boot0 pin must be tied to ground at boot when programming with ST-Link. It can also be used as user button after boot.

Boot0 pin s already connected to ground in the Sharky module, so R2 can be not populated.

If you do not use the bootloader you can leave the pin disconnected.

Connect the Boot0 pin to 3V3 then reset to load the embedded bootloader on boot.

#### 5.2.5. SWD - JLink-V3SET connection

In the following circuit you can see the mapping to the cable adapter that is in the JLink-V3SET package:

## 5.3. Sharky Pro Connections

### 5.3.1. Power Supply

VDD, VDDUSB and VBAT must be connected to power supply. Optionally VDDA can be connected to power supply or to an external AVDD level.

#### 5.3.2. Reset Circuit

Reset pin is already pulled up internally in the STM32WB. From ST datasheet:

#### 6.3.18 NRST pin characteristics

The NRST pin input driver uses the CMOS technology. It is connected to a permanent pull-up resistor,  $R_{\rm PU}$ .

So NRST pin can be directly connected to the NRST signal of JLink V3SET

### 5.3.3. Boot0 pin

Boot0 pin must be tied to ground at boot when programming with ST-Link. It can also be used as user button after boot.

Boot0 pin s already connected to ground in the Sharky module, so R2 can be not populated.

If you do not use the bootloader you can leave the pin disconnected.

Connect the Boot0 pin to 3V3 then reset to load the embedded bootloader on boot.

#### 5.3.4. SWD - JLink-V3SET connection

In the following circuit you can see the mapping to the cable adapter that is in the JLink-V3SET package:

#### 5.3.5. External antenna

This paragraph pertains only to Sharky Pro no Antenna module.

The H4 pin can be directly connected to an onboard antenna or connector for external antenna.

## 5.4. STLink-V3SET expansion board

STLink-V3SET is composed by two boards:

- MB1440B main board

- MB1441B expansion board (optional)

If the expansion board is plugged in the main board, the connector CN6 can be used to connect to the Sharky board debugging signal. From the UM2448 ST manual:

| STLINK Pin N.              | Description | Sharky Pin N. | Sharky Pro Pin N. | Description        |  |

|----------------------------|-------------|---------------|-------------------|--------------------|--|

| 1                          | T_VCC       | VCC           | VCC               | Input for STLink   |  |

| 2                          | T_SWCLK     | 7             | B4                | PA14/SWCLK         |  |

| 3                          | GND         | GND           | GND               |                    |  |

| 4                          | T_SWDIO     | 10            | C2                | PA13/SWDIO         |  |

| 5                          | T_NRST      | 30            | D8                | NRST               |  |

| 6                          | T_SWO       | 13            | A5                | PB3/SWO (optional) |  |

| Table 4. SWD connector CN6 |             |               |                   |                    |  |

Document: SHARKY - User's Guide

2020/07/20

## 5.5. Operating Conditions

Working temperature range: -40 to 85°C

Junction temperature range: -40 to 105 °C

Working relative humidity range: 20 to 80%

Power Supply: 1.71 to 3.6 V

USB supply voltage, USB used: 3.0 to 3.6 V

# 6. Board Layout

The following pictures show the dimensions of the three Sharky types.

# 6.1. Sharky Module

## 6.2. Sharky Pro Module with Chip Antenna

## 6.3. Sharky Pro Module No Antenna

Figure 24. Sharky Pro Module dimensions with no antenna - view from top of module

Document: SHARKY - User's Guide

2020/07/20

## 6.4. Mounting Suggestions

The module must be placed on host board, the printed antenna area must not overlap with the carrier board. The portion of the module containing the antenna should stick out over the edge of the host board.

Figure 25 shows the best case module placement in host board.

Do not place the module in the middle of the host board or far away from the host board edge.

Follow the module placement, keepout, host PCB cutout recommendation as shown in Figure 25

Avoid routing any traces in the region on the top layer of the host board which will be directly below the module area.

Keep the large metal objects away from antenna to avoid electromagnetic field blocking. Do not enclose the antenna within a metal shield.

Keep any components which may radiate noise or signals within the  $2.4~\mathrm{GHz}-2.5~\mathrm{GHz}$  frequency band away from the antenna and if possible, shield those components. Any noise radiated from the host board in this frequency band will degrade the sensitivity of the module.

Make sure the width of the traces routed to GND, VDD and VBAT rails are sufficiently larger forhandling the peak Tx current consumption

#### 6.4.1. Sharky PCB Antenna

The Sharky module must be mounted leaving the antenna section of the PCB outside the host PCB ad in Figure 15.

In this configuration, it is necessary to keep the output power of the last Bluetooth channel (2480MHz) below 1dBm for regulatory limits. Or as an alternative, the last Bluetooth channel must not to be used.

#### 6.4.2. Sharky uFL Antenna

The Sharky uFL antenna module has no particular requirements for board placement.

Keep the large metal objects away from antenna to avoid electromagnetic field blocking. Do not enclose the antenna within a metal shield.

Keep any components which may radiate noise or signals within the 2.4 GHz - 2.5 GHz frequency band away from the antenna and if possible, shield those components. Any noise

radiated from the host board in this frequency band will degrade the sensitivity of the module.

Make sure the width of the traces routed to GND, VDD and VBAT rails are sufficiently larger forhandling the peak Tx current consumption

### 6.4.3. Sharky Pro Chip Antenna

### 6.4.4. Sharky Pro external antenna

## 6.4.5. Sharky uFL Suggested Antennas

| Manufacturer | Part Number | Frequencies                                     | Specification                                                                    |

|--------------|-------------|-------------------------------------------------|----------------------------------------------------------------------------------|

| 2J-antennae  | 2JP0102P    | WIFI / BLUETOOTH<br>(2.4 GHz)<br>WIFI (5.0 GHz) | Impedance: 50 Ohm<br>Polarization: Linear<br>Gain: 5.0 dBi Max.<br>VSWR: < 2.4:1 |

## 6.5. Sharky Breakout

## 6.5.1. Sharky PCB/uFL antenna

Figure 28. Sharky Module Breakout for Sharky PCB antenna and uFL Antenna

Part number for ordering with module soldered:

MDX-BRK-STWBP-R01: with PCB antenna module

MDX-BRK-STWBU-R01: with uFL antenna module

#### 6.5.2. Sharky Pro Chip Antenna

Part number for ordering with module soldered:

MDX-BRK-STWBC-R01: with Sharky Pro Chip Antenna Module

#### 6.5.3. Sharky Pro No Antenna

Part number for ordering with module soldered:

MDX-BRK-STWBW-R01: with Sharky Pro no Antenna Module

# 7. Radiation pattern plots

## 7.1. Sharky PCB-Ant module

Figure 31. Sharky PCB Antenna radiation pattern

# 7.2. Sharky Pro Chip Antenna module

2020/07/20

# 8. Firmware Upload

The STM32WB SoC inside the Sharky module has 2 cores that share the same FLASH and SRAM addresses:

- M0+ core for embedded communication stack

- M4 core for user application

The module is delivered with BLE communication stack firmware installed on M0+ core and Transparent VCP firmware on M4 core. This configuration allows testing the module with STM32CubeMonitor-RF application from ST that can be downloaded from:

#### https://www.st.com/en/development-tools/stm32cubemonrf.html

Thread and other stacks can be installed by the user.

### 8.1. FW upload to M4 core

The GUI application for flashing firmware is STM32CubeProgrammer, available for Windows, Linux and MacOS operating systems. It can be downloaded from ST at:

#### https://www.st.com/en/development-tools/stm32cubeprog.html

The firmware for the M4 CPU can be uploaded:

- Using an STLink V2 or V3 device connected to the SWD interface

- Using the embedded ROM Bootloader that is selected by rising the BOOT0 pin on reset. In this case the firmware can be uploaded via USB or UART

## 8.2. FW upload to M0+ core

The M0+ firmware cannot be uploaded using STLink programmer, only the internal bootloader is allowed to update the firmware.

ST provides the en.stm32cubewb.zip package (download from: <a href="https://www.st.com/en/embedded-software/stm32cubewb.html">https://www.st.com/en/embedded-software/stm32cubewb.html</a>)

With the following compiled communication staks:

- stm32wb5x\_BLE\_Stack\_fw.bin

- Full BLE Stack 5.0 certified : Link Layer, HCI, L2CAP, ATT, SM, GAP and GATT database

- o BT SIG Certification listing: Declaration ID D042164

- stm32wb5x\_BLE\_HCILayer\_fw.bin

- o HCI Layer only mode 5.0 certified : Link Layer, HCI

- o BT SIG Certification listing: Declaration ID D042213

- stm32wb5x\_Thread\_FTD\_fw.bin

- o Full Thread Device certified v1.1

Document: SHARKY - User's Guide

2020/07/20

- To be used for Leader / Router / End Device Thread role (full features excepting Border Router)

- stm32wb5x Thread MTD fw.bin

- Minimal Thread Device certified v1.1

- To be used for End Device and Sleepy End Device Thread role

- stm32wb5x\_BLE\_Thread\_fw.bin

- Static Concurrent Mode BLE Thread

- Supports Full BLE Stack 5.0 certified and Full Thread Device certified v1.1

- stm32wb5x Mac 802 15 4 fw.bin

- o MAC API is based on latest official IEEE Std 802.15.4-2011

- o To be used for MAC FFD and RFD devices

- stm32wb5x\_rfmonitor\_phy802\_15\_4\_fw.bin

- Dedicated firmware binary to be used with STM32CubeMonitor-RF application.

- Refer to STM32CubeMonitor-RF User Manual (UM2288) to get application details.

To flash the firmware follow the instructions (from the file "Release\_Notes.html" in /STM32Cube\_FW\_WB\_V1.0.0/Projects/STM32WB\_Copro\_Wireless\_Binaries extracted from en.stm32cubewb.zip package:

- STEP 1: Use STM32CubeProgrammer

- Version 1.4 or higher.

- It gives access to Firmware Upgrade Service (FUS) (AN 5185) through Bootloader.

- It is currently available as Command Line Interface (CLI) mode.

- STEP 2: Access to Bootloader USB Interface (system flash)

- Boot mode selected by Boot0 pin set to VDD (check option bytes nBOOT0 and nBOOT1 are set)

- Keep user button pressed during reboot

- STEP 3 : Delete current wireless stack :

- STM32\_Programmer\_CLI.exe -c port=usb1 -fwdelete

- STEP 4 : Download new wireless stack :

- STM32\_Programmer\_CLI.exe -c port=usb1 -fwupgrade [Wireless\_Coprocessor\_Binary] [Install address] firstinstall=1

- Please check Binary Install Address Table for Install@ parameter depending of the binary.

- STEP 5: Revert STEP 2 procedure to put back device in normal mode.

Detailed informations and instructions for STM32CubeProgrammer in the manual: <a href="https://www.st.com/content/ccc/resource/technical/document/user\_manual/group0/76/3e/bd/0d/cf/4d/45/25/DM00403500/files/DM00403500.pdf/jcr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/translations/en.DM00403500.pdf/gr:content/transla

# 9. Software Development

The firmware can be developed and uploaded with STLink V2 or V3 device using the integrated IDE provided by ST, that can be downloaded from <a href="https://www.st.com/en/development-tools/stm32cubeide.html">https://www.st.com/en/development-tools/stm32cubeide.html</a>

The developed application runs on the M4 core and interfaces to the communication stack on M0+ core using the communication functions provided by ST.

Figure 33. STM32CubeIDE from ST

In order to develop a custom firmware to be uploaded to the Sharky Module the following tools are necessary:

- A Windows/Linux/MacOS PC

- STM32CubeIDE

- STLink V2 or V3 device <a href="https://www.st.com/content/st\_com/en/products/development-tools/hardware-development-tools/hardware-development-tools-for-stm32/st-link-v2.html">https://www.st.com/content/st\_com/en/products/development-tools/hardware-development-tools-for-stm32/st-link-v2.html</a>

The ST-LINK/V2 is an in-circuit debugger and programmer for the STM8 and STM32 microcontroller families. The single wire interface module (SWIM) and JTAG/serial wire debugging (SWD) interfaces are used to communicate with any STM8 or STM32 microcontroller located on an application board.

## 10. References and Useful Links

#### 10.1. Data Sheets and documents

- https://www.st.com/content/st\_com/en/products/microcontrollers-microprocessors/st m32-32-bit-arm-cortex-mcus/stm32-wireless-mcus/stm32wb-series/stm32wbx5/stm3 2wb55ce.html

- https://www.st.com/resource/en/datasheet/stm32wb55ce.pdf

- https://www.st.com/resource/en/reference\_manual/dm00318631.pdf

- https://www.st.com/resource/en/programming\_manual/dm00046982.pdf

#### 10.2. Tools

- https://www.st.com/en/development-tools/stm32cubeide.html

- https://www.st.com/en/development-tools/stm32cubeprog.html

- https://www.st.com/en/development-tools/stm32cubemx.html

- https://www.st.com/en/development-tools/stm32cubemonrf.html

#### 10.3. WebSites

- http://www.midatronics.com

- https://www.st.com

## 10.4. Bibliography

- http://www.summitdata.com/blog/ble-overview/

- https://www.ncbi.nlm.nih.gov/pmc/articles/PMC6111614/

## 11. FCC

### 11.1. Label and Compliance Information (FCC)

A host product itself is required to comply with all other applicable FCC equipment authorization regulations, requirements, and equipment functions that are not associated with the transmitter module portion.

The SHARKY module have been labeled with its own FCC ID number. If the FCC ID is not visible when the module is installed inside another device, then the outside of the finished product into which the module is installed must display a label referring to the enclosed module. This exterior label can use wording as follows:

Contains Transmitter Module:

FCC ID: 2AVSQSHARKY

Or

Contains

FCC ID: 2AVSQSHARKY

The SHARKY module is compliant with the following standards:

FCC 15.247

The SHARKY module is compliant to Part 15 of the FCC Rules:

Operation is subject to the following two conditions:

- (1) this device may not cause harmful interference, and

- (2) this device must accept any interference received, including interference that may cause undesired operation.

This device has been designed and complies with the safety requirements for portable (<20cm) RF exposure in accordance with FCC rule part 2.1093 and KDB 447498 D01 as demonstrated in the RF exposure analysis. Installers must ensure that this device must not be co-located or operated in conjunction with any other antenna or transmitter except in accordance with FCC multi-transmitter product procedures.

Unauthorized repairs, changes or modifications could result in permanent damage to the equipment and void your warranty and your authority to operate this device under Part 15 of the FCC Rules.

NOTE: This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a

Document: SHARKY - User's Guide

2020/07/20

commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his own expense.

This device is intended only for OEM integrators under the following condition: - The transmitter module may not be co-located with any other transmitter or antenna. As long as the condition above is met, further transmitter test will not be required. However, the OEM integrator is still responsible for testing their end-product for any additional compliance requirements required with this module installed.

#### **IMPORTANT NOTE:**

In the event that this condition cannot be met (for example certain laptop configurations or colocation with another transmitter), then the FCC authorization is no longer considered valid and the FCC ID cannot be used on the final product. In these circumstances, the OEM integrator will be responsible for re-evaluating the end product (including the transmitter) and obtaining a separate FCC authorization.

#### Manual Information to the End User:

The OEM integrator has to be aware not to provide information to the end user regarding how to install or remove this RF module in the user's manual of the end product which integrates this module. The end user manual shall include all required regulatory information/warning as show in this manual.