# Self-Protected Low Side Driver with Temperature and Current Limit

# NCV8402, NCV8402A

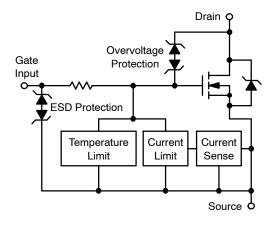

NCV8402/A is a three terminal protected Low–Side Smart Discrete device. The protection features include overcurrent, overtemperature, ESD and integrated Drain–to–Gate clamping for overvoltage protection. This device offers protection and is suitable for harsh automotive environments.

#### **Features**

- Short-Circuit Protection

- Thermal Shutdown with Automatic Restart

- Overvoltage Protection

- Integrated Clamp for Inductive Switching

- ESD Protection

- NCV8402AMNWT1G Wettable Flanks Product

- dV/dt Robustness

- Analog Drive Capability (Logic Level Input)

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q101 Qualified and PPAP Capable

- These Devices are Pb-Free and are RoHS Compliant

## **Typical Applications**

- Switch a Variety of Resistive, Inductive and Capacitive Loads

- Can Replace Electromechanical Relays and Discrete Circuits

- Automotive / Industrial

| V <sub>(BR)DSS</sub><br>(Clamped) | R <sub>DS(ON)</sub> TYP | I <sub>D</sub> MAX |

|-----------------------------------|-------------------------|--------------------|

| 42 V                              | 165 m $\Omega$ @ 10 V   | 2.0 A*             |

<sup>\*</sup>Max current limit value is dependent on input condition.

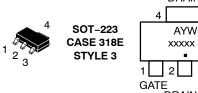

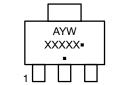

#### **MARKING DIAGRAMS**

DFN6 CASE 506AX

3

SOURCE

DFN6 (WF) CASE 506DK

A = Assembly Location

/ = Year

W or WW = Work Week xxxxx = V8402 or 8402A

■ = Pb-Free Package

(Note: Microdot may be in either location)

#### **DFN6 PACKAGE PIN DESCRIPTION**

|   | G | NC        | NC |

|---|---|-----------|----|

| ſ | 1 | 2         | 3  |

|   |   | 7<br>EPAI | )  |

|   | 6 | 5         | 4  |

|   | S | S         | S  |

| Pin# | Symbol | Description |

|------|--------|-------------|

| 1    | G      | Gate Input  |

| 2    | NC     | No Connect  |

| 3    | NC     | No Connect  |

| 4    | S*     | Source      |

| 5    | S*     | Source      |

| 6    | S*     | Source      |

| 7    | EPAD   | Drain       |

\*Pins 4, 5, 6 are internally shorted together. It is recommended to short these pins externally.

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 11 of this data sheet.

## **MAXIMUM RATINGS** ( $T_J = 25^{\circ}C$ unless otherwise noted)

|                                                                                                      | Rating                                         |                                                                                                  | Symbol                                                 | Value                | Unit   |

|------------------------------------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------|--------|

| Drain-to-Source Voltage Internally                                                                   | Clamped                                        |                                                                                                  | $V_{DSS}$                                              | 42                   | V      |

| Drain-to-Gate Voltage Internally C                                                                   | lamped                                         | $(R_G = 1.0 M\Omega)$                                                                            | $V_{DGR}$                                              | 42                   | V      |

| Gate-to-Source Voltage                                                                               |                                                |                                                                                                  | $V_{GS}$                                               | ±14                  | V      |

| Continuous Drain Current                                                                             |                                                |                                                                                                  | I <sub>D</sub>                                         | Internally L         | imited |

| Total Power Dissipation – SOT-223                                                                    | 3 Version                                      | @ T <sub>A</sub> = 25°C (Note 1)<br>@ T <sub>A</sub> = 25°C (Note 2)<br>@ T <sub>S</sub> = 25°C) | P <sub>D</sub>                                         | 1.1<br>1.74<br>8.9   | W      |

| Total Power Dissipation – DFN Vers                                                                   | sion                                           | @ T <sub>A</sub> = 25°C (Note 1)<br>@ T <sub>A</sub> = 25°C (Note 2)<br>@ T <sub>S</sub> = 25°C) | P <sub>D</sub>                                         | 0.76<br>1.78<br>8.9  | W      |

| Maximum Continuous Drain Current – SOT–223 Version<br>@ $T_A = 25^{\circ}C$<br>@ $T_A = 25^{\circ}C$ |                                                |                                                                                                  | Ι <sub>D</sub>                                         | 1.54<br>1.94<br>6.75 | Α      |

| Maximum Continuous Drain Curren                                                                      | t – DFN Version                                | @ T <sub>A</sub> = 25°C (Note 1)<br>@ T <sub>A</sub> = 25°C (Note 2)<br>@ T <sub>S</sub> = 25°C) | Ι <sub>D</sub>                                         | 1.28<br>1.97<br>6.75 | Α      |

| Thermal Resistance                                                                                   | SOT223 Junction-to-                            | Ambient Steady State (Note 1) -Ambient Steady State (Note 2) -Soldering Point Steady State       | $egin{array}{l} R_{	hetaJA} \ R_{	hetaJS} \end{array}$ | 114<br>72<br>14      | °C/W   |

|                                                                                                      | DFN Junction-to-                               | Ambient Steady State (Note 1) -Ambient Steady State (Note 2) -Soldering Point Steady State       | $egin{array}{l} R_{	hetaJA} \ R_{	hetaJS} \end{array}$ | 163<br>70<br>14      |        |

| Single Pulse Drain-to-Source Avalar ( $V_{DD}$ = 32 V, $V_{G}$ = 5.0 V, $I_{PK}$ = 1.0 A             |                                                |                                                                                                  | E <sub>AS</sub>                                        | 150                  | mJ     |

| Load Dump Voltage                                                                                    | $(V_{GS} = 0 \text{ and } 10 \text{ V}, R_I =$ | 2.0 Ω, $R_L = 9.0 Ω$ , $t_d = 400 ms$ )                                                          | $V_{LD}$                                               | 55                   | V      |

| Operating Junction Temperature                                                                       |                                                |                                                                                                  | TJ                                                     | -40 to 150           | °C     |

| Storage Temperature                                                                                  |                                                |                                                                                                  | T <sub>stg</sub>                                       | -55 to 150           | °C     |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Surface-mounted onto min pad FR4 PCB, (2 oz. Cu, 0.06" thick).

2. Surface-mounted onto 2" sq. FR4 board (1" sq., 1 oz. Cu, 0.06" thick).

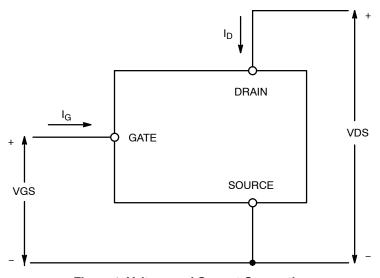

Figure 1. Voltage and Current Convention

## $\textbf{ELECTRICAL CHARACTERISTICS} \ (T_J = 25^{\circ}C \ unless \ otherwise \ noted)$

| Parameter                                                      | Test Condition                                                                          | Symbol                              | Min | Тур  | Max | Unit    |

|----------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------|-----|------|-----|---------|

| OFF CHARACTERISTICS                                            | •                                                                                       |                                     |     |      |     |         |

| Drain-to-Source Breakdown Voltage                              | $V_{GS} = 0 \text{ V}, I_D = 10 \text{ mA}, T_J = 25^{\circ}\text{C}$                   | V <sub>(BR)DSS</sub>                | 42  | 46   | 55  | V       |

| (Note 3)                                                       | V <sub>GS</sub> = 0 V, I <sub>D</sub> = 10 mA, T <sub>J</sub> = 150°C<br>(Note 5)       |                                     | 40  | 45   | 55  |         |

| Zero Gate Voltage Drain Current                                | $V_{GS} = 0 \text{ V}, V_{DS} = 32 \text{ V}, T_{J} = 25^{\circ}\text{C}$               | I <sub>DSS</sub>                    |     | 0.25 | 4.0 | μΑ      |

| Zero Gate Voltage Drain Current                                | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 32 V, T <sub>J</sub> = 150°C<br>(Note 5)       | I <sub>DSS</sub>                    |     | 1.1  | 20  | μΑ      |

| Gate Input Current                                             | $V_{DS} = 0 \text{ V}, V_{GS} = 5.0 \text{ V}$                                          | I <sub>GSSF</sub>                   |     | 50   | 100 | μΑ      |

| ON CHARACTERISTICS (Note 3)                                    |                                                                                         |                                     |     |      |     |         |

| Gate Threshold Voltage                                         | $V_{GS} = V_{DS}, I_{D} = 150 \mu A$                                                    | V <sub>GS(th)</sub>                 | 1.3 | 1.8  | 2.2 | V       |

| Gate Threshold Temperature Coefficient                         |                                                                                         | V <sub>GS(th)</sub> /T <sub>J</sub> |     | 4.0  |     | -mV/°C  |

| Static Drain-to-Source On-Resistance                           | $V_{GS} = 10 \text{ V}, I_D = 1.7 \text{ A}, T_J = 25^{\circ}\text{C}$                  | R <sub>DS(on)</sub>                 |     | 165  | 200 | mΩ      |

|                                                                | V <sub>GS</sub> = 10 V, I <sub>D</sub> = 1.7 A, T <sub>J</sub> = 150°C<br>(Note 5)      |                                     |     | 305  | 400 |         |

|                                                                | V <sub>GS</sub> = 5.0 V, I <sub>D</sub> = 1.7 A, T <sub>J</sub> = 25°C                  |                                     |     | 195  | 230 |         |

|                                                                | V <sub>GS</sub> = 5.0 V, I <sub>D</sub> = 1.7 A, T <sub>J</sub> = 150°C<br>(Note 5)     |                                     |     | 360  | 460 |         |

|                                                                | V <sub>GS</sub> = 5.0 V, I <sub>D</sub> = 0.5 A, T <sub>J</sub> = 25°C                  |                                     |     | 190  | 230 |         |

|                                                                | V <sub>GS</sub> = 5.0 V, I <sub>D</sub> = 0.5 A, T <sub>J</sub> = 150°C (Note 5)        |                                     |     | 350  | 460 |         |

| Source-Drain Forward On Voltage                                | V <sub>GS</sub> = 0 V, I <sub>S</sub> = 7.0 A                                           | $V_{SD}$                            |     | 1.0  |     | V       |

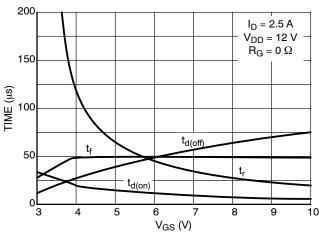

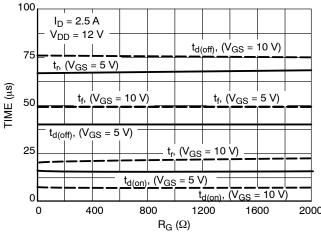

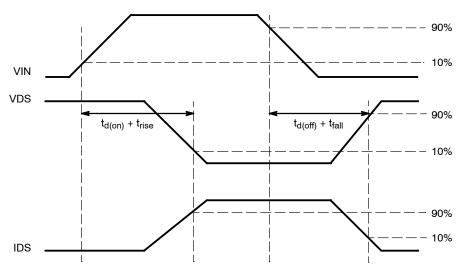

| SWITCHING CHARACTERISTICS (Note                                | 5)                                                                                      |                                     | •   |      |     |         |

| Turn-On Time (10% V <sub>IN</sub> to 90% I <sub>D</sub> )      |                                                                                         | t <sub>on</sub>                     |     | 25   | 30  | μs      |

| Turn-Off Time (90% V <sub>IN</sub> to 10% I <sub>D</sub> )     |                                                                                         | t <sub>off</sub>                    |     | 120  | 200 | μs      |

| Turn-On Rise Time (10% I <sub>D</sub> to 90% I <sub>D</sub> )  | V <sub>GS</sub> = 10 V, V <sub>DD</sub> = 12 V,                                         | t <sub>rise</sub>                   |     | 20   | 25  | μs      |

| Turn-Off Fall Time (90% I <sub>D</sub> to 10% I <sub>D</sub> ) | $I_D = 2.5 \text{ A}, R_L = 4.7 \Omega$                                                 | t <sub>fall</sub>                   |     | 50   | 70  | μs      |

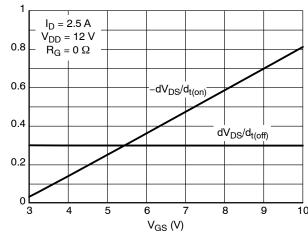

| Slew-Rate ON (70% to 50% V <sub>DD</sub> )                     |                                                                                         | -dV <sub>DS</sub> /dt <sub>ON</sub> |     | 0.8  | 1.2 | V/μs    |

| Slew-Rate OFF (50% to 70% V <sub>DD</sub> )                    |                                                                                         | dV <sub>DS</sub> /dt <sub>OFF</sub> |     | 0.3  | 0.5 | V/μs    |

| SELF PROTECTION CHARACTERISTIC                                 | S (T <sub>J</sub> = 25°C unless otherwise noted) (                                      | Note 4)                             |     |      |     |         |

| Current Limit                                                  | V <sub>DS</sub> = 10 V, V <sub>GS</sub> = 5.0 V, T <sub>J</sub> = 25°C<br>(Note 6)      | I <sub>LIM</sub>                    | 3.7 | 4.3  | 5.0 | А       |

|                                                                | V <sub>DS</sub> = 10 V, V <sub>GS</sub> = 5.0 V, T <sub>J</sub> = 150°C<br>(Notes 5, 6) |                                     | 2.3 | 3.0  | 3.7 |         |

|                                                                | V <sub>DS</sub> = 10 V, V <sub>GS</sub> = 10 V, T <sub>J</sub> = 25°C<br>(Note 6)       |                                     | 4.2 | 4.8  | 5.4 |         |

|                                                                | V <sub>DS</sub> = 10 V, V <sub>GS</sub> = 10 V, T <sub>J</sub> = 150°C<br>(Notes 5, 6)  |                                     | 2.7 | 3.6  | 4.5 |         |

| Temperature Limit (Turn-off)                                   | V <sub>GS</sub> = 5.0 V (Notes 5, 6)                                                    | T <sub>LIM(off)</sub>               | 150 | 175  | 200 | °C      |

| Thermal Hysteresis                                             | V <sub>GS</sub> = 5.0 V                                                                 | $\Delta T_{LIM(on)}$                |     | 15   |     |         |

| Temperature Limit (Turn-off)                                   | V <sub>GS</sub> = 10 V (Notes 5, 6)                                                     | T <sub>LIM(off)</sub>               | 150 | 165  | 185 |         |

| Thermal Hysteresis                                             | V <sub>GS</sub> = 10 V                                                                  | $\Delta T_{LIM(on)}$                |     | 15   |     | <u></u> |

| GATE INPUT CHARACTERISTICS (Note                               | = 5)                                                                                    |                                     |     |      |     |         |

| Device ON Gate Input Current                                   | V <sub>GS</sub> = 5 V I <sub>D</sub> = 1.0 A                                            | I <sub>GON</sub>                    |     | 50   |     | μΑ      |

|                                                                | V <sub>GS</sub> = 10 V I <sub>D</sub> = 1.0 A                                           |                                     |     | 400  |     | 1       |

- Pulse Test: Pulse Width ≤300 µs, Duty Cycle ≤ 2%.

Fault conditions are viewed as beyond the normal operating range of the part.

Not subject to production testing.

Refer to Application Note AND8202/D for dependence of protection features on gate voltage.

#### **ELECTRICAL CHARACTERISTICS** (T<sub>.J</sub> = 25°C unless otherwise noted)

| Parameter                              | Test Condition Symbol                          |                  | Min  | Тур  | Max | Unit |

|----------------------------------------|------------------------------------------------|------------------|------|------|-----|------|

| GATE INPUT CHARACTERISTICS (Note       | 5)                                             | -                |      |      |     |      |

| Current Limit Gate Input Current       | $V_{GS} = 5 \text{ V}, V_{DS} = 10 \text{ V}$  | I <sub>GCL</sub> |      | 0.05 |     | mA   |

|                                        | V <sub>GS</sub> = 10 V, V <sub>DS</sub> = 10 V | 7                |      | 0.4  |     |      |

| Thermal Limit Fault Gate Input Current | V <sub>GS</sub> = 5 V, V <sub>DS</sub> = 10 V  | I <sub>GTL</sub> |      | 0.15 |     | mA   |

|                                        | V <sub>GS</sub> = 10 V, V <sub>DS</sub> = 10 V | 7                |      | 0.7  |     |      |

| ESD ELECTRICAL CHARACTERISTICS         | (T <sub>J</sub> = 25°C unless otherwise noted) | (Note 5)         |      |      |     |      |

| Electro-Static Discharge Capability    | Human Body Model (HBM)                         | ESD              | 4000 |      |     | V    |

|                                        | Machine Model (MM)                             |                  | 400  |      |     | 1    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

- Pulse Test: Pulse Width ≤[300 μs, Duty Cycle ≤ 2%.

Fault conditions are viewed as beyond the normal operating range of the part.

- 5. Not subject to production testing.6. Refer to Application Note AND8202/D for dependence of protection features on gate voltage.

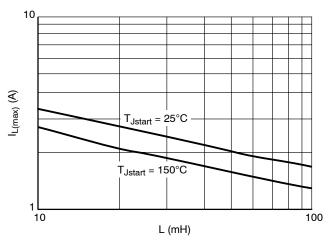

#### **TYPICAL PERFORMANCE CURVES**

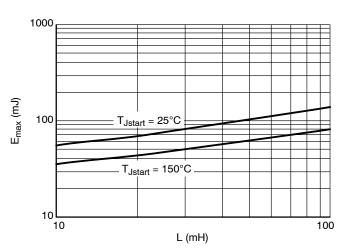

Figure 2. Single Pulse Maximum Switch-off Current vs. Load Inductance

Figure 3. Single Pulse Maximum Switching Energy vs. Load Inductance

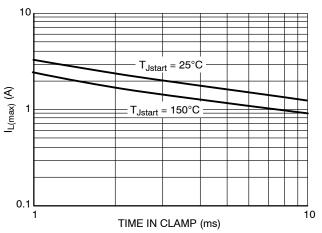

Figure 4. Single Pulse Maximum Inductive Switch-off Current vs. Time in Clamp

Figure 5. Single Pulse Maximum Inductive Switching Energy vs. Time in Clamp

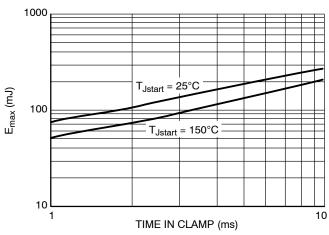

Figure 6. On-state Output Characteristics

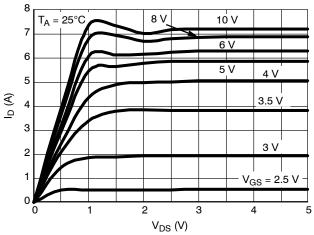

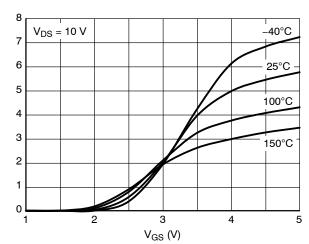

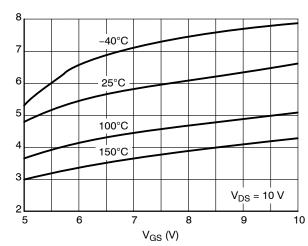

Figure 7. Transfer Characteristics

I<sub>D</sub> (A)

#### **TYPICAL PERFORMANCE CURVES**

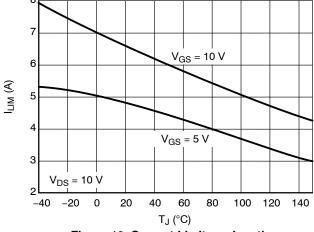

I⊔M (A)

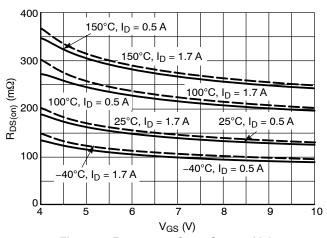

Figure 8.  $R_{DS(on)}$  vs. Gate-Source Voltage

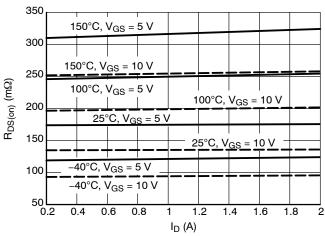

Figure 9. R<sub>DS(on)</sub> vs. Drain Current

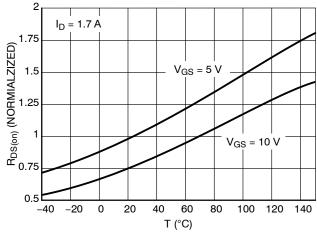

Figure 10. Normalized R<sub>DS(on)</sub> vs. Temperature

Figure 11. Current Limit vs. Gate-Source Voltage

Figure 12. Current Limit vs. Junction Temperature

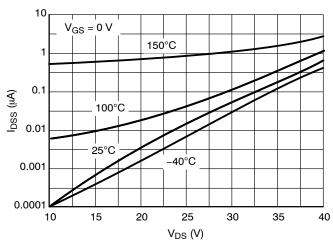

Figure 13. Drain-to-Source Leakage Current

#### **TYPICAL PERFORMANCE CURVES**

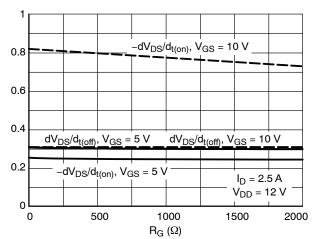

DRAIN-SOURCE VOLTAGE SLOPE (V/µs)

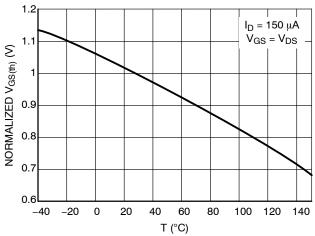

Figure 14. Normalized Threshold Voltage vs. Temperature

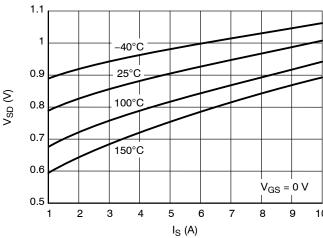

Figure 15. Source-Drain Diode Forward Characteristics

Figure 16. Resistive Load Switching Time vs.

Gate-Source Voltage

Figure 17. Resistive Load Switching

Drain-Source Voltage Slope vs. Gate-Source

Voltage

Figure 18. Resistive Load Switching Time vs.

Gate Resistance

Figure 19. Drain-Source Voltage Slope during Turn On and Turn Off vs. Gate Resistance

DRAIN-SOURCE VOLTAGE SLOPE (V/μs)

#### **TYPICAL PERFORMANCE CURVES**

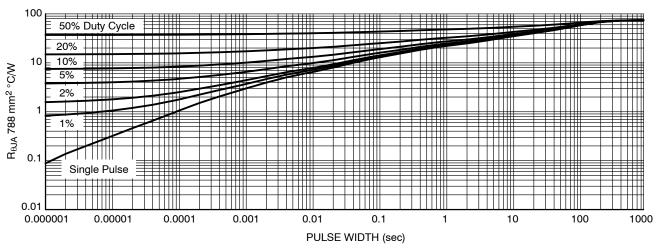

Figure 20. Transient Thermal Resistance - SOT-223 Package

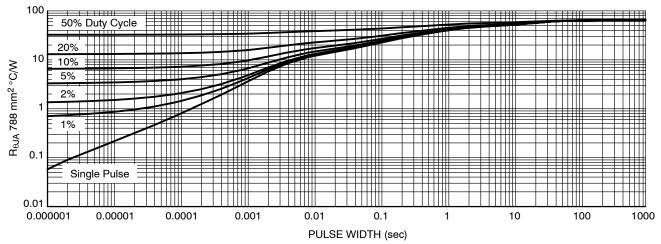

Figure 21. Transient Thermal Resistance - DFN Package

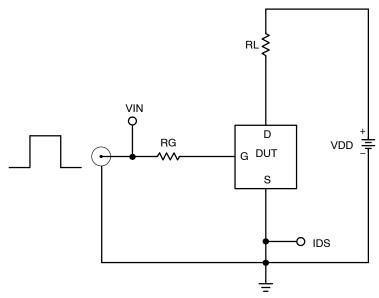

## **TEST CIRCUITS AND WAVEFORMS**

Figure 22. Resistive Load Switching Test Circuit

Figure 23. Resistive Load Switching Waveforms

## **TEST CIRCUITS AND WAVEFORMS**

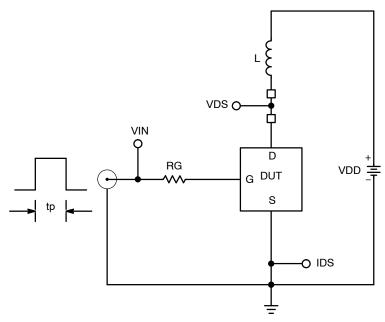

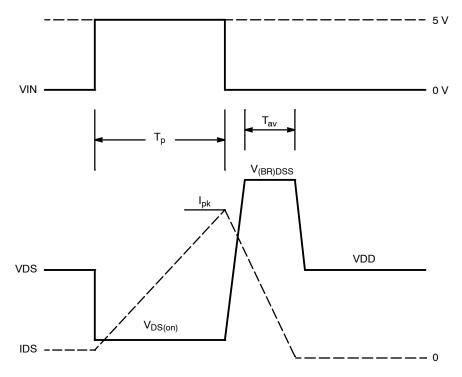

Figure 24. Inductive Load Switching Test Circuit

Figure 25. Inductive Load Switching Waveforms

#### **ORDERING INFORMATION**

| Device*        | Package                           | Shipping <sup>†</sup> |

|----------------|-----------------------------------|-----------------------|

| NCV8402STT1G   | SOT-223                           | 1000 / Tape & Reel    |

| NCV8402ASTT1G  | (Pb-Free)                         |                       |

| NCV8402STT3G   | SOT-223                           | 4000 / Tape & Reel    |

| NCV8402ASTT3G  | (Pb-Free)                         |                       |

| NCV8402AMNT2G  | DFN6<br>(Pb-Free)                 | 2000 / Tape & Reel    |

| NCV8402AMNWT1G | DFN6<br>(Pb-Free, Wettable Flank) | 3000 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

\*NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q101 Qualified and PPAP

Capable.

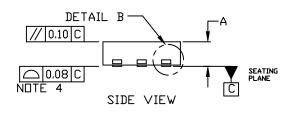

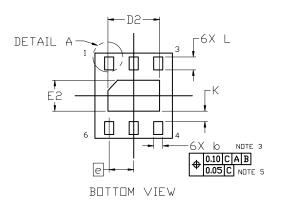

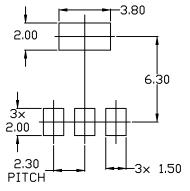

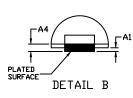

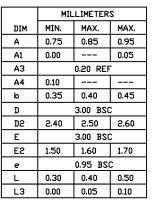

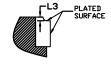

#### PACKAGE DIMENSIONS

#### DFN6 3.0x3.3, 0.95P CASE 506AX

**ISSUE A**

**DATE 22 SEP 2020**

#### NDTES:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 2009.

- CONTROLLING DIMENSION: MILLIMETERS

DIMENSION & APPLIES TO PLATED TERMINALS AND IS

MEASURED BETWEEN 0.15 AND 0.30MM FROM THE

- TERMINAL TIP.

COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

- POSITIONAL TOLERANCE APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

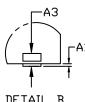

DETAIL B

DETAIL A

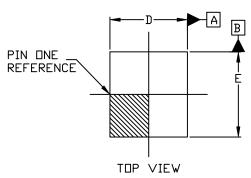

| 'L | LEIGHTIN | INTIMALS:   |          |      |  |  |

|----|----------|-------------|----------|------|--|--|

|    |          | MILLIMETERS |          |      |  |  |

|    | DIM      | MIN.        | N□M.     | MAX. |  |  |

|    | Α        | 0.80        | 0.90     | 1.00 |  |  |

|    | A1       | 0.00        |          | 0.05 |  |  |

|    | b        | 0.30        | 0.35     | 0.40 |  |  |

|    | D        | 2.90        | 3.00     | 3.10 |  |  |

|    | D2       | 1.90        | 2.00     | 2.10 |  |  |

|    | E        | 3,20        | 3,30     | 3.40 |  |  |

|    | E2       | 1.10        | 1.20     | 1.30 |  |  |

|    | е        | 1           | 0.95 BSC | ,    |  |  |

|    | K        | 0.40 REF    |          |      |  |  |

|    | L        | 0.40        | 0.50     | 0.60 |  |  |

|    | L1       | 0.00        | -        | 0.15 |  |  |

RECOMMENDED MOUNTING FOOTPRINT

## **GENERIC MARKING DIAGRAM\***

XXXXX XXXXX AYWW= XXXX = Specific Device Code

= Assembly Location

= Year = Work Week WW

= Pb-Free Package

(Note: Microdot may be in either location)

For additional information on our Pb-Free strategy and soldering details, please download the IIN Semiconductor Soldering and Mounting Techniques Reference Manual, SILDERRM/D.

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "■", may or may not be present. Some products may not follow the Generic Marking.

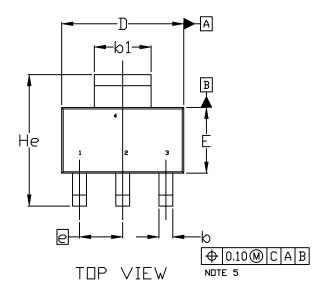

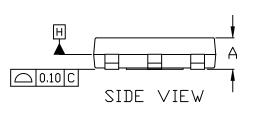

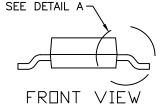

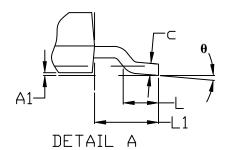

**SOT-223 (TO-261)** CASE 318E-04 ISSUE R

**DATE 02 OCT 2018**

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- 2. CONTROLLING DIMENSION: MILLIMETERS

- 3. DIMENSIONS D & E DO NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.200MM PER SIDE.

- 4. DATUMS A AND B ARE DETERMINED AT DATUM H.

- 5. ALLIS DEFINED AS THE VERTICAL DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT OF THE PACKAGE BODY.

- 6. POSITIONAL TOLERANCE APPLIES TO DIMENSIONS 6 AND 61.

|     | MILLIMETERS |          |      |  |

|-----|-------------|----------|------|--|

| DIM | MIN.        | N□M.     | MAX. |  |

| Α   | 1.50        | 1.63     | 1.75 |  |

| A1  | 0.02        | 0.06     | 0.10 |  |

| b   | 0.60        | 0.75     | 0.89 |  |

| b1  | 2.90        | 3.06     | 3.20 |  |

| C   | 0.24        | 0.29     | 0.35 |  |

| D   | 6.30        | 6.50     | 6.70 |  |

| E   | 3.30        | 3.50     | 3.70 |  |

| е   |             | 2,30 BSC | ,    |  |

| L   | 0.20        |          |      |  |

| L1  | 1.50        | 1.75     | 2.00 |  |

| He  | 6.70        | 7.00     | 7.30 |  |

| θ   | 0°          |          | 10°  |  |

RECOMMENDED MOUNTING FOOTPRINT

| DOCUMENT N | IUMBER:  | 98ASB42680B      | Electronic versions are uncontrolled except when accessed directly from the Document Reposi<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------|----------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCF      | RIPTION: | SOT-223 (TO-261) |                                                                                                                                                                                | PAGE 1 OF 2 |  |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

#### SOT-223 (TO-261) CASE 318E-04 ISSUE R

**DATE 02 OCT 2018**

| STYLE 1:<br>PIN 1. BASE<br>2. COLLECTOR<br>3. EMITTER<br>4. COLLECTOR | STYLE 2:<br>PIN 1. ANODE<br>2. CATHODE<br>3. NC<br>4. CATHODE        | STYLE 3:<br>PIN 1. GATE<br>2. DRAIN<br>3. SOURCE<br>4. DRAIN           | STYLE 4:<br>PIN 1. SOURCE<br>2. DRAIN<br>3. GATE<br>4. DRAIN   | STYLE 5:<br>PIN 1. DRAIN<br>2. GATE<br>3. SOURCE<br>4. GATE    |

|-----------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------|

| STYLE 6:<br>PIN 1. RETURN<br>2. INPUT<br>3. OUTPUT<br>4. INPUT        | STYLE 7:<br>PIN 1. ANODE 1<br>2. CATHODE<br>3. ANODE 2<br>4. CATHODE | STYLE 8:<br>CANCELLED                                                  | STYLE 9:<br>PIN 1. INPUT<br>2. GROUND<br>3. LOGIC<br>4. GROUND | STYLE 10:<br>PIN 1. CATHODE<br>2. ANODE<br>3. GATE<br>4. ANODE |

| STYLE 11:<br>PIN 1. MT 1<br>2. MT 2<br>3. GATE<br>4. MT 2             | STYLE 12:<br>PIN 1. INPUT<br>2. OUTPUT<br>3. NC<br>4. OUTPUT         | STYLE 13:<br>PIN 1. GATE<br>2. COLLECTOR<br>3. EMITTER<br>4. COLLECTOR |                                                                |                                                                |

### **GENERIC MARKING DIAGRAM\***

= Assembly Location Α

= Year

W = Work Week XXXXX = Specific Device Code

= Pb-Free Package

(Note: Microdot may be in either location) \*This information is generic. Please refer to device data sheet for actual part marking. Pb–Free indicator, "G" or microdot "•", may or may be present. Some products may

not follow the Generic Marking.

| DOCUMENT NUMBER: | 98ASB42680B      | Electronic versions are uncontrolled except when accessed directly from the Document Reposi<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | SOT-223 (TO-261) |                                                                                                                                                                                | PAGE 2 OF 2 |

ON Semiconductor and at a trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

PIN ONE

REFERENCE

2X 0.10 C

2X 0.10 C

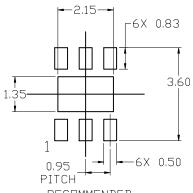

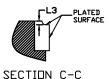

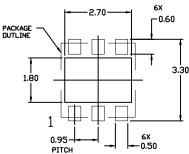

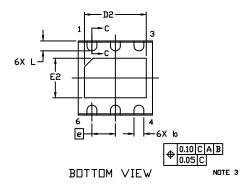

#### DFNW6 3x3, 0.95P CASE 506DK **ISSUE A**

В

Ė

**DATE 07 MAY 2021**

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- CONTROLLING DIMENSION: MILLIMETERS

- DIMENSION 6 APPLIES TO THE PLATED TERMINALS AND IS MEASURED BETWEEN 0.10 AND 0.20mm FROM THE TERMINAL TIP.

- PROFILE APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

#### RECOMMENDED MOUNTING FOOTPRINT

For additional information on our Pb-Free strategy and soldering details, please download the IN Semiconductor Soldering and Mounting Techniques Reference Manual, SDLDERRM/D.

### TOP VIEW DETAIL B // 0.10 C SEATING PLANE △ 0.05 C NOTE 4 C SIDE VIEW

#### **GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code = Assembly Location Α

= Wafer Lot 1 Υ = Year W = Work Week = Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "■", may or may not be present. Some products may not follow the Generic Marking.

Electronic versions are uncontrolled except when accessed directly from the Document Repository. **DOCUMENT NUMBER:** 98AON12549G Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. **DESCRIPTION: DFNW6 3X3, 0.95P PAGE 1 OF 1**

ON Semiconductor and un are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the

onsemi, Onsemi, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.or

#### ADDITIONAL INFORMATION

**TECHNICAL PUBLICATIONS:**

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at www.onsemi.com/support/sales