# Microsemi.

## **IdealBridge™ Dual MOSFET-based Bridge Rectifier**

**PRELIMINARY**

#### Description

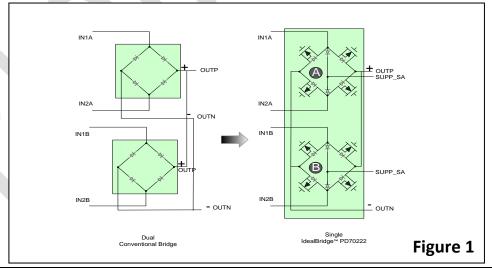

PD70222 is a dual pack of MOSFET-based full-bridge rectifiers. It contains low-R<sub>DS</sub> 0.15Ω N-channel MOSFETs for much higher overall efficiency and higher output power, particularly when used in Powered Devices for Power over Ethernet (PoE) applications. The entire drive circuitry for driving the MOSFETs is onchip, including a charge pump for driving the high-side N-channel MOSFETs. The total forward drop (bridge offset) introduced by the IdealBridge™ rectifier is only 180mV at 0.6A, compared to a standard bridge rectifier that typically presents 2000mV of forward drop.

PD70222 IdealBridge™ can support over 1A current, making it the ideal choice not only for modern energy-saving 2-pair applications compliant with IEEE802.3af and IEEE802.3at (Type 1 and Type 2), but also 4-pair Powered Devices such as for UPOE (51W) and POH (Power over HDBase-T, 73W).

In addition, PD70222 is capable of helping to identify at the physical layer itself whether a 2-pair PSE or a 4-pair PSE is providing power over the cable. It does that by sensing the voltage on the line (un-rectified) side of the pairs.

#### **Features**

- Active circuit with low forward-drop to replace dissipative passive diode bridges

- ♦ Self-contained drive circuitry for MOSFETs

- Designed to support IEEE802.3af/at, UPOE and Power over HDBase-T (PoH)

- Integrated 0.15Ω N-Channel MOSFETs for 0.3Ω total path resistance

- "Power present" indicator signals for identifying 4-pair bridge power

- ♦ Low leakage, < 12μA during detection

- ♦ Wide operating voltage range up to 57V

- ◆ -40°C to +85°C ambient

- ♦ Available in 40 pin package

- ♦ RoHS Compliant

#### **Applications**

- Power over Ethernet (all IEEE compliant 2-pair modes)

- Proprietary 4-pair standards, UPOE (Universal PoE) and POH

**PRELIMINARY**

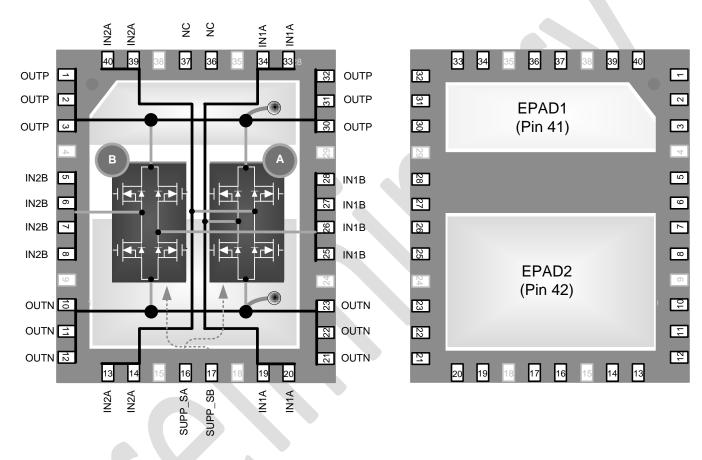

## **Pin Configuration and Pinout**

## **PD70222**

**TOP VIEW** 6×8 MLPQ – 40L

BOTTOM VIEW 6×8 MLPQ – 40L

**Figure 2: Internal Construction and Pinout**

## **Ordering Information**

| Ambient     | Туре                       | Part Marking | Tape and Reel | Package            |

|-------------|----------------------------|--------------|---------------|--------------------|

| Temperature |                            |              |               |                    |

| -40 to 85°C | RoHS compliant,<br>Pb-free | PD70222      | PD70222ILQ-TR | MLP-Quad (40 lead) |

**PRELIMINARY**

## **Pin Description**

| Pin Number     | Pin Designator | Description                                                      |  |

|----------------|----------------|------------------------------------------------------------------|--|

| 1, 2, 3        | OUTP           | Rectified positive (upper) rail shared by both bridges           |  |

| 4              | N.A.           | Not applicable (pin not present)                                 |  |

| 5, 6, 7, 8     | IN2B           | Input "2" of bridge rectifier number B                           |  |

| 9              | N.A.           | Not applicable (pin not present)                                 |  |

| 10, 11, 12     | OUTN           | Rectified negative (lower) rail shared by both bridges           |  |

| 13, 14         | IN2A           | Input "2" of bridge rectifier number A                           |  |

| 15             | N.A.           | Not applicable (pin not present)                                 |  |

| 16             | SUPP_SA        | Input power supply detect pin for bride rectifier number A. Goes |  |

|                |                | high when pairs connected to this bridge are powered by the      |  |

|                |                | PSE                                                              |  |

| 17             | SUPP_SB        | Input power supply detect pin for bride rectifier number B. Goes |  |

|                |                | high when pairs connected to this bridge are powered by the      |  |

|                |                | PSE                                                              |  |

| 18             | N.A.           | Not applicable (pin not present)                                 |  |

| 19, 20         | IN1A           | Input "1" of bridge rectifier number A                           |  |

| 21, 22, 23     | OUTN           | Rectified negative (lower) rail shared by both bridges, same as  |  |

|                |                | Pins 10, 11 and 12                                               |  |

| 24             | N.A.           | Not applicable (pin not present)                                 |  |

| 25, 26, 27, 28 | IN1B           | Input "1" of bridge rectifier number B                           |  |

| 29             | N.A.           | Not applicable (pin not present)                                 |  |

| 30, 31, 32     | OUTP           | Rectified positive (upper) rail shared by both bridges. Same as  |  |

|                |                | Pins 1, 2 and 3                                                  |  |

| 33, 34         | IN1A           | Input "A" of bridge rectifier number 1. Same as Pins 19 and 20   |  |

| 35             | N.A.           | Not applicable (pin not present)                                 |  |

| 36, 37         | N.C            | Not connected; do not connect externally (leave floating)        |  |

| 38             | N.A.           | Not applicable (pin not present)                                 |  |

| 39, 40         | IN2A           | Input "2" of bridge rectifier number A. Same as Pins 13 and 14   |  |

| 41             | EPAD1          | Connect to OUTP on PCB                                           |  |

| 42             | EPAD2          | Connect to OUTN on PCB                                           |  |

**PRELIMINARY**

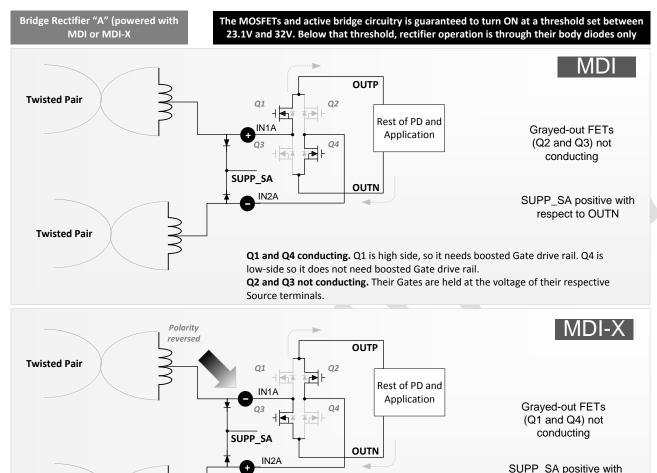

#### **PURPOSE OF CHARGE PUMP:**

**Twisted Pair**

Therefore, in both cases above, the FETs connected to OUTP (the "high-side" FETs) are the ones which require a boosted Gate drive rail so they can be turned ON. The on-chip charge pump provides the boosted Gate drive rail for the high-side FETs. The FETs connected to OUTN ("low-side" FETs) do not need a boosted drive rail to be turned ON.

Source terminals.

#### **PURPOSE AND USE OF SUPPLY PINS:**

Since the above twisted pair set is delivering power, in both cases above, SUPP\_SA is positive with respect to OUTN. But if these two twisted pairs were not connected to a PSE, SUPP\_SA would be low. Therefore, in the case of a standard 2-pair or 4-pair PDs with two bridge rectifiers (4-pairs), one connected to the data pairs, the other to the spare pairs, the presence of high voltage on SUPP\_SA and/or SUPP\_SB will indicate whether the data pairs or spare pairs, or both, are connected to PSEs. So SUPP\_SA and SUPP\_SB can be used to indicate 2-pair or 4-pair PoE operation.

side so it does not need boosted Gate drive rail.

Q2 and Q3 conducting. Q2 is high side, so it needs boosted Gate drive rail. Q3 is low-

Q1 and Q4 not conducting. Their Gates are held at the voltage of their respective

Figure 3: Principle of Operation

respect to OUTN

**PRELIMINARY**

## **Absolute Maximum Ratings**

Performance is not necessarily guaranteed over this entire range. These are maximum stress ratings only. Exceeding these ratings, even momentarily, can cause immediate damage, or negatively impact long-term operating reliability.

|                                                                          |                                | Min  | Max  | Units |

|--------------------------------------------------------------------------|--------------------------------|------|------|-------|

| IN1A, IN1B, IN2A, IN2B t                                                 | o OUTN                         | -0.3 | 72   | V     |

| IN1A to IN2A                                                             |                                | -0.3 | 72   | V     |

| IN1B to IN2B                                                             |                                | -0.3 | 72   | V     |

| IN1A, IN1B, IN2A, IN2B t                                                 | o OUTP                         | -72  |      | V     |

| IN1A, IN2A to IN1B                                                       |                                | -0.3 | 72   | V     |

| IN1A, IN2A to IN2B                                                       |                                | -0.3 | 72   | V     |

| OUTP to OUTN                                                             |                                | -0.3 | 72   | V     |

| OUTP to IN1A, IN1B, IN2                                                  | OUTP to IN1A, IN1B, IN2A, IN2B |      | 72   | V     |

| SUPP_SA, SUPP_SB to OUTN                                                 |                                | -0.3 | 72   | V     |

| I <sub>INA</sub> , I <sub>INB</sub> (currents through bridge A and/or B) |                                |      | TBD  | Α     |

| Junction Temperature                                                     | Junction Temperature           |      | 150  | °C    |

| Lead Soldering Temperature (40s, reflow)                                 |                                |      | 260  | °C    |

| Storage Temperature                                                      |                                | -65  | 150  | °C    |

| ESD rating                                                               | HBM                            |      | ±2   | kV    |

|                                                                          | MM                             |      | ±200 | V     |

|                                                                          | CDM                            |      | ±500 | V     |

Note: EPAD1 is connected by copper plane on PCB to OUTP, and EPAD2 is similarly connected to OUTN. OUTN is ground for IC.

## **Operating Ratings**

Performance is generally guaranteed over this range as further detailed below under Electrical Characteristics.

|                                  | Min | Max | Units |

|----------------------------------|-----|-----|-------|

| IN1A, IN1B to OUTN               | TBD | 57  | V     |

| IN2A, IN2B to OUTN               | TBD | 57  | V     |

| Junction Temperature             | -40 | 125 | °C    |

| Port Current (I <sub>INx</sub> ) | 0   | 1.5 | Α     |

Note: Corresponding Ambient Temperature is -40 to 85 °C

**PRELIMINARY**

## **Thermal Properties**

| Thermal Resistance | Min | Тур | Max | Units |

|--------------------|-----|-----|-----|-------|

| $\theta_{JA}$      |     | 31  |     | °C/W  |

| $\theta_{JL}$      |     | 2.5 |     | °C/W  |

| $\theta_{JC}$      |     | TBD |     | °C/W  |

**Note:** The  $\theta_{Jx}$  numbers assume no forced airflow. Junction Temperature is calculated using  $T_J = T_A + (P_D \times \theta_{JA})$ . In particular,  $\theta_{JA}$  is a function of the PCB construction. The stated number above is for a four-layer board in accordance with JESD-51 (JEDEC).

#### **Electrical Characteristics**

Unless otherwise specified under conditions, the Min and Max ratings stated below apply over the entire specified operating ratings of the device. Typ values stated are either by design or by production testing at 25°C ambient.

| Symbol               | Parameter                                            | Conditions                                                                                                         | Min  | Тур  | Max | Units    |

|----------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------|------|-----|----------|

| V <sub>INx</sub>     | Input Voltage for Bridge "x", where x is "A" or "B". |                                                                                                                    |      |      | 57  | <b>\</b> |

| IQ                   | Quiescent<br>Current (both<br>bridges<br>combined)   | $2.5V < V_{INx} < 10.1V$ , $500\mu$ load or $25k$ signature detection resistor connected. No load on SUPP_Sx pins. |      | 6    | 12  | μΑ       |

|                      | 1                                                    | 10.2V < V <sub>INx</sub> < 23V, 50mA load<br>between OUTP and OUTN. No<br>load on SUPP_Sx pins.                    |      |      | 80  | μΑ       |

|                      |                                                      | $V_{\text{INx}}$ = 55V. 1.5A load between OUTP and OUTN. 900kΩ load resistor on each SUPP_Sx pin.                  |      |      | 750 | μΑ       |

| V <sub>TURN_ON</sub> | Active turn-<br>on voltage of<br>FETs                |                                                                                                                    | 23.1 | 27.5 | 32  | V        |

| V <sub>HYS</sub>     | Turn-on<br>voltage<br>hysteresis                     |                                                                                                                    |      | TBD  |     | V        |

Copyright © 2013 Rev. 0.35, May 2013

**PRELIMINARY**

|                        | Alternate input voltage polarity                                |                                                                                       |                                          | 200        |            |              | ms |

|------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------|------------|------------|--------------|----|

| V <sub>OFFSET</sub>    | Bridge offset                                                   | V <sub>INx</sub> > 32V, two<br>FETs in series                                         | $I_{INx} = 0.6A$ $I_{INx} = 0.6A$        |            | 180<br>300 | TBD<br>TBD   | mV |

|                        |                                                                 | V <sub>INx</sub> < 32V, two body diodes in                                            | $I_{INx} = 1mA$ $I_{INx} = 5mA$          | 398<br>508 |            | 1190<br>1294 |    |

| R <sub>DS</sub>        | FET Drain to<br>Source                                          | series $I_D = 0.6A$ $I_D = 1A$                                                        | I <sub>INx</sub> = 40mA                  | 658        | TBD<br>TBD | 1116<br>TBD  | Ω  |

| I <sub>R</sub>         | Resistance Leakage Current (Reverse)                            |                                                                                       | $I_D = 1.5A$ $V_{OUTP} - V_{OUTN} = 57V$ |            | 0.15       | 40           | μΑ |

| V <sub>BFD</sub>       | Backfeed<br>Voltage                                             | Between input terminals with 100kΩ resistor across them and 57V between OUTP and OUTN |                                          |            |            | 2.7          | V  |

| I <sub>MAX_LOW</sub>   | Maximum Forward Current (per bridge) below V <sub>TURN ON</sub> | Polarity changeover > 20ms                                                            |                                          |            |            | 0.45         | A  |

| I <sub>MAX_HIGH</sub>  | Maximum Forward Current (per bridge) above V <sub>TURN ON</sub> |                                                                                       |                                          | 1.5        |            | TBD          | Α  |

| V <sub>SUPP_HIGH</sub> | Max voltage<br>on SUPP_SA<br>and SUPP_SB<br>pins                | V <sub>INx</sub> = 36V                                                                |                                          | 34         |            |              | V  |

| V <sub>SUPP_LOW</sub>  | Min voltage<br>on SUPP_SA<br>and SUPP_SB<br>pins                | V <sub>INx</sub> = TBDV                                                               |                                          |            |            | 26           | V  |

D2

X - depopulated pin

**PRELIMINARY**

E4

**E**3

E2

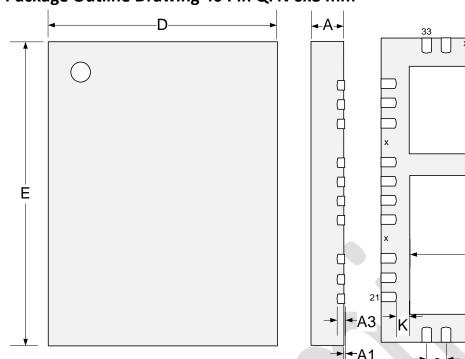

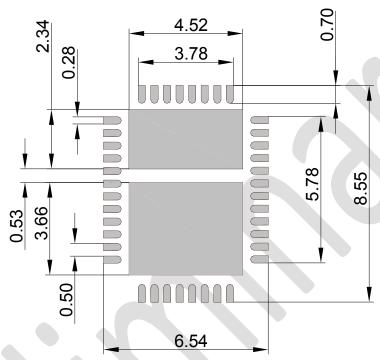

## Package Outline Drawing 40 Pin QFN 6x8 mm

|     | MILLIMETERS |      | Inc       | HES   |

|-----|-------------|------|-----------|-------|

| Dim | MIN         | MAX  | MIN       | MAX   |

| Α   | 0.80        | 1.00 | 0.031     | 0.039 |

| A1  | 0.00        | 0.05 | 0         | 0.002 |

| A3  | 0.20        | REF  | 0.008     | 8 REF |

| b   | 0.18        | 0.30 | 0.007     | 0.012 |

| D   | 6.00        | BSC  | 0.236 BSC |       |

| E   | 8.00 BSC    |      | 0.315 BSC |       |

| D2  | 4.35        | 4.6  | 0.171     | 0.181 |

| E2  | 6.35        | 6.6  | 0.250     | 0.260 |

| E3  | 3.5         | 3.75 | 0.138     | 0.148 |

| E4  | 2.2         | 2.4  | 0.087     | 0.094 |

| е   | 0.50 BSC    |      | 0.020     | O BSC |

| K   | 0.20        | -    | 0.008     | -     |

| L   | 0.37        | 0.57 | 0.014     | 0.022 |

#### Note:

- 1. Dimensions do not include protrusions; these shall not exceed 0.155mm (.006") on any side. Lead dimension shall not include solder coverage.

- 2. Dimensions are in millimeters, inches for reference only.

**PRELIMINARY**

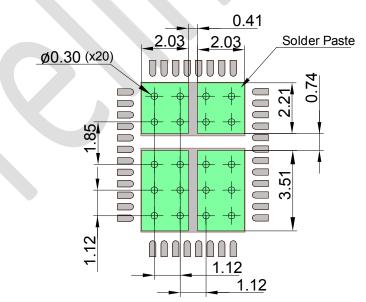

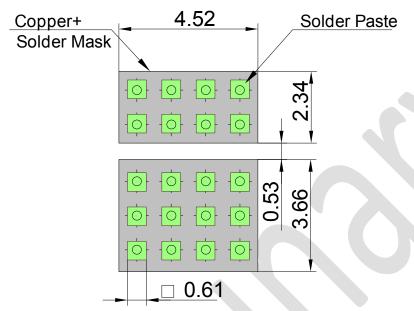

## **Recommended PCB layout**

Recommended PCB layout pattern for PD70222 is described in the following three figures.

Figure 4: PD70222 Top layer Copper Recommended PCB Layout (mm)

Figure 5: PD70222 Top layer Solder Paste and Vias Recommended PCB Layout for Thermal Pad Array (mm)

**PRELIMINARY**

Figure 6: PD70222 Bottom layer Copper and Solder Paste Recommended PCB Layout for Thermal Pad Array (mm)

**PRFLIMINARY**

The information contained in the document (unless it is publicly available on the Web without access restrictions) is PROPRIETARY AND CONFIDENTIAL information of Microsemi and cannot be copied, published, uploaded, posted, transmitted, distributed or disclosed or used without the express duly signed written consent of Microsemi. If the recipient of this document has entered into a disclosure agreement with Microsemi, then the terms of such Agreement will also apply. This document and the information contained herein may not be modified, by any person other than authorized personnel of Microsemi. No license under any patent, copyright, trade secret or other intellectual property right is granted to or conferred upon you by disclosure or delivery of the information, either expressly, by implication, inducement, estoppels or otherwise. Any license under such intellectual property rights must be approved by Microsemi in writing signed by an officer of Microsemi.

Microsemi reserves the right to change the configuration, functionality and performance of its products at anytime without any notice. This product has been subject to limited testing and should not be used in conjunction with life-support or other mission-critical equipment or applications. Microsemi assumes no liability whatsoever, and Microsemi disclaims any express or implied warranty, relating to sale and/or use of Microsemi products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Any performance specifications believed to be reliable but are not verified and customer or user must conduct and complete all performance and other testing of this product as well as any user or customers final application. User or customer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the customer's and user's responsibility to independently determine suitability of any Microsemi product and to test and verify the same. The information contained herein is provided "AS IS, WHERE IS" and with all faults, and the entire risk associated with such information is entirely with the User. Microsemi specifically disclaims any liability of any kind including for consequential, incidental and punitive damages as well as lost profit. The product is subject to other terms and conditions which can be located on the web at http://www.microsemi.com/legal/tnc.asp

#### **Revision History**

| Revision Level / Date | Para. Affected | Description                                           |

|-----------------------|----------------|-------------------------------------------------------|

| 0.2 / 4 Oct 2012      | -              | Initial Release – Preliminary version                 |

| 0.3 / 30 April 2013   |                | Adding package description and Recommended PCB layout |

| 0.35 / 8 May 2013     |                | Adding Package tollerances                            |

© 2013 Microsemi Corp. All rights reserved.

For support contact: sales\_AMSG@microsemi.com

Visit our web site at: www.microsemi.com Catalog Number: DS\_PD70222