### **FEATURES**

- Ideal Diode-OR and Inrush Current Control for **Redundant Supplies**

- Low Loss Replacement for Power Schottky Diodes

- Enables Safe Board Insertion into a Live Backplane

- 2.9V to 18V Operating Range

- Current Monitor Output

- Controls N-Channel MOSFETs

- Limits Peak Fault Current in  $\leq$  1us

- Adjustable Current Limit with Foldback

- Adjustable Start-Up and Current Limit Fault Delay

- 0.5us Ideal Diode Turn-On and Turn-Off Time

- Smooth Switchover without Oscillation

- Fault. Power Good and Diode Status Outputs

- LTC4236-1: Latch Off After Fault

- LTC4236-2: Automatic Retry After Fault

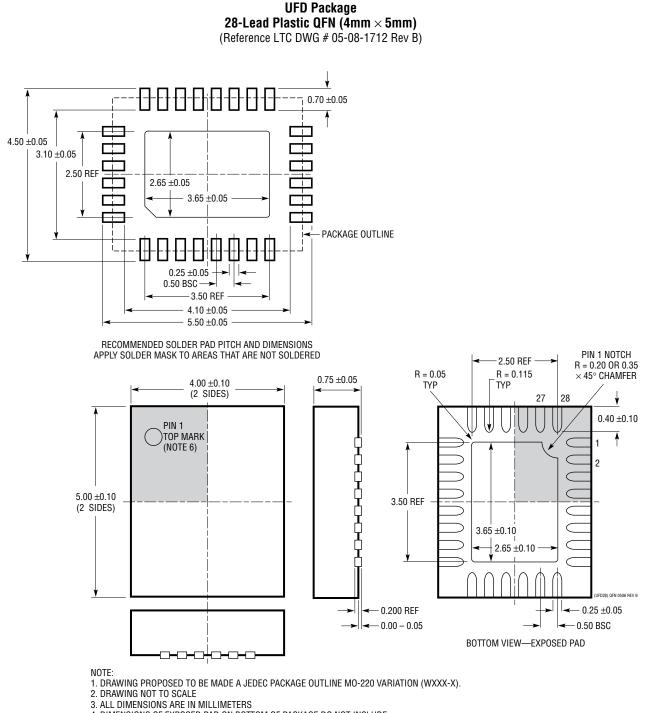

- 28-Pin 4mm x 5mm QFN Package

### **APPLICATIONS**

- **Redundant Power Supplies**

- High Availability Systems and Servers

- Telecom and Network Infrastructure

### Dual Ideal Diode-OR and Single Hot Swap Controller with Current Monitor DESCRIPTION

The LTC<sup>®</sup>4236 offers ideal diode-OR and Hot Swap functions for two power rails by controlling external N-channel MOSFETs. MOSFETs acting as ideal diodes replace two high power Schottky diodes and the associated heat sinks. saving power and board area. A Hot Swap control MOSFET allows a board to be safely inserted and removed from a live backplane by limiting inrush current. The supply output is also protected against short-circuit faults with a fast acting foldback current limit and electronic circuit breaker.

The LTC4236 regulates the forward voltage drop across the ideal diode MOSFETs to ensure smooth current transfer from one supply to the other without oscillation. The ideal diode MOSFETs turn on quickly to reduce the load voltage droop during supply switchover. If the input supply fails or is shorted, a fast turn-off minimizes reverse current transients.

A current sense amplifier translates the voltage across the sense resistor to a ground referenced signal. The LTC4236 provides adjustable start-up delay, turn-on/-off control, and reports fault and power good status for the supply.

LT, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents, including 7920013, 8022679.

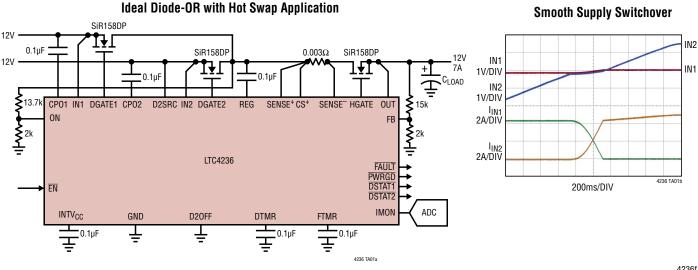

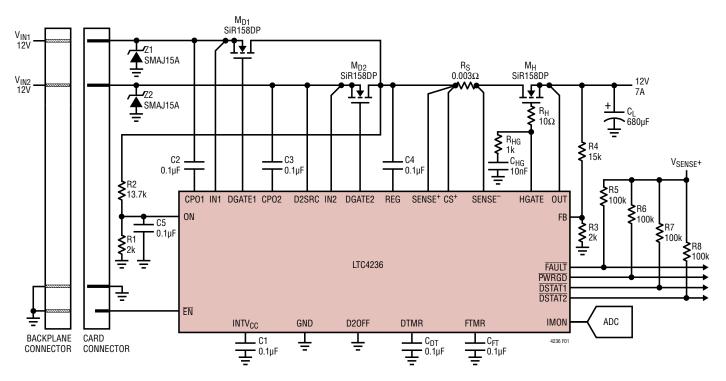

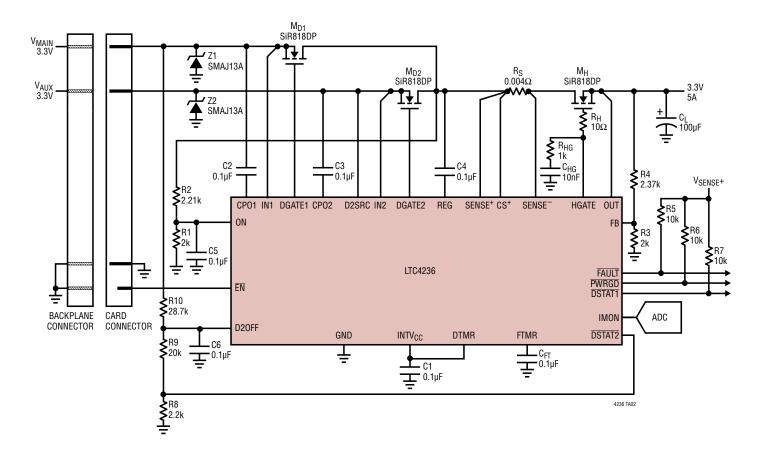

### TYPICAL APPLICATION

4236f

#### **ABSOLUTE MAXIMUM RATINGS** (Notes 1, 2)

#### Supply Voltages

| Supply Voltages                                                                |  |

|--------------------------------------------------------------------------------|--|

| IN1, IN2–0.3V to 24V                                                           |  |

| INTV <sub>CC</sub> –0.3V to 7V                                                 |  |

| REGSENSE <sup>+</sup> – 5V to SENSE <sup>+</sup> + 0.3V                        |  |

| Input Voltages                                                                 |  |

| ON, D20FF, EN0.3V to 24V                                                       |  |

| FTMR, DTMR0.3V to INTV <sub>CC</sub> + 0.3V                                    |  |

| FB                                                                             |  |

| SENSE <sup>+</sup> , SENSE <sup>-</sup> , CS <sup>+</sup> , D2SRC –0.3V to 24V |  |

| Output Voltages                                                                |  |

| IMON–0.3V to 7V                                                                |  |

| FAULT, PWRGD, DSTAT1, DSTAT20.3V to 24V                                        |  |

| CP01, CP02 (Notes 3, 4)0.3V to 35V                                             |  |

| DGATE1, DGATE2 (Notes 3, 4)0.3V to 35V                                         |  |

| HGATE (Note 5)0.3V to 35V                                                      |  |

| OUT                                                                            |  |

| Average Currents                                                               |  |

| FAULT, PWRGD, DSTAT1, DSTAT25mA                                                |  |

| INTV <sub>CC</sub> 10mA                                                        |  |

| Operating Ambient Temperature Range                                            |  |

| LTC4236C 0°C to 70°C                                                           |  |

| LTC4236I40°C to 85°C                                                           |  |

| Storage Temperature Range65°C to 150°C                                         |  |

|                                                                                |  |

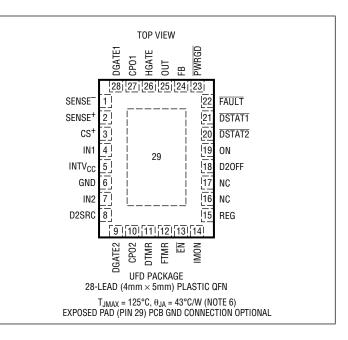

### PIN CONFIGURATION

### ORDER INFORMATION

| LEAD FREE FINISH  | TAPE AND REEL       | PART MARKING | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|-------------------|---------------------|--------------|---------------------------------|-------------------|

| LTC4236CUFD-1#PBF | LTC4236CUFD-1#TRPBF | 42361        | 28-Lead (4mm x 5mm) Plastic QFN | 0°C to 70°C       |

| LTC4236CUFD-2#PBF | LTC4236CUFD-2#TRPBF | 42362        | 28-Lead (4mm x 5mm) Plastic QFN | 0°C to 70°C       |

| LTC4236IUFD-1#PBF | LTC4236IUFD-1#TRPBF | 42361        | 28-Lead (4mm x 5mm) Plastic QFN | -40°C to 85°C     |

| LTC4236IUFD-2#PBF | LTC4236IUFD-2#TRPBF | 42362        | 28-Lead (4mm x 5mm) Plastic QFN | -40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

## **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>IN</sub> = 12V, unless otherwise noted.

| SYMBOL                                  | PARAMETER                                                                                | CONDITIONS                                                                                                                                                                                                                               |   | MIN         | ТҮР            | MAX            | UNITS          |

|-----------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------|----------------|----------------|----------------|

| Supplies                                |                                                                                          |                                                                                                                                                                                                                                          |   |             |                |                |                |

| V <sub>IN</sub>                         | Input Supply Range                                                                       |                                                                                                                                                                                                                                          |   | 2.9         |                | 18             | V              |

| I <sub>IN</sub>                         | Input Supply Current                                                                     |                                                                                                                                                                                                                                          |   |             | 2.7            | 4              | mA             |

| VINTVCC                                 | Internal Regulator Voltage                                                               | I = 0, -500µA                                                                                                                                                                                                                            | • | 4.5         | 5              | 5.5            | V              |

| VINTVCC(UVL)                            | Internal V <sub>CC</sub> Undervoltage Lockout                                            | INTV <sub>CC</sub> Rising                                                                                                                                                                                                                | • | 2.1         | 2.2            | 2.3            | V              |

| ΔV <sub>INTVCC(HYST)</sub>              | Internal V <sub>CC</sub> Undervoltage Lockout Hysteresis                                 |                                                                                                                                                                                                                                          |   | 30          | 60             | 90             | mV             |

| Ideal Diode Co                          | ntrol                                                                                    | l                                                                                                                                                                                                                                        |   |             |                |                |                |

| $\Delta V_{FWD(REG)}$                   | Forward Regulation Voltage<br>(V <sub>INn</sub> – V <sub>SENSE</sub> +)                  |                                                                                                                                                                                                                                          | • | 2           | 15             | 28             | mV             |

| $\Delta V_{DGATE}$                      | External N-Channel Gate Drive $(V_{DGATE1} - V_{IN1})$ and $(V_{DGATE2} - V_{D2SRC})$    | $ \begin{array}{l} {\sf IN} < {\sf 7V}, \ \Delta {\sf V}_{FWD} = 0.15{\sf V}; \ {\sf I} = 0, \ -1\mu {\sf A} \\ {\sf IN} = {\sf 7V} \ to \ 18{\sf V}, \ \Delta {\sf V}_{FWD} = 0.15{\sf V}; \ {\sf I} = 0, \ -1\mu {\sf A} \end{array} $ | • | 5<br>10     | 7<br>12        | 14<br>14       | V<br>V         |

| $\Delta V_{DGATE(ST)}$                  | Diode MOSFET On Detect Threshold $(V_{DGATE1} - V_{IN1})$ and $(V_{DGATE2} - V_{D2SRC})$ | $\overline{\text{DSTAT}}$ Pulls Low, $\Delta V_{FWD}$ = 50mV                                                                                                                                                                             | • | 0.3         | 0.7            | 1.1            | V              |

| I <sub>D2SRC</sub>                      | D2SRC Pin Current                                                                        | D2SRC = 0V                                                                                                                                                                                                                               | • |             | -90            | -130           | μA             |

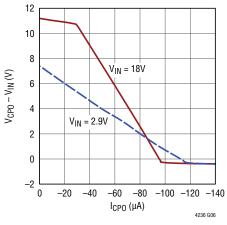

| I <sub>CPO(UP)</sub>                    | CPOn Pull-Up Current                                                                     | CPO = IN = D2SRC = 2.9V<br>CPO = IN = D2SRC = 18V                                                                                                                                                                                        | • | -60<br>-50  | -100<br>-90    | -130<br>-120   | μA<br>μA       |

| IDGATE(FPU)                             | DGATEn Fast Pull-Up Current                                                              | $\Delta V_{FWD} = 0.2V, \Delta V_{DGATE} = 0V, CPO = 17V$                                                                                                                                                                                |   |             | -1.5           |                | A              |

| IDGATE(FPD)                             | DGATEn Fast Pull-Down Current                                                            | $\Delta V_{FWD} = -0.2V, \Delta V_{DGATE} = 5V$                                                                                                                                                                                          |   |             | 1.5            |                | A              |

| IDGATE2(DN)                             | DGATE2 Off Pull-Down Current                                                             | D20FF = 2V, $\Delta V_{DGATE2}$ = 2.5V                                                                                                                                                                                                   |   | 50          | 100            | 200            | μA             |

| t <sub>ON(DGATE)</sub>                  | DGATEn Turn-On Delay                                                                     | $\Delta V_{FWD} = 0.2V$ , $C_{DGATE} = 10nF$                                                                                                                                                                                             |   |             | 0.25           | 0.5            | μs             |

| t <sub>OFF(DGATE)</sub>                 | DGATEn Turn-Off Delay                                                                    | $\Delta V_{FWD} = -0.2V, C_{DGATE} = 10nF$                                                                                                                                                                                               |   |             | 0.2            | 0.5            | μs             |

| t <sub>PLH(DGATE2)</sub>                | D2OFF Low to DGATE2 High                                                                 |                                                                                                                                                                                                                                          |   |             | 50             | 100            | μs             |

| Hot Swap Contr                          | ol                                                                                       |                                                                                                                                                                                                                                          |   |             |                |                |                |

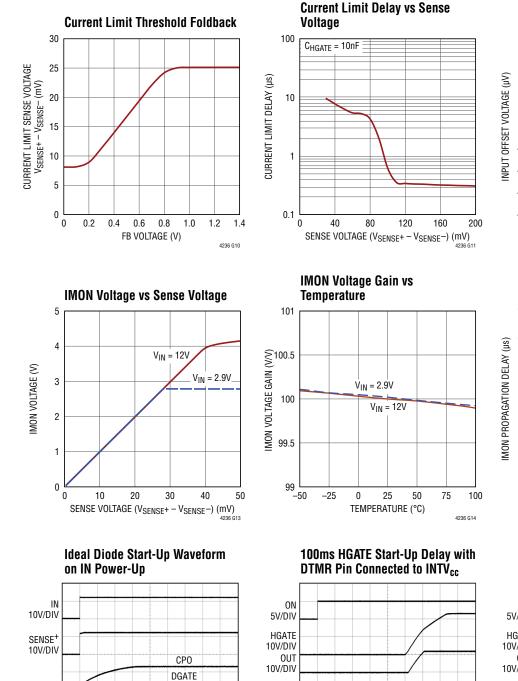

| $\Delta V_{SENSE(TH)}$                  | Current Limit Sense Voltage Threshold<br>(V <sub>SENSE</sub> + – V <sub>SENSE</sub> –)   | FB = 1.3V<br>FB = 0V                                                                                                                                                                                                                     | • | 22.5<br>5.8 | 25<br>8.3      | 27.5<br>10.8   | mV<br>mV       |

| V <sub>SENSE</sub> +(UVL)               | SENSE <sup>+</sup> Undervoltage Lockout                                                  | SENSE <sup>+</sup> Rising                                                                                                                                                                                                                |   | 1.8         | 1.9            | 2              | V              |

| $\Delta V_{\text{SENSE}+(\text{HYST})}$ | SENSE <sup>+</sup> Undervoltage Lockout Hysteresis                                       |                                                                                                                                                                                                                                          |   | 10          | 50             | 90             | mV             |

| I <sub>SENSE</sub> +                    | SENSE <sup>+</sup> Pin Current                                                           | SENSE <sup>+</sup> = 12V                                                                                                                                                                                                                 |   | 0.3         | 0.8            | 1.3            | mA             |

| I <sub>SENSE</sub> <sup>-</sup>         | SENSE <sup>-</sup> Pin Current                                                           | SENSE <sup>-</sup> = 12V                                                                                                                                                                                                                 |   | 10          | 40             | 100            | μA             |

| I <sub>CS</sub> +                       | CS <sup>+</sup> Pin Current                                                              | $CS^+ = 12V, \Delta V_{SENSE} = 0V$                                                                                                                                                                                                      |   |             |                | ±1             | μA             |

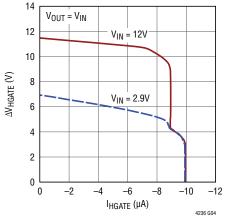

| $\Delta V_{\text{HGATE}}$               | External N-Channel Gate Drive<br>(V <sub>HGATE</sub> – V <sub>OUT</sub> )                | IN < 7V, I = 0, -1µA<br>IN = 7V to 18V, I = 0, -1µA                                                                                                                                                                                      | • | 5<br>10     | 7<br>12        | 14<br>14       | V              |

| $\Delta V_{HGATE(H)}$                   | Gate High Threshold (V <sub>HGATE</sub> – V <sub>OUT</sub> )                             |                                                                                                                                                                                                                                          |   | 3.6         | 4.2            | 4.8            | V              |

| HGATE(UP)                               | External N-Channel Gate Pull-Up Current                                                  | Gate Drive On, HGATE = 0V                                                                                                                                                                                                                |   | -7          | -10            | -13            | μA             |

| I <sub>HGATE(DN)</sub>                  | External N-Channel Gate Pull-Down Current                                                | Gate Drive Off, OUT = 12V,<br>HGATE = OUT + 5V                                                                                                                                                                                           | • | 1           | 2              | 4              | mA             |

| HGATE(FPD)                              | External N-Channel Gate Fast Pull-Down<br>Current                                        | Fast Turn-Off, OUT = 12V,<br>HGATE = OUT + 5V                                                                                                                                                                                            | • | 100         | 200            | 350            | mA             |

| t <sub>PHL(SENSE)</sub>                 | Sense Voltage (SENSE⁺ – SENSE⁻)<br>High to HGATE Low                                     | $\Delta V_{\text{SENSE}} = 200 \text{mV}, C_{\text{HGATE}} = 10 \text{nF}$                                                                                                                                                               | • |             | 0.5            | 1              | μs             |

| t <sub>off(hgate)</sub>                 | ON Low to HGATE Low<br>EN High to HGATE Low<br>SENSE <sup>+</sup> Low to HGATE Low       | SENSE+ UVLO                                                                                                                                                                                                                              | • |             | 10<br>20<br>10 | 20<br>40<br>20 | μs<br>μs<br>μs |

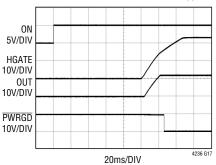

| t <sub>D(HGATE)</sub>                   | ON High, EN Low to HGATE Turn-On Delay                                                   | DTMR = INTV <sub>CC</sub>                                                                                                                                                                                                                |   | 50          | 100            | 150            | ms             |

| t <sub>P(HGATE)</sub>                   | ON to HGATE Propagation Delay                                                            | ON = Step 0.8V to 2V                                                                                                                                                                                                                     |   |             | 10             | 20             | μs             |

| /                                       | -                                                                                        | 1                                                                                                                                                                                                                                        |   |             |                |                | 4236f          |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>IN</sub> = 12V, unless otherwise noted.

| SYMBOL                           | PARAMETER                                                                       | CONDITIONS                                                                                                                                                                                       |   | MIN                    | TYP                      | MAX        | UNITS    |

|----------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------------------|--------------------------|------------|----------|

| Inputs                           |                                                                                 | 1                                                                                                                                                                                                |   | 1                      |                          |            |          |

| V <sub>D20FF(H,TH)</sub>         | D2OFF Pin High Threshold                                                        | D20FF Rising                                                                                                                                                                                     | • | 1.21                   | 1.235                    | 1.26       | V        |

| V <sub>D20FF(L,TH)</sub>         | D2OFF Pin Low Threshold                                                         | D20FF Falling                                                                                                                                                                                    | • | 1.19                   | 1.215                    | 1.24       | V        |

| $\Delta V_{D20FF(HYST)}$         | D2OFF Pin Hysteresis                                                            |                                                                                                                                                                                                  | • | 10                     | 20                       | 30         | mV       |

| V <sub>IN(TH)</sub>              | ON, FB Pin Threshold Voltage                                                    | Voltage Rising                                                                                                                                                                                   | • | 1.21                   | 1.235                    | 1.26       | V        |

| ΔV <sub>ON(HYST)</sub>           | ON Pin Hysteresis                                                               |                                                                                                                                                                                                  | • | 40                     | 80                       | 120        | mV       |

| ΔV <sub>FB(HYST)</sub>           | FB Pin Hysteresis                                                               |                                                                                                                                                                                                  | • | 10                     | 20                       | 30         | mV       |

| V <sub>ON(RESET)</sub>           | ON Pin Fault Reset Threshold Voltage                                            | ON Falling                                                                                                                                                                                       | • | 0.57                   | 0.6                      | 0.63       | V        |

| I <sub>IN(LEAK)</sub>            | Input Leakage Current (ON, FB, D2OFF)                                           | V = 5V                                                                                                                                                                                           | • |                        | 0                        | ±1         | μA       |

| V <sub>EN(TH)</sub>              | EN Pin Threshold Voltage                                                        | EN Rising                                                                                                                                                                                        | • | 1.185                  | 1.235                    | 1.284      | V        |

| $\Delta V_{\overline{EN}(HYST)}$ | EN Pin Hysteresis                                                               |                                                                                                                                                                                                  | • | 60                     | 110                      | 200        | mV       |

| I <sub>EN(UP)</sub>              | EN Pull-Up Current                                                              | ĒN = 1V                                                                                                                                                                                          | • | -7                     | -10                      | -13        | μA       |

| V <sub>TMR(H)</sub>              | FTMR, DTMR Pin High Threshold                                                   |                                                                                                                                                                                                  | • | 1.198                  | 1.235                    | 1.272      | V        |

| V <sub>TMR(L)</sub>              | FTMR, DTMR Pin Low Threshold                                                    |                                                                                                                                                                                                  | • | 0.15                   | 0.2                      | 0.25       | V        |

| I <sub>FTMR(UP)</sub>            | FTMR Pull-Up Current                                                            | FTMR = 1V, In Fault Mode                                                                                                                                                                         | • | -80                    | -100                     | -120       | μA       |

| I <sub>FTMR(DN)</sub>            | FTMR Pull-Down Current                                                          | FTMR = 2V, No Faults                                                                                                                                                                             | • | 1.3                    | 2                        | 2.7        | μΑ       |

| D <sub>RETRY</sub>               | Auto-Retry Duty Cycle                                                           |                                                                                                                                                                                                  | • | 0.07                   | 0.15                     | 0.23       | %        |

| I <sub>DTMR(UP)</sub>            | DTMR Pull-Up Current                                                            | DTMR = 0.6V                                                                                                                                                                                      | • | -8                     | -10                      | -12        | μΑ       |

| I <sub>DTMR(DN)</sub>            | DTMR Pull-Down Current                                                          | DTMR = 1.5V                                                                                                                                                                                      | • | 1                      | 5                        | 10         | mA       |

| $\Delta V_{\text{DTMR(TH)}}$     | DTMR Pin Threshold Voltage<br>(V <sub>DTMR</sub> – V <sub>INTVCC</sub> )        | t <sub>D(HGATE)</sub> Start-Up Delay                                                                                                                                                             | • | -0.1                   | -0.3                     | -0.5       | V        |

| t <sub>RST(ON)</sub>             | ON Low to FAULT High                                                            |                                                                                                                                                                                                  |   |                        | 20                       | 40         | μs       |

| t <sub>PG(FB)</sub>              | FB Low to PWRGD High                                                            |                                                                                                                                                                                                  | • |                        | 20                       | 40         | μs       |

| Outputs                          |                                                                                 | - L                                                                                                                                                                                              |   |                        |                          |            |          |

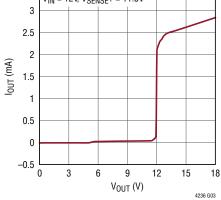

| I <sub>OUT</sub>                 | OUT Pin Current                                                                 | OUT = 11V, IN = 12V, ON = 2V<br>OUT = 13V, IN = 12V, ON = 2V                                                                                                                                     | • |                        | 40<br>2.5                | 100<br>4   | μA<br>mA |

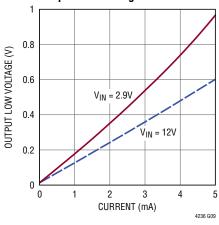

| V <sub>OL</sub>                  | Output Low Voltage<br>(FAULT, PWRGD, DSTAT1, DSTAT2)                            | I = 1mA<br>I = 3mA                                                                                                                                                                               | • |                        | 0.15<br>0.4              | 0.4<br>1.2 | V<br>V   |

| V <sub>OH</sub>                  | Output High Voltage (FAULT, PWRGD)                                              | $I = -1\mu A$                                                                                                                                                                                    |   | INTV <sub>CC</sub> – 1 | INTV <sub>CC</sub> – 0.5 |            | V        |

| I <sub>OH</sub>                  | Input Leakage Current<br>(FAULT, PWRGD, DSTAT1, DSTAT2)                         | V = 18V                                                                                                                                                                                          | • |                        | 0                        | ±1         | μA       |

| I <sub>PU</sub>                  | Output Pull-Up Current (FAULT, PWRGD)                                           | V = 1.5V                                                                                                                                                                                         | • | -7                     | -10                      | -13        | μA       |

| Current Monito                   | )r                                                                              | ·                                                                                                                                                                                                |   |                        |                          |            |          |

| $\Delta V_{REG}$                 | Floating Regulator Voltage<br>(V <sub>SENSE</sub> + – V <sub>REG</sub> )        | $I_{REG} = \pm 1 \mu A$                                                                                                                                                                          | • | 3.6                    | 4.1                      | 4.6        | V        |

| $\Delta V_{SENSE(FS)}$           | Input Sense Voltage Full Scale<br>(V <sub>SENSE</sub> + – V <sub>SENSE</sub> –) | SENSE <sup>+</sup> = 12V                                                                                                                                                                         | • | 25                     |                          |            | mV       |

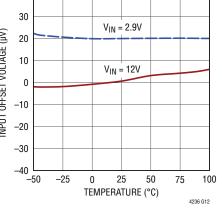

| V <sub>IMON(OS)</sub>            | IMON Input Offset Voltage                                                       | $\Delta V_{SENSE} = 0V$                                                                                                                                                                          | • |                        |                          | ±150       | μV       |

| GIMON                            | IMON Voltage Gain                                                               | $\Delta V_{SENSE} = 20 mV$ and 5 mV                                                                                                                                                              | • | 99                     | 100                      | 101        | V/V      |

| VIMON(MAX)                       | IMON Maximum Output Voltage                                                     | $\begin{array}{l} \Delta V_{\text{SENSE}} = 70 \text{mV}, \ 5\text{V} \leq \text{SENSE}^+ \leq 18\text{V} \\ \Delta V_{\text{SENSE}} = 35 \text{mV}, \ \text{SENSE}^+ = 2.9\text{V} \end{array}$ | • | 3.5<br>2.7             |                          | 5.5<br>2.9 | V<br>V   |

| VIMON(MIN)                       | IMON Minimum Output Voltage                                                     | $\Delta V_{SENSE} = 200 \mu V$                                                                                                                                                                   | • |                        |                          | 40         | mV       |

| R <sub>IMON(OUT)</sub>           | IMON Output Resistance                                                          | $\Delta V_{\text{SENSE}} = 200 \mu V$                                                                                                                                                            | • | 15                     | 20                       | 27         | kΩ       |

4236f

### **ELECTRICAL CHARACTERISTICS**

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to GND unless otherwise specified.

**Note 3:** An internal clamp limits the DGATE1 and CPO1 pins to a minimum of 10V above and a diode below IN1. Driving these pins to voltages beyond the clamp may damage the device.

**Note 4:** An internal clamp limits the DGATE2 and CPO2 pins to a minimum of 10V above and a diode below D2SRC. Driving these pins to voltages beyond the clamp may damage the device.

**Note 5:** An internal clamp limits the HGATE pin to a minimum of 10V above and a diode below OUT. Driving this pin to voltages beyond the clamp may damage the device.

**Note 6:** Thermal resistance is specified when the exposed pad is soldered to a  $3^{"} \times 5^{"}$ , four layer, FR4 board.

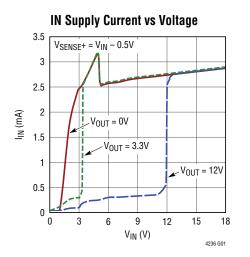

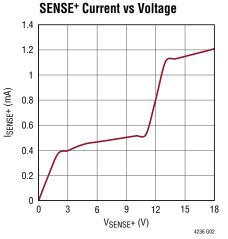

### **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ , $V_{IN} = 12V$ , unless otherwise noted.

**OUT Current vs Voltage** 3.5 V<sub>IN</sub> = 12V, V<sub>SENSE</sub>+ = 11.5V

Hot Swap Gate Voltage vs Current

$V_{IN} = 18V$

I<sub>DGATE</sub> (µA)

-100 -120 -140

4236 G07

$V_{IN} = 2.9V$

Hot Swap Gate Voltage vs IN Voltage 14  $V_{OUT} = V_{IN}$ 12 **AVHGATE (V)** 10 8 6 4 0 3 6 9 12 15 18  $V_{IN}(V)$ 4236 G05

**CPO Voltage vs Current**

**Diode Gate Voltage vs Current Diode Gate Voltage vs IN Voltage** 14  $V_{SENSE}$ + =  $V_{IN}$  - 0.15V  $V_{SENSE}$  + =  $V_{IN}$  - 0.15V 12 **AVDGATE (V)** 10 8 6 4

3

0

6

9

$V_{IN}(V)$

12

15

18

4236 G08

# Downloaded from Arrow.com.

12

10

8

6

4

2

0 -2

0 -20 -40 -60 -80

**AVDGATE (V)**

For more information www.linear.com/LTC4236

### TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ , $V_{IN} = 12V$ , unless otherwise noted.

4236 G16

10ms/DIV

#### **Current Sense Amplifier Input Offset Voltage vs Temperature**

40

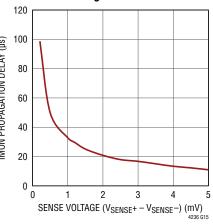

#### **IMON Propagation Delay vs** Sense Voltage

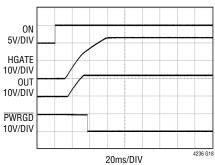

Adjustable HGATE Start-Up Delay with 0.1µF Capacitor at DTMR pin

10V/DIV

### PIN FUNCTIONS

**CP01, CP02:** Charge Pump Output. Connect a capacitor from CP01 or CP02 to the corresponding IN1 or D2SRC pin. The value of this capacitor is approximately  $10 \times$  the gate capacitance (C<sub>ISS</sub>) of the external MOSFET for ideal diode control. The charge stored on this capacitor is used to pull up the ideal diode MOSFET gate during a fast turn-on. Leave this pin open if fast ideal diode turn-on is not needed.

**CS+:** Positive Current Sense Input for Current Sense Amplifier. Connect this pin to the input of the current sense resistor. The voltage between CS<sup>+</sup> and SENSE<sup>-</sup> is translated to a ground referenced signal at IMON pin.

**DGATE1, DGATE2:** Ideal Diode MOSFET Gate Drive Output. Connect this pin to the gate of an external N-channel MOSFET for ideal diode control. An internal clamp limits the gate voltage to 12V above and a diode voltage below IN1 or D2SRC. During fast turn-on, a 1.5A pull-up charges DGATE from CPO. During fast turn-off, a 1.5A pull-down discharges DGATE1 to IN1 and DGATE2 to D2SRC.

**D20FF:** Control Input. A rising edge above 1.235V turns off the external ideal diode MOSFET in the IN2 supply path and a falling edge below 1.215V allows the MOSFET to be turned on. Connect this pin to an external resistive divider from IN1 to make IN1 the higher priority input supply when IN1 and IN2 are equal.

**D2SRC:** Ideal Diode MOSFET Gate Drive Return. Connect this pin to the source of the external N-channel MOSFET switch in the IN2 power path. The gate fast pull-down current returns through this pin when DGATE2 is discharged.

**DSTAT1:** Diode MOSFET Status Output. Open drain output that pulls low when the MOSFET gate drive voltage between DGATE1 and IN1 exceeds 0.7V indicating that the MOSFET diode path is on. Otherwise it goes high impedance. It requires an external pull-up resistor to a positive supply. Leave open if unused.

**DSTAT2:** Diode MOSFET Status Output. Open drain output that pulls low when the MOSFET gate drive voltage between DGATE2 and D2SRC exceeds 0.7V indicating that the MOSFET diode path is on. Otherwise it goes high impedance. It requires an external pull-up resistor to a positive supply. Leave open if unused.

**DTMR:** Debounce Timer Capacitor Terminal. Connect this pin to either  $INTV_{CC}$  for fixed 100ms delay or an external capacitor to ground for adjustable start-up delay (123ms/µF) when EN toggles low.

**EN**: Enable Input. Ground this pin to enable Hot Swap control. If this pin is pulled high, the Hot Swap MOSFET is not allowed to turn on. A  $10\mu$ A current source pulls this pin up to a diode below INTV<sub>CC</sub>. Upon EN going low when ON is high, there is a start-up delay for debounce as configured at the DTMR pin, after which the fault is cleared.

**FAULT:** Overcurrent Fault Status Output. Output that pulls low when the fault timer expires during an overcurrent fault. Otherwise it is pulled high by a  $10\mu$ A current source to a diode below INTV<sub>CC</sub>. It may be pulled above INTV<sub>CC</sub> using an external pull-up. Leave open if unused.

**FB:** Foldback and Power Good Comparator Input. Connect this pin to an external resistive divider from OUT. If the voltage falls below 1.215V, the PWRGD pin pulls high to indicate the power is bad. If the voltage falls below 0.9V, the output power is considered bad and the current limit is reduced. Tie to INTV<sub>CC</sub> to disable foldback.

**FTMR:** Fault Timer Capacitor Terminal. Connect a capacitor between this pin and ground to set a  $12ms/\mu F$  duration for current limit before the external Hot Swap MOSFET is turned off. The duration of the off time is  $8s/\mu F$ , resulting in a 0.15% duty cycle.

**GND:** Device Ground.

### PIN FUNCTIONS

**HGATE:** Hot Swap MOSFET Gate Drive Output. Connect this pin to the gate of the external N-channel MOSFET for Hot Swap control. An internal  $10\mu$ A current source charges the MOSFET gate. An internal clamp limits the gate voltage to 12V above and a diode voltage below OUT. During an undervoltage generated turn-off, a 2mA pull-down discharges HGATE to ground. During an output short or INTV<sub>CC</sub> undervoltage lockout, a fast 200mA pull-down discharges HGATE to OUT.

**IN1, IN2:** Positive Supply Input and Ideal Diode MOSFET Gate Drive Return. Connect this pin to the power input side of the external ideal diode MOSFET. The 5V  $INTV_{CC}$  supply is generated from IN1, IN2 and OUT via an internal diode-OR. The voltage sensed at this pin is used to control DGATE. The gate fast pull-down current returns through IN1 pin when DGATE1 is discharged.

**INTV<sub>CC</sub>:** Internal 5V Supply Decoupling Output. This pin must have a  $0.1\mu$ F or larger capacitor to GND. An external load of less than 500 $\mu$ A can be connected at this pin. An undervoltage lockout threshold of 2.2V will turn off both MOSFETs.

**IMON:** Current Sense Monitoring Output. This pin voltage is proportional to the sense voltage across the current sense resistor with a voltage gain of 100. An internal 20k resistor is connected from this pin to ground.

**ON:** ON Control Input. A rising edge above 1.235V turns on the external Hot Swap MOSFET and a falling edge below 1.155V turns it off. Connect this pin to an external resistive divider from SENSE<sup>+</sup> to monitor the supply undervoltage condition. Pulling the ON pin below 0.6V resets the fault latch after an overcurrent fault. Tie to INTV<sub>CC</sub> if unused.

**OUT:** Hot Swap MOSFET Gate Drive Return. Connect this pin to the output side of the external MOSFET. The gate fast pull-down current returns through this pin when HGATE is discharged.

**PWRGD:** Power Status Output. Output that pulls low when the FB pin rises above 1.235V and the MOSFET gate drive between HGATE and OUT exceeds 4.2V. Otherwise it is pulled high by a 10 $\mu$ A current source to a diode below INTV<sub>CC</sub>. It may be pulled above INTV<sub>CC</sub> using an external pull-up. Leave open if unused.

**REG:** Internal Regulated Supply for Current Sense Amplifier. A  $0.1\mu$ F or larger capacitor should be tied from REG to SENSE<sup>+</sup>. This pin is not designed to drive external circuits.

**SENSE+:** Positive Current Sense Input. Connect this pin to the diode-OR output of the external ideal diode MOS-FETs and input of the current sense resistor. The voltage sensed at this pin is used for monitoring the current limit and also to control DGATE for forward voltage regulation and reverse turn-off. This pin has an undervoltage lockout threshold of 1.9V that will turn off the Hot Swap MOSFET.

**SENSE<sup>-</sup>:** Negative Current Sense Input. Connect this pin to the output of the current sense resistor. The current limit circuit controls HGATE to limit the voltage between SENSE<sup>+</sup> and SENSE<sup>-</sup> to 25mV or less depending on the voltage at the FB pin.

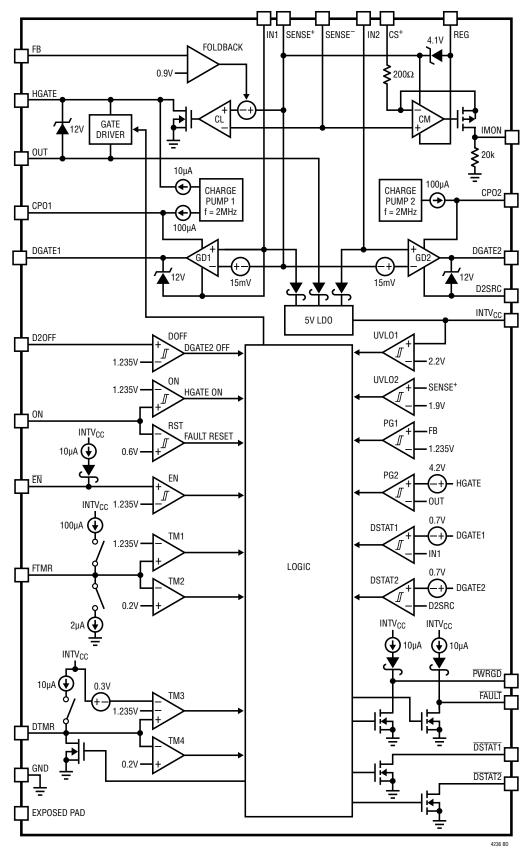

### **BLOCK DIAGRAM**

### OPERATION

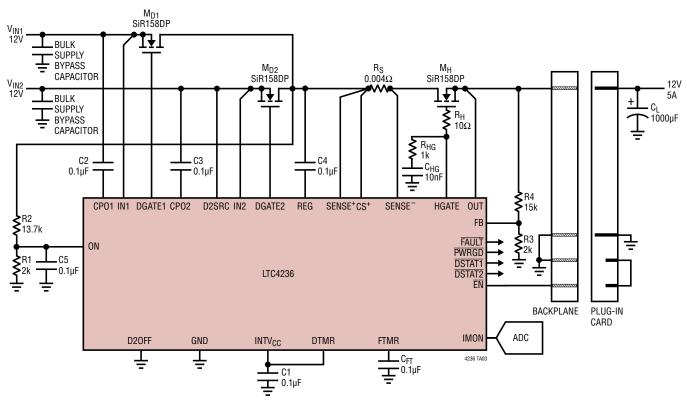

The LTC4236 functions as an input supply diode-OR with inrush current limiting and overcurrent protection by controlling the external N-channel MOSFETs ( $M_{D1}$ ,  $M_{D2}$  and  $M_{H}$ ) on a supply path. This allows boards to be safely inserted and removed in systems with a backplane powered by redundant supplies. The LTC4236 has a single Hot Swap controller and two separate ideal diode controllers, each providing independent control for the two input supplies.

When the LTC4236 is first powered up, the gates of the external MOSFETs are held low, keeping them off. As the DGATE2 pull-up can be disabled by the D2OFF pin, DGATE2 will pull high only when the D2OFF pin is pulled low. The gate drive amplifier (GD1, GD2) monitors the voltage between the IN and SENSE<sup>+</sup> pins and drives the respective DGATE pin. The amplifier quickly pulls up the DGATE pin, turning on the MOSFET for ideal diode control, when it senses a large forward voltage drop. With the ideal diode MOSFETs acting as input supply diode-OR, the SENSE<sup>+</sup> pin voltage rises to the highest of the supplies at the IN1 and IN2 pins. An external capacitor connected at the CPO pin provides the charge needed to guickly turn on the ideal diode MOSFET. An internal charge pump charges up this capacitor at device power-up. The DGATE pin sources current from the CPO pin and sinks current into the IN1, D2SRC and GND pins. When the DGATE1 to IN1 or DGATE2 to D2SRC voltage exceeds 0.7V, the respective DSTAT pin pulls low to indicate that the ideal diode MOSFET is turned on.

Pulling the ON pin high and  $\overline{\text{EN}}$  pin low initiates a debounce timing cycle that can be a fixed 100ms or adjustable delay as configured at the DTMR pin. After this timing cycle, a 10µA current source from the charge pump ramps up the HGATE pin. When the Hot Swap MOSFET turns on, the inrush current is limited at a level set by an external sense resistor (R<sub>S</sub>) connected between the SENSE<sup>+</sup> and SENSE<sup>-</sup> pins. An active current limit amplifier (CL) servos the gate of the MOSFET to 25mV or less across the current sense resistor depending on the voltage at the FB pin. Inrush current can be further reduced, if desired, by adding a capacitor from HGATE to GND. When FB voltage rises above 1.235V and the MOSFET's gate drive (HGATE to OUT voltage) exceeds 4.2V, the PWRGD pin pulls low.

The high side current sense amplifier (CM) provides accurate monitoring of current through the current sense resistor. The sense voltage is amplified by 100 times and level shifted from the positive rail to a ground-referred output at the IMON pin. The output signal is analog and may be used as is or measured with an ADC.

When the ideal diode MOSFET is turned on, the gate drive amplifier controls DGATE to servo the forward voltage drop ( $V_{IN} - V_{SENSE}$ +) across the MOSFET to 15mV. If the load current causes more than 15mV of voltage drop, the gate voltage rises to enhance the MOSFET. For large output currents, the MOSFET's gate is driven fully on and the voltage drop is equal to  $I_{LOAD}$ •R<sub>DS(ON)</sub> of the MOSFET.

In the case of an input supply short-circuit when the MOSFETs are conducting, a large reverse current starts flowing from the load towards the input. The gate drive amplifier detects this failure condition and turns off the ideal diode MOSFET by pulling down the DGATE pin.

In the case where an overcurrent fault occurs on the supply output, the current is limited with foldback. After a delay set by 100 $\mu$ A charging the FTMR pin capacitor, the fault timer expires and pulls the HGATE pin low, turning off the Hot Swap MOSFET. The FAULT pin is also latched low. At this point, the DGATE pin continues to pull high and keeps the ideal diode MOSFET on.

Internal clamps limit both the DGATE1 and CPO1 to IN1, and DGATE2 and CPO2 to D2SRC voltages to 12V. The same clamps also limit the DGATE and CPO pins to a diode voltage below the IN1 or D2SRC pins. Another internal clamp limits the HGATE to OUT voltage to 12V and also clamps the HGATE pin to a diode voltage below the OUT pin.

Power to the LTC4236 is supplied from either the IN or OUT pins, through an internal diode-OR circuit to a low dropout regulator (LDO). That LDO generates a 5V supply at the INTV<sub>CC</sub> pin and powers the LTC4236's internal low voltage circuitry.

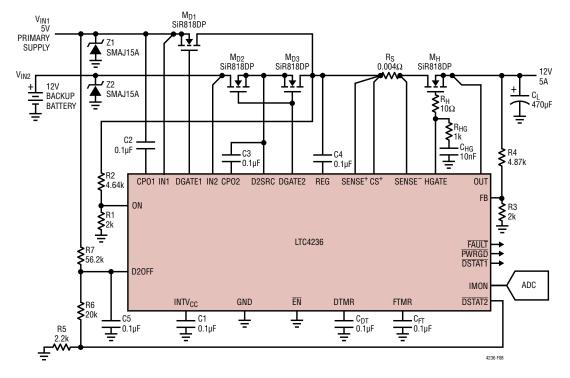

High availability systems often employ parallel-connected power supplies or battery feeds to achieve redundancy and enhance system reliability. Power ORing diodes are commonly used to connect these supplies at the point of load at the expense of power loss due to significant diode forward voltage drop. The LTC4236 minimizes this power loss by using external N-channel MOSFETs as the pass elements, allowing for a low voltage drop from the supply to the load when the MOSFETs are turned on. When an input source voltage drops below the output common supply voltage, the appropriate MOSFET is turned off, thereby matching the function and performance of an ideal diode. By adding a current sense resistor and a Hot Swap MOSFET after the parallel-connected ideal diode MOSFETs, the LTC4236 enhances the ideal diode performance with inrush current limiting and overcurrent protection (see Figure 1). This allows the board to be safely inserted and removed from a live backplane without damaging the connector.

#### Internal V<sub>CC</sub> Supply

The LTC4236 operates with an input supply from 2.9V to 18V. The power supply to the device is internally regulated at 5V by a low dropout regulator (LDO) with an output at the INTV<sub>CC</sub> pin. An internal diode-OR circuit selects the highest of the supplies at the IN and OUT pins to power the device through the LDO. The diode-OR scheme permits the device's power to be kept alive by the OUT voltage when the IN supplies have collapsed or shut off.

An undervoltage lockout circuit prevents all of the MOSFETs from turning on until the INTV<sub>CC</sub> voltage exceeds 2.2V. A 0.1 $\mu$ F capacitor is recommended between the INTV<sub>CC</sub> and GND pins, close to the device for bypassing. No external supply should be connected at the INTV<sub>CC</sub> pin so as not to affect the LDO's operation. A small external load of less than 500 $\mu$ A can be connected at the INTV<sub>CC</sub> pin.

Figure 1. Card Resident Diode-OR with Hot Swap Application

#### Turn-On Sequence

The board power supply at the OUT pin is controlled with external N-channel MOSFETs ( $M_{D1}$ ,  $M_{D2}$  and  $M_{H}$ ) in Figure 1. The ideal diode MOSFETs connected in parallel on the supply side function as a diode-OR, while  $M_{H}$  on the load side acts as a Hot Swap MOSFET controlling the power supplied to the output load. The sense resistor  $R_{S}$  monitors the load current for overcurrent detection. The HGATE capacitor  $C_{HG}$  controls the gate slew rate to limit the inrush current. Resistor  $R_{HG}$  with  $C_{HG}$  compensates the current control loop, while  $R_{H}$  prevents high frequency oscillations in the Hot Swap MOSFET.

During a normal power-up, the ideal diode MOSFETs turn on first. As soon as the internally generated supply,  $INTV_{CC}$ , rises above its 2.2V undervoltage lockout threshold, the internal charge pump is allowed to charge up the CPO pins. Because the ideal diode MOSFETs are connected in parallel as a diode-OR, the SENSE<sup>+</sup> pin voltage approaches the highest of the supplies at the IN1 and IN2 pins. The MOSFET associated with the lower input supply voltage will be turned off by the corresponding gate drive amplifier.

Before the Hot Swap MOSFET can be turned on,  $\overline{\text{EN}}$  must remain low and ON must remain high for a debounce cycle as configured at the DTMR pin, to ensure that any contact bounces during the insertion have ceased. At the end of the debounce cycle, the internal fault latch is cleared. The Hot Swap MOSFET is then allowed to turn on by charging up HGATE with a 10µA current source from the charge pump. The voltage at the HGATE pin rises with a slope equal to 10µA/C<sub>HG</sub> and the supply inrush current flowing into the load capacitor C<sub>L</sub> is limited to:

$$I_{\text{INRUSH}} = \frac{C_{\text{L}}}{C_{\text{HG}}} \bullet 10 \mu \text{A}$$

The OUT voltage follows the HGATE voltage when the Hot Swap MOSFET turns on. If the voltage across the current sense resistor  $R_S$  becomes too high based on the FB pin voltage, the inrush current will be limited by the internal current limiting circuitry. Once the MOSFET gate overdrive exceeds 4.2V and the FB pin voltage is above 1.235V, the PWRGD pin pulls low to indicate that the power is good.

Once OUT reaches the input supply voltage, HGATE continues to ramp up. An internal 12V clamp limits the HGATE voltage above OUT.

When the ideal diode MOSFET is turned on, the gate drive amplifier controls the gate of the MOSFET to servo the forward voltage drop across the MOSFET to 15mV. If the load current causes more than 15mV of drop, the MOSFET gate is driven fully on and the voltage drop is equal to  $I_{LOAD} \bullet R_{DS(ON)}$ .

#### **Turn-Off Sequence**

The external MOSFETs can be turned off by a variety of conditions. A normal turn-off for the Hot Swap MOSFET is initiated by pulling the ON pin below its 1.155V threshold (80mV ON pin hysteresis), or pulling the EN pin above its 1.235V threshold. Additionally, an overcurrent fault that exceeds the fault timer period also turns off the Hot Swap MOSFET. Normally, the LTC4236 turns off the MOSFET by pulling the HGATE pin to ground with a 2mA current sink.

All of the MOSFETs turn off when  $INTV_{CC}$  falls below its undervoltage lockout threshold (2.2V). The DGATE pin is pulled down with a 100µA current to one diode voltage below the IN1 or D2SRC pins, while the HGATE pin is pulled down to the OUT pin by a 200mA current. When D2OFF is pulled high above 1.235V, the ideal diode MOSFET in the IN2 power path is turned off with DGATE2 pulled low by a 100µA current.

The gate drive amplifier controls the ideal diode MOSFET to prevent reverse current when the input supply falls below SENSE<sup>+</sup>. If the input supply collapses quickly, the gate drive amplifier turns off the ideal diode MOSFET with a fast pull-down circuit. If the input supply falls at a more modest rate, the gate drive amplifier controls the MOSFET to maintain SENSE<sup>+</sup> at 15mV below IN.

#### Board Presence Detect with $\overline{\text{EN}}$

If ON is high when the  $\overline{\text{EN}}$  pin goes low, indicating a board presence, the LTC4236 initiates a timing cycle as configured at the DTMR pin for contact debounce. It defaults to internal 100ms delay if DTMR is tied to INTV<sub>CC</sub>. If an external capacitor C<sub>DT</sub> is connected from the DTMR pin to GND, the delay is given by charging the capacitor to 1.235V with

a 10 $\mu$ A current. Thereafter, the capacitor is discharged to ground by a 5mA current. For a given debounce delay, the equation for setting the external capacitor C<sub>DT</sub> value is:

$C_{DT} = t_{DB} \bullet 0.0081 \ [\mu F/ms]$

Upon board insertion, any bounces on the  $\overline{EN}$  pin restart the timing cycle. When the debounce timing cycle is done, the internal fault latch is cleared. If the  $\overline{EN}$  pin remains low at the end of the timing cycle, HGATE is charged up with a 10µA current source to turn on the Hot Swap MOSFET.

If the  $\overline{\text{EN}}$  pin goes high, indicating a board removal, the HGATE pin is pulled low with a 2mA current sink after a 20µs delay, turning off the Hot Swap MOSFET without clearing any latched fault.

### **Overcurrent Fault**

The LTC4236 features an adjustable current limit with foldback that protects the external MOSFET against short circuits or excessive load current. The voltage across the external sense resistor  $R_S$  is monitored by an active current limit amplifier. The amplifier controls the gate of the Hot Swap MOSFET to reduce the load current as a function of the output voltage sensed by the FB pin during active current limit. A graph in the Typical Performance Characteristics shows the current limit sense voltage versus FB voltage.

An overcurrent fault occurs when the output has been in current limit for longer than the fault timer period configured at the FTMR pin. Current limiting begins when the sense voltage between the SENSE<sup>+</sup> and SENSE<sup>-</sup> pins reaches 8.3mV to 25mV depending on the FB pin voltage. The gate of the Hot Swap MOSFET is brought under control by the current limit amplifier and the output current is regulated to limit the sense voltage to less than 25mV. At this point, the fault timer starts with a  $100\mu\text{A}$  current charging the FTMR pin capacitor. If the FTMR pin voltage exceeds its 1.235V threshold, the external MOSFET turns off with HGATE pulled to ground by 2mA and FAULT pulls low.

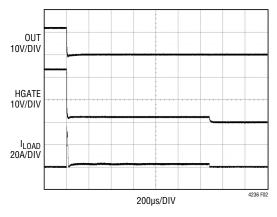

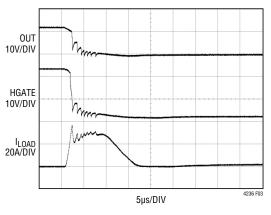

After the Hot Swap MOSFET turns off, the FTMR pin capacitor is discharged with a  $2\mu$ A pull-down current until its threshold reaches 0.2V. This is followed by a cool-off period of 14 timing cycles as described in the FTMR Pin Functions. Figure 2 shows an overcurrent fault on the 12V output.

Figure 2. Overcurrent Fault on 12V Output

Figure 3. Severe Short-Circuit on 12V Output

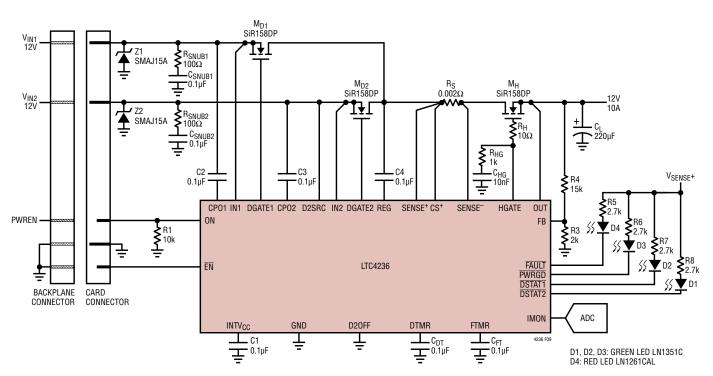

In the event of a severe short-circuit fault on the 12V output as shown in Figure 3, the output current can surge to tens of amperes. The LTC4236 responds within 1µs to bring the current under control by pulling the HGATE to OUT voltage down to zero volts. Almost immediately, the gate of the Hot Swap MOSFET recovers rapidly due to the charge stored in the R<sub>HG</sub> and C<sub>HG</sub> network and current is actively limited until the fault timer expires. Due to parasitic supply lead inductance, an input supply without any bypass capacitor may collapse during the high current surge and then spike upwards when the current is interrupted. Figure 9 shows the input supply transient suppressors comprising of Z1, R<sub>SNUB1</sub>, C<sub>SNUB1</sub> and Z2, R<sub>SNUB2</sub>, C<sub>SNUB2</sub> for the two supplies if there is no input capacitance.

#### **FTMR Pin Functions**

An external capacitor C<sub>FT</sub> connected from the FTMR pin to GND serves as fault timing when the supply output is

in active current limit. When the voltage across the sense resistor exceeds the foldback current limit threshold (from 25mV to 8.3mV), FTMR pulls up with  $100\mu$ A. Otherwise, it pulls down with  $2\mu$ A. The fault timer expires when the 1.235V FTMR threshold is exceeded, causing the FAULT pin to pull low. For a given fault timer period, the equation for setting the external capacitor C<sub>FT</sub> value is:

$C_{FT} = t_{FT} \bullet 0.083 \ [\mu F/ms]$

After the fault timer expires, the FTMR pin capacitor pulls down with  $2\mu$ A from the 1.235V FTMR threshold until it reaches 0.2V. Then, it completes 14 cooling cycles consisting of the FTMR pin capacitor charging to 1.235V with a 100 $\mu$ A current and discharging to 0.2V with a  $2\mu$ A current. At that point, the HGATE pin voltage is allowed to start up if the fault has been cleared as described in the Resetting Fault section. When the latched fault is cleared during the cool-off period, the FAULT pin pulls high. The total cool-off time for the MOSFET after an overcurrent fault is:

$t_{COOL} = C_{FT} \bullet 8 [s/\mu F]$

After the cool-off period, the HGATE pin is only allowed to pull up if the fault has been cleared for the latchoff part. For the auto-retry part, the latched fault is cleared automatically following the cool-off period and the HGATE pin voltage is allowed to restart.

#### Resetting Fault (LTC4236-1)

For the latchoff part, an overcurrent fault is latched after the fault timer expires and the FAULT pin is asserted low. Only the Hot Swap MOSFET is turned off and the ideal diode MOSFETs are not affected.

To reset a latched fault and restart the output, pull the ON pin below 0.6V for more than 100 $\mu$ s and then high above 1.235V. The fault latch resets and the FAULT pin de-asserts on the falling edge of the ON pin. When ON goes high again and the cool-off cycle has completed, a debounce timing cycle is initiated before the HGATE pin voltage restarts. Toggling the EN pin high and then low again also resets a fault, but the FAULT pin pulls high at the end of the debounce cycle before the HGATE pin voltage starts up. Bringing all the supplies below the INTV<sub>CC</sub> undervoltage lockout threshold (2.2V) shuts off all the MOSFETs and resets the fault latch. A debounce cycle is

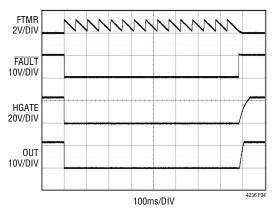

#### Auto-Retry after a Fault (LTC4236-2)

For the auto-retry part, the latched fault is reset automatically at the end of the cool-off period as described in the FTMR Pin Functions section. At the end of the cool-off period, the fault latch is cleared and FAULT pulls high. The HGATE pin voltage is allowed to start up and turn on the Hot Swap MOSFET. If the output short persists, the supply powers up into a short with active current limiting until the fault timer expires and FAULT again pulls low. A new cool-off cycle begins with FTMR ramping down with a 2µA current. The whole process repeats itself until the output short is removed. Since  $t_{FT}$  and  $t_{COOL}$  are a function of FTMR capacitance  $C_{FT}$ , the auto-retry cycle is equal to 0.15%, irrespective of  $C_{FT}$ .

Figure 4 shows an auto-retry sequence after an overcurrent fault.

Figure 4. Auto-Retry Sequence After a Fault

#### **Monitor Undervoltage Fault**

The ON pin functions as a turn-on control and an input supply monitor. A resistive divider connected between the supply diode-OR output (SENSE<sup>+</sup>) and GND at the ON pin monitors the supply for undervoltage condition. The undervoltage threshold is set by proper selection of the resistors at the ON rising threshold voltage (1.235V).

For Figure 1, if R1 = 2k, R2 = 13.7k, the input supply undervoltage threshold is set to 9.7V.

An undervoltage fault occurs if the diode-OR output supply falls below its undervoltage threshold. If the ON pin voltage falls below 1.155V but remains above 0.6V, the Hot Swap MOSFET is turned off by a 2mA pull-down from HGATE to ground. The Hot Swap MOSFET turns back on instantly without the debounce cycle when the diode-OR output supply rises above its undervoltage threshold. However, if the ON pin voltage drops below 0.6V, it turns off the Hot Swap MOSFET and clears the fault latch. The Hot Swap MOSFET turns back on only after a debounce cycle when the diode-OR output supply is restored above its undervoltage threshold.

During the undervoltage fault condition, FAULT will not be pulled low but PWRGD will be pulled high as HGATE is pulled low. The ideal diode function controlled by the ideal diode MOSFET is not affected by the undervoltage (UV) fault condition.

#### **Power Good Monitor**

Internal circuitry monitors the MOSFET gate overdrive between the HGATE and OUT pins. Also, the FB pin that connects to OUT through a resistive divider is used to determine a power good condition. The power good comparator drives high when the FB pin rises above 1.235V, and drives low when FB falls below 1.215V. The power good status for the input supply is reported via an open-drain output, PWRGD. It is normally pulled high by an external pull-up resistor or the internal 10µA pull-up. The PWRGD pin pulls low when the FB power good comparator is high and the HGATE drive exceeds 4.2V. The PWRGD pin goes high when the HGATE is turned off by the ON or EN pins, or when the FB power good comparator drives low, or when INTV<sub>CC</sub> enters undervoltage lockout.

#### **Current Sense Monitor**

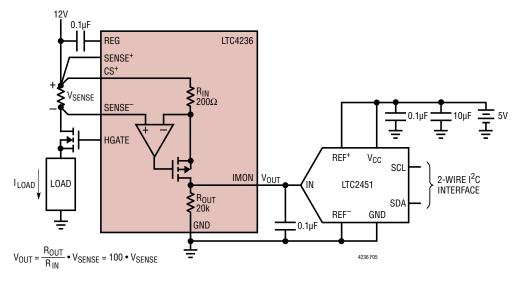

The current through the external sense resistor is monitored by LTC4236's current sense amplifier at the CS<sup>+</sup> and SENSE<sup>-</sup> pins (see Figure 5). The amplifier uses auto-zeroing circuitry to achieve an offset below 150µV over temperature, sense voltage and input supply voltage. The frequency of the auto-zero clock is 10kHz. An internal resistor RIN is connected between the amplifier's negative input terminal and CS<sup>+</sup> pin. The sense amplifier loop forces the negative input terminal to have the same potential as SENSE<sup>-</sup> and that develops a potential across R<sub>IN</sub> to be the same as the sense voltage V<sub>SENSE</sub>. A corresponding current, V<sub>SENSE</sub>/R<sub>IN</sub>, will flow through R<sub>IN</sub>. The high impedance inputs of the sense amplifier will not conduct this input current, allowing it to flow through an internal MOSFET to a resistor  $\mathsf{R}_{\mathsf{OUT}}$  connected between the IMON and GND pins. The IMON output voltage is equal to (R<sub>OUT</sub>/R<sub>IN</sub>) • V<sub>SENSE</sub>. The resistor ratio R<sub>OUT</sub>/R<sub>IN</sub> defines the voltage gain of the sense amplifier and is set to 100 with  $R_{IN} = 200\Omega$  and  $R_{OUT} = 20k$ . Full scale input sense voltage to the sense amplifier is 25mV, corresponding to an output of 2.5V. For input supply voltages greater than

Figure 5. High Side Current Monitor with LTC2451 ADC

5V, the output clamps at 3.5V if the allowable input sense voltage range is exceeded.

#### IMON Output Filtering

A capacitor connected in parallel with  $R_{OUT}$  will give a low pass response. This will reduce unwanted noise at the output, and may also be useful as a charge reservoir to keep the output steady while driving a switching circuit such as an ADC (see Figure 5). This output capacitor  $C_{OUT}$  in parallel with  $R_{OUT}$  will create a pole in the output response at:

$$f_{C} = \frac{1}{2 \bullet \pi \bullet R_{OUT} \bullet C_{OUT}}$$

#### **REG Pin Bypassing**

The LTC4236 has an internally regulated supply near SENSE<sup>+</sup> for internal bias of the current sense amplifier. It is not intended for use as a supply or bias pin for external circuitry. A  $0.1\mu$ F capacitor should be connected between the REG and SENSE<sup>+</sup> pins. This capacitor should be located very near to the device and close to the REG pin for the best performance.

#### **REG and IMON Start-Up**

The start-up current of the current sense amplifier when the LTC4236 is powered on consists of two parts: the first is the current necessary to charge the REG bypass capacitor, which is nominally 0.1  $\mu$ F. Since the REG voltage charges to approximately 4.1V below the SENSE<sup>+</sup> voltage, this can require a significant amount of start-up current. The second source is the output current that flows into R<sub>OUT</sub>, which upon start-up may temporarily drive the IMON output high for less than 2ms. This is a temporary condition which will cease when the sense amplifier settles into normal closed-loop operation.

#### **CPO and DGATE Start-Up**

The CPO pin voltage is initially pulled up to a diode below the IN1 or D2SRC pin when first powered up (see Figure 1). However, for application with back-to-back MOSFETs in IN2 power path, CPO2 starts off at OV since D2SRC is near ground (see Figure 8). CPO starts ramping up 7 $\mu$ s after INTV<sub>CC</sub> clears its undervoltage lockout level. Another 40 $\mu$ s later, DGATE also starts ramping up with CPO. The CPO ramp rate is determined by the CPO pull-up current into the combined CPO and DGATE pin capacitances. An internal clamp limits the CPO pin voltage to 12V above the IN1 or D2SRC pin, while the final DGATE pin voltage is determined by the DGATE1 and DGATE2 pin voltages above IN1 and D2SRC respectively.

#### **CPO Capacitor Selection**

The recommended value of the capacitor between the CPO1 and IN1, and CPO2 and D2SRC pins is approximately  $10 \times$  the input capacitance  $C_{ISS}$  of the ideal diode MOSFET. A larger capacitor takes a correspondingly longer time to charge up by the internal charge pump. A smaller capacitor suffers more voltage drop during a fast gate turn-on event as it shares charge with the MOSFET gate capacitance.

#### **MOSFET Selection**

The LTC4236 drives N-channel MOSFETs to conduct the load current. The important features of the MOSFETs are on-resistance  $R_{DS(ON)}$ , the maximum drain-source voltage  $BV_{DSS}$  and the threshold voltage.

The gate drive for the ideal diode and Hot Swap MOSFET is guaranteed to be greater than 5V when the supply voltages at IN1 and IN2 are between 2.9V and 7V. When the supply voltages at IN1 and IN2 are greater than 7V, the gate drive is guaranteed to be greater than 10V. The gate drive is limited to 14V. An external Zener diode can be used to clamp the potential from the MOSFET's gate to source if the rated breakdown voltage is less than 14V.

The maximum allowable drain-source voltage  $BV_{DSS}$  must be higher than the supply voltage including supply transients as the full supply voltage can appear across the MOSFET. If an input or output is connected to ground, the full supply voltage will appear across the MOSFET. The  $R_{DS(ON)}$  should be small enough to conduct the maximum load current, and also stay within the MOSFET's power rating.

#### **Supply Transient Protection**

When the capacitances at the input and output are very small, rapid changes in current during input or output short-circuit events can cause transients that exceed the 24V absolute maximum ratings of the IN and OUT pins. To minimize such spikes, use wider traces or heavier trace plating to reduce the power trace inductance. Also, bypass locally with a  $10\mu$ F electrolytic and  $0.1\mu$ F ceramic, or alternatively clamp the input with a transient voltage suppressor (Z1, Z2). A  $100\Omega$ ,  $0.1\mu$ F snubber damps the response and eliminates ringing (See Figure 9).

#### Design Example

As a design example for selecting components, consider a 12V system with a 7A maximum load current for the two supplies (see Figure 1).

First, select the appropriate value of the current sense resistor  $R_S$  for the 12V supply. Calculate the sense resistor value based on the maximum load current  $I_{LOAD(MAX)}$  and the lower limit for the current limit sense voltage threshold  $\Delta V_{SENSE(TH)(MIN)}$ .

$$R_{S} = \frac{\Delta V_{SENSE(TH)(MIN)}}{I_{LOAD(MAX)}} = \frac{22.5mV}{7A} = 3.2m\Omega$$

Choose a  $3m\Omega$  sense resistor with a 1% tolerance.

Next, calculate the  $R_{DS(ON)}$  of the ideal diode MOSFET to achieve the desired forward drop at maximum load. Assuming a forward drop,  $\Delta V_{FWD}$  of 30mV across the MOSFET:

$$R_{DS(ON)} \le \frac{\Delta V_{FWD}}{I_{LOAD(MAX)}} = \frac{30mV}{7A} = 4.2m\Omega$$

The SiR158DP offers a good choice with a maximum  $R_{DS(ON)}$  of 1.8m $\Omega$  at  $V_{GS}$  = 10V. The input capacitance  $C_{ISS}$  of the SiR158DP is about 4980pF. Slightly exceeding the 10× recommendation, a 0.1µF capacitor is selected for C2 and C3 at the CPO pins.

Next, verify that the thermal ratings of the selected Hot Swap MOSFET are not exceeded during power-up or an overcurrent fault. Assuming the MOSFET dissipates power due to inrush current charging the load capacitor  $C_L$  at power-up, the energy dissipated in the MOSFET is the same as the energy stored in the load capacitor, and is given by:

$$\mathsf{E}_{\mathsf{CL}} = \frac{1}{2} \bullet \mathsf{C}_{\mathsf{L}} \bullet \mathsf{V}_{\mathsf{IN}}^2$$

For  $C_L = 680\mu$ F, the time it takes to charge up  $C_L$  is calculated as:

$$t_{CHARGE} = \frac{C_{L} \bullet V_{IN}}{I_{INRUSH}} = \frac{680\mu F \bullet 12V}{1A} = 8ms$$

The inrush current is set to 1A by adding capacitance  $C_{HG}$  at the gate of the Hot Swap MOSFET.

$$C_{HG} = \frac{C_{L} \bullet I_{HGATE(UP)}}{I_{INRUSH}} = \frac{680\mu F \bullet 10\mu A}{1A} = 6.8nF$$

Choose a practical value of 10nF for  $C_{HG}$ .

The average power dissipated in the MOSFET is calculated as:

$$P_{AVG} = \frac{E_{CL}}{t_{CHARGE}} = \frac{1}{2} \cdot \frac{680\mu F \cdot (12V)^2}{8ms} = 6W$$

The MOSFET selected must be able to tolerate 6W for 8ms during power-up. The SOA curves of the SiR158DP provide 45W (1.5A at 30V) for 100ms. This is sufficient to satisfy the requirement. The increase in junction temperature due to the power dissipated in the MOSFET is  $\Delta T = P_{AVG} \cdot Zth_{JC}$  where Zth<sub>JC</sub> is the junction-to-case thermal impedance. Under this condition, the SiR158DP data sheet indicates that the junction temperature will increase by 3°C using Zth<sub>JC</sub> = 0.5°C/W (single pulse).

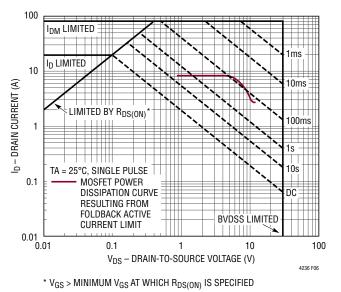

Next, the power dissipated in the MOSFET during an overcurrent fault must be safely limited. The fault timer capacitor ( $C_{FT}$ ) is used to prevent power dissipation in the MOSFET from exceeding the SOA rating during active current limit. A good way to determine a suitable value for  $C_{FT}$  is to superimpose the foldback current limit profile shown in the Typical Performance Characteristics on the MOSFET data sheet's SOA curves.

For the SiR158DP MOSFET, this exercise yields the plot in Figure 6.

Figure 6. SiR158DP SOA with Design Example MOSFET Power Dissipation Superimposed

As can be seen, the LTC4236's foldback current limit profile roughly coincides with the 100ms SOA contour. Since this SOA plot is for an ambient temperature of 25°C only, a maximum fault timer period of much less than 100ms should be considered, such as 10ms or less. Selecting a  $0.1\mu$ F ±10% value for C<sub>FT</sub> yields a maximum fault timer period of 1.75ms which should be small enough to protect the MOSFET during any overcurrent fault scenario.

Next, select the values for the resistive divider at the ON pin that defines the undervoltage threshold of 9.7V for the 12V supply at SENSE<sup>+</sup>. Since the leakage current for the ON pin can be as high as  $\pm 1\mu$ A, the total resistance in the divider should be low enough to minimize the resulting offset error. Calculate the bottom resistor R1 based on the following equation to obtain less than  $\pm 0.2\%$  error due to leakage current.

$$R1 = \left(\frac{V_{0N(TH)}}{I_{1N(LEAK)}}\right) \bullet 0.2\% = \left(\frac{1.235V}{1\mu A}\right) \bullet 0.2\% = 2.4k$$

Choose R1 to be 2k to achieve less than  $\pm 0.2\%$  error and calculating R2 yields:

$$R2 = \left(\frac{V_{IN(UV)}}{V_{ON(TH)}} - 1\right) \bullet R1$$

$$R2 = \left(\frac{9.7V}{1.235V} - 1\right) \bullet 2k = 13.7k$$

It remains to select the values for the FB pin resistive divider in order to set a power good threshold of 10.5V. Keeping in mind the FB pin's  $\pm 1\mu$ A leakage current, choose a value of 2k for the bottom resistor R3. Calculating the top resistor R4 value yields:

$$R4 = \left(\frac{V_{OUT(PG)}}{V_{FB(TH)}} - 1\right) \bullet R3$$

$$R4 = \left(\frac{10.5V}{1.235V} - 1\right) \bullet 2k = 15k$$

The subsequent offset error due to the FB pin leakage current will be less than  $\pm 0.2\%$ .

The final components to consider are a  $0.1\mu$ F bypass (C1) at the INTV<sub>CC</sub> pin and a  $0.1\mu$ F capacitor (C4) connected between the REG and SENSE<sup>+</sup> pins.

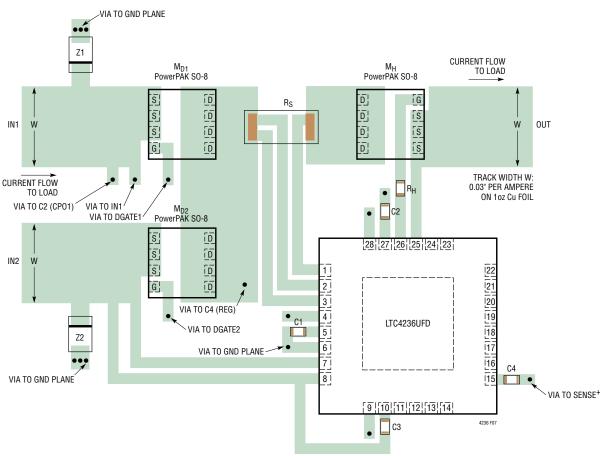

#### **PCB Layout Considerations**

To achieve accurate current sensing, a Kelvin connection for the sense resistor is recommended. The PCB layout should be balanced and symmetrical to minimize wiring errors. In addition, the PCB layout for the sense resistor and the power MOSFET should include good thermal management techniques for optimal device power dissipation. A recommended PCB layout is illustrated in Figure 7.