# **Low Noise Regulated Charge Pump DC-DC** Converter

# **Description**

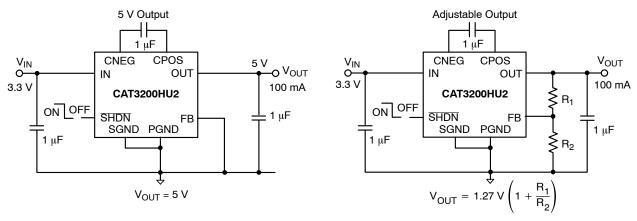

The CAT3200HU2 is a switched capacitor boost converter that delivers a low noise, regulated output voltage. The CAT3200HU2 gives a fixed regulated 5 V output when the FB pin is tied to ground, otherwise it provides an adjustable output using external resistors. The constant frequency 2 MHz charge pump allows small 1 µF ceramic capacitors to be used.

Maximum output loads of up to 100 mA can be supported over a wide range of input supply voltages making the device ideal for battery-powered applications.

A shutdown control input allows the device to be placed in power-down mode, reducing the supply current to less than 1 µA.

In the event of short circuit or overload conditions, the device is fully protected by both foldback current limiting and thermal overload detection. In addition, a soft start, slew rate control circuit limits inrush current during power-up.

The CAT3200HU2 is available in the tiny 8-pad UDF 2 mm x 2 mm package.

## **Features**

- Constant High Frequency (2 MHz) Operation

- Regulated Output Voltage (5 V Fixed or Adjustable)

Low Quiescent Current (1.7 mA Tvp.)

- Soft Start, Slew Rate Control

- Reverse Leakage Protection

- Thermal Overload Shutdown Protection

- Low Value External Capacitors (1 μF)

- Foldback Current Overload Protection

- Shutdown Current less than 1 µA

- 8-pad UDFN 2 mm x 2 mm Package

- These Devices are Pb-Free, Halogen Free/BFR Free and are RoHS Compliant

# **Typical Applications**

- 3 V to 5 V Boost Conversion

- 2.5 V to 3.3 V Boost Conversion

- White LED Driver

- Handheld Portable Devices

# ON Semiconductor®

http://onsemi.com

UDFN-8 **HU2 SUFFIX** CASE 517AW

## MARKING DIAGRAM

CA = Product Name

X = Assembly Location

Y = Production Year (Last Digit)

M = Production Month (1–9, O, N, D)

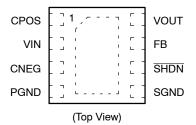

#### **PIN CONNECTIONS**

#### ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 2 of this data sheet.

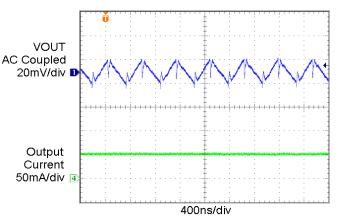

Figure 1. Typical Application Circuits

#### **Table 1. ORDERING INFORMATION**

| Orderable Part Number | Output Voltage     | Package | Lead Finish | Shipping (Note 1) |

|-----------------------|--------------------|---------|-------------|-------------------|

| CAT3200HU2-GT3        | 5 V and Adjustable | UDFN-8  | NiPdAu      | 3,000             |

<sup>1.</sup> For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

# **Table 2. PIN FUNCTION DESCRIPTION**

| Pin No. | Pin Name | Description                                  |

|---------|----------|----------------------------------------------|

| 1       | CPOS     | Positive connection for the flying capacitor |

| 2       | VIN      | Input power supply                           |

| 3       | CNEG     | Negative connection for the flying capacitor |

| 4       | PGND     | Power ground                                 |

| 5       | SGND     | Ground reference for all voltages            |

| 6       | SHDN     | Shutdown control logic input (Active LOW)    |

| 7       | FB       | Feedback to set the output voltage           |

| 8       | VOUT     | Regulated output voltage                     |

|         | Tab      | Connect to ground on PCB                     |

# **Table 3. ABSOLUTE MAXIMUM RATINGS**

| Rating                                                                                | Value       | Unit |

|---------------------------------------------------------------------------------------|-------------|------|

| V <sub>IN</sub> , V <sub>FB</sub> , SHDN, C <sub>NEG</sub> , C <sub>POS</sub> Voltage | -0.6 to +6  | V    |

| V <sub>OUT</sub>                                                                      | -0.6 to +7  | V    |

| V <sub>OUT</sub> Short Circuit Duration                                               | Indefinite  |      |

| Output Current                                                                        | 200         | mA   |

| ESD Protection (HBM)                                                                  | 2000        | V    |

| Junction Temperature Range                                                            | 150         | °C   |

| Storage Temperature Range                                                             | -65 to +160 | °C   |

| Lead Soldering Temperature (10 sec)                                                   | 300         | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

**Table 4. RECOMMENDED OPERATING CONDITIONS**

| Parameter                                                      | Conditions              | Symbol            | Min | Тур | Max | Unit |

|----------------------------------------------------------------|-------------------------|-------------------|-----|-----|-----|------|

| Input Voltage                                                  | 5 V output              | V <sub>IN</sub>   | 2.7 |     | 4.5 | V    |

|                                                                | 3.3 V adjustable output |                   | 2.2 |     | 3.0 | V    |

| C <sub>IN</sub> , C <sub>OUT</sub> , C <sub>FLY</sub> (Note 2) |                         |                   | 1.0 | 2.2 | 4.7 | μF   |

| Load Current                                                   |                         | I <sub>LOAD</sub> |     |     | 100 | mA   |

| Ambient Temperature Range                                      |                         | T <sub>AMB</sub>  | -40 |     | 85  | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

# **Table 5. ELECTRICAL CHARACTERISTICS**

(Recommended operating conditions unless otherwise specified.  $C_{IN}$ ,  $C_{OUT}$ ,  $C_{FLY}$  are 1  $\mu F$  ceramic capacitors and  $V_{IN}$  is set to 3.6 V.)

| Parameter                                  | Conditions                                                                                                                                 | Symbol            | Min  | Тур  | Max            | Units |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|------|----------------|-------|

| Regulated Output                           | $I_{LOAD} \leq 40 \text{ mA}, V_{IN} \geq 2.7 \text{ V}, V_{FB} = 0 \text{ V}$                                                             | V <sub>OUT</sub>  | 4.8  | 5.0  | 5.2            | V     |

|                                            | $I_{LOAD} \le 100 \text{ mA}, V_{IN} \ge 3.1 \text{ V}, V_{FB} = 0 \text{ V}$                                                              |                   |      |      | $\sim$ ( $G$ ) |       |

| Line Regulation                            | $3.1 \text{ V} \leq \text{V}_{\text{IN}} \leq 4.5 \text{ V}, \text{I}_{\text{LOAD}} = 50 \text{ mA},$ $\text{V}_{\text{FB}} = 0 \text{ V}$ | V <sub>LINE</sub> |      | 6    | ,<br>,         | mV    |

| Load Regulation                            | I <sub>LOAD</sub> = 10 mA to 100 mA,<br>V <sub>IN</sub> = 3.6 V, V <sub>FB</sub> = 0 V                                                     | VLOAD             | NEV  | 20   |                | mV    |

| Switching Frequency                        |                                                                                                                                            | Fosc              | 1.3  | 2.0  | 2.6            | MHz   |

| Output Ripple Voltage                      | $I_{LOAD}$ = 100 mA, $V_{OUT}$ = 5 V, $C_{OUT}$ = 1 μF, excluding ESR on $C_{OUT}$ and PCB                                                 | V <sub>R</sub>    | 25   | 30   | 45             | mVp-p |

| Efficiency                                 | I <sub>LOAD</sub> = 50 mA, V <sub>IN</sub> = 3 V, V <sub>OUT</sub> = 5 V                                                                   | 2 P               | ZΔ   | 81   | 85             | %     |

| Ground Current                             | I <sub>LOAD</sub> = 0 mA, SHDN = V <sub>IN</sub>                                                                                           | I <sub>GND</sub>  |      | 1.6  | 4              | mA    |

| Shutdown Input Current                     | I <sub>LOAD</sub> = 0 mA, SHDN = 0 V                                                                                                       | ISHDN             |      |      | 1              | μΑ    |

| FB Voltage                                 | Adjustable output only                                                                                                                     | $V_{FB}$          | 1.22 | 1.27 | 1.32           | V     |

| FB Input Current                           | C REMINEU.                                                                                                                                 | I <sub>FB</sub>   | -50  |      | 50             | nA    |

| Open-Loop Resistance                       | $I_{LOAD} = 100 \text{ mA}, V_{IN} = 3 \text{ V}$                                                                                          | R <sub>OL</sub>   |      | 10   |                | Ω     |

| V <sub>OUT</sub> Turn-on time (10% to 90%) | $I_{LOAD} = 0 \text{ mA}, V_{IN} = 3 \text{ V}$                                                                                            | T <sub>ON</sub>   |      | 0.5  |                | ms    |

| SHDN Logic High Level                      | 1 CAS CAN                                                                                                                                  | V <sub>IH</sub>   | 1.3  |      |                | V     |

| SHDN Logic Low Level                       | 01/25/                                                                                                                                     | $V_{IL}$          |      |      | 0.4            | V     |

| Reverse Leakage into OUT pin               | V <sub>OUT</sub> = 5 V, Shutdown mode, V <sub>IN</sub> = 3.0 V                                                                             | I <sub>ROUT</sub> |      | 15   | 30             | μΑ    |

| Reverse Leakage from IN pin                | V <sub>OUT</sub> = 5 V, Shutdown mode, V <sub>IN</sub> = 3.0 V                                                                             | I <sub>RIN</sub>  |      |      | 1              | μΑ    |

| Short-circuit Output                       | V <sub>OUT</sub> = 0 V                                                                                                                     | I <sub>SC</sub>   |      | 80   |                | mA    |

| Thermal Shutdown                           |                                                                                                                                            | T <sub>SD</sub>   |      | 160  |                | °C    |

| Thermal Hysteresis                         |                                                                                                                                            | T <sub>HYST</sub> |      | 20   |                | °C    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

<sup>2.</sup> Refer to the Application Information section of this datasheet for more details.

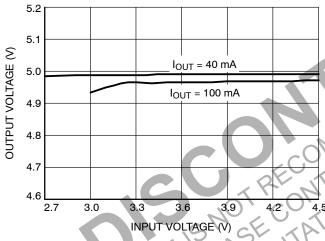

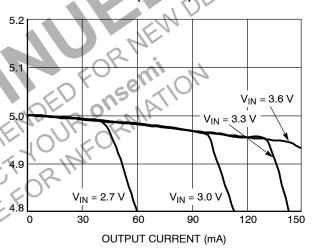

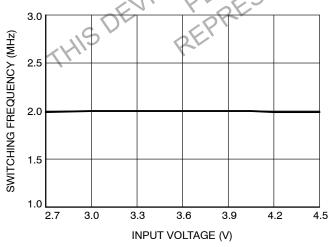

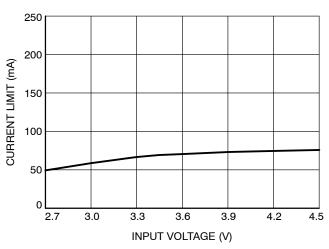

#### TYPICAL PERFORMANCE CHARACTERISTICS

$(V_{IN} = 3.3 \text{ V}, V_{FB} = GND \text{ (5 V output)}, C_{IN} = C_{OUT} = C_{FLY} = 1 \text{ } \mu\text{F}, \text{ [C0805C105K9RACTU]}, T_{AMB} = 25^{\circ}\text{C)}$

OUTPUT VOLTAGE (V)

2.2 (A) 2.0 1.8 1.8 1.6 1.2 2.7 3.0 3.3 3.6 3.9 4.2 4.5 INPUT VOLTAGE (V)

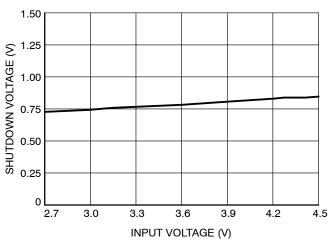

Figure 2. Shutdown Input Threshold vs. Input Voltage

Figure 3. Quiescent Current vs. Input Voltage (No Load)

Figure 4. Output Voltage vs. Input Voltage

Figure 5. Output Voltage vs. Output Current

Figure 6. Oscillator Frequency vs. Input Voltage

Figure 7. Short Circuit Current vs. Input Voltage

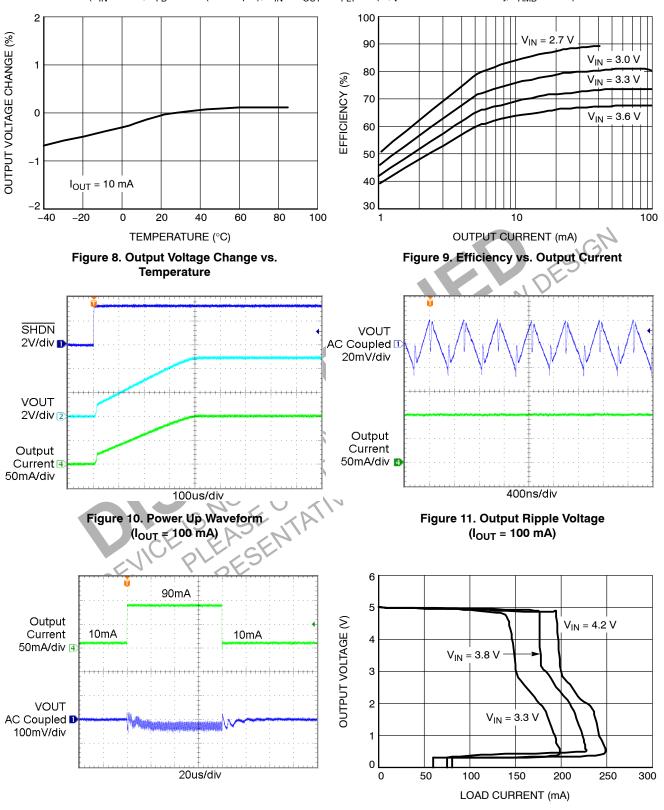

# TYPICAL PERFORMANCE CHARACTERISTICS

$(V_{IN} = 3.3 \text{ V}, V_{FB} = GND \text{ (5 V output)}, C_{IN} = C_{OUT} = C_{FLY} = 1 \text{ } \mu\text{F, [C0805C105K9RACTU]}, T_{AMB} = 25 ^{\circ}\text{C)}$

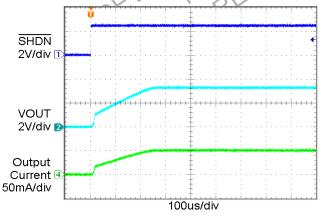

Figure 12. Load Transient Response

Figure 13. Foldback Current Limit

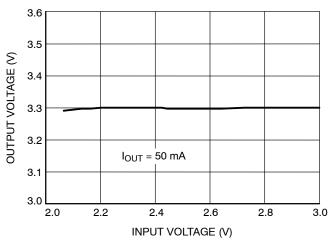

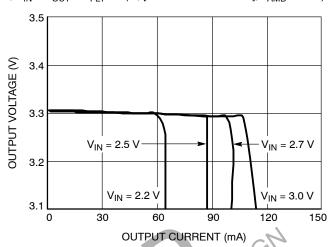

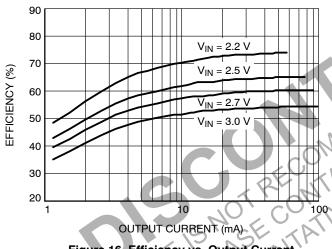

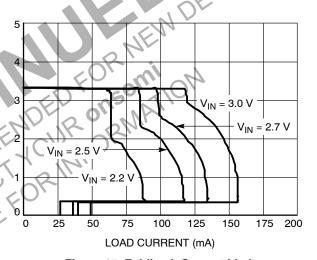

#### TYPICAL PERFORMANCE CHARACTERISTICS

$(V_{IN} = 2.5 \text{ V}, V_{OUT} = 3.3 \text{ V} \text{ (adjustable output)}, R1 = 16 \text{ k}\Omega, R2 = 10 \text{ k}\Omega, C_{IN} = C_{OUT} = C_{FLY} = 1 \text{ }\mu\text{F}, [C0805C105K9RACTU], T_{AMB} = 25^{\circ}\text{C})$

Figure 14. Output Voltage vs. Input Voltage

Figure 15. Output Voltage vs. Output Current

Figure 16. Efficiency vs. Output Current

Figure 17. Foldback Current Limit

Figure 18. Power Up Waveform  $(I_{OUT} = 50 \text{ mA})$

Figure 19. Output Ripple Voltage  $(I_{OUT} = 50 \text{ mA})$

#### **Pin Functions**

VIN is the power supply. During normal operation the device draws a supply current which is almost constant. A very brief interval of non–conduction will occur at the switching frequency. The duration of the non–conduction interval is set by the internal non–overlapping "break–before–make" timing. VIN should be bypassed with a 1  $\mu$ F to 4.7  $\mu$ F low ESR (Equivalent Series Resistance) ceramic capacitor.

For filtering, a low ESR ceramic bypass capacitor (1  $\mu$ F) in close proximity to the IN pin prevents noise from being injected back into the power supply.

**SHDN** is the logic control input (active low) that places the device into shutdown mode. The internal logic is CMOS and the pin does not use an internal pull-down resistor. The SHDN pin should not be allowed to float.

**CPOS, CNEG** pins are the positive and negative connections respectively for the charge pump flying capacitor. A low ESR ceramic capacitor (1  $\mu$ F) should be connected between these pins. During initial power-up it may be possible for the capacitor to experience a voltage reversal and for this reason, avoid using a polarized (tantalum or aluminum) flying capacitor.

**VOUT** is the regulated output voltage to power the load. During normal operation, the device will deliver a train of current pulses to the pin at a frequency of 2 MHz. Adequate filtering on the pin can typically be achieved through the use of a low ESR ceramic bypass capacitor (1  $\mu$ F to 4.7  $\mu$ F) in close proximity to the VOUT pin. The ESR of the output capacitor will directly influence the output ripple voltage.

When the shutdown mode is entered, the output is immediately isolated from the input supply, however, the output will remain connected to the internal feedback resistor network (400 k $\Omega$ ). The feedback network will result in a reverse current of 10  $\mu A$  to 20  $\mu A$  to flow back through the device to ground.

Whenever the device is taken out of shutdown mode, the output voltage will experience a slew rate controlled power-up. Full operating voltage is typically achieved in less than 0.5 ms.

**SGND** is the ground reference for all voltages on the CAT3200HU2.

**FB** is the feedback input pin. An output divider should be connected from VOUT to FB to program the output voltage when used in adjustable output mode. When used in 5 V fixed output mode, connect the FB pin directly to GND.

**PGND** is the power ground.

#### **Device Operation**

The CAT3200HU2 uses a switched capacitor charge pump to boost the voltage at IN to a regulated output voltage. Regulation is achieved by sensing the output voltage through an internal resistor divider (FB pin = GND) and modulating the charge pump output current based on the

error signal. A 2-phase non-overlapping clock activates the charge pump switches. The flying capacitor is charged from the IN voltage on the first phase of the clock. On the second phase of the clock it is stacked in series with the input voltage and connected to VOUT. The charging and discharging the flying capacitor continues at a free running frequency of typically 2 MHz.

In shutdown mode all circuitry is turned off and the CAT3200HU2 draws only leakage current from the VIN supply. VOUT is disconnected from VIN. The \$\overline{SHDN}\$ pin is a CMOS input with a threshold voltage of approximately 0.8 V. The CAT3200HU2 is in shutdown when a logic LOW is applied to the \$\overline{SHDN}\$ pin. The \$\overline{SHDN}\$ pin is a high impedance CMOS input. \$\overline{SHDN}\$ does not have an internal pull–down resistor and should not be allowed to float. It must always be driven with a valid logic level.

# Short-Circuit and Thermal Protection

The CAT3200HU2 has built-in short-circuit current limiting and over temperature protection. During overload conditions, output current is limited to approximately 225 mA. At higher temperatures, or if the input voltage is high enough to cause excessive chip self heating, the thermal shutdown circuit shuts down the charge pump as the junction temperature exceeds approximately 160°C. Once the junction temperature drops back to approximately 140°C, the charge pump is enabled. The CAT3200HU2 will cycle in and out of thermal shutdown indefinitely without latch-up or damage until a short-circuit on VOUT is removed.

#### Programming the CAT3200HU2 Output Voltage (FB Pin)

The CAT3200HU2 version has an internal resistive divider to program the output voltage. The programmable CAT3200HU2 may be set to an arbitrary voltage via an external resistive divider. Since it employs a voltage doubling charge pump, it is not possible to achieve output voltages greater than twice the available input voltage. Figure 20 shows the required voltage divider connection. The voltage divider ratio is given by the formula:

$$\frac{R1}{R2} = \frac{V_{OUT}}{1.27 \, V} - 1$$

Typical values for total voltage divider resistance can range from several  $k\Omega$  up to 1  $M\Omega$ .

Figure 20. Programming the Adjustable Output

#### Application Information

#### **Ceramic Capacitors**

Ceramic capacitors of different dielectric materials lose their capacitance with higher temperature and voltage at different rates. For example, a capacitor made of X5R or X7R material will retain most of its capacitance from -40°C to 85°C whereas a Z5U or Y5V style capacitor will lose considerable capacitance over that range.

Z5U and Y5V capacitors may also have voltage coefficient causing them to lose 60% or more of their capacitance when the rated voltage is applied. When comparing different capacitors it is often useful to consider the amount of achievable capacitance for a given case size rather than discussing the specified capacitance value. For example, over rated voltage and temperature conditions, a 1 μF, 10 V, Y5V ceramic capacitor in an 0603 case may not provide any more capacitance than a 0.22 µF, 10 V, X7R available in the same 0603 case. For many CAT3200HU2 applications these capacitors can be considered roughly equivalent.

#### **Output Ripple**

The output ripple voltage is related to the output capacitor size C<sub>OUT</sub> and ESR (equivalent series resistance) and can be calculated using the formula below:

$$V_{R} = I_{LOAD} / (2 \cdot F_{OSC} \cdot C_{OUT}) + 2 \cdot ESR_{COUT} \cdot I_{LOAD}$$

where F<sub>OSC</sub> is the switching frequency.

#### **Efficiency**

The efficiency is basically set by the ratio between the input voltage V<sub>IN</sub> and the output voltage V<sub>OUT</sub>, and can be calculated using the formula below:

Efficiency [%] =

$$100 \cdot P_{OUT} / P_{IN}$$

=  $100 \cdot V_{OUT} \cdot I_{LOAD} / (V_{IN} \cdot I_{IN})$

where F<sub>OSC</sub> is the switching frequency, and

$$I_{IN} = I_{GND} + 2 \cdot I_{LOAD}$$

If we neglect the Ground current (IGND), then the efficiency is basically equal to:

Efficiency [%]

$$\approx 100 \cdot V_{OUT} / (2 \cdot V_{IN})$$

## **Layout Guidance**

The CAT3200HU2 2 MHz switching frequency requires minimum trace length and impedance for C<sub>IN</sub>, C<sub>OUT</sub>, and C<sub>FLY</sub> capacitors. This can be accomplished by placing these THIS DEVELOPMENT OF THE PRESENTATIVE PRESENT components close to the IC. The CIN capacitor ground connection can connect directly to PGND and a wide, single trace should connect PGND and SGND. COUT should be star-connected to SGND, along with FB resistor network, if

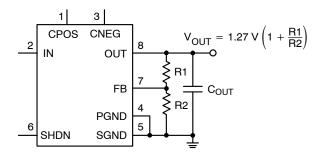

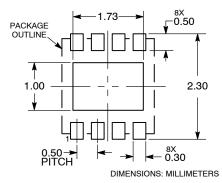

# **UDFN8, 2x2**

**DATE 13 NOV 2015**

#### NOTES:

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. DIMENSION 6 APPLIES TO PLATED TERMINALS AND IS MEASURED BETWEEN 0.15

AND 0.30 MM FROM THE TERMINAL TIP.

- AND U.30 MM FROM THE TERMINAL TIP.

COPLANARITY APPLIES TO THE EXPOSED

PAD AS WELL AS THE TERMINALS.

FOR DEVICE OPN CONTAINING W OPTION,

DETAIL B ALTERNATE CONSTRUCTION IS

|     | MILLIMETERS |      |  |  |  |

|-----|-------------|------|--|--|--|

| DIM | MIN MAX     |      |  |  |  |

| Α   | 0.45        | 0.55 |  |  |  |

| A1  | 0.00        | 0.05 |  |  |  |

| A3  | 0.13        | REF  |  |  |  |

| b   | 0.18        | 0.30 |  |  |  |

| D   | 2.00        | BSC  |  |  |  |

| D2  | 1.50        | 1.70 |  |  |  |

| E   | 2.00        | BSC  |  |  |  |

| E2  | 0.80        | 1.00 |  |  |  |

| е   | 0.50 BSC    |      |  |  |  |

| L   | 0.20        | 0.45 |  |  |  |

| L1  |             | 0.15 |  |  |  |

# **GENERIC MARKING DIAGRAM\***

XX = Specific Device Code

= Date Code

= Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ■", may or may not be present.

#### **RECOMMENDED SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the onsemi Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER: | 98AON34462E | Electronic versions are uncontrolled except when accessed directly from the Document Reposi<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | UDFN8, 2X2  |                                                                                                                                                                                | PAGE 1 OF 1 |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, Onsemi, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="https://www.onsemi.org/bit/Patent-Marking.pdf">www.onsemi.org/bit/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Shoul

#### ADDITIONAL INFORMATION

**TECHNICAL PUBLICATIONS:**

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at www.onsemi.com/support/sales