# **Four-Channel Remote Temperature Sensor**

**MAX31732**

# **General Description**

The MAX31732 is a multi-channel temperature sensor that monitors its own temperature and the temperatures of up to four external diode-connected transistors. A resistance cancellation feature compensates for up to  $300\Omega$  of series resistance between the external thermal diode and the MAX31732, while beta compensation corrects for temperature-measurement errors due to low-beta sensing transistors. The sensor also allows ideality factors between 0.9844 and 1.311.

The MAX31732 offers two open-drain, active-low alarm outputs, ALARM1 and ALARM2. When the measured temperature of a channel crosses the respective primary overtemperature/undertemperature threshold levels, ALARM1 asserts low, and a status bit is set in the corresponding thermal status registers. When the measured temperature of a channel crosses the secondary overtemperature/undertemperature threshold levels, ALARM2 asserts low and a status bit is set in the corresponding thermal status registers. The highest temperature register allows the controller to obtain the temperature of the hottest channel.

A 512-bit nonvolatile memory (NVM) allows the MAX31732 to program the configuration registers during power-up without software/firmware intervention. The NVM also captures the fault temperature for each remote and local channel for further analysis at a later time.

The 2-wire serial interface accepts SMBus protocols (write byte, read byte, send byte, and receive byte) for reading the temperature data and programming the temperature thresholds. Any one of the eight available target addresses can be selected using the address selection input (ADD), which can be connected to ground or connected to a grounded resistor.

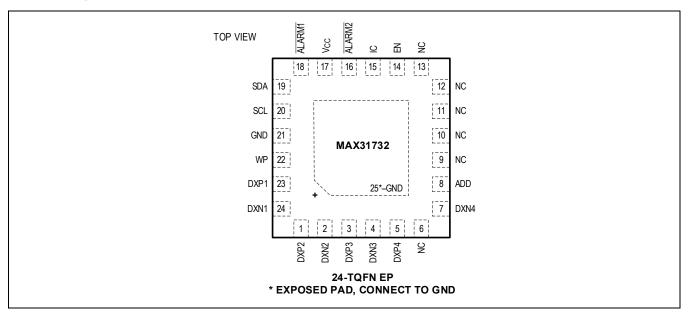

The is specified over the -40°C to +125°C operating temperature range and with a 3.0V to 3.6V input supply range. MAX31732 is available in a 24-pin, 4mm x 4mm TQFN package.

# **Applications**

- Temperature Measurement of On-Chip CPU, ASIC, SOC, or FPGA diodes or remote discrete diodes

- Industrial-Thermal Management

#### **Features**

- One Local and Four Remote Temperature-Sensing Channels

- ±1°C Remote Temperature-Measurement Accuracy (-40°C to +125°C)

- -64°C to +150°C Remote Temperature-Measurement Range

- Up to  $300\Omega$  Resistance Cancellation for Remote Channels

- Compensation for Low Beta Transistors

- 12 Bit. 0.0625°C Resolution

- Two Programmable Alarm Temperature Thresholds

- Eight Selectable Target Addresses

- Flexible I<sup>2</sup>C/SMBus Interfaces to a Variety of Microcontrollers

- Ideality Factor of up to 1.311

- NVM Facilitates Configuration and Fault Logging

Ordering Information appears at end of data sheet.

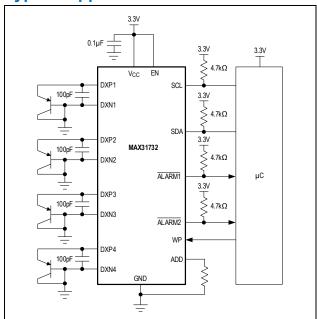

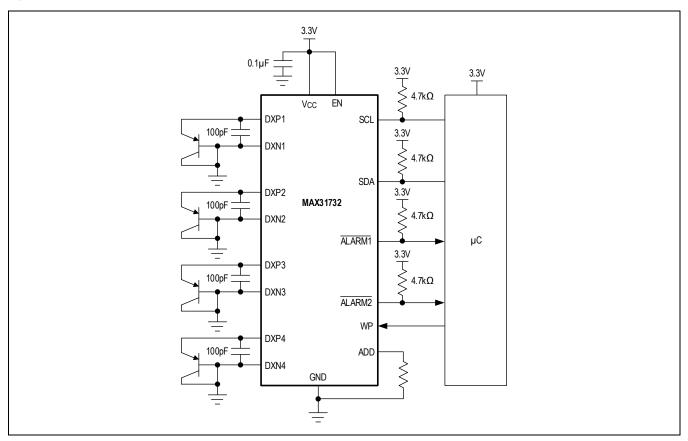

# **Typical Application Circuit**

19-101906; Rev 1; 2/25

# **TABLE OF CONTENTS**

| General Description                                                | 1  |

|--------------------------------------------------------------------|----|

| Applications                                                       | 1  |

| Features                                                           | 1  |

| Typical Application Circuit                                        | 1  |

| Absolute Maximum Ratings                                           | 4  |

| Package Information                                                | 4  |

| Package Information (continued)                                    | 5  |

| Electrical Characteristics                                         | 6  |

| Timing Diagrams                                                    | 7  |

| Typical Performance Characteristics                                | 8  |

| Pin Configurations                                                 | 9  |

| Pin Descriptions                                                   | 9  |

| Functional Diagram                                                 | 10 |

| Detailed Description                                               | 11 |

| Overview                                                           | 11 |

| ADC Conversion Sequence                                            | 11 |

| Series-Resistance Cancellation                                     | 11 |

| Low Power Mode                                                     | 11 |

| Enable Input (EN)                                                  | 11 |

| Write-Protect Input (WP)                                           | 12 |

| I <sup>2</sup> C/SMBus Digital Interface                           | 12 |

| SRAM Register Map                                                  | 14 |

| Temperature Measurement (Address = 0x02 to 0x0B)                   | 18 |

| Extended Temperature Measurement                                   | 19 |

| Temperature Channel Enable Register (Address = 0x0E)               | 20 |

| Highest Temperature Registers (Address = 0x45 and 0x46)            | 20 |

| Highest Temperature Enable Register (Address = 0x1A)               | 21 |

| Reference Temperature Registers (Address = 0x2F to 0x38)           | 21 |

| Overtemperature Threshold Registers                                | 22 |

| (Primary Address = 0x1D to 0x26, Secondary Address = 0x29 to 0x2D) | 22 |

| Undertemperature Threshold Registers                               | 23 |

| (Primary Address = 0x27 to 0x28, Secondary Address = 0x2E)         | 23 |

| Status Registers                                                   | 23 |

| Diode Fault Detection (Address =0x44)                              | 26 |

| Configuration Registers                                            | 27 |

| Alarm Outputs                                                      | 28 |

| Alarm Output Mask Registers (Address = 0x1B and 0x1C)              | 29 |

# Four-Channel Remote Temperature Sensor

| Effect of Ideality Factor                        | 30 |

|--------------------------------------------------|----|

| Beta Compensation                                | 31 |

| Noise Filter                                     | 32 |

| Custom Offset Register                           | 33 |

| Multi-Time Programmable Nonvolatile Memory (MTP) | 34 |

| Accessing MTP Registers                          | 37 |

| Applications Information                         | 39 |

| Reading MTP Registers                            | 39 |

| Programming MTP Registers                        | 39 |

| MTP Multi-Byte Configuration Store               | 39 |

| MTP Single Word Configuration Store              | 39 |

| Programming User Software Revision Registers     | 39 |

| Power-Up Process                                 | 39 |

| MTP Fault Logging Registers                      | 40 |

| On-Demand Loading                                | 40 |

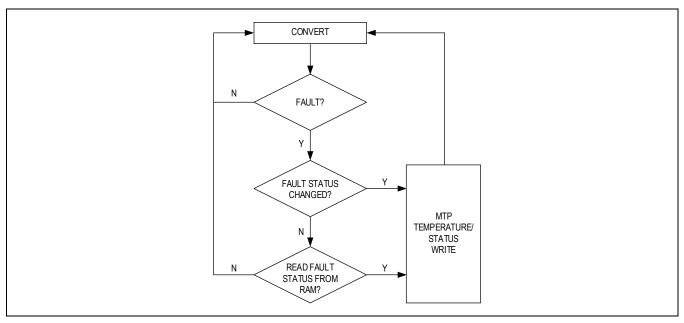

| MTP Temperature and Status recording             | 41 |

| Avoiding MTP Conflicts                           | 42 |

| Clearing MTP fault login registers               | 42 |

| Setting Overtemperature Limits                   | 42 |

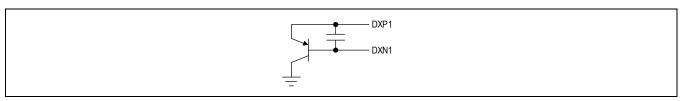

| Discrete Remote Diodes                           | 42 |

| Unused Diode Channels                            | 43 |

| Thermal Mass                                     | 43 |

| ADC Noise Filtering                              | 43 |

| Typical Application Circuit                      | 45 |

| Ordering Information                             | 15 |

# **Absolute Maximum Ratings**

| $V_{CC}$ , | SCL,       | SDA,        | ALARM1,            | ALARM2,                  | ADD,     | Operating Temperature Range       | 40°C to +125°C |

|------------|------------|-------------|--------------------|--------------------------|----------|-----------------------------------|----------------|

| WP, EN     | l          |             |                    | 0.3V                     | to 3.7V  | Junction Temperature              | +150°C         |

| DXP 1,     | 2, 3, 4 an | d DXN 1,    | 2, 3, 4            | 0.3V to V <sub>C</sub> ( | c + 0.3V | Storage Temperature Range         | 65°C to +150°C |

| ESD Pr     | otection ( | All Pins, F | luman Body M       | lodel)                   | 2kV      | Lead Temperature (soldering, 10s) | +300°C         |

|            |            |             | ation $(T_A = +7)$ |                          |          | Soldering Temperature (reflow)    | +260°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

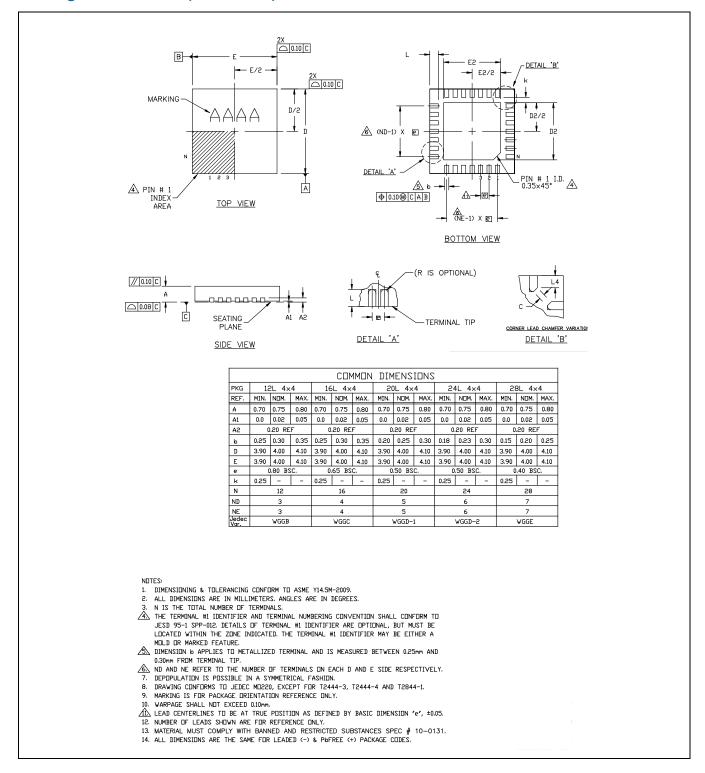

# **Package Information**

| Package Code                                               | T2444+4C             |

|------------------------------------------------------------|----------------------|

| Outline Number                                             | <u>21-0139</u>       |

| Land Pattern Number                                        | 90-0022              |

| Thermal Resistance, Single Layer Board:                    |                      |

| Junction-to-Ambient (θ <sub>JA</sub> )                     | 48°C/W               |

| Junction-to-Case Thermal Resistance $(\theta_{\text{JC}})$ | 3°C/W                |

| Thermal Resistance                                         | e, Four Layer Board: |

| Junction-to-Ambient (θ <sub>JA</sub> )                     | 36°C/W               |

| Junction-to-Case Thermal Resistance $(\theta_{JC})$        | 3°C/W                |

For the latest package outline information and land patterns (footprints), go to Packaging Index. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>Thermal Characterization of IC Packages</u>.

# **Package Information (continued)**

# **Electrical Characteristics**

$(3.0 \text{V} \le \text{V}_{CC} \le 3.6 \text{V} = \text{Power Supply Voltage}, T_{A} = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C} = \text{Ambient Temperature}. All specifications are subject to change.)}$

| PARAMETER                                        | SYMBOL                 | CONI                                                                      | DITIONS                                  | MIN  | TYP    | MAX  | UNITS             |

|--------------------------------------------------|------------------------|---------------------------------------------------------------------------|------------------------------------------|------|--------|------|-------------------|

| Supply Voltage                                   | V <sub>CC</sub>        |                                                                           |                                          | 3    |        | 3.6  |                   |

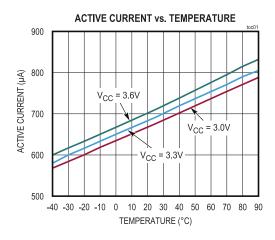

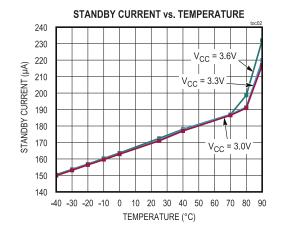

| Shutdown Supply<br>Current                       | I <sub>SD</sub>        | Shutdown: EN = 0V                                                         | ,                                        |      | 175    |      | μA                |

| Active Supply Current                            | $I_{Q}$                | Operating, β compe                                                        | nsation disabled                         |      | 700    | 1200 | μΑ                |

| POR Threshold                                    | $V_{POR}$              | V <sub>CC</sub> Falling Edge                                              |                                          |      | 2.6    | 2.8  | V                 |

| POR Threshold<br>Hysteresis                      |                        |                                                                           |                                          |      | 125    |      | mV                |

| Temperature Resolution                           |                        |                                                                           |                                          |      | 0.0625 |      | °C                |

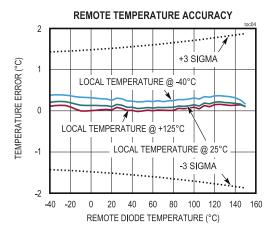

| Remote Temperature<br>Accuracy                   |                        | T <sub>A</sub> = -40°C to<br>+125°C, T <sub>RJ</sub> =<br>-40°C to +150°C | 3 sigma w/<br>diodes batch<br>calibrated | -2   | ±1     | 2    | °C                |

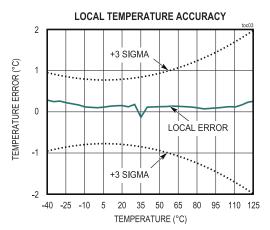

| Local Temperature<br>Accuracy                    |                        | T <sub>A</sub> = -40°C to<br>+125°C ( <u>Note 4</u> )                     | 3 sigma                                  | -2   |        | 2    | °C                |

| Temperature<br>Measurement Noise                 |                        | T <sub>A</sub> = -40°C to<br>+125°C                                       | No Filtering                             |      | 0.25   |      | °C <sub>RMS</sub> |

| Temperature Hysteresis                           |                        | Comparator Mode (                                                         | Only                                     |      | 2      |      | °C                |

| Conversion Time Per                              |                        | β compensation dis                                                        | abled                                    |      |        | 100  | ms                |

| Channel                                          |                        | β compensation en                                                         | abled                                    |      |        | 150  | 1115              |

| Conversion Time for all                          |                        | β compensation dis                                                        | abled                                    |      |        | 450  | ms                |

| the channels                                     |                        | β compensation ena                                                        | abled                                    |      |        | 700  | 1115              |

| Remote-Diode Source                              | I <sub>RJ</sub>        | High Level                                                                |                                          | 200  |        |      |                   |

| Current                                          | 'RJ                    | Low Level                                                                 |                                          |      | 12     |      | μΑ                |

| DVN# Piec Voltage                                |                        | β compensation dis                                                        | abled                                    |      |        | 0.3  | - v               |

| DXN# Bias Voltage                                |                        | β compensation en                                                         | abled                                    |      | 0.73   | 1.0  | V                 |

| ALARM1, ALARM2                                   | $V_{OL}$               | I <sub>SINK</sub> = 1 mA                                                  |                                          |      |        | 100  | mV                |

| Output Low Voltage                               | *OL                    | I <sub>SINK</sub> = 6 mA                                                  |                                          |      |        | 300  | IIIV              |

| EN, WP, SCL SDA,<br>ADD Input Leakage<br>Current | I <sub>LEAK</sub>      |                                                                           |                                          |      | 0.01   | 1    | μΑ                |

| Output High Leakage<br>Current                   |                        | ALARM1, ALARM2                                                            | , SDA                                    |      |        | 1    | μA                |

| MTP Programming Time                             | T <sub>MTP</sub>       | 2 Bytes (Note 5)                                                          |                                          |      |        | 25   | ms                |

| Total MTP Programming Time                       | T <sub>MTP_TOTAL</sub> | ( <u>Note 1</u> )                                                         |                                          |      |        | 650  | ms                |

| Total MTP Loading<br>Time                        | T <sub>MTP_LOAD</sub>  | ( <u>Note 5</u> )                                                         |                                          |      |        | 10   | ms                |

| MTP Write Cycles                                 |                        | T <sub>A</sub> = +85°C ( <u>Note 2</u> )                                  | )                                        | 1000 |        |      | cycles            |

| LOGIC INPUT (EN, WP, S                           | SDA, SCL)              |                                                                           |                                          |      |        |      |                   |

| Input Voltage Low                                | $V_{IL}$               |                                                                           |                                          |      |        | 0.4  | V                 |

| Input Voltage High                               | $V_{IH}$               |                                                                           |                                          | 1.4  |        |      |                   |

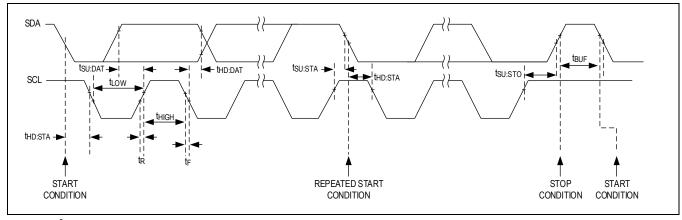

| I <sup>2</sup> C/SMBus-COMPATIBL                 | E TIMING               |                                                                           |                                          |      |        |      |                   |

| Serial-Clock Frequency                           | f <sub>CLK</sub>       |                                                                           |                                          |      |        | 400  | kHz               |

|                                                  |                        |                                                                           |                                          |      |        |      |                   |

$(3.0 \text{V} \le \text{V}_{CC} \le 3.6 \text{V} = \text{Power Supply Voltage}, T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C} = \text{Ambient Temperature}. All specifications are subject to change.)}$

| 11010 0                                               |                      |                                                        |     |     |     |       |

|-------------------------------------------------------|----------------------|--------------------------------------------------------|-----|-----|-----|-------|

| PARAMETER                                             | SYMBOL               | CONDITIONS                                             | MIN | TYP | MAX | UNITS |

| Bus Free Time Between<br>STOP and START<br>Conditions | t <sub>BUF</sub>     | f <sub>CLK</sub> = 400kHz                              | 1.3 |     |     | μs    |

| Repeated START Condition Setup Time                   | t <sub>SU:STA</sub>  |                                                        | 0.6 |     |     | μs    |

| START Condition Setup<br>Time                         |                      | 90% of SCL to 90% of SDA,<br>f <sub>CLK</sub> = 400kHz | 0.6 |     |     | μs    |

| START Condition Hold<br>Time                          | thd:STA              | 90% of SDA to 90% of SCL,<br>f <sub>CLK</sub> = 400kHz | 0.6 |     |     | μs    |

| STOP Condition Setup<br>Time                          | t <sub>SU:STO</sub>  | 90% of SCL to 90% of SDA,<br>f <sub>CLK</sub> = 400kHz | 0.6 |     |     | μs    |

| Clock Low Period                                      | t <sub>LOW</sub>     | 10% to 10%                                             | 1   |     |     | μs    |

| Clock High Period                                     | <sup>t</sup> HIGH    | 90% to 90%                                             | 1   |     |     | μs    |

| Data-In Hold Time                                     | t <sub>HD:DAT</sub>  |                                                        | 0.3 |     |     | μs    |

| Data-In Setup Time                                    | t <sub>SU:DAT</sub>  |                                                        | 100 |     |     | ns    |

| Receive Clock/Data<br>Rise Time                       | t <sub>R</sub>       |                                                        |     |     | 300 | ns    |

| Receive Clock/Data Fall Time                          | t <sub>F</sub>       |                                                        |     |     | 300 | ns    |

| Pulse Width of Spike<br>Suppressed                    | t <sub>SP</sub>      |                                                        | 0   |     | 50  | ns    |

| Bus Timeout                                           | <sup>t</sup> TIMEOUT |                                                        | 25  |     | 45  | ms    |

- **Note 1:** The MTP memory programming temperature range is -40°C to +85°C.

- Note 2: Guaranteed by design.

- **Note 3:** All devices are production tested at T<sub>A</sub> = 25°C. Specifications over temperature limits are guaranteed by design. Typical values are not guaranteed.

- Note 4: Guaranteed by design and oil bath characterization. Oil bath QA sampling was done at 25°C.

- Note 5: Guaranteed by design and bench correlation.

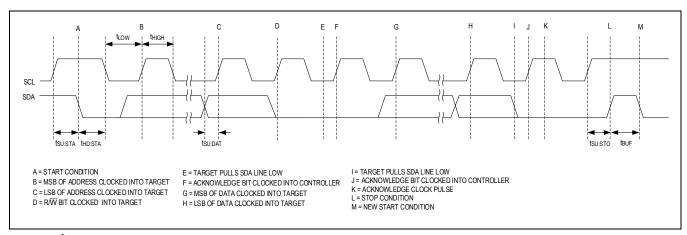

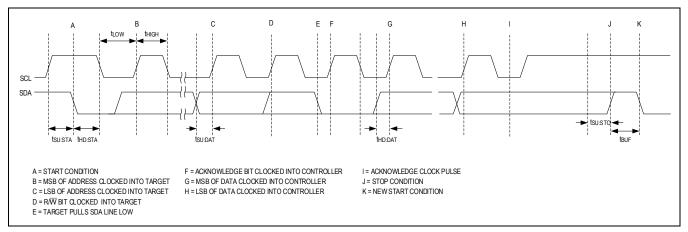

# **Timing Diagrams**

Figure 1. I<sup>2</sup>C/SMBus Timing Diagram

# **Typical Performance Characteristics**

$T_A = 25$ °C, unless otherwise noted.

# **Pin Configurations**

# **Pin Descriptions**

| PIN                     | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                             |

|-------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                       | DXP2   | Combined Current Source and Anode Input for Channel 2 Remote Diode. Connect DXP2 to the anode of a remote-diode-connected, temperature-sensing transistor. Leave DXP2 unconnected or connect to DXN2 if the channel 2 remote diode is not used. Connect a 100pF capacitor between DXP2 and DXN2 for noise filtering. |

| 2                       | DXN2   | Cathode Input for Channel 2 Remote Diode. Connect the DXN2 pin to GND and the negative input of the sensor, except in the case of a transistor where base-current compensation is used (connect DXN2 to the base of the transistor).                                                                                 |

| 3                       | DXP3   | Combined Current Source and Anode Input for Channel 3 Remote Diode. Connect DXP3 to the anode of a remote-diode-connected, temperature-sensing transistor. Leave DXP3 unconnected or connect to DXN3 if the channel 3 remote diode is not used. Connect a 100pF capacitor between DXP3 and DXN3 for noise filtering. |

| 4                       | DXN3   | Cathode Input for Channel 3 Remote Diode.  Connect the DXN3 pin to GND and the negative input of the sensor except in the case of a transistor where the base-current compensation is used (connect DXN3 to the base of the transistor).                                                                             |

| 5                       | DXP4   | Combined Current Source and Anode Input for Channel 4 Remote Diode. Connect DXP4 to the anode of a remote-diode-connected, temperature-sensing transistor. Leave DXP4 unconnected or connect to DXN4 if the channel 4 remote diode is not used. Connect a 100pF capacitor between DXP4 and DXN4 for noise filtering. |

| 6, 9, 10,<br>11, 12, 13 | NC     | No Connection. Connect to other NCs or leave unconnected.                                                                                                                                                                                                                                                            |

| 7                       | DXN4   | Cathode Input for Channel 4 Remote Diode. Connect the DXN4 pin to GND and the negative input of the sensor except in the case of a transistor where the base-current compensation is used (connect DXN4 to the base of the transistor).                                                                              |

| 8                       | ADD    | Address-Select Input. Sampled at power-up. One of the eight possible addresses can be selected by connecting ADD to GND.                                                                                                                                                                                             |

| 14                      | EN     | Enable Input. Drive EN high to enable the MAX31732. Drive EN low to place the MAX31732 in shutdown mode. In shutdown mode, DXN# and DXP# are high-impedance.                                                                                                                                                         |

| 15                      | IC     | Internally Connected. IC is internally connected to $V_{CC}$ . Connect IC to $V_{CC}$ or leave unconnected.                                                                                                                                                                                                          |

| 16                      | ALARM2 | Active-Low, Open-Drain Secondary Overtemperature/Undertemperature Alarm Output. ALARM2 can also be used as an SMBus alert output by setting the device to interrupt mode using the Configuration                                                                                                                     |

|    |          | register. When enabled, the pin asserts low when the temperature of any channel goes beyond the secondary programmed thresholds.                                                                                                                                                                                     |

|----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17 | $V_{CC}$ | Supply Voltage Input. Bypass to GND with a 0.1µF capacitor very close to the device.                                                                                                                                                                                                                                 |

| 18 | ALARM1   | Active-Low, Open-Drain Primary Overtemperature/Undertemperature Output. ALARM1 can also be used as an SMBus alert output by setting the device to interrupt mode using the Configuration register. When enabled, the pin asserts low when the temperature of any channel goes beyond a primary programmed threshold. |

| 19 | SDA      | I <sup>2</sup> C/SMBus Serial-Data Input/Output. Connect SDA to a pullup resistor.                                                                                                                                                                                                                                   |

| 20 | SCL      | I <sup>2</sup> C/SMBus Serial-Clock Input. Connect SCL to a pullup resistor.                                                                                                                                                                                                                                         |

| 21 | GND      | Ground.                                                                                                                                                                                                                                                                                                              |

| 22 | WP       | Active-High Write Protect Input. Drive WP high to disable writing to volatile and nonvolatile memory.  Drive WP low to enable writing to volatile and nonvolatile memory.                                                                                                                                            |

| 23 | DXP1     | Combined Current Source and Anode Input for Channel 1 Remote Diode. Connect DXP to the anode of a remote-diode-connected, temperature-sensing transistor. Leave DXP1 unconnected or connect to DXN1 if the channel 1 remote diode is not used. Connect a 100pF between DXP1 and DXN1 for noise filtering.            |

| 24 | DXN1     | Cathode Input for Channel 1 Remote Diode. Connect the DXN1 pin to GND and the negative input of the sensor except in the case of a transistor where the base-current compensation is used (connect DXN1 to the base of the transistor).                                                                              |

| 25 | GND      | Exposed Pad. Connect to GND.                                                                                                                                                                                                                                                                                         |

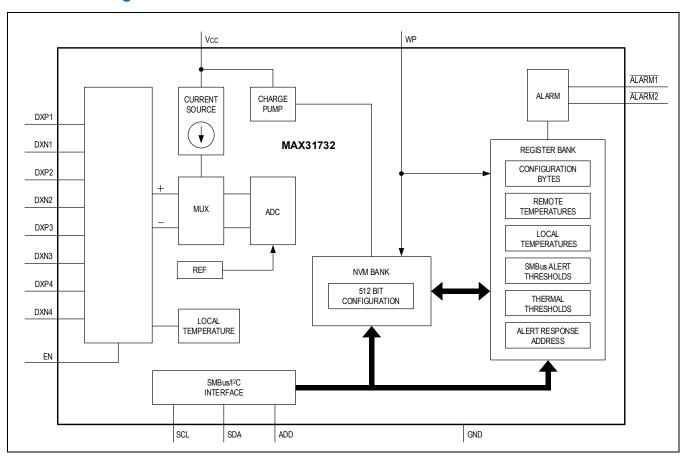

# **Functional Diagram**

# **Detailed Description**

#### Overview

The MAX31732 is a precision temperature monitor that features one local and four remote temperature-sensing channels with programmable Overtemperature/Undertemperature thresholds for each channel. Each remote temperature channel is independently programmable to a custom ideality factor between 0.9844 and 1.311.

Communication with the device is achieved through the I<sup>2</sup>C/SMBus-compatible serial interface and the alarm outputs, ALARM1 and ALARM2. ALARM1 asserts low when the temperature of any channel exceeds the software-programmed temperature thresholds in the *Primary Threshold Limit* registers. ALARM2 asserts low when the temperature of any channel exceeds the software-programmed temperature thresholds in the *Secondary Threshold Limit* registers. ALARM1 and ALARM2 normally operate in comparator mode and can be connected to a fan, system shutdown, or other thermal-management circuitry. Alarm outputs can also operate in interrupt mode to serve as an SMBus alert interrupt.

The MAX31732 includes a 512-bit multi-time programmable nonvolatile memory (MTP) that helps facilitate device configuration during power-up or during normal operation if desired. During the power-up process, when V<sub>CC</sub> exceeds the POR threshold voltage of 2.6V (typ), all configuration registers from the MTP are loaded into their respective registers in SRAM. The fault-logging registers in the MTP memory help preserve temperature fault data and the status bit for the channel that measures temperature outside of the programmed undertemperature and overtemperature threshold limits in the *Primary Threshold Limit* registers (0x1D–0x28) in *SRAM Register Map*.

# **ADC Conversion Sequence**

When all channels are active, the MAX31732 measures the temperature on remote channel 1, followed by remote channel 2, remote channel 3, remote channel 4, and the local channel. The conversion result for each enabled channel is stored in the temperature data register (0x02–0x0B) in SRAM. No conversion can be performed on any channel with the conditions listed below:

- No diode connected between DXP# and DXN# inputs

- DXP# and DXN# are shorted together

- DXP# and DXN# are shorted to V<sub>CC</sub>

- DXP# is shorted to GND (DXN# shorted to GND can also be enabled)

- Remote or local channel is not enabled in the Temperature Enable Register, 0x0E (SRAM)

- Beta Compensation is enabled, and the measured beta is less than 0.09 (Low Beta Fault)

#### **Series-Resistance Cancellation**

The series resistance of remote diodes can cause temperature measurement errors when used with conventional remote temperature sensors. The MAX31732 offers an always-on series-cancellation feature for remote channels 1–4 that eliminates the effect of diode series resistance and interconnection resistance. The cancellation range is from  $0\Omega$  to  $300\Omega$ .

#### **Low Power Mode**

Enter software-standby mode by setting the STOP bit to 1 in the Configuration1 register. Software-standby mode disables the ADC and reduces the supply current to approximately 150µA. During software standby, data is retained in memory and the bus interface is active and listening for commands. If a START condition is recognized, activity on the bus causes the supply current to increase. If a standby command is received while a conversion is in progress, the conversion cycle is finished, then the device enters shutdown, and the temperature registers are updated.

#### **Enable Input (EN)**

EN is an active-high logic-level input. When EN is pulled low, the following is true:

- The remote channel inputs (DXP# and DXN#) are forced into high-impedance mode.

- The internal ADC is disabled, and the current conversion is interrupted.

- The I<sup>2</sup>C/SMBus interface remains active to provide access to device registers.

- ALARM1 and ALARM2 outputs are disabled and pulled high through the external pull-up resistors.

# Write-Protect Input (WP)

WP is an active-high logic-level input that write-protects the configuration registers in the MTP and the volatile SRAM when pulled high. Drive WP low to disable the write-protect mode and allow updates to device configuration registers through the I<sup>2</sup>C/SMBus interface. During write-protect mode, the I<sup>2</sup>C/SMBus communication interface can perform read operation only.

# I<sup>2</sup>C/SMBus Digital Interface

The device is I<sup>2</sup>C/SMBus 2.0 compatible and supports four standard SMBus protocols: write byte, read byte, send byte, and receive byte, as well as block reads and writes (See <u>Figure 2</u>). The shorter receive-byte protocol allows quicker transfers, provided that the correct register was previously selected by a read-byte instruction. Use caution with the shorter protocols in multi-controller systems since a second controller could overwrite the register byte without informing the first controller. <u>Figure 3</u> is the SMBus write timing diagram, and <u>Figure 4</u> is the SMBus read timing diagram. I<sup>2</sup>C burst read is limited to 16 data bytes for registers 0x0E and above. When reading back from the remote or local temperature or status registers (0x02 to 0x0D), the I<sup>2</sup>C burst read is limited to 2 bytes (LSB register followed by MSB register for a given sensor channel).

The **write-byte** format consists of the controller transmitting the target address, followed by the address for the targeted register, followed by the 8 bits of data to be written to the targeted register. To write multiple bytes to two or more contiguous registers, write a new byte after each ACK. The register address then increments after each byte is written. End the transaction with a STOP condition.

The **read-byte** format consists of the controller transmitting the target address followed by the address for the register to be read. The controller then begins a new transaction by sending the target address again, after which the target returns the data from the selected register. To read multiple bytes from two or more contiguous registers, continue reading after each ACK. The register address then increments after each byte is read. Conclude the overall transaction with a NACK and a STOP condition.

When the MSB byte of a 2-byte temperature value is read, the device prevents updates of the second byte's contents until the second byte has been read. If the second byte has not been read within an SMBus timeout period (nominally 35ms), it is again allowed to update.

The **send-byte** format can be used to transmit a register address without a transfer of data. It consists of the controller transmitting the target address followed by the address of the targeted register.

The **receive-byte** format can be used to read data from a register that was previously selected. It consists of the controller transmitting the target address, after which the target returns the data from the register that was previously selected. After this command completes, the address pointer does not increment.

| S                                   | ADDRESS                                                                | WR                                    | ACK                      | REGIST                                                     | TER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ACK                                     | D          | ATA                           | ACK                           | P                            | EC                            | ACK    | Р                  |                                     |                                     |                                 |             |        |          |                      |      |      |

|-------------------------------------|------------------------------------------------------------------------|---------------------------------------|--------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------|-------------------------------|-------------------------------|------------------------------|-------------------------------|--------|--------------------|-------------------------------------|-------------------------------------|---------------------------------|-------------|--------|----------|----------------------|------|------|

|                                     | 7 BITS                                                                 |                                       | 0                        | 8 BIT                                                      | S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                         | 8          | BITS                          |                               | 8 1                          | BITS                          |        |                    |                                     |                                     |                                 |             |        |          |                      |      |      |

| ) CHIP-S                            | ADDRESS: EQU<br>SELECT LINE C<br>E WRITE-BYTE                          | OF A 3-\                              | WIRE IN                  | ITERFAC                                                    | E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SE                                      | TBYT       | HE COM                        | MAND E                        | SYTE (T                      | THE REG<br>TO SETT<br>SAMPLIN | HRESHO | ,                  |                                     |                                     |                                 |             |        |          |                      |      |      |

| S                                   | ADDRESS                                                                | WR                                    | ACK                      | REGIS                                                      | TER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ACK                                     | D          | ATA                           | ACK                           |                              |                               |        |                    |                                     | DATA                                | ACK                             | (           | DATA   |          | ACK                  |      |      |

|                                     | 7 BITS                                                                 | 0                                     |                          | 8 BIT                                                      | S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                         | 8          | BITS                          |                               |                              |                               |        |                    | 8                                   | BITS                                |                                 |             | 8 BITS |          |                      |      |      |

|                                     |                                                                        |                                       | D                        | ATA                                                        | ACK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                         |            | Τ.                            |                               |                              | DATA                          | ACK    |                    | DATA                                | ACK                                 |                                 | PEC         | A      | ск       | Р                    |      |      |

|                                     |                                                                        |                                       | 8 1                      | BITS                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |            |                               |                               |                              | 8 BITS                        |        | 8                  | BITS                                |                                     | 8                               | BITS        |        |          |                      |      |      |

| FAD-BY                              | TE FORMAT                                                              |                                       |                          |                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |            |                               |                               |                              |                               |        |                    |                                     |                                     |                                 |             |        |          |                      |      |      |

|                                     |                                                                        |                                       |                          |                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |            |                               |                               |                              |                               |        |                    |                                     |                                     |                                 |             |        |          |                      |      |      |

| S                                   | ADDRESS                                                                | WR                                    | ACK                      | REGIS                                                      | TER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ACK                                     | S          | ADDF                          | RESS                          | RD                           | ACK                           | DATA   | ١                  | PE                                  | EC N                                | NACK                            | Р           |        |          |                      |      |      |

| S<br>ARGET A                        | ADDRESS 7 BITS ADDRESS:                                                | WR<br>0                               | R                        | 8 BIT                                                      | S<br>BYTE:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SELEC                                   | TS         | 7 BI                          |                               | 1                            |                               | BIT:   | 6                  | 8 B                                 | ITS E: READS                        |                                 |             |        |          |                      |      |      |

| S<br>ARGET A<br>QUIVALE<br>ELECT L  | ADDRESS 7 BITS  ADDRESS: ENT TO CHIP LINE E READ-BYTE I                | 0 O                                   | RI<br>W<br>RI            | 8 BIT<br>EGISTER<br>HICH REGEADING F                       | BYTE:<br>GISTEF<br>ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SELEC<br>R YOU                          | CTS<br>ARE | 7 BI<br>TARG<br>REPE<br>IN DA | ITS<br>GET ADI<br>EATED I     | 1<br>DRESS<br>DUE TO         | :<br>D CHANG<br>ECTION        | 8 BIT  | DAT<br>THE<br>THE  | 8 B<br>A BYTE<br>E REGIS<br>E COMM  | ITS E: READS BTER SET IAND BYT      | FROM<br>BY                      | 1           |        |          | DAT                  |      | 401/ |

| S<br>ARGET A<br>QUIVALE<br>ELECT L  | ADDRESS 7 BITS  ADDRESS: ENT TO CHIP LINE E READ-BYTE I ADDRESS        | 0<br>F <b>ORMA</b><br>WR              | RI<br>W<br>RI            | 8 BIT<br>EGISTER<br>HICH REG<br>EADING F                   | BYTE:<br>GISTEF<br>FROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SELEC                                   | TS         | 7 BI TARG REPE IN DA          | GET ADI<br>EATED I<br>ATA FLC | 1 DRESS DUE TO               | :<br>CHANG                    | 8 BIT  | DAT<br>THE<br>THE  | 8 B<br>A BYTE<br>E REGIS<br>E COMM  | ITS E: READS STER SET               | FROM<br>BY<br>E                 | ATA         | ACI    | <        | DAT                  | _    | ACK  |

| S<br>ARGET A<br>QUIVALE<br>ELECT L  | ADDRESS 7 BITS  ADDRESS: ENT TO CHIP LINE E READ-BYTE I                | 0 O                                   | RI<br>W<br>RI            | 8 BIT<br>EGISTER<br>HICH REGEADING F                       | BYTE:<br>GISTEF<br>FROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SELEC<br>R YOU                          | CTS<br>ARE | 7 BI<br>TARG<br>REPE<br>IN DA | GET ADI<br>EATED I<br>ATA FLC | 1<br>DRESS<br>DUE TO         | :<br>D CHANG<br>ECTION        | 8 BIT  | DAT<br>THE<br>THE  | 8 B<br>FA BYTE<br>E REGIS<br>E COMM | ITS E: READS BTER SET IAND BYT      | FROM<br>BY<br>E                 | 1           | ACI    |          | DAT                  | _    | ACK  |