XDP<sup>™</sup> Digital Power

**Design Guide**

**Revision 1.1**

### About this document

#### Scope and purpose

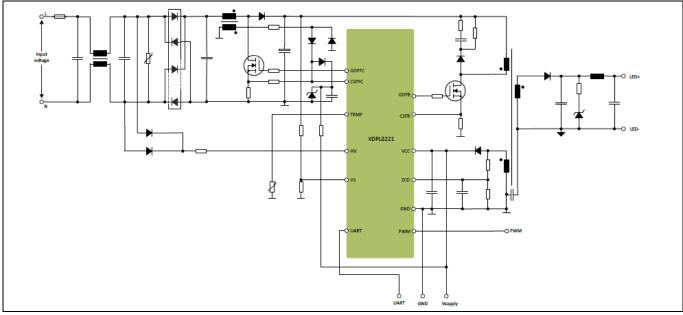

This document is a step-by-step guide for designing high-performance dual-stage digital PFC+Flyback AC-DC converter using the XDPL8221 controller for LED lighting applications. The document also describes parameter handling for Infineon typical use cases using the Infineon .dp Vision tool for the Infineon XDPL8221.

#### **Intended audience**

This document is intended for anyone wishing to design high-performance dual-stage digital PFC+Flyback AC/DC-DC converter for LED lighting based on the digital controller XDPL8221.

## **Table of contents**

| Abou   | t this document                                                      | 1  |

|--------|----------------------------------------------------------------------|----|

| Table  | e of contents                                                        | 1  |

| 1      | Introduction                                                         | 3  |

| 1.1    | Product highlights                                                   | 3  |

| 1.2    | Design features                                                      | 3  |

| 1.3    | Target applications                                                  | 3  |

| 1.4    | Pin configuration and description                                    | 4  |

| 2      | Hardware design                                                      | 6  |

| 2.1    | System specification of a 100 W driver for LED lighting applications | 6  |

| 2.2    | Schematic                                                            | 7  |

| 2.3    | Bridge rectifier                                                     | 8  |

| 2.4    | Design PFC boost converter                                           | 8  |

| 2.4.1  | Main PFC boost inductor                                              | 8  |

| 2.4.2  | PFC Boost diode                                                      | 11 |

| 2.4.3  | PFC Power MOSFET                                                     |    |

| 2.4.4  | PFC MOSFET Gate driver                                               | 13 |

| 2.4.5  | PFC Current sense and zero-crossing detection                        |    |

| 2.4.6  | PFC Output voltage sense                                             | 16 |

| 2.4.7  | PFC Output capacitor                                                 |    |

| 2.4.8  | PFC Multi-mode control                                               |    |

| 2.4.9  | PFC Start-up and steady state control                                | 20 |

| 2.4.10 | ) Input voltage sensing                                              | 22 |

| 2.4.11 | PFC Protection features                                              | 23 |

| 2.4.11 | I.1 Bus voltage protection                                           | 23 |

| 2.4.11 | I.2 Input voltage protection                                         | 25 |

| 2.4.11 | L.3 Over-current protection                                          | 25 |

# XDP<sup>™</sup> Digital Power

#### Introduction

| 2.4.11. | .4 Soft-start failure                      | 26 |

|---------|--------------------------------------------|----|

| 2.4.11. | .5 CCM protection                          | 26 |

| 2.5     | Design the flyback converter               | 26 |

| 2.5.1   | Design the flyback transformer             | 27 |

| 2.5.1.1 | . Transformer turns ratio                  | 27 |

| 2.5.1.2 | Primary magnetizing inductance             | 28 |

| 2.5.1.3 | Flyback transformer winding turns          |    |

| 2.5.2   | Flyback primary power MOSFET               | 33 |

| 2.5.3   | Flyback MOSFET gate driver                 | 34 |

| 2.5.4   | Flyback primary snubber                    | 34 |

| 2.5.5   | Flyback secondary rectifier diode          |    |

| 2.5.6   | Flyback secondary snubber                  | 37 |

| 2.5.7   | Flyback secondary output capacitor         | 37 |

| 2.5.8   | Flyback zero-crossing detection divider    |    |

| 2.5.9   | Flyback current sense resistor             |    |

| 2.5.10  | Flyback operating window                   | 40 |

| 2.5.11  | Flyback multi-mode control                 | 42 |

| 2.5.12  | Flyback start-up control                   |    |

| 2.5.13  | Flyback protection features                | 45 |

| 2.5.13. | .1 Flyback primary over-current protection | 45 |

| 2.5.13. | .2 Flyback output under-voltage protection | 46 |

| 2.5.13. | .3 Flyback output over-voltage protection  | 46 |

| 2.5.13. | .4 Flyback output over-current protection  | 47 |

| 2.5.13. | .5 Flyback output over-power protection    | 47 |

| 2.5.13. |                                            |    |

| 2.5.13. | .7 Soft-start failure                      | 48 |

| 2.5.13. | .8 Other flyback protections               | 48 |

| 2.6     | Design the power supply for XDPL8221       | 48 |

| 2.7     | Design the bleeder                         |    |

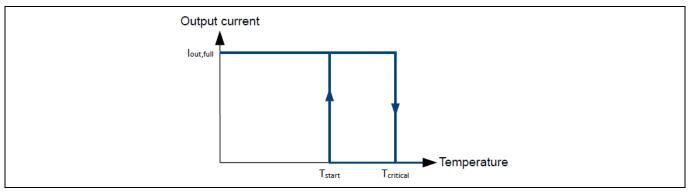

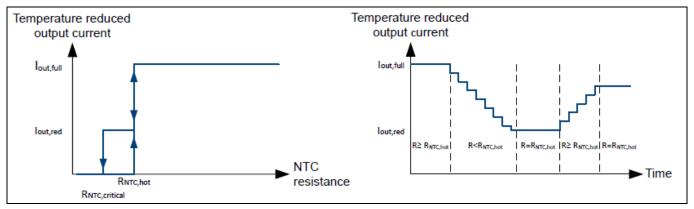

| 2.8     | Design the adaptive temperature protection | 52 |

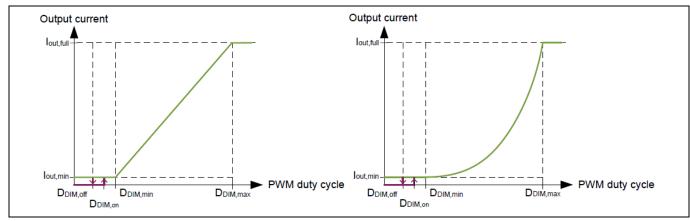

| 2.9     | Design the dimming interface               |    |

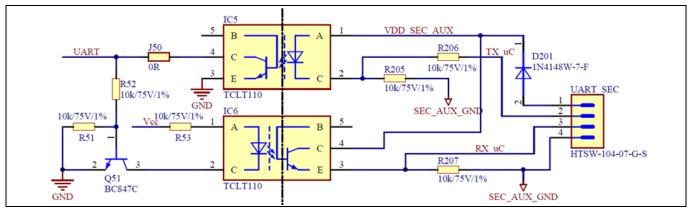

| 2.10    | UART Interface                             |    |

| 2.11    | PCB Layout guidelines                      | 56 |

| 2.11.1  | Star connection of grounding               | 56 |

| 2.11.2  | Filtering capacitors of XDPL8221           | 56 |

| 2.11.3  | PFC Voltage sense circuit                  | 56 |

| 2.11.4  |                                            |    |

| 2.11.5  | Other layout considerations                | 57 |

| 3       | Configuration setup and procedures         | 58 |

| 3.1     | Design parameters                          | 58 |

| 3.2     | XDPL8221 Configuration                     | 58 |

| Refere  | ences                                      | 59 |

| Revisi  | on history                                 | 60 |

# 1 Introduction

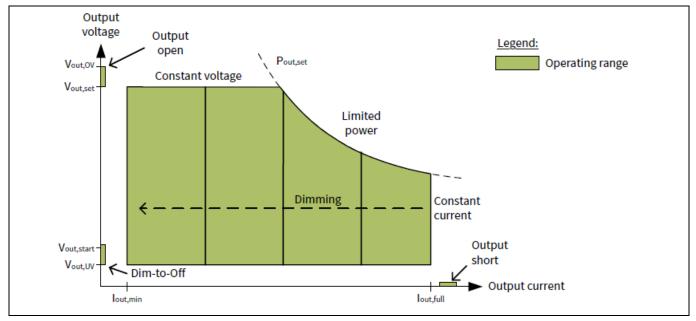

The digital controller IC XDPL8221 belongs to the Infineon XDP<sup>™</sup> digital power family. It provides an independent PFC boost and Flyback dual stage control to achieve an output which combines a constant voltage (CV), constant current (CC) and limited Power (LP) for LED luminaires. The IC is available in a PG-DSO-16 package and supports many features with only a minimum requirement of external components. The digital engine of the IC offers the possibility to configure operational parameters and protection modes. This eases the design phase and allows a high product variety with a reduced number of hardware variants. Accurate primary side output voltage and current control eliminates a secondary side feedback loop.

This design guide provides detailed information how to calculate the major power stage component values, as well as the setting of parameters for general functions and protection features. Useful tips on PCB layout are included to help the developers to optimize their PCB design. Finally, the installation and usage of a Graphical User Interface – .dp Vision is described to guide the customer to set parameters for the digital IC. The numeric values below are shown for the 100W reference board with universal input voltage.

# 1.1 Product highlights

- UART Command Interface enables real-time communication for smart control applications.

- Flicker-free dimming by analog reduction of output driving current down to 1%

- Primary side regulated (PSR) constant voltage (CV), constant current (CC), limited power (LP) output.

- High current accuracy output of typical +/- 2% across universal AC/DC input voltage range (90 Vrms to 305 Vrms) with extended output voltage range from 16 VDC to 48 VDC.

- Multi-mode flyback stage control (QRM+DCM+ABM) ensures high power efficiency over the entire load range and low dimming output down to 1% of the full current.

- High power factor (PF >0.9) and low input current total harmonic distortion (iTHD < 15%) for AC and DC input up to 300 V (RMS) and load down to 30%.

- Integrated 600 V startup cell ensures fast time to light and low power consumption.

- Adapted external temperature protection.

## 1.2 Design features

- Universal AC input (120 V to 277 VAC +/- 10%) or DC input (120 V to 430 VDC +/-10%)

- Extended output voltage range from 16 V to 48 VDC

- Recommended power range from 25 W to 150 W

## **1.3** Target applications

• Driver for LED luminaires

#### Introduction

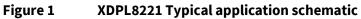

# 1.4 Pin configuration and description

Pin assignments and basic pin description information are shown below.

| Table 1 | Pin definitions and functions |

|---------|-------------------------------|

|         |                               |

| Name | Pin | Туре | Function                                                                                           |

|------|-----|------|----------------------------------------------------------------------------------------------------|

| GDFB | 1   | 0    | Flyback Gate Drive Output                                                                          |

|      |     |      | Output for directly driving a power MOSFET of the Flyback converter via a resistor.                |

| CSFB | 2   | I    | Flyback Current Sense Input                                                                        |

|      |     |      | Connected to an external shunt resistor and the source of a power MOSFET of the Flyback converter. |

| VCC  | 3   | I    | Positive Power Supply                                                                              |

# XDP™ Digital Power

#### Introduction

|       |    |     | IC power supply                                                                       |

|-------|----|-----|---------------------------------------------------------------------------------------|

| GND   | 4  | -   | Ground                                                                                |

|       |    |     | IC Ground                                                                             |

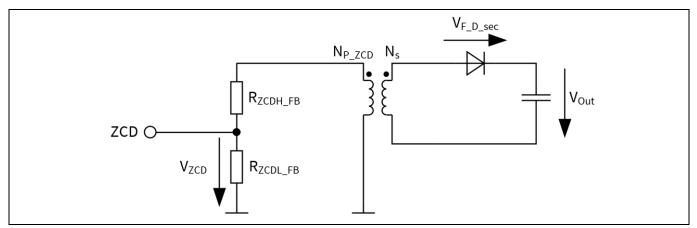

| ZCD   | 5  | I   | Flyback Zero-crossing Detection                                                       |

|       |    |     | Connected to the Flyback auxiliary winding via a resistive divider for zero-crossing  |

|       |    |     | detection as well as primary side output voltage sensing for output regulation and    |

|       |    |     | backup bus voltage sensing for safety.                                                |

| VS    | 6  | I   | PFC Voltage Sense                                                                     |

|       |    |     | Connected to DC bus via a resistive divider for the PFC boost converter output        |

|       |    |     | voltage sensing.                                                                      |

| N.U.  | 7  | -   | Not Used, to be connected to GND externally                                           |

| HV    | 8  | I   | High Voltage Input                                                                    |

|       |    |     | Connected to the AC mains via external rectifier diode and resistor. An internal 600V |

|       |    |     | HV startup-cell is used to charge VCC initially. In addition, sampled high-voltage    |

|       |    |     | sensing is also used for AC/DC detection and brown-out.                               |

| PWM   | 9  | I   | PWM Dimming                                                                           |

|       |    |     | The PWM pin is used as a dimming input.                                               |

| TEMP  | 10 | I   | External Temperature Sensor                                                           |

|       |    |     | Connected to an external NTC resistor to sense the environment temperature.           |

| CSPFC | 11 | 1   | PFC Current Sensing                                                                   |

|       |    |     | Connected to an external shunt resistor and the source of a power MOSFET of the       |

|       |    |     | PFC boost converter. Additionally, it is connected to the PFC aux winding for zero-   |

|       |    |     | crossing detection.                                                                   |

| N.U.  | 12 | I/O | Not Used, to be connected to GND externally                                           |

| GDPFC | 13 | 0   | PFC Gate Drive Output                                                                 |

|       |    |     | Output for directly driving a power MOSFET of the PFC boost converter via a resistor. |

| UART  | 14 | -   | Universal Asynchronous Receiver Transmitter (UART) Communication                      |

|       |    |     | The UART pin is used for the UART interface to support parameterization.              |

| N.C.  | 15 | -   | Not Connected. Externally to be connected to GND.                                     |

| N.C.  | 16 | -   | Not Connected. Externally to be connected to GND.                                     |

# 2 Hardware design

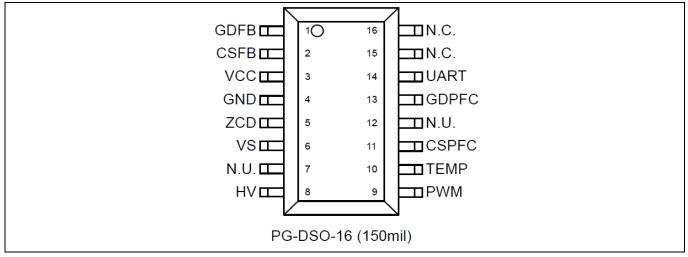

The hardware design part provides detailed calculation of power component values as well as the setting of parameters of general functions and protection features for both PFC boost and Flyback converters. Useful tips on PCB layout are included to help the customers optimize their PCB design.

The design example used in this hardware design part is a 100 W Constant Current mode driver reference design for direct driving of LED lighting applications. The customer can easily apply their own target specifications according this example and obtain the design parameters by themselves.

# 2.1 System specification of a 100 W driver for LED lighting applications

The system specification of a 100W driver reference design for LED lighting applications is given as following:

| Parameter                                   | Symbol                      | Target value | Unit            |

|---------------------------------------------|-----------------------------|--------------|-----------------|

| Input characteristic                        | ·                           |              |                 |

| Nominal input AC voltage (RMS)              | V <sub>in_AC</sub>          | 120 to 300   | $V_{\text{AC}}$ |

| Nominal input DC voltage                    | V <sub>in_DC</sub>          | 120 to 300   | V <sub>DC</sub> |

| Nominal output DC voltage                   | V <sub>OUT</sub>            | 16 to 48     | $V_{\text{DC}}$ |

| Nominal output DC current                   | Ι <sub>ουτ</sub>            | 550 to 2500  | mA              |

| Nominal output power                        | Po                          | 100          | W               |

| Power Factor                                | PF                          | > 0.9        |                 |

| THD                                         | iTHD                        | < 15         | %               |

| Power Efficiency                            | η                           | < 89         | %               |

| PFC stage                                   |                             |              |                 |

| PFC MOSFET Maximum drain-source voltage     | V <sub>DS_PFC</sub>         | 600          | V               |

| Maximum PFC stage output power              | P <sub>O_PFC</sub>          | 110          | W               |

| Minimum PFC switching frequency             | $f_{sw,min\_PFC}$           | 22           | kHz             |

| Maximum PFC switching frequency             | $f_{sw,max\_PFC}$           | 80           | kHz             |

| Flyback stage                               |                             |              |                 |

| Nominal Input voltage                       | V <sub>DC</sub>             | 460          | $V_{\text{DC}}$ |

| Maximum output power                        | Po                          | 100          | W               |

| Nominal output overvoltage threshold        | V <sub>OUT,OV</sub>         | 53           | V               |

| Flyback MOSFET maximum drain-source voltage | $V_{\text{DS}_{\text{FB}}}$ | 800          | V               |

| Minimum switching frequency                 | f <sub>sw,min</sub>         | 16           | kHz             |

Hardware design

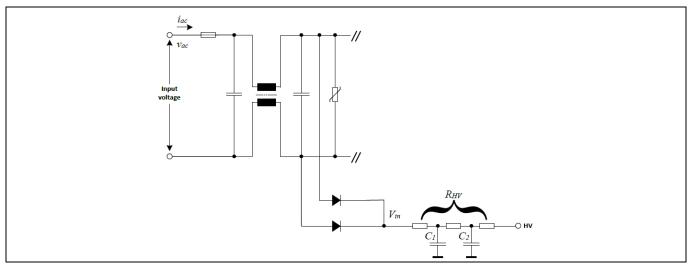

#### 2.2 Schematic

#### 2.3 Bridge rectifier

The bridge rectifier usually has the highest semiconductor power loss in the PFC boost converter. Using a higher rated current bridge rectifier can reduce the forward voltage drop, which reduces the total power dissipation at a small incremental cost. The total power loss is calculated using the average input current flowing through two of the bridge rectifying diodes if the forward voltage is assumed as 1 V:

$$P_{loss\_BR} = I_{BR\_avg} * 2 * V_{F\_BR} = \frac{2\sqrt{2}}{\pi} * \frac{P_{O\_PFC\_max}}{V_{in\_rms\_min} * \eta_{PFC}} * 2 * V_{F\_BR} = 2.71W$$

With the value of power loss, an appropriate bridge rectifier based on its thermal characteristics should be selected.

#### 2.4 Design PFC boost converter

Power Factor Correction (PFC) shapes the input current of the power supply to be in synchronization with the mains voltage, in order to maximize the real power drawn from the mains. In a perfect PFC circuit, the input current follows the input voltage as a pure resistor, without any input current harmonics. In the 100 W driver reference design, PFC is implemented as a boost converter which works in the Quasi-Resonant Mode (QRM) with constant on-time control. The converter provides the following flyback stage a constant high DC voltage as input which ensures flicker-free light output. This chapter describes the methodology for designing the QRM PFC Boost converter based on XDPL8221; including PFC boost inductor design, equations for power losses estimation, selection guide for power semiconductor devices and passive components.

#### 2.4.1 Main PFC boost inductor

As the key magnetic component of the PFC boost converter, the boost inductor has the main function of energy storage. Its inductance is given as the following formula:

$$L_{PFC} = \frac{V_{in\_pk}^{2} * (V_{bus} - V_{in\_pk}) * \eta_{PFC}}{4 * V_{bus} * P_{O\_PFC} * f_{PFC}}$$

Where

- L<sub>PFC</sub> -- Inductance of the PFC boost inductor

- V<sub>in\_pk</sub>-- Peak value of the input AC mains

- V<sub>bus</sub> -- Bus voltage as the PFC output

- $\eta_{PFC}$  -- Estimated power efficiency of the PFC boost converter

- PO\_PFC -- Output Power of the PFC boost converter

- f<sub>PFC</sub> -- Operation switching frequency of the PFC boost inductor

In the 100 W driver reference design, the output of the PFC boost converter is chosen as 460 V so that a high power factor is still guaranteed at the maximum AC/DC input. The minimum switching frequency limited at 22 kHz to avoid audible noise is controlled by XPDL8221 through "maximum switching period time-out" approach, which starts the next switching cycle when 45 µs of maximum switching period is reached. The detailed variables values are given in the following table:

XDP<sup>™</sup> Digital Power

Hardware design

#### Table 3 PFC design specification

| Parameter                                                                    | Symbol                  | Value | Unit |

|------------------------------------------------------------------------------|-------------------------|-------|------|

| AC/DC input under voltage threshold                                          | V <sub>UV_rms</sub>     | 76    | V    |

| AC/DC input overvoltage threshold                                            | V <sub>OV_rms</sub>     | 320   | V    |

| Maximum PFC boost converter output power                                     | P <sub>O_PFC_max</sub>  | 110   | W    |

| Maximum PFC On time                                                          | t <sub>on,max_PFC</sub> | 32    | μs   |

| Minimum PFC On time                                                          | t <sub>on,min_PFC</sub> | 200   | ns   |

| Minimum switching frequency                                                  | $f_{sw,min\_PFC}$       | 22    | kHz  |

| Estimated PFC boost converter power efficiency<br>@ maximum AC input voltage | $\eta_{\text{PFC}}$     | ≤96   | %    |

| Nominal PFC boost converter output voltage                                   | V <sub>bus</sub>        | 460   | V    |

| Power Factor                                                                 | PF                      | > 0.9 | -    |

The maximum possible inductance should be calculated at both lowest (input under voltage threshold) and highest possible input voltage (input overvoltage threshold) with full load and minimum switching frequency.

At 76 VAC input:

$$L_{PFC_{-76}} = \frac{\left(76 * \sqrt{2}\right)^2 * \left(460 - 76 * \sqrt{2}\right) * 0.96}{4 * 460 * 110 * 22 * 10^3} \approx 0.88 \ mH$$

At 320 VAC input:

$$L_{PFC_{320}} = \frac{\left(320 * \sqrt{2}\right)^2 * \left(460 - 320 * \sqrt{2}\right) * 0.96}{4 * 460 * 110 * 22 * 10^3} \approx 1.15 \ mH$$

The suitable inductance must be less than the smaller one of both.

$$L_{PFC} < min(L_{PFC_{76}}, L_{PFC_{320}})$$

Other considerations regarding PFC choke inductance:

- The selected PFC inductance must be small enough to cover the maximum output power at the minimum input (e.g. to cover the brown-in/out feature).

- Bigger PFC inductance has the advantage at light load in comparison to smaller inductance due to longer on time. This ensures smaller minimum output power in DCM when the LED load is small (e.g. 1% dimming) and avoids unwanted bus voltage ripples due to the limited minimum on time of the IC controller.

- For the maximum output power, bigger PFC inductance has longer on time and lower switching frequency. It must be guaranteed that these two parameters are still within the limit of XDPL8221.

- Bigger PFC inductance leads to bigger choke size and more winding turns which cause more winding loss. In contrast, smaller inductance has smaller size and less winding turns but higher frequency which could lead to more switching loss.

In the reference design,  $L_{PFC}$  =0.6 mH is chosen to avoid magnetic saturation in all worst cases like start-up and load transient. After the PFC choke inductance is fixed, the choke relevant parameters can be calculated as following with the assumption of the boundary concudtion mode operation:

Maximum input current (RMS) happens at minimum AC input and maximum output power:

$$I_{in\_rms\_max} = \frac{P_{O\_PFC\_max}}{V_{UV\_rms} * \eta_{PFC}} = 1.5 A$$

#### Hardware design

Maximum input peak current:

$$I_{in\_pk\_max} = \sqrt{2} * I_{in\_rms\_max} = 2.12 A$$

Maximum inductor peak current:

$I_{L,pk\_PFC\_max} = 2 * I_{in\_pk\_max} = 4.24 A$

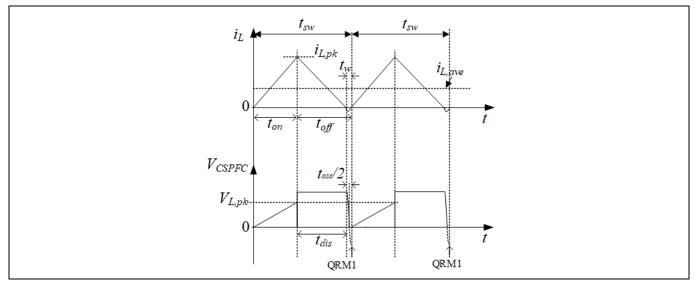

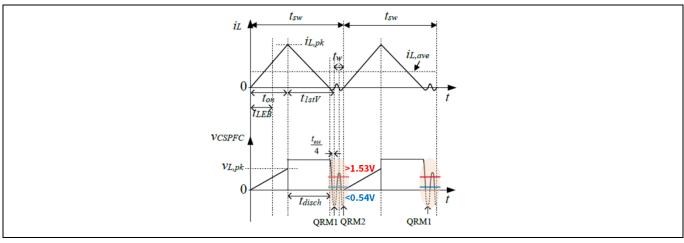

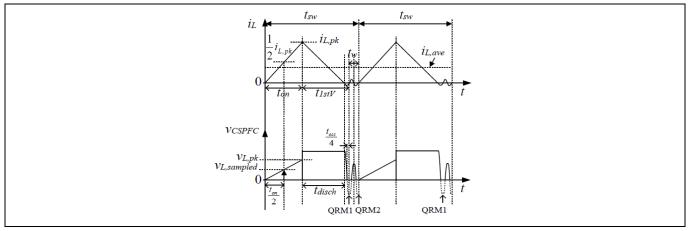

Figure 4 Boost inductor current waveform in a switching cycle

According to the **Figure 4** above, other important parameters of the PFC boost converter can be calculated as following if the QRM1 operation is assumed:

Maximum on-time:

$$t_{on\_max} = \frac{L_{PFC} * I_{L,pk\_PFC\_max}}{\sqrt{2} * V_{UV\_rms}} = 23 \ \mu s$$

If  $T_{osc}$  = 1.5 us is assumed, off time at minimum AC input and maximum output power:

$$t_{off} = \frac{L_{PFC} * I_{L,pk\_PFC\_max}}{V_{bus} - \sqrt{2} * V_{UV\_rms}} + 0.5 * T_{osc} = 7.97 \,\mu s$$

the lowest frequency for maximum output power of PFC converter in QRM:

$$f_{PFC\_min} = \frac{1}{t_{on\_max} + t_{off}} = 32.3 \ kHz$$

Maximum current (RMS) through the PFC inductor during on-time:

$$I_{L,PFC\_on\_rms\_max} = I_{L,pk\_PFC\_max} * \sqrt{\frac{1}{3}} * t_{on\_max} * f_{PFC\_min} = 2.11A$$

Maximum current (RMS) through the PFC inductor during off-time:

$$I_{L,PFC\_off\_rms\_max} = I_{L,pk\_PFC\_max} * \sqrt{\frac{1}{3}} * t_{off} * f_{PFC\_min} = 1.24A$$

Thus the maximum PFC inductor current (RMS):

$$I_{L\_rms\_max} = \sqrt{I_{L,PFC\_on\_rms\_max}^2 + I_{L,PFC\_off\_rms\_max}^2} = 2.45 A$$

## XDPL8221 Digital PFC+Flyback Controller IC XDP<sup>™</sup> Digital Power Hardware design

To realize the zero crossing detection of the inductor current for the quasi-resistant mode switching, an additional auxiliary winding is introduced in the PFC inductor. It is recommended to keep the maximum voltage across the auxiliary winding below 50V which is proportional to the maximum voltage drop across the PFC inductor main winding. This must comply with the maximum voltage rating of the components which are connected to the auxiliary winding. In the 100 W reference design, a turns-ratio of 10:1 is used.

The important parameters of the PFC boost inductor are summarized in the following **Table 4**:

#### Table 4 PFC boost inductor design parameters

| PFC Boost converter                         |                                        |       |      |

|---------------------------------------------|----------------------------------------|-------|------|

| Parameter                                   | Symbol                                 | Value | Unit |

| Main Inductance of the PFC boost inductor   | L <sub>PFC</sub>                       | 600   | μH   |

| Minimum switching frequency in QRM          | $\mathbf{f}_{PFC}$ _min                | 32.3  | kHz  |

| Maximum inductor peak current               | I <sub>L,pk_PFC_max</sub>              | 4.24  | А    |

| Maximum input current (RMS)                 | I <sub>in_rms_max</sub>                | 1.5   | А    |

| Maximum input peak current                  | l <sub>in_pk_max</sub>                 | 2.12  | А    |

| Maximum inductor current (RMS)              | I <sub>L_rms_max</sub>                 | 2.45  | А    |

| Maximum on-time                             | t <sub>on_max</sub>                    | 23    | μs   |

| Turns-ratio of primary to auxiliary winding | N <sub>p_PFC</sub> /N <sub>a_PFC</sub> | 10:1  | -    |

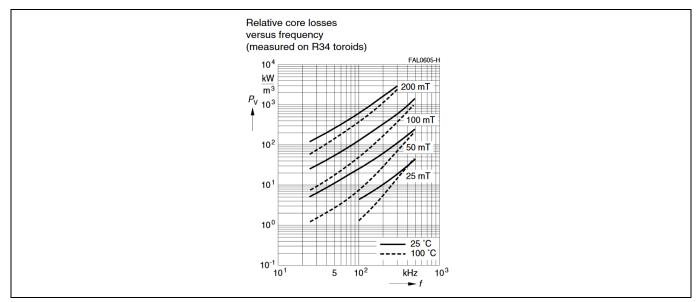

Based on the calculated specifications above, the inductor can be constructed according to different design requirements like size, power efficiency and temperature etc. by selecting different bobbin and core. In order to avoid core saturation and achieve an optimized core loss, the flux density  $B_{max}$  is recommended not to exceed 0.3.

In the Infineon 100 W driver reference design, the PFC boost inductor is constructed by the Würth Electronic under part no. **750343236** as a design example. The specification sheet is given as following in **Table 5**:

| Parameter                                   | Value         | Unit |

|---------------------------------------------|---------------|------|

| Inductance                                  | 600           | μH   |

| Bobbin                                      | ETD34         | -    |

| Core material                               | TP4A or DMR44 | -    |

| Turns-ratio of primary to auxiliary winding | 10:1          | -    |

| DC resistance primary winding               | 0.13          | Ω    |

| DC resistance auxiliary winding             | 0.033         | Ω    |

| Saturation current                          | 4.3           | А    |

#### Table 5Parameters of Würth inductor 750343252

The maximum main inductor copper loss can be calculated based on the specification above as:

$$P_{loss\_L\_PFC} = I_{L\_rms\_max}^2 * R_{DC\_L\_PFC} = 0.76 \text{ W}$$

#### 2.4.2 PFC Boost diode

The selection of the boost diode is a major decision in the PFC boost converter design and it is related to the converter efficiency. Following considerations should be taken into account:

Reverser break down voltage

It must be chosen higher than the bus voltage with at least 20% margin:

$V_{RRM_D_PFC} < 1.2 * V_{bus_OVP1} = 582 V$

A 600V diode is suitable here in the 100W reference design.

• Average rectified forward current

It must be higher than the maximum average PFC diode current calculated as following:

$$I_{D\_PFC\_avg\_max} = \frac{\sqrt{3}}{2} * I_{L,PFC\_off\_rms\_max} = 1.07 A$$

Using a diode with high current capability will benefit the power efficiency.

• Forward voltage

It is directly related to the power efficiency. So the forward voltage should be chosen as small as possible.

• Reverse recovery time

As the PFC boost converter is controlled by XDPL8221 in the QRM+DCM mode, the PFC boost diode current goes back to zero while the PFC MOSFET turns on. So there is no current commutation between PFC diode and MOSFET and thus no switching loss by reverse recovery. It is not necessary to choose an ultra-fast diode.

• Power loss

The only power loss which should be considered is conduction loss. With a forward voltage of 0.5V assumed, the diode conduction loss can be calculated as following:

$$P_{loss\_D\_PFC} = I_{D\_PFC\_avg\_max} * V_{F\_D\_PFC} = 0.535 W$$

• Thermal characteristic

With the thermal resistance of the diode  $R_{D_{PFC_{TH_{JA}}}}$  and ambient temperature  $T_A$ , the PFC diode temperature without heat sink is calculated as:

$$T_{D\_PFC} = P_{loss\_D\_PFC} * R_{D\_PFC\_TH\_JA} + T_A$$

The important parameters for the boost diode which used in the 100 W driver reference design are summarized in the following **Table 6**:

#### Table 6 Boost Diode Design Parameters

| Parameter                         | Symbol                     | Value | Unit |

|-----------------------------------|----------------------------|-------|------|

| Maximum reverse voltage           | V <sub>RRM_D_PFC</sub>     | 600   | V    |

| Average rectified forward current | I <sub>D_PFC_avg</sub>     | 4     | A    |

| Maximum PFC diode RMS current     | I <sub>D_PFC_rms_max</sub> | 1.24  | A    |

| Forward voltage                   | V <sub>F_D_PFC</sub>       | 0.5   | V    |

#### 2.4.3 PFC Power MOSFET

The selection of the PFC power MOSFET is based mainly on the consideration of the break down voltage and power dissipation. According to the operating bus voltage, a 600 V MOSFET is suitable. In the QRM+DCM mode PFC boost converter, the overall MOSFET losses comprise:

Conduction loss

## XDPL8221 Digital PFC+Flyback Controller IC XDP™ Digital Power Hardware design

These losses are frequency independent and do not scale significantly with frequency. It is calculated as following:

$$P_{con\_loss\_MOS\_PFC} = I_{L,PFC\_on\_rms\_max}^2 * R_{DS(ON)}$$

• Turn-on transition loss

As the converter works in the QRM+DCM mode, the turn-on transition loss caused by the magnetizing current can be ignored because the current rises from zero when a switching cycle starts. But to discharge the parasitic capacitors like  $C_{oss}$  and  $C_{can}$  through the MOSFET channel can cause significant turn-on transition loss. These losses occur every switching cycle and are thus frequency dependent.

• E<sub>oss</sub> and

$$1/2 \cdot C_{can} \cdot V^2$$

loss

As mentioned above, the energy stored in  $C_{can}$  and  $C_{oss}$  at the time of turn-on must be dissipated in the MOSFET channel and current sense resistor during the turn-on transition. The energy stored in any capacitor is fundamentally a function of the square of the voltage across it, and thus the  $E_{oss}$  and  $\frac{1}{2} \cdot C_{can} \cdot V^2$  losses can be very significant during high line conditions. These losses occur every switching cycle and are thus frequency dependent. To simplify the calculation, we assumed that the switching loss is approximately the half of the conduction loss:

$$P_{sw\_loss\_MOS\_PFC} = \frac{1}{2} * P_{con\_loss\_MOS\_PFC}$$

• Gate driver loss

These losses also scale linearly with frequency, but are generally a quite small contribution to the overall losses (at switching frequencies of below hundred kilohertz) and depend almost exclusively on the MOSFET  $Q_g$  (total gate-charge). The gate-driver power is typically dissipated in the external gate resistor and gate-driver itself and thus does not need to be considered in the thermal calculation of MOSFET.

In the 100 W driver reference design, the 600V Infineon MOSFET IPA60R190C6 of C6 family is used. With the  $R_{DS(ON)}$  of 190 m $\Omega$ , the total loss of the MOSFET is calculated as below:

$$P_{loss\_MOS\_PFC} = P_{sw\_loss\_MOS\_PFC} + P_{con\_loss\_MOS\_PFC} = 1.5 * P_{con\_loss\_MOS\_PFC} = 0.63 W$$

The important parameters for PFC MOSFET are summarized in the following **Table 7**:

| Parameter                  | Symbol                        | Value | Unit |  |

|----------------------------|-------------------------------|-------|------|--|

| Break down voltage         | $V_{BR_{DSS_{PFC}}}$          | 650   | V    |  |

| MOSFET on-resistance       | R <sub>DS(ON)</sub>           | 190   | mΩ   |  |

| PFC MOSFET conduction loss | P <sub>loss_MOS_PFC_con</sub> | 0.42  | W    |  |

| PFC MOSFET switching loss  | P <sub>loss_MOS_PFC_sw</sub>  | 0.21  | W    |  |

| PFC MOSFET total loss      | Ploss_MOS_PFC                 | 0.63  | W    |  |

Table 7 PFC MOSFET Design parameters

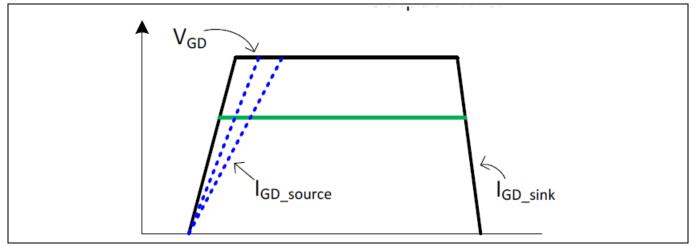

#### 2.4.4 PFC MOSFET Gate driver

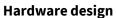

The XDPL8221 PFC boost converter gate driver GDPFC offers following advanced features:

- Configurable charge current from 30 up to 118 mA for turn-on slope optimization with dpVision tool

- Configurable gate voltage from 4.5 to up to 15 V

Downloaded from Arrow.com.

## XDP<sup>™</sup> Digital Power

Figure 5 Configurable gate driver with gate voltage and charge current

Due to the configurable gate charge current and voltage, the external gate resistor should not be selected too high. A gate resistor of 10  $\Omega$  should fit for most application cases. The soft turn on for improved EMI result is guaranteed by the configurable constant current gate charging. Following table shows the recommend range of the external gate resistor for a stable gate drive operation of different MOSFET:

| Parameter                          | Symbol          | Value      |       | Unit |

|------------------------------------|-----------------|------------|-------|------|

| MOSFET Gate capacitance            | Cg              | 1.0 to 2.0 |       | nF   |

| MOSFET gate source current         | l <sub>gs</sub> | 100        |       | mA   |

| MOSFET gate source resistance      | $R_{gs}$        | 10         | 100   | kΩ   |

| Recommended external gate resistor | R <sub>g</sub>  | 5~20       | 15~25 | Ω    |

Table 8

Recommended external gate resistor value

# 2.4.5 PFC Current sense and zero-crossing detection

The pin CSPFC of the XDPL8221 is used for two different purposes in one switching cycle. During the on time of the PFC MOSFET, it is used as current sense pin. The current sense of the PFC boost converter is used to limit the turn on time of the PFC MOSFET by sensing the peak current flowing through the MOSFET in order to protect it and also the boost inductor from the over-power situation. When the MOSFET is turned off, the pin is used as ZCD pin. The zero-crossing detection catches the moment when the boost inductor current goes back to zero and the next switching cycle can be started so that the boost converter always works in the QRM or DCM mode with minimum switching loss.

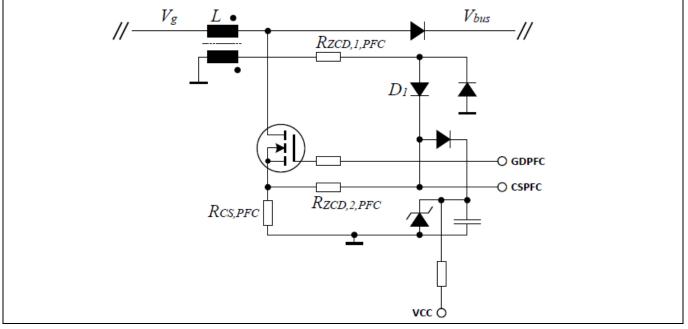

As the **Figure 6** shows below, when the PFC MOSFET turns on, the rectifier diode  $D_1$  blocks the negative voltage drop across the PFC auxiliary winding so that the CSPFC pin is effectively connected only to the shunt resistor  $R_{CS\_PFC}$  via the resistor  $R_{ZCD\_PFC}$  and thus only sees the peak current sense voltage signal. When the PFC MOSFET turns off, a positive voltage drop is forwarded by  $D_1$ . The CSPFC pin is connected effectively to a resistor divider  $R_{ZCD1\_PFC}$  and  $R_{ZCD2\_PFC}$ . A zener diode and a capacitor are necessary to clamp the pin voltage not higher than 3.3 V. Another diode is required to decouple the current sensing signal from the clamping circuit.

XDP<sup>™</sup> Digital Power

# infineon

#### Hardware design

Figure 6 Schematic of shared CS and ZCD functions at the CSPFC pin

The ratio of the resistor divider  $R_{ZCD1\_PFC}$  and  $R_{ZCD2\_PFC}$  decides the amplitude of the oscillation at the CSPFC pin. So that the comparator for the zero crossing detection works correctly, the amplitude of the oscillation at the CSPFC pin must be higher than the 1.53 V as shown in the **Figure 7**. The ratio of the divider must be designed theoretically as following:

$$(V_{bus} - V_{in_pk_max}) * \frac{N_{a_pFC}}{N_{p_pFC}} * \frac{R_{ZCD2_pFC}}{R_{ZCD1_pFC} + R_{ZCD2_pFC}} > 1.5 * 1.54 V$$

# Attention: The bus voltage ripple and the parasitic resistance of the winding which leads to the damping of the amplitude should be also taken into account if necessary. Wrongly designed of the divider ratio will cause the losing of the PFC ZCD signal.

Figure 7 Hysteretic comparator threshold for zero crossing detection

To design the PFC current sense shunt resistor, following condition must be complied:

## XDPL8221 Digital PFC+Flyback Controller IC XDP<sup>™</sup> Digital Power Hardware design

$I_{L,pk\_PFC\_max} * R_{CS_{PFC}} < V_{OCP1\_PFC\_max} = 1.214 V$

and

$$R_{CS\_PFC} < \frac{1.214V}{I_{L,pk\_PFC\_max}} = 0.28 \,\Omega$$

The value of the current sense resistor is chosen to  $0.165 \Omega$  with two resistors  $0.33 \Omega$  parallel connected. This splits the power dissipation and reduces the thermal stress. The maximum power loss of each shunt resistor is:

$P_{loss\_shunt\_PFC\_max} = 0.5 * I_{L\_RMS\_max}^2 * R_{CS\_PFC} = 0.5 * 1.71A^2 * 0.33 = 0.48 W$

This should be considered while selecting the proper shunt resistor type.

The important design parameters for bus voltage sensing are summarized in the following Table 9:

Table 9

PFC Current sense and ZCD design parameters

| Parameter                             | Symbol                    | Value            | Unit |

|---------------------------------------|---------------------------|------------------|------|

| Upper resistor of the PFC ZCD divider | R <sub>ZCD1_PFC</sub>     | 4.7              | kΩ   |

| Lower resistor of the PFC ZCD divider | R <sub>ZCD2_PFC</sub>     | 33               | kΩ   |

| PFC OCP1 maximum operating range      | V <sub>OCP1_PFC_max</sub> | 1.214            | V    |

| PFC current sense resistor            | R <sub>cs_pfc</sub>       | 0.33//0.33=0.165 | Ω    |

## 2.4.6 PFC Output voltage sense

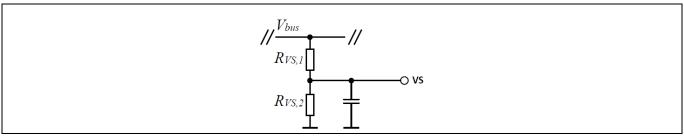

As shown in the **Figure 8** below, the bus voltage is measured at the VS pin of XDPL8221 through a resistor divider. This measurement is used as the input of the PFC output voltage regulator to generate the PWM control signal for PFC MOSFET and offers the protection functions for the PFC boost converter. It is strongly recommended to add a filter capacitor near the VS pin to filter the switching noise in order to get a precise and stable measurement result. The VS pin has a very low leakage current so the intolerance can be ignored.

Figure 8 Bus voltage measurement

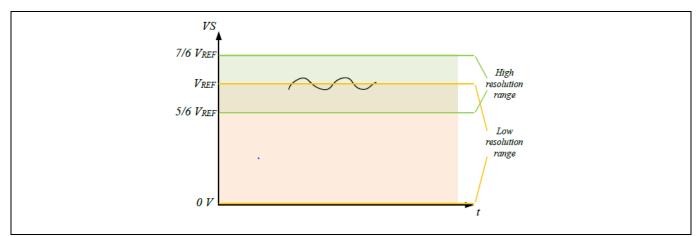

Inside the XDPL8221, the VS pin is connected to an 8-Bit Analog-to-Digital Converter (ADC) which utilizes two voltage ranges for the bus voltage measurement results. This gives the advantage that on the one hand, the whole voltage range started from 0V is monitored. On the other hand the operating range is sensed with a high resolution so that the regulation accuracy is guaranteed.

As shown in the **Figure 9**, the wide voltage range from 0 to  $V_{REF}$  results in a low resolution. If the nominal operating bus voltage  $V_{bus}$  = 460 V is assumed in the normal operation and mapped to  $V_{REF}$  by the resistor divider as recommended, then a 8-Bit ADC gives the range 0 ~ 460 V a resolution of

Wide Range Resolution =

$$\frac{V_{bus}}{256} \approx 1.8 V/LSB$$

#### **Hardware design**

This range is used to monitor the start-up behavior or other failures.

The narrow voltage range from 5/6 V<sub>REF</sub> to 7/6 V<sub>REF</sub> gives a three times better resolution. If the nominal operating bus voltage  $V_{bus}$  = 460 V is assumed and mapped to  $V_{REF}$ , then a 8-Bit ADC gives the range from 5/6\* $V_{bus}$  = 383 V to  $7/6^* V_{bus} = 536 V a resolution of$

Narrow Range Resolution

$$=$$

$\frac{1}{3} * \frac{V_{bus}}{256} \approx 0.6 V/LSB$

So in the steady state operation, the high-resolution range is used to get an accurate bus voltage regulation.

**Figure 9 Bus voltage sensing ranges**

The calculation of the resistor divider is given as following if the V<sub>bus</sub> = 460 V is mapped to V<sub>REF</sub>:

$$\frac{R_{VS1\_PFC}}{R_{VS2\_PFC}} = \frac{V_{bus} - V_{REF}}{V_{REF}} = 188.46$$

To reduce the inaccuracy caused by the resistor divider, it is necessary to select the bus voltage sensing resistors with a tolerance of 1% or less. In the 100 W driver reference design, to reduce the voltage stress, the upper resistor  $R_{VS1\_PFC}$  consists of three resistors of each 3.32 M $\Omega$  and the lower resistor  $R_{VS1\_PFC}$  is selected as 52.3 k $\Omega$ .

Note: As indicated in the XDPL8221 Datasheet, the Vcc pin voltage must be higher than 3.4 V before the voltage of VS exceeds 1.2 V. So it is recommended to select the divider with high impedance. This also helps to reduce the power consumption in the stand-by mode.

The criteria to switch between these two ranges are as following if the tolerance of the resistors can be ignored:

- The PFC boost converter always starts in the narrow (high resolution) range •

- In the narrow (high resolution) range, if the bus voltage V<sub>bus</sub>< 406 V then it will be switched to wide range •

- In the wide (low resolution) range, if the bus voltage V<sub>bus</sub> > 430 V, then it will be switched to the narrow range ٠

Note: In order to reduce the switching noise coupled in the Bus voltage sense signal, a filter capacitor of 1 nF is strongly recommended to be placed directly near the VS pin.

The important design parameters for bus voltage sensing are summarized in the following **Table 10**:

Hardware design

#### Table 10Bus voltage sensing design parameters

| Parameter                                  | Symbol               | Value     | Unit  |

|--------------------------------------------|----------------------|-----------|-------|

| Nominal PFC boost converter output voltage | V <sub>bus</sub>     | 460       | V     |

| XDPL8221 internal ADC reference voltage    | V <sub>REF</sub>     | 2.428     | V     |

| Bus voltage sensing divider upper resistor | R <sub>VS1_PFC</sub> | 3.32 x 3  | MΩ    |

| Bus voltage sensing divider lower resistor | R <sub>VS2_PFC</sub> | 52.3      | kΩ    |

| Bus voltage sensing filter capacitor       | C <sub>vs</sub>      | 1         | nF    |

| Narrow (High Resolution) range             | -                    | 383 ~ 536 | V     |

| Resolution of narrow range                 | -                    | 0.6       | V/LSB |

| Wide (Low Resolution) range                | -                    | 0~460     | V     |

| Resolution of wide range                   | -                    | 1.8       | V/LSB |

#### 2.4.7 PFC Output capacitor

The PFC bus capacitor can be calculated with the following formula if the ESR of the capacitor is small enough to be neglected and the peak to peak voltage ripple is selected as 20 V. Please note that the tolerance of 20% of the capacitance needs to be taken into account as well.

$$C_{bus} = \frac{I_{out\_PFC\_max}}{2 * \pi * f_{line\_min} * V_{bus\_ripple\_pp}} * 1.2 = 46 \,\mu F$$

With

$$I_{out\_PFC\_max} = \frac{P_{O\_PFC\_max}}{V_{bus}} = 0.24 A$$

Regarding the voltage rating with consideration of over-voltage protection threshold, a 500 V capacitor is necessary. But due to the price and size factors, it is reasonable to use two 250V rating capacitors in series. The ESR of the capacitor should be selected as small as possible and the allowed maximum ripple current should have enough margins. In the 100 W driver reference design, one 500 V capacitor of 47  $\mu$ F with low ESR is selected. To symmetrize the voltage stress on the two in series connected capacitors, an in parallel connected high ohmics resistor divider is recommended, which will increase the stand by power consumption lightly nevertheless.

The important parameters for the bus capacitor selection are summarized in the following table:

#### Table 11 Bus Capacitors Design Parameters

| Parameter                                  | Symbol                     | Value   | Unit |

|--------------------------------------------|----------------------------|---------|------|

| Nominal PFC boost converter output voltage | V <sub>bus</sub>           | 460     | V    |

| Maximum PFC boost converter output power   | P <sub>out_PFC_max</sub>   | 110     | W    |

| Bus voltage ripple (peak to peak)          | V <sub>bus_ripple_pp</sub> | 20      | V    |

| AC input line frequency                    | <b>f</b> <sub>line</sub>   | 45 ~ 66 | Hz   |

| PFC Bus capacitor                          | C <sub>bus</sub>           | 47      | μF   |

#### 2.4.8 PFC Multi-mode control

The PFC boost converter regulates the output bus voltage through the calculated constant on-time:

## XDPL8221 Digital PFC+Flyback Controller IC XDP<sup>™</sup> Digital Power Hardware design

$$t_{on\_PFC} = \frac{2 * P_{O\_PFC\_max} * L_{PFC}}{V_{in\_rms}^2 * \eta_{PFC}}$$

As shown from the formula above, when the inductance is fixed and the line input voltage is constant, the PFC on-time is only dependent on the converter output power. The output voltage is sensed and fed into the internal regulator for on-time calculation. With the calculated on-time and frequency law, a switching cycle is defined.

For PFC boost converter operating in the QRM (quasi resonant mode), the PFC MOSFET is turned on with constant on-time throughout the complete AC half cycle and the off-time is varying during the AC half cycle depending on the instantaneous input voltage applied. A new switching cycle starts after the inductor current reaches zero. It is ideal for full load operation, where the on-time is large. However, the on-time reduces at light load, resulting in very high switching frequency especially near the zero-crossings of the AC input. The high switching frequency increases the switching loss, resulting in poor efficiency at light load. Therefore the multi-mode control is implemented.

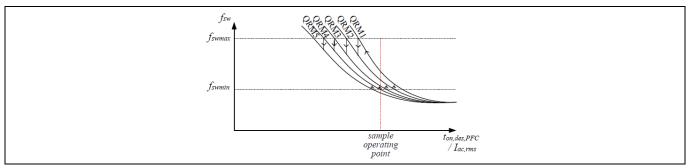

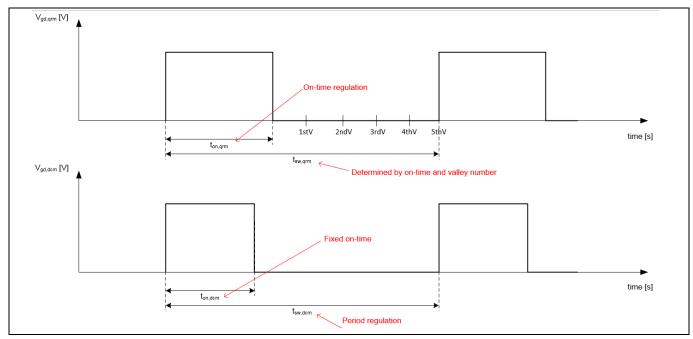

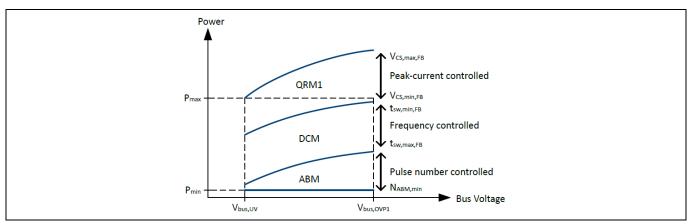

XDPL8221 uses QRM+DCM operation for PFC load regulation. At full load and heavy load, PFC is running with QRM1 for the best power efficiency. When the load decreases, XDPL8221 reduces the on time and switching frequency at the same time by adding an additional delay into each switching cycle through selecting further inductor current valleys to achieve QRM2 and up to maximum QRM5 (configurable) operation. **Figure 10** illustrates the QRM2 valley switching in multi-mode PFC control as an example. In case of light load e.g. deep dimming, DCM operation with fixed on time is applied to further reduce the power transfer: the adjustment of the switching period will regulate the load change and the switching frequency can be reduced.

Figure 10 PFC Boost multi-mode control with QRM2

The multi-mode control is defined in the frequency law, which consisting of a maximum switching frequency  $f_{sw_PFC_max}$  and a minimum switching frequency  $f_{sw_PFC_min}$  controls the valley selection (QRMn). In this way, the switching frequency is limited within the defined range and efficiency at light load can be improved. An illustration of the frequency law is shown in **Figure 11**:

Figure 11 Frequency law for operating mode

#### Hardware design

The switching between QRM and DCM operation is described in the following Figure 12:

- PFC will enter DCM operation from QRM once the internal calculated on time is smaller than ton\_dcm\_PFC

- PFC will leave DCM operation back to QRM once the switching frequency is higher than fsw\_max\_dcm\_PFC

#### Figure 12 Mode switching between QRMn and DCM operation

The important design parameters for multi-mode control are summarized in the following table:

| Table 12 | Input Voltage Sensing Design Parameters |

|----------|-----------------------------------------|

|----------|-----------------------------------------|

| Parameter                                        | Symbol                  | Value | Unit |

|--------------------------------------------------|-------------------------|-------|------|

| Maximum PFC boost converter switching frequency  | $f_{sw_max_PFC}$        | 80    | kHz  |

| Minimum PFC boost converter switching frequency  | $f_{sw\_min\_PFC}$      | 22    | kHz  |

| The minimum on time to enter the DCM operation   | ton_dcm_PFC             | 300   | ns   |

| The maximum frequency to leave the DCM operation | $f_{sw\_max\_dcm\_PFC}$ | 150   | kHz  |

| Maximum allowed valley                           | $N_{valley\_max\_PFC}$  | 8     | -    |

## 2.4.9 PFC Start-up and steady state control

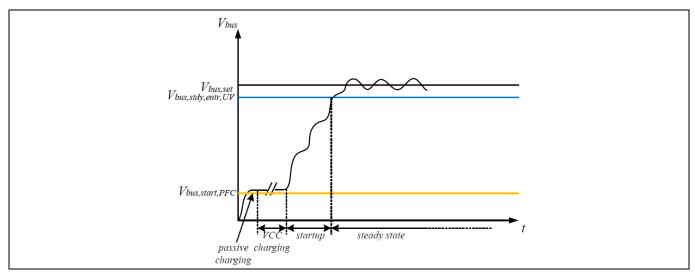

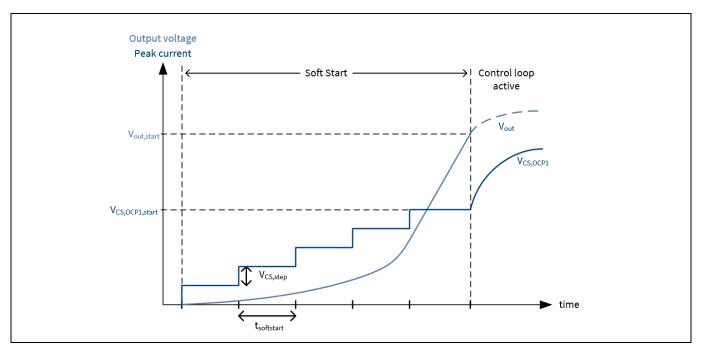

After the AC or DC voltage is applied at the input, the bus voltage is charged by the bridge rectifier and PFC diode. The Vcc capacitors are charged by the high voltage start-up cell till the Vcc on threshold is reached and the XDPL8221 is active. After activation, XDPL8221 checks first if the bus voltage is higher than V<sub>bus\_start\_PFC</sub> (brown-in condition). The PFC boost converter begins with the soft-start phase one the condition is fulfilled. After the threshold V<sub>bus\_steady\_entry\_UV</sub> is reached within the time t<sub>start\_max\_PFC</sub>, the start-up phase is over and the controller will switch to the steady state operation till the operating bus voltage value V<sub>bus\_steil</sub> is reached. Once the bus voltage is still lower than the threshold beyond the time, the PFC soft-start failure will be triggered. This is shown in the following **Figure 13**:

XDPL8221 PFC stage uses PIT1 (Proportional-Integral-T1) controller to control the bus voltage in start-up and steady state operation:

#### Hardware design

- Term P is proportional to the bus voltage error (difference between current bus voltage value and the operating nominal bus voltage value)

- Term I accounts for past values of the bus voltage error and integrates them over time to produce the I-term.

- Term T1 is a low pass filter which eliminates the noise in the error signal.

Figure 13 PFC Boost Converter Start-Up Control

The PIT1 controller parameters used for the start-up and steady state may be different because of different requirements of the control loop. In the start-up phase, the control loop reacts fast because a fast dynamic response is important in order to settle the bus voltage at the defined operation level as soon as possible so that the flyback stage can start quickly and take over the IC power supply. Furthermore, it also helps to reduce the time-to-light. On the contrary, a relative slow loop response in the steady state operation is desired for the stable bus voltage regulation. To reduce the PFC bus voltage ripple in the DCM operation, the controller gain can be configured, too. This eliminates the possible flicker in the deep dimming condition.

For all PIT1 controller gain parameters in XDPL8221: the higher the gain value is, the lower is the gain.

The important design parameters for PFC Boost Converter Start-up control are summarized in the table below:

| Table 13 | PFC Start-up design parameters |

|----------|--------------------------------|

|----------|--------------------------------|

| Parameter                                                     | Symbol                       | Value | Unit |

|---------------------------------------------------------------|------------------------------|-------|------|

| Voltage threshold to start PFC stage                          | $V_{bus\_start\_PFC}$        | 75    | V    |

| Voltage threshold for closed loop regulation                  | $V_{bus\_steady\_entry\_UV}$ | 448   | V    |

| Nominal PFC boost converter output voltage                    | $V_{bus\_set}$               | 460   | V    |

| Proportional gain of PIT1 regulator in the start-up phase     | SVP <sub>start_up</sub>      | 5     | -    |

| Integral gain of PIT1 regulator in the start-up phase         | SVI <sub>start_up</sub>      | 9     | -    |

| Proportional gain of PIT1 regulator in the steady state phase | SVP <sub>steady_state</sub>  | 4     | -    |

| Integral gain of PIT1 regulator in the steady state phase     | SVI <sub>steady_state</sub>  | 7     | -    |

| T1 filter gain in the steady state phase                      | SVT                          | 6     | -    |

| Proportional gain of PIT1 regulator in the DCM operation      | SVP <sub>dcm</sub>           | 1     | -    |

| Integral gain of PIT1 regulator in DCM operation              | SVI <sub>dcm</sub>           | 7     | -    |

Hardware design

## 2.4.10 Input voltage sensing

The rectified input voltage is measured through an external current limitation resistor  $R_{HV}$  at the HV pin as shown in the **Figure 14**. This path provides not only the input voltage sensing function, but also the power supply via the IC internal built HV start-up cell for XDPL8221 before the Vcc reaches the on-threshold.

The input voltage sensing distinguishes whether the AC or DC voltage is applied at input. Meanwhile, input voltage measurement provides the brown-in, brown-out and input over voltage protection. The threshold of each protection may be different for AC or DC input.

Figure 14 Input voltage sensing

To charge the Vcc capacitors through the IC internal start-up cell, the charge current must be limited not to overpower the start-up cell. The current limitation resistor R<sub>HV</sub> must fulfill the following condition:

$$R_{HV} > \frac{\sqrt{2} * V_{in\_max\_rms}}{I_{HV\_max}} = 45 \ k\Omega$$

Because of internal setup of the HV pin to measure the input precisely, it is mandatory to use the HV current limitation resistor  $R_{HV}$  = 99k $\Omega$  in order to limit the maximum HV pin current to 9.6 mA. To reduce the voltage and power stress of the resistor, it is strongly recommended to split it into three 1206 resistors of each 20 k $\Omega$ . To improve the accuracy of the measurement, resistors with tolerance less than 1% should be selected.

Note: To reduce the switching due to the PFC stage at the input stage and to increase the accuracy of the input voltage measurement, it is highly recommended to add high voltage filter capacitors with typical value of 680 pF after each HV resistor as shown in the **Figure 14**.

The important design parameters for input voltage sensing are summarized in the following table:

| Parameter                        | Symbol              | Value   | Unit |

|----------------------------------|---------------------|---------|------|

| Maximum AC input Voltage         | Vin_AC_max_rms      | 305     | Vrms |

| Maximum DC input voltage         | $V_{in_DC_max}$     | 305     | V    |

| Maximum current of start-up cell | I <sub>HV_max</sub> | 9.6     | mA   |

| HV current limitation resistor   | R <sub>HV</sub>     | 20x3=60 | kΩ   |

Table 14

Input voltage sensing design parameters

Hardware design

# 2.4.11 PFC Protection features

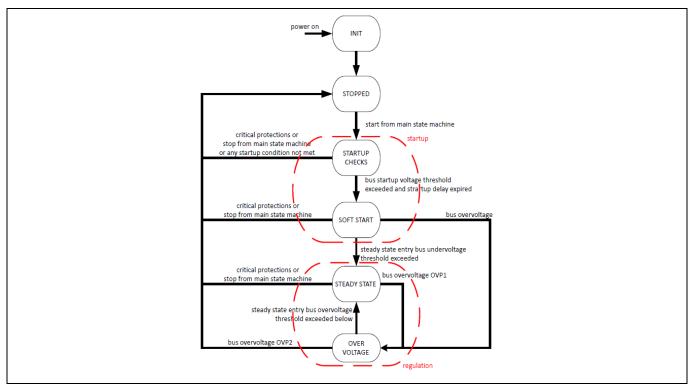

The digital controller XDPL8221 provides all around protections for both power components and input/output of the PFC boost converter. As illustrated below in the control state machine (**Figure 15**), the protections are active after the system enters the start-up checks state (when Vcc voltage reaches the on-threshold). While the start-up checks, the input/output are monitored before starts PFC to protect against possible under/over-voltage. After the system is in the soft-start state, more protections like over-current, over-power and CCM protection are also activated. An overview of which protection enabled in which operating state is given in the following **Table 15**:

Figure 15 PFC Boost converter control state machine

#### Table 15 PFC Protection states

| Protection                                | Stopped  | Soft-Start | SteadyState | Over Voltage |

|-------------------------------------------|----------|------------|-------------|--------------|

| Bus Over-oltage Protection level 2 (OVP2) | Disabled | Enabled    | Enabled     | Enabled      |

| Bus Under-voltage Protection              | Disabled | Disabled   | Enabled     | Enabled      |

| Input Over-voltage Protection             | Disabled | Enabled    | Enabled     | Enabled      |

| Input Under-voltage Protection            | Disabled | Enabled    | Enabled     | Enabled      |

| Over-current Protection level 2           | Disabled | Enabled    | Enabled     | Enabled      |

| Soft-Start Failure                        | Disabled | Enabled    | Disabled    | Disabled     |

| CCM Protection                            | Disabled | Disabled   | Enabled     | Disabled     |

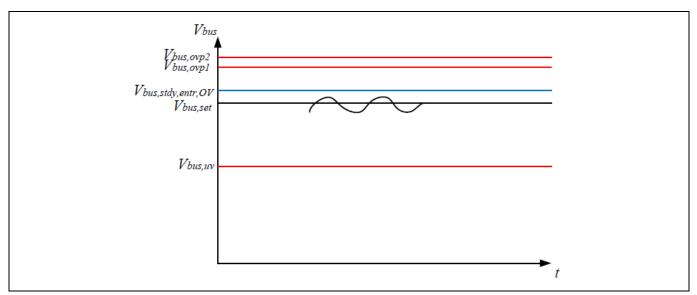

## 2.4.11.1 Bus voltage protection

The voltage at the VS pin which represents the bus voltage is sensed for the bus voltage protection.

Bus over-voltage protection is mandatory to protect the DC-link electrolytic capacitor, boost diode and MOSFET of the flyback converter. There are two different level protections defined:

#### Hardware design

- The OVP1 is part of the regulation loop and controlled by the firmware. When the OVP1 threshold V<sub>bus\_OVP1</sub> is continuously triggered beyond the configured blanking time t<sub>blank\_bus\_OVP1</sub>, the PFC gate driver is stopped by the firmware. In this case, flyback converter should go on switching to help discharging the bus capacitor. The PFC gate driver is only enabled again when the bus voltage falls below the level V<sub>bus\_steady\_entry\_OV</sub>. No further protection action is necessary.

- The OVP2 in contrast is a hardware protection and the gate driver is disabled if the fixed OVP2 threshold V<sub>bus\_OVP2</sub> is triggered beyond the defined blanking time t<sub>blank\_bus\_OVP2</sub> and without any firmware delay. In this case, flyback converter will also stop working and XDPL8221 will enter the latch mode. The OVP2 threshold is defined as a VS pin voltage of 2.8V, which together with the bus voltage sense divider results in the corresponding voltage at the bus.

- Bus under-voltage protection is meaningful to prevent the flyback transformer from running into saturation. When the threshold V<sub>bus\_UV</sub> is continuously triggered beyond the configured blanking time t<sub>blank\_bus\_UV</sub>, both PFC and flyback converter operations are stopped and XDPL8221 will enter the auto-restart mode.

The different OVP thresholds are illustrated in the following:

Figure 16 PFC Bus voltage protection thresholds

The important design parameters for bus voltage protection are summarized in the table below:

| Table 16 | PFC Bus voltage protection design parameters |

|----------|----------------------------------------------|

|----------|----------------------------------------------|

| Parameter                                     | Symbol                       | Value        | Unit | Configurable |

|-----------------------------------------------|------------------------------|--------------|------|--------------|

| Bus over-voltage protection level 2 threshold | V <sub>bus_OVP2</sub>        | 536          | V    | No           |

| Blanking time for OVP2                        | t <sub>blank_bus_OVP2</sub>  | 200          | ns   | Yes          |

| Reaction OVP2                                 | -                            | Auto-Restart | -    | Yes          |

| Bus over-voltage protection level 1 threshold | V <sub>bus_OVP1</sub>        | 485          | V    | Yes          |

| Blanking time for OVP1                        | t <sub>blank_bus_OVP1</sub>  | 384          | μs   | Yes          |

| Recovery threshold from OVP1                  | $V_{bus\_steady\_entry\_OV}$ | 472          | V    | Yes          |

| Bus under-voltage protection threshold        | $V_{bus_UV}$                 | 300          | V    | Yes          |

| Blanking time for under-voltage               | t <sub>blank_bus_UV</sub>    | 500          | ms   | Yes          |

| Reaction bus under-voltage protection         | -                            | Auto-Restart | -    | Yes          |

Hardware design

## 2.4.11.2 Input voltage protection

Input voltage protection is realized by monitoring the voltage at the HV pin. After the XDPL8221 is active and before the PFC boost converter is started, the input voltage is checked first. Once the input RMS voltage is between the threshold  $V_{in\_start\_max}$ , PFC will start. After this, input will be monitored continuously. If the input voltage touches the under-voltage or over-voltage threshold beyond the blanking time, XDPL8221 will enter the auto-restart mode.

The important design parameters for input voltage protection are summarized in the table below:

| Parameter                                       | Symbol                       | Value        | Unit | Configurable |

|-------------------------------------------------|------------------------------|--------------|------|--------------|

| Minimum input voltage to start PFC Converter    | Vin_start_min                | 88           | Vrms | Yes          |

| Maximum input voltage to start PFC Converter    | $V_{\text{in\_start\_max}}$  | 308          | Vrms | Yes          |

| Input under-voltage protection during operation | V <sub>in_UV</sub>           | 76           | Vrms | Yes          |

| Blanking time for input over-/under-voltage     | t <sub>blank_Vin_OV_UV</sub> | 100          | ms   | Yes          |

| Reaction input under-voltage protection         | -                            | Auto-Restart | -    | Yes          |

| Input over-voltage protection during operation  | V <sub>in_OV</sub>           | 320          | Vrms | Yes          |

| Reaction input over-voltage protection          | -                            | Auto-Restart | -    | Yes          |

| Table 17 | PFC Input voltage protection design parameters |

|----------|------------------------------------------------|

|----------|------------------------------------------------|

Note:

The thresholds listed in the table above are related to the selected HV resistor of 60 kΩ. Different HV resistor will result in different thresholds.

## 2.4.11.3 Over-current protection

The over-current protection is necessary to control the maximum current flowing through the PFC boost inductor and PFC MOSFET so that they are not over-powered. This is realized by monitoring the voltage across the PFC shunt resistor. If the voltage reaches the threshold and beyond the blanking time, PFC gate will be switched off. There are two level of the over-current protection:

- Over-current Protection level 1: by touching the threshold V<sub>CS\_PFC\_OCP1</sub> of the OCP1 beyond the blanking time t<sub>blank\_OCP1\_PFC</sub>, PFC gate will be switched off and the next switching cycle will be started again after the zero-crossing signal is detected. No further action will be taken. This is a cycle by cycle power limitation.

- Over-current Protection level 2: by touching the threshold V<sub>CS\_PFC\_OCP2</sub> of the OCP2, both PFC and flyback gate drive will be switched off and XDPL8221 will enter the latch mode

The important design parameters for PFC over-current protection are summarized in the table below:

| Parameter                                     | Symbol                      | Value | Unit | Configurable |

|-----------------------------------------------|-----------------------------|-------|------|--------------|

| PFC Over-current protection level 1 threshold | V <sub>CS_PFC_OCP1</sub>    | 0.75  | V    | Yes          |

| Blanking time for PFC OCP1                    | t <sub>blank_OCP1_PFC</sub> | 200   | ns   | Yes          |

| PFC Over-current protection level 2 threshold | V <sub>CS_PFC_OCP2</sub>    | 1.6   | V    | No           |

| Blanking time for PFC OCP2                    | t <sub>blank_OCP2_PFC</sub> | 600   | ns   | Yes          |

| Reaction to PFC OCP2                          | -                           | Latch | -    | Yes          |

Table 18

PFC Over-current design parameters

Hardware design

## 2.4.11.4 Soft-start failure

When the input voltage is low beyond the nominal range or the output is over-loaded, the start-up time of the PFC boost converter may be extended to an unexpected long value. In both cases, the protection could be triggered and XDPL8221 will enter the auto-restart mode. The PFC soft-start time  $t_{start_PFC}$  is defined and monitored from the moment that PFC stage is started till the bus voltage reaches the threshold  $V_{bus_steady_entry_UV}$ . If this time exceeds the maximum allowed PFC soft-start time  $t_{start_PFC_max}$ , protection will be triggered and XDPL8221 will enter the auto-restart mode.

The important design parameters for soft-start failure are summarized in the table below:

Table 19

PFC Soft-start failure design parameters

| Parameter                           | Symbol                       | Value | Unit | Configurable |

|-------------------------------------|------------------------------|-------|------|--------------|

| Voltage threshold for start-up end  | $V_{bus\_steady\_entry\_UV}$ | 448   | V    | Yes          |

| Maximum allowed PFC soft-start time | t <sub>start_PFC_max</sub>   | 400   | ms   | Yes          |

## 2.4.11.5 CCM protection

Continuous conduction mode (CCM) operation occurs when the magnetizing current does not decrease to zero before the next switching cycle starts. This happens usually when the difference of the bus voltage and input voltage is very small, which is the case of start-up or boost diode short. However, when the output is over-loaded or input voltage is too low, the inductor peak current will be very high and the demagnetizing of boost inductor cannot be operated completely, too. At start-up, the CCM operation is allowed for limited time but in other conditions, XDPL8221 must enter the protection mode.

The CCM operation is monitored at the PFC CS pin. When the ZCD signal does not come till the maximum switching period time-out happens, it will be treated as a CCM cycle. If the CCM operation happens beyond the blanking time  $t_{blank\_CCM\_PFC}$ , XDPL8221 will enter the auto-restart mode.

The important design parameters for CCM protection are summarized in the table below:

#### Table 20 PFC CCM protection design parameters

| Parameter                           | Symbol                | Value | Unit | Configurable |

|-------------------------------------|-----------------------|-------|------|--------------|

| Blanking time for PFC CCM operation | $t_{blank\_CCM\_PFC}$ | 12    | ms   | Yes          |

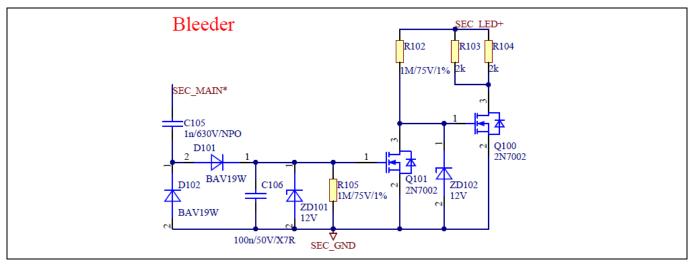

#### 2.5 Design the flyback converter

The flyback converter takes the boosted DC voltage as input and converts it to a configurable wide range DC output with the programmable constant current on the secondary side. The controller XDPL8221 provides a primary side output voltage and current control without the external regulator on the secondary side. This chapter describes the methodology for designing the multi-mode control (QRM+DCM+ABM) flyback converter based on XDPL8221, which includes the flyback transformer design, power losses estimation, selection guide for power semiconductor devices and passive components.

The design specification for the 100 W driver reference design is given in the following table:

#### Table 21 Flyback converter design specification

| Flyback converter        |                      |       |      |  |  |

|--------------------------|----------------------|-------|------|--|--|

| Parameter                | Symbol               | Value | Unit |  |  |

| Minimum DC input voltage | V <sub>bus_min</sub> | 440   | V    |  |  |

#### Hardware design

| Nominal DC input voltage                        | V <sub>bus</sub>       | 460         | V   |

|-------------------------------------------------|------------------------|-------------|-----|

| Maximum DC input voltage                        | $V_{\text{bus}\_max}$  | 485         | V   |

| Maximum flyback converter output power          | P <sub>O_max</sub>     | 100         | W   |

| Minimum switching frequency                     | f <sub>sw_FB_min</sub> | 16          | kHz |

| Estimated flyback converter power efficiency    | $\eta_{FB}$            | < 93        | %   |

| Flyback converter output voltage                | V <sub>out</sub>       | 16 to 48    | V   |

| Flyback converter output over-voltage threshold | V <sub>out_OV</sub>    | 53          | V   |

| Flyback converter output current                | l <sub>out</sub>       | 550 to 2500 | mA  |

| Maximum flyback MOSFET drain-source voltage     | $V_{DS_max}$           | 800         | V   |

| Secondary diode forward voltage                 | V <sub>F</sub>         | 1           | V   |

| Secondary diode voltage rating                  | V <sub>RRM</sub>       | 400         | V   |

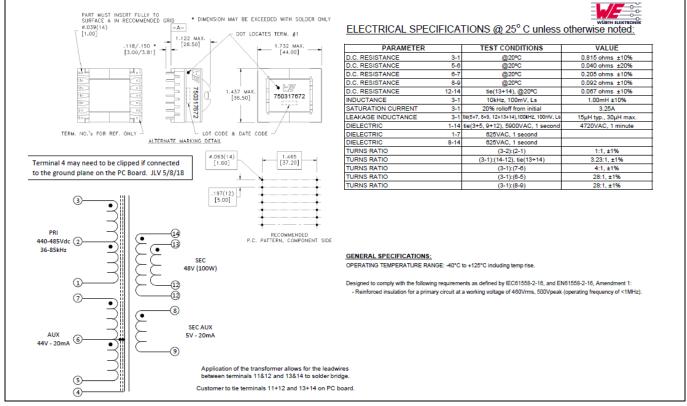

#### 2.5.1 Design the flyback transformer

For flyback converter, the transformer is the most important factor that determines the performance such as the efficiency, output regulation and EMI. Contrary to the normal transformer, the flyback transformer is inherently an inductor that provides energy storage, coupling and isolation for the flyback converter. In the general transformer, the current flows in both the primary and secondary winding at the same time. However, in the flyback transformer, the current flows only in the primary winding while the energy in the core is charged and in the secondary winding while the energy in the core is discharged. Usually a gap is introduced between the cores to increase the energy storage capacity. The general transformer design procedures are briefly described below.

#### 2.5.1.1 Transformer turns ratio

The transformer turns-ratio n decides not only the reflected voltage from the secondary side to the primary side, which affects the primary side flyback MOSFET selection, but also the maximum switching duty cycle  $D_{max}$  of the flyback converter.

A higher transformer turns-ratio steps down the voltage from input to output more, such that a higher duty cycle may be employed. The maximum duty cycle is exactly defined by the turn-ratio, since magnetizing time and demagnetizing time are functions of input voltage and reflected output voltage respectively. The duty cycle of the QR mode flyback can be calculated as following:

$$D = \frac{t_{on}}{t_{on} + t_{off}} = \frac{n * (V_{out} + V_F)}{V_{bus} + n * (V_{out} + V_F)}$$

with

$$t_{off} = t_{demag} + 0.5 * T_{osc}$$

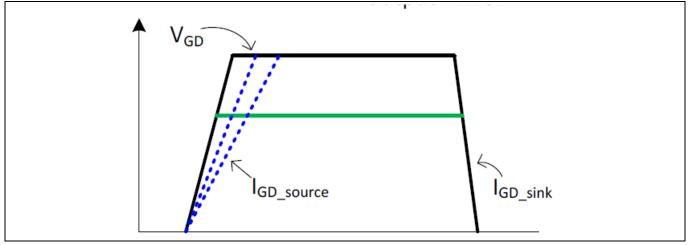

This expression for D clearly approaches 1 asymptotically when n approaches ∞ (and 0 when n approaches 0). Nevertheless, a high turns-ratio means high reflected voltage from the secondary to primary side, which requires a higher MOSFET drain-source break down voltage. Therefore, the maximum transformer turns-ratio depends on the expected maximum input voltage and reflected output voltage, since the sum of the two determines the voltage stress across drain-source of primary side MOSFET during the demagnetization period like following:

$$V_{DS\_MOS\_max\_FB} = V_{bus\_max} + n * V_{out\_max}$$

## XDPL8221 Digital PFC+Flyback Controller IC XDP™ Digital Power Hardware design

During turn-off of the primary side MOSFET, energy stored in leakage inductance will charge up the  $C_{oss}$  of the primary MOSFET causing an overvoltage spike to occur on top of the steady-state stress voltage. Depending on the leakage inductance value and the  $C_{oss}$  characteristics of the MOSFET employed, the snubber circuit can be tuned to guarantee operation within the voltage rating of the MOSFET, when employing a de-rating factor as is norm in the industry. In the 100 W driver reference design, 800 V MOSFET is selected with a de-rating of 85% is assumed. So the maximum turns-ratio  $n_{max}$  is calculated as:

$$n \le n_{max} = \frac{0.85 * V_{DS_{MOS_{FB}}} - V_{bus_max}}{V_{out_max}} = 3.67$$

A low transformer turns-ratio could be desirable for several reasons. One reason is the conduction losses on the output loop, since the primary peak current is defined independent of the transformer turns-ratio by the DCM Flyback power equation:

$$P_{out} = \frac{1}{2} * L_{FB} * i_{p\_pk}^2 * f_{FB} * \eta_{FB}$$

The output loop peak-current is the input peak current reflected across the transformer:

$$i_{s\_pk} = n * i_{p\_pk}$$

A smaller turns-ratio will reduce the secondary peak current and thus the conduction loss. One other reason could be the construction of the transformer itself. In order to get a strong coupling with accurate turns-ratio, there is a minimum practical limit to the number of physical turns on the output-side. With a minimum output winding turns-count and a maximum input winding turns-count, a practical upper limit to the transformer turns-ratio will also exist. With the electrical requirements known, the minimum transformer turns-ratio can be found similarly as the maximum, but based on voltage rating for the desired output rectifier diode V<sub>RRM</sub>. The steady state voltage stress across the diode is the sum of the transformer winding voltage and the output voltage, both of which have known maxima from previous calculations. The MOSFET voltage rating must adhere to de-rating criteria:

$$n \ge n_{min} = \frac{V_{bus\_max}}{0.8 * V_{RRM} - V_{out\_max}} = 2.52$$

Nevertheless, a very low turns-ratio leads to a low duty cycle or smaller on-time at light load. If this small on-time is not able to be output by the controller, then the burst mode is unavoidable, which could lead to higher ripple on the output and audible noise. In the 100 W driver reference design, the turns-ratio is chosen as:

$$\frac{N_p}{N_s} = n = 3.2$$

#### 2.5.1.2 Primary magnetizing inductance

The primary magnetizing inductance scaling can be done in several ways. One such way would be to ensure that at least full power can be produced at lowest bus voltage while staying in QRM operation.

As already described in the previous chapter, the maximum duty cycle occurs at minimum bus voltage and maximum output voltage:

$$D_{max\_FB} = \frac{n * (V_{out\_max} + V_{F\_D\_sec})}{V_{bus\_min} + n * (V_{out\_max} + V_{F\_D\_sec})} = 0.28$$

## XDPL8221 Digital PFC+Flyback Controller IC XDP<sup>™</sup> Digital Power Hardware design

But as the voltage and current could change at the full output power, the more critical working point happens at the maximum output current under full load. So the possible minimum duty cycle at full power in QRM operation is:

$$D_{min\_QRM\_FB} = \frac{n * (\frac{P_{out\_max\_FB}}{I_{out\_max\_FB}} + V_{F\_D\_sec})}{V_{bus\_min} + n * (\frac{P_{out\_max\_FB}}{I_{out\_max\_FB}} + V_{F\_D\_sec})} = 0.23$$

If a minimum switching frequency for full load in the QRM of 35 kHz is assumed, the maximum possible magnetizing inductance is then calculated as:

$$L_{p\_max\_FB} = \frac{V_{bus\_min}^2 * D_{min\_QRM\_FB}^2 * \eta_{FB}}{2 * P_{o\_max\_FB} * f_{sw\_QR\_min\_FB}} = 1.18 \text{ mH}$$

Thus, in the 100W reference design, the primary flyback main inductance is chosen as:

$$L_{P\_FB} = 1 \text{m}H < L_{p\_FB\_max}$$

Therewith the maximum reflected voltage is:

$$V_{R max} = n * (V_{out max} + V_F) = 172.8 V$$

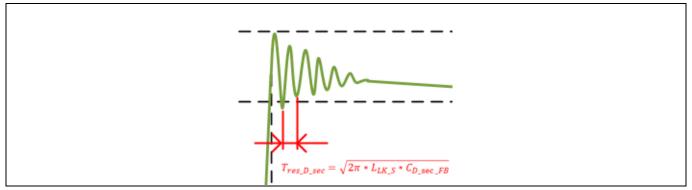

The minimum switching frequency in the QRM happens at full load with full output current and minimum bus voltage, if an oscillation period  $T_{osc\_FB}$  in the QRM is assumed as 1.5µs:

$$f_{sw\_QR\_min\_FB} = \frac{1}{\frac{1}{\frac{V_{bus\_min}^2 * D_{\min\_QRM\_FB}^2 * \eta_{FB}}{2 * P_{o\_max\_FB} * L_{p\_FB}}} + 0.5 * T_{osc\_FB}} = 40 \, kHz$$

The switching frequency at full load with full output voltage and minimum bus voltage is:

$$f_{sw_QR_Vout_max\_FB} = \frac{1}{\frac{1}{\frac{V_{bus\_min}^2 * D_{max\_FB}^2 * \eta_{FB}}{2 * P_{o\_max\_FB} * L_{p\_FB}}} + 0.5 * T_{osc\_FB}} = 63.9 \, kHz$$

The maximum primary peak current appears at minimum bus voltage, maximum output current and full load:

$$I_{p_pk_max_FB} = \sqrt{\frac{2 * P_{O_max}}{L_{P_FB} * \eta_{FB} * f_{sw_FB_QR_min}}} = 2.37 A$$

The maximum on-time happens at minimum bus voltage, maximum output current and full load:

$$t_{on\_max\_FB} = \frac{L_{p\_FB} * I_{p\_pk\_max\_FB}}{V_{bus\_min}} = 5.38 \,\mu s$$

The maximum primary RMS current is:

$$I_{p\_rms\_max\_FB} = I_{p\_pk\_max\_FB} * \sqrt{\frac{D_{min\_QRM\_FB}}{3}} = 0.65 A$$

The maximum primary DC current is:

$$I_{p\_DC\_max\_FB} = \frac{1}{2} * I_{p\_pk\_max\_FB} * D_{min\_QRM\_FB} = 0.26 A$$

#### XDPL8221 Digital PFC+Flyback Controller IC XDP<sup>™</sup> Digital Power Hardware design

The maximum primary AC current is:

$$I_{p\_AC\_max\_FB} = \sqrt{I_{p\_rms\_max\_FB}^2 - I_{p\_DC\_max\_FB}^2} = 0.59 A$$

The maximum secondary peak current is:

$$I_{s_pk_max_FB} = n * I_{p_pk_max_FB} = 7.6 A$$

The maximum secondary RMS current is