# 3.3V CMOS 16-BIT IDT7 TRANSPARENT D-TYPE OBS LATCH WITH 3-STATE OUTPUTS, 5 VOLT TOLERANT I/O AND BUS-HOLD

# IDT74LVCH16373A OBSOLETE PART

# **FEATURES:**

- Typical tsk(o) (Output Skew) < 250ps

- ESD > 2000V per MIL-STD-883, Method 3015; > 200V using machine model (C = 200pF, R = 0)

- Vcc = 3.3V ± 0.3V, Normal Range

- Vcc = 2.7V to 3.6V, Extended Range

- CMOS power levels (0.4

W typ. static)

- · All inputs, outputs, and I/O are 5V tolerant

- · Supports hot insertion

- · Available in TSSOP package

# DRIVE FEATURES:

- · High Output Drivers: ±24mA

- · Reduced system switching noise

# **APPLICATIONS:**

- 5V and 3.3V mixed voltage systems

- Data communication and telecommunication systems

# **DESCRIPTION**

The LVCH16373A 16-bit transparent D-type latch is built using advanced dual metal CMOS technology. This high-speed, low-power latch is ideal for temporary storage of data. The LVCH16373A can be used for implementing memory address latches, I/O ports, and bus drivers. The Output Enable and Latch Enable controls are organized to operate each device as two 8-bit latches or one 16-bit latch. Flow-threagy organization of signal pins simplifies lag ut. All inputs are designed withing teresis for improved noise margin

All pins of the Liv SH2 4373A can be drive arrorm. There is 3V or 5V devices. This feature is two it is use of the device as a ranslator in a mixed 3.3V/5V supply as tell.

The LCH 6373A has "bus gold" which retains the inputs' last state whenever the input goes had lightly dedance. This prevents floating inputs and eliminates the new transput up/down resistors.

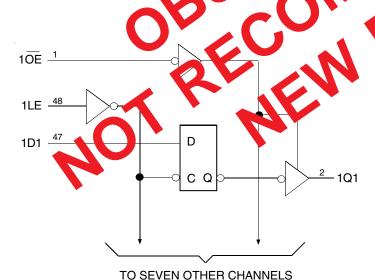

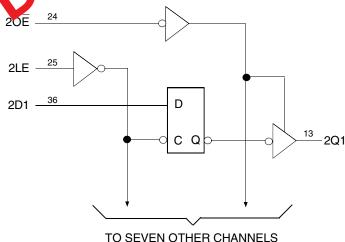

# FUNCTIONAL BLOCK DIL GI AM

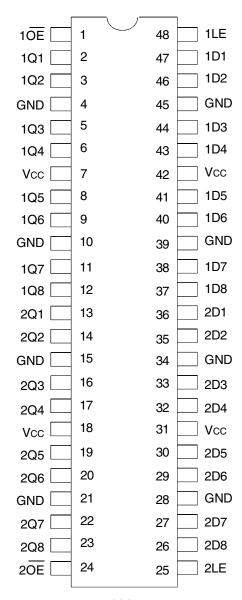

# **PIN CONFIGURATION**

TSSOP TOP VIEW

# ABSOLUTE MAXIMUM RATINGS(1)

| Symbol     | Description                                   | Max          | Unit |

|------------|-----------------------------------------------|--------------|------|

| VTERM      | Terminal Voltage with Respect to GND          | -0.5 to +6.5 | V    |

| Tstg       | Storage Temperature                           | -65 to +150  | °C   |

| lout       | DC Output Current                             | -50 to +50   | mA   |

| lik<br>lok | Continuous Clamp Current,<br>VI < 0 or Vo < 0 | -50          | mA   |

| lcc<br>Iss | Continuous Current through each Vcc or GND    | ±100         | mA   |

### NOTE:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# CAPACITANCE (TA = +25°C, F = 1.0MHz)

| Symbol | Parameter <sup>(1)</sup> | Conditions | Тур. | Max. | Unit |

|--------|--------------------------|------------|------|------|------|

| CIN    | Input Capacitance        | VIN = 0V   | 4.5  | 6    | pF   |

| Соит   | Output Capacitance       | Vout = 0V  | 6.5  | 8    | pF   |

| CI/O   | I/O Port Capacitance     | VIN = 0V   | 6.5  | 8    | pF   |

### NOTE:

1. As applicable to the device type.

# **PIN DESCRIPTION**

| Pin Names | Description                       |  |

|-----------|-----------------------------------|--|

| хDх       | Data Inputs <sup>(1)</sup>        |  |

| xLE       | Latch Enable Input                |  |

| xŌĒ       | Output Enable Inputs (Active LOW) |  |

| хОх       | 3-State Outputs                   |  |

### NOTE:

1. These pins have "Bus-Hold". All other pins are standard inputs, outputs, or I/Os.

# FUNCTION TABLE(1)

|     | Inputs |                   |                  |

|-----|--------|-------------------|------------------|

| хDх | xLE    | х <mark>ОЕ</mark> | хQх              |

| Н   | Н      | L                 | Н                |

| L   | Н      | L                 | L                |

| Х   | L      | L                 | Q <sup>(2)</sup> |

| Х   | Х      | Н                 | Z                |

### NOTES:

- 1. H = HIGH Voltage Level

- X = Don't Care

- L = LOW Voltage Level

- Z = High-Impedance

- 2. Output level before the indicated steady-state input conditions were established.

# IDT74LVCH16373A 3.3VCMOS16-BITTRANSPARENTD-TYPELATCH

# DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified:

Operating Condition:  $TA = -40^{\circ}C$  to  $+85^{\circ}C$

| Symbol       | Parameter                                   | Test Cor                          | nditions            | Min.         | Typ. <sup>(1)</sup> | Max. | Unit |

|--------------|---------------------------------------------|-----------------------------------|---------------------|--------------|---------------------|------|------|

| ViH          | Input HIGH Voltage Level                    | Vcc = 2.3V to 2.7V                |                     | 1.7          | _                   | _    | V    |

|              |                                             | Vcc = 2.7V to 3.6V                |                     | 2            | _                   | _    |      |

| VIL          | Input LOW Voltage Level                     | Vcc = 2.3V to 2.7V                |                     | _            | _                   | 0.7  | V    |

|              |                                             | Vcc = 2.7V to 3.6V                |                     | _            | _                   | 0.8  |      |

| Іін          | Input Leakage Current                       | Vcc = 3.6V                        | VI = 0 to 5.5V      | _            | _                   | ±5   | μA   |

| lıL          |                                             |                                   |                     |              |                     |      |      |

| lozн         | High Impedance Output Current               | Vcc = 3.6V                        | Vo = 0 to 5.5V      | _            | _                   | ±10  | μA   |

| lozl         | (3-State Output pins)                       |                                   |                     |              |                     |      |      |

| loff         | Input/Output Power Off Leakage              | $VCC = 0V$ , $VIN or VO \le 5.5V$ |                     | _            | _                   | ±50  | μA   |

| Vik          | Clamp Diode Voltage                         | VCC = 2.3V, IIN = -18mA           |                     | _            | -0.7                | -1.2 | V    |

| VH           | Input Hysteresis                            | Vcc = 3.3V                        |                     | T -          | 100                 | _    | mV   |

| ICCL         | Quiescent Power Supply Current              | VCC = 3.6V                        | VIN = GND or VCC    | _            | _                   | 10   | μΑ   |

| Iссн<br>Iссz |                                             | $3.6 \le VIN \le 5.5V^{(2)}$      |                     | <del> </del> | _                   | 10   |      |

| ∆lcc         | Quiescent Power Supply Current<br>Variation | One input at Vcc - 0.6V, other in | nputs at Vcc or GND | _            |                     | 500  | μΑ   |

# NOTES:

- 1. Typical values are at Vcc = 3.3V, +25°C ambient.

- 2. This applies in the disabled state only.

# **BUS-HOLD CHARACTERISTICS**

| Symbol | Parameter <sup>(1)</sup>         | Test Conditions |                | Min.        | Typ. <sup>(2)</sup> | Max. | Unit |

|--------|----------------------------------|-----------------|----------------|-------------|---------------------|------|------|

| Івнн   | Bus-Hold Input Sustain Current   | Vcc = 3V        | VI = 2V        | <b>-</b> 75 | _                   | _    | μΑ   |

| IBHL   |                                  |                 | VI = 0.8V      | 75          | _                   | _    |      |

| Івнн   | Bus-Hold Input Sustain Current   | Vcc = 2.3V      | VI = 1.7V      | _           | _                   | _    | μΑ   |

| IBHL   |                                  |                 | VI = 0.7V      | _           | _                   | _    |      |

| Івнно  | Bus-Hold Input Overdrive Current | Vcc = 3.6V      | VI = 0 to 3.6V | _           | _                   | ±500 | μΑ   |

| Івньо  |                                  |                 |                |             |                     |      |      |

# NOTES:

- 1. Pins with Bus-Hold are identified in the pin description.

- 2. Typical values are at Vcc = 3.3V, +25°C ambient.

# IDT74LVCH16373A 3.3VCMOS16-BITTRANSPARENTD-TYPE LATCH

# **OUTPUT DRIVE CHARACTERISTICS**

| Symbol | Parameter           | Test Con           | ditions <sup>(1)</sup> | Min.    | Max. | Unit |

|--------|---------------------|--------------------|------------------------|---------|------|------|

| Vон    | Output HIGH Voltage | Vcc = 2.3V to 3.6V | IOH = - 0.1mA          | Vcc-0.2 | _    | V    |

|        |                     | Vcc = 2.3V         | IOH = -6mA             | 2       | _    |      |

|        |                     | Vcc = 2.3V         | Iон = - 12mA           | 1.7     | _    |      |

|        |                     | Vcc = 2.7V         |                        | 2.2     | _    |      |

|        |                     | VCC = 3V           |                        | 2.4     | _    |      |

|        |                     | Vcc = 3V           | IOH = - 24mA           | 2.2     | _    |      |

| Vol    | Output LOW Voltage  | Vcc = 2.3V to 3.6V | IoL = 0.1mA            | _       | 0.2  | V    |

|        |                     | Vcc = 2.3V         | IoL = 6mA              | _       | 0.4  |      |

|        |                     |                    | IoL = 12mA             | _       | 0.7  |      |

|        |                     | Vcc = 2.7V         | IoL = 12mA             | _       | 0.4  |      |

|        |                     | VCC = 3V           | IOL = 24mA             | 1       | 0.55 |      |

### NOTF:

# OPERATING CHARACTERISTICS, Vcc = 3.3V ± 0.3V, Ta = 25°C

| Symbol | Parameter                                                | Test Conditions     | Typical | Unit |

|--------|----------------------------------------------------------|---------------------|---------|------|

| CPD    | Power Dissipation Capacitance per Latch Outputs enabled  | CL = 0pF, f = 10Mhz | 39      | pF   |

| CPD    | Power Dissipation Capacitance per Latch Outputs disabled |                     | 6       |      |

# SWITCHING CHARACTERISTICS(1)

|           |                                         | Vcc = | = 2.7V | Vcc = 3.3 | V ± 0.3V |      |

|-----------|-----------------------------------------|-------|--------|-----------|----------|------|

| Symbol    | Parameter                               | Min.  | Max.   | Min.      | Max.     | Unit |

| tplH      | Propagation Delay                       | _     | 4.9    | 1.6       | 4.2      | ns   |

| tphL tphL | xDx to xQx                              |       |        |           |          |      |

| tplH      | Propagation Delay                       | _     | 5.3    | 2.1       | 4.6      | ns   |

| tphL tphL | xLE to xQx                              |       |        |           |          |      |

| tpzh      | Output Enable Time                      | _     | 5.7    | 1.3       | 4.7      | ns   |

| tpzL      | xOE to xQx                              |       |        |           |          |      |

| tphz      | Output Disable Time                     | _     | 6.3    | 2.5       | 5.9      | ns   |

| tplz      | xOE to xQx                              |       |        |           |          |      |

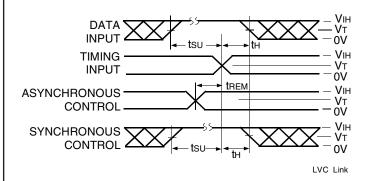

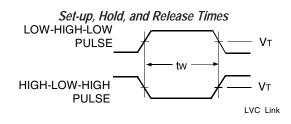

| tsu       | Set-up Time, data before LE↓HIGH or LOW | 1.7   | _      | 1.7       | _        | ns   |

| tH        | Hold Time, data after LE↓ HIGH or LOW   | 1.2   | _      | 1.2       | _        | ns   |

| tw        | Pulse Width xLE HIGH                    | 3.3   | _      | 3.3       | _        | ns   |

| tsk(o)    | Output Skew <sup>(2)</sup>              | _     | _      | _         | 500      | ps   |

### NOTES:

- 1. See TEST CIRCUITS AND WAVEFORMS.  $TA = -40^{\circ}C$  to  $+85^{\circ}C$ .

- 2. Skew between any two outputs of the same package and switching in the same direction.

<sup>1.</sup> VIH and VIL must be within the min. or max. range shown in the DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE table for the appropriate Vcc range. TA = - 40°C to + 85°C.

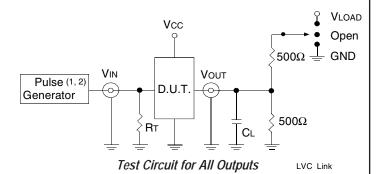

# TEST CIRCUITS AND WAVEFORMS

# **TEST CONDITIONS**

| Symbol | $Vcc^{(1)} = 3.3V \pm 0.3V$ | Vcc <sup>(1)</sup> =2.7V | Vcc <sup>(2)</sup> =2.5V±0.2V | Unit |

|--------|-----------------------------|--------------------------|-------------------------------|------|

| VLOAD  | 6                           | 6                        | 2 x Vcc                       | V    |

| VIH    | 2.7                         | 2.7                      | Vcc                           | V    |

| VT     | 1.5                         | 1.5                      | Vcc / 2                       | V    |

| VLZ    | 300                         | 300                      | 150                           | mV   |

| VHZ    | 300                         | 300                      | 150                           | mV   |

| CL     | 50                          | 50                       | 30                            | pF   |

### **DEFINITIONS:**

CL = Load capacitance: includes jig and probe capacitance.

RT = Termination resistance: should be equal to ZouT of the Pulse Generator.

### NOTES:

- 1. Pulse Generator for All Pulses: Rate  $\leq$  10MHz: tF  $\leq$  2.5ns: tR  $\leq$  2.5ns.

- 2. Pulse Generator for All Pulses: Rate  $\leq$  10MHz; tF  $\leq$  2ns; tR  $\leq$  2ns.

# **SWITCH POSITION**

| Test                                    | Switch |

|-----------------------------------------|--------|

| Open Drain<br>Disable Low<br>Enable Low | VLOAD  |

| Disable High<br>Enable High             | GND    |

| All Other Tests                         | Open   |

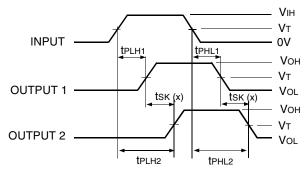

tsk(x) = |tplh2 - tplh1| or |tphl2 - tphl1|

Output Skew - tsk(x)

## NOTES:

- For tsk(o) OUTPUT1 and OUTPUT2 are any two outputs.

- For tsk(b) OUTPUT1 and OUTPUT2 are in the same bank.

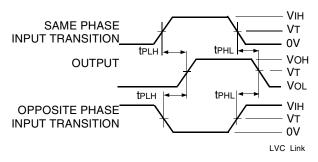

# Propagation Delay

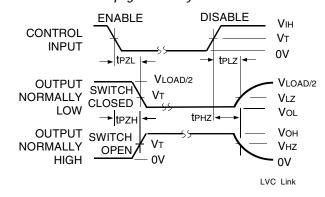

# Enable and Disable Times

1. Diagram shown for input Control Enable-LOW and input Control Disable-HIGH.

Pulse Width

LVC Link

IDT74LVCH16373A 3.3VCMOS16-BITTRANSPARENTD-TYPE LATCH

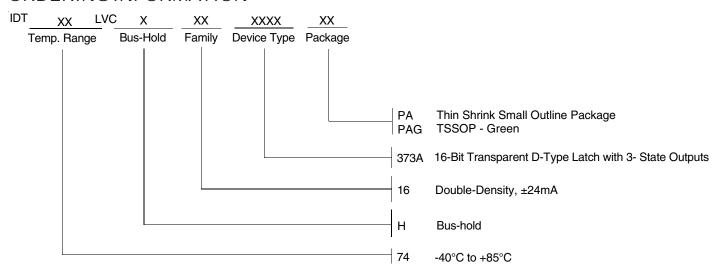

# ORDERING INFORMATION

# **DATASHEET DOCUMENT HISTORY**

07/13/2015 PDN# CQ-14-05 issued. See IDT.com for PDN specifics.

09/06/2019 Datasheet changed to Obsolete Status.

### **Notice**

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.4.0-1 November 2017)

# Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

# Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

# Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

www.renesas.com/contact/