### FEATURES

- PLL generated or direct master clock

- Low EMI design

- DAC with 110 dB dynamic range and SNR

- 96 dB THD + N

- 3.3 V single supply

- Tolerance for 5 V logic inputs

- Supports 24 bits and 8 kHz to 192 kHz sample rates

- Differential DAC output

- Log volume control with autoramp function

- SPI® controllable for flexibility

- Software-controllable clickless mute

- Software power-down

- Right-justified, left-justified, I<sup>2</sup>S, and TDM modes

- Master and slave modes up to 16-channel input/output

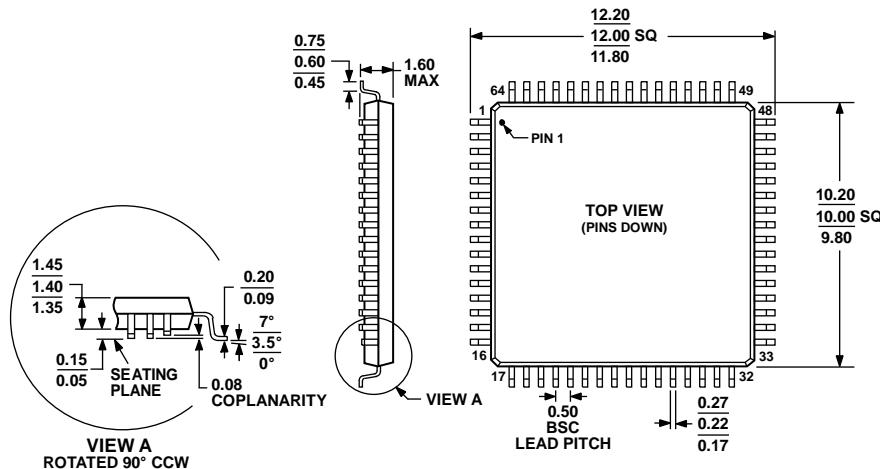

- 64-lead LQFP

- Qualified for automotive applications

### APPLICATIONS

- Automotive audio systems

- Home Theater Systems

- Set-top boxes

- Digital audio effects processors

### GENERAL DESCRIPTION

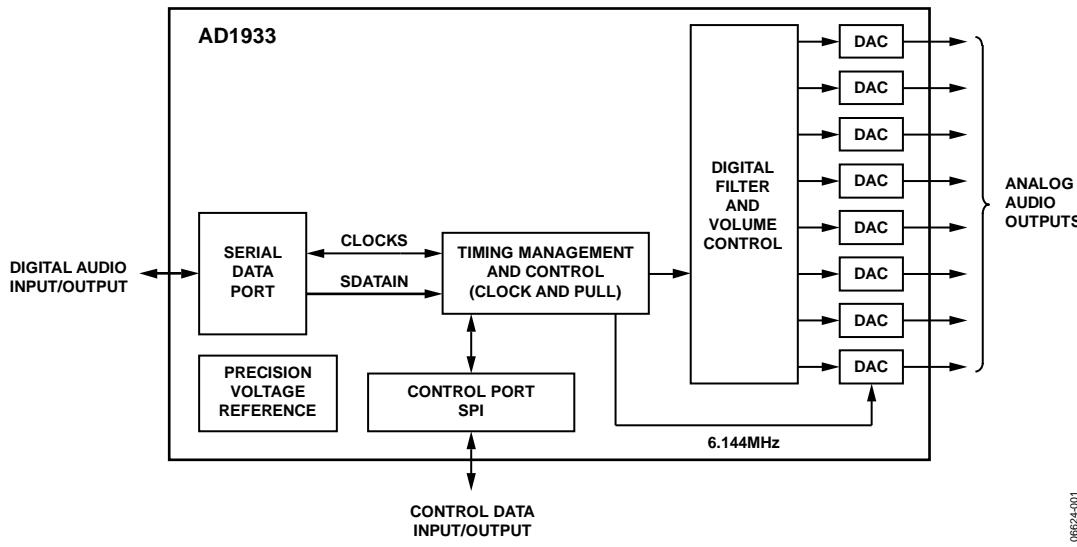

The AD1933 is a high performance, single chip that provides eight digital-to-analog converters (DACs) with differential output using the Analog Devices, Inc., patented multibit sigma-delta ( $\Sigma$ - $\Delta$ ) architecture. An SPI port is included, allowing a microcontroller to adjust volume and many other parameters. The AD1933 operates from 3.3 V digital and analog supplies. The AD1933 is available in a 64-lead (differential output) LQFP. Other members of this family include a single-ended DAC output version.

The AD1933 is designed for low EMI. This consideration is apparent in both the system and circuit design architectures. By using the on-board PLL to derive the master clock from the LR clock or from an external crystal, the AD1933 eliminates the need for a separate high frequency master clock and can also be used with a suppressed bit clock. The DACs are designed using the latest Analog Devices continuous time architectures to further minimize EMI. By using 3.3 V supplies, power consumption is minimized, further reducing emissions.

### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

06824-001

Rev. E

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©2007–2013 Analog Devices, Inc. All rights reserved.

Technical Support [www.analog.com](http://www.analog.com)

# AD1933\* PRODUCT PAGE QUICK LINKS

Last Content Update: 12/19/2017

---

## COMPARABLE PARTS

View a parametric search of comparable parts.

## DOCUMENTATION

### Application Notes

- AN-1365: AD1933/AD1934/AD1938/AD1939/AD1974 Boot Up Application

### Data Sheet

- AD1933: 8-Channel DAC with PLL and Differential Outputs, 192 kHz, 24 Bits Data Sheet

## TOOLS AND SIMULATIONS

- AD1938 IBIS Model

## DESIGN RESOURCES

- AD1933 Material Declaration

- PCN-PDN Information

- Quality And Reliability

- Symbols and Footprints

## DISCUSSIONS

View all AD1933 EngineerZone Discussions.

## SAMPLE AND BUY

Visit the product page to see pricing options.

## TECHNICAL SUPPORT

Submit a technical question or find your regional support number.

## DOCUMENT FEEDBACK

Submit feedback for this data sheet.

---

This page is dynamically generated by Analog Devices, Inc., and inserted into this data sheet. A dynamic change to the content on this page will not trigger a change to either the revision number or the content of the product data sheet. This dynamic page may be frequently modified.

## TABLE OF CONTENTS

|                                                  |    |

|--------------------------------------------------|----|

| Features .....                                   | 1  |

| Applications .....                               | 1  |

| General Description .....                        | 1  |

| Functional Block Diagram .....                   | 1  |

| Revision History .....                           | 2  |

| Specifications.....                              | 3  |

| Test Conditions.....                             | 3  |

| Analog Performance Specifications .....          | 3  |

| Crystal Oscillator Specifications.....           | 4  |

| Digital Input/Output Specifications.....         | 4  |

| Power Supply Specifications.....                 | 5  |

| Digital Filters.....                             | 5  |

| Timing Specifications .....                      | 6  |

| Absolute Maximum Ratings.....                    | 7  |

| Thermal Resistance .....                         | 7  |

| ESD Caution.....                                 | 7  |

| Pin Configuration and Function Descriptions..... | 8  |

| Typical Performance Characteristics .....        | 10 |

| Theory of Operation .....                        | 11 |

## REVISION HISTORY

### 2/13—Rev. D to Rev. E

|                                                     |    |

|-----------------------------------------------------|----|

| Changes to t <sub>CLH</sub> Comments, Table 7 ..... | 6  |

| Changes to Serial Control Port Section .....        | 12 |

### 10/11—Rev. C to Rev. D

|                                                 |    |

|-------------------------------------------------|----|

| Changes to Pin 14 in Figure 2 and Table 10..... | 8  |

| Changes to Ordering Guide .....                 | 25 |

| Added Automotive Products Section.....          | 25 |

### 7/11—Rev. B to Rev. C

|                                                              |            |

|--------------------------------------------------------------|------------|

| Deleted Reference to I <sup>2</sup> C.....                   | Throughout |

| Changes to Table 10, DSDATAx/AUXDATA1 Pin Descriptions ..... | 8          |

|                                            |    |

|--------------------------------------------|----|

| Digital-to-Analog Converters (DACs) .....  | 11 |

| Clock Signals.....                         | 11 |

| Reset and Power-Down .....                 | 11 |

| Serial Control Port .....                  | 12 |

| Power Supply and Voltage Reference.....    | 13 |

| Serial Data Ports—Data Format.....         | 13 |

| Time-Division Multiplexed (TDM) Modes..... | 13 |

| Daisy-Chain Mode .....                     | 15 |

| Control Registers.....                     | 19 |

| Definitions.....                           | 19 |

| PLL and Clock Control Registers.....       | 19 |

| DAC Control Registers.....                 | 20 |

| Auxiliary TDM Port Control Registers ..... | 22 |

| Additional Modes.....                      | 23 |

| Application Circuits .....                 | 24 |

| Outline Dimensions .....                   | 25 |

| Ordering Guide .....                       | 25 |

| Automotive Products .....                  | 25 |

### 1/11—Rev. A to Rev. B

|                                                                   |   |

|-------------------------------------------------------------------|---|

| Changes to Features .....                                         | 1 |

| Change to Table Summary, Table 2 and Table Summary, Table 4 ..... | 4 |

| Changes to Table Summary, Table 7 .....                           | 6 |

### 9/09—Rev. 0 to Rev. A

|                                                           |    |

|-----------------------------------------------------------|----|

| Change to Title.....                                      | 1  |

| Change to Table 10 .....                                  | 9  |

| Change to Power Supply and Voltage Reference Section..... | 13 |

| Updated Outline Dimensions .....                          | 25 |

| Changes to Ordering Guide .....                           | 25 |

### 10/07—Revision 0: Initial Version

## SPECIFICATIONS

### TEST CONDITIONS

Performance of all channels is identical, exclusive of the interchannel gain mismatch and interchannel phase deviation specifications.

|                                   |                                                           |

|-----------------------------------|-----------------------------------------------------------|

| Supply voltages (AVDD, DVDD)      | 3.3 V                                                     |

| Temperature range <sup>1</sup>    | As specified in Table 1 and Table 2                       |

| Master clock                      | 12.288 MHz (48 kHz $f_s$ , 256 $\times f_s$ mode)         |

| Input sample rate                 | 48 kHz                                                    |

| Measurement bandwidth             | 20 Hz to 20 kHz                                           |

| Word width                        | 24 bits                                                   |

| Load capacitance (digital output) | 20 pF                                                     |

| Load current (digital output)     | $\pm 1$ mA or 1.5 k $\Omega$ to $\frac{1}{2}$ DVDD supply |

| Input voltage high                | 2.0 V                                                     |

| Input voltage low                 | 0.8 V                                                     |

<sup>1</sup> Functionally guaranteed at  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  case temperature.

### ANALOG PERFORMANCE SPECIFICATIONS

Specifications guaranteed at an ambient temperature of  $25^{\circ}\text{C}$ .

Table 1.

| Parameter                         | Test Conditions/Comments        | Min  | Typ         | Max       | Unit                    |

|-----------------------------------|---------------------------------|------|-------------|-----------|-------------------------|

| DIGITAL-TO-ANALOG CONVERTERS      |                                 |      |             |           |                         |

| Dynamic Range                     | 20 Hz to 20 kHz, $-60$ dB input | 102  | 107         |           | dB                      |

| No Filter (RMS)                   |                                 | 105  | 110         |           | dB                      |

| With A-Weighted Filter (RMS)      |                                 |      | 112         |           | dB                      |

| With A-Weighted Filter (Avg)      |                                 |      |             |           |                         |

| Total Harmonic Distortion + Noise | 0 dBFS                          |      |             |           |                         |

| Differential Version              | Two channels running            |      | -96         |           | dB                      |

|                                   | Eight channels running          |      | -86         | -76       | dB                      |

| Full-Scale Output Voltage         |                                 |      | 1.76 (4.96) |           | V rms (V p-p)           |

| Gain Error                        |                                 | -10  |             | +10       | %                       |

| Interchannel Gain Mismatch        |                                 | -0.2 |             | +0.2      | dB                      |

| Offset Error                      |                                 | -25  | -6          | +25       | mV                      |

| Gain Drift                        |                                 | -30  |             | +30       | ppm/ $^{\circ}\text{C}$ |

| Interchannel Isolation            |                                 |      | 100         |           | dB                      |

| Interchannel Phase Deviation      |                                 |      | 0           |           | Degrees                 |

| Volume Control Step               |                                 |      | 0.375       |           | dB                      |

| Volume Control Range              |                                 |      | 95          |           | dB                      |

| De-emphasis Gain Error            |                                 |      |             | $\pm 0.6$ | dB                      |

| Output Resistance at Each Pin     |                                 |      | 100         |           | $\Omega$                |

| REFERENCE                         |                                 |      |             |           |                         |

| Internal Reference Voltage        | FILTR pin                       |      | 1.50        |           | V                       |

| External Reference Voltage        | FILTR pin                       | 1.32 | 1.50        | 1.68      | V                       |

| Common-Mode Reference Output      | CM pin                          |      | 1.50        |           | V                       |

| REGULATOR                         |                                 |      |             |           |                         |

| Input Supply Voltage              | VSUPPLY pin                     | 4.5  | 5.0         | 5.5       | V                       |

| Regulated Supply Voltage          | VSENSE pin                      | 3.19 | 3.37        | 3.55      | V                       |

Specifications measured at a case temperature of 125°C.

Table 2.

| Parameter                         | Test Conditions/Comments      | Min  | Typ         | Max  | Unit          |

|-----------------------------------|-------------------------------|------|-------------|------|---------------|

| DIGITAL-TO-ANALOG CONVERTERS      |                               |      |             |      |               |

| Dynamic Range                     | 20 Hz to 20 kHz, -60 dB input |      |             |      |               |

| No Filter (RMS)                   |                               | 101  | 107         |      | dB            |

| With A-Weighted Filter (RMS)      |                               | 104  | 110         |      | dB            |

| With A-Weighted Filter (Average)  |                               |      | 112         |      | dB            |

| Total Harmonic Distortion + Noise | 0 dBFS                        |      |             |      |               |

| Differential Version              | Two channels running          |      | -94         |      | dB            |

|                                   | Eight channels running        |      | -86         | -70  | dB            |

| Full-Scale Output Voltage         |                               |      | 1.76 (4.96) |      | V rms (V p-p) |

| Gain Error                        |                               | -10  |             | +10  | %             |

| Interchannel Gain Mismatch        |                               | -0.2 |             | +0.2 | dB            |

| Offset Error                      |                               | -25  | -6          | +25  | mV            |

| Gain Drift                        |                               | -30  |             | +30  | ppm/°C        |

| REFERENCE                         |                               |      |             |      |               |

| Internal Reference Voltage        | FILTR pin                     |      | 1.50        |      | V             |

| External Reference Voltage        | FILTR pin                     | 1.32 | 1.50        | 1.68 | V             |

| Common-Mode Reference Output      | CM pin                        |      | 1.50        |      | V             |

| REGULATOR                         |                               |      |             |      |               |

| Input Supply Voltage              | VSUPPLY pin                   | 4.5  | 5.0         | 5.5  | V             |

| Regulated Supply Voltage          | VSENSE pin                    | 3.2  | 3.43        | 3.65 | V             |

## CRYSTAL OSCILLATOR SPECIFICATIONS

Table 3.

| Parameter        | Min | Typ | Max | Unit  |

|------------------|-----|-----|-----|-------|

| Transconductance |     | 3.5 |     | mmhos |

## DIGITAL INPUT/OUTPUT SPECIFICATIONS

-40°C < T<sub>C</sub> < +125°C, DVDD = 3.3 V ± 10%.

Table 4.

| Parameter                                    | Test Conditions/Comments                                                               | Min         | Typ      | Max      | Unit |

|----------------------------------------------|----------------------------------------------------------------------------------------|-------------|----------|----------|------|

| High Level Input Voltage (V <sub>IH</sub> )  |                                                                                        | 2.0         |          |          | V    |

| High Level Input Voltage (V <sub>IH</sub> )  | MCLKI/XI pin                                                                           | 2.2         |          |          | V    |

| Low Level Input Voltage (V <sub>IL</sub> )   |                                                                                        |             | 0.8      |          | V    |

| Input Leakage                                | I <sub>IH</sub> @ V <sub>IH</sub> = 2.4 V<br>I <sub>IL</sub> @ V <sub>IL</sub> = 0.8 V |             | 10<br>10 | μA<br>μA |      |

| High Level Output Voltage (V <sub>OH</sub> ) | I <sub>OH</sub> = 1 mA                                                                 | DVDD - 0.60 |          |          | V    |

| Low Level Output Voltage (V <sub>OL</sub> )  | I <sub>OL</sub> = 1 mA                                                                 |             | 0.4      |          | V    |

| Input Capacitance                            |                                                                                        |             | 5        |          | pF   |

## POWER SUPPLY SPECIFICATIONS

Table 5.

| Parameter                    | Test Conditions/Comments          | Min | Typ | Max | Unit |

|------------------------------|-----------------------------------|-----|-----|-----|------|

| SUPPLIES                     |                                   |     |     |     |      |

| Voltage                      | DVDD                              | 3.0 | 3.3 | 3.6 | V    |

|                              | AVDD                              | 3.0 | 3.3 | 3.6 | V    |

|                              | VSUPPLY                           | 4.5 | 5.0 | 5.5 | V    |

| Digital Current              | Master clock = 256 $f_s$          |     |     |     |      |

| Normal Operation             | $f_s$ = 48 kHz                    |     | 56  |     | mA   |

|                              | $f_s$ = 96 kHz                    |     | 65  |     | mA   |

|                              | $f_s$ = 192 kHz                   |     | 95  |     | mA   |

|                              | $f_s$ = 48 kHz to 192 kHz         |     | 2.0 |     | mA   |

| Power-Down                   |                                   |     |     |     |      |

| Analog Current               |                                   |     |     |     |      |

| Normal Operation             |                                   |     | 74  |     | mA   |

| Power-Down                   |                                   |     | 23  |     | mA   |

| DISSIPATION                  |                                   |     |     |     |      |

| Operation                    | Master clock = 256 $f_s$ , 48 kHz |     |     |     |      |

| All Supplies                 |                                   |     | 429 |     | mW   |

| Digital Supply               |                                   |     | 185 |     | mW   |

| Analog Supply                |                                   |     | 244 |     | mW   |

| Power-Down, All Supplies     |                                   |     | 83  |     | mW   |

| POWER SUPPLY REJECTION RATIO |                                   |     |     |     |      |

| Signal at Analog Supply Pins | 1 kHz, 200 mV p-p                 |     | 50  |     | dB   |

|                              | 20 kHz, 200 mV p-p                |     | 50  |     | dB   |

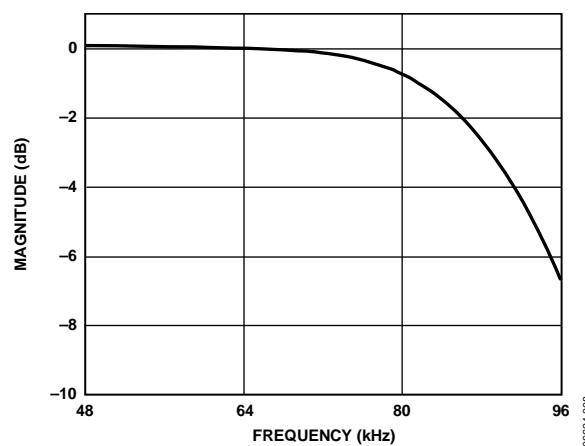

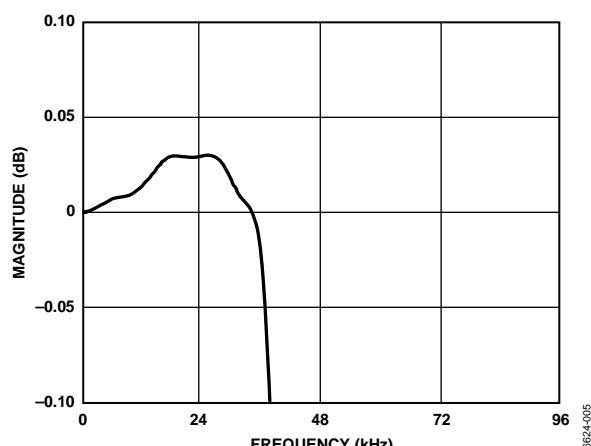

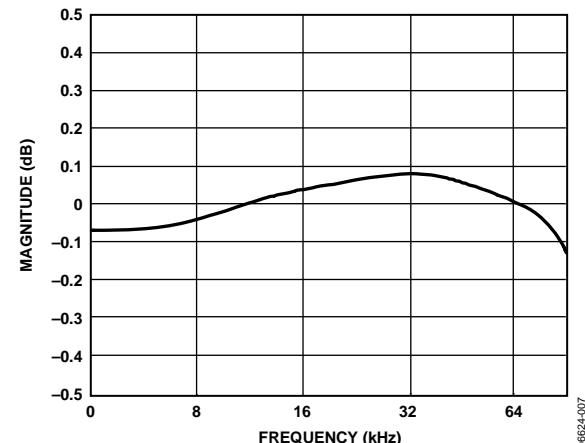

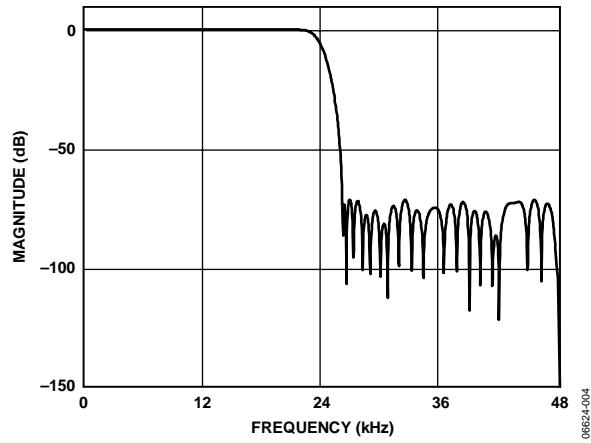

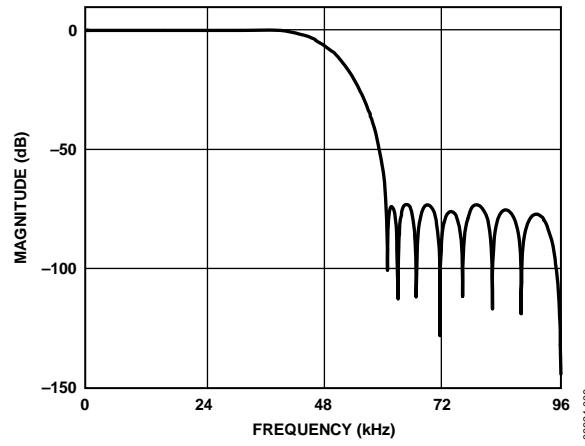

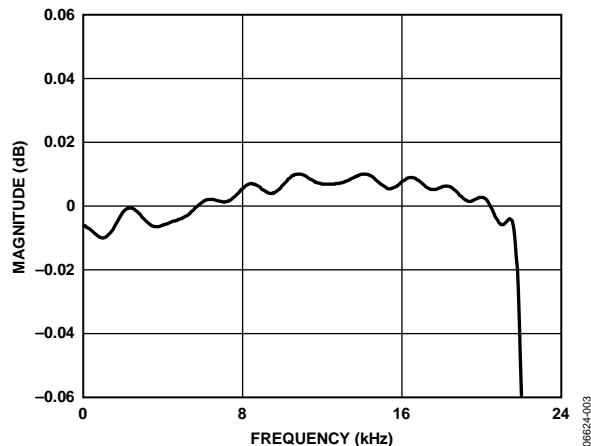

## DIGITAL FILTERS

Table 6.

| Parameter                | Mode                            | Factor       | Min | Typ | Max   | Unit |

|--------------------------|---------------------------------|--------------|-----|-----|-------|------|

| DAC INTERPOLATION FILTER |                                 |              |     |     |       |      |

| Pass Band                | 48 kHz mode, typical @ 48 kHz   | 0.4535 $f_s$ |     | 22  |       | kHz  |

|                          | 96 kHz mode, typical @ 96 kHz   | 0.3646 $f_s$ | 35  |     |       | kHz  |

|                          | 192 kHz mode, typical @ 192 kHz | 0.3646 $f_s$ |     | 70  |       | kHz  |

| Pass-Band Ripple         | 48 kHz mode, typical @ 48 kHz   |              |     |     | ±0.01 | dB   |

|                          | 96 kHz mode, typical @ 96 kHz   |              |     |     | ±0.05 | dB   |

|                          | 192 kHz mode, typical @ 192 kHz |              |     |     | ±0.1  | dB   |

| Transition Band          | 48 kHz mode, typical @ 48 kHz   | 0.5 $f_s$    |     | 24  |       | kHz  |

|                          | 96 kHz mode, typical @ 96 kHz   | 0.5 $f_s$    |     | 48  |       | kHz  |

|                          | 192 kHz mode, typical @ 192 kHz | 0.5 $f_s$    |     | 96  |       | kHz  |

| Stop Band                | 48 kHz mode, typical @ 48 kHz   | 0.5465 $f_s$ |     | 26  |       | kHz  |

|                          | 96 kHz mode, typical @ 96 kHz   | 0.6354 $f_s$ |     | 61  |       | kHz  |

|                          | 192 kHz mode, typical @ 192 kHz | 0.6354 $f_s$ |     | 122 |       | kHz  |

| Stop-Band Attenuation    | 48 kHz mode, typical @ 48 kHz   |              | 70  |     |       | dB   |

|                          | 96 kHz mode, typical @ 96 kHz   |              | 70  |     |       | dB   |

|                          | 192 kHz mode, typical @ 192 kHz |              | 70  |     |       | dB   |

| Group Delay              | 48 kHz mode, typical @ 48 kHz   | 25/ $f_s$    |     | 521 |       | μs   |

|                          | 96 kHz mode, typical @ 96 kHz   | 11/ $f_s$    |     | 115 |       | μs   |

|                          | 192 kHz mode, typical @ 192 kHz | 8/ $f_s$     |     | 42  |       | μs   |

## TIMING SPECIFICATIONS

-40°C < T<sub>C</sub> < +125°C, DVDD = 3.3 V ± 10%.

Table 7.

| Parameter                                                       | Condition               | Comments                                                                                                             | Min  | Max  | Unit              |

|-----------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------|------|------|-------------------|

| INPUT MASTER CLOCK (MCLK) AND RESET                             |                         |                                                                                                                      |      |      |                   |

| $t_{MH}$                                                        | MCLK duty cycle         | DAC clock source = PLL clock @ 256 f <sub>s</sub> , 384 f <sub>s</sub> , 512 f <sub>s</sub> , and 768 f <sub>s</sub> | 40   | 60   | %                 |

| $t_{MH}$                                                        |                         | DAC clock source = direct MCLK @ 512 f <sub>s</sub> (bypass on-chip PLL)                                             | 40   | 60   | %                 |

| $f_{MCLK}$                                                      | MCLK frequency          | PLL mode, 256 f <sub>s</sub> reference                                                                               | 6.9  | 13.8 | MHz               |

| $f_{MCLK}$                                                      |                         | Direct 512 f <sub>s</sub> mode                                                                                       |      | 27.6 | MHz               |

| $t_{PDR}$                                                       | <u>RST</u> low          |                                                                                                                      | 15   |      | ns                |

| $t_{PDRR}$                                                      | <u>RST</u> recovery     | Reset to active output                                                                                               | 4096 |      | t <sub>MCLK</sub> |

| PLL                                                             |                         |                                                                                                                      |      |      |                   |

| Lock Time                                                       | MCLK and LR clock input |                                                                                                                      |      | 10   | ms                |

| 256 f <sub>s</sub> VCO Clock, Output Duty Cycle<br>MCLKO/XO Pin |                         |                                                                                                                      | 40   | 60   | %                 |

| SPI PORT                                                        |                         |                                                                                                                      |      |      |                   |

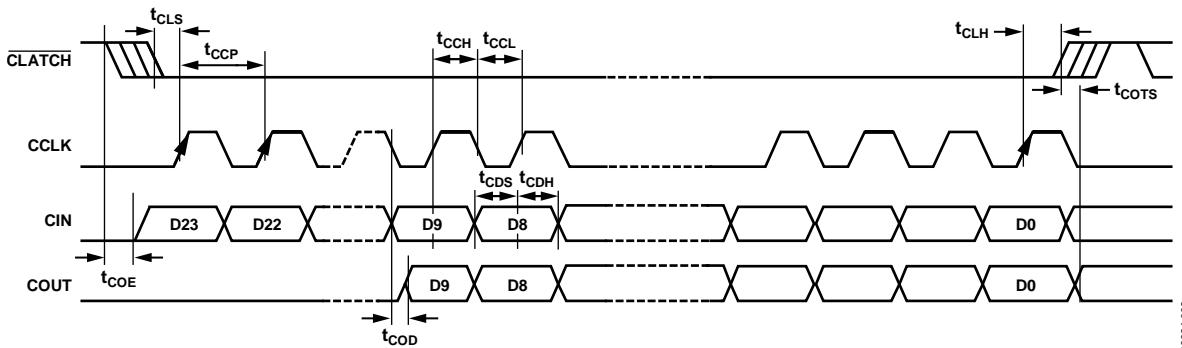

| $t_{CCH}$                                                       | CCLK high               | See Figure 9                                                                                                         | 35   |      | ns                |

| $t_{CCL}$                                                       | CCLK low                |                                                                                                                      | 35   |      | ns                |

| $f_{CCLK}$                                                      | CCLK frequency          | $f_{CCLK} = 1/t_{CCP}$ , only t <sub>CCP</sub> shown in Figure 9                                                     |      | 10   | MHz               |

| $t_{CD5}$                                                       | CIN setup               | To CCLK rising                                                                                                       | 10   |      | ns                |

| $t_{CDH}$                                                       | <u>CIN</u> hold         | From CCLK rising                                                                                                     | 10   |      | ns                |

| $t_{CLS}$                                                       | <u>CLATCH</u> setup     | To CCLK rising                                                                                                       | 10   |      | ns                |

| $t_{CLH}$                                                       | <u>CLATCH</u> hold      | From CCLK rising                                                                                                     | 10   |      | ns                |

| $t_{CLHIGH}$                                                    | <u>CLATCH</u> high      | Not shown in Figure 9                                                                                                | 10   |      | ns                |

| $t_{COE}$                                                       | COUT enable             | From CCLK falling                                                                                                    |      | 30   | ns                |

| $t_{COD}$                                                       | COUT delay              | From CCLK falling                                                                                                    |      | 30   | ns                |

| $t_{COH}$                                                       | COUT hold               | From CCLK falling, not shown in Figure 9                                                                             | 30   |      | ns                |

| $t_{COTS}$                                                      | COUT tristate           | From CCLK falling                                                                                                    | 30   |      | ns                |

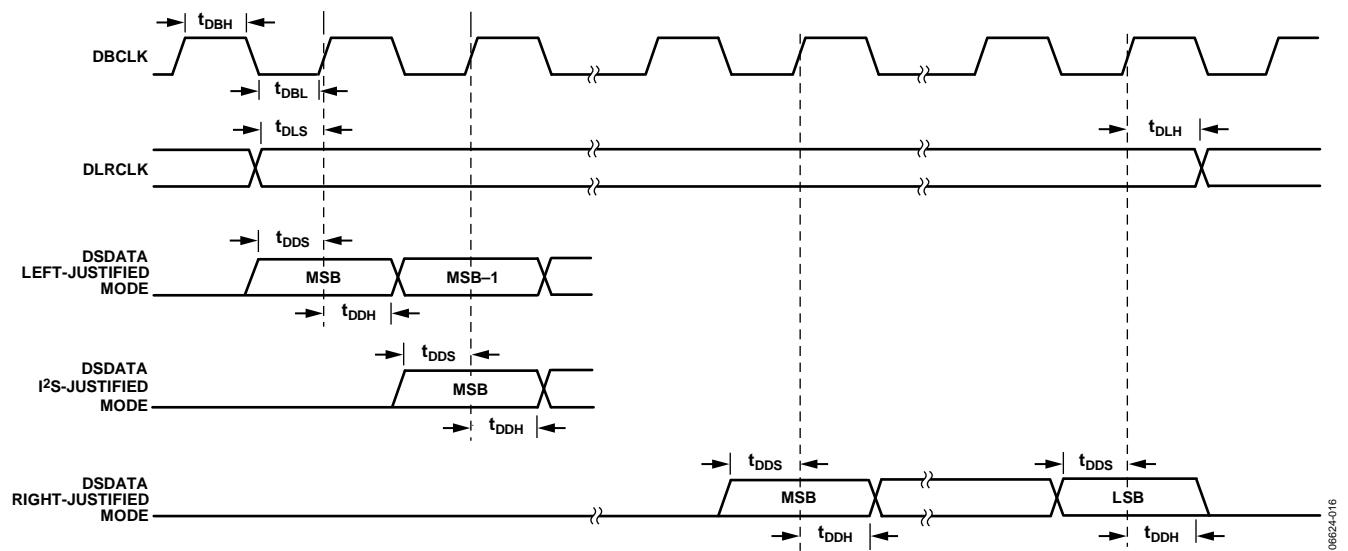

| DAC SERIAL PORT                                                 |                         |                                                                                                                      |      |      |                   |

| $t_{DBH}$                                                       | DBCLK high              | See Figure 16                                                                                                        | 10   |      | ns                |

| $t_{DBL}$                                                       | DBCLK low               | Slave mode                                                                                                           | 10   |      | ns                |

| $t_{DLS}$                                                       | DLRCLK setup            | Slave mode                                                                                                           | 10   |      | ns                |

| $t_{DLH}$                                                       | DLRCLK hold             | To DBCLK rising, slave mode                                                                                          | 10   |      | ns                |

| $t_{DLS}$                                                       | DLRCLK skew             | From DBCLK rising, slave mode                                                                                        | 5    |      | ns                |

| $t_{DDS}$                                                       | DSDATA setup            | From DBCLK falling, master mode                                                                                      | -8   | +8   | ns                |

| $t_{DDH}$                                                       | DSDATA hold             | To DBCLK rising                                                                                                      | 10   |      | ns                |

| From DBCLK rising                                               | 5                       | ns                                                                                                                   |      |      |                   |

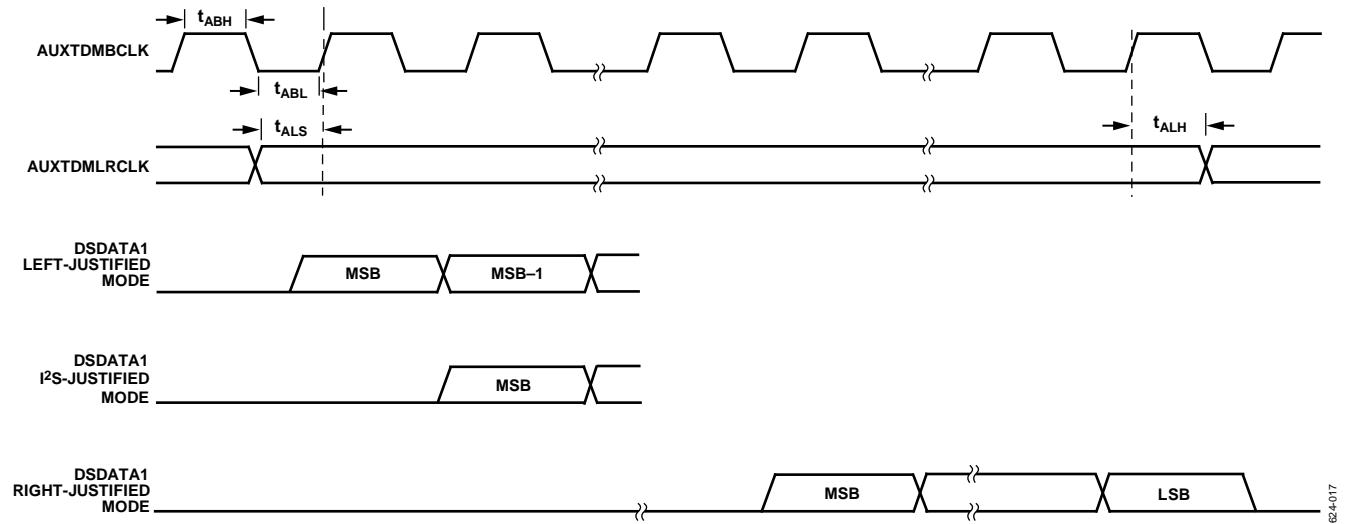

| AUXTDM SERIAL PORT                                              |                         |                                                                                                                      |      |      |                   |

| $t_{ABH}$                                                       | AUXTDMBCLK high         | See Figure 17                                                                                                        | 10   |      | ns                |

| $t_{ABL}$                                                       | AUXTDMBCLK low          | Slave mode                                                                                                           | 10   |      | ns                |

| $t_{ALS}$                                                       | AUXTDMRLCLK setup       | Slave mode                                                                                                           | 10   |      | ns                |

| $t_{ALH}$                                                       | AUXTDMRLCLK hold        | To AUXTDMBCLK rising, slave mode                                                                                     | 10   |      | ns                |

| $t_{ALS}$                                                       | AUXTDMRLCLK skew        | From AUXTDMBCLK rising, slave mode                                                                                   | 5    |      | ns                |

| $t_{DDS}$                                                       | DSDATA setup            | From AUXTDMBCLK falling, master mode                                                                                 | -8   | +8   | ns                |

| $t_{DDH}$                                                       | DSDATA hold             | To AUXTDMBCLK, not shown in Figure 17                                                                                | 10   |      | ns                |

| From AUXTDMBCLK rising, not shown in Figure 17                  | 5                       | ns                                                                                                                   |      |      |                   |

| AUXILIARY INTERFACE                                             |                         |                                                                                                                      |      |      |                   |

| $t_{DXDD}$                                                      | AUXDATA delay           | From AUXBCLK falling                                                                                                 |      | 18   | ns                |

| $t_{XBH}$                                                       | AUXBCLK high            |                                                                                                                      | 10   |      | ns                |

| $t_{XBL}$                                                       | AUXBCLK low             |                                                                                                                      | 10   |      | ns                |

| $t_{DLS}$                                                       | AUXLRCLK setup          | To AUXBCLK rising                                                                                                    | 10   |      | ns                |

| $t_{DLH}$                                                       | AUXLRCLK hold           | From AUXBCLK rising                                                                                                  | 5    |      | ns                |

## ABSOLUTE MAXIMUM RATINGS

**Table 8.**

| Parameter                           | Rating                 |

|-------------------------------------|------------------------|

| Analog (AVDD)                       | –0.3 V to +3.6 V       |

| Digital (DVDD)                      | –0.3 V to +3.6 V       |

| VSUPPLY                             | –0.3 V to +6.0 V       |

| Input Current (Except Supply Pins)  | ±20 mA                 |

| Analog Input Voltage (Signal Pins)  | –0.3 V to AVDD + 0.3 V |

| Digital Input Voltage (Signal Pins) | –0.3 V to DVDD + 0.3 V |

| Operating Temperature Range (Case)  | –40°C to +125°C        |

| Storage Temperature Range           | –65°C to +150°C        |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### THERMAL RESISTANCE

$\theta_{JA}$  represents thermal resistance, junction-to-ambient;  $\theta_{JC}$  represents thermal resistance, junction-to-case. All characteristics are for a 4-layer board.

**Table 9. Thermal Resistance**

| Package Type | $\theta_{JA}$ | $\theta_{JC}$ | Unit |

|--------------|---------------|---------------|------|

| 64-Lead LQFP | 47            | 11.1          | °C/W |

### ESD CAUTION

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

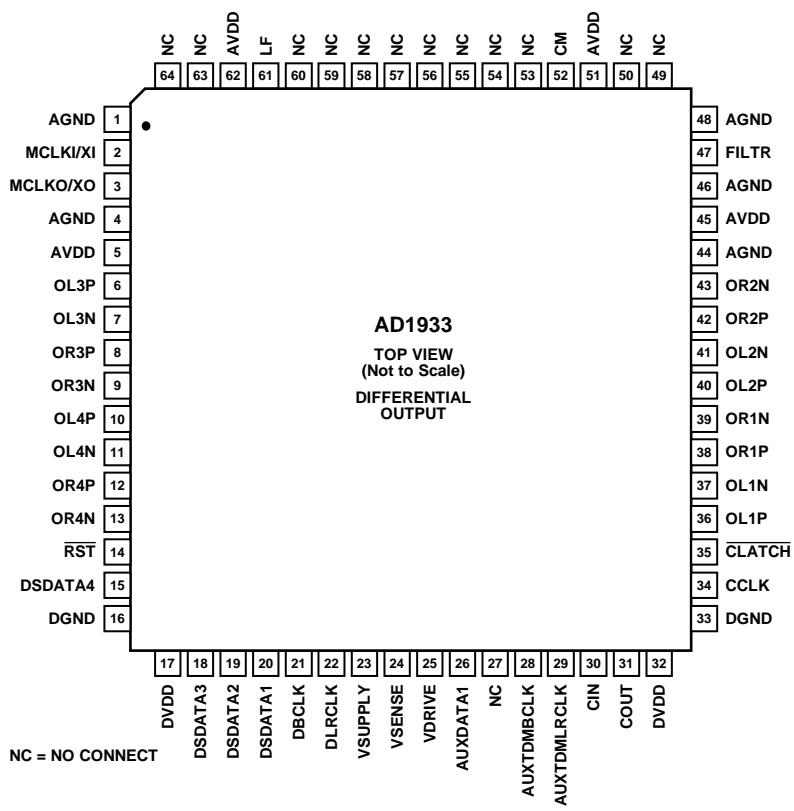

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

0624-402

Figure 2. Pin Configuration

Table 10. Pin Function Descriptions

| Pin No. | Input/Output | Mnemonic | Description                                                                                                            |

|---------|--------------|----------|------------------------------------------------------------------------------------------------------------------------|

| 1       | I            | AGND     | Analog Ground.                                                                                                         |

| 2       | I            | MCLKI/XI | Master Clock Input/Crystal Oscillator Input.                                                                           |

| 3       | O            | MCLKO/XO | Master Clock Output/Crystal Oscillator Output.                                                                         |

| 4       | I            | AGND     | Analog Ground.                                                                                                         |

| 5       | I            | AVDD     | Analog Power Supply. Connect to analog 3.3 V supply.                                                                   |

| 6       | O            | OL3P     | DAC 3 Left Positive Output.                                                                                            |

| 7       | O            | OL3N     | DAC 3 Left Negative Output.                                                                                            |

| 8       | O            | OR3P     | DAC 3 Right Positive Output.                                                                                           |

| 9       | O            | OR3N     | DAC 3 Right Negative Output.                                                                                           |

| 10      | O            | OL4P     | DAC 4 Left Positive Output.                                                                                            |

| 11      | O            | OL4N     | DAC 4 Left Negative Output.                                                                                            |

| 12      | O            | OR4P     | DAC 4 Right Positive Output.                                                                                           |

| 13      | O            | OR4N     | DAC 4 Right Negative Output.                                                                                           |

| 14      | I            | RST      | Reset (Active Low).                                                                                                    |

| 15      | I/O          | DSDATA4  | DACSerial Data Input 4. Input to DAC4 data in/TDM DAC2 data out (dual-line mode)/AUX DAC2 data out (to external DAC2). |

| 16      | I            | DGND     | Digital Ground.                                                                                                        |

| 17      | I            | DVDD     | Digital Power Supply. Connect to digital 3.3 V supply.                                                                 |

| 18      | I/O          | DSDATA3  | DAC Serial Data Input 3. Data input to DAC3 in/TDM DAC2 data in (dual-line mode)/AUX not used.                         |

| 19      | I/O          | DSDATA2  | DAC Serial Data Input 2. Data input to DAC2 data in/TDM DAC data out/AUX not used.                                     |

| 20      | I            | DSDATA1  | DAC Serial Data Input 1. Data input to DAC1 data in/TDM DAC data in/AUX TDM data in.                                   |

| 21      | I/O          | DBCLK    | Bit Clock for DACs. Regular stereo, TDM, or daisy-chain TDM mode.                                                      |

| 22      | I/O          | DLRCLK   | LR Clock for DACs. Regular stereo, TDM, or daisy-chain TDM mode.                                                       |

| Pin No.               | Input/Output | Mnemonic      | Description                                                                                             |

|-----------------------|--------------|---------------|---------------------------------------------------------------------------------------------------------|

| 23                    | I            | VSUPPLY       | 5 V Input to Regulator, Emitter of Pass Transistor.                                                     |

| 24                    | I            | VSENSE        | 3.3 V Output of Regulator, Collector of Pass Transistor.                                                |

| 25                    | O            | VDRIVE        | Drive for Base of Pass Transistor.                                                                      |

| 26                    | O            | AUXDATA1      | AUX DAC1 data out (to external DAC1).                                                                   |

| 27, 49, 50,<br>63, 64 |              | NC            | No Connect.                                                                                             |

| 28                    | I/O          | AUXTDMBCLK    | Auxiliary Mode Only DAC TDM Bit Clock.                                                                  |

| 29                    | I/O          | AUXTDMRLCLK   | Auxiliary Mode Only DAC LR TDM Clock.                                                                   |

| 30                    | I            | CIN           | Control Data Input (SPI).                                                                               |

| 31                    | I/O          | COUT          | Control Data Output (SPI).                                                                              |

| 32                    | I            | DVDD          | Digital Power Supply. Connect to digital 3.3 V supply.                                                  |

| 33                    | I            | DGND          | Digital Ground.                                                                                         |

| 34                    | I            | CCLK          | Control Clock Input (SPI).                                                                              |

| 35                    | I            | <u>CLATCH</u> | Latch Input for Control Data (SPI).                                                                     |

| 36                    | O            | OL1P          | DAC 1 Left Positive Output.                                                                             |

| 37                    | O            | OL1N          | DAC 1 Left Negative Output.                                                                             |

| 38                    | O            | OR1P          | DAC 1 Right Positive Output.                                                                            |

| 39                    | O            | OR1N          | DAC 1 Right Negative Output.                                                                            |

| 40                    | O            | OL2P          | DAC 2 Left Positive Output.                                                                             |

| 41                    | O            | OL2N          | DAC 2 Left Negative Output.                                                                             |

| 42                    | O            | OR2P          | DAC 2 Right Positive Output.                                                                            |

| 43                    | O            | OR2N          | DAC 2 Right Negative Output.                                                                            |

| 44                    | I            | AGND          | Analog Ground.                                                                                          |

| 45                    | I            | AVDD          | Analog Power Supply. Connect to analog 3.3 V supply.                                                    |

| 46                    | I            | AGND          | Analog Ground.                                                                                          |

| 47                    | O            | FILTR         | Voltage Reference Filter Capacitor Connection. Bypass with $10 \mu\text{F}  100 \text{nF}$ to AGND.     |

| 48                    | I            | AGND          | Analog Ground.                                                                                          |

| 51                    | I            | AVDD          | Analog Power Supply. Connect to analog 3.3 V supply.                                                    |

| 52                    | O            | CM            | Common-Mode Reference Filter Capacitor Connection. Bypass with $47 \mu\text{F}  100 \text{nF}$ to AGND. |

| 53 to 60              | I            | NC            | Must Be Tied to Common Mode, Pin 52. Alternately, ac-couple these pins to ground.                       |

| 61                    | O            | LF            | PLL Loop Filter, Return to AVDD.                                                                        |

| 62                    | I            | AVDD          | Analog Power Supply. Connect to analog 3.3 V supply.                                                    |

## TYPICAL PERFORMANCE CHARACTERISTICS

## THEORY OF OPERATION

### DIGITAL-TO-ANALOG CONVERTERS (DACs)

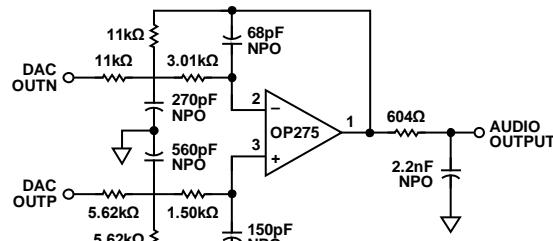

The AD1933 DAC channels are arranged as differential, four stereo pairs giving eight analog outputs for minimum external components. The DACs include on-board digital reconstruction filters with 70 dB stop-band attenuation and linear phase response, operating at an oversampling ratio of 4 (48 kHz or 96 kHz modes) or 2 (192 kHz mode). Each channel has its own independently programmable attenuator, adjustable in 255 steps in increments of 0.375 dB. Digital inputs are supplied through four serial data input pins (one for each stereo pair) and a common frame clock (DLRCLK) and bit clock (DBCLK). Alternatively, one of the TDM modes can be used to access up to 16 channels on a single TDM data line.

Each output pin has a nominal common-mode dc level of 1.5 V and swings  $\pm 1.27$  V for a 0 dBFS digital input signal. A third-order, external, low-pass filter is recommended to remove high frequency noise present on the output pins. The use of op amps with low slew rates or low bandwidths can cause high frequency noise and tones to fold down into the audio band; therefore, exercise care in selecting these components.

The voltage at CM, the common-mode reference pin, can be used to bias the external op amps that buffer the output signals (see the Power Supply and Voltage Reference section).

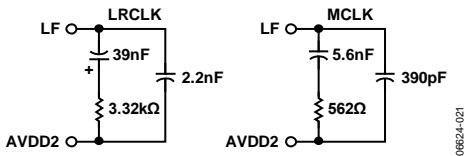

### CLOCK SIGNALS

The on-chip, phase-locked loop (PLL) can be selected to reference the input sample rate from either of the LRCLK pins or 256, 384, 512, or 768 times the sample rate, referenced to the 48 kHz mode from the MCLKI/XI pin. The default at power-up is  $256 \times f_s$  from MCLKI/XI pin. In 96 kHz mode, the master clock frequency stays at the same absolute frequency; therefore, the actual multiplication rate is divided by 2. In 192 kHz mode, the actual multiplication rate is divided by 4. For example, if a device in the AD1933 family is programmed in  $256 \times f_s$  mode, the frequency of the master clock input is  $256 \times 48$  kHz = 12.288 MHz. If the AD1933 is then switched to 96 kHz operation (by writing to the SPI port), the frequency of the master clock should remain at 12.288 MHz, which becomes  $128 \times f_s$ . In 192 kHz mode, this becomes  $64 \times f_s$ .

The internal clock for the DACs varies by mode:  $512 \times f_s$  (48 kHz mode),  $256 \times f_s$  (96 kHz mode), or  $128 \times f_s$  (192 kHz mode). By default, the on-board PLL generates this internal master clock from an external clock. A direct  $512 \times f_s$  (referenced to 48 kHz mode) master clock can be used for DACs if selected in the PLL and Clock Control 1 register.

The PLL can be powered down in the PLL and Clock Control 0 register. To ensure reliable locking when changing PLL modes, or if the reference clock is unstable at power-on, power down the PLL and power it back up when the reference clock has stabilized.

The internal master clock can be disabled in the PLL and Clock Control 0 register to reduce power dissipation when the AD1933 is idle. The clock should be stable before it is enabled. Unless a standalone mode is selected (see the Serial Control Port section), the clock is disabled by reset and must be enabled by writing to the SPI port for normal operation.

To maintain the highest performance possible, limit the clock jitter of the internal master clock signal to less than a 300 ps rms time interval error (TIE). Even at these levels, extra noise or tones can appear in the DAC outputs if the jitter spectrum contains large spectral peaks. If the internal PLL is not used, it is highly recommended that an independent crystal oscillator generate the master clock. In addition, it is especially important that the clock signal not be passed through an FPGA, CPLD, or other large digital chip (such as a DSP) before being applied to the AD1933. In most cases, this induces clock jitter due to the sharing of common power and ground connections with other unrelated digital output signals. When the PLL is used, jitter in the reference clock is attenuated above a certain frequency depending on the loop filter.

### RESET AND POWER-DOWN

The function of the RST pin sets all the control registers to their default settings. To avoid pops, reset does not power down the analog outputs. After RST is deasserted, and the PLL acquires lock condition, an initialization routine runs inside the AD1933. This initialization lasts for approximately 256 master clock cycles.

The power-down bits in the PLL and Clock Control 0 and DAC Control 1 registers power down the respective sections. All other register settings are retained. To guarantee proper startup, the RST pin should be pulled low by an external resistor.

## SERIAL CONTROL PORT

The AD1933 has an SPI control port that permits programming and reading back of the internal control registers for the ADCs, DACs, and clock system. A standalone mode is also available for operation without serial control; standalone is configured at reset by connecting CIN, CCLK, and CLATCH to ground. In standalone mode, all registers are set to default, except the internal MCLK enable, which is set to 1. The ADC ABCLK and ALRCLK clock ports are set to master/slave by the connecting the COUT pin to either DVDD or ground. Standalone mode only supports stereo mode with an I<sup>S</sup>S data format and 256 fs MCLK rate. Refer to Table 11 for details. If CIN, CCLK, and CLATCH are not grounded, the AD1933 SPI port is active. It is recommended to use a weak pull-up resistor on CLATCH in applications that have a microcontroller. This pull-up resistor ensures that the AD1933 recognizes the presence of a microcontroller.

The SPI control port of the AD1933 is a 4-wire serial control port. The format is similar to the Motorola SPI format except the input data-word is 24 bits wide. The serial bit clock and latch can be completely asynchronous to the sample rate of the DACs. Figure 9 shows the format of the SPI signal. The first byte is a global address with a read/write bit. For the AD1933, the address is 0x04, shifted left 1 bit due to the R/W bit. The second byte is the AD1933 register address and the third byte is the data.

Figure 9. Format of SPI Signal

## POWER SUPPLY AND VOLTAGE REFERENCE

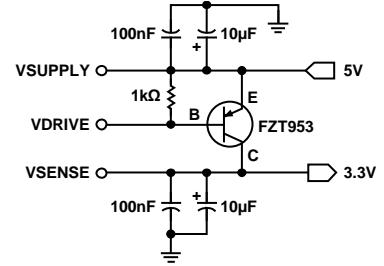

The AD1933 is designed for 3.3 V supplies. Separate power supply pins are provided for the analog and digital sections. These pins should be bypassed with 100 nF ceramic chip capacitors, as close to the pins as possible, to minimize noise pickup. A bulk aluminum electrolytic capacitor of at least 22  $\mu$ F should also be provided on the same PCB as the DAC. For critical applications, improved performance is obtained with separate supplies for the analog and digital sections. If this is not possible, it is recommended that the analog and digital supplies be isolated by means of a ferrite bead in series with each supply. It is important that the analog supply be as clean as possible.

The AD1933 includes a 3.3 V regulator driver that only requires an external pass transistor and bypass capacitors to make a 5 V to 3.3 V regulator. If the regulator driver is not used, connect VSUPPLY, VDRIVE, and VSENSE to DGND.

All digital inputs are compatible with TTL and CMOS levels. All outputs are driven from the 3.3 V DVDD supply and are compatible with TTL and 3.3 V CMOS levels.

The DAC internal voltage reference (VREF) is brought out on FILTR and should be bypassed as close as possible to the chip, with a parallel combination of 10  $\mu$ F and 100 nF. Any external current drawn should be limited to less than 50  $\mu$ A.

The internal reference can be disabled in the PLL and Clock Control 1 register and FILTR can be driven from an external source. This can be used to scale the DAC output to the clipping level of a power amplifier based on its power supply voltage, DAC output gain is proportional to the FILTR voltage.

The CM pin is the internal common-mode reference. It should be bypassed as close as possible to the chip, with a parallel combination of 47  $\mu$ F and 100 nF. This voltage can be used to bias external op amps to the common-mode voltage of the input and output signal pins. The output current should be limited to less than 0.5 mA source and 2 mA sink.

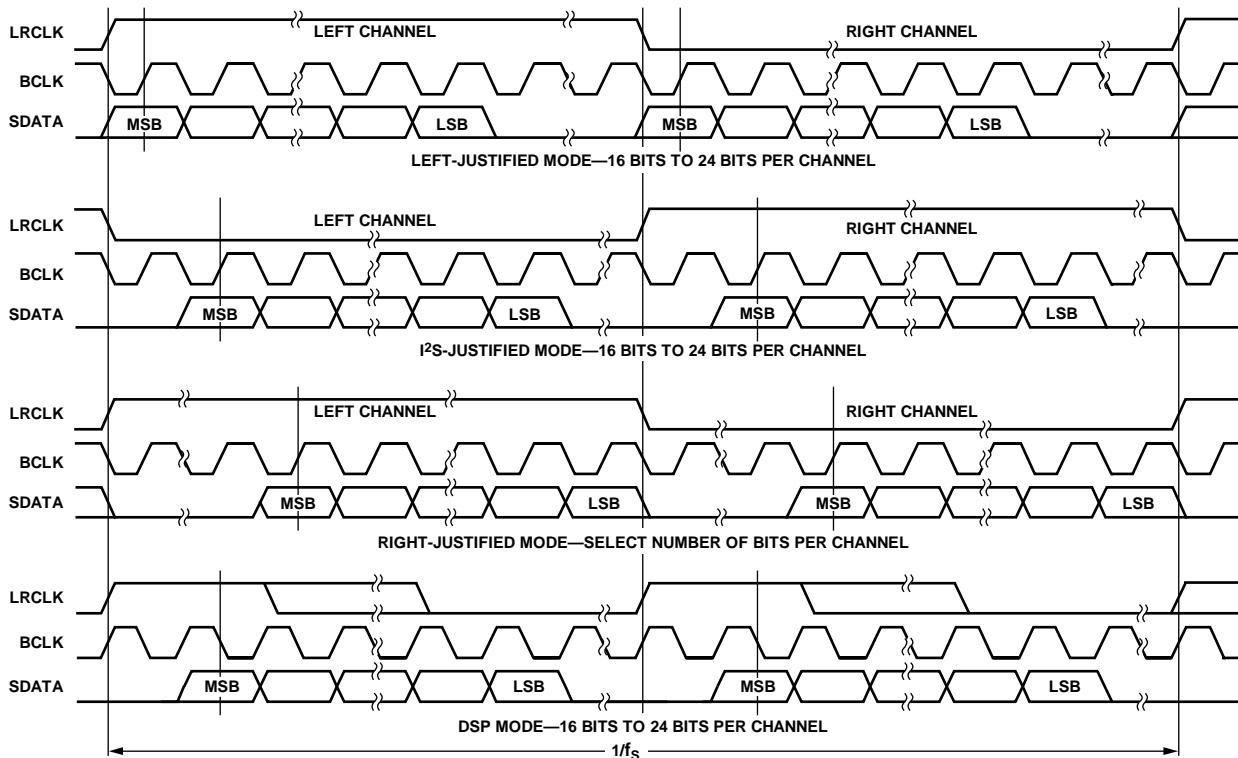

## SERIAL DATA PORTS—DATA FORMAT

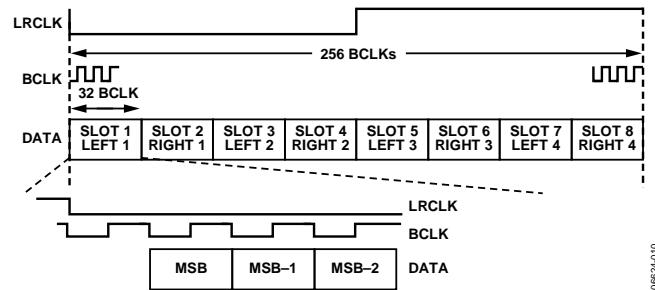

The eight DAC channels use a common serial bit clock (DBCLK) and a common left-right framing clock (DLRCLK) in the serial data port. The clock signals are all synchronous with the sample rate. The normal stereo serial modes are shown in Figure 15.

The DAC serial data modes default to I<sup>2</sup>S. The ports can also be programmed for left-justified, right-justified, and TDM modes. The word width is 24 bits by default and can be programmed for 16 or 20 bits. The DAC serial formats are programmable according to the DAC Control 0 register. The polarity of the DBCLK and DLRCLK is programmable according to the DAC Control 1 register. The auxiliary TDM port is also provided for

applications requiring more than eight DAC channels. In this mode, the AUXTDMRLCLK and AUXTDMBCLK pins are configured as TDM port clocks. In regular TDM mode, the DLRCLK and DBCLK pins are used as the TDM port clocks. The auxiliary TDM serial port format and its serial clock polarity are programmable according to the Auxiliary TDM Port Control 0 register and the Auxiliary TDM Port Control 1 register. Both DAC and auxiliary TDM serial ports are programmable to become the bus masters according to the DAC Control 1 register and auxiliary TDM Control 1 register. By default, both auxiliary TDM and DAC serial ports are in slave mode.

## TIME-DIVISION MULTIPLEXED (TDM) MODES

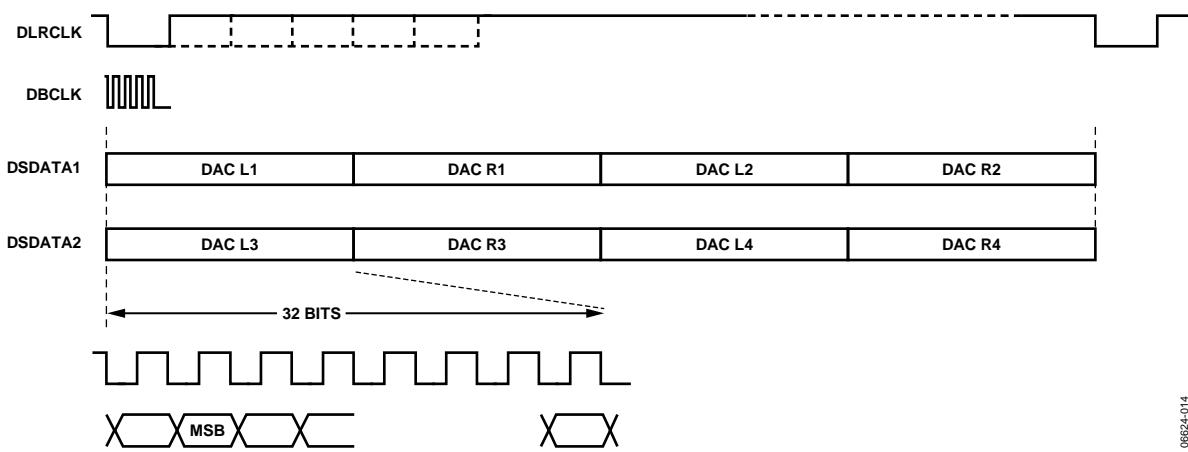

The AD1933 serial ports have several different TDM serial data modes. The most commonly used configuration is shown in Figure 10. In Figure 10, the eight on-chip DAC data slots are packed into one TDM stream. In this mode, DBCLK is 256 fs.

The I/O pins of the serial ports are defined according to the serial mode selected. For a detailed description of the function of each pin in TDM and auxiliary modes, see Table 11.

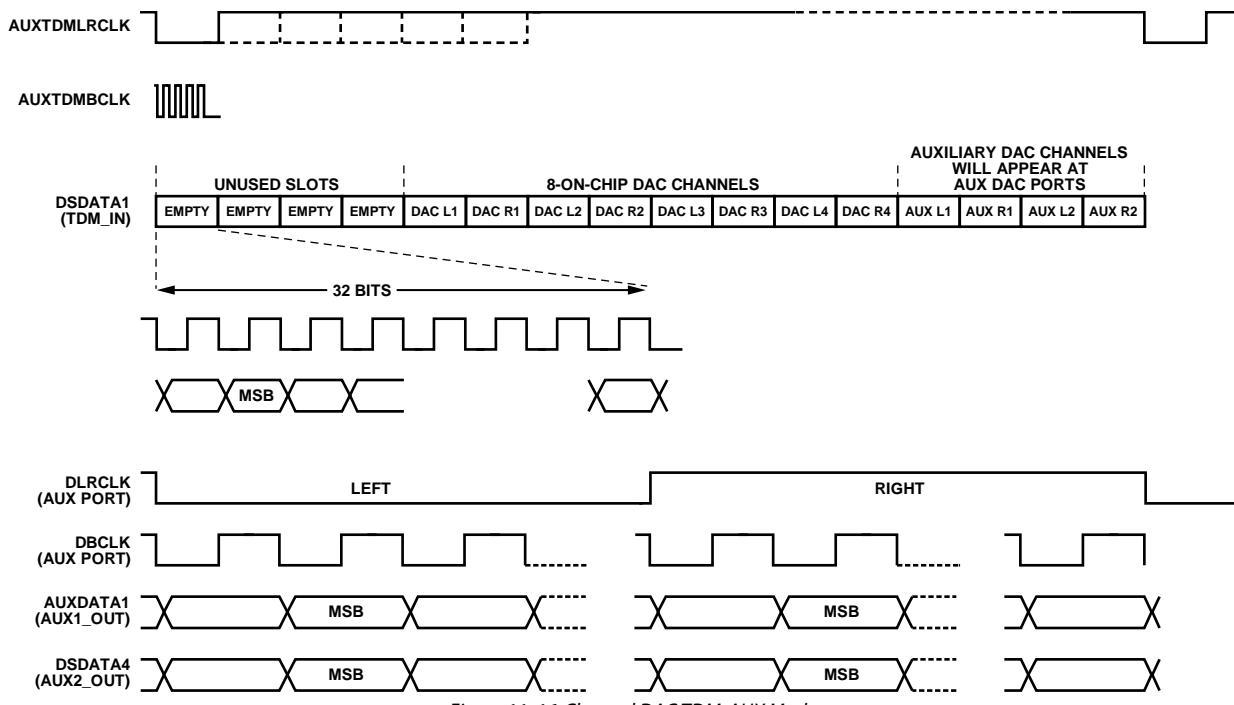

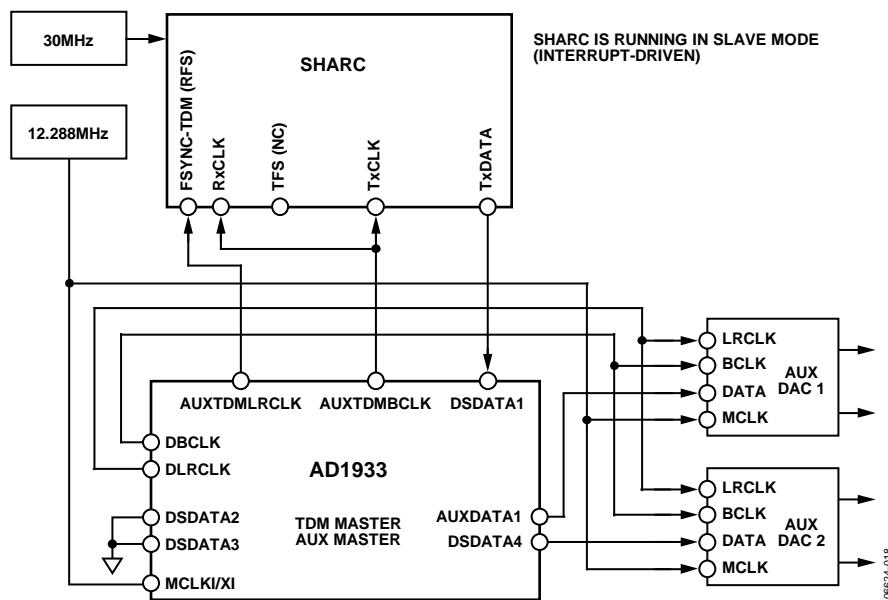

The AD1933 allows systems with more than eight DAC channels to be easily configured by the use of an auxiliary serial data port. The DAC TDM-AUX mode is shown in Figure 11. In this mode, the AUX channels are the last four slots of the 16-channel TDM data stream. These slots are extracted and output to the AUX serial port. One major difference between the TDM mode and an auxiliary TDM mode is the assignment of the TDM port pins, as shown in Table 11. In auxiliary TDM mode, DBCLK and DLRCLK are assigned as the auxiliary port clocks, and AUXTDMBCLK and AUXTDMRLCLK are assigned as the TDM port clocks. In regular TDM or 16-channel, daisy-chain TDM mode, the DLRCLK and DBCLK pins are set as the TDM port clocks.

It should be noted that due to the high AUXTDMBCLK frequency, 16-channel auxiliary TDM mode is available only in the 48 kHz/44.1 kHz/32 kHz sample rate.

Figure 10. DAC TDM (8-Channel I<sup>2</sup>S Mode)

08624-010

**Table 11. Pin Function Changes in TDM-AUX Mode**

| Pin Name    | Stereo Modes               | TDM Modes                                   | AUX Modes                            |

|-------------|----------------------------|---------------------------------------------|--------------------------------------|

| AUXDATA1    | Not Used (Float)           | Not Used (Float)                            | AUX Data Out 1 (to External DAC 1)   |

| DSDATA1     | DAC 1 Data In              | DAC TDM Data In                             | TDM Data In                          |

| DSDATA2     | DAC 2 Data In              | DAC TDM Data Out                            | Not Used (Ground)                    |

| DSDATA3     | DAC 3 Data In              | DAC TDM Data In 2 (Dual-Line Mode)          | Not Used (Ground)                    |

| DSDATA4     | DAC 4 Data In              | DAC TDM Data Out 2 (Dual-Line Mode)         | AUX Data Out 2 (to External DAC 2)   |

| AUXTDMRLCLK | Not Used (Ground)          | Not Used (Ground)                           | TDM Frame Sync In/TDM Frame Sync Out |

| AUXTDMBCLK  | Not Used (Ground)          | Not Used (Ground)                           | TDM BCLK In/TDM BCLK Out             |

| DLRCLK      | DAC LRCLK In/DAC LRCLK Out | DACTDM Frame Sync In/DAC TDM Frame Sync Out | AUX LRCLK In/AUX LRCLK Out           |

| DBCLK       | DAC BCLK In/DAC BCLK Out   | DAC TDM BCLK In/DAC TDM BCLK Out            | AUX BCLK In/AUX BCLK Out             |

Figure 11. 16-Channel DAC TDM-AUX Mode

## DAISY-CHAIN MODE

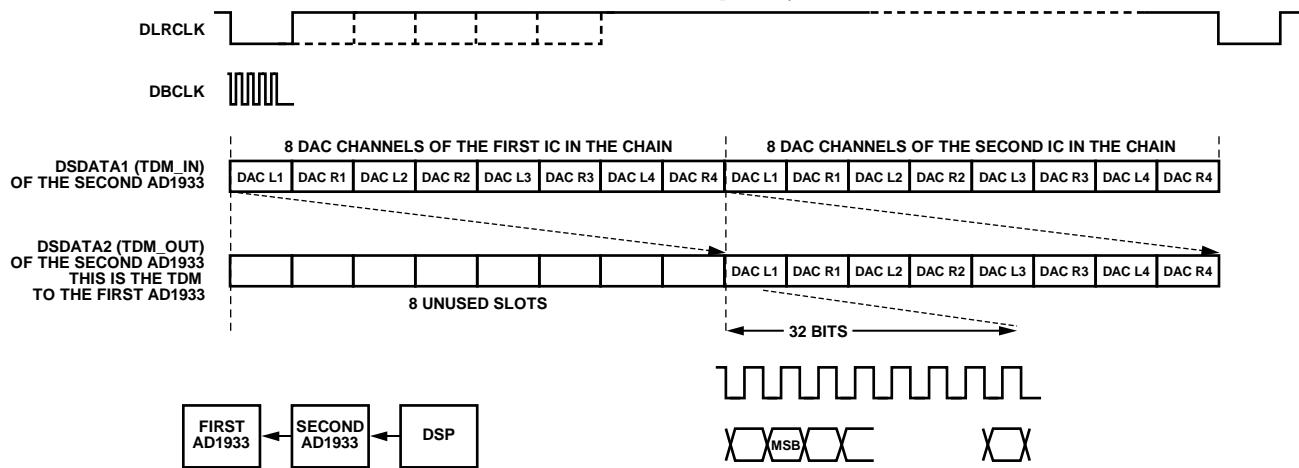

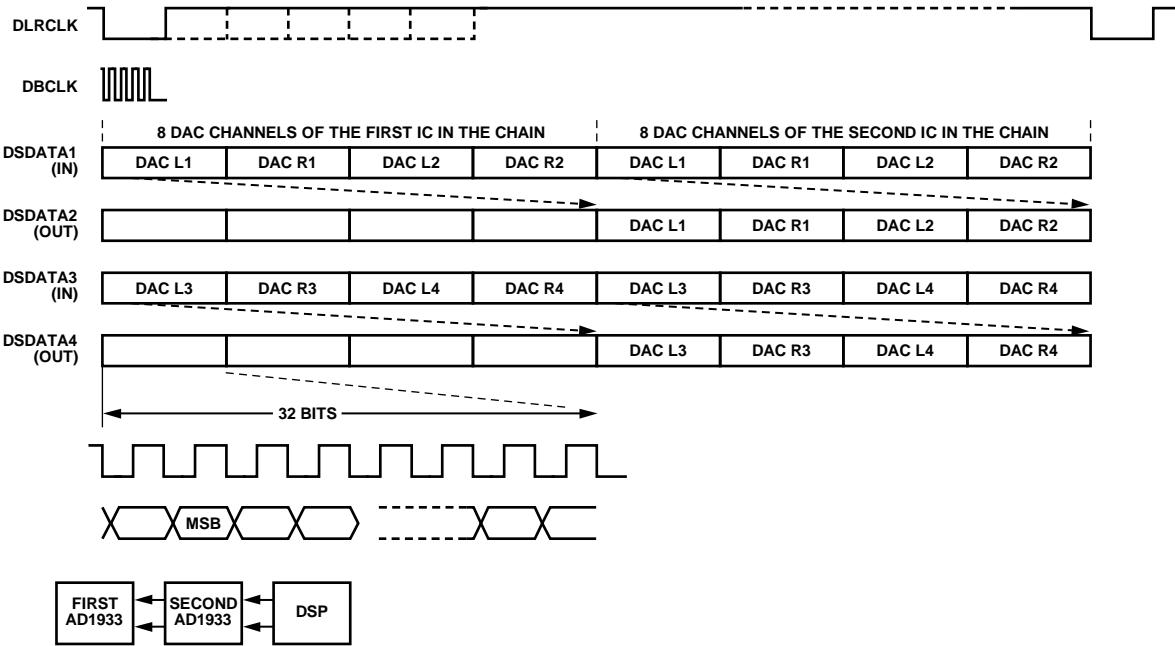

The AD1933 also allows a daisy-chain configuration to expand the system 16 DACs (see Figure 12). In this mode, the DBCLK frequency is 512 fs. The first eight slots of the DAC TDM data stream belong to the first AD1933 in the chain and the last eight slots belong to the second AD1933. The second AD1933 is the device attached to the DSP TDM port.

To accommodate 16 channels at a 96 kHz sample rate, the AD1933 can be configured into a dual-line, DAC TDM mode, as shown in Figure 13. This mode allows a slower DBCLK than normally required by the one-line TDM mode.

Again, the first four channels of each TDM input belong to the first AD1933 in the chain and the last four channels belong to the second AD1933.

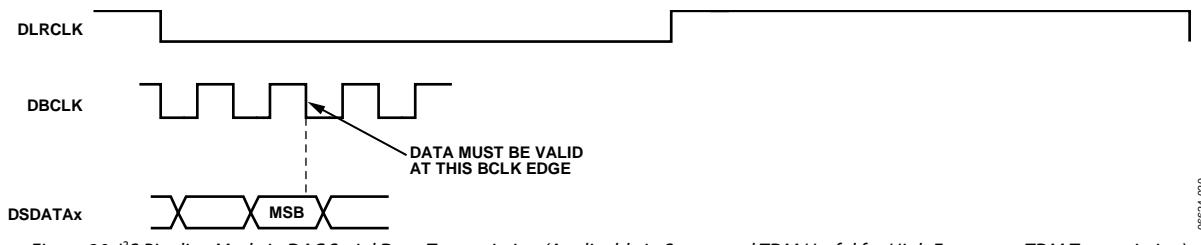

The dual-line, DAC TDM mode can also be used to send data at a 192 kHz sample rate into the AD1933, as shown in Figure 14. The I/O pins of the serial ports are defined according to the serial mode selected. See Table 12 for a detailed description of the function of each pin. See Figure 18 for a typical AD1933 configuration with two external stereo DACs. Figure 15 and Figure 16 show the serial mode formats. For maximum flexibility, the polarity of LRCLK and BCLK are programmable. In these figures, all of the clocks are shown with their normal polarity. The default mode is I<sup>2</sup>S.

Figure 12. Single-Line DAC TDM Daisy-Chain Mode (Applicable to 48 kHz Sample Rate, 16-Channel, Two AD1933 Daisy Chain)

Figure 13. Dual-Line, DAC TDM Mode (Applicable to 96 kHz Sample Rate, 16-Channel, Two AD1933 Daisy Chain; DSDATA3 and DSDATA4 Are the Daisy Chain)

Figure 14. Dual-Line, DAC TDM Mode (Applicable to 192 kHz Sample Rate, 8-Channel Mode)

06824-014

06824-015

## NOTES

1. DSP MODE DOES NOT IDENTIFY CHANNEL.

2. LRCLK NORMALLY OPERATES AT  $f_s$  EXCEPT FOR DSP MODE, WHICH IS  $2 \times f_s$ .

3. BCLK FREQUENCY IS NORMALLY  $64 \times$  LRCLK BUT MAY BE OPERATED IN BURST MODE.

Figure 15. Stereo Serial Modes

Figure 16. DAC Serial Timing

Figure 17. AUXTDM Serial Timing

Table 12. Pin Function Changes in TDM-AUX Mode (Replication of Table 11)

| Pin Name    | Stereo Modes               | TDM Modes                                   | AUX Modes                            |

|-------------|----------------------------|---------------------------------------------|--------------------------------------|

| AUXDATA1    | Not Used (Float)           | Not Used (Float)                            | AUX Data Out 1 (to External DAC 1)   |

| DSDATA1     | DAC 1 Data In              | DAC TDM Data In                             | TDM Data In                          |

| DSDATA2     | DAC 2 Data In              | DAC TDM Data Out                            | Not Used (Ground)                    |

| DSDATA3     | DAC 3 Data In              | DAC TDM Data In 2 (Dual-Line Mode)          | Not Used (Ground)                    |

| DSDATA4     | DAC 4 Data In              | DAC TDM Data Out 2 (Dual-Line Mode)         | AUX Data Out 2 (to External DAC 2)   |

| AUXTDMRLCLK | Not Used (Ground)          | Not Used (Ground)                           | TDM Frame Sync In/TDM Frame Sync Out |

| AUXTDMBCLK  | Not Used (Ground)          | Not Used (Ground)                           | TDM BCLK In/TDM BCLK Out             |

| DLRCLK      | DAC LRCLK In/DAC LRCLK Out | DAC TDM Frame Sync In/DACTDM Frame Sync Out | AUX LRCLK In/AUX LRCLK Out           |

| DBCLK       | DAC BCLK In/DAC BCLK Out   | DAC TDM BCLK In/DAC TDM BCLK Out            | AUX BCLK In/AUX BCLK Out             |

Figure 18. Example of AUX Mode Connection to SHARC® (AD1933 as TDM Master/AUX Master Shown)

## CONTROL REGISTERS

### DEFINITIONS

The global address for the AD1933 is 0x04, shifted left 1 bit due to the R/W bit. All registers are reset to 0, except for the DAC volume registers that are set to full volume.

Note that the first setting in each control register parameter is the default setting.

**Table 13. Register Format**

|     | Global Address | R/W | Register Address | Data |

|-----|----------------|-----|------------------|------|

| Bit | 23:17          | 16  | 15:8             | 7:0  |

**Table 14. Register Addresses and Functions**

| Address | Function                     |

|---------|------------------------------|

| 0       | PLL and Clock Control 0      |

| 1       | PLL and Clock Control 1      |

| 2       | DAC Control 0                |

| 3       | DAC Control 1                |

| 4       | DAC Control 2                |

| 5       | DAC individual channel mutes |

| 6       | DAC L1 volume control        |

| 7       | DAC R1 volume control        |

| 8       | DAC L2 volume control        |

| 9       | DAC R2 volume control        |

| 10      | DAC L3 volume control        |

| 11      | DAC R3 volume control        |

| 12      | DAC L4 volume control        |

| 13      | DAC R4 volume control        |

| 14      | Reserved                     |

| 15      | Auxiliary TDM Port Control 0 |

| 16      | Auxiliary TDM Port Control 1 |

## PLL AND CLOCK CONTROL REGISTERS

**Table 15. PLL and Clock Control 0**

| Bit | Value | Function                                 | Description                                                        |

|-----|-------|------------------------------------------|--------------------------------------------------------------------|

| 0   | 0     | Normal operation                         | PLL power-down                                                     |

|     | 1     | Power-down                               |                                                                    |

| 2:1 | 00    | Input 256 ( $\times 44.1$ kHz or 48 kHz) | MCLKI/XI pin functionality (PLL active), master clock rate setting |

|     | 01    | Input 384 ( $\times 44.1$ kHz or 48 kHz) |                                                                    |

|     | 10    | Input 512 ( $\times 44.1$ kHz or 48 kHz) |                                                                    |

|     | 11    | Input 768 ( $\times 44.1$ kHz or 48 kHz) |                                                                    |

| 4:3 | 00    | XTAL oscillator enabled                  | MCLKO/XO pin, master clock rate setting                            |

|     | 01    | $256 \times f_s$ VCO output              |                                                                    |

|     | 10    | $512 \times f_s$ VCO output              |                                                                    |

|     | 11    | Off                                      |                                                                    |

| 6:5 | 00    | MCLKI/XI                                 | PLL input                                                          |

|     | 01    | DLRCLK                                   |                                                                    |

|     | 10    | AUXTDMRLRCLK                             |                                                                    |

|     | 11    | Reserved                                 |                                                                    |

| 7   | 0     | Disable: DAC idle                        | Internal master clock enable                                       |

|     | 1     | Enable: DAC active                       |                                                                    |

Table 16. PLL and Clock Control 1

| Bit | Value | Function   | Description                    |

|-----|-------|------------|--------------------------------|

| 0   | 0     | PLL clock  | DAC clock source select        |

|     | 1     | MCLK       |                                |

| 1   | 0     | PLL clock  | Clock source select            |

|     | 1     | MCLK       |                                |

| 2   | 0     | Enabled    | On-chip voltage reference      |

|     | 1     | Disabled   |                                |

| 3   | 0     | Not locked | PLL lock indicator (read-only) |

|     | 1     | Locked     |                                |

| 7:4 | 0000  | Reserved   |                                |

## DAC CONTROL REGISTERS

Table 17. DAC Control 0

| Bit | Value | Function                         | Description                |

|-----|-------|----------------------------------|----------------------------|

| 0   | 0     | Normal                           |                            |

|     | 1     | Power-down                       |                            |

| 2:1 | 00    | 32 kHz/44.1 kHz/48 kHz           | Sample rate                |

|     | 01    | 64 kHz/88.2 kHz/96 kHz           |                            |

|     | 10    | 128 kHz/176.4 kHz/192 kHz        |                            |

|     | 11    | Reserved                         |                            |

|     | 000   | 1                                | SDATA delay (BCLK periods) |

| 5:3 | 001   | 0                                |                            |

|     | 010   | 8                                |                            |

|     | 011   | 12                               |                            |

|     | 100   | 16                               |                            |

|     | 101   | Reserved                         |                            |

|     | 110   | Reserved                         |                            |

|     | 111   | Reserved                         |                            |

|     | 00    | Stereo (normal)                  | Serial format              |

| 7:6 | 01    | TDM (daisy chain)                |                            |

|     | 10    | DAC aux mode (DAC-, TDM-coupled) |                            |

|     | 11    | Dual-line TDM                    |                            |

Table 18. DAC Control 1

| Bit | Value | Function                            | Description               |

|-----|-------|-------------------------------------|---------------------------|

| 0   | 0     | Latch in midcycle (normal)          | BCLK active edge (TDM in) |

|     | 1     | Latch in at end of cycle (pipeline) |                           |

| 2:1 | 00    | 64 (2 channels)                     | BCLKs per frame           |

|     | 01    | 128 (4 channels)                    |                           |

|     | 10    | 256 (8 channels)                    |                           |

|     | 11    | 512 (16 channels)                   |                           |

|     | 0     | Left low                            | LRCLK polarity            |

| 3   | 1     | Left high                           |                           |

|     | 0     | Slave                               | LRCLK master/slave        |

| 4   | 1     | Master                              |                           |

|     | 0     | Slave                               | BCLK master/slave         |

| 5   | 1     | Master                              |                           |

|     | 0     | DBCLK pin                           | BCLK source               |

| 6   | 1     | Internally generated                |                           |

|     | 0     | Normal                              | BCLK polarity             |

| 7   | 1     | Inverted                            |                           |

Table 19. DAC Control 2

| Bit | Value | Function       | Description                                    |

|-----|-------|----------------|------------------------------------------------|

| 0   | 0     | Unmute         | Master mute                                    |

|     | 1     | Mute           |                                                |

| 2:1 | 00    | Flat           | De-emphasis (32 kHz/44.1 kHz/48 kHz mode only) |

|     | 01    | 48 kHz curve   |                                                |

|     | 10    | 44.1 kHz curve |                                                |

|     | 11    | 32 kHz curve   |                                                |

| 4:3 | 00    | 24             | Word width                                     |

|     | 01    | 20             |                                                |

|     | 10    | Reserved       |                                                |

|     | 11    | 16             |                                                |

| 5   | 0     | Noninverted    | DAC output polarity                            |

|     | 1     | Inverted       |                                                |

| 7:6 | 00    | Reserved       |                                                |

Table 20. DAC Individual Channel Mutes

| Bit | Value | Function | Description      |

|-----|-------|----------|------------------|

| 0   | 0     | Unmute   | DAC 1 left mute  |

|     | 1     | Mute     |                  |

| 1   | 0     | Unmute   | DAC 1 right mute |

|     | 1     | Mute     |                  |

| 2   | 0     | Unmute   | DAC 2 left mute  |

|     | 1     | Mute     |                  |

| 3   | 0     | Unmute   | DAC 2 right mute |

|     | 1     | Mute     |                  |

| 4   | 0     | Unmute   | DAC 3 left mute  |

|     | 1     | Mute     |                  |

| 5   | 0     | Unmute   | DAC 3 right mute |

|     | 1     | Mute     |                  |

| 6   | 0     | Unmute   | DAC 4 left mute  |

|     | 1     | Mute     |                  |

| 7   | 0     | Unmute   | DAC 4 right mute |

|     | 1     | Mute     |                  |

Table 21. DAC Volume Controls

| Bit | Value    | Function         | Description        |

|-----|----------|------------------|--------------------|

| 7:0 | 0        | No attenuation   | DAC volume control |

|     | 1 to 254 | -3/8 dB per step |                    |

|     | 255      | Full attenuation |                    |

**AUXILIARY TDM PORT CONTROL REGISTERS****Table 22. Auxiliary TDM Control 0**

| Bit | Value | Function                            | Description                |

|-----|-------|-------------------------------------|----------------------------|

| 1:0 | 00    | 24                                  |                            |

|     | 01    | 20                                  |                            |

|     | 10    | Reserved                            |                            |

|     | 11    | 16                                  |                            |

| 4:2 | 000   | 1                                   | SDATA delay (BCLK periods) |

|     | 001   | 0                                   |                            |

|     | 010   | 8                                   |                            |

|     | 011   | 12                                  |                            |

|     | 100   | 16                                  |                            |

|     | 101   | Reserved                            |                            |

|     | 110   | Reserved                            |                            |

|     | 111   | Reserved                            |                            |

| 6:5 | 00    | Reserved                            | Serial format              |

|     | 01    | Reserved                            |                            |

|     | 10    | DAC aux mode                        |                            |

|     | 11    | Reserved                            |                            |

| 7   | 0     | Latch in midcycle (normal)          | BCLK active edge (TDM in)  |

|     | 1     | Latch in at end of cycle (pipeline) |                            |

**Table 23. Auxiliary TDM Control 1**

| Bit | Value | Function                                                        | Description        |

|-----|-------|-----------------------------------------------------------------|--------------------|

| 0   | 0     | 50/50 (allows 32, 24, 20, or 16 bit clocks (BCLKs) per channel) | LRCLK format       |

|     | 1     | Pulse (32 BCLKs per channel)                                    |                    |

| 1   | 0     | Drive out on falling edge (DEF)                                 | BCLK polarity      |

|     | 1     | Drive out on rising edge                                        |                    |

| 2   | 0     | Left low                                                        | LRCLK polarity     |

|     | 1     | Left high                                                       |                    |

| 3   | 0     | Slave                                                           | LRCLK master/slave |

|     | 1     | Master                                                          |                    |

| 5:4 | 00    | 64                                                              | BCLKs per frame    |

|     | 01    | 128                                                             |                    |

|     | 10    | 256                                                             |                    |

|     | 11    | 512                                                             |                    |

| 6   | 0     | Slave                                                           | BCLK master/slave  |

|     | 1     | Master                                                          |                    |

| 7   | 0     | AUXTDMBCLK pin                                                  | BCLK source        |

|     | 1     | Internally generated                                            |                    |

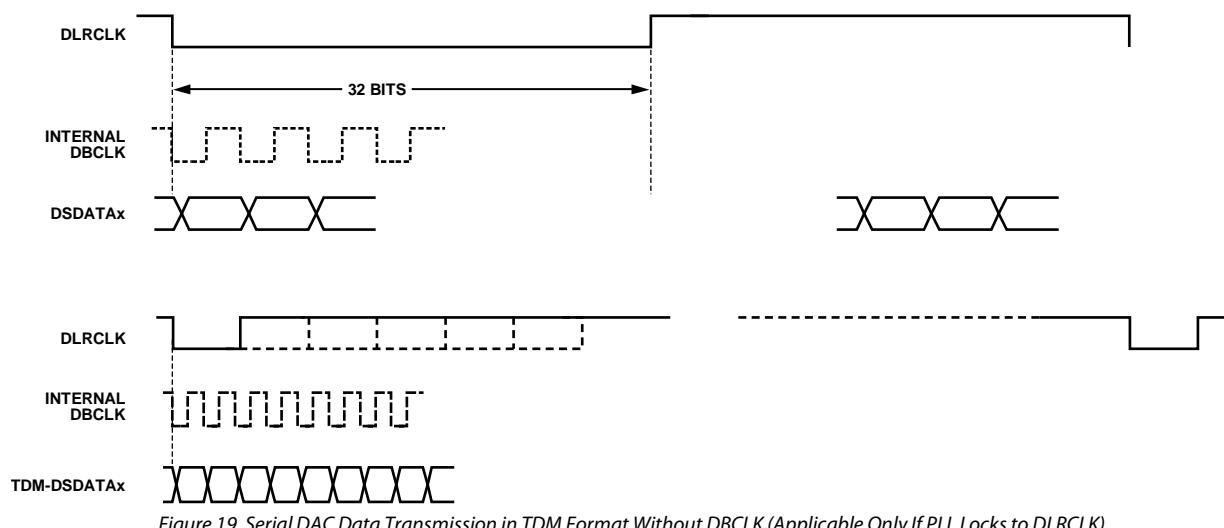

## ADDITIONAL MODES

The AD1933 offers several additional modes for board level design enhancements. To reduce the EMI in board level design, serial data can be transmitted without an explicit BCLK. See Figure 19 for an example of a DAC TDM data transmission mode that does not require high speed DBCLK. This configuration is applicable when the AD1933 master clock is generated by the PLL with the DLRCLK as the PLL reference frequency.

To relax the requirement for the setup time of the AD1933 in cases of high speed TDM data transmission, the AD1933 can latch in the data using the falling edge of DBCLK. This effectively dedicates the entire BCLK period to the setup time. This mode is useful in cases where the source has a large delay time in the serial data driver. Figure 20 shows this pipeline mode of data transmission. Both the BLCK-less and pipeline modes are available.