A Business Partner of

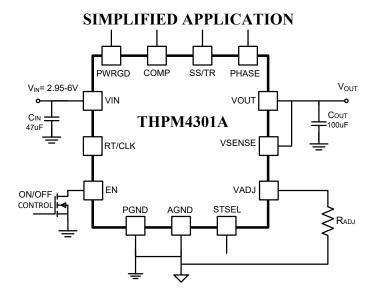

# THPM4301A

## 3.3V/5V Input 6A Output POL Power Module

#### **Features**

- Integrated Point of Load power module using in Inductor technology

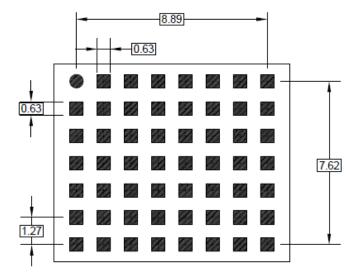

- Small footprint, low-profile, 11mm x 9.1mm x 2.8mm, with LGA Package (0.63 mm Pads)

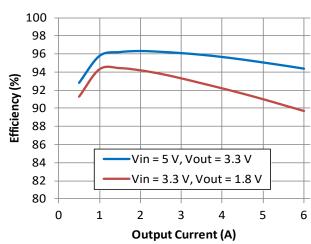

- Efficiency up to 96%

- High output current, 6A without derating at 85°C ambient with no air flow

- Wide output voltage adjustment: 0.6V to 3.6V

- Pre-bias startup capability

- User adjustable switching frequency

- Synchronization to external clock signal

- Adjustable soft-start time for output voltage

- Output voltage sequencing / tracking

- Enable signal input and Power Good signal output

- Programmable Under Voltage Lock Out (UVLO)

- Output Over Current Protection (OCP)

- Over temperature protection

- Operating temperature range -40°C to 85°C

#### **Applications**

- Broadband and communications equipment

- DSP and FPGA Point of Load applications

- High density distributed power systems

- PCI express / PXI express

- Automated test and medical equipment

#### Description

THPM4301A is an easy-to-use 6A output integrated Point of Load (POL) power supply module. It contains integrated power MOSFETs, driver, PWM controller, a high-performance inductor, input and output capacitors and other passive components in one low profile LGA package using Inductor technology.

There is no need for loop compensation, sensitive PCB layout, inductor selection or in-circuit production testing. Each module is fully tested.

The THPM4301A can be programmed for any output voltage between 0.6V and 3.6V using a single external resistor. For an output voltage of 0.6V no resistor is required.

THPM4301A can deliver full 6A load current without derating at 85°C ambient temperature with no airflow.

Small size (11mm x 9.1mm) and low profile (2.8mm) allows the THPM4301A to be placed very close to its load or on the back side of the PCB for high density applications.

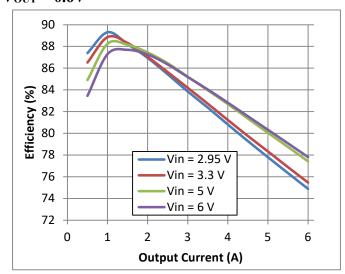

#### EFFICIENCY VS LOAD CURRENT

1/24

# ABSOLUTE MAXIMUM (1) RATINGS over operating temperature range (unless otherwise noted)

|                |                                     | VAl  | VALUE |      |

|----------------|-------------------------------------|------|-------|------|

|                |                                     | MIN  | MAX   | Unit |

|                | VIN                                 | -0.3 | 7     | V    |

|                | EN                                  | -0.3 | 7     | V    |

|                | VSENSE                              | -0.3 | VOUT  | V    |

| I 37 - 14      | COMP                                | -0.3 | 3     | V    |

| Input Voltage  | PWRGD                               | -0.3 | 6     | V    |

|                | SS / TR                             | -0.3 | 3     | V    |

|                | STSEL                               | -0.3 | 3     | V    |

|                | RT / CLK                            | -0.3 | 6     | V    |

| Output Voltage | VOUT                                | -0.6 | VIN   | V    |

| Source Current | EN                                  |      | 100   | μΑ   |

| Source Current | RT / CLK                            |      | 100   | μΑ   |

|                | COMP                                |      | 100   | μΑ   |

| Sink Current   | PWRGD                               |      | 10    | mA   |

|                | SS / TR                             |      | 100   | μΑ   |

|                | Operating Junction Temperature      |      | 150   | °C   |

| Temperature    | Storage Temperature                 | -55  | 150   | °C   |

|                | Peak solder reflow body temperature |      | 245   | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the module. These are stress ratings only, and functional operation of the module at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect reliability.

### **ORDERING INFORMATION**

| Output Voltage | <b>Module Part Number</b> | Pad Finish | Package Type | Temperature Range |

|----------------|---------------------------|------------|--------------|-------------------|

| Adjustable     | THPM4301A                 | Au (RoHS)  | LGA          | -40°C to 85°C     |

A Business Partner of

### **ELECTRICAL CHARACTERISTICS:**

The electrical performance is based on the following conditions unless otherwise stated: 25°C ambient temperature, no air flow;  $V_{IN} = 5V$ ,  $^{(1)}V_{OUT} = 1.8V$ ,  $I_{OUT} = 6A$ ,  $C_{INI} = 47\mu F$  ceramic,  $C_{OUT} = 2 \times 47\mu F$  ceramic.

| PARAMETERS           |                                          | TEST CONDITIONS                                           |                    |                                               | MIN   | TYP   | MAX  | UNIT |

|----------------------|------------------------------------------|-----------------------------------------------------------|--------------------|-----------------------------------------------|-------|-------|------|------|

| I <sub>OUT</sub> :   | Output current                           | $T_A = -40$ °C to 85°C, natural convection                |                    | 0                                             |       | 6     | A    |      |

| V <sub>IN</sub> :    | Input voltage                            | Over I <sub>OUT</sub> range, -40°C to 85°C                |                    | 2.95                                          |       | 6     | V    |      |

| $V_{START}$          | Startup voltage                          | Over I <sub>OUT</sub> range, -40                          | 0°C to             | o 85°C [Note 1]                               |       | 2.8   |      | V    |

| UVLO                 | Under Voltage Lock Out                   | Over I <sub>OUT</sub> range, -40                          | 0°C to             | o 85°C [Note 1]                               |       | 2.5   |      | V    |

| Hystere              | esis between V <sub>START</sub> and UVLO | Over I <sub>OUT</sub> range [No                           | ote 1]             |                                               |       | 0.3   |      | V    |

|                      | Set point accuracy                       | $T_A = 25$ °C, $I_{OUT} = 3$                              | BA [N              | ote 2]                                        |       | ±1%   |      |      |

|                      | Temperature variation                    | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}$ | C, Iou             | UT = 3A                                       |       | ±0.3% |      |      |

| $V_{OUT}$            | Line regulation                          | Over V <sub>IN</sub> range, T <sub>A</sub>                | $= 25^{\circ}$     | $^{\circ}$ C, $I_{OUT} = 3A$                  |       | ±0.2% |      |      |

|                      | Load regulation                          | Over $I_{OUT}$ range, $T_A = 25$ °C, $V_{IN} = 5V$        |                    |                                               | ±0.2% |       |      |      |

| V <sub>OUT(ad)</sub> | : Output voltage adjust range            | Over I <sub>OUT</sub> range, T <sub>A</sub>               | $\lambda = -40$    | 0°C to 85°C                                   | 0.6   |       | 3.6  | V    |

|                      | Efficiency                               | V - 5V                                                    | V <sub>OUT</sub> = | $= 3.3 \text{V}, I_{\text{OUT}} = 3 \text{A}$ |       | 96.1% |      |      |

|                      |                                          | $V_{IN} = 5V$                                             | V <sub>OUT</sub> = | $= 3.3 \text{V}, I_{\text{OUT}} = 6 \text{A}$ |       | 94.2% |      |      |

| η                    |                                          | V - 2 2V                                                  | V <sub>OUT</sub> = | $= 2.5 \text{V}, I_{\text{OUT}} = 3 \text{A}$ |       | 95.4% |      |      |

|                      |                                          | $V_{IN} = 3.3V$ $V_{OUT} = 2.5V, I_{OUT} = 6A$            |                    | $= 2.5 \text{V}, I_{\text{OUT}} = 6 \text{A}$ |       | 92.3% |      |      |

| $F_S$                | Switching frequency [Note 3]             | $R_T = 127K\Omega$ between RT/CLK and AGND                |                    |                                               | 750   |       | kHz  |      |

| Output               | voltage ripple                           | 20MHz bandwidth                                           |                    |                                               | 20    |       | mVpp |      |

| $I_{LIM}$            | Current Limit Point                      |                                                           |                    |                                               | 9.0   |       | A    |      |

| $V_{\text{EN-H}}$    | Enable control                           | Enable high voltage                                       |                    |                                               | 1.3   |       | V    |      |

| $V_{\text{EN-L}}$    | Enable control                           | Enable low voltage                                        |                    |                                               | 1.18  |       | V    |      |

|                      |                                          | 37 41 1 11                                                | 1.4                | Good                                          |       | 93%   |      |      |

| PWR G                | tood:                                    | V <sub>OUT</sub> rising threshold                         |                    | Fault                                         |       | 105%  |      |      |

| FWKG                 | ioou.                                    | V falling throughold                                      | -14                | Good                                          |       | 103%  |      |      |

|                      |                                          | V <sub>OUT</sub> falling threshold                        |                    | Fault                                         |       | 91%   |      |      |

| Thorms               | ıl shutdown                              | Thermal shutdown                                          |                    |                                               | 170   |       | °C   |      |

| 1 Helilla            | ii Siiutuowii                            | Thermal shutdown recovery hysteresis                      |                    |                                               | 15    |       | °C   |      |

**Note 1**: With  $R_{EN1} = 14.7 k \Omega$  and  $R_{EN2} = 12.7 k \Omega$  as shown in Fig. 28.

**Note 2:** With 0.1% tolerance external voltage set resistor.

Note 3: 750kHz is suitable for 3.3V output, but lower switching frequencies are recommended for lower output voltages. See

Table 3 for recommended switching frequency, and refer to page 19 for information on adjusting the frequency.

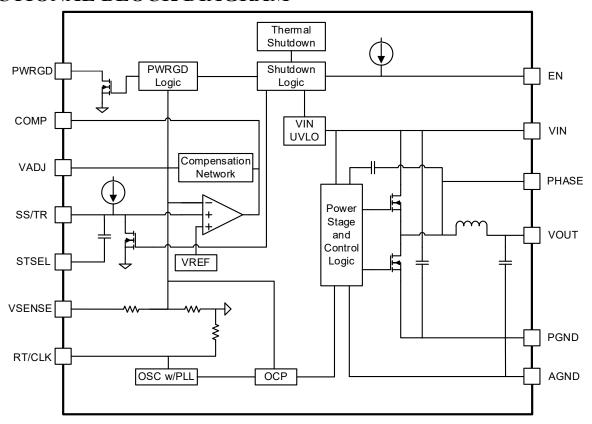

## FUNCTIONAL BLOCK DIAGRAM

A Business Partner of

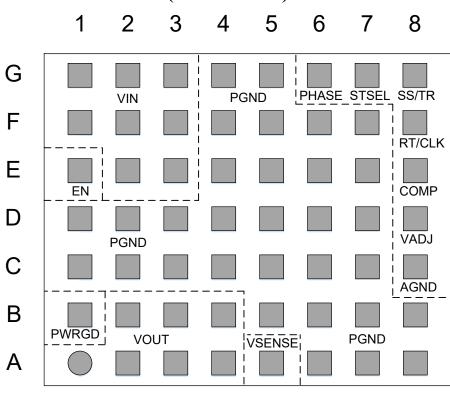

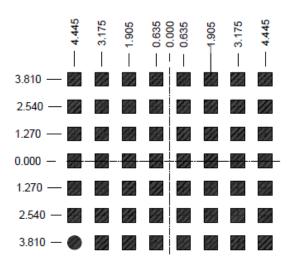

# PIN DESCRIPTIONS

| PIN Name                                                                                        | Description                                                                                          |  |  |  |

|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|--|--|

| VIN                                                                                             | The positive input voltage power pin, which is referenced to PGND. Connect external input            |  |  |  |

| (E2-E3, F1-F3, G1-G3)                                                                           | filter capacitors between these pins and PGND plane, close to module.                                |  |  |  |

| PHASE                                                                                           | Switching node pin. Connect this pin to a small copper island under the module for best              |  |  |  |

| (G6)                                                                                            | thermal performance. Do not connect any external component to this pin or use this pin for any       |  |  |  |

| (00)                                                                                            | other functions.                                                                                     |  |  |  |

| VOUT                                                                                            | Output voltage. Connect external output filter capacitors between these pins and PGND plane,         |  |  |  |

| (A1-A4, B2-B4)                                                                                  | close to the module.                                                                                 |  |  |  |

| PGND                                                                                            | Zero DC voltage reference for power circuitry. These pins should be connected directly to            |  |  |  |

| (A6-A8, B5-B8, C1-C7,                                                                           | the PCB ground plane. The module's heat transfer is through these pins and all of them must be       |  |  |  |

| D1-D7, E4-E7, F4-F7,                                                                            | connected together externally with a copper plane located directly under the module.                 |  |  |  |

| G4-G5)                                                                                          |                                                                                                      |  |  |  |

|                                                                                                 | <b>Zero DC voltage reference for the analog control circuitry</b> . A small analog ground plane is   |  |  |  |

| AGND                                                                                            | recommended. RT/CLK, STSEL, SS/TR pins should be referenced to analog ground. AGND                   |  |  |  |

| (C8)                                                                                            | and PGND should be connected at a single point is such a way that load current does not flow         |  |  |  |

|                                                                                                 | in the AGND plane.                                                                                   |  |  |  |

|                                                                                                 | <b>Startup mode selection</b> . Short to AGND for soft-start operation with extended soft-start time |  |  |  |

| STSEL                                                                                           | determined by a capacitor connected between SS/TR pin and AGND. Leave this pin open for              |  |  |  |

| (G7)                                                                                            | tracking operation or selecting default soft-start time that is nominally 1.1ms. See SS/TR pin       |  |  |  |

|                                                                                                 | description below for more details.                                                                  |  |  |  |

|                                                                                                 | <b>Soft-start or tracking operation</b> . When SS/TR pin is open and STSEL pin is shorted to         |  |  |  |

|                                                                                                 | AGND, the power module operates in soft-start mode with the default soft-start time of 1.1ms.        |  |  |  |

| SS/TR                                                                                           | Longer soft-start time can be achieved with an additional capacitor connected between SS/TR          |  |  |  |

| (G8)                                                                                            | pin and AGND.                                                                                        |  |  |  |

| (30)                                                                                            | Capacitor value can be selected based on Equation 4 or values provided in Table 2. For               |  |  |  |

|                                                                                                 | tracking operation, leave STSEL open and do not connect additional capacitor between SS/TR           |  |  |  |

|                                                                                                 | and AGND. Connect this pin to the voltage to be tracked. Refer to Fig. 30 for more details.          |  |  |  |

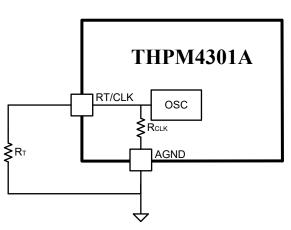

|                                                                                                 | Switching frequency and external synchronization pin. An internal $90.9K\Omega$ resistor is          |  |  |  |

| RT/CLK                                                                                          | connected between RT/CLK and AGND to set the switching frequency to 450KHz. An external              |  |  |  |

| (F8)                                                                                            | synchronization clock can be connected to RT/CLK pin to synchronize the switching frequency          |  |  |  |

|                                                                                                 | of the module. More details are provided on page 19.                                                 |  |  |  |

|                                                                                                 | <b>Enable pin</b> with internal pull-up current source. Pull this pin to below 1.18V to disable the  |  |  |  |

| EN                                                                                              | power module. Float this pin or pull to above 1.3V to enable the power module. This pin can be       |  |  |  |

| (E1)                                                                                            | used to adjust the under voltage lockout (UVLO) level with two additional resistors forming a        |  |  |  |

|                                                                                                 | voltage divider from V <sub>IN</sub> to AGND as shown in Fig. 28.                                    |  |  |  |

| COMP                                                                                            | Compensation pin. The COMP pin should be open.                                                       |  |  |  |

| (E8)                                                                                            |                                                                                                      |  |  |  |

| VADJ                                                                                            | Output voltage adjustment pin. Connect a resistor, R <sub>ADJ</sub> , between VADJ pin and AGND pin  |  |  |  |

| (D8)                                                                                            | to set the desired output voltage, as shown in Fig. 15.                                              |  |  |  |

| PWRGD                                                                                           | <b>Power Good pin.</b> An open drain output that is pulled low when VSENSE voltage is less than      |  |  |  |

| (B1) 91% or greater than 105% of the nominal output voltage. PWRGD is floating when the         |                                                                                                      |  |  |  |

| at VSENSE pin is between 93% and 103% of the nominal output voltage.                            |                                                                                                      |  |  |  |

| Remote sensing pin for the output voltage. Connect this signal to VOUT close to the load for    |                                                                                                      |  |  |  |

| VSENSE improved regulation. Do not use an LC filter between VOUT pins of the module and the poi |                                                                                                      |  |  |  |

| (A5)                                                                                            | where VSENSE is connected.                                                                           |  |  |  |

|                                                                                                 | <b>Note</b> : this pin is not connected to VOUT inside the module and must be connected externally.  |  |  |  |

# LGA PACKAGE 56 PINS (TOP VIEW)

Security E

A Business Partner of

# TYPICAL CHARACTERISTICS (Note 1)

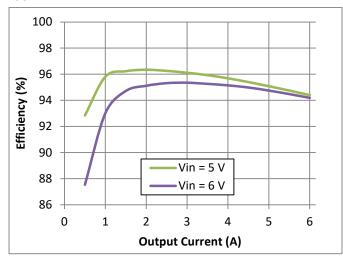

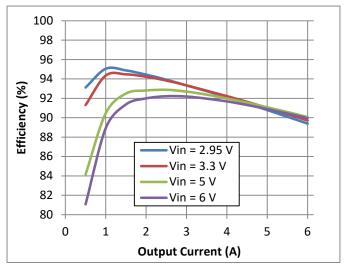

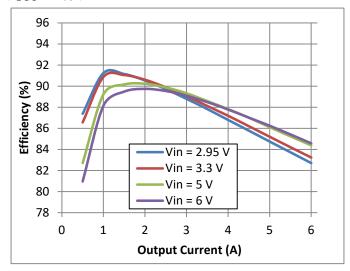

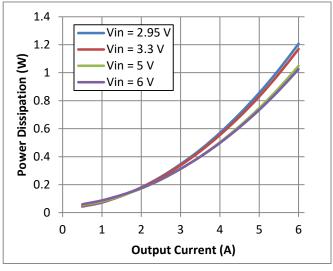

#### $V_{OUT} = 3.3V$

Fig. 1 Efficiency vs Output Current

Fig. 2 Power Dissipation vs Output Current

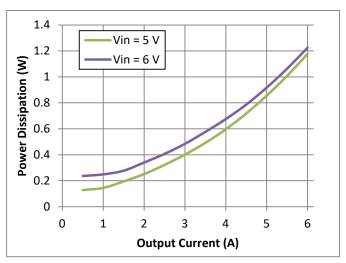

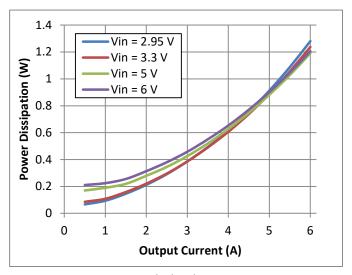

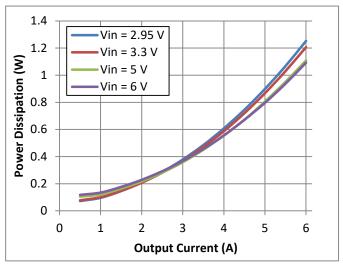

### $V_{OUT} = 2.5V$

Fig. 3 Efficiency vs Output Current

Fig. 4 Power Dissipation vs Output Current

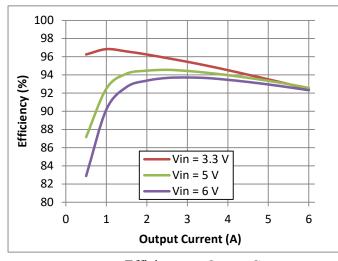

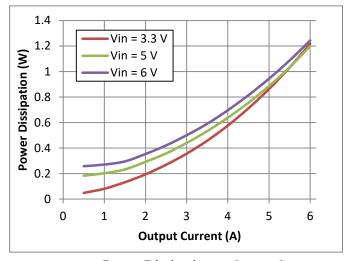

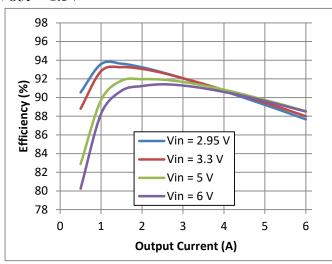

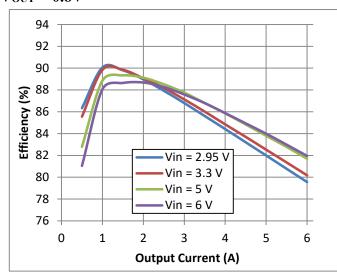

#### $V_{OUT} = 1.8V$

Fig. 5 Efficiency vs Output Current

Fig. 6 Power Dissipation vs Output Current

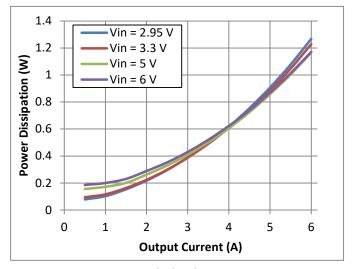

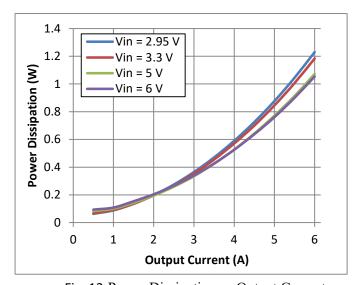

#### $V_{OUT} = 1.5V$

Fig. 7 Efficiency vs Output Current

Fig. 8 Power Dissipation vs Output Current

#### $V_{OUT} = 1.0V$

Fig. 9 Efficiency vs Output Current

Fig. 10 Power Dissipation vs Output Current

#### $V_{OUT} = 0.8V$

Fig. 11 Efficiency vs Output Current

Fig. 12 Power Dissipation vs Output Current

### $V_{OUT} = 0.6V$

Fig. 13 Efficiency vs Output Current

Fig. 14 Power Dissipation vs Output Current

Note 1: The above curves (Fig. 1 to Fig. 14) are derived from measured data taken on samples of the THPM4301A tested at room temperature (25°C), and are considered to be typical for the product.

### APPLICATION INFORMATION

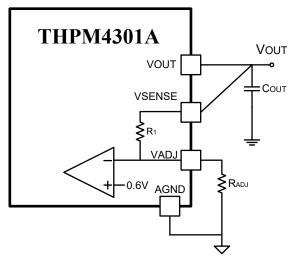

## **Output Voltage Adjustment**

A Business Partner of

The output voltage of THPM4301A can be adjusted from 0.6V to 3.6V using an external resistor between VADJ pin and AGND pin, as shown in Fig. 15. The required resistor value R<sub>ADJ</sub> can be calculated using equation (1).

Fig. 15 Output Voltage Setting

$$R_{ADJ}(K\Omega) = \frac{R_1 \times 0.6}{V_O - 0.6} \tag{1}$$

where  $R1 = 20k\Omega$  and  $V_0$  is the desired output voltage in Volts. For best set-point accuracy, it is recommended to use a 0.1% tolerance resistor. [Note: R1 is internal to the module as shown in Fig. 15].

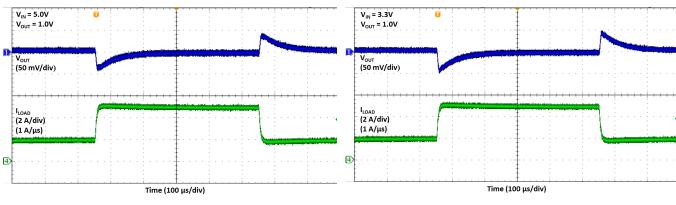

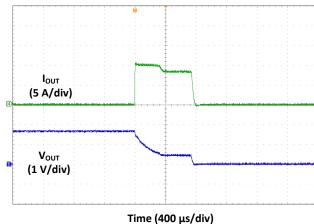

## **Transient Response**

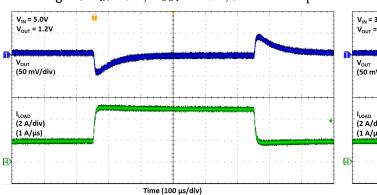

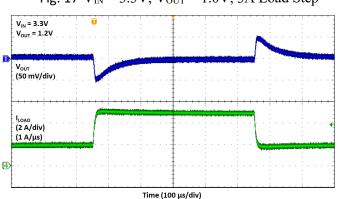

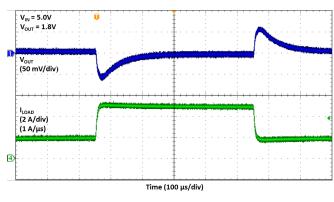

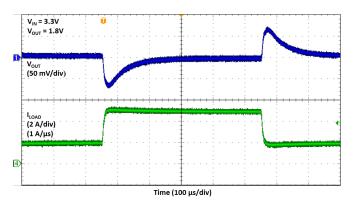

The following table summarizes the measured output voltage overshoot and undershoot when the load current undergoes a step change between 2A and 5A. The slew rate for the current change is 1A/µs. The measured waveforms are given from Fig. 16 to Fig. 21. The measurement is obtained when the input capacitor consists of one 47μF ceramic capacitor in parallel with one 220µF electrolytic capacitor, and the output capacitor consists of four 47µF ceramic capacitors in parallel. If smaller output voltage deviation is required, larger output capacitor values can be used.

Table 1. Output Voltage Transient Response

Testing Conditions: C<sub>IN1</sub> = 1 x 47μF CERAMIC, C<sub>IN2</sub> = 220μF ELECTROLYTIC, C<sub>OUT</sub> = 4 × 47μF CERAMIC

|             |                      | 3A LOAD STEP, 2A to 5A, (1A/μs) |               |  |

|-------------|----------------------|---------------------------------|---------------|--|

| $V_{IN}(V)$ | V <sub>OUT</sub> (V) | VOLTAGE DEVIATION               | RECOVERY TIME |  |

|             |                      | (mV)                            | (µs)          |  |

| 3.3         | 1.0                  | 50                              | 155           |  |

| 5.0         | 1.0                  | 45                              | 145           |  |

| 3.3         | 1.2                  | 55                              | 150           |  |

| 5           | 1.2                  | 50                              | 150           |  |

| 3.3         | 1.8                  | 70                              | 170           |  |

| 5           |                      | 65                              | 165           |  |

Fig. 16  $V_{IN} = 5V$ ,  $V_{OUT} = 1.0V$ , 3A Load Step

Fig. 17  $V_{IN} = 3.3V$ ,  $V_{OUT} = 1.0V$ , 3A Load Step

Fig. 18  $V_{IN} = 5V$ ,  $V_{OUT} = 1.2V$ , 3A Load Step

Fig. 19  $V_{\rm IN}$  = 3.3V,  $V_{\rm OUT}$  = 1.2V, 3A Load Step

Fig. 20  $V_{IN}$  = 5V,  $V_{OUT}$  = 1.8V, 3A Load Step

Fig. 21  $V_{IN} = 3.3V$ ,  $V_{OUT} = 1.8V$ , 3A Load Step

## **Application Schematics**

A Business Partner of

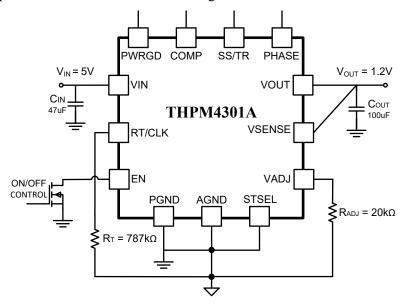

Fig. 22 shows a typical schematic for a 1.2V output application using THPM4301A with switching frequency of 500 kHz. The adjustment resistor, R<sub>ADJ</sub>, is selected as 20kΩ calculated based on Equation (1). RT/CLK is connected to ground with a 787k $\Omega$  resistor to select the recommended switching frequency. STSEL pin is connected to AGND to select the default startup time. The ON/OFF CONTROL signal is used to turn on and off the power module.

Fig. 22 Typical Schematic  $V_{IN} = 2.95V$  to 6.0V,  $V_{OUT} = 1.2V$ ,  $F_S = 500kHz$

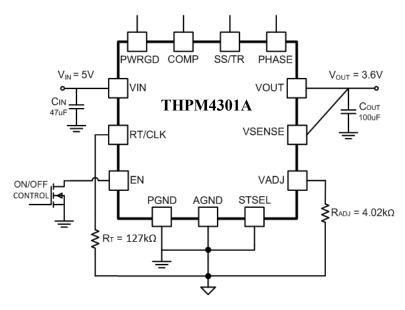

Fig. 23 shows a typical schematic for a 5V input, 3.6V output application using THPM4301A. The adjustment resistor,  $R_{ADJ}$ , is selected as  $4.02k\Omega$  calculated based on Equation (1). In this example, the switching frequency is selected as 750kHz by connecting the timing resistor of  $127k\Omega$  between RT/CLK pin and AGND pin.

Fig. 23 Typical Schematic  $V_{IN} = 4.4V$  to 6.0V,  $V_{OUT} = 3.6V$ ,  $F_S = 750kHz$

## **Power Good (PWRGD)**

The PWRGD pin is an open drain output, and can be used to indicate when the output voltage is within the normal operating range. This pin is pulled low when VSENSE voltage is less than 91% or greater than 105% of the nominal output voltage. Also, the PWRGD pin is pulled low if the input UVLO or thermal shutdown is asserted, or if the EN pin is pulled low.

There is a 2% hysteresis, so once the VSENSE pin is within 93% to 103% of the nominal output voltage the PWRGD pin is de-asserted and the pin floats.

It is recommended to use a pull-up resistor between  $1k\Omega$  and  $100k\Omega$  to a voltage source that is 5.5V or less. The PWRGD will be in a valid state (high or low as above) once the VIN input voltage is greater than 1.2V.

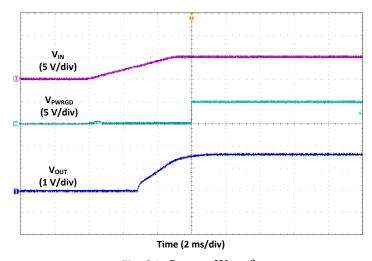

## **Power-Up Characteristics**

When configured as shown in the front page schematic (page 1), THPM4301A produces a regulated output voltage whenever a valid input voltage is present.

During the power-up, internal soft-start circuitry slows the rate that the output voltage rises, thereby limiting the charging current to the output capacitor.

Fig. 24 shows the startup waveforms for THPM4301A, operating from a 5V input and with the output voltage adjusted to 1.8V. The waveform is measured with a 3A constant current load.

Fig. 24 Startup Waveforms

## Enable (On/Off) Operation and Under Voltage Lockout (UVLO) Setup

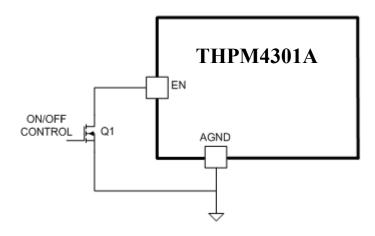

The EN pin provides an external on/off control of the power module and is lightly pulled up internally with a current source. The module is enabled if this pin is left open or its voltage exceeds the  $V_{\text{EN-H}}$  threshold voltage, and the power module starts operation once the input voltage is higher than  $V_{\text{START}}$ .

When the voltage at EN pin is below the  $V_{\text{EN-L}}$  threshold voltage, the power module stops switching and enters low quiescent current state.

If an application requires controlling the EN pin, an open drain or open collector logic can be used to interface with the pin, as shown in Fig. 25. In this figure, high ON/OFF CONTROL signal level (Low EN) disables the power module.

14/24

Copyright©2019 THine Electronics, Inc.

Fig. 25 Typical ON/OFF Control Schematic

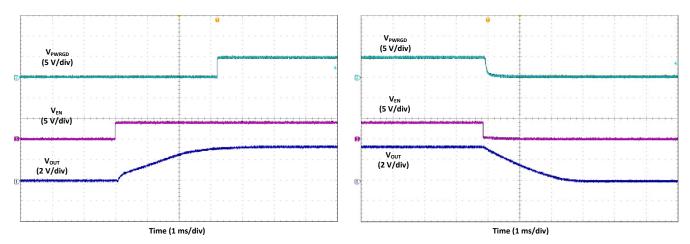

Fig. 26 and Fig. 27 show the typical output voltage waveforms when THPM4301A is enabled (turned on) and disabled (turned off) by the EN pin. In these figures, the top trace is the power good signal, the middle trace is the EN pin voltage, and the bottom trace is the output voltage.

Fig. 26 Waveforms at Enable Turn-On

Fig. 27 Waveforms at Enable Turn-Off

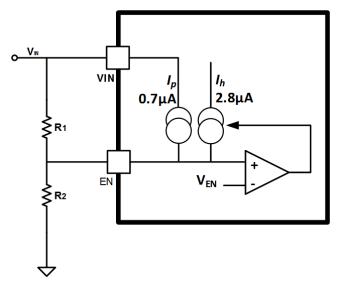

Under-voltage lockout can be used to prevent the output from starting until the input voltage is within its normal range. For input under voltage lockout (UVLO) adjustment, use the EN pin as shown in Fig. 28 to set the UVLO level by using two external resistors. Once the EN pin voltage exceeds 1.3V, an additional  $2.8\mu A$  of current is added to provide input voltage hysteresis. Resistor  $R_{EN1}$  and  $R_{EN2}$  can be calculated using Equations (4) and (5) based on the required startup voltage and shutdown voltage.

Fig. 28 Input Under-Voltage Lockout Setup

$$R_{EN1} = \frac{V_{START} \left( \frac{V_{EN\_FALLING}}{V_{EN\_RISING}} \right) - UVLO}{I_p \left( 1 - \frac{V_{EN\_FALLING}}{V_{EN\_RISING}} \right) + I_h}$$

$$R_{EN2} = \frac{R_{EN1} \times V_{EN\_FALLING}}{UVLO - V_{EN\_FALLING} + R_{EN1} \times (I_p + I_h)}$$

(5)

$$R_{EN2} = \frac{R_{EN1} \times V_{EN\_FALLING}}{UVLO - V_{EN\_FALLING} + R_{EN1} \times (I_p + I_h)}$$

(5)

$I_h = 2.8 \mu A$ ,  $I_p = 0.7 \mu A$ ,  $V_{EN~RISING} = 1.3 V$ ,  $V_{EN~FALLING} = 1.18 V$ .

As an example, if  $R_{EN1} = 14.7 \text{k} \Omega$  and  $R_{EN2} = 12.7 \text{k} \Omega$ ,  $V_{START}$  will be 2.8V and UVLO will be 2.5V.

It is recommended to set the minimum UVLO level of the module at 2.45V or higher to ensure proper operation before shutdown.

## **Soft-Start or Tracking Pin (SS/TR)**

The soft-start function forces the output voltage to rise gradually to its nominal value rather than rising as rapidly as possible. Soft-Start mode is selected when the module is used independently without tracking or sequencing. To select soft-start operation mode the STSEL pin is connected to AGND. This will activate the internal soft-start capacitor for a nominal soft-start time of 1.1ms. An external capacitor between the SS/TR pin to ground can be used to increase the soft-start time to higher values if desired.

Table 2 shows the soft-start time using typical soft-start capacitor values.

Table 2. Soft-start capacitor values and soft-start time

| External capacitor (nF) | open | 4.7 | 10  |

|-------------------------|------|-----|-----|

| SS Time (ms)            | 1.1  | 2.7 | 4.4 |

If other startup time is needed, Equation (6) provides the relationship between the external soft-start capacitor value  $C_{SS}$  and the soft-start time,  $T_{SS}$ .

16/24

$$C_{SS} = 3 \times T_{SS}(ms) - 3.3(nF) \tag{6}$$

Copyright©2019 THine Electronics, Inc.

#### THPM4301A Rev.1.00 E

During the soft-start period, VSENSE voltage will follow the SS/TR pin voltage up to 90% of the nominal voltage setpoint. When the SS/TR voltage is greater than 90% of the nominal voltage, the effective system reference voltage will be changed from the SS/TR voltage to the internal voltage reference to close the voltage loop.

If the input voltage falls below the UVLO, or a thermal shutdown event occurs, or the EN pin is pulled down to below 1.18V, the THPM4301A will stop switching and the SS/TR will be discharged to below 60mV before the module restarts.

## Sequencing and Tracking

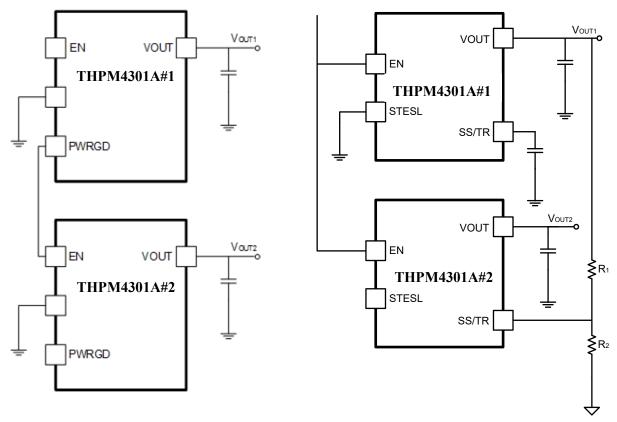

The term sequencing is used when two or more separate modules are configured to start one after the other, in sequence. The term tracking is used when two or more modules are configured so that they start together, with their output voltages tracking each other during startup. This is done by having one module act as a master and the other(s) act as slave(s). Sequencing and tracking startup can be implemented using the SS/TR, EN and PWRGD pins.

The sequential startup connection is shown in Fig. 29. The power good pin (PWRGD) of the first THPM4301A module is connected to the EN pin of the second THPM4301A module, which will be enabled only after the output voltage of the first THPM4301A module reaches regulation range and its PWRGD is asserted. **Note**: The THPM4301A can start in sequence with another THPM4301A or with any other POL having a compatible Power Good output.

With tracking mode the output voltage of the THPM4301A is controlled by another voltage applied to its SS/TR input. Tracking startup of two THPM4301A modules can be achieved by connecting a resistor network of  $R_1$  and  $R_2$  as shown in Fig. 30, where the output voltage of the second THPM4301A module (bottom) will track the output voltage of the first THPM4301A module (top). In this case, the soft-start time of THPM4301A module #1 is determined by the capacitor connected to its SS/TR pin and the STSEL pin is connected to ground. The voltage at SS / TR pin of the second THPM4301A module is directly controlled by the output voltage of the first THPM4301A module through the resistor divider ( $R_1$  and  $R_2$ ). The STSEL pin of the second THPM4301A module should be left open. Resistor divider  $R_1$  and  $R_2$  in Fig. 30 can be calculated using Equations (7) and (8). Note: The THPM4301A can track any external voltage, so the master can be a THPM4301A or any other POL.

$$R_1 = \frac{V_{OUT1} \times 5}{0.9} (k\Omega) \tag{7}$$

$$R_2 = \frac{0.9 \times R_1}{V_{OUT1} - 0.9} (k\Omega) \tag{8}$$

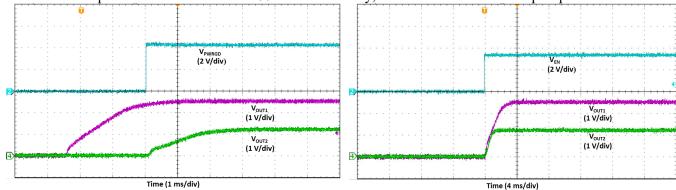

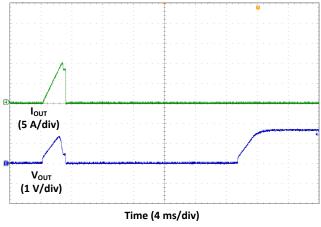

Fig. 31 gives the output voltage waveforms of two THPM4301A modules operating in sequential startup mode. It shows that PWRGD signal becomes high when the first THPM4301A (2.5V output in this example) enters regulation and then the second THPM4301A (1.2V output in the example) begins to start up.

Fig. 32 gives the output voltage waveforms of two THPM4301A modules operating in tracking startup mode. It shows that  $V_{OUT1}$  follows  $V_{OUT2}$  until the lower voltage rail ( $V_{OUT2}$ ) enters regulation (1.2V in this example). Then,  $V_{OUT1}$  continues to rise to its steady state value (2.5V in the example).

17/24

Copyright©2019 THine Electronics, Inc.

A Business Partner of

Fig. 29 Sequencing Startup Schematic

Fig. 30 Tracking Startup Schematic

**Note**: when used in tracking mode, if the slave unit (module #2 in Fig. 30) shuts down while the other module is still operating, a latch-up condition can occur where the slave unit does not restart. To avoid this, it is necessary to pull down the SS/TR pin of module #2 to below 60mV momentarily, to initiate a normal start-up sequence.

Fig. 31 Sequencing Startup,

$$V_{OUT1} = 2.5V, V_{OUT2} = 1.2V$$

Fig. 32 Tracking Startup,

$$V_{OUT1} = 2.5V, V_{OUT2} = 1.2V$$

# Switching Frequency Selection and Timing Resistor (RT/CLK Pin)

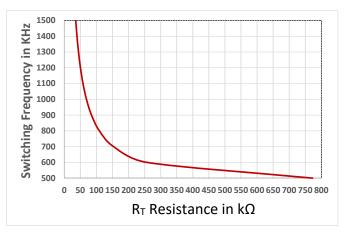

The switching frequency of the THPM4301A can be adjusted over a wide range from approximately 450 kHz to 750kHz. A resistor between RT/CLK and AGND can be used to increase the switching frequency. An internal resistor,  $R_{CLK}=90.9k\Omega$ , sets the minimum (default) switching frequency to 450 KHz. Generally, a higher frequency is preferred for higher output voltages as indicated in Table 3 .

The user can increase the switching frequency by adding an external resistor,  $R_T$ , between RT/CLK pin and AGND, as shown in Fig. 33, where  $R_T$  is calculated using Equation (9). The relationship between switching frequency and  $R_T$  resistor value is shown in Fig. 34.

$$R_{T}(k\Omega) = \frac{R_{CLK}}{\left[F_{SW}(kHz)\right]^{1.052} \times R_{CLK} - 1}$$

(9)

Fig. 33 Switching Frequency Adjustment

Fig. 34 Switching Frequency vs R<sub>T</sub> for THPM4301A

The recommended switching frequency for different output voltages is shown in Table 3, which also shows the nearest standard 1% values for R<sub>T</sub>.

19/24

Table 3. - Recommended switching frequency and  $R_T$  value

| Output voltage | Recommended switching frequency (kHz) | Resistor R <sub>T</sub> |

|----------------|---------------------------------------|-------------------------|

| 3.3            | 750                                   | 127kΩ                   |

| 2.5            | 650                                   | 191kΩ                   |

| 1.8            | 600                                   | 255kΩ                   |

| 1.5            | 550                                   | 383kΩ                   |

| 1.2            | 500                                   | 787kΩ                   |

| 1.0            | 500                                   | 787kΩ                   |

| 0.8            | 450                                   | Open                    |

| 0.6            | 450                                   | Open                    |

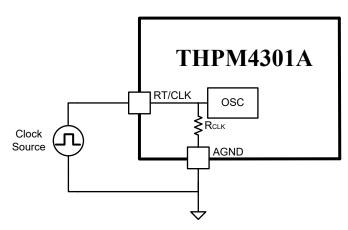

# Synchronization with RT/CLK pin

RT/CLK pin can also be used to synchronize the THPM4301A to an external system clock, as shown in Fig. 35. To implement the synchronization feature, a clock signal with on time of at least 75ns should be applied to the RT/CLK pin. The logic zero level of the clock signal must be lower than 0.6V and the logic high level of the clock signal must be higher than 1.6V. The synchronization frequency range is between 450kHz and 750kHz.

The rising edge of the phase node (PHASE) will be synchronized to the falling edge of RT/CLK pin.

Fig. 35 Synchronizing to a System Clock

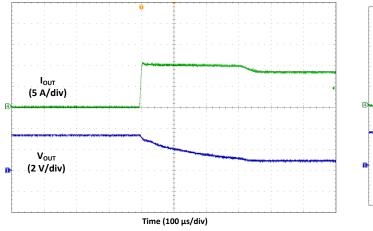

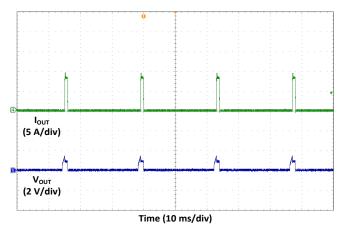

## **Over-Current Protection**

A Business Partner of

A hiccup current limiting function is provided in the THPM4301A to protect against output overload or short-circuit. During an over-current condition, the load current is initially limited to approximately 9A and the output voltage is reduced to approximately 0.8V as shown in Fig. 36. If the over-current condition is not removed within approximately 1ms, the module will be shut down, as shown in Fig. 37. [Please note that the time scale is different for these two figures.

Fig. 36 Over-current Limiting

Fig. 37 Hiccup Mode Current Limit Shut-down

When the over-current condition is removed, the output voltage recovers automatically to the nominal voltage, as shown in Fig. 38. If the over-current condition is not removed, the power module operates in hiccup mode, as shown in Fig. 39. The hiccup period is about 25ms.

21/24

Fig. 38 Recovery from Over-current Shut-down

Fig. 39 Hiccup Mode Current Limit Restart into Short-Circuit

#### THPM4301A Rev.1.00 E

## **Input protection**

In most applications, the input power source provides current limiting (typically fold-back or hiccup mode) and as long as the average fault current is limited to approximately 10A or less, no further protection is required.

If the THPM4301A is powered from a battery or other high current source, it is recommended to include an external fuse (maximum 10A) in the input to the module. The THPM4301A includes full protection against output overcurrent or short-circuit, and the fuse will not operate under any output overload condition.

### **Thermal Considerations**

The absolute maximum junction temperature is 150°C but it is recommended to keep the operating temperature well below this value. Maximum recommended case temperature is 115°C, which corresponds to a junction temperature of approximately 125°C.

The thermal resistance from case to ambient ( $\theta_{CA}$ ) depends on the PCB layout as well as the amount of cooling airflow. When mounted on the EVM,  $\theta_{CA}$  is approximately 15°C/watt in still air.

THPM4301A implements an internal thermal shutdown to protect itself if the junction temperature of the power MOSFET exceeds 170°C. The thermal shutdown forces the module to stop switching when the junction temperature exceeds the thermal shutdown threshold. Once the die temperature reduces by about 15°C, the module restarts automatically.

## **Layout Considerations**

To achieve the best electrical and thermal performance, an optimized PCB layout is required. Some considerations for the PCB layout are:

- Use large copper areas for power planes (V<sub>IN</sub>, V<sub>OUT</sub>, and especially PGND) to minimize conduction loss and thermal stress.

- Place ceramic input and output capacitors close to the module pins to minimize high frequency noise.

- Place any additional output capacitors between the main ceramic capacitor and the load.

- Connect the AGND and PGND copper areas at a single point, preferable under the AGND pin of the module.

22/24

- Place R<sub>SENSE</sub>, R<sub>T</sub>, and C<sub>SS</sub> as close as possible to their respective pins.

- Do not connect the PHASE pin to any other components.

- Use multiple vias to connect the power planes to internal layers.

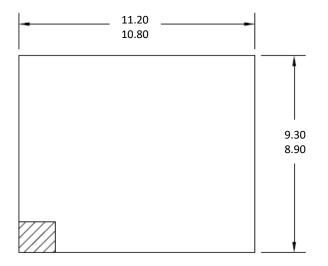

# Package dimensions and PCB pads

ALL DIMENSIONS IN MILLIMETERS FLATNESS OF LGA PLANE: MAX 0.1mm

Package Top View

Package Side View

Package Bottom View

Suggested PCB Layout Top View

#### THPM4301A Rev.1.00 E

## **Notices and Requests**

- 1. The product specifications described in this material are subject to change without prior notice.

- 2. The circuit diagrams described in this material are examples of the application which may not always apply to the customer's design. Thine Electronics, Inc. ("Thine") is not responsible for possible errors and omissions in this material. Please note even if errors or omissions should be found in this material, Thine may not be able to correct them immediately.

- 3. This material contains THine's copyright, know-how or other proprietary. Copying or disclosing to third parties the contents of this material without THine's prior permission is prohibited.

- 4. Note that even if infringement of any third party's industrial ownership should occur by using this product, THine will be exempted from the responsibility unless it directly relates to the production process or functions of the product.

5. Product Application

- 5.1 Application of this product is intended for and limited to the following applications: audio-video device, office automation device, communication device, consumer electronics, smartphone, feature phone, and amusement machine device. This product must not be used for applications that require extremely high-reliability/safety such as aerospace device, traffic device, transportation device, nuclear power control device, combustion chamber device, medical device related to critical care, or any kind of safety device.

- 5.2 This product is not intended to be used as an automotive part, unless the product is specified as a product conforming to the demands and specifications of IATF16949 ("the Specified Product") in this data sheet. Thine accepts no liability whatsoever for any product other than the Specified Product for it not conforming to the aforementioned demands and specifications.

- 5.3 THine accepts liability for demands and specifications of the Specified Product only to the extent that the user and THine have been previously and explicitly agreed to each other.

- 6. Despite our utmost efforts to improve the quality and reliability of the product, faults will occur with a certain small probability, which is inevitable to a semi-conductor product. Therefore, you are encouraged to have sufficiently redundant or error preventive design applied to the use of the product so as not to have our product cause any social or public damage.

- 7. Please note that this product is not designed to be radiation-proof.

- 8. Testing and other quality control techniques are used to this product to the extent THine deems necessary to support warranty for performance of this product. Except where mandated by applicable law or deemed necessary by THine based on the user's request, testing of all functions and performance of the product is not necessarily performed.

- 9. Customers are asked, if required, to judge by themselves if this product falls under the category of strategic goods under the Foreign Exchange and Foreign Trade Act.

- 10. The product or peripheral parts may be damaged by a surge in voltage over the absolute maximum ratings or malfunction, if pins of the product are shorted by such as foreign substance. The damages may cause a smoking and ignition. Therefore, you are encouraged to implement safety measures by adding protection devices, such as fuses.

24/24

### **Contact**

THine@cel.com

Copyright©2019 THine Electronics, Inc.