### **General Description**

The MAX4987AE/MAX4987BE are overvoltage protection devices with built-in ESD protection for USB data lines. These devices feature a low  $100m\Omega$  (typ) RoN internal nFET switch and protect low-voltage systems against voltage faults up to +28V. When the input voltage exceeds the overvoltage threshold or decreases below the undervoltage threshold, the internal nFET switch is turned off to prevent damage to the protected components.

All switches feature a minimum 1.5A current-limit protection. During a short-circuit occurrence, the switch operates in an autoretry mode where the internal nFET switch is turned on to check if the fault has been removed. The autoretry interval is 30ms, and if the fault is removed, the nFET switch remains on.

The MAX4987AE/MAX4987BE feature low-capacitance (3pF) ESD protection for USB data lines that allow transmission of high-speed USB 2.0 signals.

The overvoltage threshold (OVLO) is preset to 6.15V. The undervoltage thresholds (UVLO) are preset to 2.55V (MAX4987AE) or 4.2V (MAX4987BE). When the input voltage drops below the undervoltage (UVLO) threshold, the devices enter a low-current standby mode.

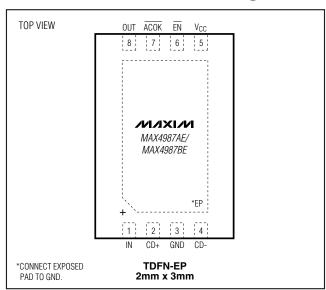

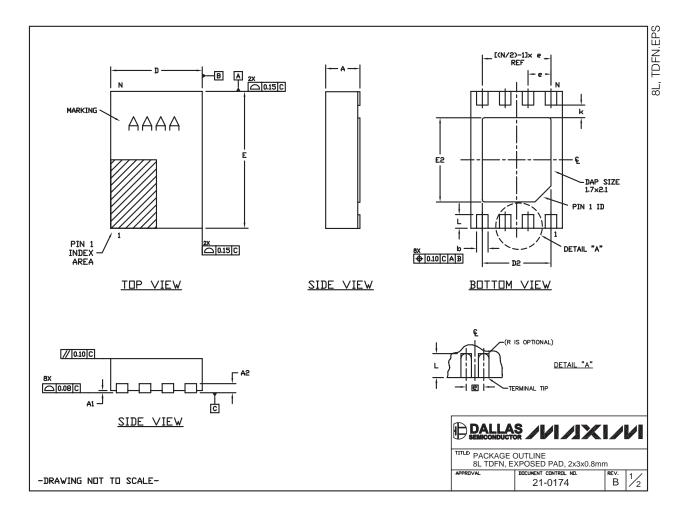

All devices are offered in a small 2mm x 3mm, 8-pin TDFN package and operate over the -40°C to +85°C extended temperature range.

**Applications**

Cell Phones Media Players

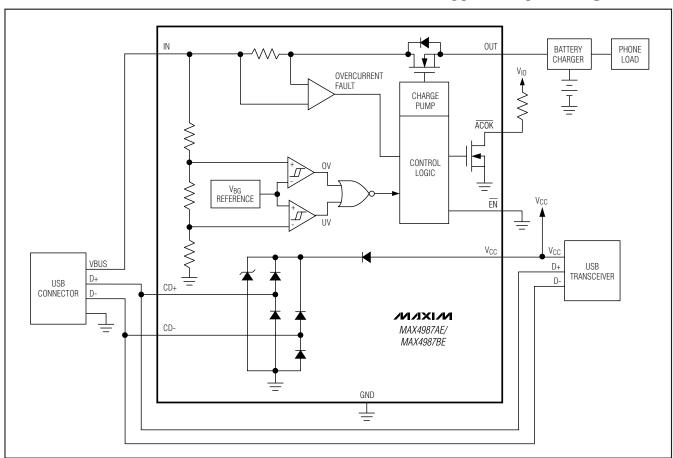

Typical Operating Circuit appears at end of data sheet.

#### **Features**

- ♦ Input Voltage Protection Up to +28V

- ♦ Integrated Low Ron (100mΩ) nFET Switch

- ♦ Internal Overcurrent Protection 1.5A (min)

- **♦** Overcurrent Protection (Autoretry)

- **♦ Enable Input**

- ♦ Internal 30ms Startup Delay

- **♦ Low-Capacitance USB High-Speed Data Line ESD** Protection (3pF)

- ±15kV Human Body Model ±15kV IEC 61000-4-2 Air Gap ±6kV IEC 61000-4-2 Contact

- ♦ Thermal-Shutdown Protection

- ♦ 2mm x 3mm, 8-Pin TDFN Package

### Pin Configuration

## Ordering Information/Selector Guide

| PART                   | PIN-<br>PACKAGE | TOP MARK | PACKAGE<br>CODE | UVLO (V) | OVLO (V) | OVERCURRENT<br>MODE |

|------------------------|-----------------|----------|-----------------|----------|----------|---------------------|

| MAX4987AEETA+          | 8 TDFN-EP**     | AAI      | T823-1          | 2.55     | 6.15     | Autoretry           |

| <b>MAX4987BE</b> ETA+* | 8 TDFN-EP**     | AAJ      | T823-1          | 4.2      | 6.15     | Autoretry           |

**Note:** All devices are specified over the -40°C to +85°C operating temperature range.

Maxim Integrated Products 1

<sup>+</sup>Denotes a lead-free package.

<sup>\*</sup>Future product—contact factory for availability.

<sup>\*\*</sup>EP = Exposed paddle.

#### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages referenced to GND.)              |                              | Package Junctio             |

|------------------------------------------------|------------------------------|-----------------------------|

| ÎN                                             | 0.3V to +30V                 | (θ <sub>JC</sub> ) (Note 1) |

| OUT                                            | 0.3V to $+(IN + 0.3V)$       | Operating Tempe             |

| VCC, EN, ACOK, CD+, CD                         | 0.3V to +6V                  | Junction Temper             |

| Continuous Power Dissipation (T <sub>A</sub> = | +70°C) for multilayer board: | Storage Tempera             |

| 8-Pin TDFN (derate 16.7mW/°C al                | bove +70°C)1333mW            | Lead Temperatur             |

| Package Junction-to-Ambient Therm              |                              |                             |

| (Aux) (Note 1)                                 | 60 0°C/W                     |                             |

| Package Junction-to-Case Thermal Resista | nce           |

|------------------------------------------|---------------|

| (θ <sub>JC</sub> ) (Note 1)              | 10.8°C/W      |

| Operating Temperature Range              | 40°C to +85°C |

| Junction Temperature                     | +150°C        |

| Storage Temperature Range                |               |

| Lead Temperature (soldering)             | +300°C        |

|                                          |               |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a 4-layer board. For detailed information on package thermal considerations, go to <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = +2.2V \text{ to } +28V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{IN} = +5V$  and  $T_A = +25^{\circ}\text{C}.)$

| PARAMETER                          | SYMBOL              | CONDITIONS                                     |                                              | MIN  | TYP  | MAX  | UNIT |

|------------------------------------|---------------------|------------------------------------------------|----------------------------------------------|------|------|------|------|

| ANALOG SWITCH                      |                     |                                                |                                              |      |      |      |      |

| Input-Voltage Range                | VIN                 |                                                |                                              | 2.2  |      | 28   | V    |

| V <sub>CC</sub> Input Voltage      | Vcc                 |                                                |                                              |      |      | 5.5  | V    |

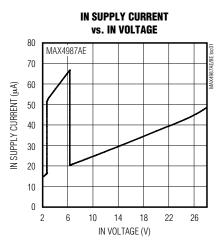

| least Cuanty Course                | 1                   | EN = 0V, V <sub>IN</sub> > V <sub>UVLO</sub>   |                                              |      | 60   | 150  | μΑ   |

| Input Supply Current               | IIN                 | $\overline{EN} = 5V, V_{IN} > V_{U}$           | EN = 5V, V <sub>IN</sub> > V <sub>UVLO</sub> |      | 50   | 100  |      |

| UVLO Supply Current                | luvlo               | VIN < VUVLO                                    |                                              |      |      | 40   | μΑ   |

|                                    |                     | () ( folling)                                  | MAX4987AE                                    | 2.3  |      |      | V    |

| IN I la de muelto de la calcout    | \/                  | (V <sub>IN</sub> falling)                      | MAX4987BE                                    | 3.8  |      |      |      |

| IN Undervoltage Lockout            | Vuvlo               | () (                                           | MAX4987AE                                    | 2.35 | 2.55 | 2.75 |      |

|                                    |                     | (V <sub>IN</sub> rising)                       | MAX4987BE                                    | 3.85 | 4.2  | 4.45 |      |

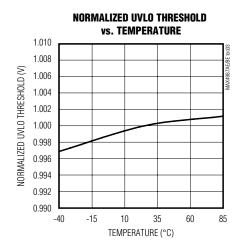

| IN Undervoltage Lockout Hysteresis |                     |                                                |                                              |      | 1    |      | %    |

| O 11 T: 1                          | Vovlo               | (V <sub>IN</sub> rising)                       |                                              | 5.55 | 6.15 | 6.45 | V    |

| Overvoltage Trip Level             |                     | (V <sub>IN</sub> falling)                      |                                              | 5.5  |      |      |      |

| IN Overvoltage Lockout Hysteresis  |                     |                                                |                                              |      | 1    |      | %    |

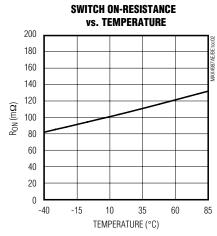

| Switch On-Resistance               | Ron                 | V <sub>IN</sub> = 5V, I <sub>OUT</sub> = 500mA |                                              |      | 100  | 200  | mΩ   |

| Overcurrent Protection Threshold   | I <sub>LIM</sub>    |                                                |                                              | 1.5  |      | 4.2  | А    |

| Maximum Output Capacitance         |                     | $V_{IN} = 5V$ , no overc                       | current shutdown                             |      | 1000 |      | μF   |

| CD+ and CD- Leakage Current        | I <sub>LKG_CD</sub> | $V_{CC} = 5.5V, V_{CD}$                        | = 0V, 3.3V                                   | -300 |      | +300 | nA   |

| CD+ and CD- Capacitance            | Ccd                 | f = 1MHz, V <sub>CD</sub> = 0.5 <sub>P-P</sub> |                                              |      | 3    |      | рF   |

| DIGITAL SIGNALS                    |                     |                                                |                                              |      |      |      |      |

| ACOK Output Low Voltage            | VoL                 | I <sub>SINK</sub> = 1mA                        |                                              |      |      | 0.4  | V    |

| ACOK High-Leakage Current          |                     | VACOK = 5.5V, flag deasserted                  |                                              |      |      | 1    | μΑ   |

| EN Input-Voltage High              | VIH                 |                                                |                                              | 1.4  |      |      | V    |

| EN Input-Voltage Low               | V <sub>I</sub> L    |                                                |                                              |      |      | 0.4  | V    |

| EN Input-Leakage Current           | I <sub>LEAK</sub>   | $V_{EN} = 5.5V$                                |                                              | -1   |      | +1   | μΑ   |

2 \_\_\_\_\_\_\_/W/XI/W

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = +2.2V \text{ to } +28V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{IN} = +5V$  and  $T_A = +25^{\circ}\text{C}.)$

| PARAMETER SYMBOL            |                    | CONDITIONS                                                                                | MIN | TYP | MAX | UNIT |

|-----------------------------|--------------------|-------------------------------------------------------------------------------------------|-----|-----|-----|------|

| TIMING CHARACTERISTICS (Not | te 2)              |                                                                                           | •   |     |     |      |

| Debounce Time               | tINDBC             | Time from V <sub>UVLO</sub> < V <sub>IN</sub> < V <sub>OVLO</sub> to charge-pump enable   | 30  |     |     | ms   |

| ACOK Assertion Time         | tacok              | V <sub>UVLO</sub> < V <sub>IN</sub> < V <sub>OVLO</sub> , to <del>ACOK</del> low          |     | 30  |     | ms   |

| Switch Turn-On Time         | ton                | $V_{UVLO} < V_{IN} < V_{OVLO}$ , $R_{LOAD} = 100\Omega$ , from 10% to 90% of $V_{OUT}$    |     | 3   |     | ms   |

| Switch Turn-Off Time        | toff               | $V_{IN} < V_{UVLO}$ or $V_{IN} > V_{OVLO}$ to internal switch off, $R_{LOAD} = 100\Omega$ | 10  |     | μs  |      |

| Current-Limit Turn-Off Time | t <sub>BLANK</sub> | Overcurrent fault to internal switch off                                                  | 10  |     |     | μs   |

| I Autoretry Time            |                    | From overcurrent fault to internal switch turn-on                                         | 30  |     |     | ms   |

| THERMAL PROTECTION          |                    |                                                                                           |     |     |     |      |

| Thermal Shutdown            | TSHDN              |                                                                                           |     | 150 |     | °C   |

| Thermal-Shutdown Hysteresis |                    |                                                                                           |     | 40  |     | °C   |

| ESD PROTECTION              |                    |                                                                                           |     |     |     |      |

|                             |                    | Human Body Model                                                                          |     | ±15 |     |      |

| CD+ and CD-                 |                    | IEC 61000-4-2 Air Gap                                                                     |     | ±15 |     | kV   |

|                             |                    | IEC 61000-4-2 Contact                                                                     |     | ±6  |     |      |

| All Other Pins              |                    | Human Body Model                                                                          |     | ±2  |     | kV   |

Note 2: All timing is specified using 20% and 80% levels, unless otherwise noted.

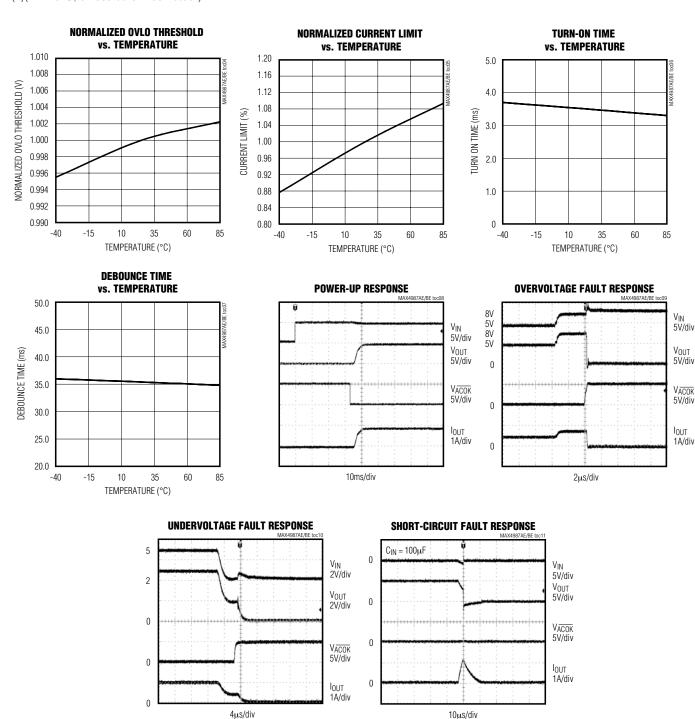

### Typical Operating Characteristics

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

Typical Operating Characteristics (continued)

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

### **Pin Description**

| PIN | NAME | FUNCTION                                                                                                                                                                                                                           |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | IN   | Voltage Input. Bypass IN with a 1µF ceramic capacitor as close to the device as possible to obtain ±15kV HBM ESD protection. No capacitor required to obtain ±2kV HBM ESD protection.                                              |

| 2   | CD+  | USB Data Line                                                                                                                                                                                                                      |

| 3   | GND  | Ground                                                                                                                                                                                                                             |

| 4   | CD-  | USB Data Line                                                                                                                                                                                                                      |

| 5   | Vcc  | Positive Supply-Voltage Input. VCC is required only when USB signals are present.                                                                                                                                                  |

| 6   | ĒN   | Enable Active-Low Input. Drive EN low to enable the switch. Drive EN high to disable the switch.                                                                                                                                   |

| 7   | ACOK | Open-Drain Adapter-Voltage Indicator Output. ACOK is driven low after the V <sub>IN</sub> voltage is stable between UVLO and OVLO for 30ms (typ). Connect a pullup resistor from ACOK to the logic I/O voltage of the host system. |

| 8   | OUT  | Output Voltage. Output of internal switch.                                                                                                                                                                                         |

| EP  | EP   | Exposed Pad. Connect exposed pad to ground. Do not use EP as a sole ground connection.                                                                                                                                             |

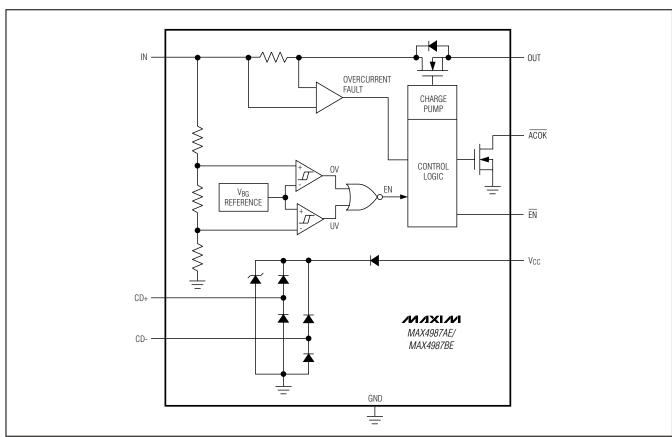

## Functional Diagram

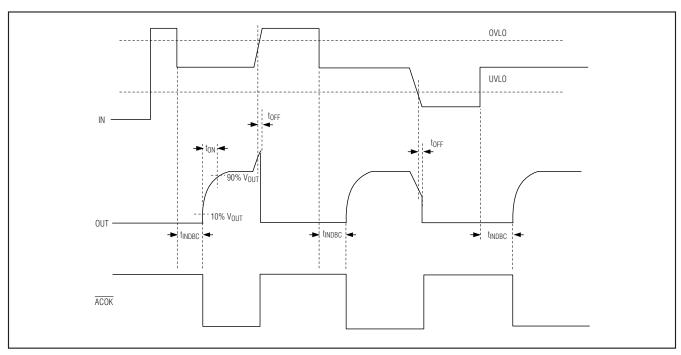

Figure 1. MAX4987AE/MAX4987BE Timing Diagram

### **Detailed Description**

The MAX4987AE/MAX4987BE are overvoltage protection devices with integrated ESD protection for USB data lines. These devices feature a low RON internal FET and protect low-voltage systems against voltage faults up to +28V. If the input voltage exceeds the overvoltage threshold, the internal nFET switch is turned off to prevent damage to the protected components. The 30ms debounce time prevents false turn-on of the internal nFET switch during startup. An open-drain active-low logic output is available to signal that a successful power-up has occurred.

#### **Device Operation**

The MAX4987AE/MAX4987BE have an internal oscillator and charge pump that control the turn-on of the internal nFET switch. The internal oscillator controls the timers that enable the turn-on of the charge pump and controls the state of the open-drain  $\overline{ACOK}$  output. If  $V_{IN} < V_{UVLO}$  or if  $V_{IN} > V_{OVLO}$ , the internal oscillator remains off, thus disabling the charge pump. If  $V_{UVLO} < V_{IN} < V_{OVLO}$ , the internal charge pump is enabled. The charge-pump startup, after a 30ms internal delay, turns on the internal nFET switch and asserts  $\overline{ACOK}$  (see Figure 1). At any time, if  $V_{IN}$  drops below  $V_{UVLO}$  or rises above  $V_{OVLO}$ ,  $\overline{ACOK}$  is pulled high and the charge pump is disabled.

#### Internal nFET Switch

The MAX4987AE/MAX4987BE incorporate an internal nFET switch with a  $100m\Omega$  (typ) on-resistance. The nFET switch is internally driven by a charge pump that generates a voltage above the input voltage. The MAX4987AE/MAX4987BE is equipped with a 1.5A (min) current-limit protection that turns off the nFET switch within 5µs (typ) during an overcurrent fault condition.

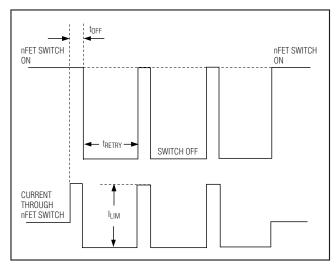

#### **Autoretry**

The MAX4987AE/MAX4987BE have an overcurrent autoretry function that turns on the nFET switch again after a 30ms (typ) retry time (see Figure 2). If the faulty load condition is still present after the blanking time, the switch turns off again and the cycle is repeated. The fast turn-off time and 30ms retry time result in a very low duty cycle in order to keep power consumption low. If the faulty load condition is not present, the switch remains on.

#### **Undervoltage Lockout (UVLO)**

The MAX4987AE has a 2.55V undervoltage-lockout threshold (UVLO), while the MAX4987BE has a 4.15V UVLO threshold. When  $V_{IN}$  is less than  $V_{UVLO}$ ,  $\overline{ACOK}$  is high impedance.

6 \_\_\_\_\_

#### Overvoltage Lockout (OVLO)

The MAX4987AE/MAX4987BE have a 6.15V (typ) overvoltage threshold (OVLO). When V<sub>IN</sub> is greater than V<sub>OVLO</sub>, ACOK is high impedance.

#### ACOK

$\overline{\text{ACOK}}$  is an active-low open-drain output that asserts low when VUVLO < VIN < VOVLO following the 30ms (typ) debounce period. Connect a pullup resistor from ACOK to the logic I/O voltage of the host system. During a short-circuit fault,  $\overline{\text{ACOK}}$  may deassert due to VIN not being in the valid operating voltage range.

#### **Thermal-Shutdown Protection**

The MAX4987AE/MAX4987BE feature thermal-shutdown circuitry. The internal nFET switch turns off when the junction temperature exceeds T<sub>SHDN</sub> and immediately goes into a fault mode. The device exits thermal shutdown after the junction temperature cools by +40°C (typ).

### Applications Information

#### IN Bypass Capacitor

For most applications, bypass IN to GND with a 1 $\mu$ F ceramic capacitor as close to the device as possible to enable  $\pm 15$ kV HBM ESD protection on IN. If  $\pm 15$ kV HBM ESD protection is not required, there is no capacitor required at IN. If the power source has significant inductance due to long lead length, take care to prevent overshoots due to the LC tank circuit and provide protection if necessary to prevent exceeding the absolute maximum rating on IN.

#### **ESD Test Conditions**

ESD performance depends on a number of conditions. The MAX4987AE/MAX4987BE are specified for  $\pm 15 \text{kV}$  HBM ESD protection on the CD+, CD-, and IN pins when IN is bypassed to ground with a 1µF ceramic capacitor. The CD+ and CD- inputs are also protected against  $\pm 15 \text{kV}$  Air Gap and  $\pm 6 \text{kV}$  contact IEC 61000-4-2 ESD events.

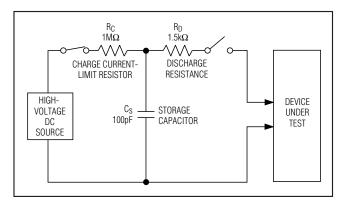

#### **Human Body Model**

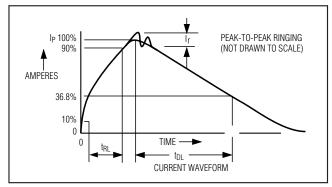

Figure 3 shows the Human Body Model, and Figure 4 shows the current waveform it generates when discharged into a low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest, that is then discharged into the device through a  $1.5 k\Omega$  resistor.

#### IEC 61000-4-2

The IEC 61000-4-2 standard covers ESD testing and performance of finished equipment. It does not specifically refer to integrated circuits. The MAX4987AE/ MAX4987BE

Figure 2. Autoretry Timing Diagram

Figure 3. Human Body ESD Test Model

Figure 4. Human Body Current Waveform

are specified for  $\pm 15 \text{kV}$  Air-Gap Discharge and  $\pm 6 \text{kV}$  Contact Discharge IEC 61000-4-2 on the CD+ and CD-pins.

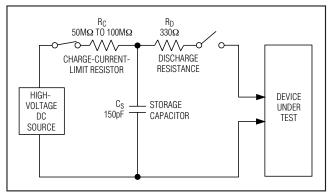

The major difference between tests done using the Human Body Model and IEC 61000-4-2 is a higher peak current in IEC 61000-4-2, due to lower series resistance. Hence, the ESD withstand voltage measured to IEC 61000-4-2 generally is lower than that measured using the Human Body Model. Figure 5 shows the IEC 61000-4-2 model. The Contact Discharge method connects the probe to the device before the probe is charged. The Air-Gap Discharge test involves approaching the device with a charged probe.

Figure 5. IEC 61000-4-2 ESD Test Model

### **Typical Operating Circuit**

\_Chip Information

PROCESS: BICMOS

### \_Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

#### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to www.maxim-ic.com/packages.)

|        | DIMENCIONO     |      |      |  |  |  |

|--------|----------------|------|------|--|--|--|

|        | DIMENSIONS     |      |      |  |  |  |

| SYMBOL | MIN.           | NOM. | MAX. |  |  |  |

| А      | 0.70           | 0.75 | 0.80 |  |  |  |

| Е      | 2.95           | 3.00 | 3.05 |  |  |  |

| D      | 1.95           | 2.00 | 2.05 |  |  |  |

| A1     | 0.00           | 0.02 | 0.05 |  |  |  |

| L      | 0.30           | 0.40 | 0.50 |  |  |  |

| k      | 0.20 MIN.      |      |      |  |  |  |

| A2     | 0.20 REF.      |      |      |  |  |  |

| N      | 8              |      |      |  |  |  |

| е      | 0.50 BSC       |      |      |  |  |  |

| b      | 0.18 0.25 0.30 |      |      |  |  |  |

|        | EXPOSED PAD PACKAGE        |      |      |      |      |      |  |

|--------|----------------------------|------|------|------|------|------|--|

| PKG.   |                            | E2   |      | D2   |      |      |  |

| CODE   | MIN. NOM. MAX. MIN. NOM. N |      |      |      |      | MAX. |  |

| T823-1 | 1.60                       | 1.75 | 1.90 | 1.50 | 1.63 | 1.75 |  |

- NOTES:

1. ALL DIMENSIONS ARE IN mm. ANGLES IN DEGREES.

2. COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

COPLANARITY SHALL NOT EXCEED 0.08mm.

3. WARPAGE SHALL NOT EXCEED 0.10mm.

4. PACKAGE LENGTH/PACKAGE WIDTH ARE CONSIDERED AS SPECIAL CHARACTERISTIC(S).

5. COMPLY TO JEDEC MO229, TYPE 1, VERSION WCED—2.

6. "N" IS THE TOTAL NUMBER OF LEADS.

7. NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY.

8. MARKING IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

9. MATERIAL MIST COMPLY WITH BANNED AND RESTRICTED SUBSTANCES SPEC #10—013

- 9. MATERIAL MUST COMPLY WITH BANNED AND RESTRICTED SUBSTANCES SPEC #10-0131.

DALLAS /// IX/// PACKAGE OUTLINE 8L TDFN, EXPOSED PAD, 2x3x0.8mm

21-0174

-DRAWING NOT TO SCALE-

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2007 Maxim Integrated Products

is a registered trademark of Maxim Integrated Products, Inc.