# Dual-Synchronous, Step-Down Controller with Out-of-Audio™ Operation and 100-mA LDOs for Notebook System Power

Check for Samples: TPS51125A

#### **FEATURES**

- Wide Input Voltage Range: 5.5 V to 28 V

- Output Voltage Range: 2 V to 5.5 V

- Built-in 100-mA 5-V/3.3-V LDO with Switches

- **Built-in 1% 2-V Reference Output**

- With/Without Out-of-Audio™ Mode Selectable **Light Load and PWM only Operation**

- Internal 1.6-ms Voltage Servo Softstart

- Adaptive On-Time Control Architecture with Four Selectable Frequency Setting

- 4500 ppm/°C R<sub>DS(on)</sub> Current Sensing

- **Built-In Output Discharge**

- **Power Good Output**

- **Built-in OVP/UVP/OCP**

- Thermal Shutdown (Non-latch)

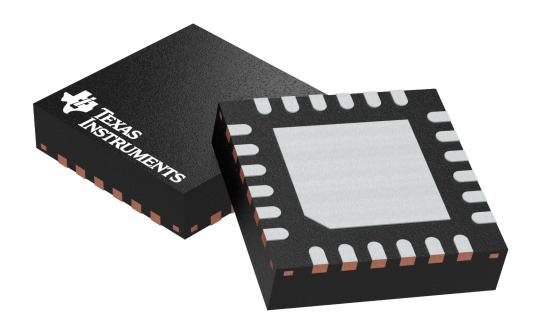

- QFN24 (RGE)

#### APPLICATIONS

- **Notebook Computers**

- I/O Supplies

- **System Power Supplies**

#### DESCRIPTION

The TPS51125A is a cost effective, dual-synchronous buck controller targeted for notebook system power supply solutions. It provides 5-V and 3.3-V LDOs and requires few external components. The 270-kHz VCLK output can be used to drive an external charge pump, generating gate drive voltage for the load switches without reducing the main converter's efficiency. The TPS51125A supports high efficiency, fast transient response and provides a combined power-good signal. Out-of-Audio™ mode light-load operation enables low acoustic noise at much higher efficiency than conventional forced PWM operation.  $D\text{-}CAP^{\mathsf{TM}}$ Adaptive on-time control convenient and efficient operation. The part operates with supply input voltages ranging from 5.5 V to 28 V and supports output voltages from 2 V to 5.5 V. The TPS51125A is available in a 24-pin QFN package and is specified from -40°C to 85°C ambient temperature range.

Table 1. Differences between the TPS51125 and TPS51125A

|                                    | TPS51125                                             | TPS51125A                                                        |

|------------------------------------|------------------------------------------------------|------------------------------------------------------------------|

|                                    | VREG5: at least 33 μF                                | VREG5: 10 μF or larger (X5R or X7R)                              |

| LDO Output Capacitance Requirement | VREG3: at most 10 μF<br>(1 μF acceptable at no load) | VREG3: 10 μF or larger (X5R or X7R) (1 μF acceptable at no load) |

|                                    | VREF: 0.22 μF to 1 μF                                | VREF: 0.22 μF to 1 μF (X5R or X7R)                               |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. Out-of-Audio, D-CAP are trademarks of Texas Instruments.

# ORDERING INFORMATION(1)(2)

| T <sub>A</sub> | PACKAGE                                    | DEVICE NUMBER | PINS | OUTPUT SUPPLY            | MINIMUM<br>QUANTITY | ECO PLAN           |

|----------------|--------------------------------------------|---------------|------|--------------------------|---------------------|--------------------|

| 40°C to 95°C   | -40°C to 85°C Plastic Quad Flat Pack (QFN) |               | 0.4  | Tape and reel (small)    | 250                 | Green (RoHS and no |

| -40-0 to 85-0  |                                            |               | 24   | Tape and reel<br>(large) | 3000                | Sb/Br)             |

- (1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or visit the TI website at www.ti.com.

- (2) Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package

# ABSOLUTE MAXIMUM RATINGS(1)

over operating free-air temperature range (unless otherwise noted)

| DADAMETED               |                                                              | VALUE |     | LINIT |

|-------------------------|--------------------------------------------------------------|-------|-----|-------|

|                         | PARAMETER                                                    |       |     | UNIT  |

|                         | VBST1, VBST2                                                 | -0.3  | 36  |       |

|                         | VIN                                                          | -0.3  | 30  |       |

| Industrialization (1)   | LL1, LL2                                                     | -2.0  | 30  |       |

| Input voltage range (1) | LL1, LL2, pulse width < 20 ns                                | -5.0  | 30  |       |

|                         | VBST1, VBST2 (2)                                             | -0.3  | 6   | V     |

|                         | EN0, ENTRIP1, ENTRIP2, VFB1, VFB2, VO1, VO2, TONSEL, SKIPSEL | -0.3  | 6   |       |

|                         | DRVH1, DRVH2                                                 | -1.0  | 36  |       |

| Output voltage range    | DRVH1, DRVH2 (2)                                             | -0.3  | 6   |       |

|                         | PGOOD, VCLK, VREG3, VREG5, VREF, DRVL1, DRVL2                | -0.3  | 6   |       |

| Electrostatic discharge | Human body model (HBM) QSS 009-105 (JESD22-A114A)            |       | 2   | 137   |

|                         | Charged device model (CDM) QSS 009-147 (JESD22-C101B.01)     |       | 1.5 | kV    |

| TJ                      | Junction temperature range                                   | -40   | 125 | °C    |

| T <sub>stg</sub>        | Storage temperature                                          | -55   | 150 | 0     |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **DISSIPATION RATINGS**

2-oz. trace and copper pad with solder.

| PACKAGE                   | T <sub>A</sub> < 25°C POWER RATING | DERATING FACTOR ABOVE T <sub>A</sub><br>= 25°C | T <sub>A</sub> = 85°C POWER RATING |

|---------------------------|------------------------------------|------------------------------------------------|------------------------------------|

| 24 pin RGE <sup>(1)</sup> | 1.85 W                             | 18.5 mW/°C                                     | 0.74 W                             |

(1) Enhanced thermal conductance by 3x3 thermal vias beneath thermal pad.

Submit Documentation Feedback

Downloaded from Arrow.com.

<sup>(2)</sup> Voltage values are with respect to the corresponding LLx terminal.

# RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

| -                    | PARAMETER                                                    |      |     |    |

|----------------------|--------------------------------------------------------------|------|-----|----|

| Supply voltage       | VIN                                                          | 5.5  | 28  |    |

|                      | VBST1, VBST2                                                 | -0.1 | 34  |    |

| Input voltage range  | VBST1, VBST2 (wrt LLx)                                       | -0.1 | 5.5 |    |

| input voltage range  | EN0, ENTRIP1, ENTRIP2, VFB1, VFB2, VO1, VO2, TONSEL, SKIPSEL | -0.1 | 5.5 |    |

|                      | DRVH1, DRVH2                                                 | -0.8 | 34  | V  |

|                      | DRVH1, DRVH2 (wrt LLx)                                       | -0.1 | 5.5 |    |

| Output voltage range | LL1, LL2                                                     | -1.8 | 28  |    |

|                      | VREF, VREG3, VREG5                                           | -0.1 | 5.5 |    |

|                      | PGOOD, VCLK, DRVL1, DRVL2                                    | -0.1 | 5.5 |    |

| T <sub>A</sub>       | Operating free-air temperature                               | -40  | 85  | °C |

Copyright © 2009–2012, Texas Instruments Incorporated

# **ELECTRICAL CHARACTERISTICS**

over operating free-air temperature range, VIN = 12 V (unless otherwise noted)

|                      | PARAMETER                  | CONDITIONS                                                                                                        | MIN   | TYP   | MAX  | UNIT |  |

|----------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------|-------|-------|------|------|--|

| SUPPLY CL            | IRRENT                     |                                                                                                                   |       |       |      |      |  |

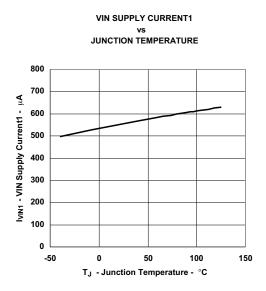

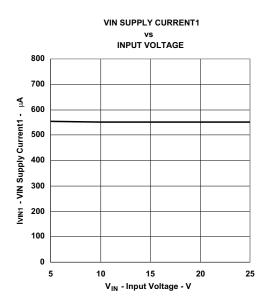

| I <sub>VIN1</sub>    | VIN supply current1        | VIN current, T $_{\rm A}$ = 25°C, no load, VO1 = 0 V, VO2 = 0 V, EN0=open, ENTRIPx = 5 V, VFB1 = VFB2 = 2.05 V    |       | 0.55  | 1    | mA   |  |

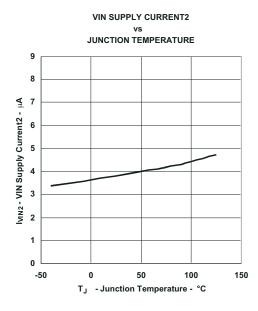

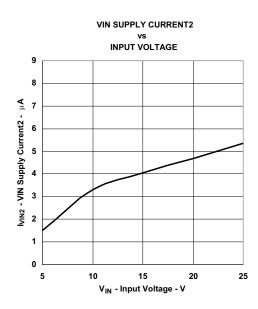

| I <sub>VIN2</sub>    | VIN supply current2        | VIN current, $T_A = 25^{\circ}C$ , no load, VO1 = 5 V, VO2 = 3.3 V, EN0=open, ENTRIPx = 5 V, VFB1 = VFB2 = 2.05 V |       | 4     | 6.5  | μΑ   |  |

| I <sub>VO1</sub>     | VO1 current                | VO1 current, $T_A$ = 25°C, no load, VO1 = 5 V, VO2 = 3.3 V, EN0=open, ENTRIPx = 5 V, VFB1 = VFB2 = 2.05 V         |       | 0.8   | 1.5  | mA   |  |

| I <sub>VO2</sub>     | VO2 current                | VO2 current, $T_A$ = 25°C, no load, VO1 = 5 V, VO2 = 3.3 V, EN0=open, ENTRIPx = 5 V, VFB1 = VFB2 = 2.05 V         |       | 12    | 100  |      |  |

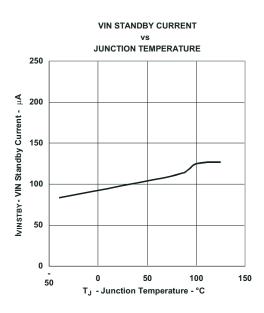

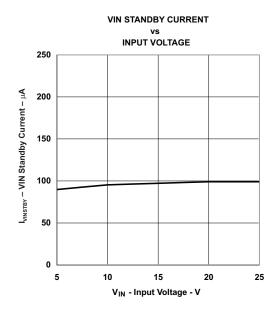

| I <sub>VINSTBY</sub> | VIN standby current        | VIN current, T <sub>A</sub> = 25°C, no load,<br>EN0 = 1.2 V, ENTRIPx = 0 V                                        |       | 95    | 150  | μΑ   |  |

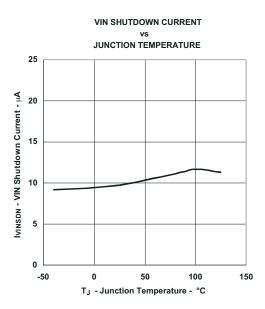

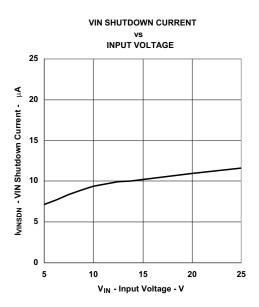

| I <sub>VINSDN</sub>  | VIN shutdown current       | VIN current, T <sub>A</sub> = 25°C, no load,<br>EN0 = ENTRIPx = 0 V                                               |       | 10    | 25   |      |  |

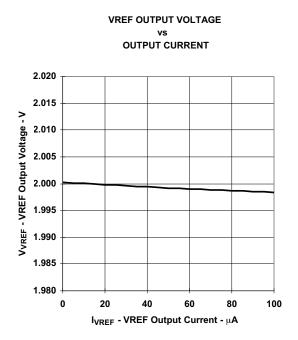

| VREF OUTF            | TUT                        |                                                                                                                   |       |       |      |      |  |

|                      | VREE output voltage        | I <sub>VREF</sub> = 0 A                                                                                           | 1.98  | 2.00  | 2.02 | V    |  |

| $V_{VREF}$           | VREF output voltage        | -5 μA < I <sub>VREF</sub> < 100 μA                                                                                | 1.97  | 2.00  | 2.03 | V    |  |

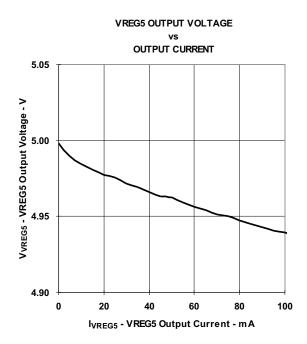

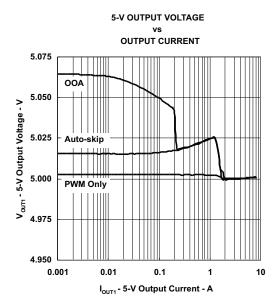

| VREG5 OUT            | <b>TPUT</b>                |                                                                                                                   |       |       |      |      |  |

|                      |                            | VO1 = 0 V, I <sub>VREG5</sub> < 100 mA, T <sub>A</sub> = 25°C                                                     | 4.8   | 5     | 5.2  |      |  |

| $V_{VREG5}$          | VREG5 output voltage       | VO1 = 0 V, I <sub>VREG5</sub> < 100 mA, 6.5 V < VIN < 28 V                                                        | 4.75  | 5     | 5.25 | V    |  |

|                      |                            | VO1 = 0 V, I <sub>VREG5</sub> < 50 mA, 5.5 V < VIN < 28 V                                                         | 4. 75 | 5     | 5.25 |      |  |

| I <sub>VREG5</sub>   | VREG5 output current       | VO1 = 0 V, VREG5 = 4.5 V                                                                                          | 100   | 175   | 250  | mA   |  |

| V                    | Conitals arrangeheald      | Turns on                                                                                                          | 4.55  | 4.7   | 4.85 |      |  |

| V <sub>TH5VSW</sub>  | Switch over threshold      | Hysteresis                                                                                                        | 0.15  | 0.25  | 0.3  | V    |  |

| R <sub>5VSW</sub>    | 5 V SW R <sub>ON</sub>     | VO1 = 5 V, I <sub>VREG5</sub> = 100 mA                                                                            |       | 1     | 3    | Ω    |  |

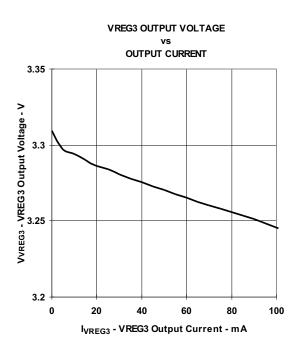

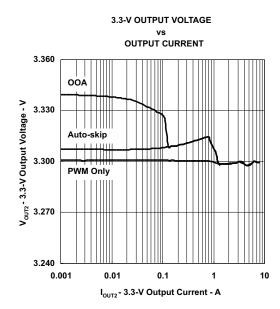

| VREG3 OUT            | <b>TPUT</b>                |                                                                                                                   |       |       |      |      |  |

|                      |                            | VO2 = 0 V, I <sub>VREG3</sub> < 100 mA, T <sub>A</sub> = 25°C                                                     | 3.2   | 3.33  | 3.46 |      |  |

| $V_{VREG3}$          | VREG3 output voltage       | VO2 = 0 V, I <sub>VREG3</sub> < 100 mA, 6.5 V < VIN < 28 V                                                        | 3.13  | 3.33  | 3.5  | V    |  |

|                      |                            | VO2 = 0 V, I <sub>VREG3</sub> < 50 mA, 5.5 V < VIN < 28 V                                                         | 3.13  | 3.33  | 3.5  |      |  |

| I <sub>VREG3</sub>   | VREG3 output current       | VO2 = 0 V, VREG3 = 3 V                                                                                            | 100   | 175   | 250  | mA   |  |

| .,                   | 0 % 1                      | Turns on                                                                                                          | 3.05  | 3.15  | 3.25 |      |  |

| $V_{TH3VSW}$         | Switch over threshold      | Hysteresis                                                                                                        | 0.1   | 0.2   | 0.25 | V    |  |

| R <sub>3VSW</sub>    | 3 V SW R <sub>ON</sub>     | VO2 = 3.3 V, I <sub>VREG3</sub> = 100 mA                                                                          |       | 1.5   | 4    | Ω    |  |

|                      | REFERENCE VOLTAGE          | <del>,</del>                                                                                                      |       |       |      |      |  |

| V <sub>IREF</sub>    | Internal reference voltage | I <sub>VREF</sub> = 0 A, beginning of ON state                                                                    | 1.95  | 1.98  | 2.01 |      |  |

|                      | <u> </u>                   | FB voltage, I <sub>VREF</sub> = 0 A, skip mode                                                                    | 1.98  | 2.01  | 2.04 |      |  |

| $V_{VFB}$            | VFB regulation voltage     | FB voltage, I <sub>VREF</sub> = 0 A, OOA mode <sup>(1)</sup>                                                      | 2.00  | 2.035 | 2.07 | V    |  |

| · VFD                |                            | FB voltage, I <sub>VREF</sub> = 0 A, continuous conduction <sup>(1)</sup>                                         |       | 2.00  |      |      |  |

| I <sub>VFB</sub>     | VFB input current          | VFBx = 2.0 V, T <sub>A</sub> = 25°C                                                                               | -20   |       | 20   | nA   |  |

|                      |                            | 1 11                                                                                                              |       |       |      |      |  |

<sup>(1)</sup> Ensured by design. Not production tested.

Submit Documentation Feedback

over operating free-air temperature range, VIN = 12 V (unless otherwise noted)

|                       | PARAMETER              | CONDITIONS                                                    | MIN         | TYP  | MAX         | UNIT |  |

|-----------------------|------------------------|---------------------------------------------------------------|-------------|------|-------------|------|--|

| V <sub>OUT</sub> DISC | HARGE                  |                                                               |             |      |             |      |  |

| I <sub>Dischg</sub>   | VOUT discharge current | ENTRIPx = 0 V, VOx = 0.5 V                                    | 10          | 60   |             | mA   |  |

| OUTPUT D              | PRIVERS                |                                                               |             |      |             |      |  |

| Б                     | DD\/II manintanan      | Source, V <sub>BSTx - DRVHx</sub> = 100 mV                    |             | 4    | 8           |      |  |

| $R_{DRVH}$            | DRVH resistance        | Sink, V <sub>DRVHx - LLx</sub> = 100 mV                       |             | 1.5  | 4           | 0    |  |

| Б                     | DDVI manintanan        | Source, V <sub>VREG5 - DRVLx</sub> = 100 mV                   |             | 4    | 8           | Ω    |  |

| $R_{DRVL}$            | DRVL resistance        | Sink, V <sub>DRVLx</sub> = 100 mV                             |             | 1.5  | 4           |      |  |

|                       | Deads                  | DRVHx-off to DRVLx-on                                         |             | 10   |             |      |  |

| $t_D$                 | Dead time              | DRVLx-off to DRVHx-on                                         |             | 30   |             | ns   |  |

| CLOCK O               | JTPUT                  | •                                                             |             |      |             |      |  |

| V <sub>CLKH</sub>     | High level voltage     | I <sub>VCLK</sub> = -10 mA, VO1 = 5 V, T <sub>A</sub> = 25 °C | 4.84        | 4.92 |             |      |  |

| V <sub>CLKL</sub>     | Low level voltage      | I <sub>VCLK</sub> = 10 mA, VO1 = 5 V, T <sub>A</sub> = 25 °C  |             | 0.06 | 0.12        | V    |  |

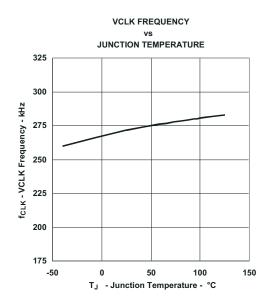

| f <sub>CLK</sub>      | Clock frequency        | T <sub>A</sub> = 25 °C                                        | 175         | 270  | 325         | kHz  |  |

| INTERNAL              | . BST DIODE            | •                                                             |             |      |             |      |  |

| V <sub>FBST</sub>     | Forward voltage        | $V_{VREG5-VBSTx}$ , $I_F = 10$ mA, $T_A = 25$ °C              | 0.7         | 0.8  | 0.9         | V    |  |

| I <sub>VBSTLK</sub>   | VBST leakage current   | VBSTx = 34 V, LLx = 28 V, T <sub>A</sub> = 25 °C              |             | 0.1  | 1           | μA   |  |

| DUTY AND              | FREQUENCY CONTROL      |                                                               |             |      | *           |      |  |

| t <sub>ON11</sub>     | CH1 on time 1          | V <sub>IN</sub> = 12 V, VO1 = 5 V, 200 kHz setting            |             | 2080 |             |      |  |

| t <sub>ON12</sub>     | CH1 on time 2          | V <sub>IN</sub> = 12 V, VO1 = 5 V, 245 kHz setting            |             | 1700 |             |      |  |

| t <sub>ON13</sub>     | CH1 on time 3          | V <sub>IN</sub> = 12 V, VO1 = 5 V, 300 kHz setting            |             | 1390 |             |      |  |

| t <sub>ON14</sub>     | CH1 on time 4          | V <sub>IN</sub> = 12 V, VO1 = 5 V, 365 kHz setting            |             | 1140 |             |      |  |

| t <sub>ON21</sub>     | CH2 on time 1          | V <sub>IN</sub> = 12 V, VO2 = 3.3 V, 250 kHz setting          |             | 1100 |             |      |  |

| t <sub>ON22</sub>     | CH2 on time 2          | V <sub>IN</sub> = 12 V, VO2 = 3.3 V, 305 kHz setting          |             | 900  |             | ns   |  |

| t <sub>ON23</sub>     | CH2 on time 3          | V <sub>IN</sub> = 12 V, VO2 = 3.3 V, 375 kHz setting          |             | 730  |             |      |  |

| t <sub>ON24</sub>     | CH2 on time 4          | V <sub>IN</sub> = 12 V, VO2 = 3.3 V, 460 kHz setting          |             | 600  |             |      |  |

| t <sub>ON(min)</sub>  | Minimum on time        | T <sub>A</sub> = 25 °C                                        |             | 80   |             |      |  |

| t <sub>OFF(min)</sub> | Minimum off time       | T <sub>A</sub> = 25 °C                                        |             | 300  |             |      |  |

| SOFT-STA              | RT                     | •                                                             |             |      |             |      |  |

| t <sub>SS</sub>       | Internal SS time       | Internal soft start                                           | 1.1         | 1.6  | 2.1         | ms   |  |

| POWERGO               | OOD                    | •                                                             |             |      |             |      |  |

|                       |                        | PG in from lower                                              | 92.50%      | 95%  | 97.50%      |      |  |

| $V_{THPG}$            | PG threshold           | PG in from higher                                             | 102.50<br>% | 105% | 107.50<br>% |      |  |

|                       |                        | PG hysteresis                                                 | 2.50%       | 5%   | 7.50%       |      |  |

| I <sub>PGMAX</sub>    | PG sink current        | PGOOD = 0.5 V                                                 | 5           | 12   |             | mA   |  |

| t <sub>PGDEL</sub>    | PG delay               | Delay for PG in                                               | 350         | 510  | 670         | μs   |  |

Copyright © 2009–2012, Texas Instruments Incorporated

over operating free-air temperature range, VIN = 12 V (unless otherwise noted)

|                       | PARAMETER                                                         | CONDITIONS                                                                                                 | MIN   | TYP   | MAX  | UNIT     |  |

|-----------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------|-------|------|----------|--|

| LOGIC THR             | ESHOLD AND SETTING CONDIT                                         | TIONS                                                                                                      |       |       |      |          |  |

|                       |                                                                   | Shutdown                                                                                                   |       |       | 0.4  |          |  |

| $V_{EN0}$             | EN0 setting voltage                                               | Enable, VCLK = off                                                                                         | 0.8   |       | 1.6  | V        |  |

|                       |                                                                   | Enable, VCLK = on                                                                                          | 2.4   |       |      |          |  |

|                       |                                                                   | V <sub>EN0</sub> = 0.2 V                                                                                   | 2     | 3.5   | 5    | _        |  |

| I <sub>EN0</sub>      | EN0 current                                                       | V <sub>EN0</sub> = 1.5 V                                                                                   | 1     | 1.75  | 2.5  | μA       |  |

| .,                    | ENTRIP1, ENTRIP2                                                  | Shutdown                                                                                                   | 350   | 400   | 450  | .,       |  |

| $V_{EN}$              | threshold                                                         | Hysteresis                                                                                                 | 10    | 30    | 60   | mV       |  |

|                       |                                                                   | 200 kHz/250 kHz                                                                                            |       |       | 1.5  |          |  |

|                       |                                                                   | 245 kHz/305 kHz                                                                                            | 1.9   |       | 2.1  |          |  |

| V <sub>TONSEL</sub>   | TONSEL setting voltage                                            | 300 kHz/375 kHz                                                                                            | 2.7   |       | 3.6  |          |  |

|                       |                                                                   | 365 kHz/460 kHz                                                                                            | 4.7   |       |      | V        |  |

|                       |                                                                   | PWM only                                                                                                   |       |       | 1.5  |          |  |

| V <sub>SKIPSEL</sub>  | SKIPSEL setting voltage                                           | Auto skip                                                                                                  | 1.9   |       | 2.1  |          |  |

| Ortif OLL             | 0 0                                                               | OOA auto skip                                                                                              | 2.7   |       |      |          |  |

| PROTECTIO             | ON: CURRENT SENSE                                                 | ·                                                                                                          |       |       |      |          |  |

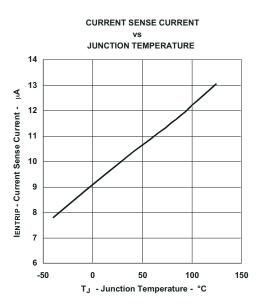

| I <sub>ENTRIP</sub>   | ENTRIPx source current                                            | V <sub>ENTRIPx</sub> = 920 mV, T <sub>A</sub> = 25°C                                                       | 9.4   | 10    | 10.6 | μA       |  |

| TC <sub>IENTRIP</sub> | ENTRIPx current temperature coefficient                           | On the basis of 25°C <sup>(2)</sup>                                                                        |       | 4500  |      | ppm/°C   |  |

| V <sub>OCLoff</sub>   | OCP comparator offset                                             | ((V <sub>ENTRIPx-GND</sub> /9)-24 mV -V <sub>GND-LLx</sub> ) voltage,<br>V <sub>ENTRIPx-GND</sub> = 920 mV | -8    | 0     | 8    |          |  |

| V <sub>OCL(max)</sub> | Maximum OCL setting                                               | V <sub>ENTRIPx</sub> = 5 V                                                                                 | 185   | 205   | 225  | mV       |  |

| V <sub>ZC</sub>       | Zero cross detection comparator offset                            | V <sub>GND-LLx</sub> voltage                                                                               | -5    | 0     | 5    |          |  |

| V <sub>ENTRIP</sub>   | Current limit threshold                                           | V <sub>ENTRIPx-GND</sub> voltage, <sup>(2)</sup>                                                           | 0.515 |       | 2    | V        |  |

| PROTECTIO             | N: UVP AND OVP                                                    |                                                                                                            |       |       |      |          |  |

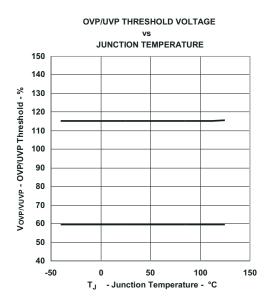

| V <sub>OVP</sub>      | OVP trip threshold                                                | OVP detect                                                                                                 | 110%  | 115%  | 120% |          |  |

| T <sub>OVPDEL</sub>   | OVP prop delay                                                    |                                                                                                            |       | 2     |      | μs       |  |

|                       | 0                                                                 | UVP detect                                                                                                 | 55%   | 60%   | 65%  |          |  |

| $V_{UVP}$             | Output UVP trip threshold                                         | Hysteresis                                                                                                 |       | 10%   |      |          |  |

| t <sub>UVPDEL</sub>   | Output UVP prop delay                                             |                                                                                                            | 20    | 32    | 40   | μs       |  |

| t <sub>UVPEN</sub>    | Output UVP enable delay                                           |                                                                                                            | 1.4   | 2     | 2.6  | ms       |  |

| UVLO                  |                                                                   | ,                                                                                                          |       |       |      |          |  |

|                       | \(\(\text{D} = 0 = 1 \) \(\text{I} \) \(\text{O} \) \(\text{I} \) | Wake up                                                                                                    | 4.1   | 4.2   | 4.3  |          |  |

| $V_{UVVREG5}$         | VREG5 UVLO threshold                                              | Hysteresis                                                                                                 | 0.38  | 0.43  | 0.48 | V        |  |

| V <sub>UVVREG3</sub>  | VREG3 UVLO threshold                                              | Shutdown (2)                                                                                               |       | VO2-1 |      |          |  |

|                       | SHUTDOWN                                                          | ı                                                                                                          |       |       |      |          |  |

|                       |                                                                   | Shutdown temperature (2)                                                                                   |       | 150   |      | _        |  |

| T <sub>SDN</sub>      | Thermal shutdown threshold                                        | Hysteresis (2)                                                                                             |       | 10    |      | °C       |  |

|                       |                                                                   | ,                                                                                                          |       |       |      | <u> </u> |  |

<sup>(2)</sup> Ensured by design. Not production tested.

Submit Documentation Feedback

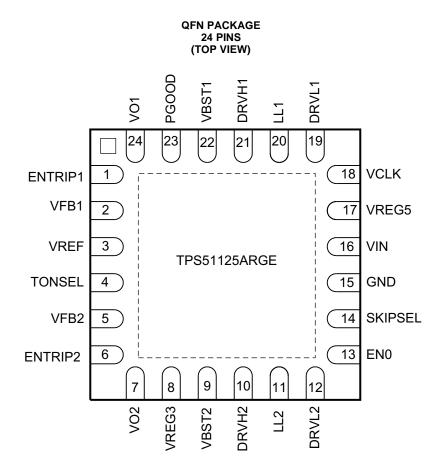

# **DEVICE INFORMATION**

# **Table 2. TERMINAL FUNCTIONS TABLE**

| TERM    | TERMINAL |     | DECORPTION                                                                                                                                                                          |  |  |

|---------|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME    | NO.      | I/O | DESCRIPTION                                                                                                                                                                         |  |  |

| VIN     | 16       | I   | High voltage power supply input for 5-V/3.3-V LDO.                                                                                                                                  |  |  |

| GND     | 15       | -   | Ground.                                                                                                                                                                             |  |  |

| VREG3   | 8        | 0   | 3.3-V power supply output. Connect 10-µF or larger, high-quality X5R or X7R ceramic capacitor to Power GND near the device. A 1-µF ceramic capacitor is acceptable when not loaded. |  |  |

| VREG5   | 17       | 0   | 5-V power supply output. Connect 10-µF or larger, high-quality X5R or X7R ceramic capacitor to Power GND near the device.                                                           |  |  |

| VREF    | 3        | 0   | $2\text{-V}$ reference voltage output. Connect 220-nF to $1\text{-}\mu\text{F}$ , high-quality X5R or X7R ceramic capacitor to Signal GND near the device.                          |  |  |

|         |          |     | Master enable input.                                                                                                                                                                |  |  |

|         |          |     | Open: LDOs on, and ready to turn on VCLK and switcher channels.                                                                                                                     |  |  |

| EN0     | 13       | I/O | $620 \text{ k}\Omega$ to GND : enable both LDOs, VCLK off and ready to turn on switcher channels. Power consumption is almost the same as the case of VCLK = ON.                    |  |  |

|         |          |     | GND : disable all circuit                                                                                                                                                           |  |  |

| ENTRIP1 | 1        | 1/0 | Channel 1 and Channel 2 enable and OCL trip setting pins.Connect resistor from this pin to GND to                                                                                   |  |  |

| ENTRIP2 | 6        | 1/0 | set threshold for synchronous R <sub>DS(on)</sub> sense. Short to ground to shutdown a switcher channel.                                                                            |  |  |

| VO1     | 24       | I/O | Output connection to SMPS. These terminals work as fixed voltage inputs and output discharge                                                                                        |  |  |

| VO2     | 7        | 1/0 | inputs. VO1 and VO2 also work as 5 V and 3.3 V switch over return power input respectively.                                                                                         |  |  |

| VFB1    | 2        | _   | SMPS feedback inputs. Connect with feedback resistor divider.                                                                                                                       |  |  |

| VFB2    | 5        |     |                                                                                                                                                                                     |  |  |

| PGOOD   | 23       | 0   | Power Good window comparator output for channel 1 and 2. (Logical AND)                                                                                                              |  |  |

|         |          |     | Selection pin for operation mode:                                                                                                                                                   |  |  |

| CKIDOEI | 4.4      |     | OOA auto skip : Connect to VREG3 or VREG5                                                                                                                                           |  |  |

| SKIPSEL | 14       | l   | Auto skip : Connect to VREF                                                                                                                                                         |  |  |

|         |          |     | PWM only: Connect to GND                                                                                                                                                            |  |  |

|         |          |     | On-time adjustment pin.                                                                                                                                                             |  |  |

|         |          |     | 365 kHz/460 kHz setting : connect to VREG5                                                                                                                                          |  |  |

| TONSEL  | 4        | ı   | 300 kHz/375 kHz setting : connect to VREG3                                                                                                                                          |  |  |

|         |          |     | 245 kHz/305 kHz setting : connect to VREF                                                                                                                                           |  |  |

|         |          |     | 200 kHz/250 kHz setting : connect to GND                                                                                                                                            |  |  |

| DRVL1   | 19       | _   | Low-side N-channel MOSFET driver outputs. GND referenced drivers.                                                                                                                   |  |  |

| DRVL2   | 12       | 0   |                                                                                                                                                                                     |  |  |

| VBST1   | 22       | 1 . | Supply input for high-side N-channel MOSFET driver (boost terminal).                                                                                                                |  |  |

| VBST2   | 9        | - I |                                                                                                                                                                                     |  |  |

| DRVH1   | 21       |     | High-side N-channel MOSFET driver outputs. LL referenced drivers.                                                                                                                   |  |  |

| DRVH2   | 10       | 0   |                                                                                                                                                                                     |  |  |

| LL1     | 20       |     | Switch node connections for high-side drivers, current limit and control circuitry.                                                                                                 |  |  |

| LL2     | 11       | - I |                                                                                                                                                                                     |  |  |

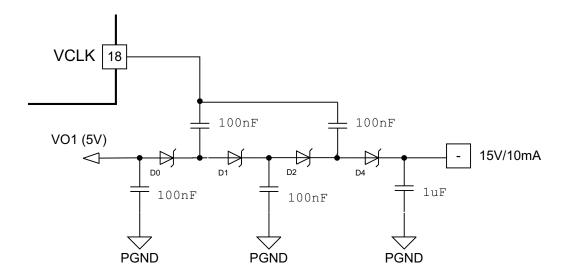

| VCLK    | 18       | 0   | 270-kHz clock output for 15-V charge pump.                                                                                                                                          |  |  |

Product Folder Links: TPS51125A

Copyright © 2009–2012, Texas Instruments Incorporated

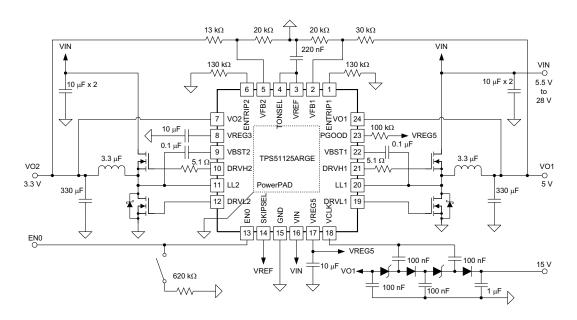

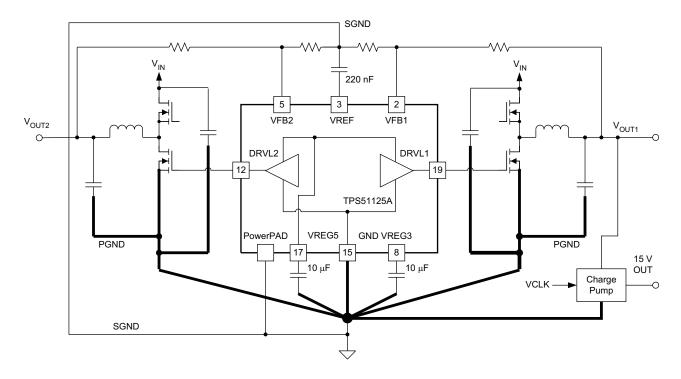

# **Typical Application Diagram**

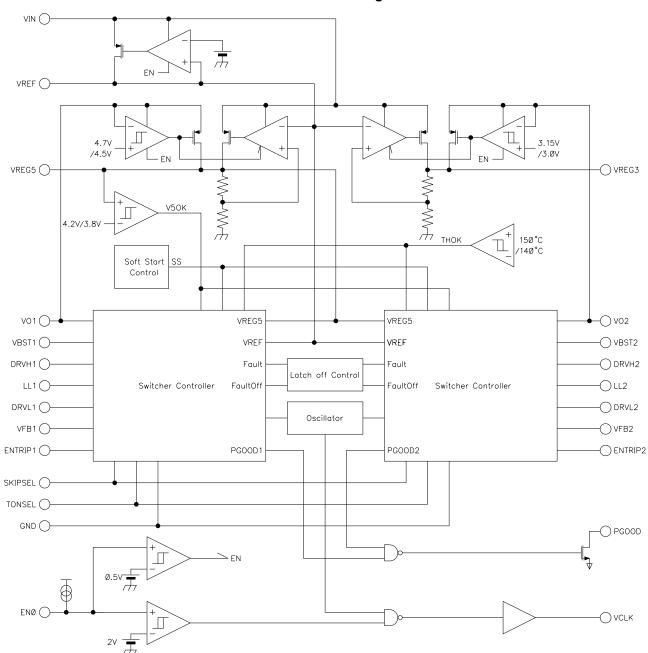

# **Functional Block Diagram**

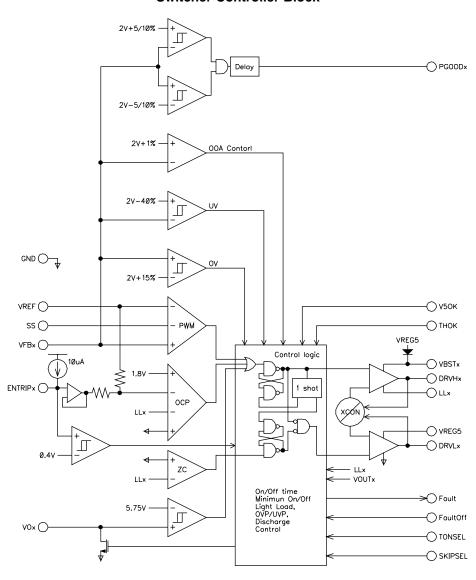

# **Switcher Controller Block**

#### **TYPICAL CHARACTERISTICS**

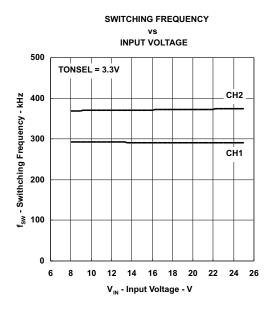

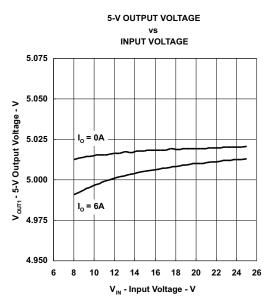

Figure 1.

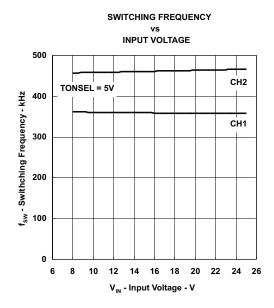

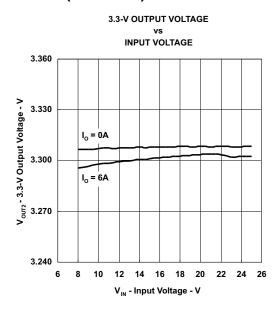

Figure 2.

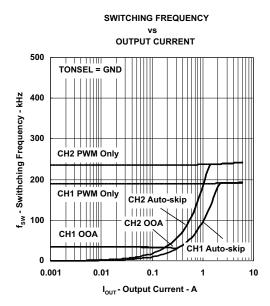

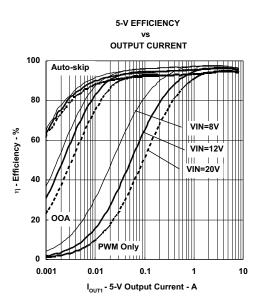

Figure 3.

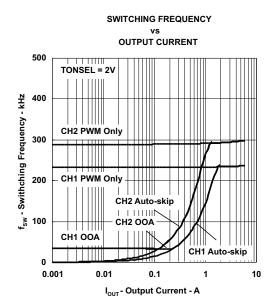

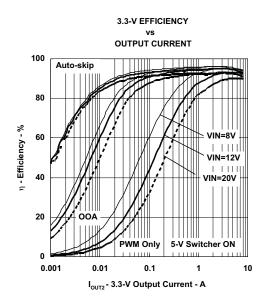

Figure 4.

Figure 5.

Figure 6.

Figure 7. Figure 8.

Downloaded from Arrow.com.

Figure 9.

Figure 10.

Figure 11.

Figure 12.

Product Folder Links: TPS51125A

Figure 13.

Figure 14.

Figure 15.

Figure 16.

Figure 17.

Figure 18.

Figure 19.

Figure 20.

Figure 21.

Figure 22.

Figure 23.

Figure 24.

Figure 25.

Figure 26.

Figure 27.

Figure 28.

Downloaded from Arrow.com.

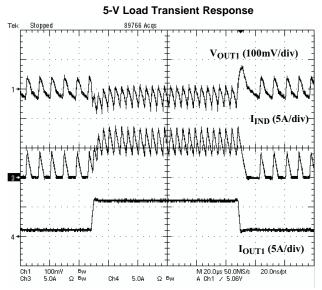

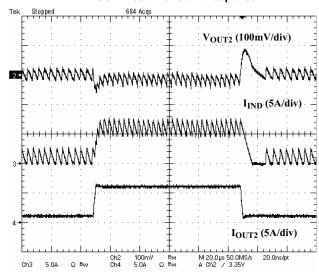

3.3-V Load Transient Response

Figure 29.

Figure 30.

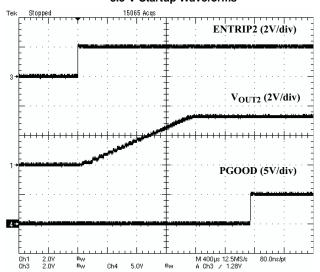

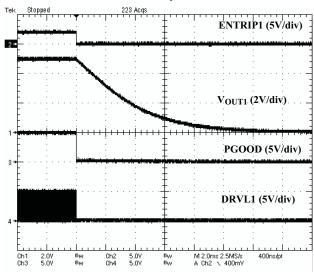

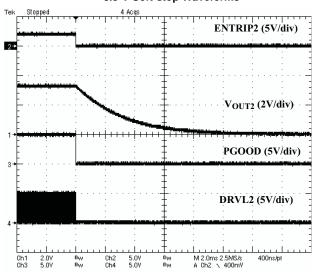

3.3-V Startup Waveforms

Figure 31.

Figure 32.

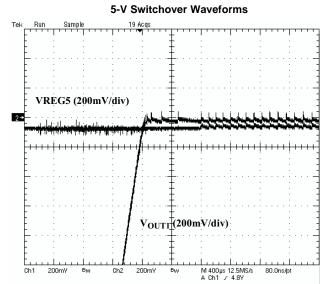

3.3-V Switchover Waveforms

Figure 33.

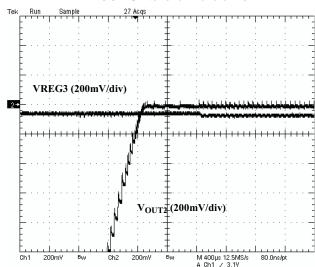

Figure 34.

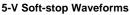

#### 3.3-V Soft-stop Waveforms

Figure 35.

Figure 36.

#### **APPLICATION INFORMATION**

#### **PWM Operations**

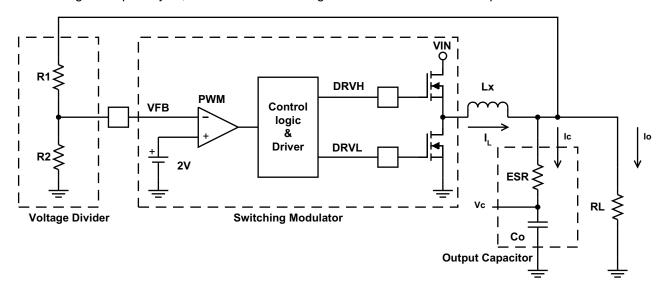

The main control loop of the switch mode power supply (SMPS) is designed as an adaptive on-time pulse width modulation (PWM) controller. It supports a proprietary D-CAP™ mode. D-CAP™ mode does not require external compensation circuit and is suitable for low external component count configuration when used with appropriate amount of ESR at the output capacitor(s).

At the beginning of each cycle, the synchronous top MOSFET is turned on, or becomes 'ON' state. This MOSFET is turned off, or becomes 'OFF' state, after internal one shot timer expires. This one shot is determined by  $V_{\text{IN}}$  and  $V_{\text{OUT}}$  to keep frequency fairly constant over input voltage range, hence it is called adaptive on-time control. The MOSFET is turned on again when the feedback point voltage, VFB, decreased to match with internal 2-V reference. The inductor current information is also monitored and should be below the over current threshold to initiate this new cycle. Repeating operation in this manner, the controller regulates the output voltage. The synchronous bottom or the "rectifying" MOSFET is turned on at the beginning of each 'OFF' state to keep the conduction loss minimum. The rectifying MOSFET is turned off before the top MOSFET turns on at next switching cycle or when inductor current information detects zero level. In the auto-skip mode or the OOA skip mode, this enables seamless transition to the reduced frequency operation at light load condition so that high efficiency is kept over broad range of load current.

# **Adaptive On-Time Control and PWM Frequency**

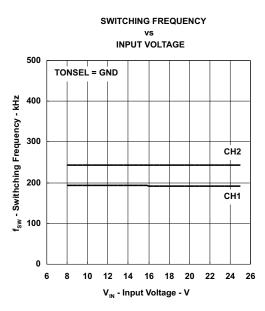

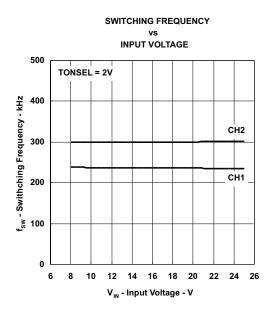

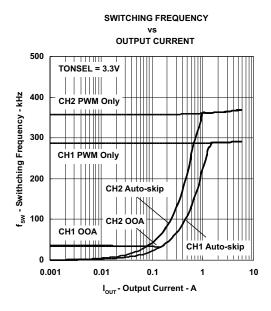

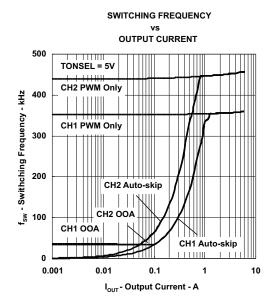

TPS51125A does not have a dedicated oscillator on board. However, the part runs with pseudo-constant frequency by feed-forwarding the input and output voltage into the on-time, one-shot timer. The on-time is controlled inverse proportional to the input voltage and proportional to the output voltage so that the duty ratio will be kept as VOUT/VIN technically with the same cycle time. The frequencies are set by TONSEL terminal connection as Table 3.

**Table 3. TONSEL Connection and Switching Frequency**

| TONOTI CONNECTION | SWITCHING | FREQUENCY |

|-------------------|-----------|-----------|

| TONSEL CONNECTION | CH1       | CH2       |

| GND               | 200 kHz   | 250 kHz   |

| VREF              | 245 kHz   | 305 kHz   |

| VREG3             | 300 kHz   | 375 kHz   |

| VREG5             | 365 kHz   | 460 kHz   |

Submit Documentation Feedback

#### **Loop Compensation**

From small-signal loop analysis, a buck converter using D-CAP<sup>TM</sup> mode can be simplified as below.

Figure 37. Simplifying the Modulator

The output voltage is compared with internal reference voltage after divider resistors, R1 and R2. The PWM comparator determines the timing to turn on high-side MOSFET. The gain and speed of the comparator is high enough to keep the voltage at the beginning of each on cycle substantially constant. For the loop stability, the 0dB frequency,  $f_0$ , defined below need to be lower than 1/4 of the switching frequency.

$$f_0 = \frac{1}{2\pi \times \mathsf{ESR} \times \mathsf{C}_{\mathsf{O}}} \le \frac{f_{\mathsf{SW}}}{4} \tag{1}$$

As  $f_0$  is determined solely by the output capacitor's characteristics, loop stability of D-CAP<sup>TM</sup> mode is determined by the capacitor's chemistry. For example, specialty polymer capacitors (SP-CAP) have Co in the order of several 100  $\mu$ F and ESR in range of 10 m $\Omega$ . These will make  $f_0$  in the order of 100 kHz or less and the loop will be stable. However, ceramic capacitors have  $f_0$  at more than 700 kHz, which is not suitable for this operational mode.

#### Ramp Signal

The TPS51125A adds a ramp signal to the 2-V reference in order to improve its jitter performance. As described in the previous section, the feedback voltage is compared with the reference information to keep the output voltage in regulation. By adding a small ramp signal to the reference, the S/N ratio at the onset of a new switching cycle is improved. Therefore the operation becomes less jitter and stable. The ramp signal is controlled to start with -20mV at the beginning of ON-cycle and to become 0 mV at the end of OFF-cycle in steady state. By using this scheme, the TPS51125A improve jitter performance without sacrificing the reference accuracy.

#### **Light Load Condition in Auto-Skip Operation**

The TPS51125A automatically reduces switching frequency at light load conditions to maintain high efficiency. This reduction of frequency is achieved smoothly and without increase of  $V_{\text{OUT}}$  ripple. Detail operation is described as follows. As the output current decreases from heavy load condition, the inductor current is also reduced and eventually comes to the point that its 'valley' touches zero current, which is the boundary between continuous conduction and discontinuous conduction modes. The rectifying MOSFET is turned off when this zero inductor current is detected. As the load current further decreased, the converter runs in discontinuous conduction mode and it takes longer and longer to discharge the output capacitor to the level that requires next 'ON' cycle. The ON time is kept the same as that in the heavy load condition. In reverse, when the output current increase from light load to heavy load, switching frequency increases to the preset value as the inductor current reaches to the continuous conduction. The transition load point to the light load operation  $I_{\text{OUT(LL)}}$  (i.e. the threshold between continuous and discontinuous conduction mode) can be calculated as follows;

$$I_{OUT(LL)} = \frac{1}{2 \times L \times f} \times \frac{\left(V_{IN} - V_{OUT}\right) \times V_{OUT}}{V_{IN}}$$

(2)

where f is the PWM switching frequency.

Switching frequency versus output current in the light load condition is a function of L,  $V_{IN}$  and  $V_{OUT}$ , but it decreases almost proportional to the output current from the  $I_{OUT(LL)}$  given above. For example, it will be 60 kHz at  $I_{OUT(LL)}$ /5 if the frequency setting is 300 kHz.

Submit Documentation Feedback

#### Out-of-Audio™ Light-Load Operation

Out-of-Audio<sup>TM</sup> (OOA) light-load mode is a unique control feature that keeps the switching frequency above acoustic audible frequencies toward virtually no load condition while maintaining best of the art high conversion efficiency. When the Out-of-Audio<sup>TM</sup> operation is selected, OOA control circuit monitors the states of both MOSFET and force to change into the 'ON' state if both of MOSFETs are off for more than 32  $\mu$ s. This means that the top MOSFET is turned on even if the output voltage is higher than the target value so that the output capacitor is tends to be overcharged.

The OOA control circuit detects the over-voltage condition and begins to modulate the on time to keep the output voltage regulated. As a result, the output voltage becomes 0.5% higher than normal light-load operation.

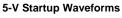

#### **Enable and Soft Start**

EN0 is the control pin of VREG5, VREG3 and VREF regulators. Bring this node down to GND disables those three regulators and minimize the shutdown supply current to 10  $\mu$ A. Pulling this node up to 3.3 V or 5 V will turn the three regulators on to standby mode. The two switch mode power supplies (channel-1, channel-2) become ready to enable at this standby mode. The TPS51125A has an internal, 1.6 ms, voltage servo softstart for each channel. When the ENTRIPx pin becomes higher than the enable threshold voltage, which is typically 430 mV, an internal DAC begins ramping up the reference voltage to the PWM comparator. Smooth control of the output voltage is maintained during start up. As TPS51125A shares one DAC with both channels, if ENTRIPx pin becomes higher than the enable threshold voltage while another channel is starting up, soft start is postponed until another channel soft start has completed. If both of ENTRIP1 and ENTRIP2 become higher than the enable threshold voltage at a same time (within 60  $\mu$ s), both channels start up at same time.

EN0 **ENTRIP1 ENTRIP2 VREF** VREG5 VREG3 CH<sub>1</sub> CH<sub>2</sub> **VCLK GND** Don't Care Don't Care Off Off Off Off Off Off R to GND Off Off On Off Off Off On On R to GND Off On On On On On Off Off R to GND Off On On On On Off On Off R to GND On Off On On On On On On Off Off On Off Off Off Open On On Open On Off On On On On Off On Off Off Open Off On On On On On Open On On On On On On On On

**Table 4. Enabling State**

#### **VREG5/VREG3 Linear Regulators**

There are two sets of 100-mA standby linear regulators which outputs 5 V and 3.3 V, respectively. The VREG5 serves as the main power supply for the analog circuitry of the device and provides the current for gate drivers. The VREG3 is intended mainly for auxiliary 3.3-V supply for the notebook system during standby mode.

Add high-quality X5R or X7R ceramic capacitor with a value of 10  $\mu$ F or larger placed close to the VREG5 and VREG3 pins to stabilize LDOs. For VREG3, a 1- $\mu$ F ceramic capacitor is acceptable when not loaded.

#### VREG5 Switch Over

When the VO1 voltage becomes higher than 4.7 V AND channel-1 internal powergood flag is generated, internal 5-V LDO regulator is shut off and the VREG5 output is connected to VO1 by internal switch over MOSFET. The 510-µs powergood delay helps a switch over without glitch.

#### **VREG3 Switch Over**

When the VO2 voltage becomes higher than 3.15 V AND channel-2 internal powergood flag is generated, internal 3.3-V LDO regulator is shut off and the VREG3 output is connected to VO2 by internal switch over MOSFET. The 510-µs powergood delay helps a switch over without glitch.

#### **Powergood**

The TPS51125A has one powergood output that indicates 'high' when both switcher outputs are within the targets (AND gated). The powergood function is activated with 2-ms internal delay after ENTRIPx goes high. If the output voltage becomes within +/-5% of the target value, internal comparators detect power good state and the powergood signal becomes high after 510-µs internal delay. Therefore PGOOD goes high around 2.5 ms after ENTRIPx goes high. If the output voltage goes outside of +/-10% of the target value, the powergood signal becomes low after 2-µs internal delay. The powergood output is an open drain output and is needed to be pulled up outside.

Also note that, in the case of Auto-skip or Out-of-Audio<sup>™</sup> mode, if the output voltage goes +10% above the target value and the power-good signal flags low, then the loop attempts to correct the output by turning on the low-side driver (forced PWM mode). After the feedback voltage returns to be within +5% of the target value and the power-good signal goes high, the controller returns back to auto-skip mode or Out-of-Audio<sup>™</sup> mode.

#### **Output Discharge Control**

When ENTRIPx is low, the TPS51125A discharges outputs using internal MOSFET which is connected to VOx and GND. The current capability of these MOSFETs is limited to discharge slowly.

#### **Low-Side Driver**

The low-side driver is designed to drive high current low  $R_{DS(on)}$  N-channel MOSFET(s). The drive capability is represented by its internal resistance, which are 4  $\Omega$  for VREG5 to DRVLx and 1.5  $\Omega$  for DRVLx to GND. A dead time to prevent shoot through is internally generated between top MOSFET off to bottom MOSFET on, and bottom MOSFET off to top MOSFET on. 5-V bias voltage is delivered from VREG5 supply. The instantaneous drive current is supplied by an input capacitor connected between VREG5 and GND. The average drive current is equal to the gate charge at Vgs = 5 V times switching frequency. This gate drive current as well as the high-side gate drive current times 5 V makes the driving power which need to be dissipated from TPS51125A package.

#### **High-Side Driver**

The high-side driver is designed to drive high current, low  $R_{DS(on)}$  N-channel MOSFET(s). When configured as a floating driver, 5-V bias voltage is delivered from VREG5 supply. The average drive current is also calculated by the gate charge at Vgs = 5 V times switching frequency. The instantaneous drive current is supplied by the flying capacitor between VBSTx and LLx pins. The drive capability is represented by its internal resistance, which are 4  $\Omega$  for VBSTx to DRVHx and 1.5 $\Omega$  for DRVHx to LLx.

Submit Documentation Feedback

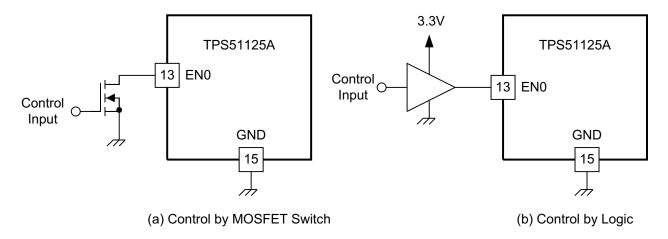

#### **VCLK for Charge Pump**

270-kHz clock signal can be used for charge pump circuit to generate approximately 15-V dc voltage. The clock signal becomes available when EN0 becomes higher than 2.4 V or open state. Example of control circuit is shown in Figure 38. Note that the clock driver uses VO1 as its power supply. Regardless of enable or disable of VCLK, power consumption of the TPS51125A is almost the same. Therefore even if VCLK is not used, one can let EN0 pin open or supply logic 'high', as shown in Figure 38, and let VCLK pin open. This approach further reduces the external part count.

Figure 38. Control Example of EN0 Master Enable

Figure 39. 15-V / 10-mA Charge Pump Configuration

#### **Current Protection**

TPS51125A has cycle-by-cycle over current limiting control. The inductor current is monitored during the 'OFF' state and the controller keeps the 'OFF' state during the inductor current is larger than the over current trip level. In order to provide both good accuracy and cost effective solution, TPS51125A supports temperature compensated MOSFET  $R_{DS(on)}$  sensing. ENTRIPx pin should be connected to GND through the trip voltage setting resistor,  $R_{TRIP}$ . ENTRIPx terminal sources  $I_{TRIP}$  current, which is 10  $\mu$ A typically at room temperature, and the trip level is set to the OCL trip voltage  $V_{TRIP}$  as below. Note that the  $V_{TRIP}$  is limited up to about 205 mV internally.

$$V_{TRIP} (mV) = \frac{R_{TRIP} (k\Omega) \times I_{TRIP} (\mu A)}{9} - 24 (mV)$$

(3)

External leakage current to ENTRIPx pin should be minimized to obtain accurate OCL trip voltage.

The inductor current is monitored by the voltage between GND pin and LLx pin so that LLx pin should be connected to the drain terminal of the bottom MOSFET properly. Itrip has 4500 ppm/°C temperature slope to compensate the temperature dependency of the  $R_{DS(on)}$ . GND is used as the positive current sensing node so that GND should be connected to the proper current sensing device, i.e. the source terminal of the bottom MOSFET.

As the comparison is done during the 'OFF' state,  $V_{TRIP}$  sets valley level of the inductor current. Thus, the load current at over current threshold,  $I_{OCP}$ , can be calculated in Equation 4.

$$I_{OCP} = \frac{V_{TRIP}}{R_{DS(on)}} + \frac{I_{RIPPLE}}{2} = \frac{V_{TRIP}}{R_{DS(on)}} + \frac{1}{2 \times L \times f} \times \frac{\left(V_{IN} - V_{OUT}\right) \times V_{OUT}}{V_{IN}}$$

$$\tag{4}$$

In an overcurrent condition, the current to the load exceeds the current to the output capacitor thus the output voltage tends to fall down. Eventually, it ends up with crossing the under voltage protection threshold and shutdown both channels.

#### **Over/Under Voltage Protection**

TPS51125A monitors a resistor divided feedback voltage to detect over and under voltage. When the feedback voltage becomes higher than 115% of the target voltage, the OVP comparator output goes high and the circuit latches as the top MOSFET driver OFF and the bottom MOSFET driver ON.

Also, TPS51125A monitors VOx voltage directly and if it becomes greater than 5.75 V the TPS51125A turns off the top MOSFET driver.

When the feedback voltage becomes lower than 60% of the target voltage, the UVP comparator output goes high and an internal UVP delay counter begins counting. After 32  $\mu$ s, TPS51125A latches OFF both top and bottom MOSFETs drivers, and shut off both drivers of another channel. This function is enabled after 2 ms following ENTRIPx has become high.

Submit Documentation Feedback

#### **UVLO Protection**

TPS51125A has VREG5 under voltage lock out protection (UVLO). When the VREG5 voltage is lower than UVLO threshold voltage both switch mode power supplies are shut off. This is non-latch protection. When the VREG3 voltage is lower than (VO2 - 1 V), both switch mode power supplies are also shut off.

#### **Thermal Shutdown**

TPS51125A monitors the temperature of itself. If the temperature exceeds the threshold value (typically 150°C), TPS51125A is shut off including LDOs. This is non-latch protection.

#### **External Parts Selection**

The external components selection is much simple in D-CAP™ Mode.

#### 1. Determine Output Voltage

The output voltage is programmed by the voltage-divider resistor, R1 and R2 shown in Figure 37. R1 is connected between VFBx pin and the output, and R2 is connected between the VFBx pin and GND. Recommended R2 value is from 10 k $\Omega$  to 20 k $\Omega$ . Determine R1 using equation as below.

$$R1 = \frac{\left(V_{\text{OUT}} - 2.0\right)}{2.0} \times R2 \tag{5}$$

#### 2. Choose the Inductor

The inductance value should be determined to give the ripple current of approximately 1/4 to 1/2 of maximum output current. Larger ripple current increases output ripple voltage and improves S/N ratio and helps stable operation.

$$L = \frac{1}{I_{\text{IND(ripple)}} \times f} \times \frac{\left(V_{\text{IN(max)}} - V_{\text{OUT}}\right) \times V_{\text{OUT}}}{V_{\text{IN(max)}}} = \frac{3}{I_{\text{OUT(max)}} \times f} \times \frac{\left(V_{\text{IN(max)}} - V_{\text{OUT}}\right) \times V_{\text{OUT}}}{V_{\text{IN(max)}}}$$

(6)

The inductor also needs to have low DCR to achieve good efficiency, as well as enough room above peak inductor current before saturation. The peak inductor current can be estimated as follows.

$$I_{IND(peak)} = \frac{V_{TRIP}}{R_{DS(on)}} + \frac{1}{L \times f} \times \frac{\left(V_{IN(max)} - V_{OUT}\right) \times V_{OUT}}{V_{IN(max)}}$$

(7)

#### 3. Choose the Output Capacitor(s)

Organic semiconductor capacitor(s) or specialty polymer capacitor(s) are recommended. Determine ESR to meet required ripple voltage. A quick approximation is as shown in Equation 8.

$$ESR = \frac{V_{OUT} \times 20 (mV) \times (1-D)}{2(V) \times I_{RIPPLE}} = \frac{20 (mV) \times L \times f}{2(V)}$$

where

- · D is the duty cycle

- the required output ripple slope is approximately 20 mV per T<sub>SW</sub> (switching period) in terms of VFB terminal voltage

#### 4. Choose the Low-Side MOSFET

It is highly recommended that the low-side MOSFET should have an integrated Schottky barrier diode, or an external Schottky barrier diode in parallel to achieve stable operation.

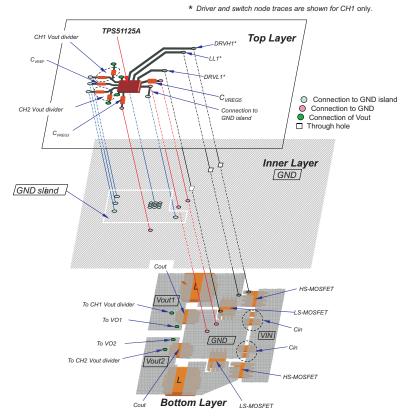

#### **Layout Considerations**

Certain points must be considered before starting a layout work using the TPS51125A.

- TPS51125A has only one GND pin and special care of GND trace design makes operation stable, especially when both channels operate. Group GND terminals of output voltage divider of both channels and the VREF capacitor as close as possible, connect them to an inner GND plane with PowerPad, overcurrent setting resistor and EN0 pull-down resistor as shown in the thin GND line of Figure 40. This trace is named Signal Ground (SGND). Group ground terminals of VIN capacitor(s), VOUT capacitor(s) and source of low-side MOSFETs as close as possible, and connect them to another GND plane with GND pin of the device, GND terminal of VREG3 and VREG5 capacitors and 15-V charge-pump circuit as shown in the bold GND line of Figure 40. This trace is named Power Ground (PGND). SGND should be connected to PGND at the middle point between ground terminal of VOUT capacitors.

- Inductor, VOUT capacitor(s), VIN capacitor(s) and MOSFETs are the power components and should be

placed on one side of the PCB (solder side). Power components of each channel should be at the same

distance from the TPS51125A. Other small signal parts should be placed on another side (component side).

Inner GND planes above should shield and isolate the small signal traces from noisy power lines.

- PCB trace defined as LLx node, which connects to source of high-side MOSFET, drain of low-side MOSFET and high-voltage side of the inductor, should be as short and wide as possible.

- High-quality X5R or X7R ceramic bypass capacitor of following capacitance value should be placed close to the device and traces should be no longer than 10 mm.

- VREG5: 10 µF or larger

- VREG3: 10 μF or larger (1 μF is acceptable when not loaded.)

- **VREF**: 220 nF to 1 μF

- Connect the overcurrent setting resistors from ENTRIPx to SGND and close to the device, right next to the

device if possible.

- The discharge path (VOx) should have a dedicated trace to the output capacitor; separate from the output voltage sensing trace. When LDO5 is switched over Vo1 trace should be 1.5 mm with no loops. When LDO3 is switched over and loaded Vo2 trace should also be 1.5 mm with no loops. There is no restriction for just monitoring Vox. Make the feedback current setting resistor (the resistor between VFBx to SGND) close to the device. Place on the component side and avoid vias between this resistor and the device.

- Connections from the drivers to the respective gate of the high-side or the low-side MOSFET should be as short as possible to reduce stray inductance. Use 0.65-mm (25 mils) or wider trace and via(s) of at least 0.5 mm (20 mils) diameter along this trace.

- All sensitive analog traces and components such as VOx, VFBx, VREF, GND, EN0, ENTRIPx, PGOOD, TONSEL and SKIPSEL should be placed away from high-voltage switching nodes such as LLx, DRVLx, DRVHx and VCLK nodes to avoid coupling.

- Traces for VFB1 and VFB2 should be short and laid apart each other to avoid channel to channel interference.

- In order to effectively remove heat from the package, prepare thermal land and solder to the package's thermal pad. Three by three or more vias with a 0.33-mm (13 mils) diameter connected from the thermal land to the internal ground plane should be used to help dissipation. This thermal land underneath the package should be connected to SGND, and should NOT be connected to PGND.

Submit Documentation Feedback

Figure 40. GND system of DC/DC converter using the TPS51125A

Figure 41. PCB Layout Design

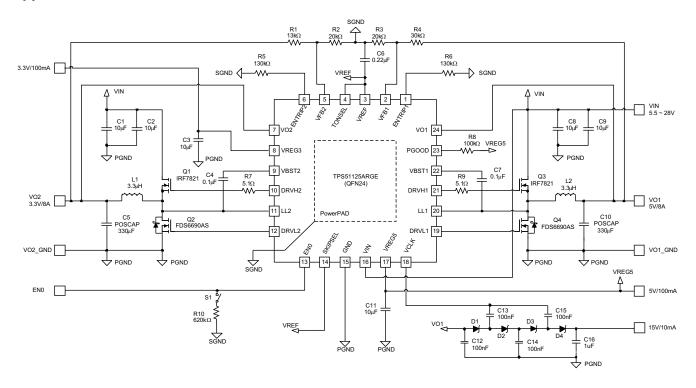

# **Application Circuit**

Figure 42. 5-V/8-A, 3.3-V/8-A Application Circuit (245-kHz/305-kHz Setting)

Table 5. List of Materials for 5-V/8-A, 3.3-V/8-A Application Circuit

| SYMBOL                | SPECIFICATION                       | MANUFACTURER | PART NUMBER    |

|-----------------------|-------------------------------------|--------------|----------------|

| C1, C2, C8, C9        | 10 μ F, 25 V                        | Taiyo Yuden  | TMK325BJ106MM  |

| C3, C11               | 10 μF, 6.3 V                        | TDK          | C2012X5R0J106K |

| C5, C10               | 330 $\mu F$ , 6.3 V, 25 $m\Omega$   | Sanyo        | 6TPE330ML      |

| L1, L2                | $3.3~\mu H,~15.6~A,~5.92$ $m\Omega$ | токо         | FDA1055-3R3M   |

| Q1, Q3                | 30 V, 9.5 mΩ                        | IR           | IRF7821        |

| Q2, Q4 <sup>(1)</sup> | 30 V, 12 mΩ                         | Fairchild    | FDS6690AS      |

Please use MOSFET with integrated Schottky barrier diode (SBD) for low side, or add SBD in parallel with normal MOSFET.

Submit Documentation Feedback

# **REVISION HISTORY**

| hanges from Revision B (September, 2009) to Revision A                                         |               |  |  |  |

|------------------------------------------------------------------------------------------------|---------------|--|--|--|

| <ul><li>Added Table 1</li><li>Added Figure 41</li></ul>                                        |               |  |  |  |

|                                                                                                |               |  |  |  |

| Changes from Revision A (January 2010) to Revision B                                           | Page          |  |  |  |

| Changed LDO Output Capacitance Requirement table from "at least" to                            | o "at most" 1 |  |  |  |

| • Changed VIN standby current value from 250 μA to 150 μA                                      | 4             |  |  |  |

| Changes from Revision B (September 2009) to Revision C                                         | Page          |  |  |  |

| Added note to table                                                                            | 6             |  |  |  |

| Added an updated Switcher Controller Block diagram                                             |               |  |  |  |

| Changes from Revision C (April 2011) to Revision D                                             | Page          |  |  |  |

| Added an updated Switcher Controller Block diagram                                             | 10            |  |  |  |

| Changed bulletted duty cycle description.                                                      | 27            |  |  |  |

| Changes from Revision D (June 2011) to Revision E                                              | Page          |  |  |  |

| Added Input voltage range parameter LL1, LL2, pulse width < 20 ns wir<br>MAXIMUM RATINGS table |               |  |  |  |

| Changes from Revision E (MARCH 2012) to Revision F                                             | Page          |  |  |  |

| Added Electrostatic discharge ratings in ABSOLUTE MAXIMUM RATIN                                | NGS table     |  |  |  |

www.ti.com 13-Aug-2021

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|----------------------|---------|

|                  |        |              |                    |      |                |              | (6)                           |                     |              |                      |         |

| FX001            | ACTIVE | VQFN         | RGE                | 24   | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | 51125A               | Samples |

| TPS51125ARGER    | ACTIVE | VQFN         | RGE                | 24   | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | 51125A               | Samples |

| TPS51125ARGET    | ACTIVE | VQFN         | RGE                | 24   | 250            | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | 51125A               | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 13-Aug-2021

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com 25-Sep-2024

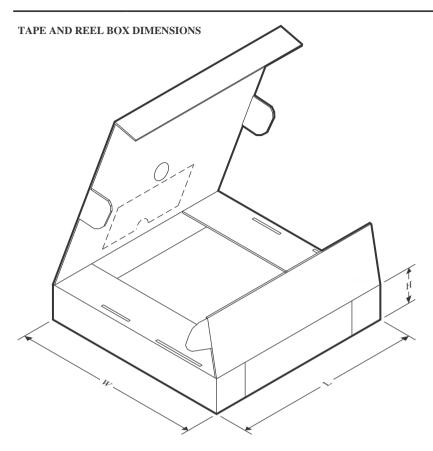

# TAPE AND REEL INFORMATION

# REEL DIMENSIONS Reel Diameter Reel Width (W1)

# TAPE DIMENSIONS KO PI BO Cavity A0

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

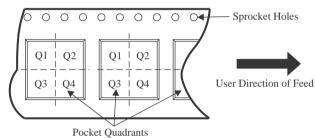

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS51125ARGER | VQFN            | RGE                | 24 | 3000 | 330.0                    | 12.4                     | 4.3        | 4.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS51125ARGER | VQFN            | RGE                | 24 | 3000 | 330.0                    | 12.4                     | 4.25       | 4.25       | 1.15       | 8.0        | 12.0      | Q2               |

| TPS51125ARGER | VQFN            | RGE                | 24 | 3000 | 330.0                    | 12.4                     | 4.25       | 4.25       | 1.15       | 8.0        | 12.0      | Q2               |

| TPS51125ARGET | VQFN            | RGE                | 24 | 250  | 180.0                    | 12.4                     | 4.25       | 4.25       | 1.15       | 8.0        | 12.0      | Q2               |

www.ti.com 25-Sep-2024

#### \*All dimensions are nominal

| 7 till dillitoriolorio di o monimidi |              |                 |      |      |             |            |             |

|--------------------------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| Device                               | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

| TPS51125ARGER                        | VQFN         | RGE             | 24   | 3000 | 367.0       | 367.0      | 38.0        |

| TPS51125ARGER                        | VQFN         | RGE             | 24   | 3000 | 356.0       | 356.0      | 35.0        |

| TPS51125ARGER                        | VQFN         | RGE             | 24   | 3000 | 346.0       | 346.0      | 33.0        |

| TPS51125ARGET                        | VQFN         | RGE             | 24   | 250  | 210.0       | 185.0      | 35.0        |

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

4204104/H

#### NOTES:

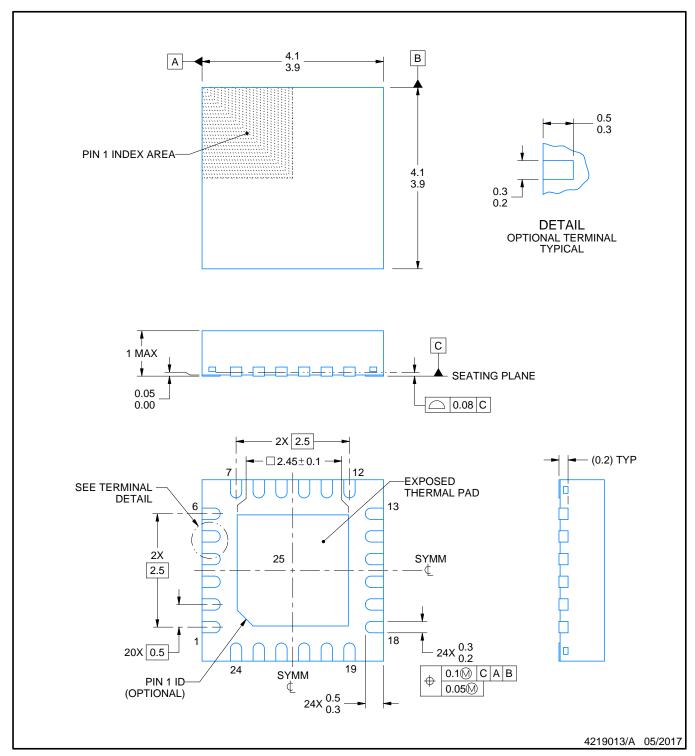

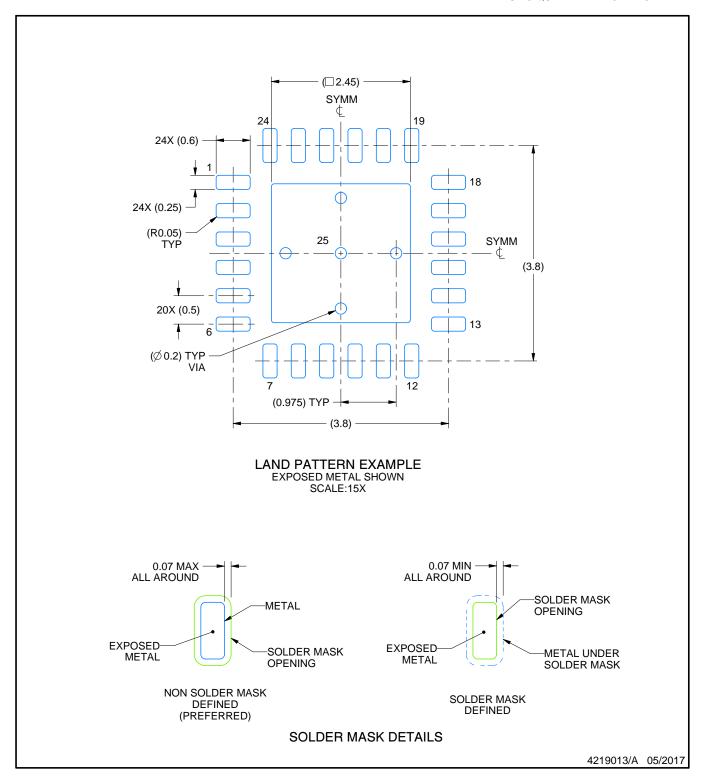

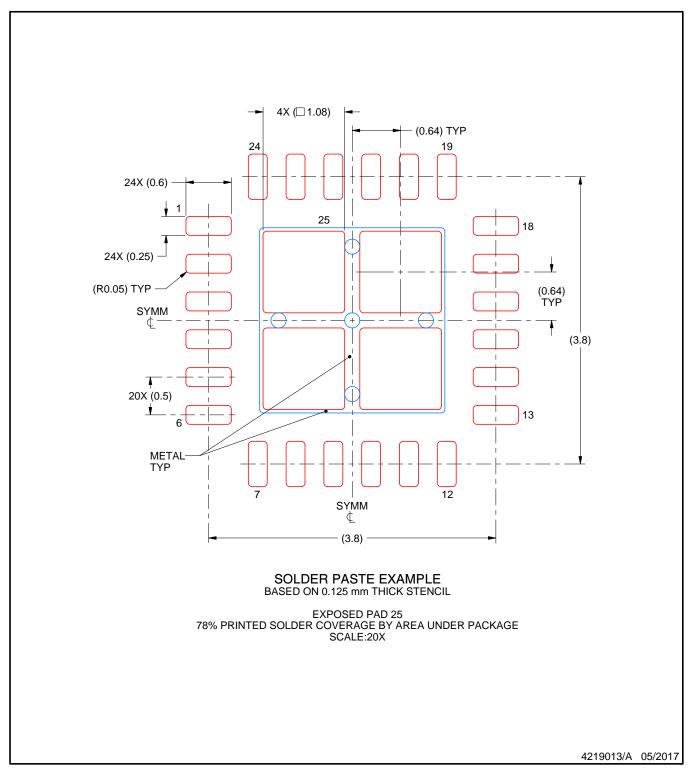

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025. Texas Instruments Incorporated