## 32-channel LED driver with automotive CAN FD Light interface

#### Datasheet - production data

#### **Features**

AEC-Q100 qualified

- General

- CAN FD Light compatible Serial Interface, Protocol Handler, Draft Specification

Proposal (DSP) available from CAN in Automation (CiA)

- High precision oscillator integrated, no external quartz required

- QFN48L 7x7 with exposed pad

- Timeout watchdog with Limp Home

- Low standby current

- Stand Alone/Fail Safe and Bus mode operation

- Direct drive (1 Direct Input), for 1 function group supporting ASIL requirements

- Widest configurability by embedded non-volatile and volatile memories

- Operating supply voltage range 5.5 V – 40 V

- Linear Regulators section

- Operating temperature range

40°C 150°C

- 32 constant current output channels, high side configuration

- Output current from 1 mA to 15 mA, parallelable outputs

- Output voltage up to 35 V

This is information on a product in full production.

- Feedback voltage to external pre-regulator, to optimize the regulation voltage minimizing overall power dissipation

- Current setting per channel by 8-bit DAC

- Analogue dimming, 8-bit PWM channel individual exponential brightness control and 8-bit global PWM dimming

- Programmable PWM frequency

- Slow turn on/off time, gradual outputs delay and dithered clock, for better EMC performances

- Protection and diagnostic

- Integrated 8-bit ADC, for full and flexible diagnostic

- 1 dedicated line for fault bus

- Temperature warning (1 threshold)

- Over-temperature shutdown

- Short circuit and open load detection and protection

- Automatic LED current derating, through external NTC measurement and device junction temperature (T<sub>J</sub>)

## **Applications**

- Automotive OLED Rear Lighting

- Automotive Ambient Lighting

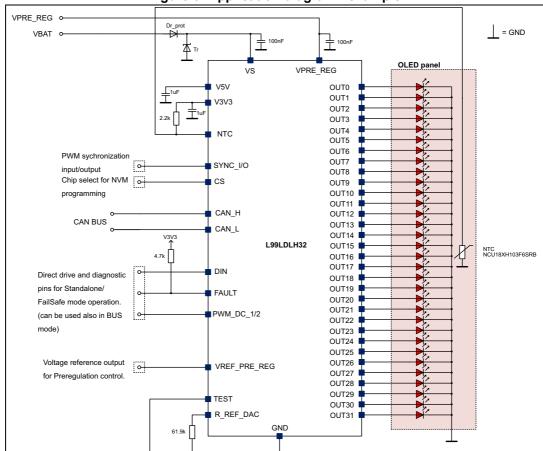

Figure 1. Simplified application schematic

www.st.com

December 2021 DS12879 Rev 5 1/141

Contents L99LDLH32

## **Contents**

| 1 | Des   | cription               | 1                                                 | 10 |

|---|-------|------------------------|---------------------------------------------------|----|

| 2 | Intro | ductio                 | n                                                 | 11 |

|   | 2.1   | Device                 | e information                                     | 12 |

| 3 | Devi  | ce sup                 | ply concept                                       | 16 |

| 4 | Line  | ar curre               | ent sources                                       | 17 |

|   | 4.1   | Gener                  | ral description                                   | 17 |

|   | 4.2   | Chanr                  | nel current setting                               | 18 |

|   | 4.3   | Chanr                  | nel driver drop-out voltage                       | 18 |

|   | 4.4   | Chanr                  | nel output gradual delay                          | 19 |

| 5 | Fund  | ctional                | description                                       | 21 |

|   | 5.1   | Opera                  | ating modes                                       | 21 |

|   |       | 5.1.1                  | Stand-by mode                                     | 22 |

|   |       | 5.1.2                  | Initialization                                    | 23 |

|   |       | 5.1.3                  | Reset mode                                        | 23 |

|   |       | 5.1.4                  | Fail Safe / Stand Alone mode                      | 24 |

|   |       | 5.1.5                  | Normal / Bus mode                                 | 24 |

|   | 5.2   | Programmable functions |                                                   | 25 |

|   |       | 5.2.1                  | Direct drive and functional configuration         | 25 |

|   |       | 5.2.2                  | PWM operation                                     | 26 |

|   | 5.3   | Protec                 | ctions and diagnostic                             | 30 |

|   |       | 5.3.1                  | Diagnostic availability and validation - strategy | 30 |

|   |       | 5.3.2                  | Fault bus capability                              | 31 |

|   |       | 5.3.3                  | Thermal warning                                   | 31 |

|   |       | 5.3.4                  | Thermal shutdown                                  | 32 |

|   |       | 5.3.5                  | LED current derating                              | 32 |

|   |       | 5.3.6                  | VS under voltage lockout                          | 32 |

|   |       | 5.3.7                  | Channel output - LED short circuit detection      | 33 |

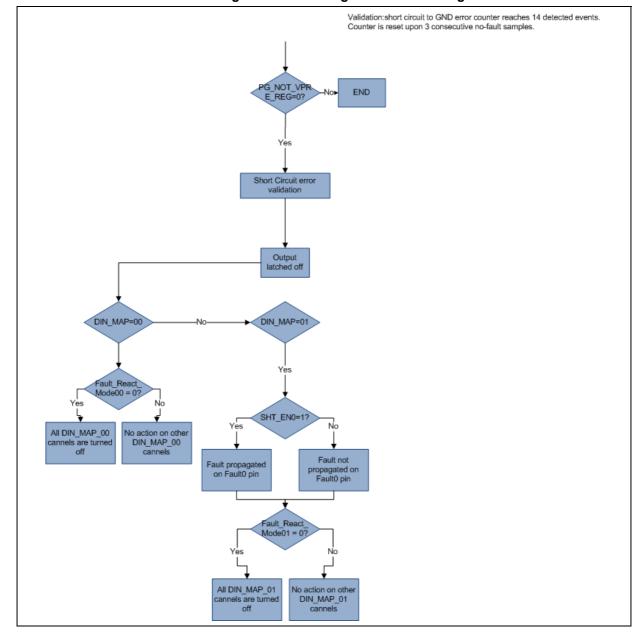

|   |       | 5.3.8                  | Channel output - short circuit to GND             | 36 |

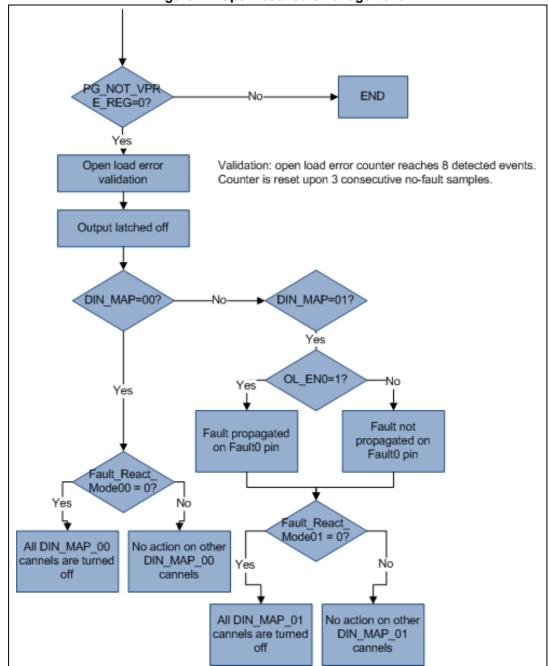

|   |       | 5.3.9                  | Channel output – Open load detection              | 37 |

L99LDLH32 Contents

| 6                | Com | nmunica  | tion interface                                                 | 40    |

|------------------|-----|----------|----------------------------------------------------------------|-------|

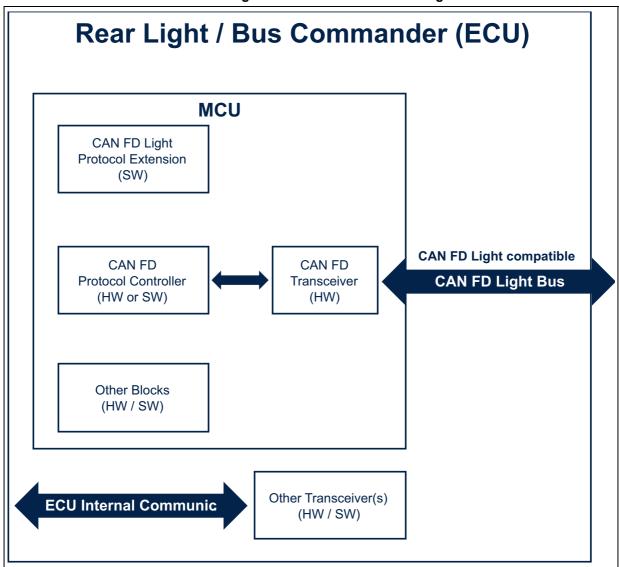

|                  | 6.1 | CAN F    | D Light compatible network protocol                            | 40    |

|                  | 6.2 | Protoc   | ol overview                                                    | 40    |

|                  |     | 6.2.1    | Basic function                                                 | 40    |

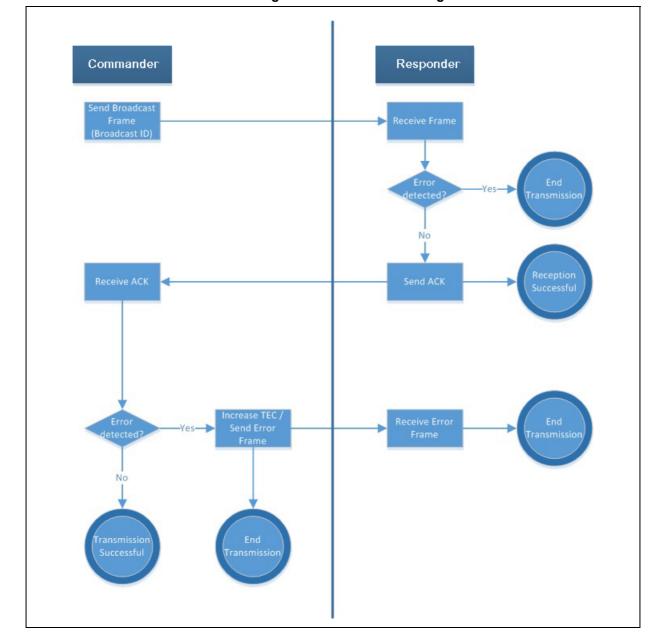

|                  |     | 6.2.2    | Commander                                                      | 41    |

|                  |     | 6.2.3    | Responder                                                      | 42    |

|                  | 6.3 | Data lir | nk layer                                                       | 43    |

|                  |     | 6.3.1    | CAN FD Light compatible frame format                           | 44    |

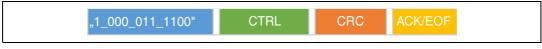

|                  |     | 6.3.2    | Wake-Up                                                        | 44    |

|                  |     | 6.3.3    | Error frames                                                   | 44    |

|                  |     | 6.3.4    | Collisions                                                     | 44    |

|                  |     | 6.3.5    | Error handling                                                 | 44    |

|                  | 6.4 | Data h   | andling                                                        | 45    |

|                  |     | 6.4.1    | Overview                                                       | 45    |

|                  | 6.5 | Broado   | cast frames                                                    | 46    |

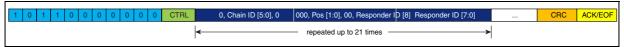

|                  |     | 6.5.1    | Frame format                                                   | 46    |

|                  |     | 6.5.2    | Broadcast frame for current setting and PWM duty cycle setting | 47    |

|                  |     | 6.5.3    | Chain initialization                                           | 48    |

|                  |     | 6.5.4    | Go to sleep/wake-up pattern                                    | 48    |

|                  |     | 6.5.5    | Synchronization Frame                                          | 49    |

|                  | 6.6 | Unicas   | t frames                                                       | 49    |

|                  |     | 6.6.1    | Unicast request frame                                          | 49    |

|                  |     | 6.6.2    | Unicast response frame                                         | 52    |

|                  |     | 6.6.3    | Global Status Byte (GSB)                                       | 52    |

|                  |     | 6.6.4    | Unicast frame – no data                                        | 54    |

|                  |     | 6.6.5    | Unicast frame – single RAM read                                | 54    |

|                  |     | 6.6.6    | Unicast frame – Single RAM read & clear                        | 54    |

|                  |     | 6.6.7    | Unicast frame – single ROM read                                | 54    |

|                  |     | 6.6.8    | Unicast frame - burst read mode RAM register                   | 54    |

|                  |     | 6.6.9    | Unicast frame – single RAM write                               | 55    |

|                  |     | 6.6.10   | Unicast frame – 3x RAM write                                   | 55    |

| 7                | FTP | and RA   | M memory mapping                                               | 56    |

|                  | 7.1 | RAM re   | egisters description                                           | 61    |

|                  |     | 7.1.1    | Channel PWM duty cycle                                         | 61    |

|                  |     | 7.1.2    | Channel current setting                                        | 69    |

| ( <del>-</del> - |     |          |                                                                |       |

| <b>— y</b> /     |     |          | DS12879 Rev 5                                                  | 3/141 |

Contents L99LDLH32

|   |       | 7.1.3    | Channel mapping on DIN                          | 77    |

|---|-------|----------|-------------------------------------------------|-------|

|   |       | 7.1.4    | Device configuration 1                          | 79    |

|   |       | 7.1.5    | Device configuration 2                          | 81    |

|   |       | 7.1.6    | Device configuration 3                          | 82    |

|   |       | 7.1.7    | Device configuration 4                          | 84    |

|   |       | 7.1.8    | Watchdog                                        | 85    |

|   |       | 7.1.9    | Position and chain identifier for Responder IDx | 86    |

|   |       | 7.1.10   | Channel output on-state voltage                 | 86    |

|   |       | 7.1.11   | Channel output status                           | 93    |

|   |       | 7.1.12   | Channel short circuit status                    | 95    |

|   |       | 7.1.13   | Channel open load status                        | 97    |

|   |       | 7.1.14   | Channel short to GND                            | 99    |

|   |       | 7.1.15   | Channel VLEDON ADC status refresh               | 101   |

|   |       | 7.1.16   | Device status 1                                 | 103   |

|   |       | 7.1.17   | Device status 2                                 | 103   |

|   |       | 7.1.18   | Device status 3                                 | 104   |

|   |       | 7.1.19   | FTP status 1                                    | 106   |

|   |       | 7.1.20   | FTP status 2                                    | 107   |

|   |       | 7.1.21   | FTP parity error status register                | 109   |

|   | 7.2   | FTP R    | ows description                                 | 110   |

|   |       | 7.2.1    | Device FTP Configuration - Row_0                | 110   |

|   |       | 7.2.2    | Device FTP Configuration - Row_1                | 110   |

|   |       | 7.2.3    | Device FTP Configuration - Row_2                | 111   |

|   |       | 7.2.4    | Device FTP Configuration - Row_3                | 112   |

|   |       | 7.2.5    | Device FTP Configuration - Row_4                | 113   |

|   |       | 7.2.6    | Device FTP Configuration - Row_11               | 113   |

|   |       | 7.2.7    | Device FTP Configuration - Row_12               | 114   |

| 8 | Elect | rical ch | naracteristics                                  | . 119 |

|   | 8.1   |          | te maximum ratings                              |       |

|   | 8.2   |          | rotection                                       |       |

|   | 8.3   | •        | al characteristics                              |       |

|   | 8.4   | Main e   | lectrical characteristics                       | . 122 |

|   | 8.5   |          | current sources                                 |       |

|   | 8.6   |          | timings and ADC characteristics                 |       |

|   | 8.7   | _        | D Light compatible transceiver characteristics  |       |

|   | 0.1   |          | D Light compatible transcerver characteristics  | . 100 |

|   |       |          |                                                 |       |

| _99LDLH32 | Contents |

|-----------|----------|

|           |          |

| 9  | Package and PCB thermal data    |    |  |  |

|----|---------------------------------|----|--|--|

|    | 9.1 QFN-48L 7x7 thermal data    | 33 |  |  |

| 10 | Package information             | 34 |  |  |

|    | 10.1 QFN48L 7x7 package outline | 34 |  |  |

|    | 10.2 QFN48L 7x7 mechanical data | 35 |  |  |

| 11 | Order codes                     | 36 |  |  |

| 12 | Revision history                | 37 |  |  |

List of tables L99LDLH32

## List of tables

| Table 1.  | Pin list description                                              | 14 |

|-----------|-------------------------------------------------------------------|----|

| Table 2.  | Minimum channel drop-out voltage at max current vs T <sub>J</sub> | 10 |

| Table 3.  | Output channel assignment to DIN                                  | 25 |

| Table 4.  | Output channel in Fail Safe / Stand Alone mode                    |    |

| Table 5.  | PWM frequency range                                               |    |

| Table 6.  | PWM phase shift (in Consumer mode)                                |    |

| Table 7.  | Diagnostic blanking time                                          |    |

| Table 8.  | Fault reaction mode                                               |    |

| Table 9.  | LED short circuit threshold - grouping                            |    |

| Table 10. | Wake-up pattern (WUP) frame                                       |    |

| Table 11. | Synchronization frame                                             |    |

| Table 12. | Unicast frame data - Operating Code and Register Address          |    |

| Table 13. | Unicast frame data - Registers access mode                        |    |

| Table 14. | Global status byte field description                              |    |

| Table 15. | RAM memory map                                                    |    |

| Table 16. | FTP memory map                                                    |    |

| Table 17. | Channel PWM duty cycle field description                          |    |

| Table 18. | Channel PWM duty cycle 0x02h field description                    |    |

| Table 19. | Channel PWM duty cycle 0x03h field description                    |    |

| Table 20. | Channel PWM duty cycle 0x04h field description                    |    |

| Table 21. | Channel PWM duty cycle 0x05h field description                    |    |

| Table 22. | Channel PWM duty cycle 0x06h field description                    |    |

| Table 23. | Channel PWM duty cycle 0x07h field description                    |    |

| Table 24. | Channel PWM duty cycle 0x08h field description                    |    |

| Table 25. | Channel PWM duty cycle 0x09h field description                    |    |

| Table 26. | Channel current setting 0x0Ah field description                   |    |

| Table 27. | Channel current setting 0x0Bh field description                   |    |

| Table 28. | Channel current setting 0x0Ch field description                   |    |

| Table 29. | Channel current setting 0x0Dh field description                   |    |

| Table 30. | Channel current setting 0x0Eh field description                   |    |

| Table 31. | Channel current setting 0x0Fh field description                   |    |

| Table 32. | Channel current setting 0x10h field description                   |    |

| Table 33. | Channel current setting 0x11h field description                   |    |

| Table 34. | Channel mapping on DIN 0x12h field description                    |    |

| Table 35. | Channel mapping on DIN 0x13h field description                    |    |

| Table 36. | Device configuration 1 field description                          |    |

| Table 37. | Device configuration 2 field description                          |    |

| Table 38. | Device configuration 3 field description                          |    |

| Table 39. | 20 MHz Oscillator, Dithering - Modulation Parameters              |    |

| Table 40. | Device configuration 4 field description                          |    |

| Table 41. | State transition bits                                             |    |

| Table 42. | Watchdog field description                                        |    |

| Table 43. | Position and chain identifier for Responder IDx field description |    |

| Table 44. | Channel output on-state voltage 0x1Fh field description           |    |

| Table 45. | Channel output on-state voltage 0x20h field description           |    |

| Table 46. | Channel output on-state voltage 0x21h field description           |    |

| Table 47. | Channel output on-state voltage 0x22h field description           |    |

| Table 48. | Channel output on-state voltage 0x23h field description           |    |

|           |                                                                   |    |

| Table 49. | Channel output on-state voltage 0x24h field description   | 90  |

|-----------|-----------------------------------------------------------|-----|

| Table 50. | Channel output on-state voltage 0x25h field description   | 91  |

| Table 51. | Channel output on-state voltage 0x26h field description   | 92  |

| Table 52. | Channel output status field description                   | 94  |

| Table 53. | Channel short circuit status field description            | 96  |

| Table 54. | Channel open load status field description                | 98  |

| Table 55. | Channel short to GND field description                    | 100 |

| Table 56. | Channel VLEDON ADC status refresh field description       | 102 |

| Table 57. | Device status 1 field description                         | 103 |

| Table 58. | Device status 2 field description                         | 104 |

| Table 59. | Device status 3 field description                         | 104 |

| Table 60. | FTP status 1 field description                            | 106 |

| Table 61. | FTP status 2 field description                            | 108 |

| Table 62. | FTP parity error status field description                 |     |

| Table 63. | Row_0                                                     |     |

| Table 64. | Row_1                                                     |     |

| Table 65. | Row_2                                                     |     |

| Table 66. | Row_3                                                     |     |

| Table 67. | Row_4                                                     |     |

| Table 68. | Row_11                                                    |     |

| Table 69. | Row_12                                                    |     |

| Table 70. | CAN bit sampling point                                    |     |

| Table 71. | Absolute maximum ratings                                  |     |

| Table 72. | ESD protection                                            |     |

| Table 73. | QFN48L 7x7 package thermal data                           |     |

| Table 74. | Thermal data, warning and shutdown                        |     |

| Table 75. | Supply                                                    |     |

| Table 76. | Output characteristics                                    |     |

| Table 77. | PWM characteristics                                       |     |

| Table 78. | NTC derating start configuration – Voltage vs Temperature |     |

| Table 79. | Digital timings                                           |     |

| Table 80. | ADC characteristics                                       | 128 |

| Table 81. | Digital I/O characteristics                               |     |

| Table 82. | CAN FD Light compatible transceiver                       |     |

| Table 83. | PCB properties                                            |     |

| Table 84. | Package mechanical data                                   | 135 |

| Table 85. | Device summary                                            |     |

| Table 86. | Document revision history                                 | 137 |

List of figures L99LDLH32

# List of figures

| Figure 1.                | Simplified application schematic                                             | 1  |

|--------------------------|------------------------------------------------------------------------------|----|

| Figure 2.                | Functional block diagram                                                     | 12 |

| Figure 3.                | Application diagram - example                                                | 13 |

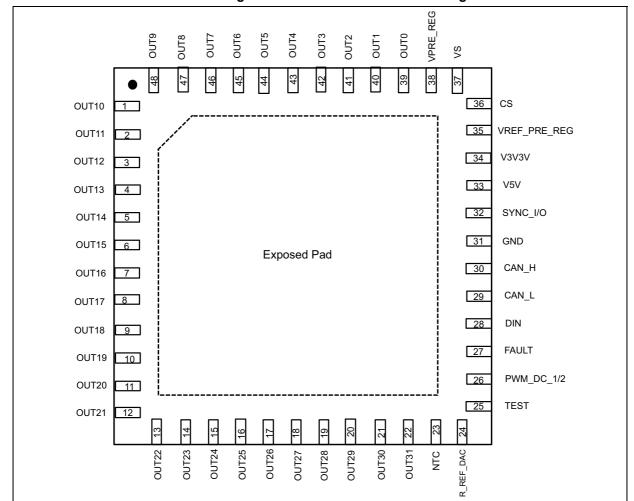

| Figure 4.                | QFN48L 7x7 connection diagram                                                | 14 |

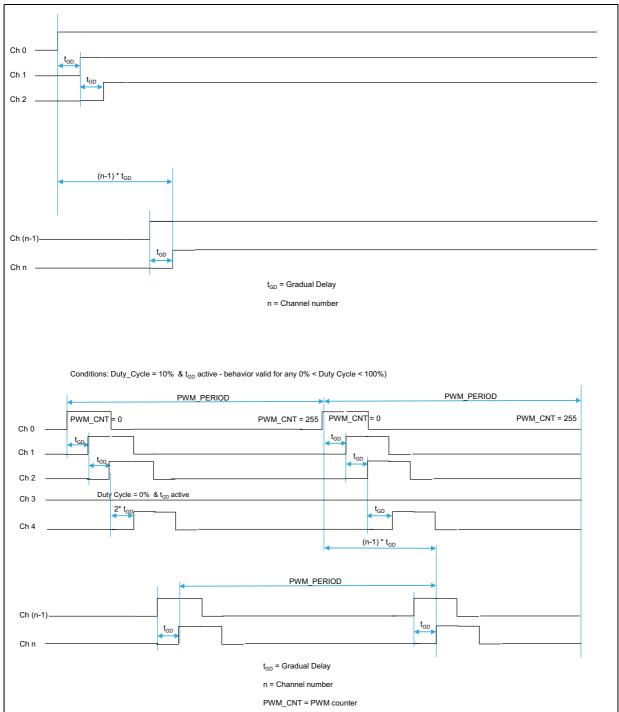

| Figure 5.                | Gradual delay concept                                                        | 20 |

| Figure 6.                | Device state diagram                                                         | 22 |

| Figure 7.                | Duty cycle vs Dimming Step                                                   | 27 |

| Figure 8.                | PWM concept for DIN function group                                           |    |

| Figure 9.                | Output & PWM control concept DIN                                             |    |

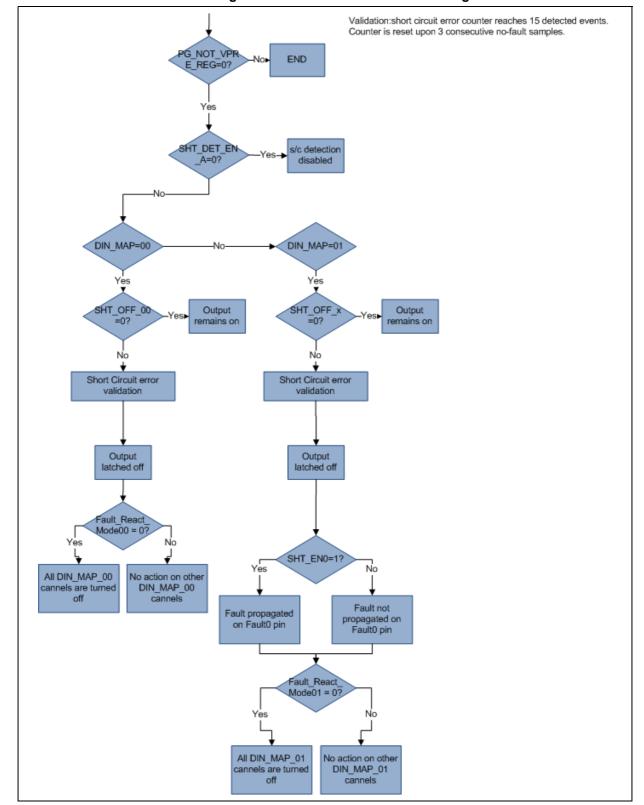

| Figure 10.               | LED short circuit fault management                                           |    |

| Figure 11.               | Short to ground fault management                                             |    |

| Figure 12.               | Open load fault management                                                   |    |

| Figure 13.               | System overview                                                              |    |

| Figure 14.               | Commander block diagram                                                      |    |

| Figure 15.               | Responder ECU Controller Device                                              |    |

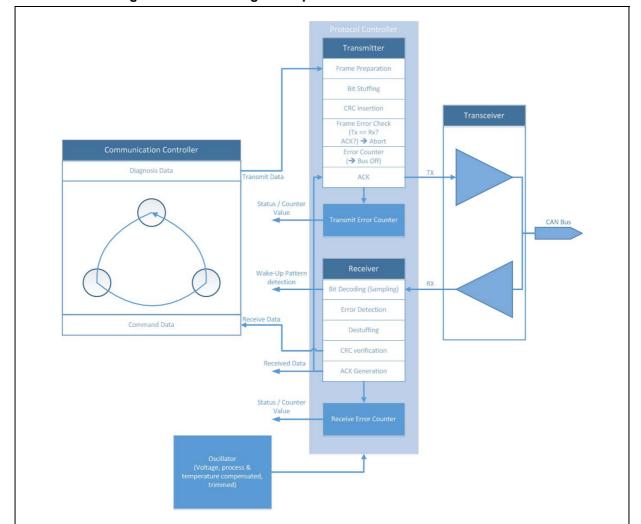

| Figure 16.               | CAN FD Light compatible Communication and Protocol Controller                |    |

| Figure 17.               | CAN FD Base Frame Format (FBFF)                                              |    |

| Figure 18.               | Broadcast message flow                                                       |    |

| Figure 19.               | Broadcast frame                                                              |    |

| Figure 20.               | Broadcast chain initialization                                               |    |

| Figure 21.               | Send-To-Sleep command                                                        |    |

| Figure 22.               | Synchronization frame                                                        |    |

| Figure 23.               | Unicast request communication between Commander and Responders               |    |

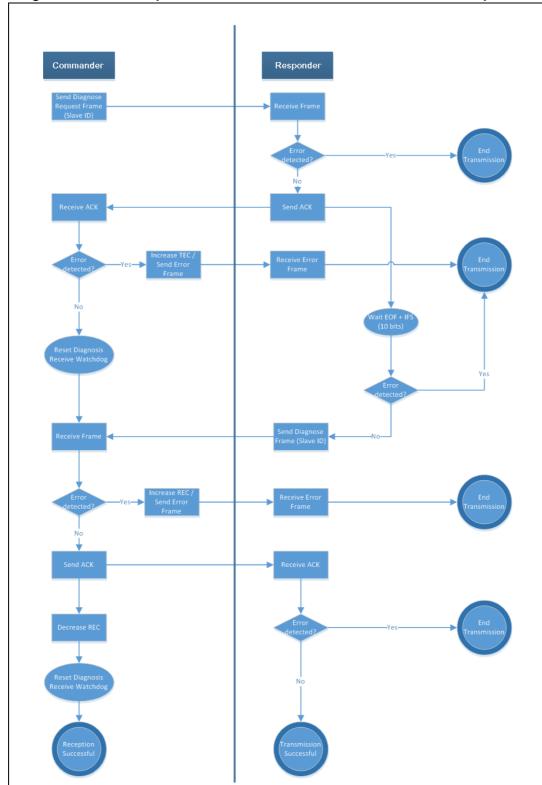

| Figure 24.               | Unicast diagnosis request frame                                              |    |

| Figure 25.               | Unicast diagnosis response frame                                             |    |

| Figure 25.               | Global Status Byte                                                           |    |

| Figure 20.               | Unicast frame w/o data - Commander request and Responder answer              |    |

| Figure 27.               | Unicast frame with single RAM read - Commander request and Responder answer  |    |

| Figure 20.               | Unicast frame with Single RAM read and clear - Commander request and         | 54 |

| i igule 29.              | Responder answer                                                             | 5/ |

| Figure 30.               | Unicast frame with burst read mode RAM register - Commander request and      | 54 |

| rigule 30.               | Responder answer                                                             | 55 |

| Eiguro 21                | Unicast frame with single RAM write - Commander request and Responder answer |    |

| Figure 31.               | Unicast frame with 3x RAM write - Commander request and Responder answer     |    |

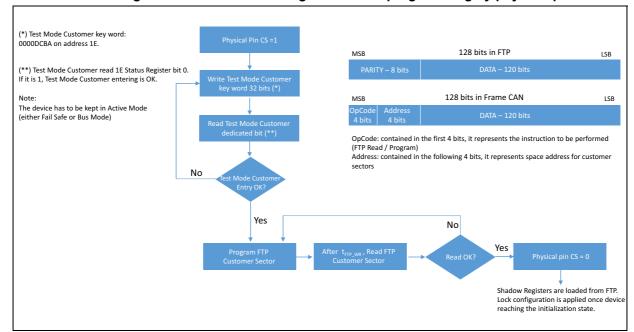

| Figure 32.<br>Figure 33. | FTP access through CAN bus - programming by physical pin CS                  |    |

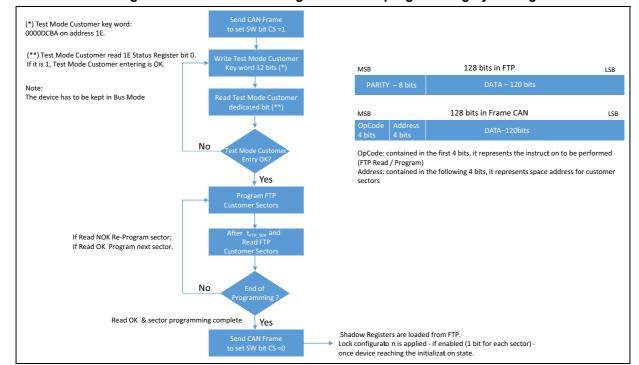

| •                        | FTP access through CAN bus - programming by physical pin CS                  |    |

| Figure 34.               |                                                                              |    |

| Figure 35.               | Channel PWM duty cycle 0x01h register                                        |    |

| Figure 36.               | Channel PWM duty cycle 0x02h register                                        |    |

| Figure 37.               | Channel PWM duty cycle 0x03h register                                        |    |

| Figure 38.               | Channel PWM duty cycle 0x04h register                                        |    |

| Figure 39.               | Channel PWM duty cycle 0x05h register                                        |    |

| Figure 40.               | Channel PWM duty cycle 0x06h register                                        |    |

| Figure 41.               | Channel PWM duty cycle 0x07h register                                        |    |

| Figure 42.               | Channel PWM duty cycle 0x08h register                                        |    |

| Figure 43.               | Channel PWM duty cycle 0x09h register                                        |    |

| Figure 44.               | Channel current setting 0x0Ah register                                       |    |

| Figure 45.               | Channel current setting 0x0Bh register                                       |    |

| Figure 46.               | Channel current setting 0x0Ch register                                       | /1 |

DS12879 Rev 5

Downloaded from Arrow.com.

| Figure 47. | Channel current setting 0x0Dh register                   | 72  |

|------------|----------------------------------------------------------|-----|

| Figure 48. | Channel current setting 0x0Eh register                   |     |

| Figure 49. | Channel current setting 0x0Fh register                   | 74  |

| Figure 50. | Channel current setting 0x10h register                   | 75  |

| Figure 51. | Channel current setting 0x11h register                   | 76  |

| Figure 52. | Channel mapping on DIN 0x12h register                    |     |

| Figure 53. | Channel mapping on DIN 0x13h register                    |     |

| Figure 54. | Device configuration register #1                         | 79  |

| Figure 55. | Device configuration register #2                         | 81  |

| Figure 56. | Device configuration register #3                         | 82  |

| Figure 57. | 20 MHz Oscillator, Dithering - Modulation Curve          |     |

| Figure 58. | Device configuration register #4                         | 84  |

| Figure 59. | Watchdog register                                        | 85  |

| Figure 60. | Position and chain identifier for Responder IDx register | 86  |

| Figure 61. | Channel output on-state voltage 0x1Fh register           | 86  |

| Figure 62. | Channel output on-state voltage 0x20h register           |     |

| Figure 63. | Channel output on-state voltage 0x21h register           | 88  |

| Figure 64. | Channel output on-state voltage 0x22h register           | 89  |

| Figure 65. | Channel output on-state voltage 0x23h register           | 89  |

| Figure 66. | Channel output on-state voltage 0x24h register           | 90  |

| Figure 67. | Channel output on-state voltage 0x25h register           | 91  |

| Figure 68. | Channel output on-state voltage 0x26h register           | 92  |

| Figure 69. | Channel output status register                           | 93  |

| Figure 70. | Channel short circuit status register                    | 95  |

| Figure 71. | Channel open load status register                        |     |

| Figure 72. | Channel short to GND register                            |     |

| Figure 73. | Channel VLEDON ADC status refresh register               | 101 |

| Figure 74. | Device status register #1                                |     |

| Figure 75. | Device status register #2                                | 103 |

| Figure 76. | Device status register #31                               |     |

| Figure 77. | FTP status register #11                                  |     |

| Figure 78. | FTP status register #21                                  |     |

| Figure 79. | FTP parity error status register                         |     |

| Figure 80. | Device FTP Configuration - Row_0                         |     |

| Figure 81. | Device FTP Configuration - Row_1                         |     |

| Figure 82. | Device FTP Configuration - Row_2                         |     |

| Figure 83. | Device FTP Configuration - Row_31                        |     |

| Figure 84. | Device FTP Configuration - Row_4                         |     |

| Figure 85. | Device FTP Configuration - Row_11                        |     |

| Figure 86. | Device FTP Configuration - Row_12                        |     |

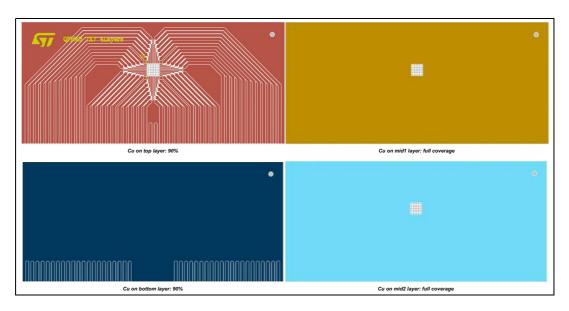

| Figure 87. | QFN-48L 7x7 on four-layer PCB                            | 133 |

| Figure 88. | Package outline                                          | 134 |

DS12879 Rev 5 9/141

Description L99LDLH32

## 1 Description

The L99LDLH32 is a monolithic 32-channel linear current regulator specifically designed for automotive exterior O/LED rear lighting applications. Thanks to the high side configuration of the output channels, the L99LDLH32 is suitable to drive OLED panel with common cathode. It guarantees up to 35 V output driving capability - to cover the OLED forward voltage wide spread - and features 32 regulated current sources able to provide from 1 mA up to 15 mA individually programmable current to drive each pixel of the OLED panel independently. As the other device in the family (L99LDLL16), the L99LDLH32 integrates a robust purely automotive CAN FD Light compatible communication interface which allows a high rate data transmission (up to 1 Mbit/s) and uses CAN FD structure for long frames. Besides the CAN FD Light compatible physical layer, the device also integrates the protocol handler, so no additional external devices are needed to facilitate communication with Commander ECU. The L99LDLH32 can operate in bus mode using CAN FD Light compatible interface or in stand-alone/fail-safe mode using internal Few Time Programmable (FTP) memory registers.

L99LDLH32 Introduction

## 2 Introduction

The L99LDLH32 is a monolithic 32-channel driver specifically designed for automotive O/LED lighting applications.

The device offers a high level of flexibility, thanks to its programmability through CAN FD Light compatible communication interface. This feature supports generic platform approaches, which require a software configurability of several parameters.

This differential robust interface offers a detailed diagnostic of the device itself - as well as of the controlled O/LED panel's pixel - and makes the device suitable for high data rate transmission, up to 1Mbit/s.

This device can operate in bus mode using CAN FD Light compatible interface or in standalone / fail-safe mode using internal few time programmable (FTP) memory registers.

As the device potentially controls safety critical functions such as tail light and turn indicators, built-in features are integrated in order to support a high level of functional safety on application level. The L99LDLH32 features a programmable timeout watchdog, a monitoring of the watchdog counter, a Limp Home (fail safe) function and 1 direct input.

Supplied directly from car battery, the L99LDLH32 guarantees up to 35 V output driving capability and features 32 regulated current sources able to provide from 1 mA up to 15 mA programmable current to drive each pixel of the O/LED panels. The current can be individually programmed using an integrated 8-bit DAC.

Each O/LED pixel can be supplied through one pre-regulator connected between battery and the integrated current source. The pre-regulated (as well as the battery) voltages are internally monitored by an 8-bit ADC, the results are stored in a dedicated result register.

The brightness can be adjusted separately for each channel through an 8-bit PWM exponential dimming control. An 8-bit linear global dimming can be superimposed to each channel individual PWM. A slow turn-on and turn-off time improves the system low noise generation performances.

The device supports control of up to 2 individual lighting functions. Each channel can be mapped or not mapped to the direct input as well as through the pre-regulated external supply voltages. This feature ensures the highest flexibility to control different lighting functions composed of different O/LED types, currents and string lengths.

Thanks to integrated high precision oscillators the device generates all relevant timing functions such as PWM frequency, duty cycle, trigger points for ADC conversion, phase shift, etc. autonomously. No external timers are required.

In the L99LDLH32, thanks to the integration of an 8-bit ADC, a complete diagnostic is also available: open load detection, short to ground detection.

Diagnostic thresholds are freely configurable for each function group. Moreover the user can configure the desired device reaction to detected faults, ensuring maximum flexibility for the application and sophisticated auto-recovery strategies.

The device features also the output gradual delay which avoids contemporary turning on of all the channels used for a specific light function, reducing the inrush current. To further improve EMI performances, the device implements an internal clock dithering to have a spread spectrum noise reduction.

DS12879 Rev 5 11/141

Downloaded from Arrow.com

Introduction **L99LDLH32**

> Thermal management is equipped with thermal warning (TW) and outputs thermal shutdown (TSD). The device performs an automatic thermal derating based on external NTC measurement as well on device junction temperature (T<sub>.I</sub>).

The supply voltage range is between  $V_{S\ MIN}$  and 40 V avoiding any additional load dump protection on power supply stage.

#### 2.1 **Device information**

DIN FAULT OUTx, VS ADC MUX NTC, Ti DIGITAL ENGINE OUT0 NTC WD & STDBY Fail Safe Current Sources & LED Fault Detection NTC / TJ OUT1 Dithering Derating SYNC\_I/O 8-bit PWM Phase Shift OUT2 CAN FD Handler VREF\_PREG Diagnostic 20MHz Logic & Registers Clock OUT31 RX/TX 5V CAN FD Logic Supply Non Volatile CAN FD PHY V3V3 L Regulator Regulator vs CAN\_H CAN\_L CS GND

Figure 2. Functional block diagram

L99LDLH32 Introduction

Figure 3. Application diagram - example

Introduction L99LDLH32

Figure 4. QFN48L 7x7 connection diagram

Table 1. Pin list description

| Pin#           | Name         | Description                                                                                                                                                                             |

|----------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1÷22,<br>39÷48 | OUTx         | Output Pin for 32-channels – High Side configuration                                                                                                                                    |

| 38             | VPRE_REG     | 1 pin for connection to external pre-regulator.                                                                                                                                         |

| 37             | VS           | Input supply pin of the IC. Connect VS to the car battery voltage.  Must be reverse protected (external diode).  Input supply for the 3.3 V and 5 V internal linear voltage regulators. |

| 36             | CS           | Chip Select input (test and programming mode entering)                                                                                                                                  |

| 35             | VREF_PRE_REG | 1 analog feedback voltage output pin. (provided as reference for VPRE_REG external Pre-regulator)                                                                                       |

| 34             | V3V3         | 3.3 V Regulator Output Voltage (Logic and I/O).<br>Connect a low ESR capacitor (1 µF) close to this pin.                                                                                |

| 33             | V5V          | 5 V Regulator Output Voltage (Communication interface supply).<br>Connect a low ESR capacitor (1 μF) close to this pin.                                                                 |

L99LDLH32 Introduction

Table 1. Pin list description (continued)

| Pin# | Name       | Description                                                                                                                                                                                            |

|------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32   | SYNC_I/O   | Synchronization input/output pin - floating when not used. (for PWM synchronization between several devices)                                                                                           |

| 31   | GND        | Ground connection.                                                                                                                                                                                     |

| 30   | CAN_H      | CAN bus high level voltage I/O                                                                                                                                                                         |

| 29   | CAN_L      | CAN bus low level voltage I/O                                                                                                                                                                          |

| 28   | DIN        | Direct Input pin                                                                                                                                                                                       |

| 27   | FAULT      | I/O pin for diagnostic. (1 Fault pin used for diagnostic)                                                                                                                                              |

| 26   | PWM_DC_1/2 | PWM DC setting pin (To select between two different PWM duty cycle setting, when internal PWM dimming in standalone mode is enabled).                                                                  |

| 25   | TEST       | Internal use only. To be connected to GND.                                                                                                                                                             |

| 24   | R_REF_DAC  | External resistor for DACs current reference It is suggested to use E96 series, 61.9 kΩ (1% tolerance standard thin film resistance, +/- 0.7%, 100 ppm/K, temperature spread in the range [-40÷100]°C) |

| 23   | NTC        | NTC pin for LEDs thermal control Connect an external NTC resistor (see <i>Table 78</i> )                                                                                                               |

| -    | EP         | Exposed Pad - suggested to connect to GND board plane, for better thermal dissipation                                                                                                                  |

## 3 Device supply concept

The L99LDLH32 IC is supplied through VS pin, connected to the car battery through an external diode for reverse polarity protection or to an external pre-regulator.

The supply voltage is in the range of  $[V_{S\_MIN} \div 40]$  V, avoiding any additional load dump protection on power supply stage. On top of that, no device reset will occur in the supply voltage range of  $[3 \div V_{S\_MIN}]$  V – to keep digital content during cold cranking pulse.

In that range –  $[3 \div V_{S\_MIN}]$  V - and till POR threshold  $(V_{3V3\_POR\_H})$  is not reached, full device protection is granted and digital part (register content and state machine) is kept alive.

An under-voltage threshold ( $V_{S\_UV}$ ) is implemented to avoid wrong output current due to low battery and, till device leaves the voltage range between under-voltage  $V_{S\_UV}$  and under-voltage reset  $V_{S\_UV\_RST}$  some parameters may deviate versus specified value.

L99LDLH32 Linear current sources

### 4 Linear current sources

## 4.1 General description

The L99LDLH32 features 32 high side linear current generators to regulate from 1 mA up to 15 mA current on the output channels.

The output channels can be put in parallel to address higher current than the programmable one and, for each channel, the current can be individually programmed by using an integrated 8-bit DAC. The output channels paralleling is allowed, provided that all these channels are controlled simultaneously. Moreover, in case of fault on one of the paralleled channels, it is recommended to deactivate all the channels belonging to the same fault bus (by setting FAULT\_REACT\_MODE bit to "0", see *Table 8*).

Supplied directly from car battery, the L99LDLH32 IC guarantees up to 35 V output driving capability - suitable to cover the OLED forward voltage wide spread.

Each O/LED string can be supplied by battery or through one pre-regulator connected between battery and linear current regulators.

The pre-regulated ( $V_{PRE\_REG}$ ) and battery ( $V_S$ ) voltages are internally monitored by an 8-bit ADC, the results are stored in a dedicated result register. The ADC is used also to monitor the device temperature ( $T_J$ ) as well as all the output channels. These channels are refreshed once per PWM period in on-state.

The minimum PWM on-time (vs PWM frequency) - to ensure a correct channel ADC reading - is t<sub>PWM\_ON\_OFF</sub> time (see *Table 77*). In any case, ADC will not perform any reading operation before a configurable blanking time (t<sub>DIAG\_BLANK</sub>, see *Table 79*) has elapsed. This blanking time is applied on the first channel turn on as well as on each PWM rising edge.

The ADC monitoring of all these parameters allows a complete diagnostic: open load detection, hard short circuit (versus ground), O/LED current derating in case of device temperature increasing.

The L99LDLH32 features an 8-bit logarithmic PWM for dimming control to adjust separately the brightness for each channel. A linear 8-bit global dimming dedicated for each function group mapped with Direct Input pin can be superimposed with the channel individual dimming.

A slow turn-on and turn-off time ( $t_{SR\_ON}$  and  $t_{SR\_OFF}$ ) of the channel improves the system low noise generation performances.

Moreover, this device features the output gradual delay (t<sub>GD</sub>) which avoids contemporary turning on of all the channels used for a specific light function, reducing the inrush current.

To further improve EMI performances, the device implements an internal clock dithering: more precisely, a triangular waveform (see the *Figure 57*) is applied to the embedded 20 MHz oscillator to have a spread spectrum noise reduction. Frequency modulation and deviation, along with rejection, are showed in the *Table 39*, for each of the eight possible configurations the user can set by means of 3 dedicated bits (DITHERING [2÷0], see FTP/RAM memory map, *Chapter 7*).

The L99LDLH32 integrates a thermal sensor block used to sense the device junction temperature (T<sub>J</sub>) as well as to detect thermal warning (TW) and thermal shutdown (TSD) thresholds, granting device protection in case of temperature increasing.

DS12879 Rev 5 17/141

Linear current sources L99LDLH32

The sensed junction temperature  $(T_J)$  is monitored by an 8-bit ADC with the aim of starting an automatic, downwards derating of the LED string current as soon as the  $T_{TW}$  -  $T_{TW\_HYS}$  threshold is reached. The derating ends when the 50% of the nominal LED current is reached, which corresponds to  $T_J$  = 165°C.

The 8-bit ADC is also used to monitor the voltage on the NTC pin, where an external resistor can be connected. If the monitored voltage – whose value depends on the temperature detected by the NTC resistor itself - reaches the  $V_{NTC\_TH}$  threshold (programmable by 3 bits, see *Table 78*), a downwards derating of the LED string current automatically starts, till 50% of the nominal LED current is reached. This corresponds to a NTC temperature 20°C higher than the one corresponding to  $V_{NTC\_TH}$ .

The monitoring of both T<sub>J</sub> and NTC voltage is contemporarily active.

The device can be controlled by a microcontroller via CAN FD Light compatible interface. Stand-alone operation (no microcontroller used) is also possible thanks to direct drive functionality and full configurability by FTP, which can be programmed (up to  $N_{\text{FTP}}$  cycles) in application via CAN FD Light compatible interface. To avoid unintentional writing, there is the possibility to lock any FTP area.

## 4.2 Channel current setting

The L99LDLH32 features 32 high side linear current generators to regulate from 1 mA up to 15 mA current on the output LED strings. The current can be individually programmed per channel through the 8-bit DAC (CURR\_SET\_CHx - see FTP/RAM memory map, Chapter 7)

The output channels can be put in parallel to address higher current than the programmable one.

Moreover, the value programmed in the 8-bit DAC per channel is stored in the RAM and can be reconfigured dynamically in Bus/Normal mode.

## 4.3 Channel driver drop-out voltage

To guarantee the regulation of the programmed channel current, a minimum output voltage (V<sub>OUTX</sub> <sub>DROP</sub>) across each current generator must be ensured.

The *Table 2* shows the minimum channel V<sub>OUTx\_DROP</sub> at the boundary of regulation region (output current is 3% less than the target value, output power MOS already in triode region). These measurements refer to only one output ON (if more channels are contemporary on, the drop voltage increases).

If on one hand a lower than minimum recommended  $V_{OUTx\_DROP}$  leads to a regulated current lower than the expected one, a too high  $V_{OUTx\_DROP}$  implies too high power dissipation.

To guarantee the current regulation and to optimize the power dissipation on each channel, in case of maximum current set on one channel and Tj at  $125^{\circ}$ C (worst case condition), the minimum output voltage drop (from device  $V_{PRE}$  REG to device OUTx) is 1.05 V.

L99LDLH32 Linear current sources

T<sub>J</sub> [°C]

VOUTX\_DROP [V]

125

1.05

25

1

-40

0.95

Table 2. Minimum channel drop-out voltage at max current vs T<sub>J</sub>

The L99LDLH32 features one analog pin (V<sub>REF\_PRE\_REG</sub>) providing a voltage proportional to the maximum output voltage of active channels plus the required drop voltage across the current regulator required for proper regulation (~1.4 V). This signal can be used in combination with an analogue discrete circuit to close directly the feedback loop with an external DC/DC converter.

For applications with a common DC/DC converter for several L99LDLH32 devices, the  $V_{REF\_PRE\_REG}$  output signal is buffered, therefore, it can be combined in wired-OR with  $V_{REF\_PREG\_REG}$  output signals from other devices to make sure only the highest reference voltage is fed back to the external DC/DC converter.

A dedicated Application Note is available for more information on this feature and how to use in application.

## 4.4 Channel output gradual delay

The L99LDLH32 features the output gradual delay, which consists in gradual turning on of the current generators. In case of driving several outputs simultaneously, the output gradual delay is applied in order to lower the current transients and improve device emissions. This feature can be activated – for all the channels - through one dedicated bit (OUT\_DELAY, see FTP/RAM memory map, *Chapter 7*).

In case one or more channels are not enabled, gradual delay is increased according to the number of channels turned OFF.

The Gradual Delay concept is valid in PWM mode as well: in this case, the PWM waveform is shifted and the gradual delay is applied also when channel is turned OFF.

The output gradual delay feature is valid both for Normal / Bus mode and Fail Safe / Stand Alone Mode. In this latter case, Direct Input (DIN) controls output channels as per FTP setting (DIN\_MAP\_CHx, 1bit - see FTP/RAM memory map, *Chapter 7*): it is suggested to apply the output gradual feature if minimum PWM on time is  $\geq$  20 µs. Otherwise, it is suggested to disable the feature by the dedicated bit.

The delay between each output is showed in Figure 5.

DS12879 Rev 5 19/141

Linear current sources L99LDLH32

Figure 5. Gradual delay concept

4

## 5 Functional description

## 5.1 Operating modes

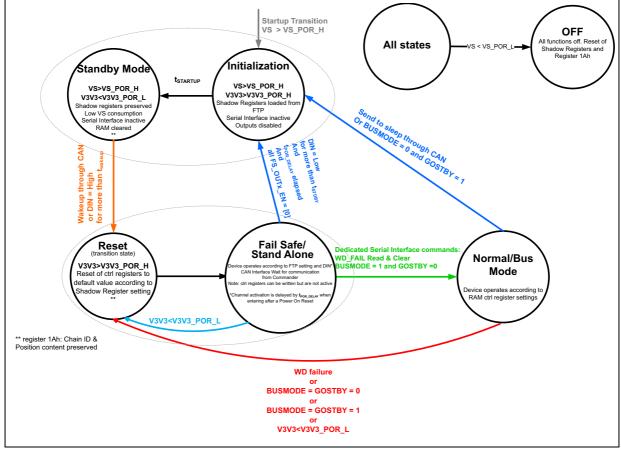

The L99LDLH32 features different operating modes. The related device states are reported in *Figure* 6 and well detailed in the following sub-chapters.

There are 2 bits for safe transition between different modes: BUSMODE and GOSTBY configuration bits (see RAM memory map, *Chapter 7*) are used to set, leave and check device Normal / Bus operating mode.

A dedicated pattern through CAN FD Light compatible interface is used to wake-up and to sleep the device. On top of that, device can be opportunely woken up or sent to sleep also through DIN pin as well as through BUSMODE / GOSTBY bits respectively.

As the device potentially controls safety critical functions such as tail light and turn indicators, built-in features are integrated to support a high level of functional safety on application level. The L99LDLH32 features a programmable timeout watchdog by WD\_CONF (2 bits - see FTP/RAM memory map, *Chapter 7*), a monitoring of the watchdog counter by WD\_STATUS (2 bits - see RAM memory map, *Chapter 7*), a Fail Safe and a Direct Input mode.

To keep the device in Normal / Bus mode, a watchdog trigger bit (WD\_TRIG<0> - see RAM memory map, *Chapter* 7) is cyclically toggled within the programmable watchdog timeout period. In case of watchdog failure, the WD\_FAIL bit (see RAM memory map, *Chapter* 7) is set and the device leaves Normal/Bus mode operation to enter Fail Safe mode.

DS12879 Rev 5 21/141

Figure 6. Device state diagram

Note:

Partial networking feature is not supported by the device. Mixed state on the bus has to be avoided. In case devices are sent to initialization / stand by mode NOT through a broadcast "send to sleep" command, the first UNICAST response frame of the device after wakeup has to be ignored.

### 5.1.1 Stand-by mode

The pre-requisite for this mode is:

Device in initialization phase

The device enters Standby mode under the following condition:

• By default, once the device is powered ( $V_S$  present) and leaves initialization phase ( $V_S > V_{S\ POR\ H}$ )

The Standby mode characteristics are:

- Shadow register <sup>(a)</sup> preserved

- RAM cleared

- V<sub>S</sub> > V<sub>S\_POR\_H</sub>

- $V_{3V3} < V_{3V3 POR L}$

- V<sub>S</sub> low consumption

- CAN FD Light compatible Interface inactive

77

The device leaves this mode if:

• Wake-up pattern is sent through CAN FD Light compatible interface

Or

DIN High for a time t > t<sub>WAKEUP</sub>

#### 5.1.2 Initialization

The device enters Initialization phase under the following conditions:

• Sleep pattern sent through CAN FD Light compatible interface

Or

One frame setting bit (BUSMODE,GOSTBY) = (0,1)

Or

DIN Low for a time t > t<sub>STDBY</sub> AND power on reset delay time (t<sub>POR\_DELAY</sub>) elapsed AND channels NOT set permanently ON in Fail Safe (FS\_OUT\_ENx [0])

The Initialization mode characteristics are:

- V<sub>S</sub> > V<sub>S POR H</sub>

- $V_{3V3} > V_{3V3 POR H}$

- Shadow register<sup>(a)</sup> loaded from FTP

- Outputs disabled

- CAN FD Light compatible Interface inactive

The device leaves automatically Initialization mode entering Standby mode after t<sub>STARTUP</sub>.

#### 5.1.3 Reset mode

The device enters Reset mode (transition state) under the following conditions:

- By default, once the device leaves Standby mode

- If device state is in Fail Safe / Stand Alone mode, when  $V_{3V3} < V_{3V3\ POR\ L}$

- If device state is Normal / Bus mode, when one of the following events occur:

- Watchdog failure

- One frame setting bits (BUSMODE,GOSTBY) = (0,0)

- One frame setting bits (BUSMODE,GOSTBY) = (1,1)

- $V_{3V3} < V_{3V3\_POR\_L}$

The Reset mode characteristics are:

- $V_{3V3} > V_{3V3}_{POR}$

- Reset of control register to default values according to the shadow register setting

- CAN FD Light compatible Interface inactive

The device leaves automatically Reset mode and enters Limp Home after 400 ns (typically).

577

DS12879 Rev 5 23/141

Shadow registers are RAM copy of FTP registers, added to speed-up transition between Standby to Fail Safe modes and Fail Safe to Normal modes.

#### 5.1.4 Fail Safe / Stand Alone mode

The device enters Fail Safe / Stand Alone mode automatically 400 ns (typically) after Reset mode.

Fail Safe / Stand Alone mode characteristics are:

- Device operates according to FTP setting and Direct Input

- CAN FD Light compatible Interface wait for communication from Commander

Note: Control registers can be written but are not active

When the device leaves this mode, it can enter Standby or Normal/Bus mode.

If the device receives the following two frames:

- The first frame reads and clears the WD\_FAIL bit (bit <15>, Device status register #3)

- The second frame (not necessarily directly consecutive to the first frame) sets BUSMODE = 1 and GOSTBY = 0 (bit <0-1>, Device configuration register #4) the device enters Bus mode.

If WD\_FAIL Read & Clear operation is not performed (and in case of WD\_FAIL = 1) device state will remain in fail safe but control register will be reset to default value.

Upon the condition:

DIN Low for a time t > t<sub>STDBY</sub> AND power on reset delay time (t<sub>POR\_DELAY</sub>) elapsed AND all channels NOT set permanently ON in Fail Safe (all FS\_OUT\_ENx bits = [0])

the device enters Standby mode.

Upon the condition:

•  $V_{3V3} < V_{3V3}_{POR}_{L}$

the device enters Reset transition mode:

- RAM content is reloaded with shadow register content

- device will remain in FAILSAFE state with GSB.RSTB = 1, to inform the user about any potential write operations already performed in Fail Safe hast to be repeated.

#### 5.1.5 Normal / Bus mode

The device enters the Normal / Bus mode if the device receives the following frames:

- The first frame reads and clears the WD FAIL bit (bit <15>, Device status register #3)

- The second frame sets BUSMODE =1 and GOSTBY = 0 (bit <0-1>, Device configuration register #4)

If WD\_FAIL Read & Clear operation is not performed (and in case of WD\_FAIL = 1) device state will remain in fail safe but control register will be reset to default value.

In this mode the device operates according to its RAM register settings. Direct Input access can be Enabled/Disabled by a dedicated bit on DIN pin (DIN\_EN - see RAM memory map, *Chapter 7*). In order to maintain the device in Normal / Bus mode the watchdog toggle bit has to be refreshed within the watchdog timeout time-frame.

The device leaves Normal / Bus mode, entering initialization state (to refresh shadow register with FTP configuration), upon the following conditions:

Send-To-Sleep pattern is sent through CAN FD Light compatible interface

**47**/

or

BUSMODE =0 and GOSTBY =1

The device leaves Normal / Bus mode, entering reset transition state, upon the following conditions:

- Watchdog failure

- One frame setting bits (BUSMODE,GOSTBY) = (0,0)

- One frame setting bits (BUSMODE,GOSTBY) = (1,1)

- $V_{3V3} < V_{3V3}_{POR_L}$ :

- RAM content reloaded with shadow register content.

- Device will reach FAILSAFE state with GSB.RSTB = 1 to inform the application about the reason of this transition.

## 5.2 Programmable functions

#### 5.2.1 Direct drive and functional configuration

#### **Output channels assignment**

The L99LDLH32 features 1 Direct Input pin (DIN).

Each output can be assigned to DIN or to none by 1 dedicated FTP bit (DIN\_MAP\_CHx - see FTP/RAM memory map, *Chapter 7*) per output channel, as showed in *Table 3*.

Table 3. Output channel assignment to DIN

| DIN_MAP_CHx <0> | Output channel status |

|-----------------|-----------------------|

| 0               | OUTx NOT mapped       |

| 1               | OUTx mapped on DIN    |

In Fail Safe / Stand Alone mode, the outputs are always controlled by DIN - according to the assignment defined in *Table 3* - except the case when the channel is programmed permanently ON by dedicated FTP bits (FS\_OUT\_ENx<0>- see FTP/RAM memory map, *Chapter 7*). When this bit is set, the related output channel "x" is permanently active in Fail Safe / Stand Alone mode regardless of the DIN – see *Table 4*.

Table 4. Output channel in Fail Safe / Stand Alone mode

| FS_OUT_ENx <0> | Output Channel Status             |

|----------------|-----------------------------------|

| 0              | OUTx according to DIN_MAP_CHx <0> |

| 1              | OUTx permanently ON               |

In case the channel is configured ON in Fail Safe / Stand Alone mode, a configurable delay of the output activation after power on reset ( $t_{POR\_DELAY}$ ) prevents any undesired flashing while configuring the devices and entering Normal / Bus mode. In other words, after power on reset, all outputs are kept off till power on reset delay time elapses to prevent any flashing during the time needed to enter in Bus mode operation.

DS12879 Rev 5 25/141

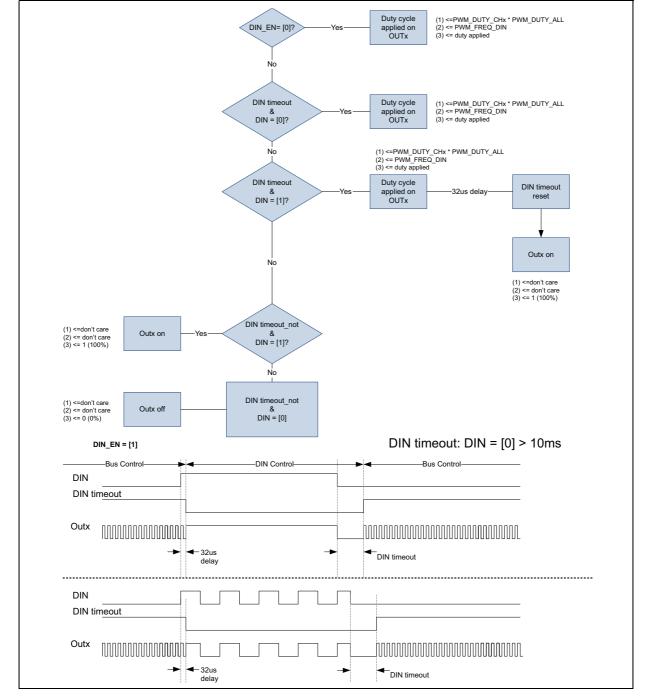

In Normal / Bus mode, the direct input access to outputs can be enabled /disabled for each channel. If enabled (DIN\_EN), bus control is applied when DIN = 0. If DIN is set (DC or PWM) the bus control is automatically disabled (after elapsing of  $t_{\text{FILTER}}$ ) and overtaken by DIN (the direct input has priority versus Bus control). Bus control is re-established upon  $t_{\text{BUS CONTROL}}$  elapse after last falling edge on DIN.

For DIN, a read-back information is available. It is forecasted one status bit (DIN\_STATUS<0> - see RAM memory map, *Chapter 7*) to support functional safety.

The L99LDLH32 features also 1 V<sub>PRE\_REG</sub> pin, to supply the current sources through an external pre-regulator.

### 5.2.2 PWM operation

In the L99LDLH32, the brightness of LED strings can be modified by PWM.

The PWM dimming could be performed in different ways:

- Through serial bus

- Through direct input

- Through power line

When PWM operation is managed through the serial bus, there are 3 bits (PWM\_FREQ\_DINx, see FTP/RAM memory map, *Chapter 7*) to configure the PWM frequency of the channels.

The PWM frequency range is reported in the below table.

| PWM_FREQ_DINx [2÷0] |       | [2÷0] | PWM_FREQ [Hz] |

|---------------------|-------|-------|---------------|

| bit 2               | bit 1 | bit 0 | FWM_FREQ [HZ] |

| 0                   | 0     | 0     | 200           |

| 0                   | 0     | 1     | 300           |

| 0                   | 1     | 0     | 400           |

| 0                   | 1     | 1     | 500           |

| 1                   | 0     | 0     | 700           |

| 1                   | 0     | 1     | 1000          |

| 1                   | 1     | 0     | 1200          |

| 1                   | 1     | 1     | 1400          |

Table 5. PWM frequency range

For all the non-mapped output channels (see *Table 3: Output channel assignment to DIN*), the PWM frequency and duty cycle will be the same as the DIN mapped channels (as reported in the *Dimming with direct input in Fail Safe/Stand Alone Mode* section).

#### Dimming with serial bus

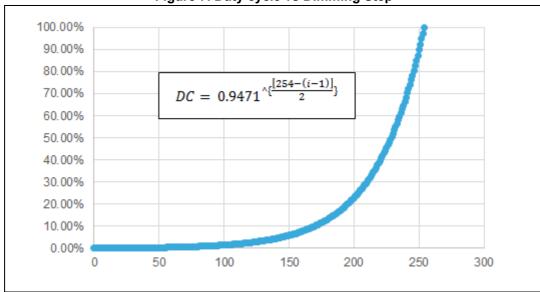

In the L99LDLH32, each channel can be individually dimmed on an 8-bit exponential duty cycle to adequate LED brightness change to human eye light perception, giving in this way the impression of brightness linear variation. The exponential law used to calculate the dimming steps is the following:

$$ton_{i} = PWM_{period} \cdot \alpha \left\{ \frac{[N - (i-1)]}{2} \right\}$$

Where ton is the LED ON-time during step number "i",  $1 \le i \le 255$ ,  $\alpha \approx 0.9471$ , N=254.

For the step number "i" = 0, DC is set to "0".

The function of duty cycle vs 8-bit PWM\_DUTY\_CHx setting is shown in the following graph. The minimum duty cycle is clamped to 0.1% in any case.

Figure 7. Duty cycle vs Dimming Step

The duty cycle is configurable through serial bus (PWM\_DUTY\_CHx, 8 bits per channel – see RAM memory map, *Chapter 7*) and the programmed value is stored in the RAM. The individual duty cycle per channel can be superimposed by a linear 8-bit global dimming PWM\_DUTY\_ALL (applicable for outputs mapped to DIN). The resulting duty cycle is the product of PWM\_DUTY\_CHx\*PWM\_DUTY\_ALL. Global dimming is not available for function group not mapped to DIN. If global dimming is not desired, the PWM\_DUTY\_ALL register has to be programmed with FFh.

Direct Input access to outputs can be enabled or disabled for each channel separately in Bus / Normal Mode. If Direct Input is enabled (by DIN\_EN configuration bit – see RAM memory map, *Chapter 7*), bus control is applied when DIN = 0. In case of DIN <> 0, the bus control is automatically disabled (after  $t_{\text{FILTER}}$  time) and overtaken by DIN: the DIN input control has priority versus bus control. After a timeout higher than  $t_{\text{BUS}\_\text{CONTROL}}$  after the last falling edge on DIN, the bus control is reactivated. The characteristics of the function group is illustrated in the following flow chart.

577

DS12879 Rev 5 27/141

Figure 8. PWM concept for DIN function group

The PWM frequency and phase relation of several devices can be synchronized versus each other through the SYNC\_I/O pin. There is one dedicated bit (SYNC I/O\_M/S - see FTP/RAM memory map, *Chapter 7*) to configure the device in Provider [1] or Consumer [0] mode.

In Provider mode, the Clock frequency with scaler and phase signal is transferred to the SYNC\_I/O line. In Consumer mode, clock frequency and phase signal on the SYNC\_I/O line are used to synchronize its own clock. Consequently the phase relation among several

devices can be configured (through FTP only) by PHASE\_DEV bits (3-bits - see FTP/RAM memory map, *Chapter 7*).

Table 6. PWM phase shift (in Consumer mode)

| PHASE_DEV [2÷0] |       | 0]    | DIMM DUACE CHIET (vol |

|-----------------|-------|-------|-----------------------|

| bit 2           | bit 1 | bit 0 | PWM_PHASE_SHIFT [µs]  |

| 0               | 0     | 0     | 0                     |

| 0               | 0     | 1     | 15                    |

| 0               | 1     | 0     | 30                    |

| 0               | 1     | 1     | 45                    |

| 1               | 0     | 0     | 60                    |

| 1               | 0     | 1     | 75                    |

| 1               | 1     | 0     | 90                    |

| 1               | 1     | 1     | 105                   |

The internal PWM clock oscillator can be reset by PWM\_SYNC bit (see RAM memory map, *Chapter 7*) in order to start the PWM period at a known phase relation.

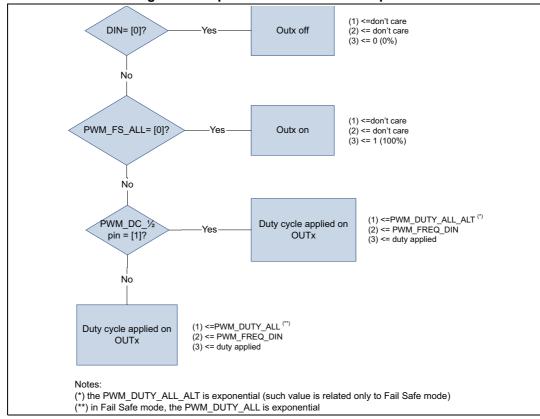

#### Dimming with direct input in Fail Safe/Stand Alone Mode

The L99LDLH32 features the channel output PWM dimming through direct input control.

The Direct Input controls the output channels as per FTP setting (see *Table 3: Output channel assignment to DIN*).

There is 1 configuration bit (PWM\_FS\_ALLx\_EN - see FTP/RAM memory map, *Chapter 7*) for enabling internal PWM dimming in Stand Alone / Fail Safe mode.

The PWM signal is deactivated by related DIN: if DIN = 0, the outputs are off; otherwise the outputs follow internal PWM signal.

In Fail Safe / Stand Alone mode, an alternative duty cycle for DIN function group can be set by an additional 8-bit register (PWM\_DUTY\_ALLx\_ALT - see FTP/RAM memory map, *Chapter 7*). This alternative duty cycle can be activated by dedicated pin PWM DC 1/2.

If this pin is set at "1", the alternative register values will be considered, otherwise, the default register PWM\_DUTY\_ALLx will be the reference.

The channel PWM control concept in Fail Safe / Stand Alone Mode is illustrated in the following flow chart.

47/

DS12879 Rev 5 29/141

Figure 9. Output & PWM control concept DIN

#### Dimming with power line

In the L99LDLH32, PWM dimming through power line is possible by rectifying the  $V_S$  supply and connecting the Power Line to the Direct Inputs through resistor divider. A buffer capacitor on  $V_S$  supply pin has to be able to supply the device during PWM off state to keep it in operating mode without any reset.

When dimming through power line is performed, PWM frequency is expected in the range of  $[100 \div 200 \text{Hz}]$  with 5% minimum duty cycle. The start-up time for light function availability is  $t_{\text{STARTUP PWM VS}}$ .

The  $t_{STARTUP\_PWM\_VS}$  parameter is the time needed for device startup, from device power up (presence of  $V_S$ ) to the channel activation.

## 5.3 Protections and diagnostic

### 5.3.1 Diagnostic availability and validation - strategy

The L99LDLH32 performs a configurable blanking time for the diagnosis, which is applied on the first channel turn on as well as on each PWM rising edge.

There are 2 configuration bits per function group (DIAG\_BLANK\_x - see FTP/RAM memory map, *Chapter 7*) to set the desired blanking time before validating any fault related to the channel.

The possible configuration is reported in the table below.

DIAG\_BLANK\_x [1÷0]

t<sub>DIAG\_BLANK\_x</sub> [us]

00

50

01

100

10

150

11

200

Table 7. Diagnostic blanking time

After  $t_{DIAG\_BLANK\_x}$  elapses, a failure counter starts and any channel fault is validated after N\_Fails number of detected failures (also non-consecutive). The N\_Fails readings are kept in memory up to N\_Fails\_reset (number of consecutive NOT failures detection), then the counter will be reset.

Diagnostic validation strategy is applied for any possible load fault: O/LED short to ground, open string, short to  $V_{PRE\_REG}$ . If the on-time of any channel is shorter than the configured blanking time, the device automatically disables fault detection on that channel and sets the pre-regulator voltage feedback to maximum.

#### 5.3.2 Fault bus capability

In the L99LDLH32, there is 1 fault pin with "Fault Bus" capability: 1 open drain fault pin (FAULT) is associated with 1 Direct Input (DIN), output channels are mapped according to DIN MAP CHx.

The fault pin is bidirectional, active low. Several fault pins of several devices can be connected together to have a common fault bus associated to a particular light function. This allows an automatic deactivation of complete light function in case of fault on single O/LED string only, according to the selected Fault reaction mode.

There is, in fact, 1-bit (FAULT\_REACT\_MODEx - see FTP/RAM memory map, *Chapter 7*) for fault reaction mode configuration:

FAULT\_REACT\_MODE <0> Fault Reaction Mode

0 Fault on one string => all strings of same fault bus deactivated

1 Fault on one string => no action on other strings

Table 8. Fault reaction mode

### 5.3.3 Thermal warning

The L99LDLH32 integrates a temperature warning with one threshold.

If the junction temperature  $(T_J)$  of the device – read by internal ADC - rises above the warning temperature threshold  $(T_{TW})$ , the thermal warning status bit (TW - see RAM memory map, Chapter 7) is set.

Thermal warning is also reported in the Global Status Byte register, in particular Global Warning (GW) bit is set.

57/

DS12879 Rev 5 31/141

As soon as the  $T_J$  drops below the thermal warning reset threshold ( $T_{TW}$ - $T_{TW\_HYS}$ ), the corresponding thermal warning status bit is automatically cleared.

Even if a temperature warning is detected, device as well as output channels are kept functional.

#### 5.3.4 Thermal shutdown

If the junction temperature of the L99LDLH32 rises above the shutdown temperature threshold ( $T_{TSD}$ ), a thermal shutdown event is detected: all the output channels are switched off and the thermal shutdown status bit (TSD – see RAM memory map, *Chapter 7*) is set. The Fault pin is pulled low.

Thermal shutdown event is also reported in the Global Status Byte register, in particular Functional Error 1 (FE1) bit is set.

As soon as the  $T_J$  drops below the thermal shutdown reset threshold ( $T_{TSD}$ - $T_{TSD}$ -HYS), the output channels are automatically re-activated. The corresponding thermal shutdown status bit ( $T_{TSD}$ ) is automatically cleared as soon as  $T_J$  drops below the thermal shutdown reset threshold, contemporarily to channel re-activation.

In case of thermal shutdown, device logic and state machine remain active.

#### 5.3.5 LED current derating

In case of temperature increasing, the device performs an automatic LED current derating based on the measurement of external NTC voltage as well as on the internal device temperature (T<sub>1</sub>).

An integrated thermal sensor is used to sense the device junction temperature  $(T_J)$  as well as to detect thermal warning (TW) and thermal shutdown (TSD) thresholds, granting device protection in case of temperature increasing. The sensed junction temperature  $(T_J)$  is monitored by an 8-bit ADC with the aim of starting an automatic, downwards derating of the LED string current as soon as the  $T_{TW}$  -  $T_{TW\_HYS}$  threshold is reached. The derating ends when the 50% of the nominal LED current is reached, which corresponds to  $T_J$  = 165°C.

The 8-bit ADC is also used to monitor the voltage on the NTC pin, where an external resistor can be connected. If the monitored voltage – whose value depends on the temperature detected by the NTC resistor itself - reaches the  $V_{NTC\_TH}$  threshold (programmable by 3 bits, see *Table 78*), a downwards derating of the LED string current automatically starts, till 50% of the nominal LED current is reached. This corresponds to a NTC temperature 20°C higher than the one corresponding to  $V_{NTC\_TH}$ .

The monitoring of both  $T_J$  and NTC voltage is contemporarily active. The actual derating is determined by the parameter which would require the most severe derating.

#### 5.3.6 VS under voltage lockout

If the  $V_S$  supply falls below  $V_S$  under-voltage threshold ( $V_S \cup V$ ), the device will be deactivated - regardless of the operating mode – and the FAULT pin will be pulled low.

This feature is implemented, in order to avoid any operation outside the allowed  $V_S$  operating range.

If Supply under-voltage event is detected, the related flag (V<sub>S\_UV</sub> – see RAM memory map, *Chapter 7*) is set and reported also in the Global Status Byte register, where Device Error (DE) bit is set.

As soon as the  $V_S$  supply crosses the under-voltage reset threshold ( $V_{S\_UV\_RES}$ ) the device is automatically re-activated.

#### 5.3.7 Channel output - LED short circuit detection

The L99LDLH32 performs the LED short circuit fault detection – both in Bus mode as well as Fail Safe / Stand Alone mode - based on voltage monitoring across the channel output voltage: the detection is done by comparing the absolute output voltage versus a configurable threshold.

The device features 2 groups of configurable short circuit threshold ( $V_{SHT\_CH\_TH}$  and  $V_{SHT\_CH\_DIN\_TH}$ , as showed in *Table 9*). This configurability allows short detection of one or more LEDs within the string connected to a given channel mapped according to DIN\_MAP\_CHx <0>.

Table 9. LED short circuit threshold - grouping

The short circuit detection can be enabled /disabled through the SHT\_DET\_EN bit (see FTP/RAM memory map, *Chapter 7*): if this bit is equal to "0", the short circuit detection is disabled, otherwise, the short circuit detection is enabled. In this latter case, two different scenarios are possible: to enable or disable the channel output deactivation in case of short circuit, by one dedicated bit (SHT\_OFF\_x – see FTP/RAM memory map, *Chapter 7*). If SHT\_OFF\_x bit is set to 0, the faulty channel output is kept active in case of short circuit, otherwise the faulty channel is latched off. The channel is recognized in short circuit as soon as its output voltage - read by ADC - is less than the specified short circuit threshold (V<sub>SHT CH TH</sub> or V<sub>SHT CH DIN TH</sub>, see *Table 9*).

In Bus mode, the faulty channel output is latched off and the dedicated fault bit (SHT\_CHx – see RAM memory map, *Chapter 7*) is set. The channel output can be restarted and the fault bit will be cleared by sending a read & clear command to address 28. Selective bitwise read & clear is possible.

In case of fault in Fail Safe / Stand Alone mode:

- for the channels configured with FS\_OUT\_EN = 0, the output is latched off and it is cleared upon falling edge of DIN with t<sub>DIN\_FALL</sub> settling time. This means that fault is not cleared during PWM dimming with PWM off-time shorter than t<sub>DIN\_FALL</sub> time.

- for the channels configured with FS\_OUT\_EN = 1, after elapsing the t<sub>AUTORESTART</sub>, the faulty channel is automatically re-activated and the SHT\_CHx bit is cleared.

If outputs are permanently enabled by FS\_OUT\_ENx = [1], in case of short circuit, they will be latched and the latch can be cleared only through a power on reset condition.

For all (and only) those channels mapped on DIN (DIN\_MAP\_CHx = 01), the L99LDH32 features the indication of short circuit on FAULT pin. If the bit SHT\_EN (see FTP/RAM memory map, *Chapter 7*) is equal to "0", the short circuit fault detection is NOT propagated on FAULT bus; whilst if SHT\_EN = 1, the short circuit of the faulty channel is indicated on associated FAULT bus (pulled low).

The channel short event is also reported in the Global Status Byte register, in particular Functional Error 2 (FE2) bit is set.

577

DS12879 Rev 5 33/141

Then, for both mapped and non-mapped channels, according to the fault reaction mode configuration bit (see *Table 8*), an automatic deactivation of the complete light function respectively of the faulty channel only is performed.

The flow chart reported in *Figure 10* shows how the device manages the faulty channel and the channels corresponding to DIN\_MAP as well as the fault pin handling.

DS12879 Rev 5

34/141

Figure 10. LED short circuit fault management

47/

DS12879 Rev 5 35/141

### 5.3.8 Channel output - short circuit to GND

The L99LDLH32 features the output channel voltage shortage to GND - both in Bus mode as well as Fail Safe / Stand Alone mode - based on voltage monitoring across the channel output voltage: the detection is done by comparing the absolute output voltage versus a fixed threshold ( $V_{OUT\ SHT\ GND\ TH}$ ).

The short circuit to GND detection is masked when the O/LED supply voltage is below a power good threshold ( $V_{PG\ TH\ VPRE\ REG}$ ).

When the channel output voltage is lower than the  $V_{OUT\_SHT\_GND\_TH}$  threshold, a shortage between a channel output and GND is detected and the related channel bit (OUT\_SHT\_GND\_CHx- see RAM memory map, *Chapter 7*) is set. In case the LED short detection threshold (either  $V_{SHT\_CH\_TH}$  or  $V_{SHT\_CH\_DIN\_TH}$ ) is set lower than the channel short to ground threshold ( $V_{OUT\_SHT\_GND\_TH}$ ), this latter protection has the highest priority.