# 48 Gbps HDMI 1:1 Transceiver

**ADV7671**

**ADI Preliminary and Confidential**

### **FEATURES**

1-input, 1-output 1 HDMI transceiver 8k60 YCbCr 4:2:0 12-bit video support 8k30 RGB/YCbCr 4:4:4 12-bit video support 4k120 4:4:4 12-bit high frame rate video support **HDMI** receiver Up to 48 Gbps FRL support Up to 18 Gbps TMDS video support eARC transmitter **On-chip 4 block EDID SRAM managed by internal MCU** EDID access in low power standby mode **HDMI transmitter** Up to 48 Gbps FRL support Up to 18 Gbps TMDS video support eARC receiver High-bandwidth Digital Content Protection (HDCP) HDCP 1.4, 2.2 and 2.3 support Independent HDCP on each transmitter and receiver port Fully integrated HDCP 1.4, 2.2, 2.3 repeater modes HDCP sink mode for audio playback **On-chip key storage in OTP** Audio Audio extraction port Audio insertion port 8-Channel 192 kHz 24-bit PCM audio support 24.576 Mb IEC61937 compressed audio support eARC transmitter or receiver with multichannel PCM, **HBR** audio and ARC support Video FRL to TMDS and TMDS to FRL modes conversion Variable Refresh Rate (VRR), Fast Vactive (FVA) and Auto Low Latency Mode (ALLM) support

Dynamic HDR passthrough support including HDMI Dynamic HDR metadata, HDR10+ and Dolby Vision™

DSC 1.2a pass-through support

#### APPLICATIONS

TV Home Theater Industrial Switching

### **GENERAL DESCRIPTION**

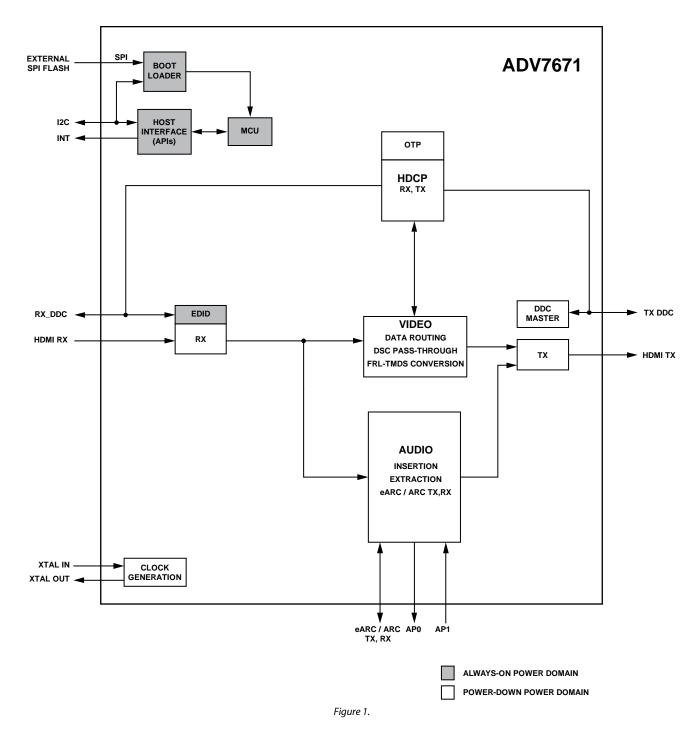

The ADV7671 is a High-Definition Multimedia Interface (HDMI<sup>®</sup>) transceiver.

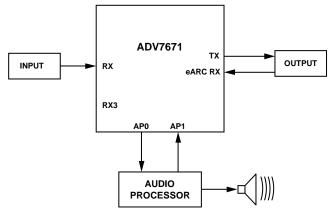

The ADV7671 supports 48 Gbps FRL and 18 Gbps TMDS video rates and provides a HDMI receiver port, a HDMI transmitter port, an audio input port, an audio output port, and an enhanced audio return channel (eARC) interface.

The HDMI receiver and transmitter support 8k60 YCbCr 4:2:0 12-bit video, 8k30 RGB 12-bit video and 4k120 RGB 12-bit high frame rate video.

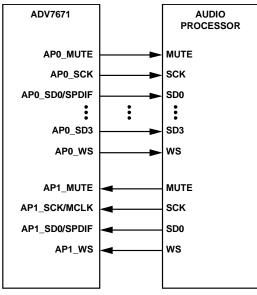

The audio input port and audio output port each support 8-channel 192 kHz PCM and compressed audio formats, including high bitrate formats.

The eARC interface can be configured as either an eARC transmitter or an eARC receiver. The eARC interface supports 8-channel 192 kHz PCM audio and high bit rate audio (HBR) compressed audio formats including Dolby TrueHD<sup>™</sup> and DTS-HD<sup>™</sup>. Audio return channel (ARC) is also supported on the eARC interface.

The ADV7671 supports pass-through of Display Stream Compression (DSC) 1.2a data and High Dynamic Range (HDR) metadata pass-through for HDMI dynamic HDR, HDR10+ and Dolby Vision<sup>™</sup>.

The ADV7671 implements the HDCP 2.3 specification to protect the delivery of premium content. HDCP 2.3 is applied in transmitter, receiver, and repeater configurations. HDCP 2.3 is backwards compatible with HDCP 2.2. HDCP 1.4 is also supported to provide interoperability with legacy devices.

The ADV7671 is configured via I<sup>2</sup>C using a high-level host controller interface (API).

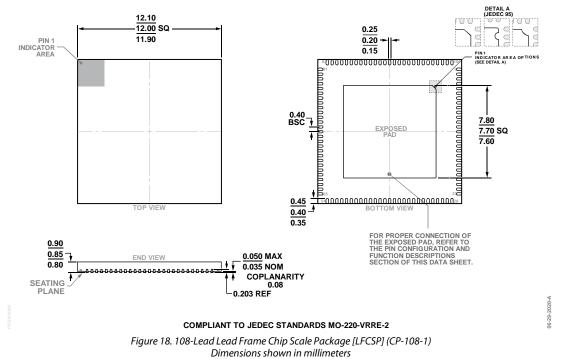

The ADV7671 is provided in a 108-Lead Lead Frame Chip Scale Package (LFCSP) with exposed paddle and is specified over the 0°C to 70°C temperature range.

Customers that wish to sample or purchase the ADV7671 must be licensed HDMI 2.1 adopters listed at HDMI.org and licensed HDCP 2.x adopters listed at Digital-CP.com.

Rev. SPrA

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2020 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# TABLE OF CONTENTS

| DSCFeatures                                   |

|-----------------------------------------------|

| Applications1                                 |

| General Description                           |

| Revision History 2                            |

| Functional Block Diagram                      |

| Specifications                                |

| Digital, DC and AC Specifications4            |

| Power Specifications - Preliminary5           |

| Timing Specifications - Preliminary6          |

| Absolute Maximum Ratings10                    |

| Thermal Resistance10                          |

| Electrostatic Discharge (ESD Ratings)10       |

| ESD Caution10                                 |

| Pin Configuration and Function Descriptions11 |

| Theory of Operation15                         |

| Power Domains15                               |

| HDMI Receiver15                               |

| HDMI Transmitter                              |

| HDCP Repeater15                               |

| HDCP15                                        |

| Audio15                                       |

### **REVISION HISTORY**

10/20—Revision SPrA: Initial Preliminary Version

| eARC17                                                  |

|---------------------------------------------------------|

| Boot Loader17                                           |

| Microcontroller Unit17                                  |

| Host Interface17                                        |

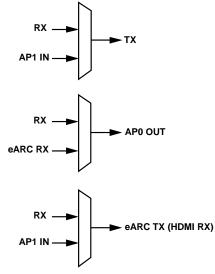

| ADV7671 Use Case                                        |

| ADV7671 Soundbar Application18                          |

| Video Formats                                           |

| Supported Video Input Formats19                         |

| Supported Video Output Formats                          |

| TMDS Transmitter Channel Swap and Polarity Inversion 23 |

| Applications Information24                              |

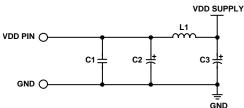

| Power Supply Decoupling                                 |

| Layout Guidelines                                       |

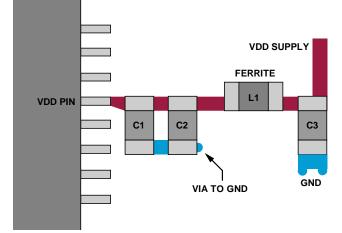

| Crystal Circuit                                         |

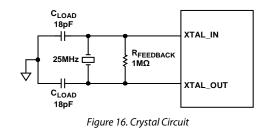

| SBVCC_5V Measurement                                    |

| ESD Protection                                          |

| EMI Considerations                                      |

| ePAD Requirements                                       |

| Outline Dimensions                                      |

| Ordering Guide                                          |

|                                                         |

### FUNCTIONAL BLOCK DIAGRAM

### **SPECIFICATIONS**

$T_{\rm MIN}$  to  $T_{\rm MAX}$  = 0°C to +70°C.

Refer to Table 2 for  $V_{\text{MIN}}$  to  $V_{\text{MAX}}$  conditions.

All specifications are preliminary and subject to change.

### DIGITAL, DC AND AC SPECIFICATIONS

### Table 1.

| Parameter                                       | Test Conditions/Comments                          | Min T | yp Max | Unit |

|-------------------------------------------------|---------------------------------------------------|-------|--------|------|

| DIGITAL INPUTS                                  |                                                   |       |        |      |

| Input Voltage, High (VIH)                       |                                                   | 2.0   |        | V    |

| Input Voltage, Low (VIL)                        |                                                   |       | 0.8    | V    |

| I <sup>2</sup> C Inputs                         |                                                   |       |        |      |

| Low to High Threshold (V <sub>TH + I2C</sub> )  |                                                   | 2.0   |        | V    |

| High to Low Threshold (V <sub>TH – I2C</sub> )  |                                                   |       | 0.8    | V    |

| Display Data Channel (DDC) Inputs               |                                                   |       |        |      |

| Low to High Threshold (V <sub>TH + DDC</sub> )  |                                                   | 3.0   |        | V    |

| High to Low Threshold (V <sub>TH - DDC</sub> )  |                                                   |       | 1.5    | V    |

| DIGITAL OUTPUTS                                 |                                                   |       |        |      |

| Output Voltage, High (VOH)                      | Output high current ( $I_{OH}$ ) = 8 mA           | 2.4   |        | V    |

| Output Voltage, Low (VOL)                       | $I_{OH} = -8 \text{ mA}$                          |       | 0.4    | V    |

| I <sup>2</sup> C Open-Drain Outputs             |                                                   |       |        |      |

| Low Level Output Voltage (V <sub>OL_I2C</sub> ) | $I_{OL} = -3 \text{ mA}$                          |       | 0.4    | V    |

| Open Drain DDC Outputs                          |                                                   |       |        |      |

| Low Level Output Voltage (V <sub>OL_DDC</sub> ) | $I_{OL} = -3 \text{ mA}$                          |       | 0.4    | V    |

| Open Drain INT Output                           |                                                   |       |        |      |

| Low Level Output Voltage (V <sub>OL_INT</sub> ) | $I_{OL} = -3 \text{ mA}$                          |       | 0.4    | V    |

| DC SPECIFICATIONS                               |                                                   |       |        |      |

| Input Leakage Current, I                        | High Impedance                                    | -10   | +10    | μΑ   |

|                                                 | High Impedance with pull-down resistor            | -10   | +100   | μΑ   |

| Output Leakage Current, IoL                     | High Impedance                                    | -10   | +10    | μΑ   |

|                                                 | High Impedance with pull-down resistor            | -10   | +100   | μΑ   |

|                                                 | High Impedance with pull-up resistor <sup>1</sup> | -10   | +10    | μΑ   |

| 8 mA Digital Output Drive (LVTTL)               | $V_{OUT} = 2.4 V$                                 | 8     |        | mA   |

|                                                 | $V_{OUT} = 0.4 V$                                 | 8     |        | mA   |

| AC SPECIFICATIONS                               |                                                   |       |        |      |

| TMDS Input Clock Frequency                      |                                                   | 25    | 340    | MHz  |

| TMDS Output Clock Frequency                     |                                                   | 25    | 340    | MHz  |

| TMDS Differential Lane Rate                     | One differential data lane                        |       | 6      | Gbps |

| TMDS Link Rate                                  | Three differential data lanes                     |       | 18     | Gbps |

| FRL Differential Lane Rate                      | One differential data lane                        |       | 12     | Gbps |

| FRL Differential Lane Rate                      | Four differential data lanes                      |       | 48     | Gbps |

<sup>1</sup> This condition is for the SPI $\overline{CS}$  pin only.

### **POWER SPECIFICATIONS - PRELIMINARY**

### Table 2.

| Parameter                         | Symbol                    | Min   | Тур | Max   | Unit |

|-----------------------------------|---------------------------|-------|-----|-------|------|

| POWER SUPPLIES                    |                           |       |     |       |      |

| Standby Power Supply <sup>1</sup> | SBVCC_5V                  | 4.5   | 5.0 | 5.5   | V    |

| RX 5 V DDC Power Input            | RX_PWR_5V                 | 4.5   | 5.0 | 5.3   | V    |

| RX 3.3 V Analog Power Supply      | VDDH                      | 3.145 | 3.3 | 3.465 | V    |

| FPLL Power Supply                 | FPLL_AVDD                 | 0.95  | 1.0 | 1.05  | V    |

| eARC Power Supply                 | eARC_PWR                  | 0.95  | 1.0 | 1.05  | V    |

| Crystal Oscillator Supply         | XTAL_VDD_3V3              | 3.145 | 3.3 | 3.465 | V    |

| TX 3.3 V Analog Power Supply      | TX_VDDHA                  | 3.145 | 3.3 | 3.465 | V    |

| TX PLL Analog Power Supply        | TX_VDDA_PLL               | 0.95  | 1.0 | 1.05  | V    |

| RX Analog 1.0 V Power Supply      | AVDD                      | 0.95  | 1.0 | 1.05  | V    |

| TX Analog Power Supply            | TX_VDDAC                  | 0.95  | 1.0 | 1.05  | V    |

| TX Analog Power Supply            | TX_VDDAD                  | 0.95  | 1.0 | 1.05  | V    |

| Digital Core Power Supply         | PWR                       | 0.95  | 1.0 | 1.05  | V    |

| CURRENT CONSUMPTION (TBD)         |                           |       |     |       |      |

| Standby Power Supply              | I <sub>SBVCC_5V</sub>     |       |     |       | mA   |

| RX 5 V DDC Power Input            | I <sub>RX_PWR_5V</sub>    |       |     |       | mA   |

| RX 3.3 V Analog Power Supply      | Ivddh                     |       |     |       | mA   |

| FPLL Power Supply                 | I <sub>FPLL_AVDD</sub>    |       |     |       | mA   |

| eARC Power Supply                 | learc_pwr                 |       |     |       | mA   |

| Crystal Oscillator Supply         | I <sub>XTAL_VDD_3V3</sub> |       |     |       | mA   |

| TX 3.3 V Analog Power Supply      | Itx_vddha                 |       |     |       | mA   |

| TX PLL Analog Power Supply        | I <sub>TX_VDDA_PLL</sub>  |       |     |       | mA   |

| RX 1.0 V Analog Power Supply      | lavdd                     |       |     |       | mA   |

| TX Analog Power Supply            | I <sub>TX_VDDAC</sub>     |       |     |       | mA   |

| TX Analog Power Supply            | ITX_VDDAD                 |       |     |       | mA   |

| Digital Core Power Supply         | I <sub>PWR</sub>          |       |     |       | mA   |

| Total Mode Power Dissipation      |                           |       |     |       | W    |

| CURRENT CONSUMPTION (TBD)         |                           |       |     |       |      |

| Standby Power Supply              | Isbvcc_5v                 |       |     |       | mA   |

| RX 5 V DDC Power Input            | I <sub>RX_PWR_5V</sub>    |       |     |       | mA   |

| RX 3.3 V Analog Power Supply      | Ivddh                     |       |     |       | mA   |

| FPLL Power Supply                 | I <sub>FPLL_AVDD</sub>    |       |     |       | mA   |

| eARC Power Supply                 | learc_pwr                 |       |     |       | mA   |

| Crystal Oscillator Supply         | I <sub>XTAL_VDD_3V3</sub> |       |     |       | mA   |

| TX 3.3 V Analog Power Supply      | Itx_vddha                 |       |     |       | mA   |

| TX PLL Analog Power Supply        | I <sub>TX_VDDA_PLL</sub>  |       |     |       | mA   |

| Rx 1.0 V Analog Power Supply      | lavdd                     |       |     |       | mA   |

| TX Analog Power Supply            | I <sub>TX_VDDAC</sub>     |       |     |       | mA   |

| TX Analog Power Supply            | I <sub>TX_VDDAD</sub>     |       |     |       | mA   |

| Digital Core Power Supply         | I <sub>PWR</sub>          |       |     |       | mA   |

| Total Mode Power Dissipation      |                           |       |     |       | W    |

<sup>1</sup> SBVCC\_5V is measured at SBVCC\_5V\_TP as shown in Figure 17.

### TIMING SPECIFICATIONS - PRELIMINARY

### Table 3.

| Parameter                                                                      | Symbol                    | Test Conditions/Comments     | Min  | Тур | Max  | Unit                  |

|--------------------------------------------------------------------------------|---------------------------|------------------------------|------|-----|------|-----------------------|

| CRYSTAL                                                                        |                           | Refer to Figure 16           |      |     |      |                       |

| External Crystal Frequency                                                     | f <sub>xtal</sub>         |                              |      | 25  |      | MHz                   |

| XTAL_IN Frequency Tolerance                                                    | f <sub>xtal_tol</sub>     |                              | -150 |     | 150  | ppm                   |

| Clock Duty Cycle                                                               | %t <sub>xtal</sub>        |                              | 40   |     | 60   | % Duty                |

|                                                                                |                           |                              |      |     |      | Cycle                 |

| Load Capacitance                                                               | CLOAD                     |                              |      | 18  |      | pF                    |

| Feedback Resistor                                                              | RFEEDBACK                 |                              |      | 1   |      | MΩ                    |

| RESET TIMING                                                                   |                           |                              |      |     |      |                       |

| Time from power stable to de-<br>assertion of internal power on<br>reset (POR) | <b>t</b> power_on_reset   |                              |      |     | 3    | ms                    |

| POWER RISE TIME                                                                |                           |                              |      |     |      |                       |

| Rise time of RX_PWR_5V                                                         | t <sub>POWER_RISE</sub>   |                              | 50   |     |      | μs                    |

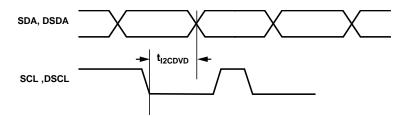

| I <sup>2</sup> C, DDC                                                          |                           | Refer to Figure 2.           |      |     |      |                       |

| SDA Data Valid Delay from SCL<br>Falling Edge                                  | t <sub>I2CDVD</sub>       | C <sub>L</sub> = 400 pF      |      |     | 700  | ns                    |

| SDA Data Valid Delay from SCL<br>Falling Edge, Receiver DDC<br>Port            | t <sub>i2CDVD_RXDDC</sub> | C <sub>L</sub> = 400 pF      |      |     | 1000 | ns                    |

| Clock Rate on Receiver DDC Port                                                | f <sub>RXDDC</sub>        | $C_{L} = 400 \text{ pF}$     |      |     | 100  | kHz                   |

| Clock Rate on Transmitter DDC<br>Port                                          | f <sub>txddc</sub>        | $C_L = 400 \text{ pF}$       |      |     | 100  | kHz                   |

| Clock Rate on I <sup>2</sup> C Port                                            | f <sub>I2C</sub>          | $C_{L} = 400 \text{ pF}$     |      |     | 1    | MHz                   |

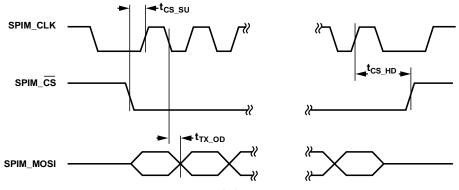

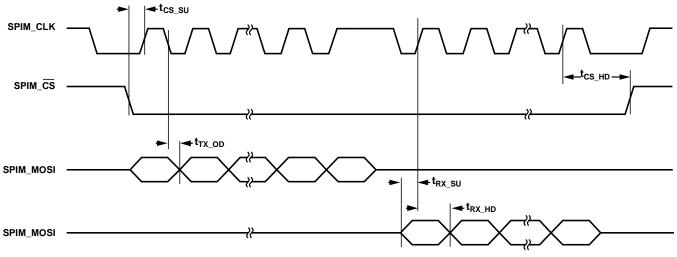

| SPI FLASH MEMORY INTERFACE                                                     |                           | Refer to Figure 3, Figure 4. |      |     |      |                       |

| SPI Master (SPIM) CLK Frequency                                                | t <sub>clk_freq</sub>     | ISP                          | 6    |     | 9    | MHz                   |

|                                                                                |                           | Boot Loader                  | 12   |     | 18   | MHz                   |

| SPIM_CS Setup Time to<br>SPIM_CLK Rising Edge                                  | $t_{\overline{CS}_{SU}}$  |                              | 25   |     |      | ns                    |

| SPIM_CS Hold Time from<br>SPIM_CLK Rising Edge                                 | $t_{\overline{CS}_{HD}}$  |                              | 220  |     |      | ns                    |

| SPIM_MOSI Output Time from<br>SPIM_CLK Falling Edge                            | t <sub>TX_OD</sub>        |                              | 0    |     | 15   | ns                    |

| SPIM_MISO Setup Time to<br>SPIM_CLK Rising Edge                                | t <sub>RX_SU</sub>        |                              | 6    |     |      | ns                    |

| SPIM_MISO Hold Time to<br>SPIM_CLK Rising Edge                                 | t <sub>RX_HD</sub>        |                              | 6    |     |      | ns                    |

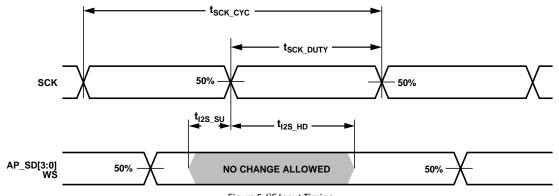

| AUDIO PORTS, I <sup>2</sup> S INPUT                                            |                           | Refer to Figure 5.           |      |     |      |                       |

| Sample Rate                                                                    | <b>f</b> s_125            |                              | 32   |     | 192  | kHz                   |

| I <sup>2</sup> S Cycle Time                                                    | tscк_сус                  | C <sub>L</sub> = 10 pF       |      |     | 1.0  | UI                    |

| I <sup>2</sup> S Duty Cycle <sup>1</sup>                                       | tsck_duty                 | $C_L = 10 \text{ pF}$        |      | 50  |      | % Т <sub>SCK_C</sub>  |

| I <sup>2</sup> S Setup Time <sup>2</sup>                                       | t <sub>I2S_SU</sub>       | $C_L = 10 \text{ pF}$        | 25   |     |      | ns                    |

| I <sup>2</sup> S Hold Time <sup>2</sup>                                        | t <sub>I2S_HD</sub>       | $C_L = 10 \text{ pF}$        | 0    |     |      | ns                    |

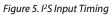

| AUDIO PORTS, S/PDIF INPUT                                                      |                           | Refer to Figure 6.           |      |     |      |                       |

| Sample Rate                                                                    | f <sub>IN_SPDIF</sub>     |                              | 32   |     | 192  | kHz                   |

| Cycle Time <sup>3</sup>                                                        | t <sub>IN_SP_CYC</sub>    |                              |      |     | 1.0  | UI                    |

| Duty Cycle <sup>3</sup>                                                        | t <sub>IN_SP_DUTY</sub>   |                              |      | 50  |      | % T <sub>I_SPCY</sub> |

# ADI Preliminary and Confidential

### **ADV7671**

| Parameter                            | Symbol                   | <b>Test Conditions/Comments</b> | Min                        | Тур | Max    | Unit                     |

|--------------------------------------|--------------------------|---------------------------------|----------------------------|-----|--------|--------------------------|

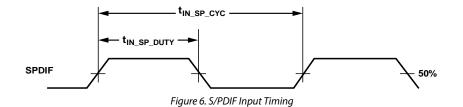

| AUDIO PORTS, I <sup>2</sup> S OUTPUT |                          | Refer to Figure 7, Figure 8.    |                            |     |        |                          |

| SCK Clock Period (TX)                | <b>t</b> <sub>TR</sub>   | $C_{L} = 10 \text{ pF}$         | 20.346                     |     |        | ns                       |

| Setup Time, SCK to SD/WS             | t <sub>su</sub>          | $C_L = 10 \text{ pF}$           | 0.4Tt <sub>TR</sub> –<br>5 |     |        | ns                       |

| Hold Time, SCK to SD/WS              | t <sub>HD</sub>          | $C_L = 10 \text{ pF}$           | 0.4Tt <sub>TR</sub> –<br>5 |     |        | ns                       |

| SCK Duty Cycle                       | tsck_duty                | $C_L = 10 \text{ pF}$           | 40                         |     | 60     | % <b>t</b> <sub>TR</sub> |

| SCK to SD or WS Delay <sup>4</sup>   | t <sub>SCK_2SD</sub>     | $C_{L} = 10 \text{ pF}$         | -20                        |     | +20    | ns                       |

| MCLK Cycle Time                      | t <sub>MCLK_CYC</sub>    | $C_{L} = 10 \text{ pF}$         | 20.0                       |     | 250    | ns                       |

| MCLK Frequency                       | <b>f</b> <sub>MCLK</sub> | $C_{L} = 10 \text{ pF}$         | 4.0                        |     | 50.0   | MHz                      |

| MCLK Duty Cycle                      | <b>t</b> MCLK_DUTY       | $C_{L} = 10 \text{ pF}$         | 45                         |     | 55     | % Тмськсус               |

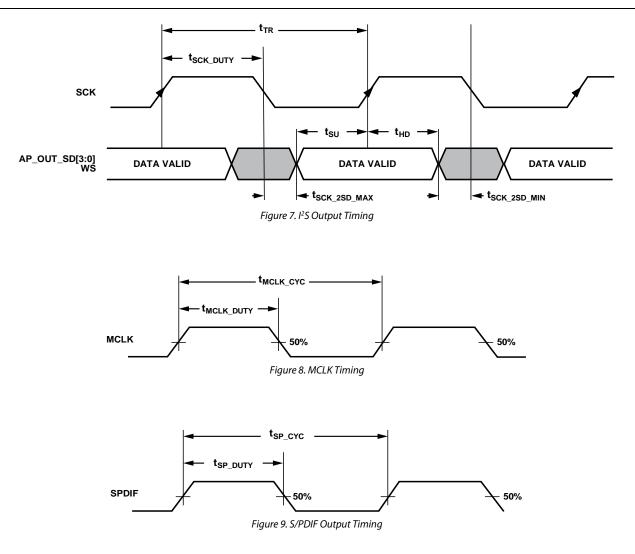

| AUDIO PORTS, S/PDIF OUTPUT           |                          | Refer to Figure 9.              |                            |     |        |                          |

| S/PDIF Cycle Time                    | t <sub>SP_CYC</sub>      | $C_{L} = 10 \text{ pF}$         |                            | 1.0 |        | UI                       |

| S/PDIF Frequency                     | <b>f</b> spdif           |                                 | 4.0                        |     | 24.576 | MHz                      |

| S/PDIF Duty Cycle                    | tsp_duty                 | $C_L = 10 \text{ pF}$           |                            | 50  |        | % T <sub>SPCYC</sub>     |

| eARC INTERFACE                       |                          |                                 |                            |     |        |                          |

| eARC Frequency                       | $f_{CLK\_eARC}$          |                                 | 4.096                      |     | 98.304 | MHz                      |

<sup>1</sup> Proportional to unit time (UI) according to sample rate. Refer to the I<sup>2</sup>S Specification or the S/PDIF Specification. <sup>2</sup> Setup and hold minimum times are based on 13.388 MHz sampling, which is adapted from Figure 3 of the Philips I<sup>2</sup>S Specification.

<sup>3</sup> Proportional to unit time (UI), according to sample rate. Refer to the S/PDIF Specification.

<sup>4</sup> Refers to SCK to WS delay

Figure 2. I<sup>2</sup>C Data Valid Delay

Figure 3. SPI Flash Write Timing

**ADI Preliminary and Confidential**

Figure 4. SPI Flash Read Timing

# ADI Preliminary and Confidential

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 4.

| Table 4.                                 |                 |

|------------------------------------------|-----------------|

| Parameter                                | Rating          |

| SBVCC_5V                                 | –0.3 V to 5.7 V |

| RX_PWR_5V                                | –0.3 V to 5.7 V |

| VDDH                                     | –0.3 V to 4.0 V |

| FPLL_AVDD                                | –0.3 V to 1.5 V |

| eARC_PWR                                 | –0.3 V to 1.5 V |

| TX_VDDHA                                 | –0.3 V to 4.0 V |

| XTAL_VDD_3V3                             | –0.3 V to 4.0 V |

| TX_VDDA_PLL                              | –0.3 V to 1.5 V |

| AVDD                                     | –0.3 V to 1.5 V |

| TX0_VDDAC                                | –0.3 V to 1.5 V |

| TX0_VDDAD                                | –0.3 V to 1.5 V |

| PWR                                      | –0.3 V to 1.5 V |

| 5 V tolerant input pins                  | –0.3 V to 5.7 V |

| Operating Temperature Range <sup>1</sup> | 0°C to + 70°C   |

| Storage Temperature Range                | –65°C to +150°C |

| Maximum Junction                         | 125°C           |

| Temperature                              |                 |

<sup>1</sup> With power applied.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Close attention to PCB thermal design is required.

Table 5 shows the thermal resistance for junction to ambient  $(\theta_{JA})$ , junction to case top  $(\theta_{JCtop})$ , junction to board  $(\theta_{JB})$ , junction to top thermal characterization number  $(\Psi_{JT})$ , and junction to board thermal characterization number  $(\Psi_{JB})$ .

#### Table 5. Thermal Resistance

| Package Type             | ΘյΑ | θ <sub>JCtop</sub> | θյβ | Ψл | $\Psi_{JB}$ | Unit |

|--------------------------|-----|--------------------|-----|----|-------------|------|

| CP-108-1 <sup>1, 2</sup> |     |                    |     |    |             | °C/W |

$^{\rm T}$  For  $\theta_{\rm JC}$  testing, 100  $\mu m$  thermal interface material (TIM) is used. TIM is assumed to have 3.6 W/mK.

<sup>2</sup> Using enhanced heat removal (PCB, heat sink, or airflow) technique improves thermal resistance values.

### **ELECTROSTATIC DISCHARGE (ESD RATINGS)**

The following ESD information is provided for handling of ESD-sensitive deices in an ESD protected area only.

Human body model (HBM) per ANSI/ESDA/JEDEC JS-001.

Charged device model (CDM) per ANSI/ESDA/JEDEC JS-002.

#### Table 6. ESD Ratings for ADV7671

| ESD Model | Withstand Threshold (V) | Class |

|-----------|-------------------------|-------|

| HBM       | ±2000                   | 2     |

| CDM       | ±500                    | C2A   |

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

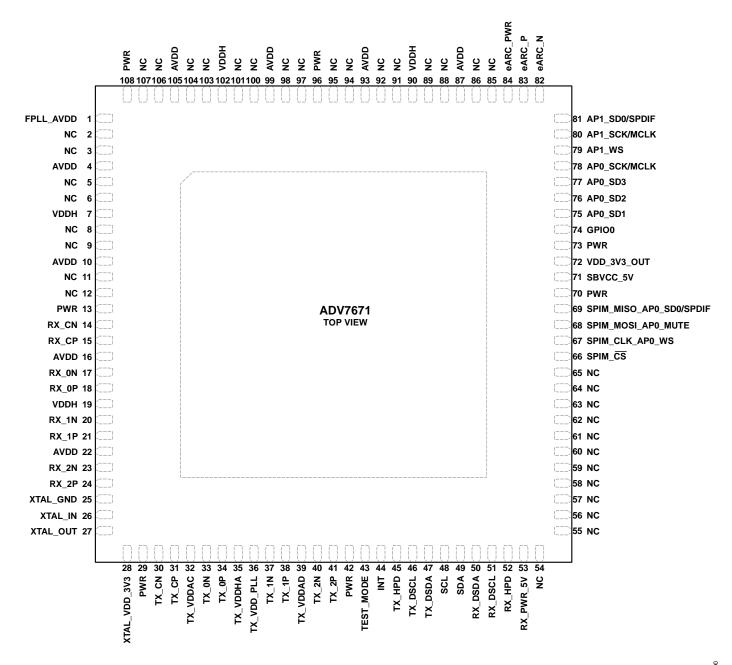

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

NOTES

1. THE EXPOSED PAD MUST BE SOLDERED TO A PAD THAT IS ELECTRICALLY CONNECTED TO THE GROUND PLANE OF THE PCB.

Figure 10. ADV7671 Pin Configuration

### Table 7. ADV7671 Pin Function Descriptions

| Pin No.       | Mnemonic | Туре                            | Description                                                                                                                                                                                                                            |

|---------------|----------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HDMI          |          |                                 |                                                                                                                                                                                                                                        |

| Transmitter   |          |                                 |                                                                                                                                                                                                                                        |

| 30            | TX_CN    | TX TMDS<br>Output               | TMDS TX Clock Negative Output or FRL Lane 3 Negative Output.                                                                                                                                                                           |

| 31            | TX_CP    | TX TMDS<br>Output               | TMDS TX Clock Positive Output or FRL Lane 3 Positive Output.                                                                                                                                                                           |

| 33            | TX_ON    | TX TMDS<br>Output               | TMDS TX Channel 0 Negative Output or FRL Lane 0 Negative Output.                                                                                                                                                                       |

| 34            | TX_OP    | TX TMDS<br>Output               | TMDS TX Channel 0 Positive Output or FRL Lane 0 Positive Output.                                                                                                                                                                       |

| 37            | TX_1N    | TX TMDS<br>Output               | TMDS TX Channel 1 Negative Output or FRL Lane 1 Negative Output.                                                                                                                                                                       |

| 38            | TX_1P    | TX TMDS<br>Output               | TMDS TX Channel 1 Positive Output or FRL Lane 1 Positive Output.                                                                                                                                                                       |

| 40            | TX_2N    | TX TMDS<br>Output               | TMDS TX Channel 2 Negative Output or FRL Lane 2 Negative Output.                                                                                                                                                                       |

| 41            | TX_2P    | TX TMDS<br>Output               | TMDS TX Channel 2 Positive Output or FRL Lane 2 Positive Output.                                                                                                                                                                       |

| 45            | TX_HPD   | TX Control<br>Input             | HDMI TX Hot Plug Detect (HPD). The HDMI transmitter uses this pin to detect when a Sink is connected. This pin is 5 V tolerant.                                                                                                        |

| 46            | TX_DSCL  | TX Control<br>Input /<br>Output | HDMI TX DDC SCL. This pin does not present a current path to GND when the device is not powered. This pin must be connected through a pull up resistor (1.5 k $\Omega$ to 2 k $\Omega$ ) to DDC 5 V. Refer to the HDMI specification.  |

| 47            | TX_DSDA  | TX Control<br>Input /<br>Output | HDMI TX0 DDC SDA. This pin does not present a current path to GND when the device is not powered. This pin must be connected through a pull up resistor (1.5 k $\Omega$ to 2 k $\Omega$ ) to DDC 5 V. Refer to the HDMI specification. |

| HDMI Receiver |          |                                 |                                                                                                                                                                                                                                        |

| 14            | RX_CN    | RX TMDS<br>Input                | TMDS RX Clock Negative Input or FRL Lane 3 Negative Input.                                                                                                                                                                             |

| 15            | RX_CP    | RX TMDS<br>Input                | TMDS RX Clock Positive Input or FRL Lane 3 Positive Input.                                                                                                                                                                             |

| 17            | RX_0N    | RX TMDS<br>Input                | TMDS RX Channel 0 Negative Input or FRL Lane 0 Negative Input.                                                                                                                                                                         |

| 18            | RX_0P    | RX TMDS<br>Input                | TMDS RX Channel 0 Positive Input or FRL Lane 0 Positive Input.                                                                                                                                                                         |

| 20            | RX_1N    | RX TMDS<br>Input                | TMDS RX Channel 1 Negative Input or FRL Lane 1 Negative Input.                                                                                                                                                                         |

| 21            | RX_1P    | RX TMDS<br>Input                | TMDS RX Channel 1 Positive Input or FRL Lane 1 Positive Input.                                                                                                                                                                         |

| 23            | RX_2N    | RX TMDS<br>Input                | TMDS RX Channel 2 Negative Input or FRL Lane 2 Negative Input.                                                                                                                                                                         |

| 24            | RX_2P    | RX TMDS<br>Input                | TMDS RX Channel 2 Positive Input or FRL Lane 2 Positive Input.                                                                                                                                                                         |

| 52            | RX_HPD   | RX Control<br>Output            | HDMI RX Hot Plug Detect (HPD). This pin is 5 V tolerant and has a 1 k $\Omega$ output impedance. This pin indicates that the EDID is readable.                                                                                         |

| 51            | RX_DSCL  | RX Control<br>Input /Output     | HDMI RX DDC SCL. This pin does not present a current path to GND when the device is not powered. This pin must be connected through a 47 k $\Omega$ pull up resistor to DDC 5 V. Refer to the HDMI specification.                      |

| 50            | RX_DSDA  | RX Control<br>Input /<br>Output | HDMI RX DDC SDA. This pin does not present a current path to GND when the device is not powered.                                                                                                                                       |

# ADI Preliminary and Confidential

| Pin No.             | Mnemonic                    | Туре                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------|-----------------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Audio               |                             |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 67                  | SPIM_CLK_AP0_WS             | LVTTL Schmitt<br>Input /<br>Output | Audio Extraction Port AP0 I <sup>2</sup> S Word Select or SPI Flash Memory Interface<br>Clock Output Signal. This pin is 5 V tolerant.                                                                                                                                                                                                                                                                                                            |

| 68                  | SPIM_MOSI_AP0_MUTE          | LVTTL Schmitt<br>Input /<br>Output | Audio Extraction Port AP0 Mute Signal or SPI Flash Memory Interface<br>Data Output. This pin is 5 V tolerant.                                                                                                                                                                                                                                                                                                                                     |

| 69                  | SPIM_MISO_<br>AP0_SD0/SPDIF | LVTTL Schmitt<br>Input /<br>Output | Audio Extraction Port AP0 I <sup>2</sup> S Serial Data Channel 0 or TDM data, or<br>SPDIF signal, or SPI Flash Memory Interface Data Input Signal. This pin is<br>5 V tolerant.                                                                                                                                                                                                                                                                   |

| 75                  | AP0_SD1                     | LVTTL Schmitt<br>Input /<br>Output | Audio Extraction Port AP0 I <sup>2</sup> S Serial Data Channel 1 or TDM data.<br>Alternatively, this pin can be configured as GPIO 1. This pin is 5 V<br>tolerant.                                                                                                                                                                                                                                                                                |

| 76                  | AP0_SD2                     | LVTTL Schmitt<br>Input /<br>Output | Audio Extraction Port AP0 I <sup>2</sup> S Serial Data Channel 2 or TDM data.<br>Alternatively, this pin can be configured as GPIO 2.                                                                                                                                                                                                                                                                                                             |

| 77                  | AP0_SD3                     | LVTTL Schmitt<br>Input /<br>Output | Audio Extraction Port AP0 I <sup>2</sup> S Serial Data Channel 3 or TDM data.<br>Alternatively, this pin can be configured as GPIO bit 3.                                                                                                                                                                                                                                                                                                         |

| 78                  | AP0_SCK/MCLK                | LVTTL Schmitt<br>Input /<br>Output | Audio Extraction Port AP0 I <sup>2</sup> S clock or S/PDIF MCLK. This pin is 5 V tolerant.                                                                                                                                                                                                                                                                                                                                                        |

| 79                  | AP1_WS                      | LVTTL Schmitt<br>Input /<br>Output | Audio Insertion Port AP1 I <sup>2</sup> S Word Select, or DSD L2. This pin is 5 V tolerant.                                                                                                                                                                                                                                                                                                                                                       |

| 80                  | AP1_SCK/MCLK                | LVTTL Schmitt<br>Input /<br>Output | Audio Insertion Port AP1 I <sup>2</sup> S clock or S/PDIF MCLK. This pin is 5 V tolerant.                                                                                                                                                                                                                                                                                                                                                         |

| 81                  | AP1_SD0/SPDIF               | LVTTL Schmitt<br>Input /<br>Output | Audio Insertion Port AP1 I <sup>2</sup> S Serial Data Channel 0 or TDM data, or S/PDIF signal. This pin is 5 V tolerant.                                                                                                                                                                                                                                                                                                                          |

| 82                  | eARC_N                      | eARC Analog<br>Input/Output        | eARC Negative Channel. This signal must be connected to the HPD pin<br>on the HDMI connector when differential eARC or ARC is in use.<br>Differential eARC or ARC is supported by on-board ac coupling.                                                                                                                                                                                                                                           |

| 83                  | eARC_P                      | eARC Analog<br>Input /<br>Output   | eARC Positive Channel or Single-Ended ARC Signal. This signal must be AC coupled through a 1 $\mu$ F external capacitor to the utility signal on the HDMI connector. In ARC receiver mode, eARC_P receives an S/PDIF signal from an ARC transmitter capable sink and outputs the signal on the audio port SPDIF pin. In ARC transmitter mode, eARC_P sends an S/PDIF audio stream from the audio port SPDIF input pin to an upstream HDMI device. |

| Control and         |                             |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Configuration<br>26 | XTAL_IN                     | LVTTL Schmitt<br>Input             | Crystal or Oscillator input. A 25 MHz crystal or oscillator clock source is required for operation.                                                                                                                                                                                                                                                                                                                                               |

| 27                  | XTAL_OUT                    | LVTTL Output                       | Crystal Feedback Output.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 43                  | TEST_MODE                   | LVTTL Input                        | This pin must be driven low in normal functional operation. This pin is 5 V tolerant.                                                                                                                                                                                                                                                                                                                                                             |

| 44                  | INT                         | LVTTL Schmitt<br>Output            | Interrupt Output. The INT pin power-on default is open drain and can be optionally programmed to push-pull LVTTL output. The polarity is negative by default but can be programmed to be positive asserted. This pin is 5 V tolerant.                                                                                                                                                                                                             |

| 48                  | SCL                         | LVTTL Schmitt<br>Input /<br>Output | I <sup>2</sup> C SCL line. This pin is 5 V tolerant.                                                                                                                                                                                                                                                                                                                                                                                              |

| 49                  | SDA                         | LVTTL Schmitt<br>Input /<br>Output | l <sup>2</sup> C SDA line. This pin is 5 V tolerant.                                                                                                                                                                                                                                                                                                                                                                                              |

ADI Preliminary and Confidential

| SPIM_CS<br>SPIM_CLK_AP0_WS<br>SPIM_MOSI_AP0_MUTE<br>SPIM_MISO_<br>AP0_SD0/SPDIF<br>GPIO0 | LVTTL Schmitt<br>Input /<br>Output<br>LVTTL Schmitt<br>Input /<br>Output<br>LVTTL Schmitt<br>Input /<br>Output<br>LVTTL Schmitt<br>Input /<br>Output<br>LVTTL Schmitt<br>Input /<br>Output | <ul> <li>SPI Flash Memory Interface Chip Select. Latched at power-on-reset to disable or enable SPI Master Boot :</li> <li>0 = Disables SPI Master Boot, 1 = Enables SPI Master Boot.</li> <li>This pin is 5 V tolerant.</li> <li>SPI Flash Memory Interface Clock Output Signal or Audio Extraction Port AP0 I<sup>2</sup>S Word Select. This pin is 5 V tolerant.</li> <li>SPI Flash Memory Interface Data Output or Audio Extraction Port AP0 Mute Signal. Latched at power-on-reset for I<sup>2</sup>C address select :</li> <li>0 = I<sup>2</sup>C Address is 0x40, 1 = I<sup>2</sup>C Address is 0x44. This pin is 5 V tolerant.</li> <li>SPI Flash Memory Interface Data Input Signal or Audio Extraction Port AP0 Mute Signal. Latched at power-on-reset for I<sup>2</sup>C address select :</li> <li>0 = I<sup>2</sup>C Address is 0x40, 1 = I<sup>2</sup>C Address is 0x44. This pin is 5 V tolerant.</li> <li>SPI Flash Memory Interface Data Input Signal or Audio Extraction Port AP0 I<sup>2</sup>S Serial Data Channel 0 or TDM data, or SPDIF signal. I<sup>2</sup>C interface strapping option. This pin is 5 V tolerant.</li> <li>General Purpose IO 0, or Audio Extraction Port AP0 DSD L6. This pin is 5 V tolerant.</li> </ul> |

|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPIM_MOSI_AP0_MUTE<br>SPIM_MISO_<br>AP0_SD0/SPDIF<br>GPIO0                               | UVTTL Schmitt<br>Input /<br>Output<br>LVTTL Schmitt<br>Input /<br>Output<br>LVTTL Schmitt<br>Input /<br>Output<br>LVTTL Schmitt<br>Input /                                                 | <ul> <li>0 = Disables SPI Master Boot, 1 = Enables SPI Master Boot.</li> <li>This pin is 5 V tolerant.</li> <li>SPI Flash Memory Interface Clock Output Signal or Audio Extraction Port AP0 I<sup>2</sup>S Word Select. This pin is 5 V tolerant.</li> <li>SPI Flash Memory Interface Data Output or Audio Extraction Port AP0 Mute Signal. Latched at power-on-reset for I<sup>2</sup>C address select :</li> <li>0 = I<sup>2</sup>C Address is 0x40, 1 = I<sup>2</sup>C Address is 0x44. This pin is 5 V tolerant.</li> <li>SPI Flash Memory Interface Data Input Signal or Audio Extraction Port AP0 I<sup>2</sup>S Serial Data Channel 0 or TDM data, or SPDIF signal. I<sup>2</sup>C interface strapping option. This pin is 5 V tolerant.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SPIM_MOSI_AP0_MUTE<br>SPIM_MISO_<br>AP0_SD0/SPDIF<br>GPIO0                               | LVTTL Schmitt<br>Input /<br>Output<br>LVTTL Schmitt<br>Input /<br>Output<br>LVTTL Schmitt<br>Input /<br>Output<br>LVTTL Schmitt<br>Input /                                                 | This pin is 5 V tolerant.<br>SPI Flash Memory Interface Clock Output Signal or Audio Extraction Port<br>APO I <sup>2</sup> S Word Select. This pin is 5 V tolerant.<br>SPI Flash Memory Interface Data Output or Audio Extraction Port APO<br>Mute Signal. Latched at power-on-reset for I <sup>2</sup> C address select :<br>$0 = I^2$ C Address is 0x40, $1 = I^2$ C Address is 0x44. This pin is 5 V tolerant.<br>SPI Flash Memory Interface Data Input Signal or Audio Extraction Port<br>APO I <sup>2</sup> S Serial Data Channel 0 or TDM data, or SPDIF signal. I <sup>2</sup> C interface<br>strapping option. This pin is 5 V tolerant.<br>General Purpose IO 0, or Audio Extraction Port APO DSD L6. This pin is 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SPIM_MOSI_AP0_MUTE<br>SPIM_MISO_<br>AP0_SD0/SPDIF<br>GPIO0                               | Input /<br>Output<br>LVTTL Schmitt<br>Input /<br>Output<br>LVTTL Schmitt<br>Input /<br>Output<br>LVTTL Schmitt<br>Input /                                                                  | SPI Flash Memory Interface Clock Output Signal or Audio Extraction Port<br>APO I <sup>2</sup> S Word Select. This pin is 5 V tolerant.<br>SPI Flash Memory Interface Data Output or Audio Extraction Port APO<br>Mute Signal. Latched at power-on-reset for I <sup>2</sup> C address select :<br>$0 = I^2$ C Address is 0x40, $1 = I^2$ C Address is 0x44. This pin is 5 V tolerant.<br>SPI Flash Memory Interface Data Input Signal or Audio Extraction Port<br>APO I <sup>2</sup> S Serial Data Channel 0 or TDM data, or SPDIF signal. I <sup>2</sup> C interface<br>strapping option. This pin is 5 V tolerant.<br>General Purpose IO 0, or Audio Extraction Port APO DSD L6. This pin is 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SPIM_MOSI_AP0_MUTE<br>SPIM_MISO_<br>AP0_SD0/SPDIF<br>GPIO0                               | Input /<br>Output<br>LVTTL Schmitt<br>Input /<br>Output<br>LVTTL Schmitt<br>Input /<br>Output<br>LVTTL Schmitt<br>Input /                                                                  | APO I <sup>2</sup> S Word Select. This pin is 5 V tolerant.<br>SPI Flash Memory Interface Data Output or Audio Extraction Port APO<br>Mute Signal. Latched at power-on-reset for I <sup>2</sup> C address select :<br>$0 = I^2$ C Address is 0x40, $1 = I^2$ C Address is 0x44. This pin is 5 V tolerant.<br>SPI Flash Memory Interface Data Input Signal or Audio Extraction Port<br>APO I <sup>2</sup> S Serial Data Channel 0 or TDM data, or SPDIF signal. I <sup>2</sup> C interface<br>strapping option. This pin is 5 V tolerant.<br>General Purpose IO 0, or Audio Extraction Port APO DSD L6. This pin is 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SPIM_MISO_<br>AP0_SD0/SPDIF<br>GPIO0                                                     | LVTTL Schmitt<br>Input /<br>Output<br>LVTTL Schmitt<br>Input /<br>Output<br>LVTTL Schmitt<br>Input /                                                                                       | Mute Signal. Latched at power-on-reset for I <sup>2</sup> C address select :<br>$0 = I^2C$ Address is 0x40, $1 = I^2C$ Address is 0x44. This pin is 5 V tolerant.<br>SPI Flash Memory Interface Data Input Signal or Audio Extraction Port<br>APO I <sup>2</sup> S Serial Data Channel 0 or TDM data, or SPDIF signal. I <sup>2</sup> C interface<br>strapping option. This pin is 5 V tolerant.<br>General Purpose IO 0, or Audio Extraction Port APO DSD L6. This pin is 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| AP0_SD0/SPDIF<br>GPIO0                                                                   | Input /<br>Output<br>LVTTL Schmitt<br>Input /                                                                                                                                              | APO I <sup>2</sup> S Serial Data Channel 0 or TDM data, or SPDIF signal. I <sup>2</sup> C interface strapping option. This pin is 5 V tolerant.<br>General Purpose IO 0, or Audio Extraction Port APO DSD L6. This pin is 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                          | Input /                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                          |                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                          |                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SRV(1 SV                                                                                 | Power                                                                                                                                                                                      | Always-on Local Power System Power Supply (5.0 V).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SBVCC_5V<br>RX_PWR_5V                                                                    | Power                                                                                                                                                                                      | RX 5 V DDC Power Input (5.0 V).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VDDH                                                                                     | Power                                                                                                                                                                                      | RX Analog Power Supply (3.3 V).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VDD_3V3_OUT                                                                              | Power Output                                                                                                                                                                               | On-Chip 3.3 V Regulator Power Output. This is a power output from the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                          |                                                                                                                                                                                            | ADV7671. This pin requires an external 2.2 $\mu$ F and 100 nF capacitor to ground. This pin is used to power the external SPI flash containing the ADV7671 Firmware and 3.3 V pull-ups associated with the standby power domain. Maximum output current is 30 mA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| FPLL_AVDD                                                                                | Power                                                                                                                                                                                      | FPLL Power Supply (1.0 V).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| eARC_PWR                                                                                 | Power                                                                                                                                                                                      | eARC Power Supply (1.0 V).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| XTAL_VDD_3V3                                                                             | Power                                                                                                                                                                                      | Crystal Oscillator Supply (3.3 V). Paired with XTAL_IO_GND to shield the XTAL_OUT and XTAL_IN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |