## Enterprise Storage Backplane Management Processor

- EEC1005 Family Members: **-UB1** and **-UB2**

- **UB1**: Original device, formerly ordered as simply “EEC1005”.

- **UB2**: Device with enhanced features.

- Complete Universal Storage Backplane Management Processor Family

- **UB1** supports SFF-TA-1005 Revision 1.3 Universal Backplane Management (UBM) over I<sub>2</sub>C

- **UB2** supports SFF-TA-1005 Revisions 1.3 and 1.4 Universal Backplane Management (UBM) over I<sub>2</sub>C

- Provides SFF-8654 compliant Host Facing Connector (HFC) communication support over I<sub>2</sub>C

- HFC connection responds to all standard UBM commands from the host

- Integrates the UBM FRU non-volatile memory on the UBM FRU I<sub>2</sub>C Address

- Provides SFF-8639 compliant U.2 Drive Facing Connector (DFC) Support

- Provides SFF-TA-1001 compliant U.3 Drive Facing Connector (DFC) Support

- Support for SES over UBM

- Supports I<sub>2</sub>C communication to Baseboard Management Controller

- Up to 8 I<sub>2</sub>C ports for UBM and BMC host interfaces

- SFF-8485 Support

- Implements up to 4 Hardware Accelerated SGPIO Legacy Interfaces for SAS/SATA backplane implementations

- Secure Boot

- EEC1005 code is authenticated by a secure boot loader prior to loading from internal flash

- Hardware accelerated crypto blocks provide fast secure boot using ECC P-256

- Secure Firmware update

- Key revocation, single level

- Supports Storage LED Management as per SFF-8489 IBPI specifications by default

- Custom LED patterns can be configured

- Scalable Solution for up to 16 Hard Drives on a Single Device

- SGPIO Host Interfaces support up to 16 drives (SAS/SATA drive types)

- UBM Host Interfaces support up to 12 drives

- (NVMe drive types)

- Up to 6 HFCs

- Supports multiple backplanes on a single chassis

- Support for NVME Hot plug and Power Disable for drives

- Integrated NV Memory for:

- UBM FRU (Field Replaceable Unit) for every HFC

- General Purpose FRU

- Configuration FRU

- Supports UBM and FRU commands tunneled through the BMC.

- Configurable Interfaces using a single analog Configuration pin:

- Up to 21 Configurations Available (**UB2**)

- Up to 13 Configurations Available (**UB1**)

- Host interface (SGPIO vs UBM)

- Number of HFCs and Drive Facing Connectors (DFCs)

- Other supported features

- Monitors system PERST

- One pin per DFC for PERST support

- Monitors for drive insertion from IFDET and PRSNT signals

- IFDET2 support (for SFF-TA-1001)

- EEC1005 **UB2** Family Member adds:

- SFF-TA-1005 Revision 1.4 Support as well as Revision 1.3

- Intel VPP Support

- EDSFF Drive Type Support

- IBPI 3-LED as well as 2-LED Support

- LED Test Mode

- NVME Drive x2 and x1 U.3 Support as well as x4. Subset of x2 and x1 U.3 also made available in the smaller 84-pin package.

- SATA/SAS/NVME 12-Drive x1 U.3 Support.

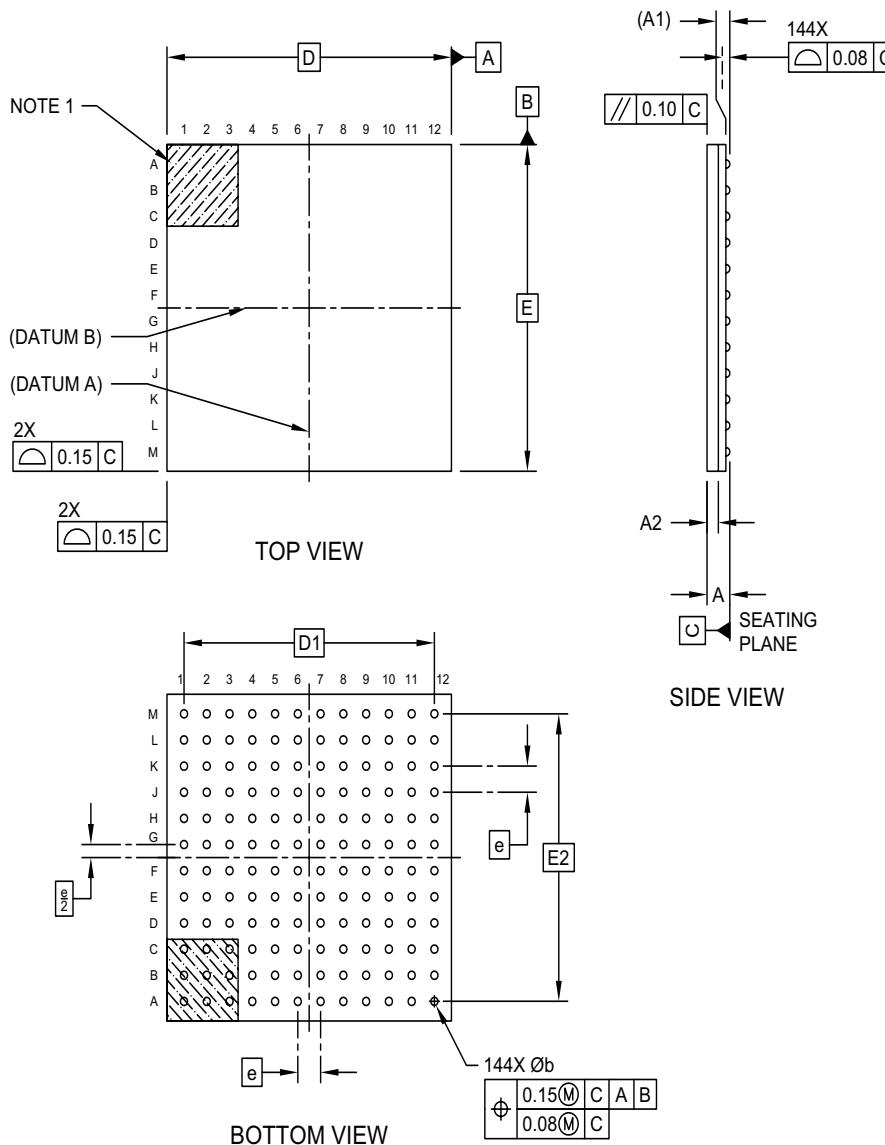

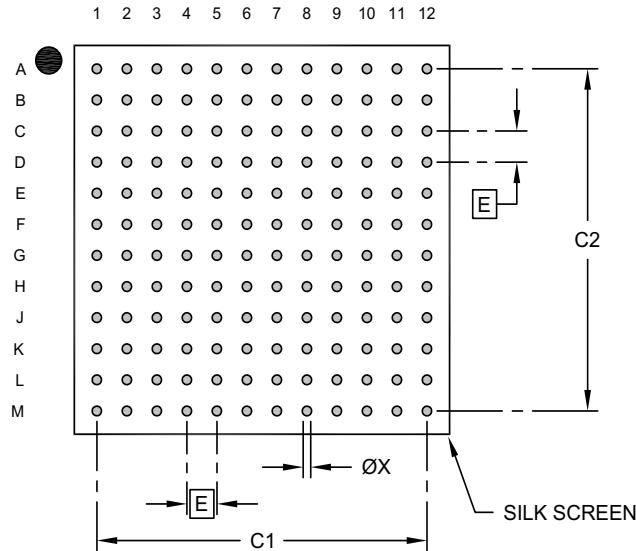

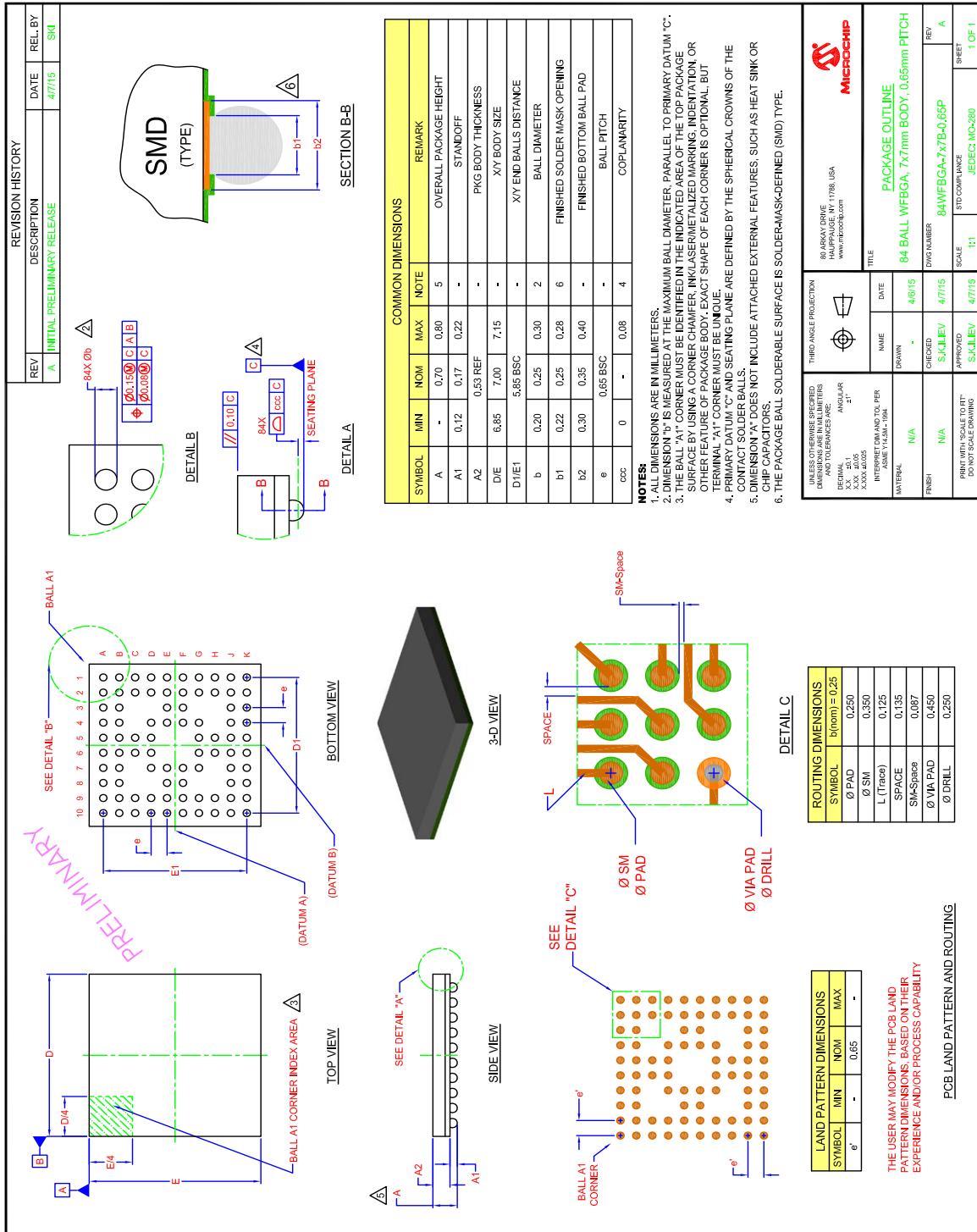

- Package Options

- 144 pin WFBGA RoHS Compliant package

- 84 pin WFBGA RoHS Compliant package

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at [docerrors@microchip.com](mailto:docerrors@microchip.com). We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

<http://www.microchip.com>

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; <http://www.microchip.com>

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

### Customer Notification System

Register on our web site at [www.microchip.com](http://www.microchip.com) to receive the most current information on all of our products.

## Table of Contents

|                                          |    |

|------------------------------------------|----|

| 1.0 General Description .....            | 4  |

| 2.0 UBM Backplane Architecture .....     | 5  |

| 3.0 Configurations .....                 | 10 |

| 4.0 Configuration FRU .....              | 15 |

| 5.0 Generic FRU .....                    | 23 |

| 6.0 UBM FRU .....                        | 24 |

| 7.0 UBM Controller Commands .....        | 26 |

| 8.0 LED Specifications .....             | 30 |

| 9.0 Multiple Chassis Configuration ..... | 33 |

| 10.0 UB2 Enhancements .....              | 35 |

| 11.0 Pin Configuration .....             | 40 |

| 12.0 Electrical Specifications .....     | 59 |

| 13.0 Package Information .....           | 64 |

## 1.0 GENERAL DESCRIPTION

EEC1005 is a family of generic, easily configurable, True Universal Backplane Management (UBM) devices that can be used on hard drive backplanes to provide complete storage enclosure management and reporting to computing host systems using industry standard communication protocols.

Family members are identified with a suffix of **UB1** or **UB2** in their ordering number, where **UB1** represents the part originally ordered as simply EEC1005. **UB2** devices incorporate enhancements in their functionality. In this document, "**UB2 Only**" will distinguish features that are only available from a device ordered with the **UB2** suffix. For a list of added UB2 features, see [Section 10.0, "UB2 Enhancements," on page 35](#). **UB2** devices are downward compatible to systems currently using **UB1** devices.

EEC1005 supports a variety of host interfaces to accommodate SAS/SATS/NVMe backplane. The SFF-8654 slimline connector (Host facing Connector) can be used to route SAS signals in which case the HBA will manage SAS/SATA drives, the same connector protocol (physically a different connector) can be used to route PCIe signals in which case the HBA will manage NVME drives. In both cases UBM will be used as management protocol with support of SGPIO as well on SAS Slimline (Configuration dependent). The device supports using U.2 and U.3 Drive facing Connectors. EEC1005 also supports Multiple Backplanes on a single chassis.

EEC1005 supports 2 or 3 LED IBPI blinking patterns for up to 16 drives. Customized LED blink pattern can also be programmed through the Configuration FRU.

The EEC1005 has a secure boot loader that authenticates and decrypts the Flash boot image (UBM application) using the AES-256, ECDSA P-256, SHA-256 cryptographic hardware accelerators. EEC1005 hardware accelerators support 128-bit and 256-bit AES encryption, ECDSA and EC\_KCDSA signing algorithms, 1024-bits to 4096-bits RSA and Elliptic asymmetric public key algorithms, and a True Random Number Generator (TRNG). Additionally, the device offers lockable OTP storage for private keys and IDs.

EEC1005 is available in 84 pin and 144 pin WFBGA packages.

### 1.1 References

1. SFF-TA-1005 Universal Backplane Management Specification

- a) Rev. 1.3 supported by EEC1005 family members UB1 and UB2

- b) Rev. 1.4 supported by EEC1005 family member UB2 only

2. SFF-8485 Serial General-Purpose Input/output (SGPIO) Specification

3. SFF-8448 SAS Sideband Signal Assignment

4. SFF-8489 Serial GPIO IBPI (International Blinking Pattern Interpretation)

5. Enterprise SSD Form Factor Version 1.0a

6. SFF-TA-1001 (U.3 Drive Connector) Specification

7. SFF-8639 (U.2 Drive Connector) Specification

8. SFF-9639 (U.2 Connector Pinout) Specification

9. SFF-8654 Slimline Connector Specification

10. SFF-9402 Multi-Protocol Internal Cables for SAS and/or PCIe (Slimline Connector Pinout) Specification

11. SCSI Enclosure Services -4 Specification

12. Intel Doc. #611488: SPR\_EDS\_VPP: Integrated I/O and PCI Express Functional Description -- Sapphire Rapids Processor

13. SFF-TA-1009: EDSFF (Enterprise and Datacenter Standard Form Factor) Specification

14. SFF-TA-1002: Protocol Agnostic Multi-Lane High Speed Connector Specification

## 2.0 UBM BACKPLANE ARCHITECTURE

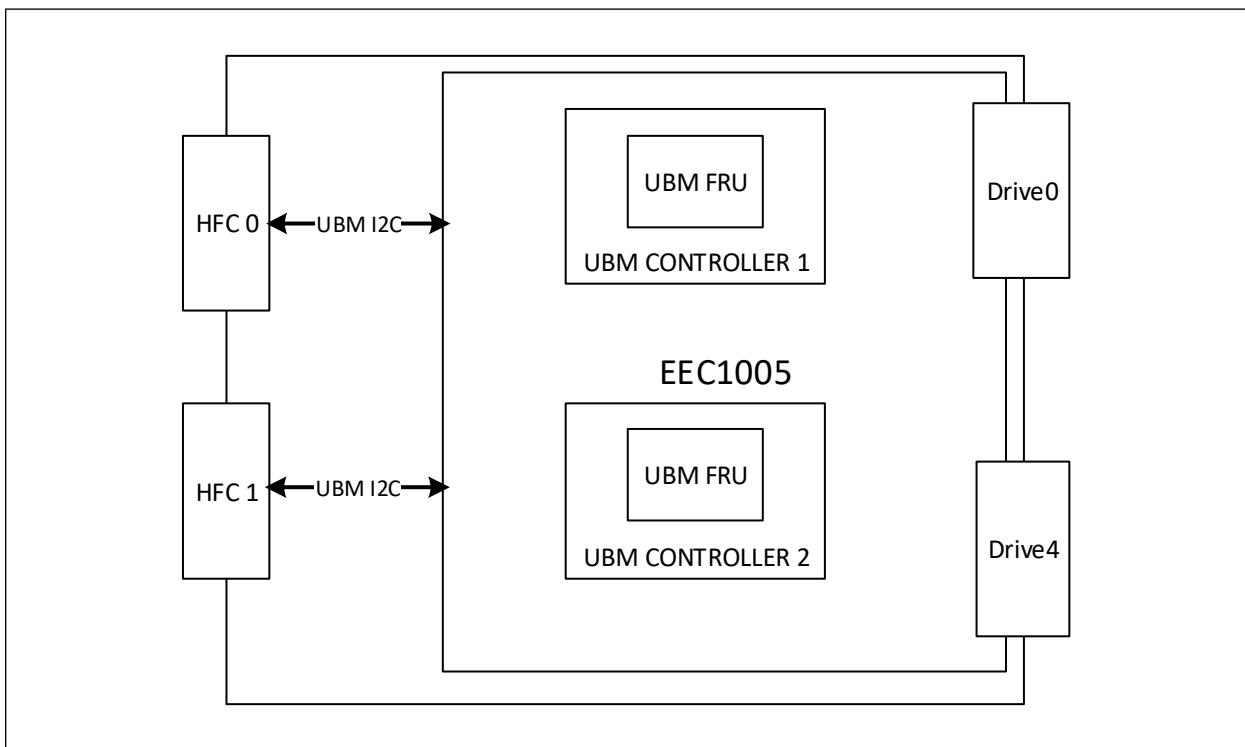

EEC1005 on the back plane communicates to the Host through GPIO or I2C interface over the Host facing Connector (Host attach configuration) or dedicated cable (Direct attach configuration). It detects hard drive being installed in the backplane and notifies the host of the insertion/removal/failure of the drive. It also blinks LEDs for each hard drive's status as explained in [Section 8.0, "LED Specifications"](#).

There are different types of Backplanes based on:

1. Number of drives the back plane supports

2. Type of host communication (For eg. I2C or GPIO)

3. Type of Drive slots (For eg. U.2 or U.3)

The different configurations of the backplane that EEC1005 supports is covered in [Section 3.0, "Configurations"](#).

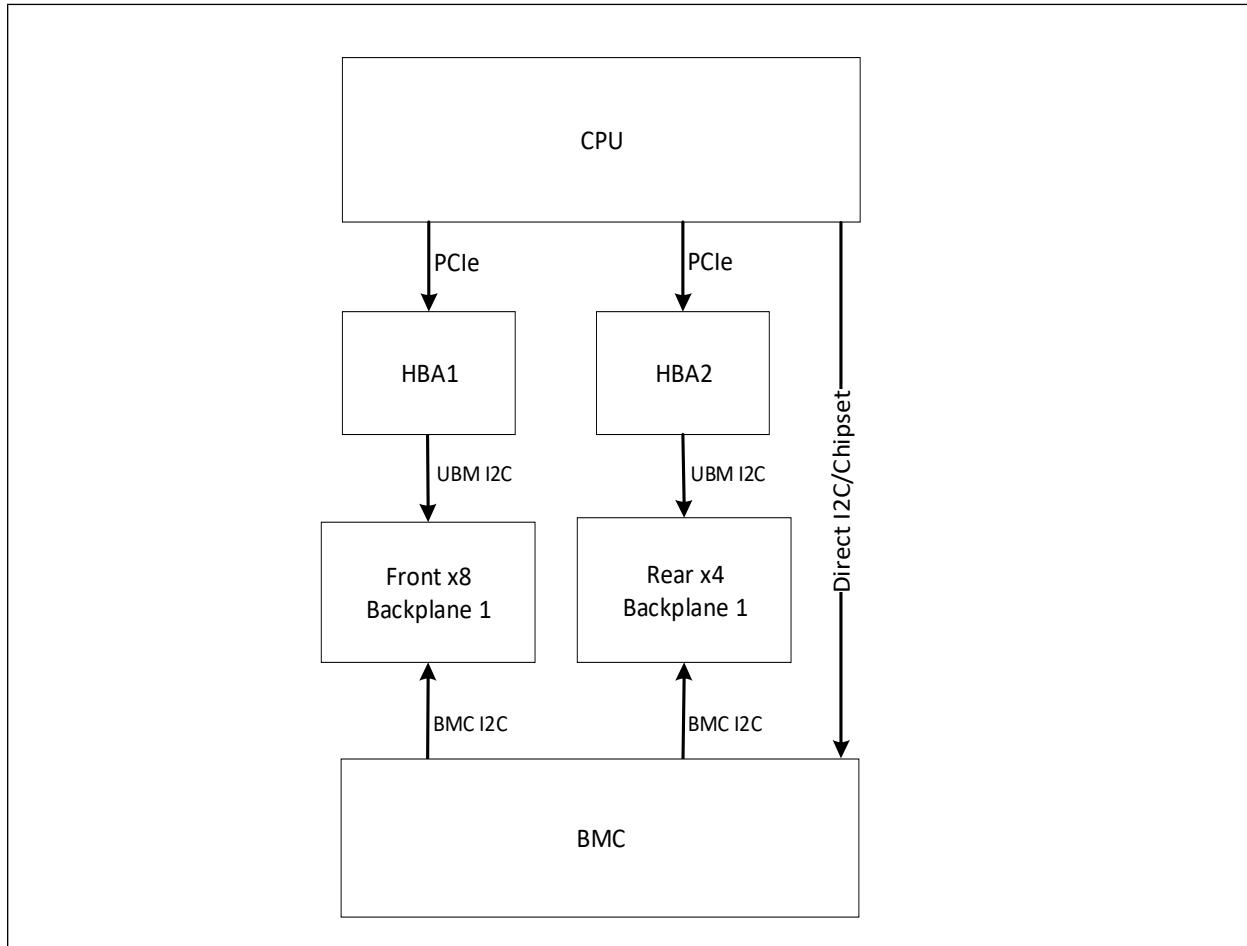

### 2.1 Direct Attach UBM Backplane

A direct attach configuration is enabled when user connects the backplane directly to mother board and the drives are not managed by an HBA. In this case the drives are managed either by BMC or PCIe Switch/Expander for switch-based configurations. EEC1005 can be used in Direct attach configurations using UBM as the management protocol from BMC (BMC Emulation) or Switch/Expander.

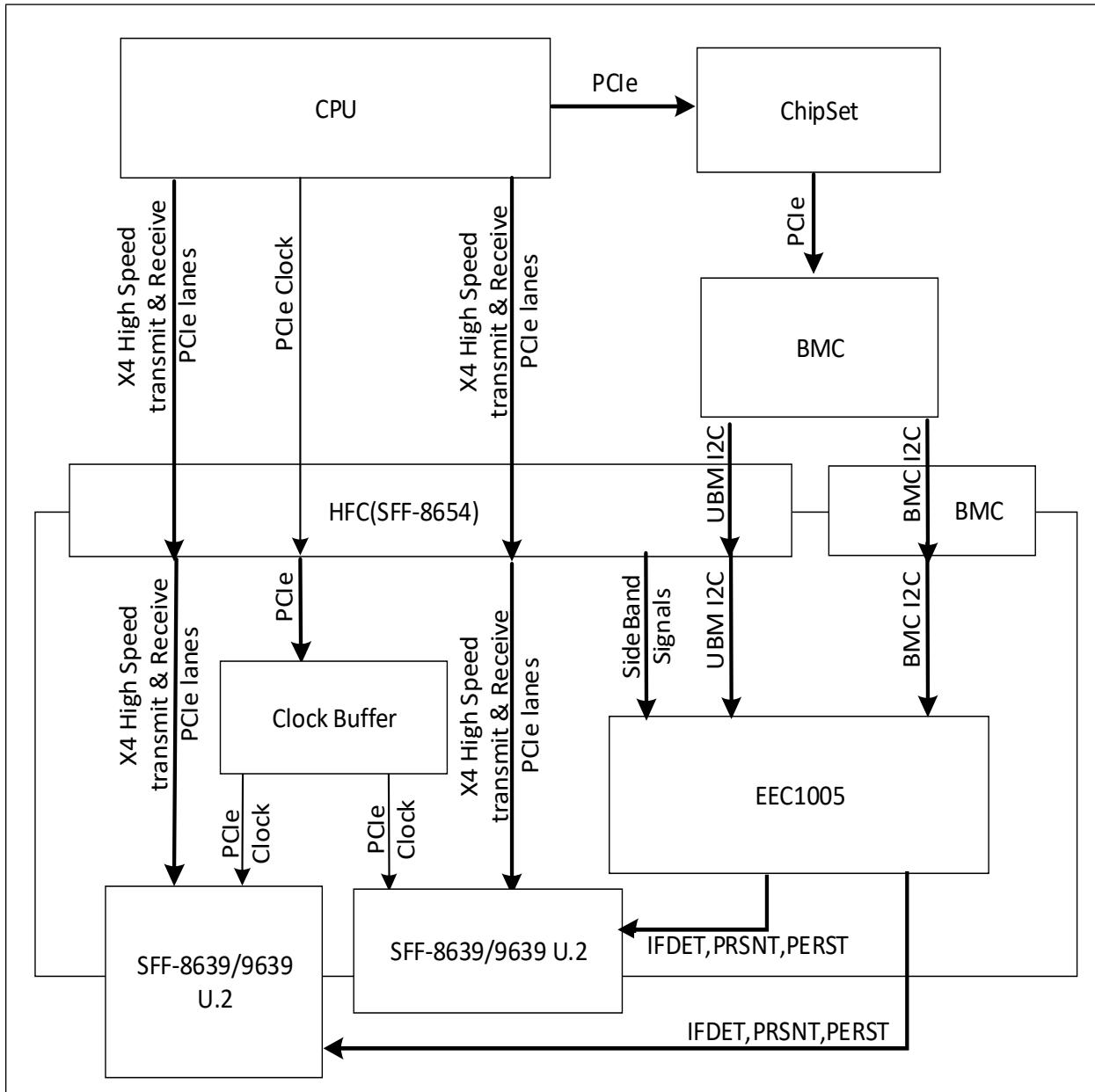

EEC1005 based backplane architectures are capable of supporting Y-cable configurations where the PCIe lanes from a single Host HFC will be split into 2x backplane HFC's, this allows splitting on PCIe clocks using clock buffers as shown in the following diagram.

## FIGURE 2-1: DIRECT ATTACH CONFIGURATION

## 2.2 Host Attach UBM Backplane

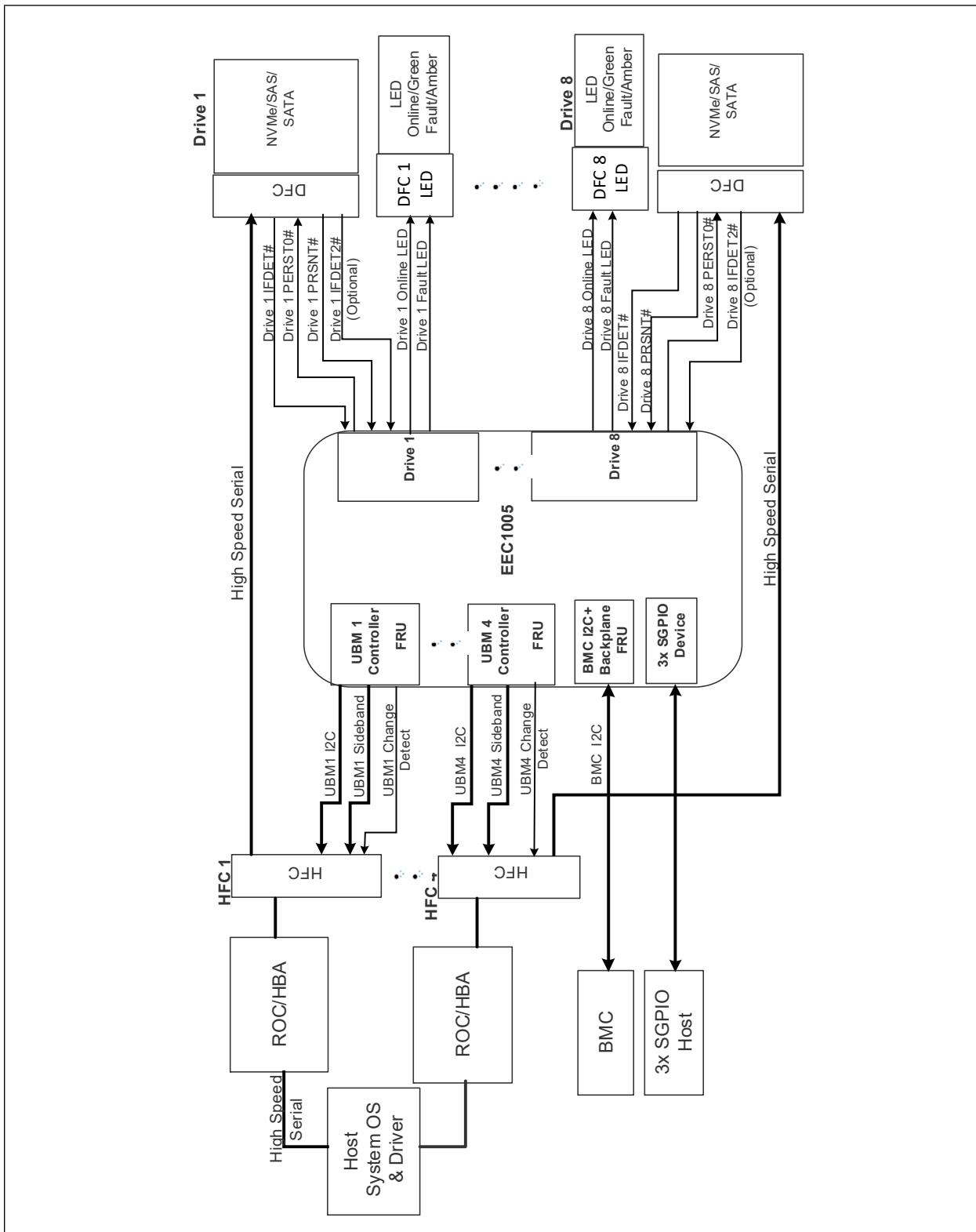

A Host attach configuration is enabled when user connects the backplane directly to SMARTROC/HBA and the drives are managed by an HBA. EEC1005 can be used in Host attach configuration as in [FIGURE 2-2: “Host Attach Configuration”](#). Each HFC is connected to a Host through a cable to communicate with EEC1005.

EEC1005 based backplane architecture supports NVME PERST functionality by allowing the Host to directly control the PERST signal. This allows the Host to directly control the reset behavior of NVME drive without adding any latency. The PERST signal will be driven from HFC and then split into 2 signals to control 2 drives from a single signal.

**Note:** The hardware bifurcation of the PCIe lanes is application dependent. Usually each HFC bifurcates x8 lanes into two x4 connections.

FIGURE 2-2: HOST ATTACH CONFIGURATION

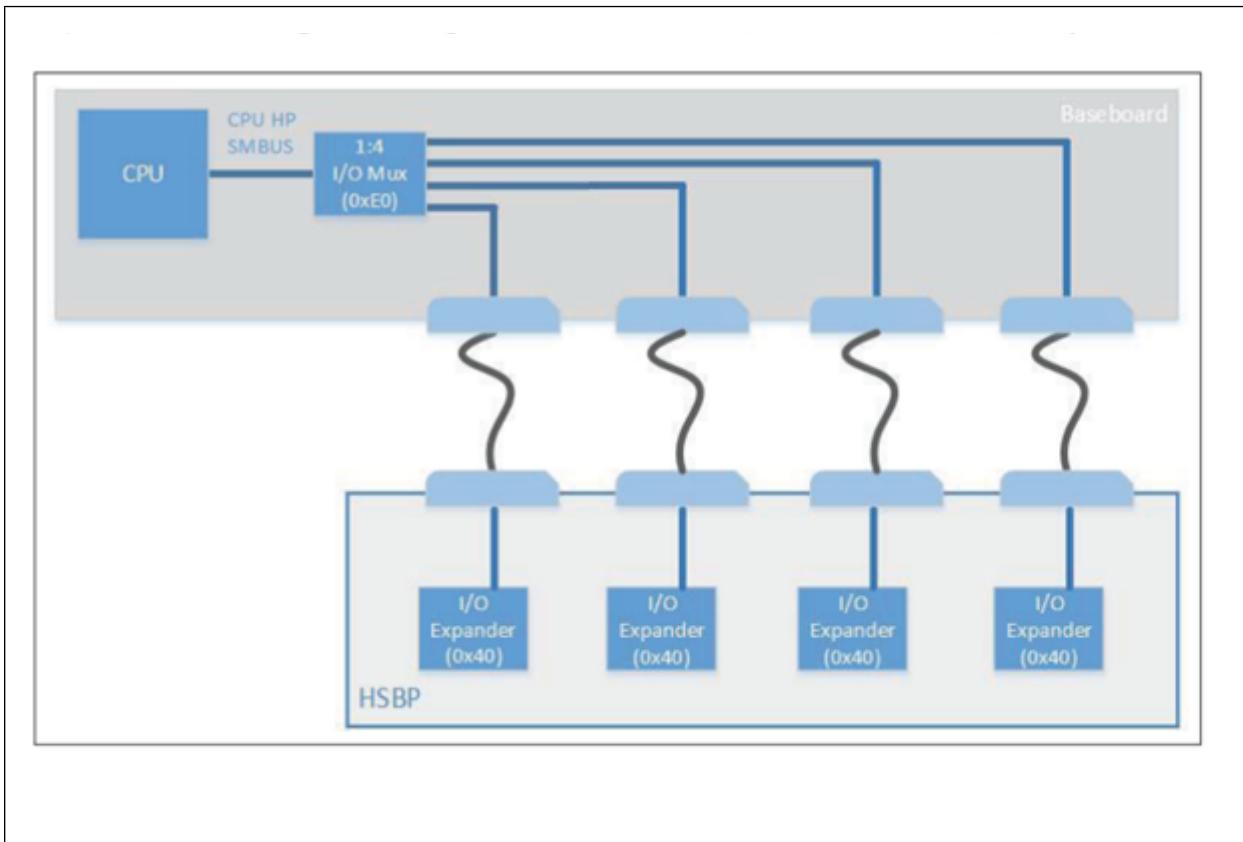

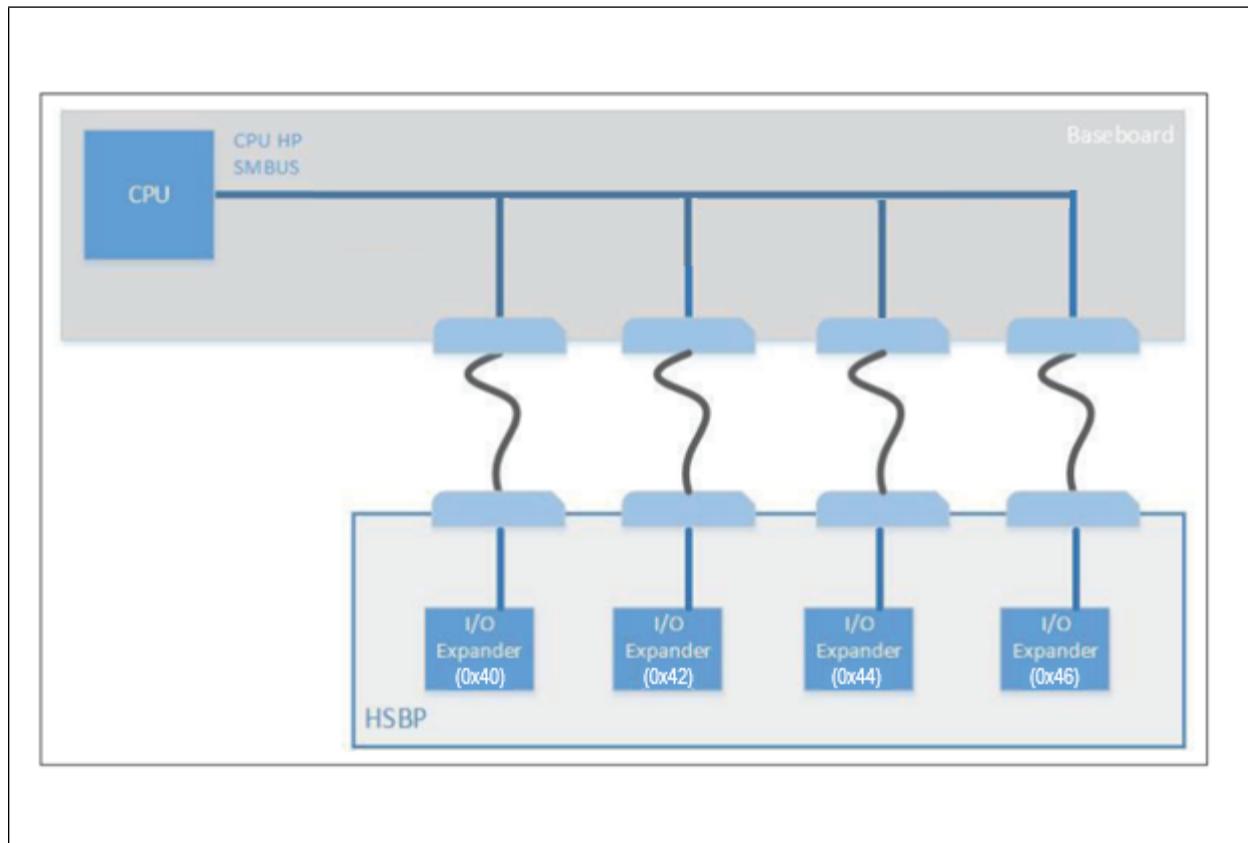

## 2.3 BMC-Tunneled I2C HFC Emulation

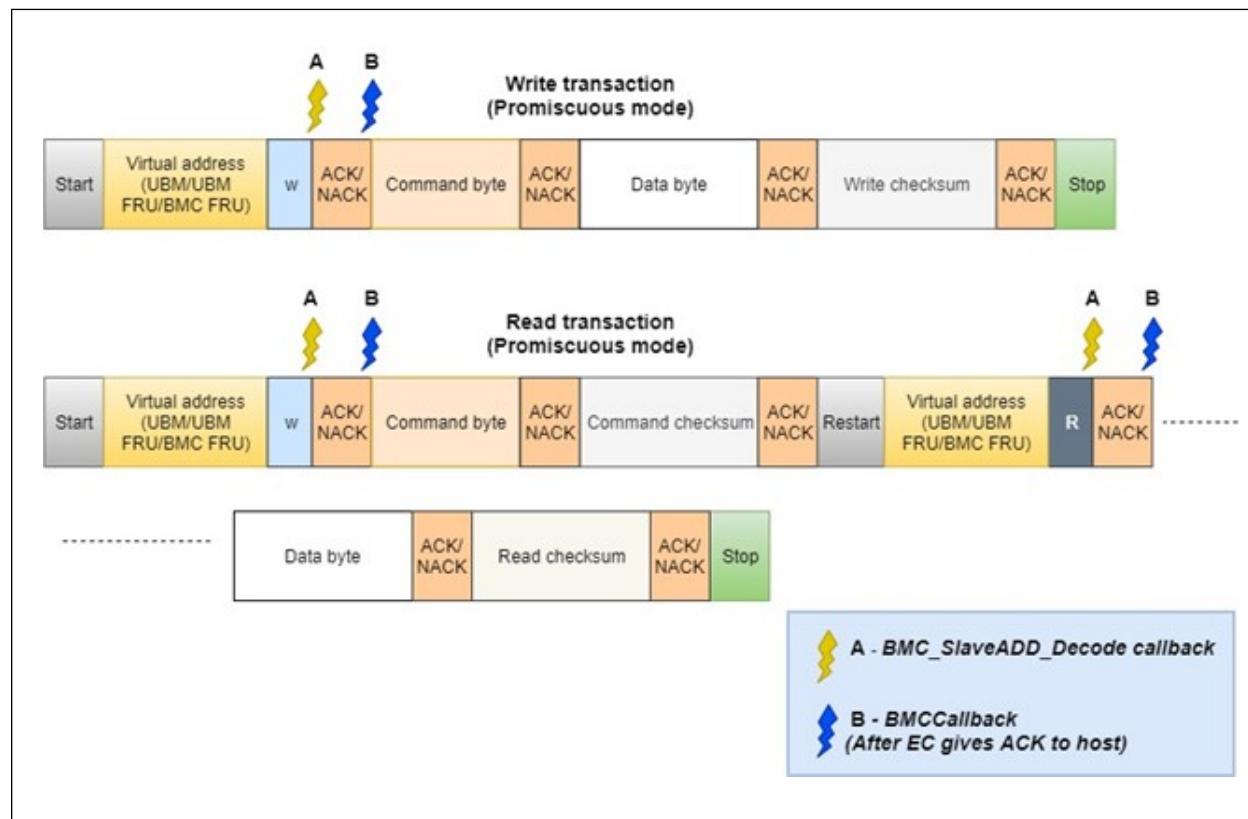

This feature is provided in order to bypass use of I2C connections from HFCs for UBM and FRU traffic, and instead to tunnel this traffic over the BMC's I2C link to the EEC.

The BMC-tunneled emulation is a method to virtualize the control of the supported UBM controllers on a backplane with BMC acting as the mediator between host and EEC. The BMC I2C interface must carry out the routing of the I2C commands supported by the UBM controller as per spec SFF-TA-1005. This section describes a high-level design of the communication interfaces, the message structure format from host to BMC and the routing of the I2C payload to the required UBM controller.

### 2.3.1 ASSUMPTIONS AND DEPENDENCIES

The message format between host and BMC is designed as per requirement need. This assumes that there is no specific standard defined for the message structure between host and BMC when communicating over I2C channel.

This assumes that the BMC is utilized only for routing the SFF-TA-1005 I2C commands to the required UBM controller. The I2C payload requested by host shall be for reading the UBM FRU's, controlling UBM controller and BMC FRU access alone.

### 2.3.2 SYSTEM DESIGN

The I2C payload transferred from host can address any of the devices listed below, by using their virtual addresses:

#### 1. UBMx FRUs

The virtual base address for UBM FRU access via BMC, in 8-bit format, is **0xAE**. An 'n' UBM FRU must be accessed using the below address byte calculated as:

$0xAE + (\text{HFC number})^2$

The virtual UBM controller FRU addresses for UBM0 – UBM5 controllers are:

UBM0 FRU – 0xAE

UBM1 FRU – 0xB0

UBM2 FRU – 0xB2

UBM3 FRU – 0xB4

UBM4 FRU – 0xB6

UBM5 FRU – 0xB8

#### 2. UBMx Controllers

The virtual base address for UBM access via BMC, in 8-bit format, is **0xD0**. An 'n' UBM controller must be accessed using the below address calculated as:

$0xD0 + (\text{HFC number})^2$

The virtual UBM controller addresses for UBM0 – UBM5 controllers are:

UBM0 – 0xD0

UBM1 – 0xD2

UBM2 – 0xD4

UBM3 – 0xD6

UBM4 – 0xD8

UBM5 – 0xDA

#### 3. Configuration FRU

The Configuration FRU access address, in 8-bit format, is **0xAA**. This memory device can be used by host to determine the number of HFC's as well.

There is only one instance of this device, and it is accessed this way through the BMC regardless of BMC-Tunneled capability. It is included here for completeness only.

#### 4. Generic FRU

The Generic FRU access address, in 8-bit format, is **0xA8**. This FRU is optionally used by Host, EEC doesn't apply this FRU.

There is only one instance of this device, and it is accessed this way through the BMC regardless of BMC-Tunneled capability. It is included here for completeness only.

## 2.3.3 MESSAGE FORMAT OF BMC-TUNNELED COMMANDS

The I2C payload from host to BMC shall have the following format, in **FIGURE 2-3: “BMC-Tunneled I2C Payload Format”**.

FIGURE 2-3: BMC-TUNNELED I2C PAYLOAD FORMAT

## 3.0 CONFIGURATIONS

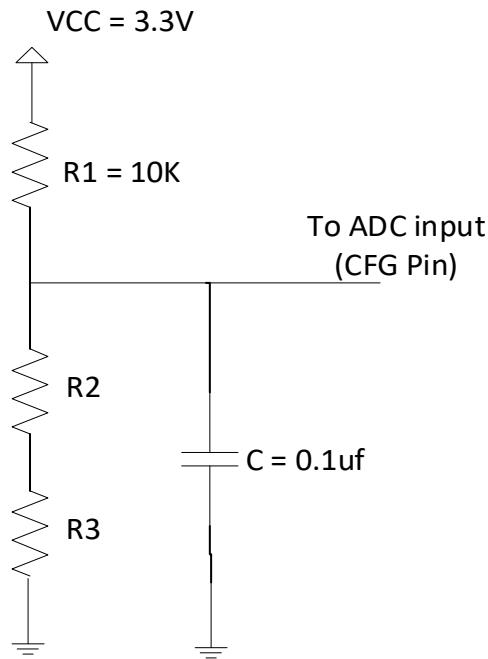

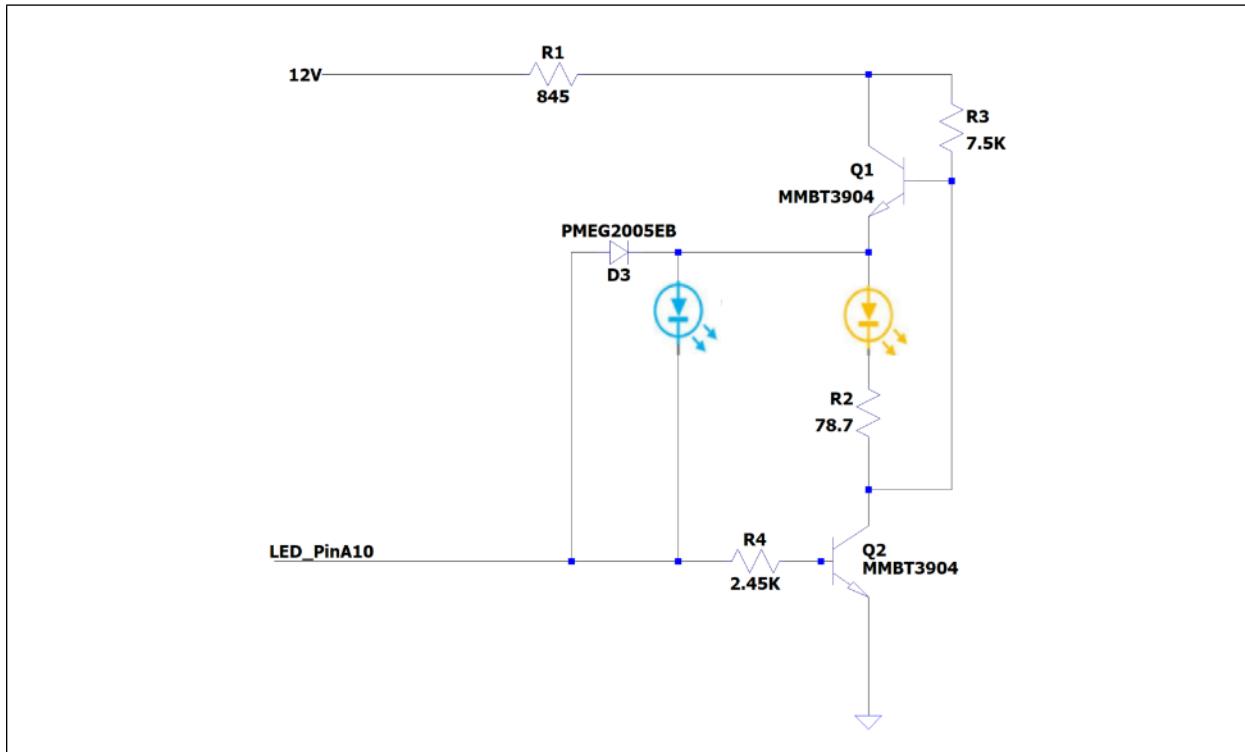

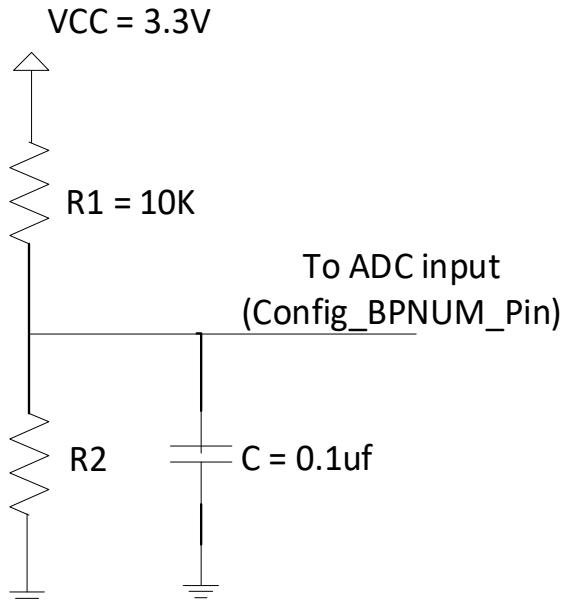

Multiple Backplane architectures are supported using EEC1005 that are configured by firmware based on an analog value sampled at one of EEC1005 input ADC pin (Config Pin) at startup. [Table 3-1, “EEC1005 Configuration Select”](#) provides the complete list of Configurations selectable based on the analog value on CONFIG\_PIN. The analog value can be set by a resistor divider network as in [Figure 3-1](#), the values of the resistors are user defined. The configuration is fixed for a Backplane and is not runtime modified. The recommendations on the resistor values are provided in [Table 3-2, “Recommended Resistor Values,” on page 13](#).

**Note:** Configuration IDs 0x0F through 0x17 below are supported only by the **UB2** family member device.

**TABLE 3-1: EEC1005 CONFIGURATION SELECT**

| EEC1005 Config <sup>a</sup>                      | Pin Count | ID   | Config (V) | Pinout                                                              | HFC Total <sup>b</sup> | HFC SAS | HFC PCIe | DFC Total | DFC SAS/SATA | DFC PCIe | DFC/HFC PCIe |

|--------------------------------------------------|-----------|------|------------|---------------------------------------------------------------------|------------------------|---------|----------|-----------|--------------|----------|--------------|

| 4 Drive GPIO                                     | 84        | 0x01 | 0.1        | <a href="#">Table 11-4, “GPIO Controller - 84 Pin Package”</a>      | 1                      | 1       | 0        | 4         | 4            | 0        | 0            |

| 8 Drive GPIO                                     | 84        | 0x02 | 0.2        | <a href="#">Table 11-4, “GPIO Controller - 84 Pin Package”</a>      | 1                      | 1       | 0        | 8         | 8            | 0        | 0            |

| 12 Drive GPIO                                    | 144       | 0x03 | 0.3        | <a href="#">Table 11-2, “GPIO Controller - 144 Pin Package”</a>     | 2                      | 2       | 0        | 12        | 12           | 0        | 0            |

| 16 Drive GPIO                                    | 144       | 0x04 | 0.4        | <a href="#">Table 11-2, “GPIO Controller - 144 Pin Package”</a>     | 2                      | 2       | 0        | 16        | 16           | 0        | 0            |

| 4 Drive UBM U.2                                  | 84        | 0x05 | 0.5        | <a href="#">Table 11-5, “UBM Controller - 84 Pin Package”</a>       | 3                      | 1       | 2        | 4         | 4            | 4        | 2            |

| 8 Drive UBM U.2                                  | 84        | 0x06 | 0.6        | <a href="#">Table 11-5, “UBM Controller - 84 Pin Package”</a>       | 5                      | 1       | 4        | 8         | 8            | 8        | 2            |

| 8 Drive UBM U.2 (Full Feature), Split Cable PCIe | 144       | 0x07 | 0.7        | <a href="#">Table 11-7, “UBM Controller - 144 Pin ALT Package”</a>  | 5                      | 1       | 4        | 8         | 8            | 8        | 4            |

| 8 Drive UBM U.3 (Min. Feature)                   | 84        | 0x08 | 0.8        | <a href="#">Table 11-5, “UBM Controller - 84 Pin Package”</a>       | 4                      | 4       | 4        | 8         | 8            | 8        | 2            |

| 8 Drive UBM U.3 (Full Feature)                   | 144       | 0x09 | 0.9        | <a href="#">Table 11-3, “UBM Controller - 144 Pin Package”</a>      | 4                      | 4       | 4        | 8         | 8            | 8        | 2            |

| 12 Drive UBM U.2 PCIe Only (Full Featured)       | 144       | 0x0A | 1.0        | <a href="#">Table 11-3, “UBM Controller - 144 Pin Package”</a>      | 6                      | 0       | 6        | 12        | 0            | 12       | 2            |

| 12 Drive UBM U.3 PCIe Only (Full Featured)       | 144       | 0x0B | 1.1        | <a href="#">Table 11-3, “UBM Controller - 144 Pin Package”</a>      | 6                      | 0       | 6        | 12        | 0            | 12       | 2            |

| <b>RESERVED</b><br>Do not select.                | N/A       | N/A  | 1.2        | N/A - Not for Customer designs.                                     | N/A                    | N/A     | N/A      | N/A       | N/A          | N/A      | N/A          |

| 8 Drive UBM+GPIO U.2                             | 144       | 0x0D | 1.3        | <a href="#">Table 11-6, “UBM_GPIO Controller - 144 Pin Package”</a> | 5                      | 1       | 4        | 8         | 8            | 8        | 2            |

**TABLE 3-1: EEC1005 CONFIGURATION SELECT**

|                                                                          |     |      |     |                                                    |     |     |     |     |     |     |     |

|--------------------------------------------------------------------------|-----|------|-----|----------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|

| 8 Drive UBM U.2<br>(Full Feature)                                        | 144 | 0x0E | 1.4 | Table 11-3, "UBM Controller - 144 Pin Package"     | 5   | 1   | 4   | 8   | 8   | 8   | 2   |

| 10 Drive UBM U.2<br>PCIE Only<br><b>UB2 Only</b>                         | 144 | 0x0F | 1.5 | Table 11-3, "UBM Controller - 144 Pin Package"     | 3   | 0   | 2   | 10  | 0   | 10  | 5   |

| 8 Drive UBM U.3<br>(Full Feature)<br>x2 Lanes<br><b>UB2 Only</b>         | 144 | 0x10 | 1.6 | Table 11-3, "UBM Controller - 144 Pin Package"     | 2   | 2   | 2   | 8   | 8   | 8   | 4   |

| 8 Drive UBM U.3<br>(Full Feature)<br>x1 Lanes<br><b>UB2 Only</b>         | 144 | 0x11 | 1.7 | Table 11-3, "UBM Controller - 144 Pin Package"     | 1   | 1   | 1   | 8   | 8   | 8   | 8   |

| <b>RESERVED</b><br>Do not select                                         | N/A | N/A  | 1.8 | N/A - Not for Customer designs.                    | N/A |

| 8 Drive UBM U.3<br>(Min. Feature)<br>x2 Lanes<br><b>UB2 Only</b>         | 84  | 0x13 | 1.9 | Table 11-5, "UBM Controller - 84 Pin Package"      | 2   | 2   | 2   | 8   | 8   | 8   | 4   |

| 8 Drive UBM U.3<br>(Min. Feature)<br>x1 Lanes<br><b>UB2 Only</b>         | 84  | 0x14 | 2.0 | Table 11-5, "UBM Controller - 84 Pin Package"      | 1   | 1   | 1   | 8   | 8   | 8   | 8   |

| 12 Drive UBM U.3<br>(Full Feature)<br>x1 Lanes<br><b>UB2 Only</b>        | 144 | 0x15 | 2.1 | Table 11-3, "UBM Controller - 144 Pin Package"     | 2   | 2   | 2   | 12  | 12  | 12  | 6   |

| 10 Drive UBM U.2<br>(Full Feature)<br>PCIE Only<br><b>UB2 Only</b>       | 144 | 0x16 | 2.2 | Table 11-3, "UBM Controller - 144 Pin Package"     | 2   | 0   | 2   | 10  | 0   | 10  | 5   |

| 8 Drive UBM U.2<br>(Full Feature)<br>Split Cable PCIe<br><b>UB2 Only</b> | 144 | 0x17 | 2.3 | Table 11-7, "UBM Controller - 144 Pin ALT Package" | 3   | 1   | 2   | 8   | 8   | 8   | 4   |

a. Configurations not mentioned in the above table, or marked RESERVED, are not supported by EEC1005, and will result in undefined operation if selected.

b. HFC Total is the number of host facing connectors required for a particular configuration.

Min. Feature Set consists of the following differences:

1. No signal HFC\_xx\_2WIRE\_RESET

2. No signal DFC\_xx\_IFDET\_2\_N

3. No signal DFC\_xx\_PWR\_DISABLE

**FIGURE 3-1: VOLTAGE DIVIDER AT ADC INPUT**

**TABLE 3-2: RECOMMENDED RESISTOR VALUES**

| EEC1005 Config                                               | Config (V) | Pinout                                                              | R2 (in Ohms) | R3(in Ohms) |

|--------------------------------------------------------------|------------|---------------------------------------------------------------------|--------------|-------------|

| 4 Drive GPIO                                                 | 0.1        | <a href="#">Table 11-4, "GPIO Controller - 84 Pin Package"</a>      | 301          | 11.5        |

| 8 Drive GPIO                                                 | 0.2        | <a href="#">Table 11-4, "GPIO Controller - 84 Pin Package"</a>      | 634          | 11          |

| 12 Drive GPIO                                                | 0.3        | <a href="#">Table 11-2, "GPIO Controller - 144 Pin Package"</a>     | 1000         | 0           |

| 16 Drive GPIO                                                | 0.4        | <a href="#">Table 11-2, "GPIO Controller - 144 Pin Package"</a>     | 1370         | 9.31        |

| 4 Drive UBM U.2                                              | 0.5        | <a href="#">Table 11-5, "UBM Controller - 84 Pin Package"</a>       | 1780         | 5.76        |

| 8 Drive UBM U.2                                              | 0.6        | <a href="#">Table 11-5, "UBM Controller - 84 Pin Package"</a>       | 2210         | 12.1        |

| 8 Drive UBM U.2 (Full Feature), Split cable PCIe             | 0.7        | <a href="#">Table 11-7, "UBM Controller - 144 Pin ALT Package"</a>  | 2610         | 82.5        |

| 8 Drive UBM U.3 (Minimum Feature)                            | 0.8        | <a href="#">Table 11-5, "UBM Controller - 84 Pin Package"</a>       | 3160         | 40.2        |

| 8 Drive UBM U.3 (Full Feature)                               | 0.9        | <a href="#">Table 11-3, "UBM Controller - 144 Pin Package"</a>      | 3740         | 10          |

| 12 Drive UBM U.2 PCIe Only (Full Featured)                   | 1.0        | <a href="#">Table 11-3, "UBM Controller - 144 Pin Package"</a>      | 4320         | 28          |

| 12 Drive UBM U.3 PCIe Only (Full Featured)                   | 1.1        | <a href="#">Table 11-3, "UBM Controller - 144 Pin Package"</a>      | 4990         | 10          |

| <b>RESERVED</b><br>Do not select.                            | 1.2        | N/A                                                                 | N/A          | N/A         |

| 8 Drive UBM+GPIO U.2                                         | 1.3        | <a href="#">Table 11-6, "UBM_GPIO Controller - 144 Pin Package"</a> | 6490         | 10          |

| 8 Drive UBM U.2 (Full Feature)                               | 1.4        | <a href="#">Table 11-3, "UBM Controller - 144 Pin Package"</a>      | 7320         | 48.7        |

| 10 Drive UBM U.2 PCIE Only (Full Feature)<br><b>UB2 Only</b> | 1.5        | <a href="#">Table 11-3, "UBM Controller - 144 Pin Package"</a>      | 7870         | 464         |

| 8 Drive UBM U.3 (Full Feature) x2 Lanes<br><b>UB2 Only</b>   | 1.6        | <a href="#">Table 11-3, "UBM Controller - 144 Pin Package"</a>      | 9310         | 102         |

# EEC1005

TABLE 3-2: RECOMMENDED RESISTOR VALUES (CONTINUED)

| EEC1005 Config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Config (V) | Pinout                                                             | R2 (in Ohms) | R3(in Ohms) |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------------------------------------------------------------|--------------|-------------|

| 8 Drive UBM U.3<br>(Full Feature) x1 Lanes<br><b>UB2 Only</b>                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1.7        | <a href="#">Table 11-3, "UBM Controller - 144 Pin Package"</a>     | 9760         | 866         |

| <b>RESERVED</b><br>Do not select.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1.8        | N/A                                                                | N/A          | N/A         |

| 8 Drive UBM U.3<br>(Min. Feature) x2 Lanes<br><b>UB2 Only</b>                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1.9        | <a href="#">Table 11-5, "UBM Controller - 84 Pin Package"</a>      | 10000        | 3570        |

| 8 Drive UBM U.3<br>(Min. Feature) x1 Lanes<br><b>UB2 Only</b>                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2.0        | <a href="#">Table 11-5, "UBM Controller - 84 Pin Package"</a>      | 15000        | 383         |

| 12 Drive UBM U.3<br>(Full Feature) x1 Lanes<br><b>UB2 Only</b>                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.1        | <a href="#">Table 11-3, "UBM Controller - 144 Pin Package"</a>     | 16500        | 1000        |

| 10 Drive UBM U.2<br>(Full Feature) PCIE Only<br><b>UB2 Only</b>                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.2        | <a href="#">Table 11-3, "UBM Controller - 144 Pin Package"</a>     | 20000        | 0           |

| 8 Drive UBM U.2<br>(Full Feature)<br>Split Cable PCIe<br><b>UB2 Only</b>                                                                                                                                                                                                                                                                                                                                                                                                                              | 2.3        | <a href="#">Table 11-7, "UBM Controller - 144 Pin ALT Package"</a> | 21500        | 1500        |

| <p><b>Note 1:</b> The resistor values suggested are based on the standard value resistors available @1% tolerance.</p> <p><b>2:</b> It is highly recommended to use 1% tolerant resistors at ADC input.</p> <p><b>3:</b> The ADC input capacitor should be 0.1uF.</p> <p><b>4:</b> The resistor R1 should be fixed at 10K.</p> <p><b>5:</b> Config values not mentioned in the above table, or marked RESERVED, are not supported by EEC1005, and will result in undefined operation if selected.</p> |            |                                                                    |              |             |

## 4.0 CONFIGURATION FRU

EEC1005 supports a 256-byte FRU (Field Replaceable Unit) that is used to initialize/input the parameters which are client specific. These parameters are read on power up as well as run time to initialize the firmware accordingly. This 256-byte FRU is accessible over BMC I2C segment, if used in an architecture where BMC exists.

**TABLE 4-1: CONFIGURATION FRU TABLE**

| Address | Group  | Field Name                                 | Pattern | LED Name | Parameters |

|---------|--------|--------------------------------------------|---------|----------|------------|

| 0x00    | Global | ACTIVITY/2WIRE_RESET OPTION                |         |          |            |

| 0x01    | Global | IBPI PATTERN 2/3 LED                       |         |          |            |

| 0x02    | Global | Backplane HFC Count                        |         |          |            |

| 0x03    | Global | Backplane DFC Count                        |         |          |            |

| 0x04    | Global | Backplane Physical Location                |         |          |            |

| 0x05    | Global | RSVD                                       |         |          |            |

| 0x06    | Global | RSVD                                       |         |          |            |

| 0x07    | Global | RSVD                                       |         |          |            |

| 0x08    | Global | RSVD                                       |         |          |            |

| 0x09    | Global | RSVD                                       |         |          |            |

| 0x0A    | Global | RSVD                                       |         |          |            |

| 0x0B    | Global | RSVD                                       |         |          |            |

| 0x0C    | Global | RSVD                                       |         |          |            |

| 0x0D    | Global | RSVD                                       |         |          |            |

| 0x0E    | Global | RSVD                                       |         |          |            |

| 0x0F    | Global | RSVD                                       |         |          |            |

| 0x10    | Global | RSVD                                       |         |          |            |

| 0x11    | Global | RSVD                                       |         |          |            |

| 0x12    | Global | RSVD                                       |         |          |            |

| 0x13    | Global | RSVD                                       |         |          |            |

| 0x14    | Global | CHECKSUM                                   |         |          |            |

| 0x15    | HFC0   | UBM CONTROLLER DEVICE CODE MSB             |         |          |            |

| 0x16    | HFC0   | UBM CONTROLLER DEVICE CODE                 |         |          |            |

| 0x17    | HFC0   | UBM CONTROLLER DEVICE CODE                 |         |          |            |

| 0x18    | HFC0   | UBM CONTROLLER DEVICE CODE LSB             |         |          |            |

| 0x19    | HFC0   | SILICON VENDOR ID VENDOR SPECIFIC 0        |         |          |            |

| 0x1A    | HFC0   | SILICON VENDOR ID VENDOR SPECIFIC 1        |         |          |            |

| 0x1B    | HFC0   | HFC IDENTITY                               |         |          |            |

| 0x1C    | HFC0   | CPRSNT# or CHANGE_DETECT#                  |         |          |            |

| 0x1D    | HFC0   | Clock Routing Capability                   |         |          |            |

| 0x1E    | HFC0   | PERST Management Override                  |         |          |            |

| 0x1F    | HFC0   | PERST Support ( <b>UB2 Only</b> )          |         |          |            |

| 0x20    | HFC0   | PWRDIS Support ( <b>UB2 Only</b> )         |         |          |            |

| 0x21    | HFC0   | VPP Address ( <b>UB2 Only</b> )            |         |          |            |

| 0x22    | HFC0   | VPP Interrupt Mode Bit ( <b>UB2 Only</b> ) |         |          |            |

| 0x23    | HFC0   | EDSFF SMBRST# Support ( <b>UB2 Only</b> )  |         |          |            |

| 0x24    | HFC0   | RSVD                                       |         |          |            |

| 0x25    | HFC0   | RSVD                                       |         |          |            |

TABLE 4-1: CONFIGURATION FRU TABLE (CONTINUED)

| Address | Group | Field Name                                 | Pattern | LED Name | Parameters |

|---------|-------|--------------------------------------------|---------|----------|------------|

| 0x26    | HFC0  | RSVD                                       |         |          |            |

| 0x27    | HFC0  | RSVD                                       |         |          |            |

| 0x28    | HFC0  | RSVD                                       |         |          |            |

| 0x29    | HFC0  | RSVD                                       |         |          |            |

| 0x2A    | HFC0  | RSVD                                       |         |          |            |

| 0x2B    | HFC0  | RSVD                                       |         |          |            |

| 0x2C    | HFC0  | CHECKSUM                                   |         |          |            |

| 0x2D    | HFC1  | UBM CONTROLLER DEVICE CODE MSB             |         |          |            |

| 0x2E    | HFC1  | UBM CONTROLLER DEVICE CODE                 |         |          |            |

| 0x2F    | HFC1  | UBM CONTROLLER DEVICE CODE                 |         |          |            |

| 0x30    | HFC1  | UBM CONTROLLER DEVICE CODE LSB             |         |          |            |

| 0x31    | HFC1  | SILICON VENDOR ID VENDOR SPECIFIC 0        |         |          |            |

| 0x32    | HFC1  | SILICON VENDOR ID VENDOR SPECIFIC 1        |         |          |            |

| 0x33    | HFC1  | HFC IDENTITY                               |         |          |            |

| 0x34    | HFC1  | CPRSNT# or CHANGE_DETECT#                  |         |          |            |

| 0x35    | HFC1  | Clock Routing Capability                   |         |          |            |

| 0x36    | HFC1  | PERST Management Override                  |         |          |            |

| 0x37    | HFC1  | PERST Support ( <b>UB2 Only</b> )          |         |          |            |

| 0x38    | HFC1  | PWRDIS Support ( <b>UB2 Only</b> )         |         |          |            |

| 0x39    | HFC1  | VPP Address ( <b>UB2 Only</b> )            |         |          |            |

| 0x3A    | HFC1  | VPP Interrupt Mode Bit ( <b>UB2 Only</b> ) |         |          |            |

| 0x3B    | HFC1  | EDSFF SMBRST# Support ( <b>UB2 Only</b> )  |         |          |            |

| 0x3C    | HFC1  | RSVD                                       |         |          |            |

| 0x3D    | HFC1  | RSVD                                       |         |          |            |

| 0x3E    | HFC1  | RSVD                                       |         |          |            |

| 0x3F    | HFC1  | RSVD                                       |         |          |            |

| 0x40    | HFC1  | RSVD                                       |         |          |            |

| 0x41    | HFC1  | RSVD                                       |         |          |            |

| 0x42    | HFC1  | RSVD                                       |         |          |            |

| 0x43    | HFC1  | RSVD                                       |         |          |            |

| 0x44    | HFC1  | CHECKSUM                                   |         |          |            |

| 0x45    | HFC2  | UBM CONTROLLER DEVICE CODE MSB             |         |          |            |

| 0x46    | HFC2  | UBM CONTROLLER DEVICE CODE                 |         |          |            |

| 0x47    | HFC2  | UBM CONTROLLER DEVICE CODE                 |         |          |            |

| 0x48    | HFC2  | UBM CONTROLLER DEVICE CODE LSB             |         |          |            |

| 0x49    | HFC2  | SILICON VENDOR ID VENDOR SPECIFIC 0        |         |          |            |

| 0x4A    | HFC2  | SILICON VENDOR ID VENDOR SPECIFIC 1        |         |          |            |

| 0x4B    | HFC2  | HFC IDENTITY                               |         |          |            |

| 0x4C    | HFC2  | CPRSNT# or CHANGE_DETECT#                  |         |          |            |

| 0x4D    | HFC2  | Clock Routing Capability                   |         |          |            |

| 0x4E    | HFC2  | PERST Management Override                  |         |          |            |

TABLE 4-1: CONFIGURATION FRU TABLE (CONTINUED)

| Address | Group | Field Name                          | Pattern | LED Name | Parameters |

|---------|-------|-------------------------------------|---------|----------|------------|

| 0x4F    | HFC2  | PERST Support (UB2 Only)            |         |          |            |

| 0x50    | HFC2  | PWRDIS Support (UB2 Only)           |         |          |            |

| 0x51    | HFC2  | VPP Address (UB2 Only)              |         |          |            |

| 0x52    | HFC2  | VPP Interrupt Mode Bit (UB2 Only)   |         |          |            |

| 0x53    | HFC2  | EDSFF SMBRST# Support (UB2 Only)    |         |          |            |

| 0x54    | HFC2  | RSVD                                |         |          |            |

| 0x55    | HFC2  | RSVD                                |         |          |            |

| 0x56    | HFC2  | RSVD                                |         |          |            |

| 0x57    | HFC2  | RSVD                                |         |          |            |

| 0x58    | HFC2  | RSVD                                |         |          |            |

| 0x59    | HFC2  | RSVD                                |         |          |            |

| 0x5A    | HFC2  | RSVD                                |         |          |            |

| 0x5B    | HFC2  | RSVD                                |         |          |            |

| 0x5C    | HFC2  | CHECKSUM                            |         |          |            |

| 0x5D    | HFC3  | UBM CONTROLLER DEVICE CODE MSB      |         |          |            |

| 0x5E    | HFC3  | UBM CONTROLLER DEVICE CODE          |         |          |            |

| 0x5F    | HFC3  | UBM CONTROLLER DEVICE CODE          |         |          |            |

| 0x60    | HFC3  | UBM CONTROLLER DEVICE CODE LSB      |         |          |            |

| 0x61    | HFC3  | SILICON VENDOR ID VENDOR SPECIFIC 0 |         |          |            |

| 0x62    | HFC3  | SILICON VENDOR ID VENDOR SPECIFIC 1 |         |          |            |

| 0x63    | HFC3  | HFC IDENTITY                        |         |          |            |

| 0x64    | HFC3  | CPRSNT# or CHANGE_DETECT#           |         |          |            |

| 0x65    | HFC3  | Clock Routing Capability            |         |          |            |

| 0x66    | HFC3  | PERST Management Override           |         |          |            |

| 0x67    | HFC3  | PERST Support (UB2 Only)            |         |          |            |

| 0x68    | HFC3  | PWRDIS Support (UB2 Only)           |         |          |            |

| 0x69    | HFC3  | VPP Address (UB2 Only)              |         |          |            |

| 0x6A    | HFC3  | VPP Interrupt Mode Bit (UB2 Only)   |         |          |            |

| 0x6B    | HFC3  | EDSFF SMBRST# Support (UB2 Only)    |         |          |            |

| 0x6C    | HFC3  | RSVD                                |         |          |            |

| 0x6D    | HFC3  | RSVD                                |         |          |            |

| 0x6E    | HFC3  | RSVD                                |         |          |            |

| 0x6F    | HFC3  | RSVD                                |         |          |            |

| 0x70    | HFC3  | RSVD                                |         |          |            |

| 0x71    | HFC3  | RSVD                                |         |          |            |

| 0x72    | HFC3  | RSVD                                |         |          |            |

| 0x73    | HFC3  | RSVD                                |         |          |            |

| 0x74    | HFC3  | CHECKSUM                            |         |          |            |

| 0x75    | HFC4  | UBM CONTROLLER DEVICE CODE MSB      |         |          |            |

| 0x76    | HFC4  | UBM CONTROLLER DEVICE CODE          |         |          |            |

| 0x77    | HFC4  | UBM CONTROLLER DEVICE CODE          |         |          |            |

| 0x78    | HFC4  | UBM CONTROLLER DEVICE CODE LSB      |         |          |            |

TABLE 4-1: CONFIGURATION FRU TABLE (CONTINUED)

| Address | Group | Field Name                               | Pattern | LED Name | Parameters |

|---------|-------|------------------------------------------|---------|----------|------------|

| 0x79    | HFC4  | SILICON VENDOR ID VENDOR SPECIFIC 0      |         |          |            |

| 0x7A    | HFC4  | SILICON VENDOR ID VENDOR SPECIFIC 1      |         |          |            |

| 0x7B    | HFC4  | HFC IDENTITY                             |         |          |            |

| 0x7C    | HFC4  | CPRSNT# or CHANGE_DETECT#                |         |          |            |

| 0x7D    | HFC4  | Clock Routing Capability                 |         |          |            |

| 0x7E    | HFC4  | PERST Management Override                |         |          |            |

| 0x7F    | HFC4  | PERST Support <b>(UB2 Only)</b>          |         |          |            |

| 0x80    | HFC4  | PWRDIS Support <b>(UB2 Only)</b>         |         |          |            |

| 0x81    | HFC4  | VPP Address <b>(UB2 Only)</b>            |         |          |            |

| 0x82    | HFC4  | VPP Interrupt Mode Bit <b>(UB2 Only)</b> |         |          |            |

| 0x83    | HFC4  | EDSFF SMBRST# Support <b>(UB2 Only)</b>  |         |          |            |

| 0x84    | HFC4  | RSVD                                     |         |          |            |

| 0x85    | HFC4  | RSVD                                     |         |          |            |

| 0x86    | HFC4  | RSVD                                     |         |          |            |

| 0x87    | HFC4  | RSVD                                     |         |          |            |

| 0x88    | HFC4  | RSVD                                     |         |          |            |

| 0x89    | HFC4  | RSVD                                     |         |          |            |

| 0x8A    | HFC4  | RSVD                                     |         |          |            |

| 0x8B    | HFC4  | RSVD                                     |         |          |            |

| 0x8C    | HFC4  | CHECKSUM                                 |         |          |            |

| 0x8D    | HFC5  | UBM CONTROLLER DEVICE CODE MSB           |         |          |            |

| 0x8E    | HFC5  | UBM CONTROLLER DEVICE CODE               |         |          |            |

| 0x8F    | HFC5  | UBM CONTROLLER DEVICE CODE               |         |          |            |

| 0x90    | HFC5  | UBM CONTROLLER DEVICE CODE LSB           |         |          |            |

| 0x91    | HFC5  | SILICON VENDOR ID VENDOR SPECIFIC 0      |         |          |            |

| 0x92    | HFC5  | SILICON VENDOR ID VENDOR SPECIFIC 1      |         |          |            |

| 0x93    | HFC5  | HFC IDENTITY                             |         |          |            |

| 0x94    | HFC5  | CPRSNT# or CHANGE_DETECT#                |         |          |            |

| 0x95    | HFC5  | Clock Routing Capability                 |         |          |            |

| 0x96    | HFC5  | PERST Management Override                |         |          |            |

| 0x97    | HFC5  | PERST Support <b>(UB2 Only)</b>          |         |          |            |

| 0x98    | HFC5  | PWRDIS Support <b>(UB2 Only)</b>         |         |          |            |

| 0x99    | HFC5  | VPP Address <b>(UB2 Only)</b>            |         |          |            |

| 0x9A    | HFC5  | VPP Interrupt Mode Bit <b>(UB2 Only)</b> |         |          |            |

| 0x9B    | HFC5  | EDSFF SMBRST# Support <b>(UB2 Only)</b>  |         |          |            |

| 0x9C    | HFC5  | RSVD                                     |         |          |            |

| 0x9D    | HFC5  | RSVD                                     |         |          |            |

| 0x9E    | HFC5  | RSVD                                     |         |          |            |

| 0x9F    | HFC5  | RSVD                                     |         |          |            |

| 0xA0    | HFC5  | RSVD                                     |         |          |            |

| 0xA1    | HFC5  | RSVD                                     |         |          |            |

TABLE 4-1: CONFIGURATION FRU TABLE (CONTINUED)

| Address | Group       | Field Name                                 | Pattern     | LED Name     | Parameters  |

|---------|-------------|--------------------------------------------|-------------|--------------|-------------|

| 0xA2    | HFC5        | RSVD                                       |             |              |             |

| 0xA3    | HFC5        | RSVD                                       |             |              |             |

| 0xA4    | HFC5        | CHECKSUM                                   |             |              |             |

| 0xA5    | HFC6        | UBM CONTROLLER DEVICE CODE MSB             |             |              |             |

| 0xA6    | HFC6        | UBM CONTROLLER DEVICE CODE                 |             |              |             |

| 0xA7    | HFC6        | UBM CONTROLLER DEVICE CODE                 |             |              |             |

| 0xA8    | HFC6        | UBM CONTROLLER DEVICE CODE LSB             |             |              |             |

| 0xA9    | HFC6        | SILICON VENDOR ID VENDOR SPECIFIC 0        |             |              |             |

| 0xAA    | HFC6        | SILICON VENDOR ID VENDOR SPECIFIC 1        |             |              |             |

| 0xAB    | HFC6        | HFC IDENTITY                               |             |              |             |

| 0xAC    | HFC6        | CPRSNT# or CHANGE_DETECT#                  |             |              |             |

| 0xAD    | HFC6        | Clock Routing Capability                   |             |              |             |

| 0xAE    | HFC6        | PERST Management Override                  |             |              |             |

| 0xAF    | HFC6        | PERST Support ( <b>UB2 Only</b> )          |             |              |             |

| 0xB0    | HFC6        | PWRDIS Support ( <b>UB2 Only</b> )         |             |              |             |

| 0xB1    | HFC6        | VPP Address ( <b>UB2 Only</b> )            |             |              |             |

| 0xB2    | HFC6        | VPP Interrupt Mode Bit ( <b>UB2 Only</b> ) |             |              |             |

| 0xB3    | HFC6        | EDSFF SMBRST# Support ( <b>UB2 Only</b> )  |             |              |             |

| 0xB4    | HFC6        | RSVD                                       |             |              |             |

| 0xB5    | HFC6        | RSVD                                       |             |              |             |

| 0xB6    | HFC6        | RSVD                                       |             |              |             |

| 0xB7    | HFC6        | RSVD                                       |             |              |             |

| 0xB8    | HFC6        | RSVD                                       |             |              |             |

| 0xB9    | HFC6        | RSVD                                       |             |              |             |

| 0xBA    | HFC6        | RSVD                                       |             |              |             |

| 0xBB    | HFC6        | RSVD                                       |             |              |             |

| 0xBC    | HFC6        | CHECKSUM                                   |             |              |             |

| 0xBD    | LED PATTERN | NOT_PRES_LED_ACT_BLINKP REP                | NOT_PRES    | LED_ACT      | BLINK-P REP |

| 0xBE    | LED PATTERN | NOT_PRES_LED_ACT_PAT_PERIOD                | NOT_PRES    | LED_ACT      | PAT_PERIOD  |

| 0xBF    | LED PATTERN | NOT_PRES_LED_STAorLOC_BLINKP REP           | NOT_PRES    | LED_STAorLOC | BLINK-P REP |

| 0xC0    | LED PATTERN | NOT_PRES_LED_STAorLOC_PAT_PERIOD           | NOT_PRES    | LED_STAorLOC | PAT_PERIOD  |

| 0xC1    | LED PATTERN | NOT_PRES_LED_FAIL_BLINKP REP               | NOT_PRES    | LED_FAIL     | BLINK-P REP |

| 0xC2    | LED PATTERN | NOT_PRES_LED_FAIL_PAT_PERIOD               | NOT_PRES    | LED_FAIL     | PAT_PERIOD  |

| 0xC3    | LED PATTERN | PRES_NO_ACT_LED_ACT_BLINKP REP             | PRES_NO_ACT | LED_ACT      | BLINK-P REP |

| 0xC4    | LED PATTERN | PRES_NO_ACT_LED_ACT_PAT_PERIOD             | PRES_NO_ACT | LED_ACT      | PAT_PERIOD  |

| 0xC5    | LED PATTERN | PRES_NO_ACT_LED_STAorLOC_BLINKP REP        | PRES_NO_ACT | LED_STAorLOC | BLINK-P REP |

TABLE 4-1: CONFIGURATION FRU TABLE (CONTINUED)

| Address | Group        | Field Name                           | Pattern      | LED Name      | Parameters  |

|---------|--------------|--------------------------------------|--------------|---------------|-------------|

| 0xC6    | LED PAT-TERN | PRES_NO_ACT_LED_STAor-LOC_PAT_PERIOD | PRES_NO_AC-T | LED_STAor-LOC | PAT_PE-RIOD |

| 0xC7    | LED PAT-TERN | PRES_NO_ACT_LED_FAIL_BLINKP REP      | PRES_NO_AC-T | LED_FAIL      | BLINK-P REP |

| 0xC8    | LED PAT-TERN | PRES_NO_ACT_LED_FAIL_PAT_PE-RIOD     | PRES_NO_AC-T | LED_FAIL      | PAT_PE-RIOD |

| 0xC9    | LED PAT-TERN | PRES_ACT_LED_ACT_BLINKP REP          | PRES_ACT     | LED_ACT       | BLINK-P REP |

| 0xCA    | LED PAT-TERN | PRES_ACT_LED_ACT_PAT_PERIOD          | PRES_ACT     | LED_ACT       | PAT_PE-RIOD |

| 0xCB    | LED PAT-TERN | PRES_ACT_LED_STAorLOC_BLINK-P REP    | PRES_ACT     | LED_STAor-LOC | BLINK-P REP |

| 0xCC    | LED PAT-TERN | PRES_ACT_LED_STAorLOC_PAT_PE-RIOD    | PRES_ACT     | LED_STAor-LOC | PAT_PE-RIOD |

| 0xCD    | LED PAT-TERN | PRES_ACT_LED_FAIL_BLINKP REP         | PRES_ACT     | LED_FAIL      | BLINK-P REP |

| 0xCE    | LED PAT-TERN | PRES_ACT_LED_FAIL_PAT_PERIOD         | PRES_ACT     | LED_FAIL      | PAT_PE-RIOD |

| 0xCF    | LED PAT-TERN | LOCATE_LED_ACT_BLINKP REP            | LOCATE       | LED_ACT       | BLINK-P REP |

| 0xD0    | LED PAT-TERN | LOCATE_LED_ACT_PAT_PERIOD            | LOCATE       | LED_ACT       | PAT_PE-RIOD |

| 0xD1    | LED PAT-TERN | LOCATE_LED_STAorLOC_BLINKP REP       | LOCATE       | LED_STAor-LOC | BLINK-P REP |

| 0xD2    | LED PAT-TERN | LOCATE_LED_STAorLOC_PAT_PERIOD       | LOCATE       | LED_STAor-LOC | PAT_PE-RIOD |

| 0xD3    | LED PAT-TERN | LOCATE_LED_FAIL_BLINKP REP           | LOCATE       | LED_FAIL      | BLINK-P REP |

| 0xD4    | LED PAT-TERN | LOCATE_LED_FAIL_PAT_PERIOD           | LOCATE       | LED_FAIL      | PAT_PE-RIOD |

| 0xD5    | LED PAT-TERN | FAIL_LED_ACT_BLINKP REP              | FAIL         | LED_ACT       | BLINK-P REP |

| 0xD6    | LED PAT-TERN | FAIL_LED_ACT_PAT_PERIOD              | FAIL         | LED_ACT       | PAT_PE-RIOD |

| 0xD7    | LED PAT-TERN | FAIL_LED_STAorLOC_BLINKP REP         | FAIL         | LED_STAor-LOC | BLINK-P REP |

| 0xD8    | LED PAT-TERN | FAIL_LED_STAorLOC_PAT_PERIOD         | FAIL         | LED_STAor-LOC | PAT_PE-RIOD |

| 0xD9    | LED PAT-TERN | FAIL_LED_FAIL_BLINKP REP             | FAIL         | LED_FAIL      | BLINK-P REP |

| 0xDA    | LED PAT-TERN | FAIL_LED_FAIL_PAT_PERIOD             | FAIL         | LED_FAIL      | PAT_PE-RIOD |

| 0xDB    | LED PAT-TERN | REBUILD_LED_ACT_BLINKP REP           | REBUILD      | LED_ACT       | BLINK-P REP |

| 0xDC    | LED PAT-TERN | REBUILD_LED_ACT_PAT_PERIOD           | REBUILD      | LED_ACT       | PAT_PE-RIOD |

| 0xDD    | LED PAT-TERN | REBUILD_LED_STAorLOC_BLINKP REP      | REBUILD      | LED_STAor-LOC | BLINK-P REP |

| 0xDE    | LED PAT-TERN | REBUILD_LED_STAorLOC_PAT_PERIOD      | REBUILD      | LED_STAor-LOC | PAT_PE-RIOD |

TABLE 4-1: CONFIGURATION FRU TABLE (CONTINUED)

| Address | Group        | Field Name                                              | Pattern   | LED Name      | Parameters  |

|---------|--------------|---------------------------------------------------------|-----------|---------------|-------------|

| 0xDF    | LED PAT-TERN | REBUILD_LED_FAIL_BLINKP REP                             | REBUILD   | LED_FAIL      | BLINK-P REP |

| 0xE0    | LED PAT-TERN | REBUILD_LED_FAIL_PAT_PERIOD                             | REBUILD   | LED_FAIL      | PAT_PE-RIOD |

| 0xE1    | LED PAT-TERN | PFA_LED_ACT_BLINKP REP                                  | PFA       | LED_ACT       | BLINK-P REP |

| 0xE2    | LED PAT-TERN | PFA_LED_ACT_PAT_PERIOD                                  | PFA       | LED_ACT       | PAT_PE-RIOD |

| 0xE3    | LED PAT-TERN | PFA_LED_STAorLOC_BLINKP REP                             | PFA       | LED_STAor-LOC | BLINK-P REP |

| 0xE4    | LED PAT-TERN | PFA_LED_STAorLOC_PAT_PERIOD                             | PFA       | LED_STAor-LOC | PAT_PE-RIOD |

| 0xE5    | LED PAT-TERN | PFA_LED_FAIL_BLINKP REP                                 | PFA       | LED_FAIL      | BLINK-P REP |

| 0xE6    | LED PAT-TERN | PFA_LED_FAIL_PAT_PERIOD                                 | PFA       | LED_FAIL      | PAT_PE-RIOD |

| 0xE7    | LED PAT-TERN | TEST_MODE_LED_ACT_BLINKP REP<br><b>(UB2 Only)</b>       | TEST MODE | LED_ACT       | BLINK-P REP |

| 0xE8    | LED PAT-TERN | TEST_MODE_LED_ACT_PAT_PERIOD<br><b>(UB2 Only)</b>       | TEST MODE | LED_ACT       | PAT_PE-RIOD |

| 0xE9    | LED PAT-TERN | TEST_MODE_LED_STAorLOC_BLINKP REP<br><b>(UB2 Only)</b>  | TEST MODE | LED_STAor-LOC | BLINK-P REP |

| 0xEA    | LED PAT-TERN | TEST_MODE_LED_STAorLOC_PAT_PE-RIOD<br><b>(UB2 Only)</b> | TEST MODE | LED_STAor-LOC | PAT_PE-RIOD |

| 0xEB    | LED PAT-TERN | TEST_MODE_LED_FAIL_BLINKP REP<br><b>(UB2 Only)</b>      | TEST MODE | LED_FAIL      | BLINK-P REP |

| 0xEC    | LED PAT-TERN | TEST_MODE_LED_FAIL_PAT_PERIOD<br><b>(UB2 Only)</b>      | TEST MODE | LED_FAIL      | PAT_PE-RIOD |

| 0xED    | LED PAT-TERN | RSVD                                                    |           |               |             |

| 0xEE    | LED PAT-TERN | RSVD                                                    |           |               |             |

| 0xEF    | LED PAT-TERN | RSVD                                                    |           |               |             |

| 0xF0    | LED PAT-TERN | RSVD                                                    |           |               |             |

| 0xF1    | LED PAT-TERN | RSVD                                                    |           |               |             |

| 0xF2    | LED PAT-TERN | RSVD                                                    |           |               |             |

| 0xF3    | LED PAT-TERN | RSVD                                                    |           |               |             |

| 0xF4    | LED PAT-TERN | RSVD                                                    |           |               |             |

| 0xF5    | LED PAT-TERN | RSVD                                                    |           |               |             |

| 0xF6    | LED PAT-TERN | RSVD                                                    |           |               |             |

| 0xF7    | LED PAT-TERN | RSVD                                                    |           |               |             |

**TABLE 4-1: CONFIGURATION FRU TABLE (CONTINUED)**

| Address | Group        | Field Name | Pattern | LED Name | Parameters |

|---------|--------------|------------|---------|----------|------------|

| 0xF8    | LED PAT-TERN | RSVD       |         |          |            |

| 0xF9    | LED PAT-TERN | RSVD       |         |          |            |

| 0xFA    | LED PAT-TERN | RSVD       |         |          |            |

| 0xFB    | LED PAT-TERN | RSVD       |         |          |            |

| 0xFC    | LED PAT-TERN | RSVD       |         |          |            |

| 0xFD    | LED PAT-TERN | RSVD       |         |          |            |

| 0xFE    | LED PAT-TERN | RSVD       |         |          |            |

| 0xFF    | LED PAT-TERN | CHECKSUM   |         |          |            |

**Note 1:** For Solid State ON, PAT\_PERIOD = 0x00 and BLINKP REP = 0x01

**2:** For Solid State OFF, PAT\_PERIOD = 0x00 and BLINKP REP = 0x00

**3:** PAT\_PERIOD = 0x28 means Not Solid State

**4:** BLINKP REP = 0x54 means 1Hz

**5:** Each count of registers increments in 25mS Intervals

**6:** PAT\_PERIOD defines the total period of the blink pattern. After it expires the pattern will repeat itself

**7:** BLINKP REP defines the period in which the LED will be ON/OFF

**8:** IBPI PATTERN 2/3 (Address 0x01) selects: 0x00 = 2-LED configuration, 0x01 = 3-LED configuration.

## 5.0 GENERIC FRU

EEC1005 has a Generic FRU space which customer can use as non volatile storage. 256 bytes are allocated for this Customer defined Generic FRU. This memory emulates AT24C02 256 byte I2C EEPROM. Read and write of data to this FRU space can be done by host over the same physical I2C interface connected to BMC at I2C target address 0xA8 in 8-bit format (0x54 in 7-bit format).

## 6.0 UBM FRU

The SFF-TA-1005 (UBM) Specification calls out for an external Field Replaceable Unit (FRU) per every UBM Controller. EEC1005 incorporates a UBM FRU for every UBM Controller as per the spec requirement within EEC1005 Memory space. This saves board space and cost.

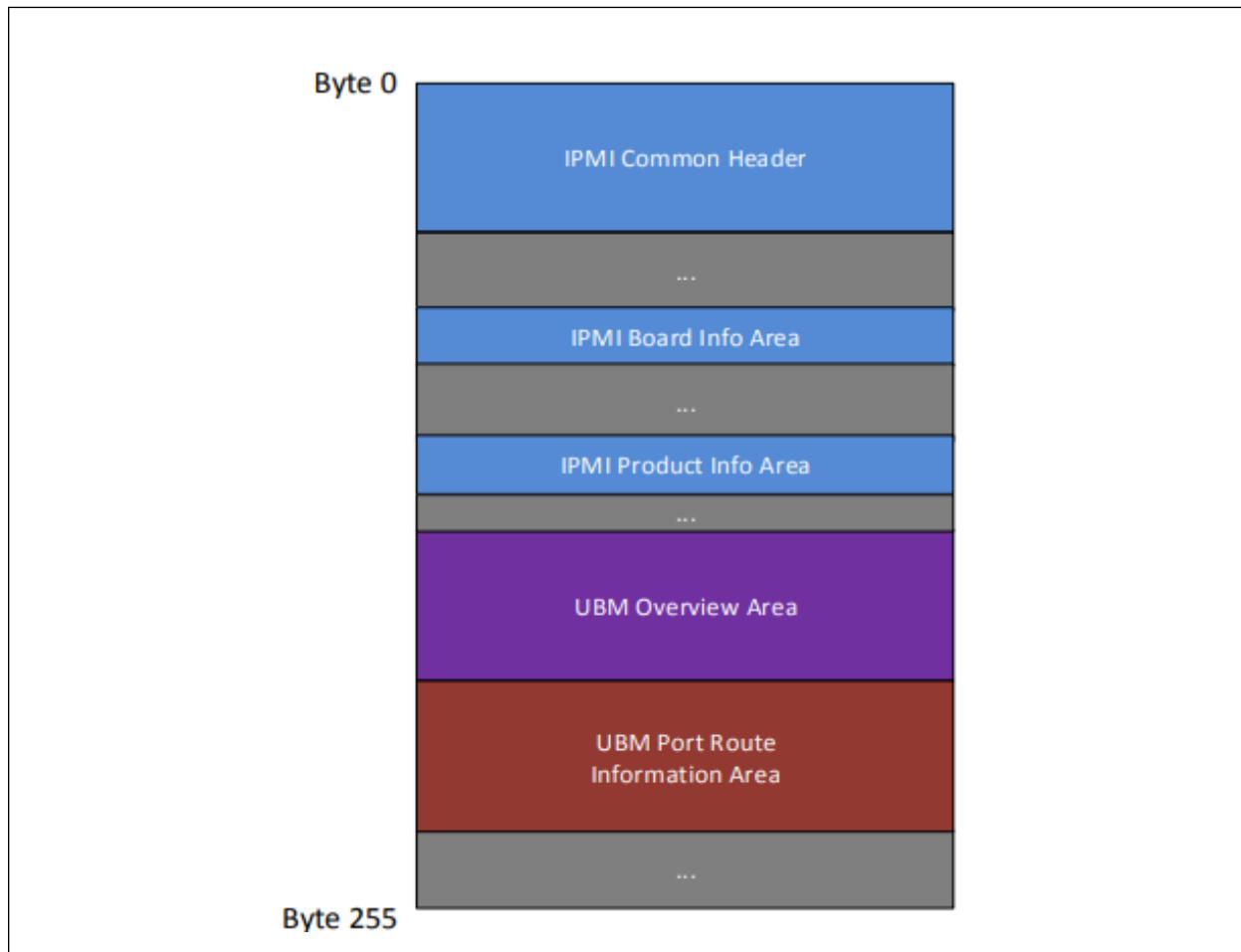

The UBM FRU on backplane is a 256 byte read-only NVRAM with IPMI FRU formatted content and is responsible for reporting static backplane information.

**FIGURE 6-1: UBM FRU FORMAT**

**FIGURE 6-2: UBM FRU**

The UBM FRU is addressed as specified by SFF-TA-1005, over Target Address 0xAE (8-bit format).

## 7.0 UBM CONTROLLER COMMANDS

The UBM Controller manages the Host facing Connector sideband I/O signaling, the Drive facing connector I/O signaling and the LED states for the DFC. It provides backplane implementation features and options for the initialization of the devices. These features are selected for the device through the CONFIG\_PIN (Section 11.3, "Pin List") as explained in Section 3.0, "Configurations".

Below is listed the UBM command set as taken from SFF-TA-1005. There are variables in UBM that are client specific; for example, the "Vendor Specific" bytes of the Silicon Identity and Revision Command. The EEC1005 allows clients to initialize those variables from FRU, and the UBM registers are initialized to these values on power up.

**TABLE 7-1: SUMMARY OF UBM COMMANDS**

| Command Code | Direction  | SFF-TA-1005 Command Name                | Notes for EEC1005                                                             |

|--------------|------------|-----------------------------------------|-------------------------------------------------------------------------------|

| 0x00         | Read Only  | Operational State                       | Fully Implemented                                                             |

| 0x01         | Read Only  | Last Command Status                     | Fully Implemented                                                             |

| 0x02         | Read Only  | Silicon Identity and Version            | See <a href="#">Section 7.1 "Silicon Identity and Version (0x02)"</a>         |

| 0x03         | Read Only  | Programming Update Mode Capabilities    | See <a href="#">Section 7.2 "Programming Update Mode Capabilities (0x03)"</a> |

| 0x04--0x1F   | --         | None (Reserved)                         |                                                                               |

| 0x20         | Read/Write | Enter Programmable Update Mode          | Fully Implemented                                                             |

| 0x21         | Read/Write | Programmable Mode Data Transfer         | Fully Implemented                                                             |

| 0x22         | Read/Write | Exit Programmable Update Mode           | Fully Implemented                                                             |

| 0x23--0x2F   | --         | None (Reserved)                         |                                                                               |

| 0x30         | Read Only  | Host Facing Connector Info              | See <a href="#">Section 7.3 "Host Facing Connector Info (0x30)"</a>           |

| 0x31         | Read Only  | Backplane Info                          | See <a href="#">Section 7.4 "Backplane Info (0x31)"</a>                       |

| 0x32         | Read Only  | Starting Slot                           | See <a href="#">Section 7.5 "Starting Slot (0x32)"</a>                        |

| 0x33         | Read Only  | Capabilities                            | See <a href="#">Section 7.6 "Capabilities (0x33)"</a>                         |

| 0x34         | Read/Write | Features                                | See <a href="#">Section 7.7 "Features (0x34)"</a>                             |

| 0x35         | Read/Write | Change Count                            | Fully Implemented                                                             |

| 0x36         | Read/Write | DFC Status and Control Descriptor Index | Fully Implemented                                                             |

| 0x37--0x3F   | --         | None (Reserved)                         |                                                                               |

| 0x40         | Read/Write | DFC Status and Control Descriptor       | Fully Implemented                                                             |

| 0x41--0x4F   | --         | None (Reserved)                         |                                                                               |

| 0x50--0x9F   | --         | None (Reserved)                         |                                                                               |

| 0xA0--0xAF   | --         | None (Vendor Specific)                  |                                                                               |

| 0xB0--0xFF   | --         | None (Reserved)                         |                                                                               |

The **UB1** device can declare only UBM Spec Version 1.3 below. The **UB2** device can declare Version 1.3 or 1.4. Version 1.4 adds a declaration for DFC SMBus Reset Control Support, in the Capabilities word (0x33 below), and a bit for DFC SMBus Reset Control in the Features word (0x34 below).

## 7.1 Silicon Identity and Version (0x02)

| Byte/Bit | 7                          | 6 | 5 | 4                                                               | 3                                                                         | 2 | 1 | 0 |

|----------|----------------------------|---|---|-----------------------------------------------------------------|---------------------------------------------------------------------------|---|---|---|

| 0        | UBM Spec Major Version = 1 |   |   |                                                                 | UBM Spec Minor Version = 3 (UB1)<br>UBM Spec Minor Version = 3 or 4 (UB2) |   |   |   |

| 1        |                            |   |   | PCIE Vendor ID (LSB) = 0x54                                     |                                                                           |   |   |   |

| 2        |                            |   |   | PCIE Vendor ID (MSB) = 0x00                                     |                                                                           |   |   |   |

| 3        |                            |   |   |                                                                 | RESERVED = 0x00                                                           |   |   |   |

| 4        |                            |   |   | UBM Controller Device Code (LSB) = Configuration FRU            |                                                                           |   |   |   |

| 5        |                            |   |   | UBM Controller Device Code = Configuration FRU                  |                                                                           |   |   |   |

| 6        |                            |   |   |                                                                 |                                                                           |   |   |   |

| 7        |                            |   |   | UBM Controller Device Code (MSB) = Configuration FRU            |                                                                           |   |   |   |

| 8        |                            |   |   |                                                                 | RESERVED = 0x0000                                                         |   |   |   |

| 9        |                            |   |   |                                                                 |                                                                           |   |   |   |

| 10       |                            |   |   | UBM Controller Image Version Minor = Backplane FW Minor Version |                                                                           |   |   |   |

| 11       |                            |   |   | UBM Controller Image Version Major = Backplane FW Major Version |                                                                           |   |   |   |

| 12       |                            |   |   | Vendor Specific = Configuration FRU                             |                                                                           |   |   |   |

| 13       |                            |   |   |                                                                 |                                                                           |   |   |   |

## 7.2 Programming Update Mode Capabilities (0x03)

| Byte/Bit | 7    | 6 | 5 | 4 | 3 | 2 | 1                  | 0 |

|----------|------|---|---|---|---|---|--------------------|---|

| 0        | RSVD |   |   |   |   |   | Update Mode = 0x01 |   |

Update Mode: The update mode will be set to 0x01 to indicate that update is supported while the device remains online. In order to support the non-destructive status of NVME drives while the update is being performed the GPIOs status will remain consistent across a firmware reset.

## 7.3 Host Facing Connector Info (0x30)

| Byte/Bit | 7                                 | 6          | 5 | 4 | 3                                                  | 2 | 1 | 0 |

|----------|-----------------------------------|------------|---|---|----------------------------------------------------|---|---|---|

| 0        | Port Type = 1 (PCIe)<br>= 0 (SAS) | RSVD = 0x0 |   |   | Host Facing Connector Identity = Configuration FRU |   |   |   |

Host Facing Connector ID will start from 0 and will report SAS HFC first followed by NVME HFC

PORT TYPE: HFCs that are SAS/SATA shall report Port Type = 0. HFCs that are PCIe shall report Port Type = 1.

## 7.4 Backplane Info (0x31)

| Byte/Bit | 7              | 6 | 5        | 4 | 3                                    | 2 | 1 | 0 |

|----------|----------------|---|----------|---|--------------------------------------|---|---|---|

| 0        | Backplane Type |   | RSVD = 0 |   | Backplane Number = Configuration FRU |   |   |   |

The Backplane Type will represent the Configuration selected from Config Pin. The Backplane Number will be read from Configuration FRU or configured based on input voltage on CONFIG\_BPNUM\_PIN.

## 7.5 Starting Slot (0x32)

| Byte/Bit | 7 | 6 |  | 5 | 4                    | 3 | 2 | 1 | 0 |

|----------|---|---|--|---|----------------------|---|---|---|---|

| 0        |   |   |  |   | Starting Slot = 0x00 |   |   |   |   |

Starting Slot is fixed to 0x0.

## 7.6 Capabilities (0x33)

| Byte/Bit | 7                    | 6                     | 5                                                                     | 4                                         | 3                     | 2                      | 1                                 | 0 |

|----------|----------------------|-----------------------|-----------------------------------------------------------------------|-------------------------------------------|-----------------------|------------------------|-----------------------------------|---|

| 0        | DFC Change Count = 1 | Change Detect Int = 1 | 2-Wire Reset = 2h                                                     | Dual Port = 0b                            | PCIe Reset Control =1 | Slot Power Control = 1 | Clock Routing = Configuration FRU |   |

| 1        | RSVD = 0x0           |                       | DFC SMBus Reset Control Support = 0 (UB1) =1 ( <b>UB2</b> ) for EDSFF | DFC PERST# Management Override support =1 | IFDET2 = 0 or 1*      | IFDET1 = 1 P4          | PRSNT = 1 P10                     |   |

CLOCK ROUTING: Set to 0 for SAS HFCS. Set to 1 for PCIe HFCs.

SLOT POWER CONTROL: Set to 1. DFCs with SAS drives will support Slot Power Control if a backplane configuration supports Power Disable Pin

PCIE RESET CONTROL: Set to 1.

DUAL PORT: Set to 0. Single ported only.

2-WIRE RESET: Set to 2h. 2-wire reset is supported. UBM FRU and UBM Controller is supported; 2Wire Mux is not supported.

CHANGE DETECT: Set to 1. One Change Detect interrupt supported per backplane HFC.

DFC CHANGE COUNT : Set to 1. Indicates if a change count is maintained per an individual DFC Status and Control Command Descriptor.

PRSNT: Set to 1. Indicates that the DFCs connected to this HFC support the PRSNT signal.

IFDET1: Set to 1. Indicates that the DFCs connected to this HFC support the IFDET1 signal.

IFDET2: This bit will be set to 1 if it is a U.3 backplane and to 0 if it is a U.2 backplane

DFC PERST# MANAGEMENT OVERRIDE : Set to 1, Override supported

DFC SMBus Reset Control Support: Presented as 0 by **UB1** parts. Feature is recognized only by **UB2** parts, but is declared here as 1 only for EDSFF drive control. The pin LED\_ACT\_N is used to present the SMBRST# signal in this case.

## 7.7 Features (0x34)

| Byte/Bit | 7                              | 6                           | 5                           | 4                           | 3                          | 2                   | 1                       | 0 |

|----------|--------------------------------|-----------------------------|-----------------------------|-----------------------------|----------------------------|---------------------|-------------------------|---|

| 0        | DFC PERST# Management Override | Operational State Mask = 1b | Drive Type Change Mask = 1b | PCIe Reset Change Mask = 1b | CPRSTN = Configuration FRU | Write Checksum = 1b | Read Checksum = 1b      |   |

| 1        | RSVD = 0x0                     |                             |                             |                             |                            |                     | DFC SMBus Reset Control |   |

READ CHECKSUM: Set to 1.

WRITE CHECKSUM CHECKING: Set to 1.

CPRSTN LEGACY MODE: Set to 0.

PCIE RESET CHANGE MASK: Set to 1.

DRIVE TYPE INSTALLED CHANGE COUNT MASK: Set to 1

OPERATIONAL STATE CHANGE COUNT MASK: Set to 1.

DFC PERST# MANAGEMENT OVERRIDE : Indicates the DFC\_PERST# behaviour when a drive has been installed

0 = No override

1 = DFC PERST# Managed upon install

2 = DFC PERST# Automatically released upon install

3 = Reserved

DFC SMBUS RESET CONTROL: Present only in UB2 parts, and only in EDSFF drive environment (Capabilities Byte 1 bit[4] = '1'.)

0 = No action taken. (default)

1 = SMBRST# signal is presented low for 1 ms min, on the LED\_ACT\_N pin. Bit returns to '0' when finished.

## 8.0 LED SPECIFICATIONS

The EEC1005 UB1 and UB2 family members both support two LED's per every DFC, on the pins `xxx_LED_ACT_N` (Activity) and `xxx_LED_STA_N` (Status), with IBPI patterns presented for various Drive states as defined in [Section 8.1, "Two-LED Configurations \(UB1 and UB2\)".](#)

In addition, the **UB2** family member can support the Three-LED IBPI standard as follows:

1. Support three LEDs (Activity, Locate and Fail) using the `LED_ACT_N` pin for Activity, and the `LED_STA_N` pin for both Fail and Locate as defined in [Section 8.2, "Three-LED Configurations \(UB2 Only\)".](#)

2. Support two of the three LEDs in EDSFF environments (Fail/Amber and Locate/Blue), using only the `LED_STA_N` pin as defined in [Section 8.2.1, "Three-LED Configurations For EDSFF".](#)

These can be controlled directly from the Host or from the EEC1005, as selected using the Configuration FRU (Address 0x01):

- 0x00 in this byte selects Two-LED configuration, and

- 0x01 (recognized only in **UB2** parts) selects Three-LED configuration.

Three-LED configuration must be explicitly selected for EDSFF designs, because this setting is not automatically assumed or imposed by the selection of EDSFF support elsewhere.

Configurable LED blink frequency/duty cycle are also supported via the Configuration FRU in order to support blink patterns that are outside the IBPI standard.