**FEATURES**

**48 kHz I<sup>2</sup>S/TDM digital output**

**High resolution: 14 bits**

**Directly compatible with the AD2425W, AD2428W, and

AD2429W A<sup>2</sup>B transceivers**

**User selectable bandwidth: 500 Hz to 4 kHz**

**Low latency: 90  $\mu\text{s}$  typical at 4 kHz bandwidth**

**Low noise**

**55  $\mu\text{g}/\sqrt{\text{Hz}}$  typical for x- and y-axes**

**120  $\mu\text{g}/\sqrt{\text{Hz}}$  typical for z-axis**

**Operating temperature range:  $-40^\circ\text{C}$  to  $+125^\circ\text{C}$**

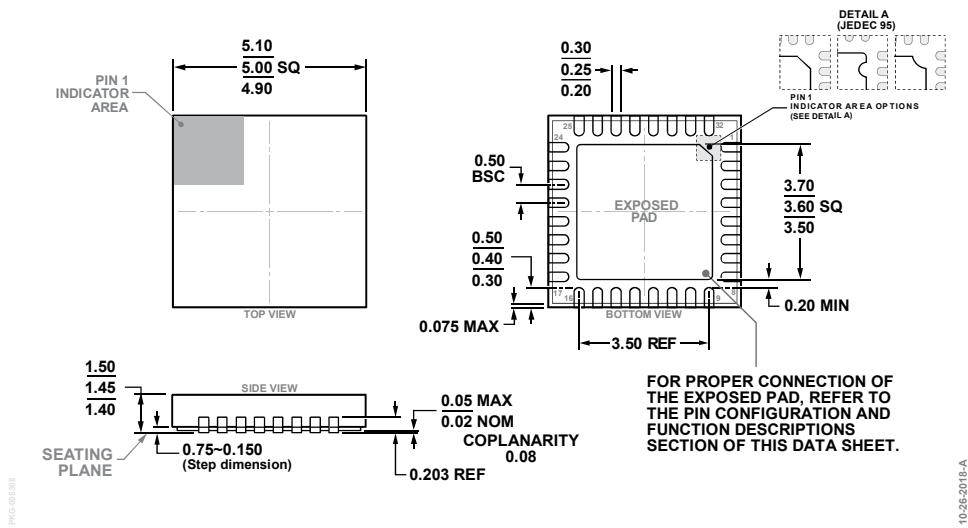

**Small, thin package: 5 mm  $\times$  5 mm  $\times$  1.45 mm LFCSP**

**AEC-Q100 qualified for automotive applications**

**APPLICATIONS**

**Wideband ANC**

**Adaptive suspension control**

**GENERAL DESCRIPTION**

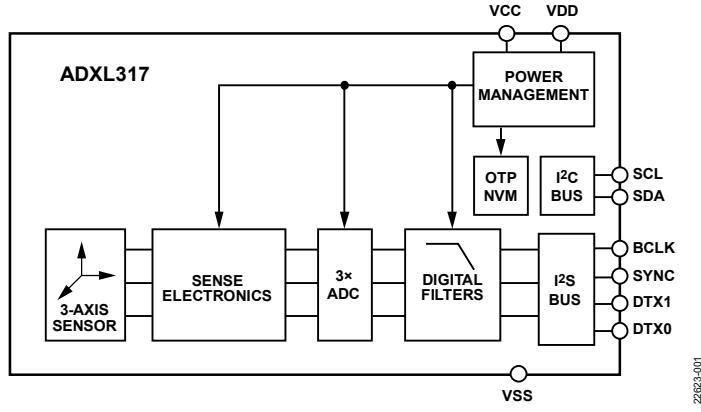

The ADXL317 is a small, thin, low latency, 3-axis accelerometer with high resolution (14-bit) measurement up to  $\pm 16\text{ g}$ . Digital output data is formatted as an I<sup>2</sup>S/time-division multiplexing (TDM) signal. Additionally, an I<sup>2</sup>C digital interface is provided for user configuration.

The ADXL317 is well suited for wideband active noise control (ANC) applications. Featuring very low latency from the moment of acceleration to the transmission of digital output data, the ADXL317 is uniquely capable of responding quickly enough to allow wideband ANC systems sufficient time to respond to noise scenarios. The low noise of the ADXL317 enhances the ability of the device to accurately discriminate various external noise sources.

Due to the wide operating temperature range and high performance, the ADXL317 is ideal for other wheel well applications, such as adaptive suspension control.

The Automotive Audio Bus (A<sup>2</sup>B<sup>®</sup>) developed by Analog Devices, Inc., introduces system wide savings in cabling costs. The ADXL317 is designed to interface directly with the A<sup>2</sup>B product portfolio, such as the AD2425W, AD2428W, and AD2429W A<sup>2</sup>B transceivers.

The ADXL317 is supplied in a small, thin, 5 mm  $\times$  5 mm  $\times$  1.45 mm, 32-pin LFCSP package. The device is qualified for use in automotive applications over the entire operating temperature range of  $-40^\circ\text{C}$  to  $+125^\circ\text{C}$ .

Note that throughout this data sheet, multifunction pins, such as DTX1/TPC, are referred to either by the entire pin name or by a single function of the pin, for example, DTX1, when only that function is relevant.

**FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

**Document Feedback**

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©2019 Analog Devices, Inc. All rights reserved.

Technical Support [www.analog.com](http://www.analog.com)

## TABLE OF CONTENTS

|                                                      |    |                                                                                   |    |

|------------------------------------------------------|----|-----------------------------------------------------------------------------------|----|

| Features .....                                       | 1  | Filtering: Noise and Latency Considerations .....                                 | 24 |

| Applications .....                                   | 1  | Register Map .....                                                                | 26 |

| General Description .....                            | 1  | Register Details .....                                                            | 27 |

| Functional Block Diagram .....                       | 1  | Device ID Registers .....                                                         | 27 |

| Revision History .....                               | 2  | User Register Key Register (Address: 0x80, Name: USER_REG_KEY, Reset: 0xBC) ..... | 30 |

| Specifications .....                                 | 3  | I <sup>2</sup> S Configuration Registers .....                                    | 31 |

| Timing Specifications .....                          | 5  | Clock Rate Register .....                                                         | 31 |

| Absolute Maximum Ratings .....                       | 7  | X-Axis Self Test Configuration Register .....                                     | 32 |

| Thermal Resistance .....                             | 7  | X-Axis Filter Configuration Register .....                                        | 32 |

| ESD Caution .....                                    | 7  | Y-Axis Self Test Configuration Register .....                                     | 33 |

| Pin Configuration and Function Descriptions .....    | 8  | Y-Axis Filter Configuration Register .....                                        | 33 |

| Typical Performance Characteristics .....            | 9  | Z-Axis Self Test Configuration Register .....                                     | 34 |

| Terminology .....                                    | 11 | Z-Axis Filter Configuration Register .....                                        | 34 |

| Theory of Operation .....                            | 14 | X-Axis Accelerometer Data Registers .....                                         | 35 |

| Overview .....                                       | 14 | Y-Axis Accelerometer Data Registers .....                                         | 35 |

| Mechanical Device Operation .....                    | 14 | Z-Axis Accelerometer Data Registers .....                                         | 35 |

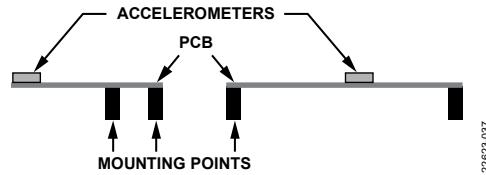

| Noise and Latency Trade-Off .....                    | 14 | Mechanical Considerations for Mounting .....                                      | 35 |

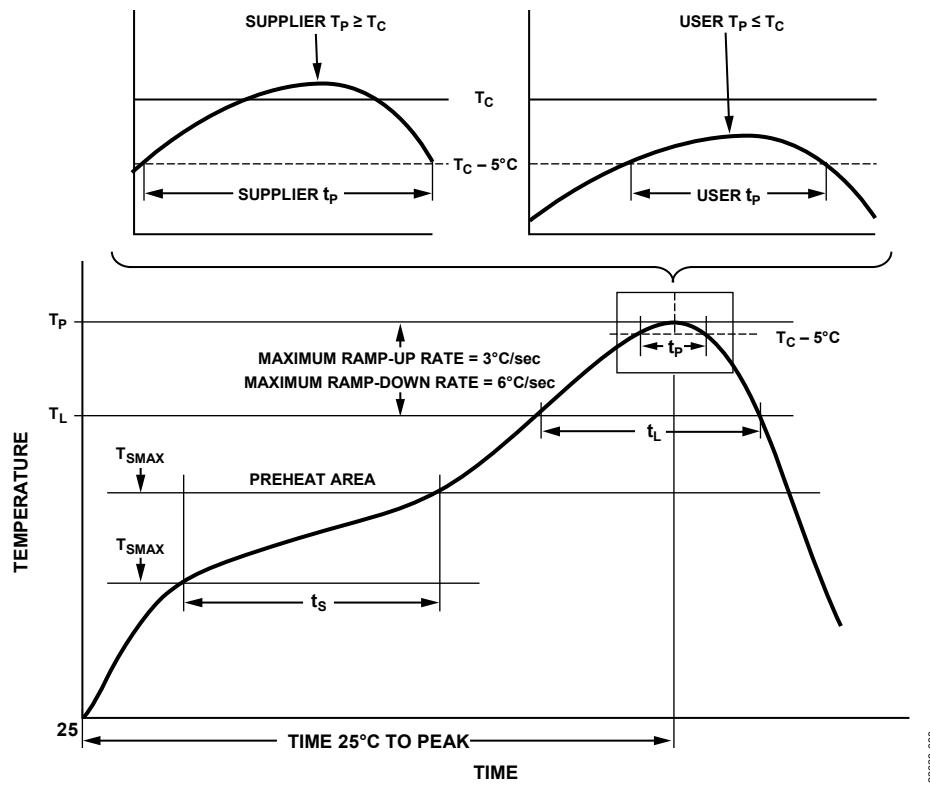

| Applications Information .....                       | 15 | Solder Reflow Profile .....                                                       | 36 |

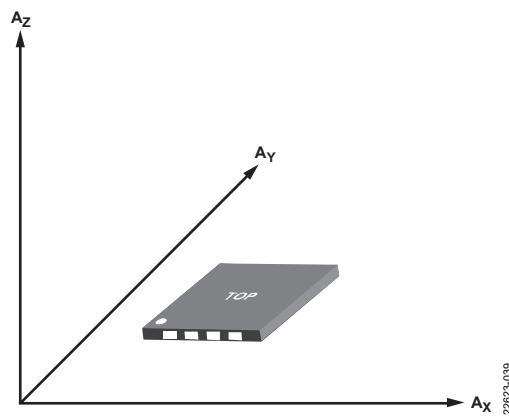

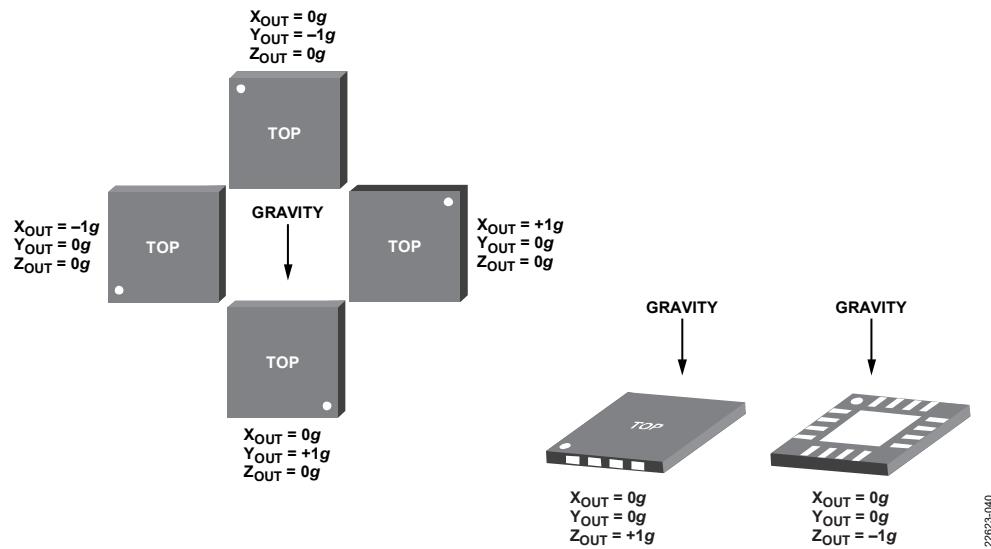

| Application Circuit .....                            | 15 | Axes of Acceleration Sensitivity .....                                            | 37 |

| Power .....                                          | 15 | Outline Dimensions .....                                                          | 38 |

| Interfacing with A <sup>2</sup> B Transceivers ..... | 15 | Ordering Guide .....                                                              | 38 |

| Using Self Test .....                                | 16 | Automotive Products .....                                                         | 38 |

| Serial Communications .....                          | 18 |                                                                                   |    |

| I <sup>2</sup> S/TDM Interface .....                 | 18 |                                                                                   |    |

| I <sup>2</sup> C Interface .....                     | 22 |                                                                                   |    |

## REVISION HISTORY

12/2019—Revision 0: Initial Version

## SPECIFICATIONS

$T_A = 25^\circ\text{C}$ ,  $V_{CC} = 3.3\text{ V}$ , acceleration =  $0\text{ g}$ , nominal clock set to 3.072 MHz or 6.144 MHz, unless otherwise specified. For complete definitions and conditions of all specifications, refer to the Terminology section.

Table 1. Accelerometer Specifications

| Parameter                             | Symbol | Test Conditions/Comments                                                                                     | Min      | Typ       | Max     | Unit                           |

|---------------------------------------|--------|--------------------------------------------------------------------------------------------------------------|----------|-----------|---------|--------------------------------|

| SENSOR                                |        | Each axis                                                                                                    |          |           |         |                                |

| Full-Scale Range                      | FSR    | Percentage of full-scale range                                                                               | $\pm 16$ | $\pm 1\#$ | $\pm 1$ | $g$                            |

| Nonlinearity                          |        |                                                                                                              |          |           |         | %                              |

| Cross Axis Sensitivity                |        |                                                                                                              |          |           |         | %                              |

| Resonant Frequency                    | $f_o$  |                                                                                                              |          |           |         |                                |

| X- and Y-Axes                         |        |                                                                                                              |          | 5.10      |         | kHz                            |

| Z-Axis                                |        |                                                                                                              |          | 3.15      |         | kHz                            |

| Quality Factor                        | Q      |                                                                                                              |          |           |         |                                |

| X- and Y-Axes                         |        |                                                                                                              |          | 3.3       |         |                                |

| Z-Axis                                |        |                                                                                                              |          | 1.75      |         |                                |

| SENSITIVITY                           |        | Each axis                                                                                                    |          |           |         |                                |

| Sensitivity <sup>1</sup>              |        | DC response                                                                                                  |          |           |         |                                |

| 500 Hz Cascaded Filter                |        |                                                                                                              | 454.5    | 500       | 555.6   | LSB/g                          |

| 1 kHz Cascaded Filter                 |        |                                                                                                              | 461.5    | 507.6     | 564.0   | LSB/g                          |

| 2 kHz Cascaded Filter                 |        |                                                                                                              | 468.6    | 515.5     | 572.7   | LSB/g                          |

| 4 kHz Cascaded Filter                 |        |                                                                                                              | 519.5    | 571.4     | 634.9   | LSB/g                          |

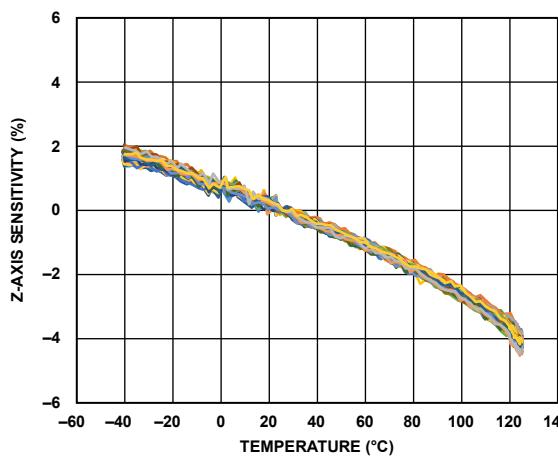

| Sensitivity Change Due to Temperature |        | $-40^\circ\text{C} \leq T_A \leq +25^\circ\text{C}$ and $+25^\circ\text{C} \leq T_A \leq +125^\circ\text{C}$ |          |           |         |                                |

| X- and Y-Axes                         |        | $1\sigma$                                                                                                    |          | $\pm 2.5$ |         | %                              |

| Z-Axis                                |        | $1\sigma$                                                                                                    |          | $\pm 4.5$ |         | %                              |

| RESOLUTION                            |        |                                                                                                              |          | 14        |         | Bits                           |

| Measurement Resolution                |        | All axes                                                                                                     |          |           |         |                                |

| ZERO $g$ BIAS LEVEL                   |        | Each axis                                                                                                    |          |           |         |                                |

| 0 $g$ Bias Error                      |        | Over full operating temperature range                                                                        |          |           |         |                                |

| Initial 0 $g$ Output Deviation        |        |                                                                                                              | -1.5     |           | +1.5    | $g$                            |

| X- and Y-Axes                         |        |                                                                                                              |          | $\pm 200$ |         | mg                             |

| Z-Axis                                |        |                                                                                                              |          | $\pm 500$ |         | mg                             |

| FREQUENCY RESPONSE                    |        | User selectable                                                                                              |          |           |         |                                |

| Cutoff (-3 dB) Frequency              |        | Filters only                                                                                                 |          |           |         |                                |

| 500 Hz Cascaded Filter                |        |                                                                                                              |          | 506       |         | Hz                             |

| 1 kHz Cascaded Filter                 |        |                                                                                                              |          | 1012      |         | Hz                             |

| 2 kHz Cascaded Filter                 |        |                                                                                                              |          | 2025      |         | Hz                             |

| 4 kHz Cascaded Filter                 |        |                                                                                                              |          | 4051      |         | Hz                             |

| NOISE                                 |        |                                                                                                              |          |           |         |                                |

| Noise Density <sup>2</sup>            |        |                                                                                                              |          |           |         |                                |

| X- and Y-Axes                         |        |                                                                                                              |          | 55        |         | $\mu\text{g}/\sqrt{\text{Hz}}$ |

| Z-Axis                                |        |                                                                                                              |          | 120       |         | $\mu\text{g}/\sqrt{\text{Hz}}$ |

| Output Noise, X- and Y-Axes           |        |                                                                                                              |          |           |         |                                |

| 500 Hz Cascaded Filter                |        |                                                                                                              |          | 2.5       | 4       | mg rms                         |

| 1 kHz Cascaded Filter                 |        |                                                                                                              |          | 5.5       | 10      | mg rms                         |

| 2 kHz Cascaded Filter                 |        |                                                                                                              |          | 22.5      | 35      | mg rms                         |

| 4 kHz Cascaded Filter                 |        |                                                                                                              |          | 85        | 110     | mg rms                         |

| Output Noise Z-Axis                   |        |                                                                                                              |          |           |         |                                |

| 500 Hz Cascaded Filter                |        |                                                                                                              |          | 4         | 9       | mg rms                         |

| 1 kHz Cascaded Filter                 |        |                                                                                                              |          | 7         | 12      | mg rms                         |

| 2 kHz Cascaded Filter                 |        |                                                                                                              |          | 30        | 40      | mg rms                         |

| 4 kHz Cascaded Filter                 |        |                                                                                                              |          | 120       | 135     | mg rms                         |

| Parameter                                                   | Symbol       | Test Conditions/Comments                                                              | Min   | Typ    | Max   | Unit    |

|-------------------------------------------------------------|--------------|---------------------------------------------------------------------------------------|-------|--------|-------|---------|

| SELF TEST                                                   |              |                                                                                       |       |        |       |         |

| Positive Self Test Output Change<br>X- and Y-Axes<br>Z-Axis | + $ST\Delta$ | DC self test magnitude                                                                | 2.16  | 3.6    | 5.04  | $g$     |

|                                                             |              |                                                                                       | 4.08  | 6.8    | 9.52  | $g$     |

| Negative Self Test Output Change<br>X- and Y-Axes<br>Z-Axis | - $ST\Delta$ | DC self test magnitude                                                                | -5.04 | -3.6   | -2.16 | $g$     |

|                                                             |              |                                                                                       | -9.52 | -6.8   | -4.08 | $g$     |

| SUPPLY                                                      |              |                                                                                       |       |        |       |         |

| Operating Voltage                                           | $V_{CC}$     |                                                                                       | 3.0   | 3.3    | 3.6   | V       |

| Regulated Input/Output (I/O) Voltage                        | $V_{DD}$     |                                                                                       |       | 1.8    |       | V       |

| Quiescent Supply Current                                    |              |                                                                                       |       |        | 5     | mA      |

| Turn On Time                                                |              |                                                                                       |       |        | 200   | $\mu s$ |

| I <sup>2</sup> S/TDM INTERFACE                              |              |                                                                                       |       | 48     |       | kHz     |

| Frame Rate                                                  |              |                                                                                       |       |        |       |         |

| Word Size                                                   |              |                                                                                       |       | 32     |       | Bits    |

| I <sup>2</sup> S/TDM2                                       |              |                                                                                       |       | 16, 32 |       | Bits    |

| TDM4                                                        |              |                                                                                       |       | 16     |       | Bits    |

| TDM8                                                        |              |                                                                                       |       |        |       |         |

| Input Clock Frequency                                       |              | BCLK from master device                                                               |       |        |       |         |

| I <sup>2</sup> S/TDM2                                       |              | 32-bit word size                                                                      |       | 3.072  |       | MHz     |

| TDM4                                                        |              | 16-bit word size                                                                      |       | 3.072  |       | MHz     |

|                                                             |              | 32-bit word size                                                                      |       | 6.144  |       | MHz     |

| TDM8                                                        |              | 16-bit word size                                                                      |       | 6.144  |       | MHz     |

| LATENCY                                                     |              |                                                                                       |       |        |       |         |

| Filter delay                                                |              | Filters only; does not include sense electronics or analog-to-digital converter (ADC) |       |        |       |         |

| 500 Hz Bandwidth                                            |              |                                                                                       |       | 585    |       | $\mu s$ |

| 1 kHz Bandwidth                                             |              |                                                                                       |       | 291    |       | $\mu s$ |

| 2 kHz Bandwidth                                             |              |                                                                                       |       | 144    |       | $\mu s$ |

| 4 kHz Bandwidth                                             |              |                                                                                       |       | 70.9   |       | $\mu s$ |

| Additional Latency                                          |              | Sense electronics and ADC                                                             |       |        |       |         |

| X- and Y-Axes                                               |              |                                                                                       |       | 13.8   |       | $\mu s$ |

| Z-Axis                                                      |              |                                                                                       |       | 20.4   |       | $\mu s$ |

| ENVIRONMENTAL                                               |              |                                                                                       |       |        |       |         |

| Operating Temperature Range                                 |              |                                                                                       | -40   |        | +125  | °C      |

<sup>1</sup> Sensitivity varies with filter setting and deviation from nominal clock frequency. This specification assumes a nominal clock of 3.072 MHz or 6.144 MHz.

<sup>2</sup> Noise density at 100 Hz with high-pass filter disabled (x\_HPF\_EN = 0). Noise density may vary across frequency.

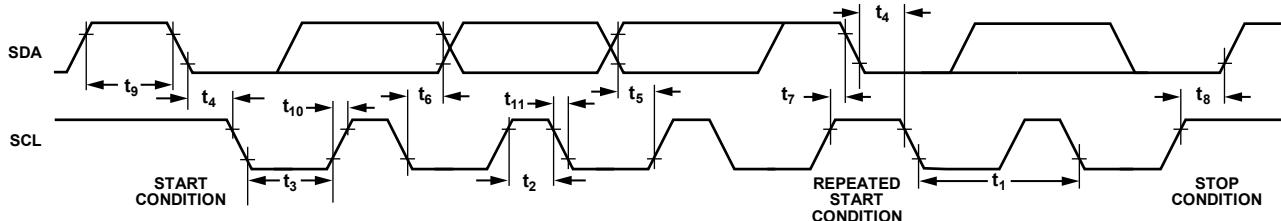

## TIMING SPECIFICATIONS

Table 2. I<sup>2</sup>C Digital Input/Output Characteristics

| Parameter            | Test Conditions/Comments         | Min                 | Limit <sup>1</sup><br>Max | Unit    |

|----------------------|----------------------------------|---------------------|---------------------------|---------|

| Digital Input        |                                  |                     |                           |         |

| Input Voltage Level  |                                  |                     |                           |         |

| Low ( $V_{IL}$ )     |                                  |                     | 0.3 $\times V_{DD}$       | V       |

| High ( $V_{IH}$ )    |                                  | 0.7 $\times V_{DD}$ |                           | V       |

| Input Current Level  |                                  |                     |                           |         |

| Low ( $I_{IL}$ )     | $V_{IN} = V_{DD}$                |                     | 0.1                       | $\mu A$ |

| High ( $I_{IH}$ )    | $V_{IN} = 0 V$                   | -0.1                |                           | $\mu A$ |

| Digital Output       |                                  |                     |                           |         |

| Output Voltage Level |                                  |                     |                           |         |

| Low ( $V_{OL}$ )     | $V_{DD} = 1.8 V, I_{OL} = 3 mA$  |                     | 400                       | mV      |

| Output Current Level |                                  |                     |                           |         |

| Low ( $I_{OL}$ )     | $V_{OL} = V_{OL, MAX}$           | 3                   |                           | mA      |

| Pin Capacitance      | $f_{IN} = 1 MHz, V_{IN} = 2.5 V$ |                     | 8                         | pF      |

| Input Frequency      |                                  |                     | 100                       | kHz     |

<sup>1</sup> Limits are based on characterization results and are not production tested.

Table 3. I<sup>2</sup>C Timing ( $T_A = 25^\circ C$ ,  $V_{CC} = 3.3 V$ )

| Parameter       | Limit <sup>1,2</sup> |     | Unit    | Description                                                  |

|-----------------|----------------------|-----|---------|--------------------------------------------------------------|

|                 | Min                  | Max |         |                                                              |

| $f_{SCL}$       |                      | 100 | kHz     | SCL clock frequency                                          |

| $t_1$           | 2.5                  |     | $\mu s$ | SCL cycle time                                               |

| $t_2$           | 0.6                  |     | $\mu s$ | SCL high time                                                |

| $t_3$           | 1.3                  |     | $\mu s$ | SCL low time                                                 |

| $t_4$           | 0.6                  |     | $\mu s$ | Start/repeated start condition hold time                     |

| $t_5$           | 100                  |     | ns      | Data setup time                                              |

| $t_6^{3,4,5,6}$ | 0                    | 0.9 | $\mu s$ | Data hold time                                               |

| $t_7$           | 0.6                  |     | $\mu s$ | Repeated start condition setup time                          |

| $t_8$           | 0.6                  |     | $\mu s$ | Stop condition setup time                                    |

| $t_9$           | 1.3                  |     | $\mu s$ | Bus-free time between a stop condition and a start condition |

| $t_{10}$        |                      | 300 | ns      | Rise time of both SCL and SDA when receiving                 |

|                 | 0                    |     | ns      | Rise time of both SCL and SDA when receiving or transmitting |

| $t_{11}$        |                      | 250 | ns      | Fall time of SDA when receiving                              |

|                 |                      | 300 | ns      | Fall time of both SCL and SDA when transmitting              |

|                 | 20 + 0.1 $C_b^7$     |     | ns      | Fall time of both SCL and SDA when receiving or transmitting |

| $C_b$           | 400                  |     | pF      | Capacitive load for each bus line                            |

<sup>1</sup> Limits are based on characterization results, with  $f_{SCL} = 100 kHz$ , and are not production tested.

<sup>2</sup> All values are in reference to the  $V_{IH}$  and  $V_{IL}$  levels shown in Table 2.

<sup>3</sup>  $t_6$  is the data hold time measured from the falling edge of SCL.  $t_6$  applies to data transmission and acknowledge.

<sup>4</sup> A transmitting device must internally provide an output hold time of at least 300 ns for the SDA signal (with respect to  $V_{IH, MIN}$  of the SCL signal) to bridge the undefined region of the falling edge of SCL.

<sup>5</sup> The maximum  $t_6$  value must be met only if the device does not stretch the low period ( $t_3$ ) of the SCL signal.

<sup>6</sup> The maximum value for  $t_6$  is a function of the clock low time ( $t_3$ ), the clock rise time ( $t_{10}$ ), and the minimum data setup time ( $t_5, MIN$ ). This value,  $t_6$ , is calculated as  $t_6, MAX = t_3 - t_{10} - t_5, MIN$ .

<sup>7</sup>  $C_b$  is the total capacitance of one bus line in picofarads.

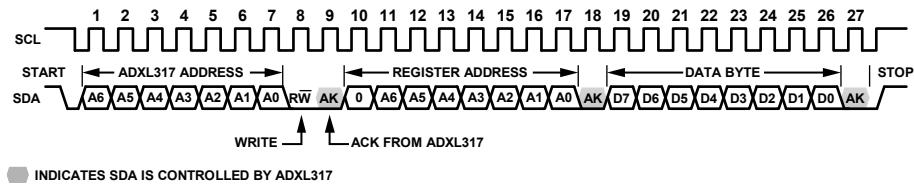

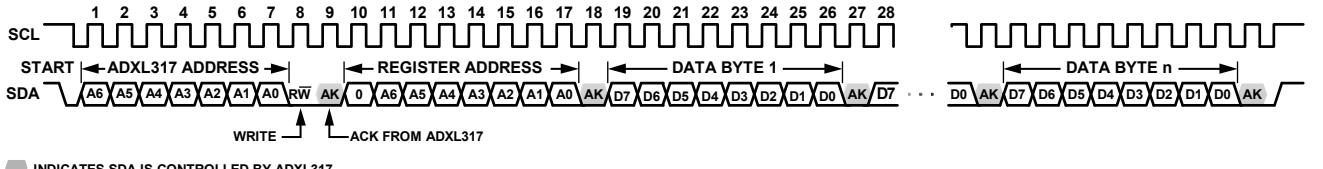

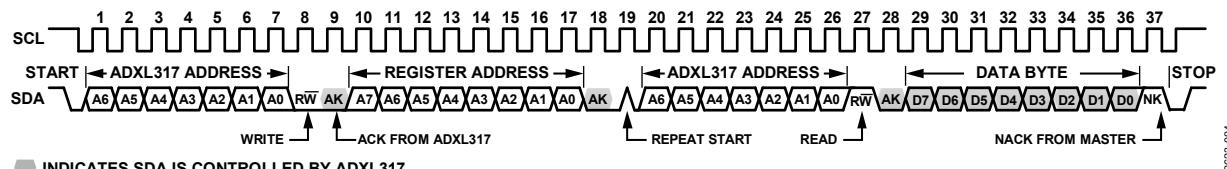

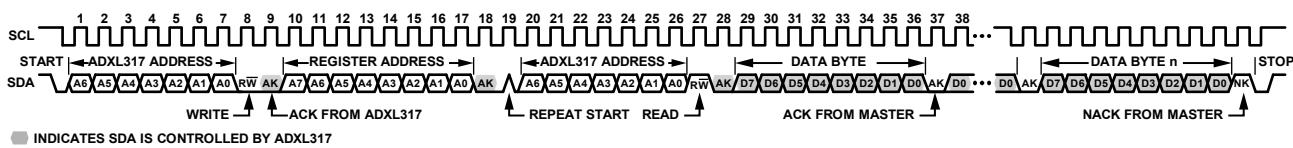

Figure 2. I<sup>2</sup>C Single-Byte Register WriteFigure 3. I<sup>2</sup>C Multibyte Register WriteFigure 4. I<sup>2</sup>C Single-Byte Register ReadFigure 5. I<sup>2</sup>C Multibyte Register ReadFigure 6. I<sup>2</sup>C Timing Diagram

## ABSOLUTE MAXIMUM RATINGS

Table 4.

| Parameter                        | Rating                                  |

|----------------------------------|-----------------------------------------|

| Mechanical Shock                 |                                         |

| Any Axis, Unpowered              | $\pm 4000 \text{ g}$ (0.5 ms half sine) |

| Any Axis, Powered                | $\pm 2000 \text{ g}$ (0.5 ms half sine) |

| Voltage                          |                                         |

| Supply Voltage                   | -0.3 V to +4.0 V                        |

| Any Pin to Ground                | -0.3 V to $V_{DD} + 0.3 \text{ V}$      |

| Electrostatic Discharge (ESD)    |                                         |

| Human Body Model (HBM), All Pins | 2 kV                                    |

| Latch-Up Current                 | 100 mA                                  |

| Storage Temperature Range        | -55°C to +150°C                         |

| Operating Temperature Range      | -40°C to +125°C                         |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

## THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.  $\theta_{JC}$  is the junction to case thermal resistance.

Table 5. Thermal Resistance

| Package Type         | $\theta_{JA}$ | $\theta_{JC}$ | Unit |

|----------------------|---------------|---------------|------|

| CS-32-4 <sup>1</sup> | 48.3          | 20.4          | °C/W |

<sup>1</sup> Test Condition 1: simulated thermal impedance values are based on a JEDEC 2S2P thermal test board with four thermal vias. See JEDEC JESD-51.

## ESD CAUTION

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

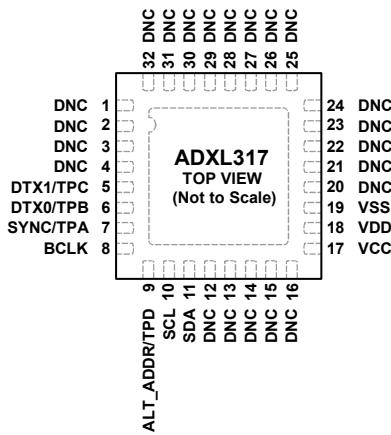

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

### NOTES

1. DNC = DO NOT CONNECT. DO NOT CONNECT TO THESE PINS.

THESE PINS MUST REMAIN FLOATING.

2. EXPOSED PAD. THE EXPOSED PAD MUST BE CONNECTED TO GROUND.

2623-007

Figure 7. Pin Configuration

Table 6. Pin Function Descriptions

| Pin No.  | Mnemonic     | Description                                                                                                                                                                     |

|----------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 to 4   | DNC          | Do Not Connect. Do not connect these pins. These pins must remain floating.                                                                                                     |

| 5        | DTX1/TPC     | I <sup>2</sup> S Data Channel 1/Test Pad C.                                                                                                                                     |

| 6        | DTX0/TPB     | I <sup>2</sup> S Data Channel 0/Test Pad B.                                                                                                                                     |

| 7        | SYNC/TPA     | I <sup>2</sup> S Sync/Test Pad A.                                                                                                                                               |

| 8        | BCLK         | I <sup>2</sup> S Clock.                                                                                                                                                         |

| 9        | ALT_ADDR/TPD | I <sup>2</sup> C Address Select/Test Pad D. Connect this pin to ground to set the ADXL317 I <sup>2</sup> C address to 0x53. Connect this pin to VDD to set the address to 0x1D. |

| 10       | SCL          | I <sup>2</sup> C Serial Clock.                                                                                                                                                  |

| 11       | SDA          | I <sup>2</sup> C Serial Data.                                                                                                                                                   |

| 12 to 16 | DNC          | Do Not Connect. Do not connect these pins. These pins must remain floating.                                                                                                     |

| 17       | VCC          | Supply Voltage.                                                                                                                                                                 |

| 18       | VDD          | Internal Regulator Output Voltage. Use this pin for the I <sup>2</sup> C high reference.                                                                                        |

| 19       | VSS          | Reference Voltage. Connect this pin to ground.                                                                                                                                  |

| 20 to 32 | DNC          | Do Not Connect. Do not connect these pins. These pins must remain floating.                                                                                                     |

|          | EP           | Exposed Pad. The exposed pad must be connected to ground.                                                                                                                       |

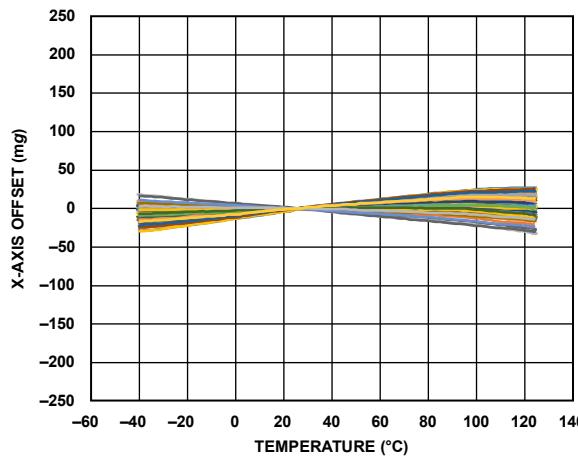

## TYPICAL PERFORMANCE CHARACTERISTICS

Figure 8. X-Axis Offset vs. Temperature

22823-008

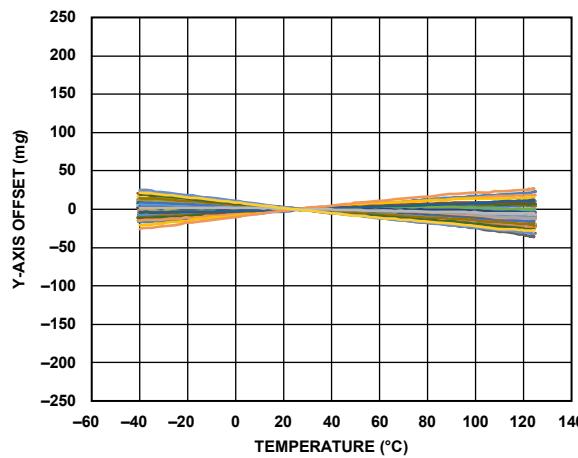

Figure 9. Y-Axis Offset vs. Temperature

22823-009

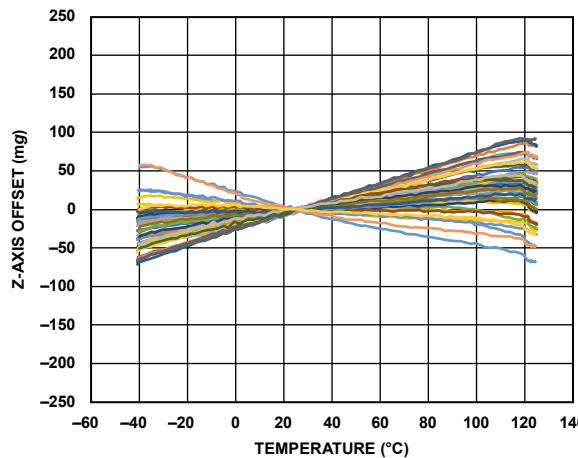

Figure 10. Z-Axis Offset vs. Temperature

22823-010

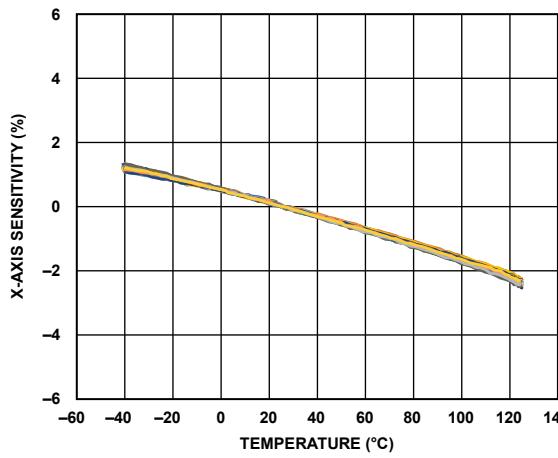

Figure 11. X-Axis Sensitivity vs. Temperature (500 Hz Cascaded Filter)

22823-011

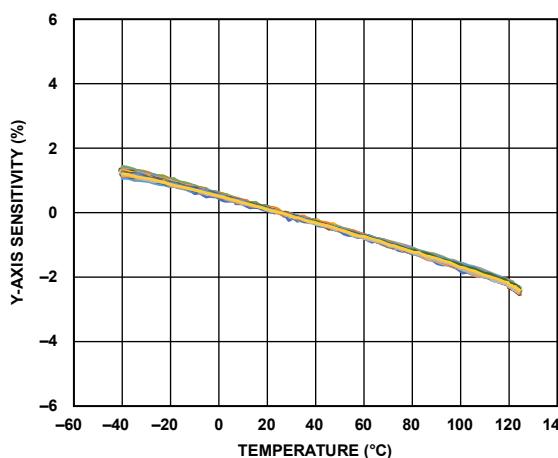

Figure 12. Y-Axis Sensitivity vs. Temperature (500 Hz Cascaded Filter)

22823-012

Figure 13. Z-Axis Sensitivity vs. Temperature (500 Hz Cascaded Filter)

22823-013

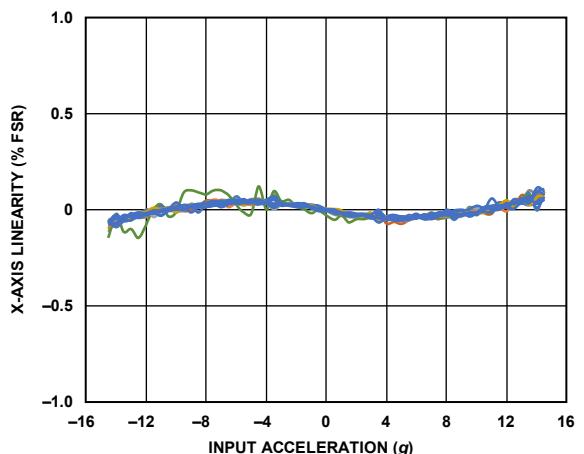

Figure 14. X-Axis Linearity

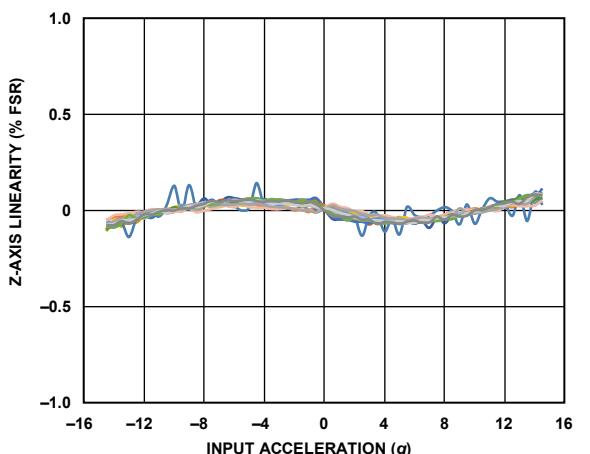

Figure 16. Z-Axis Linearity

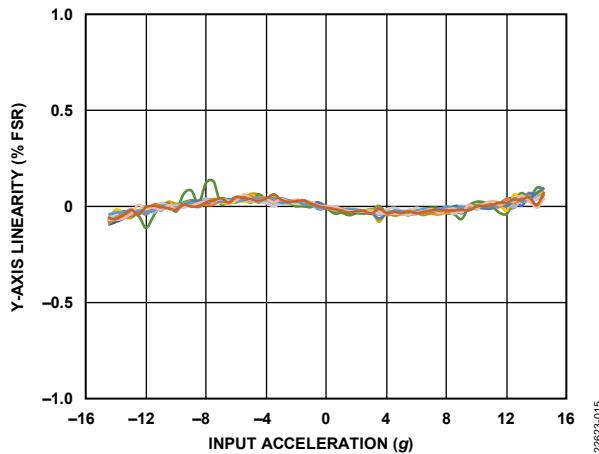

Figure 15. Y-Axis Linearity

## TERMINOLOGY

### Full-Scale Range (FSR)

The FSR of the ADXL317 is the guaranteed dynamic range at the output of the signal chain. FSR is specified as a minimum value and is guaranteed across all conditions. Acceleration measurement may be possible beyond this minimum value. However, performance characteristics are not guaranteed.

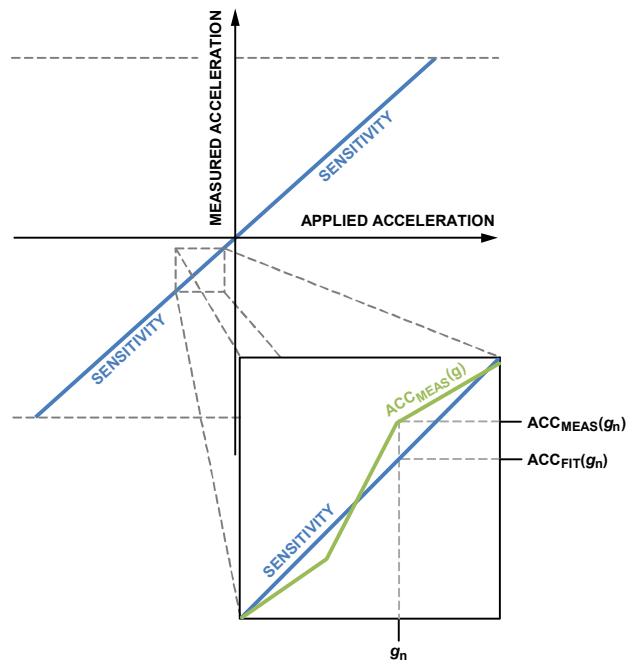

### Nonlinearity

Device nonlinearity is the maximum deviation of any sensor data point from the least squares linear fit of the acceleration data set at an equivalent input acceleration level. The acceleration data set can encompass any range of applied acceleration, up to the complete FSR of the ADXL317. Nonlinearity is defined mathematically as

$$\left| \frac{ACC_{MEAS}(g_n) - ACC_{FIT}(g_n)}{FSR} \right| \times 100\%$$

where:

$ACC_{MEAS}$  is the measured acceleration at a defined  $g_n$ .

$ACC_{FIT}$  is the predicted acceleration at a defined  $g_n$ .

$g_n$  is the input acceleration level.

Figure 17. Accelerometer Linearity Error (Not to Scale)

### Cross Axis Sensitivity

Cross axis sensitivity is the measured output of the device in response to input stimuli orthogonal to the intended sense axis. It is measured as a percentage of the applied acceleration, as follows:

$$\left[ \frac{ACC_{MEAS}(g_x)}{g_y \text{ (or } g_z\text{)}} \right] \times 100\%$$

where:

$ACC_{MEAS}(g_x)$  is the measured x-axis acceleration.

$g_y$  is the applied y-axis acceleration.

$g_z$  is the applied z-axis acceleration.

The cross axis sensitivity specification accounts for device level cross axis components only. These components include variations in sensor fabrication and the alignment of the sensor to the orthogonal axes of the package (also known as package alignment error). The cross axis specification does not account for system level sources of misalignment (for example, on the PCB or module).

### Resonant Frequency ( $f_o$ )

$f_o$  is the natural frequency at which the MEMS element has a higher gain when subjected to acceleration events. Input acceleration at this resonant frequency causes the sensor to displace by an amount equal to the applied acceleration multiplied by the quality factor (Q).

The ADXL317 uses different sensor types for the horizontal (x- and y-axes) and the vertical (z-axis) sensing axes. Therefore, the resonant frequency responses of these sensors are not the same.

### Quality Factor

The quality factor is a scalar factor that governs the increase or decrease in amplitude of an acceleration signal applied at the resonant frequency of a MEMS element.

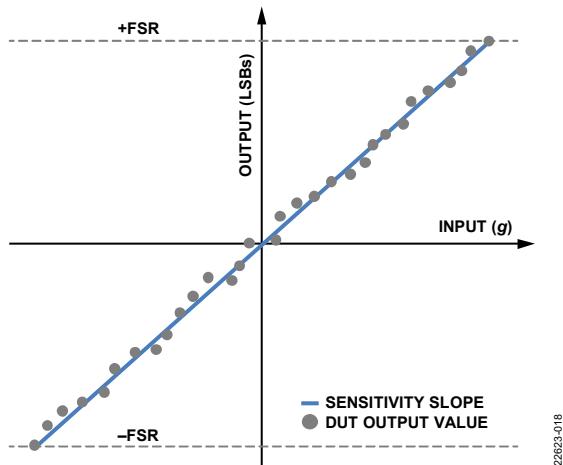

## Sensitivity

Sensitivity is the slope of the line of best fit for the acceleration transfer function, as measured across the output FSR of the ADXL317. The sensitivity defines the change in output (LSB) per unit change of input ( $g$ ). The inverse, scale factor, is in units of  $g/\text{LSB}$ .

Figure 18. Nominal Sensitivity Slope

## Measurement Resolution

Measurement resolution specifies the number of data bits in each acceleration data-word. For example, the 14-bit measurement of the ADXL317 has 16,384 bits of resolution. For an FSR of  $\pm 16\text{ g}$  ( $32\text{ g}$  total), this resolution yields a sensitivity of 500 LSB/g and a scale factor of 2.0 mg/LSB.

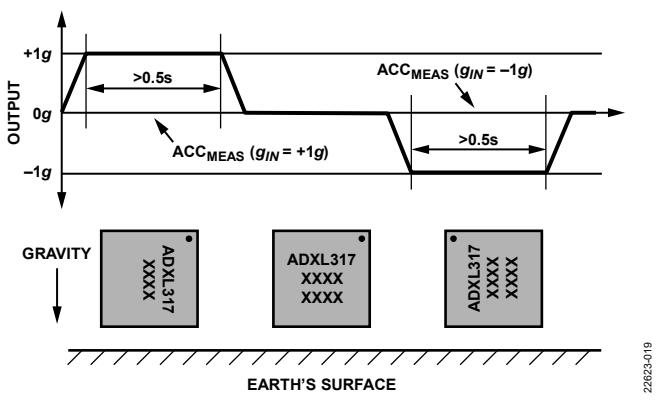

## Zero g Bias Error

The zero  $g$  bias error (also called offset) is any static error term on the output of the ADXL317. Zero  $g$  bias error is measured as the deviation from 0  $g$  with no externally applied acceleration (including gravity).

To more accurately measure offset, take measurements at orientations of  $+1\text{ g}$  and  $-1\text{ g}$  and average the results. Each measurement must be taken over a sufficiently long time window to reduce the influence of external physical stimuli that may exist in the measurement system.

$$\text{Offset} = \frac{\text{ACC}_{\text{MEAS}}(\text{g}_{\text{Input}} = 1\text{ g}) + \text{ACC}_{\text{MEAS}}(\text{g}_{\text{Input}} = -1\text{ g})}{2}$$

Figure 19. Zero  $g$  Bias Error Measurement (X-Axis Example)

## Initial Zero $g$ Output Deviation

Initial zero  $g$  output deviation is the error level at ambient conditions, measured immediately after completion of device manufacture. The initial zero  $g$  output deviation value denotes the standard deviation of the measured offset values across a large population of devices.

## Cutoff (-3 dB) Frequency

For applied ac acceleration, the cutoff (-3 dB) frequency (also referred to as bandwidth) is the frequency at which the input stimulus is attenuated in amplitude by 29.3% ( $1 - \sqrt{2}/2$ ) at the output of the signal chain. The -3 dB corner is set according to the low-pass cascaded integrated comb (CIC) filter and the low-pass infinite impulse response (IIR) filter setting as selected by the user. A high-pass filter can also be turned on by the user but is disabled by default. All other signal chain elements have an appreciably high bandwidth and are not significant contributors to the cutoff frequency.

## Noise Density

Noise density is a measure of the inherent noise in the ADXL317 and is a combination of all internal noise sources. This density is fixed by the architecture of the device and is independent of bandwidth. See the Filtering: Noise and Latency Considerations section for more information on noise density.

## Output Noise

Output noise is the realized noise in reported measurements. Whereas noise density expresses the inherent noise in the device, output noise is the union of density and bandwidth. Filters with lower bandwidths provide more aggressive filtering and, therefore, greater noise reduction than filters with higher bandwidths.

## Self Test Output Change

The sensor self test is a diagnostic test. In this test, the sensor proof mass is deflected by an electrostatic force, thereby creating a measurable output change. For a self test routine to be evaluated properly, the change in output must be measured before and after applying the self test force. If this change is within the specified values shown in Table 1, it is considered successful.

The ADXL317 features positive, negative, and ac self test routines. AC self test toggles between positive and negative self test at a rate of 100 Hz. See the Using Self Test section for more information.

## Operating Voltage ( $V_{\text{CC}}$ )

Operating voltage is the necessary voltage on the VCC pin for proper operation. Any voltages on the VCC pin outside the specified minimum and maximum values may cause the device to malfunction.

## Regulated I/O Voltage ( $V_{\text{DD}}$ )

Regulated I/O voltage is the voltage reference for both on-chip digital communication interfaces: I<sup>2</sup>S and I<sup>2</sup>C. Operating these interfaces at other values from the regulated 1.8 V may result in miscommunication between the ADXL317 and master device.

**Quiescent Supply Current**

Quiescent supply current is the current draw of the device when no data is being transmitted and the device is operating within the minimum/maximum supply voltage (VCC).

**Turn On Time**

Turn on time specifies the necessary time needed for the regulated I/O voltage (VDD) to settle to the final value. This settling indicates that the nonvolatile memory (NVM) contents have been loaded and have taken effect. Following a hardware reset, the user must wait for the specified turn on time before performing reads from or writes to the ADXL317.

**Inter-IC Sound (I<sup>2</sup>S) Protocol**

The I<sup>2</sup>S protocol is a set of specifications for the transmission of digital audio signals along a bus. This bus consists of four signals: serial clock (BCLK), synchronization signal (SYNC), and two serial data channels (DTX[1:0]). The ADXL317 acts as a slave transmitter in this protocol.

**Inter-IC (I<sup>2</sup>C) Protocol**

The I<sup>2</sup>C protocol is a set of specifications for the transmission of data between multiple ICs along only two wires: serial data (SDA) and serial clock (SCL). These lines are shared between all devices on the bus. Each device on the bus is software addressable via a unique address.

**Latency**

Latency is the time between an acceleration event hitting the ADXL317 and the measurement being available on the output channel. There are two components that define the total latency of the signal chain:

- Fixed latency imposed by the sense electronics and ADCs.

- Latency created by the adjustable low-pass (CIC and IIR) and high-pass filters.

These two components must be added together to determine the total latency of the ADXL317. Filter latency is dependent on bandwidth, with higher bandwidths requiring less time for the input signal to appear on the output of the device.

## THEORY OF OPERATION

### OVERVIEW

The ADXL317 is a complete, 3-axis acceleration measurement system designed to interface directly with the Analog Devices line of A<sup>2</sup>B transceivers, making the ADXL317 ideal for automotive noise cancellation applications. The wide range of selectable bandwidth settings, low output noise, and low latency make the ADXL317 appropriate for wideband noise sensing and adaptive suspension control.

The ADXL317 treats all three sensor channels independently. There are three analog channels in the ASIC die with separate analog signal processing for each accelerometer axis. Each analog channel is then sampled by separate digital signal processing blocks that process the samples for the common communications interface block. Therefore, if one sensor channel fails, transmission of acceleration data continues for the other axes.

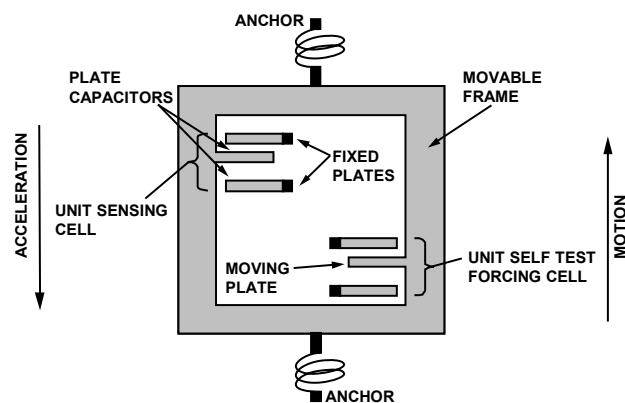

### MECHANICAL DEVICE OPERATION

The ADXL317 contains three independent sensors, one for each axis of sensitivity. Each acceleration sensor is a polysilicon, surface micromachined structure built on top of a silicon wafer. Polysilicon springs suspend the structure over the surface of the wafer and provide resistance against acceleration forces.

Deflection of the structure is measured using differential capacitors that consist of independent, fixed plates and plates attached to the moving mass. Acceleration deflects the beam and unbalances the differential capacitor, resulting in a sensor output with amplitude proportional to acceleration. Phase sensitive demodulation determines the magnitude and polarity of the acceleration.

Figure 20. Simplified View of One Sensor During Acceleration

### NOISE AND LATENCY TRADE-OFF

The ADXL317 offers several options for controlling the trade-off between output noise and latency (or delay) to accommodate a wide range of system requirements.

The ADXL317 features two cascaded, low-pass digital filters: a two-pole CIC filter and a single-pole IIR filter, which remove unwanted high frequency content from the signal. More aggressive filtering (that is, using a filter with a lower cutoff frequency) introduces more delay to the signal chain, but decreases output noise. Conversely, less aggressive filtering results in more output noise but less delay. The optimal compromise between these two parameters depends on system implementation.

The ADXL317 features four settings for each filter, for a total of 16 combinations. The noise and delay associated with a subset of these settings are shown in Table 7. For more information, see the Filtering: Noise and Latency Considerations section.

Table 7. Output Noise and Delay vs. Filter Cutoff Frequency

(T<sub>A</sub> = 25°C, V<sub>CC</sub> = 3.3 V)

| Cutoff Frequency (Hz) | Output Noise (mg rms) |        | Delay (μs) |

|-----------------------|-----------------------|--------|------------|

|                       | X-Y-Axes              | Z-Axis |            |

| 506                   | 2.5                   | 4      | 585        |

| 1012                  | 5.5                   | 7      | 291        |

| 2025                  | 22.5                  | 30     | 144        |

| 4051                  | 85                    | 120    | 70.9       |

## APPLICATIONS INFORMATION

### APPLICATION CIRCUIT

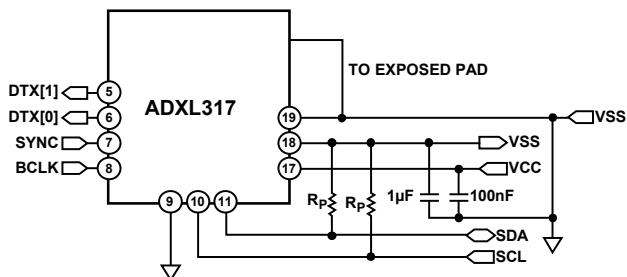

Figure 21 shows the recommended application circuit for the ADXL317. The operating power pin, VCC (Pin 17), requires a 100 nF bypass capacitor to ground (VSS, Pin 19) placed as close as possible to the pin. The voltage regulator output pin, VDD (Pin 18), requires a 1  $\mu$ F capacitor. The two I<sup>2</sup>C lines, SCL (Pin 10) and SDA (Pin 11), each require a pull-up resistor to VDD. The value of these resistors is dependent on bus capacitance. Refer to *UM10204 I<sup>2</sup>C-bus specification and user manual*, Rev. 6—4 April 2014 (NXP Semiconductor) when selecting pull-up resistor values to ensure proper operation. The exposed pad on the bottom of the package must be connected to ground.

#### NOTES

1. ALT\_ADDR MAY BE GROUNDED OR CONNECTED TO VDD. SEE THE I<sup>2</sup>C INTERFACE SECTION FOR DETAILS.

2. THE EXPOSED PAD ON THE BOTTOM OF THE PACKAGE MUST BE CONNECTED TO GROUND.

Figure 21. Recommended Application Circuit

22623-021

### POWER

The ADXL317 has a single power input pin, VCC, which operates at a nominal voltage of 3.3 V. An internal regulator steps this voltage down to 1.8 V. The VCC pin must be properly bypassed, as shown in Figure 21, to remove ac fluctuations from the power supply.

VDD is the output of the internal voltage regulator, which holds the pin at a constant 1.8 V. This pin must also be decoupled from ac noise for stability. VDD must be used as the pull-up voltage for the I<sup>2</sup>C lines (SCL and SDA).

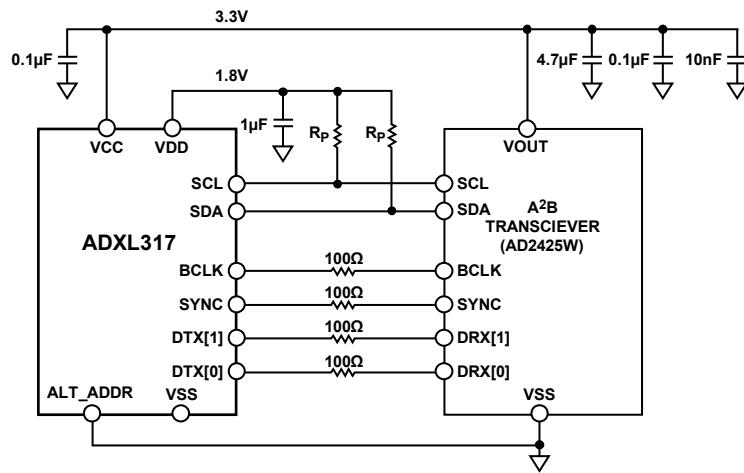

### INTERFACING WITH A<sup>2</sup>B TRANSCEIVERS

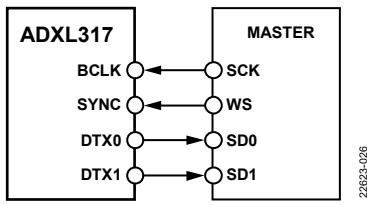

The ADXL317 is designed to interface directly with the AD2425W, or with an I<sup>2</sup>S capable A<sup>2</sup>B transceiver from Analog Devices. The connection between the ADXL317 and the AD2425W is shown in Figure 22. A generic A<sup>2</sup>B transceiver can be used. Refer to the appropriate transceiver data sheet for additional details.

#### Power

The ADXL317 operates as a phantom powered slave device and, therefore, must derive power directly from the A<sup>2</sup>B transceiver. Connect one of the VOUT pins (3.3 V) from the transceiver to VCC on the ADXL317, being sure to properly decouple the supply on both ends.

#### Communications

Directly connect the BCLK pin and the SYNC pin between the ADXL317 and the A<sup>2</sup>B transceiver. The DTX1 and DTX0 pins on the ADXL317 are outputs (data transmit) and must be connected to the corresponding DRX0 and DRX1 (data receive) pins on the transceiver. Adding small (~100  $\Omega$ ) series resistors to these four lines may improve electromagnetic interference (EMI) performance. The exact value of these resistors depends on the observed EMI characteristics of the system.

SCL and SDA must also be connected directly between the two devices, taking care to choose appropriate pull-up resistors. Use VDD as the pull-up voltage for I<sup>2</sup>C.

Figure 22. ADXL317 to A<sup>2</sup>B Transceiver Connection Diagram

## USING SELF TEST

The ADXL317 features a flexible self test routine to evaluate the condition of the sensors. Self test can be activated in one of the three following modes:

- Positive self test mode. In this mode, a positive dc excitation is applied to the sensor along the desired axis. This excitation is approximately 3.6 g for the x- and y-axes, and 6.6 g for the z-axis, plus any excitation from the environment.

- Negative self test mode. In this mode, a negative dc excitation is applied to the sensor along the desired axis. This excitation is approximately -3.6 g for the x- and y-axes and -6.6 g for the z-axis, plus any excitation from the environment.

- AC self test mode. In this mode, a 100 Hz square wave is applied to the sensor along the desired axis. The upper and lower bounds of this square wave are equal to the values of the positive and negative self tests, respectively.

When first powering on the ADXL317, the user must use the positive and negative dc self test or the ac self test to achieve an accurate understanding of device health. Each axis is capable of controlling its self test independently of the other axes, resulting in many combinations of self test settings. These settings are configured in the X\_ST, Y\_ST, and Z\_ST registers and the corresponding x\_ST\_AC, x\_ST\_POS, and x\_ST\_NEG bits. Although any number of these bits for a given axis can be asserted simultaneously, only one such force can be applied to each axis at a time. If multiple bits are asserted, self test is disabled. The mapping of all possible settings of these bits and the resultant self test force is shown in Table 8.

Table 8. Self Test Settings Combinations

| x_ST_AC | x_ST_POS | x_ST_NEG | Self Test Force       |

|---------|----------|----------|-----------------------|

| 0       | 0        | 0        | Self test is disabled |

| 0       | 0        | 1        | Negative self test    |

| 0       | 1        | 0        | Positive self test    |

| 0       | 1        | 1        | Self test is disabled |

| 1       | 0        | 0        | AC self test          |

| 1       | 0        | 1        | Self test is disabled |

| 1       | 1        | 0        | Self test is disabled |

| 1       | 1        | 1        | Self test is disabled |

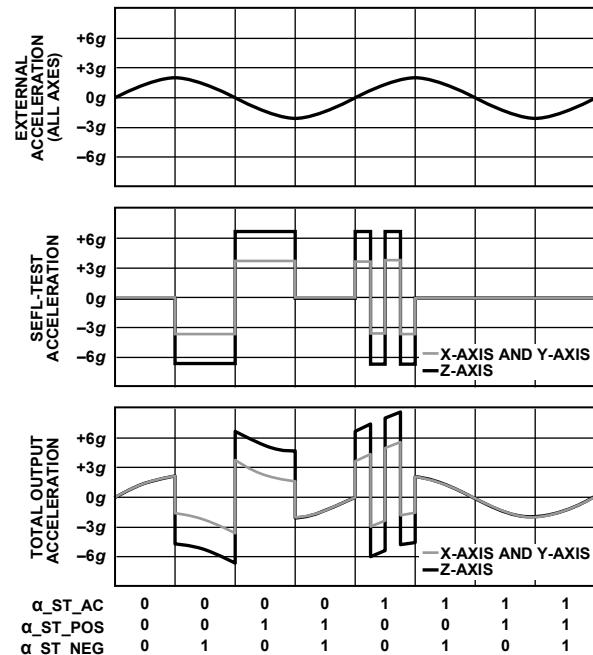

When a self test force is exerted along any axis, the value returned from the sensor is additive with any external force applied to the accelerometer, as shown in Figure 25. In this graphic, the accelerometer experiences a sine wave motion with an amplitude of 4 g. For simplicity, assume all axes receive the same input. The resultant measurement returned from the ADXL317 after applying self test is the sine wave added to the self test excitation.

Be sure to account for gravity in self test measurements.

For example, applying positive self test to the z-axis with the accelerometer sitting flat on a table (that is, with the z-axis aligned with gravity) results in acceleration of 6.6 g from self test, plus 1 g from gravity, for a total of 7.6 g. Therefore, self test is best performed in the absence of any external acceleration, other than static, known sources like gravity that can be easily calibrated out.

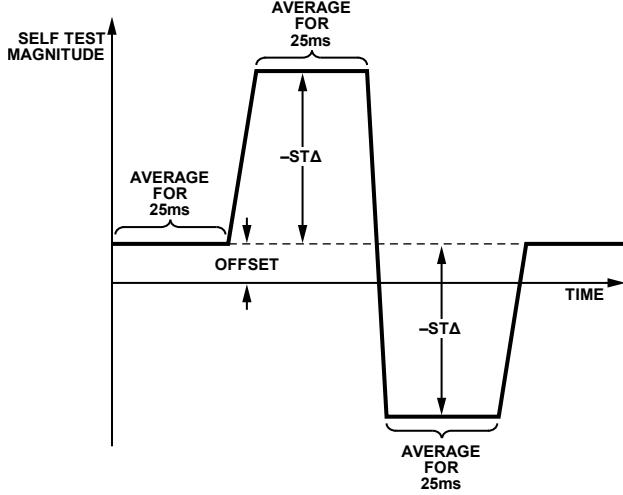

Taking an accurate self test measurement involves a few steps. For the two dc self test modes, the following routine must be followed to accurately assess the results of self test:

1. Ensure all self test functionality is disabled. That is, set the X\_ST, Y\_ST, and Z\_ST registers (Address 0x84, Address 0x86, and Address 0x88, respectively) to 0x00.

2. Read acceleration data for the x-axis. It is recommended to take an average of 25 ms to reduce the influence of noise in the measurement.

3. Activate self test by asserting the X\_ST\_POS bit and wait for the output to transition to the maximum value.

4. Read acceleration data again for 25 ms.

5. Subtract the data collected in Step 2 from the data collected in Step 4 to determine the magnitude of the self test delta ( $ST\Delta$ ).

6. Deactivate the X\_ST\_POS bit, activate the X\_ST\_NEG bit, and wait for the output to transition to the minimum value.

7. Read acceleration data again for 25 ms.

8. Compare the positive and negative  $ST\Delta$  magnitudes to the limits in Table 1. If both magnitudes are within the minimum and maximum specifications, the device passed the self test. Otherwise, the device failed and must be flagged for further investigation.

9. Repeat Step 1 to Step 8 for the y-axis and z-axis, sequentially.

Self test must be activated one channel at a time, meaning that Step 1 to Step 9 must be repeated for the x-, y-, and z-axis channels, sequentially.

Figure 23. DC Self Test Measurement

22623-023

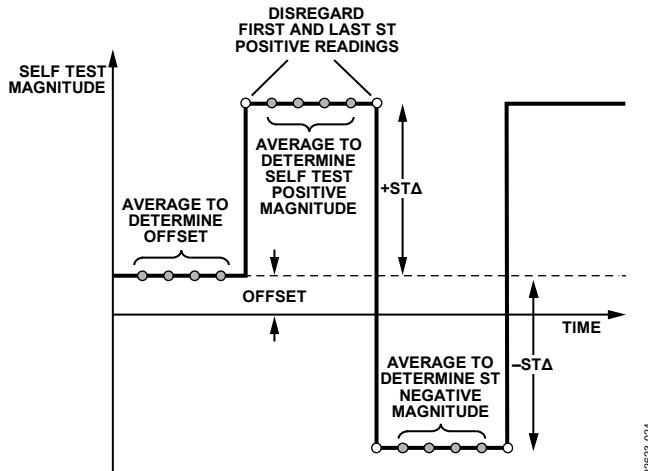

The same steps can be followed when taking an ac self test measurement. However, greater care must be taken in the timing between measurements. Additionally, it may be helpful to examine the frequency domain of the signal to determine if the sensor and signal chain are behaving as desired. For the ac self test mode, the following routine must be followed to accurately assess the results of self test:

1. Ensure all self test functionality is disabled. That is, set the X\_ST, Y\_ST, and Z\_ST registers (Address 0x84, Address 0x86, and Address 0x88, respectively) to 0x00.

2. Read acceleration data for the x-axis. It is recommended to take an average of 25 ms to reduce the influence of noise in the measurement.

3. Activate self test by asserting the X\_ST\_AC bit.

4. Read acceleration data for at least 40 ms with at least a 1 kHz data rate.

5. Determine the  $ST\Delta$  magnitudes using the procedure shown in Figure 24.

6. Compare the positive and negative  $ST\Delta$  magnitudes to the limits shown in Table 1. If both magnitudes are within the minimum and maximum specifications, the device passed the self test. Otherwise, the device failed and must be flagged for further investigation.

7. Repeat Step 1 to Step 6 for the y-axis and z-axis, sequentially.

Figure 24. AC Self Test Measurement

NOTES

1.  $\alpha = X, Y, \text{ OR } Z$

Figure 25. Self Test Settings and Resulting Output in Presence of 12.5 Hz Sinusoidal Input Acceleration

22623-025

## SERIAL COMMUNICATIONS

The ADXL317 communicates via both 4-wire I<sup>2</sup>S and 2-wire I<sup>C</sup> digital communication interfaces. The I<sup>2</sup>S bus is the primary means of outputting data, and the I<sup>C</sup> bus configures the register settings. In both cases, the ADXL317 operates as a slave device, receiving commands and responding with requested data. These two ports operate independently and use separate pins. Therefore, these ports can be used simultaneously.

### I<sup>2</sup>S/TDM INTERFACE

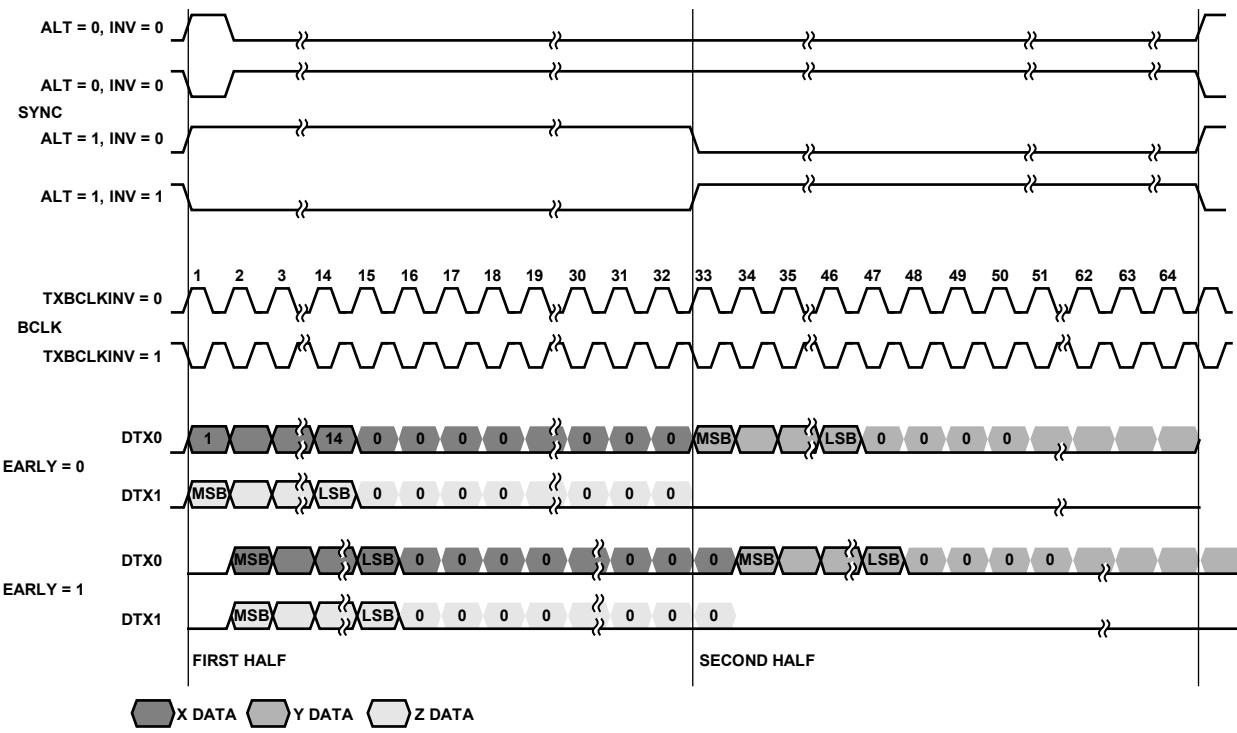

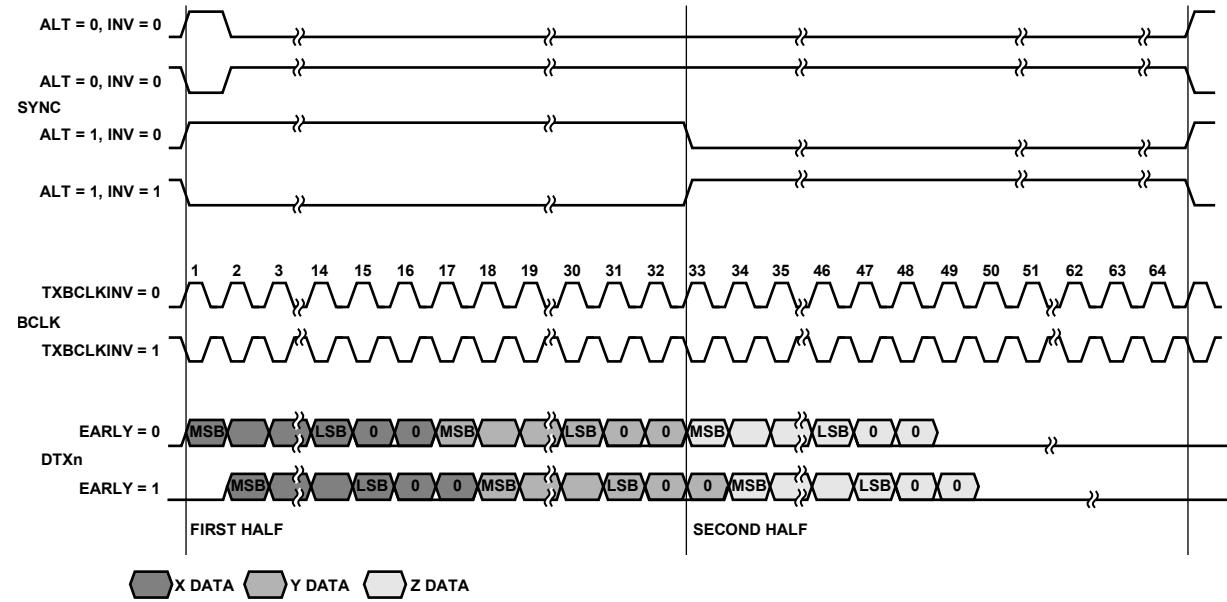

The ADXL317 constantly streams data out of the I<sup>2</sup>S port. This protocol is suitable for obtaining high speed, synchronous accelerometer data. The ADXL317 operates at a clock speed of 3.072 MHz or 6.144 MHz (typical) with a frame frequency of 48 kHz. The device supports 16-bit TDM4 and TDM8, as well as 32-bit I<sup>2</sup>S/TDM2 and TDM4.

Figure 26. I<sup>2</sup>S/TDM Wiring Diagram

#### Signals

The ADXL317 uses a 4-wire I<sup>2</sup>S interface, comprising one continuous serial clock, one synchronization signal, and two serial data channels. There are numerous naming conventions for these channels. The ADXL317 uses the same terminology and symbols as the A<sup>2</sup>B family of transceivers from Analog Devices. See Table 9 for a comparison of the names used in the I<sup>2</sup>S specification against the names used in the ADXL317.

Table 9. I<sup>2</sup>S Signal Names

| I <sup>2</sup> S Specification |        | ADXL317       |        |

|--------------------------------|--------|---------------|--------|

| Full Name                      | Symbol | Full Name     | Symbol |

| Continuous Serial Clock        | SCK    | Bit clock     | BCLK   |

| Word Select                    | WS     | Sync          | SYNC   |

| Serial Data                    | SD     | Data transmit | DTX    |

#### Bit Clock (BCLK)

The bit clock (BCLK) line controls the timing of transactions between the master (A<sup>2</sup>B transceiver or other controller) and slave (ADXL317). This clock must be supplied externally to the BCLK pin (Pin 8) at a rate of either 3.072 MHz or 6.144 MHz. The incoming clock frequency must be specified in the CLOCK\_RATE register (Address 0x83).

The ADXL317 has no internal clock, and all timing is derived from BCLK. BCLK must be running at all times for the ADXL317 to operate, even when using I<sup>C</sup> to read and/or write registers.

#### Sync (SYNC) Signal

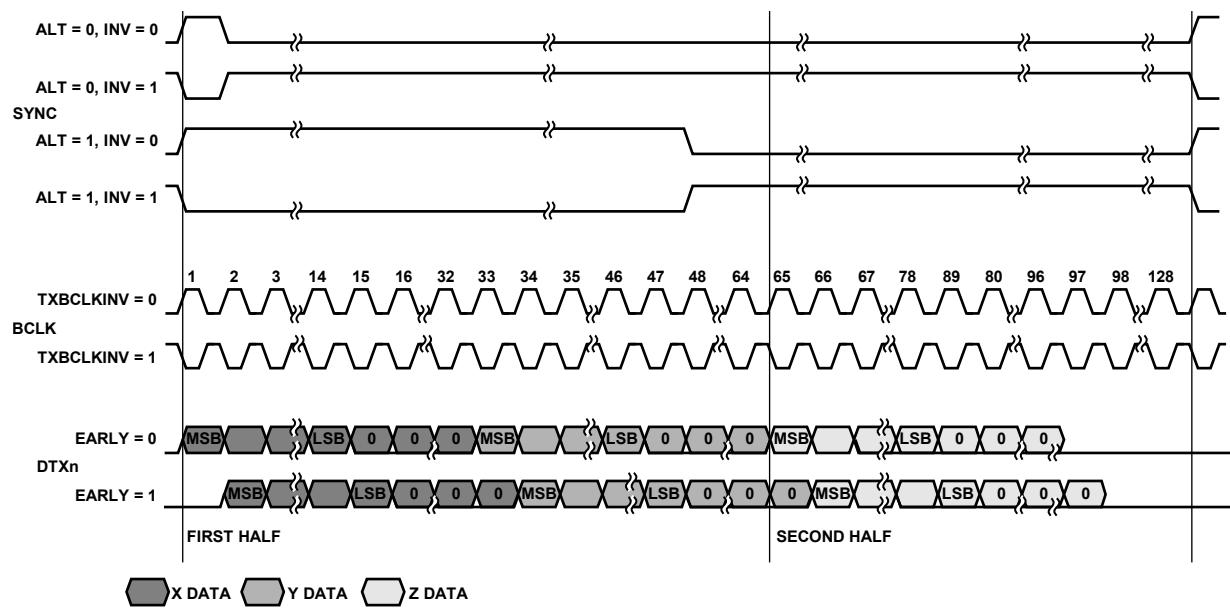

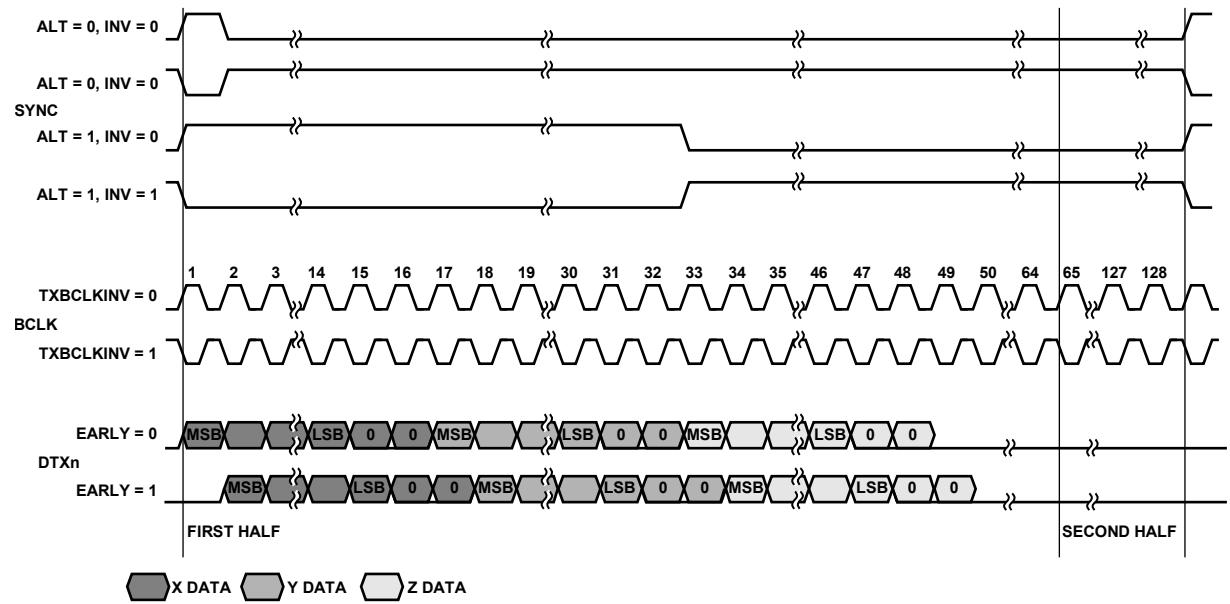

The SYNC line selects the channel being transmitted. By default, with SYNC high (set to 1), the right channel is transmitting. With SYNC low (set to 0), the left channel is transmitting (in TDM2 mode). This behavior can be reversed by asserting the INV bit in the I2S\_CFG0 register (Address 0x81). SYNC demarcates the boundary between the first and second halves of the frame.

The value of SYNC is latched on the rising edge of BCLK as long as INV (Address 0x81, Bit 7) = 0. After SYNC changes value, the timing of the transmission of the MSB of the data depends on the value of the early bit in the I2S\_CFG0 register. If early = 0, the SYNC pin changes in the same cycle as the MSB of the first data channel. If early = 1, the SYNC pin changes one cycle before the MSB of the first data channel.

By default, the SYNC pin changes value on the rising edge of BCLK. This change can be altered to occur on the falling edge by asserting the TXBCLKINV bit in the I2S\_CFG1 register.

#### Data Transmit (DTX) Signal

The data transmit (DTX) lines send data from the ADXL317 to the master device. Data is transmitted in two's complement format with the most significant bit (MSB) first. The position of the LSB in the transaction is dependent on the word length, as defined in the Packet Format section.

Data can be sent over one or both of the DTX pins, depending on the values of the TX0EN and TX1EN bits in the I2S\_CFG1 register, as well as the operating mode.

#### Packet Format

The ADXL317 features four packet formats, depending on the input clock (BCLK) frequency and system requirements. At 3.072 MHz, 32-bit I<sup>2</sup>S/TDM2 and 16-bit TDM4 are supported. At 6.144 MHz, 32-bit TDM4 and 16-bit TDM8 are supported. Note that 32-bit I<sup>2</sup>S/TDM2 mode requires two data pins, whereas the other three modes require only one.

Table 10. Required BCLK Frequencies for All Supported Output Formats

| Output Format         | 16-Bit Mode BCLK Frequency | 32-Bit Mode BCLK Frequency | No. of Pins |

|-----------------------|----------------------------|----------------------------|-------------|

| I <sup>2</sup> S/TDM2 | Not applicable             | 3.072 MHz                  | 2           |

| TDM4                  | 3.072 MHz                  | 6.144 MHz                  | 1           |

| TDM8                  | 6.144 MHz                  | Not applicable             | 1           |

In I<sup>2</sup>S/TDM2 mode, the DTX0 pin transmits data from the x- and y-axes. The DTX1 pin transmits z-axis data followed by all zeros in the second half of the transmission. BCLK must be running at 3.072 MHz, and each axis comprises 32 bits.

In TDM4 mode, data from all three axes is sent over a single pin, whereas the other pin remains at zero during the entire transaction. Each axis comprises 16 bits with BCLK running at 3.072 MHz and 32 bits at 6.144 MHz.

In TDM8 mode, the frame is further divided in eight segments. The first three segments on one pin contain data from all three axes, and the remaining segments are held at zero. BCLK must be running at 6.144 MHz, and each axis comprises 16 bits.

The frame rate for all transactions is 48 kHz, which translates to 64 clock cycles at 3.072 MHz or 128 cycles at 6.144 MHz. The number of channels in each frame is always a power of two (two, four, or eight). The ADXL317 has three channels, one for each axis. Therefore, all channels beyond the third are set

entirely to 0. Table 11 through Table 14 shows how these channels align within each frame, and Figure 27 through Figure 30 show how the various I<sup>2</sup>S configuration settings affect the timing of each transaction. Note that these figures are not to scale, and clock rates differ.

For formats that only require one data pin, the TX0EN bit and the TX1EN bit in the I2S\_CFG1 register control which pin is actively outputting data. The inactive pin is pulled low during the entirety of the transaction.

**Table 11. Two-Pin I<sup>2</sup>S/TDM2 Packet Format (3.072 MHz BCLK, 32-Bit Data, TX0EN = 1, TX1EN = 1)**

| <b>DTX0</b>          | <b>DTX1</b>          |

|----------------------|----------------------|

| X-axis data (32-bit) | Z-axis data (32-bit) |

| Y-axis data (32-bit) | 0x00000000           |

**Table 12. One-Pin TDM4 Packet Format (3.072 MHz BCLK, 16-Bit Data, TX0EN = 1, TX1EN = 0)**

| <b>DTX0</b>          | <b>DTX1</b> |

|----------------------|-------------|

| X-axis data (16-bit) | 0x0000      |

| Y-axis data (16-bit) | 0x0000      |

| Z-axis data (16-bit) | 0x0000      |

| 0x0000               | 0x0000      |

**Table 13. One-Pin TDM4 Packet Format (6.144 MHz BCLK, 32-Bit Data, TX0EN = 1, TX1EN = 0)**

| <b>DTX0</b>          | <b>DTX1</b> |

|----------------------|-------------|

| X-axis data (32-bit) | 0x00000000  |

| Y-axis data (32-bit) | 0x00000000  |

| Z-axis data (32-bit) | 0x00000000  |

| 0x00000000           | 0x00000000  |

**Table 14. One-Pin TDM8 Packet Format (6.144 MHz BCLK, 16-Bit Data, TX0EN = 1, TX1EN = 0)**

| <b>DTX0</b>          | <b>DTX1</b> |

|----------------------|-------------|

| X-axis data (16-bit) | 0x0000      |

| Y-axis data (16-bit) | 0x0000      |

| Z-axis data (16-bit) | 0x0000      |

| 0x0000               | 0x0000      |

Figure 27. 3.072 MHz I<sup>2</sup>S/TDM2 Timing (32-Bit Data)

22623-027

Figure 28. 3.072 MHz TDM4 Timing (16-Bit Data)

22623-028

Figure 29. 6.144 MHz TDM4 Timing (32-Bit Data)

22B23-029

Figure 30. 6.144 MHz TDM8 Timing (16-Bit Data)

22B23-030

## I<sup>2</sup>C INTERFACE

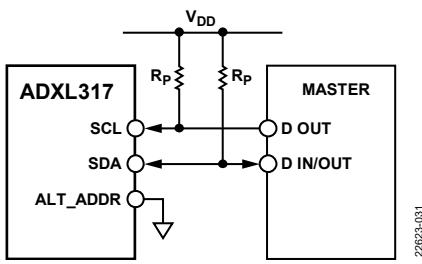

The ADXL317 features a 2-wire I<sup>2</sup>C interface through which the user performs register reads and writes. These reads and writes configure the various device settings. The I<sup>2</sup>C interface conforms to *UM10204 I<sup>2</sup>C-bus specification and user manual*, Rev. 6—4 April 2014, available from NXP Semiconductor, and supports standard data transfer mode at 100 kHz if the bus parameters shown in Table 2 and Table 3 are met. The SCL and SDA lines require pull-up resistors ( $R_P$ ). Refer to *UM10204 I<sup>2</sup>C-bus specification and user manual*, Rev. 6—4 April 2014 (NXP Semiconductor) when selecting pull-up resistor values to ensure proper operation. Single- and multi-byte reads and writes are supported, as shown in Figure 32. When communicating with the ADXL317 via I<sup>2</sup>C, BCLK must be provided with a valid clock signal.

Figure 31. I<sup>2</sup>C Wiring Diagram

### Signals

#### SCL

SCL is the serial clock input to the ADXL317. SCL is generated by the master device and requires a pull-up resistor.

#### SDA

SDA is the serial data line. SDA is bidirectional, with the ADXL317 and master device each controlling the line during different slices of each transaction. SDA also requires a pull-up resistor.

#### Definitions

A start condition is a transition of SDA from high to low while SCL is high.

A stop condition is a transition of SDA from low to high while SCL is high.

An acknowledge condition (ACK) occurs when the transmitter releases the SDA line during the acknowledge clock pulse (the ninth bit following and byte), and the receiver pulls SDA low during the entire high period of this clock pulse. This is denoted as A in the timing diagrams that follow.

A no acknowledge condition (NACK) is similar to an acknowledge, but the receiver pulls SDA high during the entire high period of the acknowledge clock pulse. This is denoted as NA in the timing diagrams that follow.

The ADXL317 device address depends on the wiring of the ALT\_ADDR pin. With this pin grounded, the address is 0x53. With this pin pulled to VDD, the address is 0x1D. All bytes are transmitted MSB first.

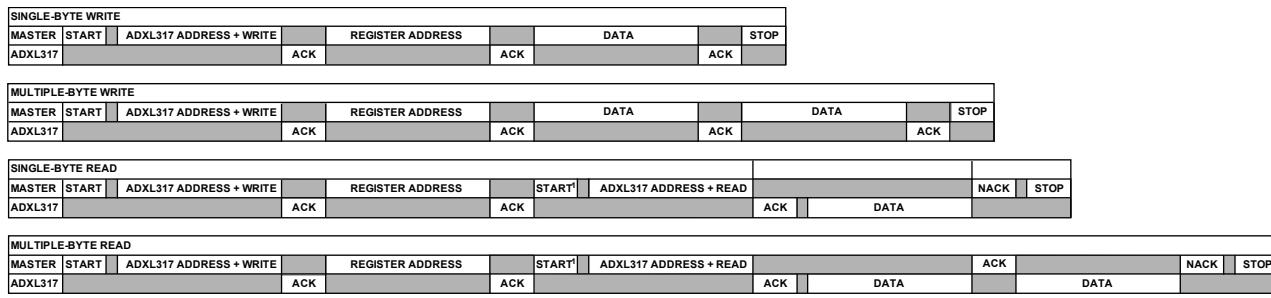

### Register Writes

All commands begin with the master transmitting a start condition followed by the ADXL317 device address and the R/W bit. Because both reads and writes require writing the desired register address to the device, the R/W bit is always low (denoting a write condition) in this first portion of the communication. The ADXL317 responds to this request with an acknowledge condition. Next, the master transmits the address of the register to be written. The ADXL317 again responds with an acknowledge. The master then transmits the data to be written to the specified register, and the ADXL317 responds one last time with an acknowledge. Finally, the transaction is terminated with the transmission of a stop condition from the master.

Multibyte writes are also supported. To write to multiple consecutive registers, the master continues to transmit data bytes between each acknowledge condition. The ADXL317 autoincrements the address and writes each byte to the subsequent register. Only after a stop condition is received does the ADXL317 stop writing.

See Figure 32 for a visual representation of the transactions described in this section. See Figure 2 and Figure 3 for waveforms.

### Register Reads

Reading from a register involves the same first few steps as writing to a register. The master sends a start condition followed by the ADXL317 device address and the R/W bit low. After the ADXL317 responds with an acknowledge, the master transmits the address of the register to read, to which the ADXL317 again responds with an acknowledge.

To differentiate this command from a register write, the master next transmits a repeated start command, followed immediately by the ADXL317 device address, plus the R/W bit high to denote a read condition. The ADXL317 responds to this request with an acknowledge, followed by the contents of the desired register. The master responds to the receipt of this data with a no acknowledge to prevent the ADXL317 from responding further, followed by a stop condition to terminate the transaction.

Multibyte reads are also supported. To read from multiple consecutive registers, the master simply responds with an acknowledge instead of a no acknowledge following the receipt of data. The ADXL317 continues to auto-increment the register address and transmit the contents of each subsequent register until a no acknowledge and stop are received.

See Figure 32 for a visual representation of these transactions and Figure 4 and Figure 5 waveforms.

**Invalid Registers**

The user accessible registers are located at Address 0x00 to Address 0x01 and Address 0x80 to Address 0x8F. See the Register Map section for details regarding the functionality

of these registers. Attempting to read a register outside of these ranges returns all zeros. However, the device responds to the request with an acknowledge condition, which applies to both single- and multi-byte transactions.

<sup>1</sup>THIS START IS EITHER A REPEATED START OR A STOP FOLLOWED BY A START.

**NOTES**

1. THE SHADED AREAS REPRESENT WHEN THE DEVICE IS LISTENING.

Figure 32. I<sup>2</sup>C Communication Format

22B23-032

## FILTERING: NOISE AND LATENCY CONSIDERATIONS

There are several filters in the signal chain of the ADXL317 that can be independently controlled. These filters are as follows:

- Low-pass CIC filter. This filter is always enabled, and the corner frequency can be set to 7.66 kHz, 3.83 kHz, 1.91 kHz, or 957 Hz.

- Low-pass IIR filter. This filter can be turned on or off and is enabled by default. The corner frequency can be set to 5.00 kHz, 2.50 kHz, 1.25 kHz, or 625 Hz.

- High-pass filter. This filter can be turned on or off and is disabled by default. The corner frequency can be set to 29.8 Hz, 7.46 Hz, 1.85 Hz, or 0.46 Hz.

By combining these settings, a wide variety of filter characteristics can be achieved. In addition to the nominal 4 kHz, 2 kHz, 1 kHz, and 500 Hz settings, obtained by matching the values in the `x_IIR_CORNER` and `x_CIC_CORNER_LPF` fields, 12 other settings are possible (see Table 15).

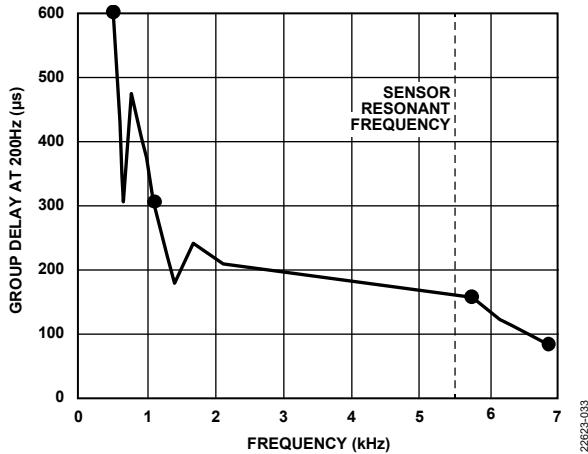

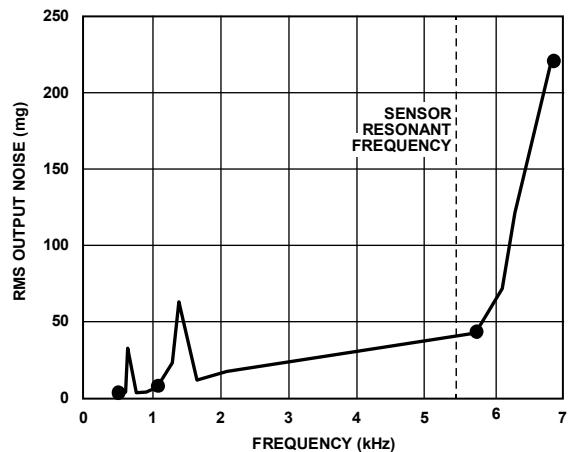

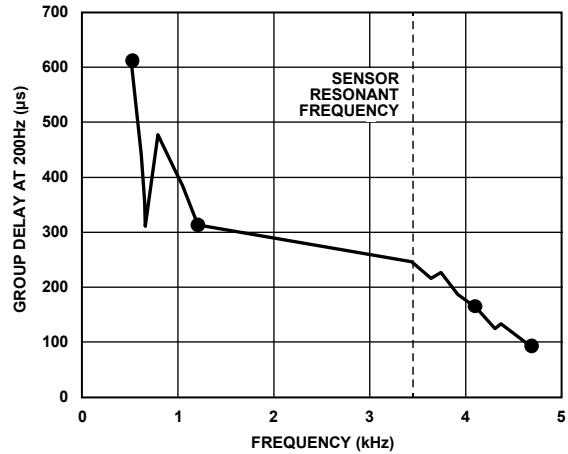

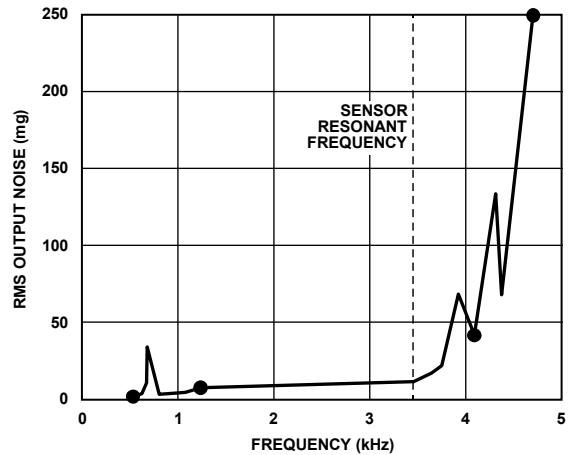

In general, a higher cutoff (-3 dB) frequency results in less delay but more noise, whereas a lower cutoff frequency results in less noise but more delay. These trends are shown in Figure 33 through Figure 36. This phenomenon is not necessarily always the case. Therefore, take care when choosing filter settings to achieve the desired trade-off between noise and latency.

The resonant frequency of the sensor has an impact on the total signal chain response. Filter settings near resonance are shifted to higher frequencies, resulting in higher effective bandwidths. Also, the front-end electronics add a constant delay of approximately 14  $\mu$ s for the x- and y-axes, and 20  $\mu$ s for the z-axis.

Figure 33. X- and Y-Axes Group Delay vs. Frequency for All Filter Settings

(See Table 15 for Specific Items in This Figure Marked with Circles)

Figure 34. X- and Y-Axes Noise vs. Frequency for All Filter Settings

(See Table 15 for Specific Items in This Figure Marked with Circles)

Figure 35. Z-Axis Group Delay vs. Frequency for All Filter Settings

(See Table 15 for Specific Items in This Figure Marked with Circles)

Figure 36. Z-Axis Noise vs. Frequency for All Filter Settings

(See Table 15 for Specific Items in This Figure Marked with Circles)

Table 15. Low-Pass Filter Settings Combinations (X- and Y-Axes)<sup>1</sup>

| CIC Filter |                      | IIR Filter |                      | Cascaded Filters Only             |                                         | Entire Signal Chain |                   |                       |                   |                    |                  |

|------------|----------------------|------------|----------------------|-----------------------------------|-----------------------------------------|---------------------|-------------------|-----------------------|-------------------|--------------------|------------------|

| Setting    | -3 dB Frequency (Hz) | Setting    | -3 dB Frequency (Hz) | -3 dB Frequency (Hz) <sup>2</sup> | Group Delay at 200 Hz (μs) <sup>3</sup> | -3 dB Frequency     |                   | Group Delay at 200 Hz |                   | RMS Noise          |                  |

|            |                      |            |                      |                                   |                                         | X- and Y-Axes (Hz)  | Z-Axis (Hz)       | X- and Y-Axes (μs)    | Z-Axis (μs)       | X- and Y-Axes (mg) | Z-Axis (mg)      |

| 00         | 7668                 | 00         | 5002                 | 4051 <sup>4</sup>                 | 70.9 <sup>4</sup>                       | 6841 <sup>4</sup>   | 4691 <sup>4</sup> | 84.7 <sup>4</sup>     | 91.3 <sup>4</sup> | 85 mg <sup>4</sup> | 120 <sup>4</sup> |

| 00         | 7668                 | 01         | 2501                 | 2343                              | 103                                     | 6297                | 4314              | 117                   | 123               |                    |                  |

| 00         | 7668                 | 10         | 1250                 | 1229                              | 166                                     | 1384                | 3912              | 180                   | 187               |                    |                  |

| 00         | 7668                 | 11         | 625                  | 622                               | 294                                     | 639                 | 668               | 308                   | 314               |                    |                  |