## **High-Speed CAN Transceiver with Partial Networking**

ATA6574

### Description

The ATA6574 is a stand-alone, high-speed CAN transceiver with partial networking that interfaces a Controller Area Network (CAN) protocol controller and a physical two-wire CAN bus designed for high-speed CAN applications in the automotive environment.

The ATA6574 provides local and enhanced remote wake-up capabilities and is available in a 14-lead SOIC package. It has a very low-power consumption in Standby and Sleep mode. Besides local wake-up via the WAKE pin and remote wake-up pattern according to ISO 11898-2:2024, the ATA6574 additionally supports ISO 11898-2:2024 compliant CAN partial networking. A CAN frame decoder evaluates the bus traffic and checks for a matching frame that has been configured into registers via the SPI. The device is able to keep the complete Automotive Electronic Control Unit (ECU) in a low-power mode, even when bus traffic is present, until a valid wake-up frame has been received. It also features a watchdog (by default off) and a Serial Peripheral Interface (SPI).

The ATA6574 is a CAN FD device. However, selective wake-up is only possible using classical CAN frames. In Sleep mode, the device can be configured to either ignore CAN FD frames or to treat CAN FD frames as frames with errors and increment the internal error counter.

The VIO pin allows the automatic adjustment of the I/O levels to the I/O level of the connected microcontroller.

The SPI interface controls the device and provides status and diagnosis information to the host MCU.

All these features make the ATA6574 an excellent choice for high-speed CAN networks, especially in applications where nodes are always connected to the battery but are only activated when they are really needed in the application.

#### **Features**

#### **CAN FD Transceiver**

- High-Speed CAN Transceiver Fully Compliant to ISO 11898-2:2024 and SAE J2284-1 to SAE J2284-5

- Autonomous Bus Biasing According to ISO 11898-2:2024

- Standard CAN Data-Rate up to 1 Mbit/s and CAN FD Data-Rate up to 5 Mbit/s (CAN FD)

- Differential Bus Receiver with Wide Common-Mode Range

- Transceiver Disengages from the Bus In Overtemperature and Low-Power Supply Mode

- Battery Supply and CAN Bus Pins Protected Against Transients According to ISO 7637

- High Electrostatic Discharge (ESD) Handling Capability on the Bus Pins

- Bus Pins Short-Circuit Protected to GND and VCC

- RXD Recessive Clamping Detection

- Transmit Data (TXD) Dominant Time-out Function

- Remote Wake-up Pattern According to ISO 11898-2:2024

- Remote Wake-up Frame According to ISO 11898-2:2024 (Selective Wake-up)

#### **Functional Safety Support**

ISO 26262:2018 Functional Safety Ready up to ASIL B

IEC 61508:2010 Functional Safety Ready up to SIL 2

#### Misc

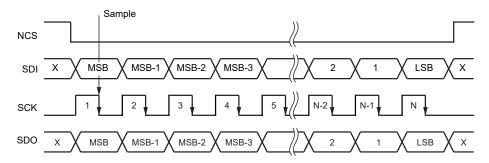

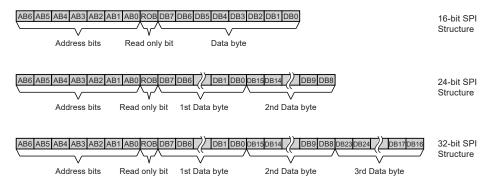

- 4 Mbit/s SPI Interface

- Low Electromagnetic Emission (EME) and High Electromagnetic Immunity (EMI)

- Very Low Current Consumption in Sleep and Standby Mode with Full Wake-up Capability

- Power-Down of the Complete Node via the INH-Output (Switching Off External Voltage Regulator(s))

- Local Wake-up via the WAKE Pin

- Host Wake-up via SPI

- Wake-up Source Recognition

- Undervoltage Detection on VS, VCC and VIO Pins

- · Overtemperature Protection

- 3.3V to 5V Microcontrollers can be Interfaced Directly via the VIO Pin

- VS Operating Voltage up to 28V, VS DC Supply Voltage up to 40V

#### Watchdog

- · Watchdog with Independent Clock Source

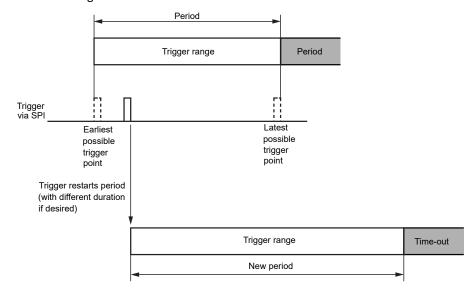

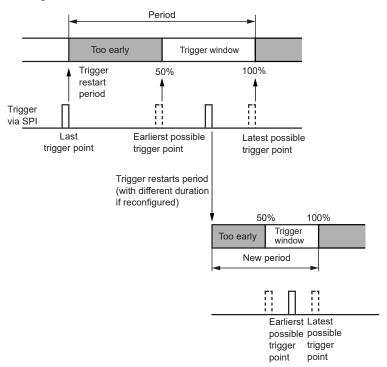

- Watchdog can be Operated in Window and Time-out Mode:

- Optional cyclic wake-up in Watchdog Time-out mode

- Watchdog automatically re-enabled when wake-up event captured

- Watchdog period-selectable

- Watchdog Reset period-selectable

#### **Automotive Qualification**

- AEC-Q100 Qualified Rev. J

- Two Ambient Temperature Grades Available:

- ATA6574-GNQW1-VAO up to  $T_{amb} = +125$ °C

- ATA6574-GNQW0-VAO up to  $T_{amb}$  = +150°C

- Fulfills the OEM "Hardware Requirements for CAN Interfaces in Automotive Applications", Rev. 1.3

- Fulfills the OEM "Requirements for Partial Networking", Rev. 2.2

- CAN FD Transceiver Fully Compliant to SAE J2962-2\_202402

- ESD According to IBEE CAN EMC Test Specification Following IEC 62228-3:2019, IEC61000-4-2:  $(330\Omega/150~pF)$  Pins VS, WAKE  $\pm$  8 kV

- ESD According to IBEE CAN EMC Test Specification Following IEC 62228-3:2019, IEC61000-4-2:  $(330\Omega/150~pF)$  Pins CANH, CANL  $\pm$  6 kV

- 14-Lead SOIC Package (Moisture Sensitivity Level 1)

## **Applications**

- Body Electronics and Lighting

- · Automotive Infotainment

- · Powertrain Systems

- Advanced Driver Assistance Systems (ADAS)

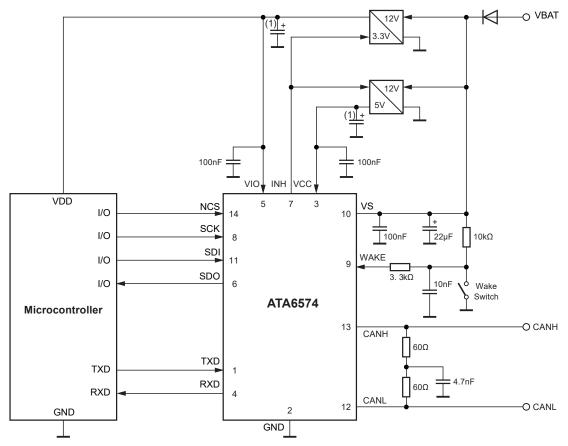

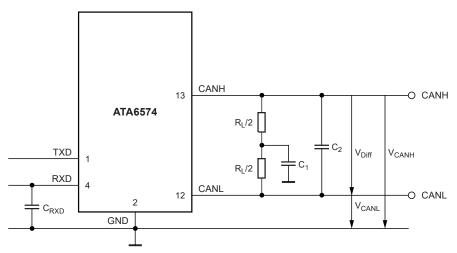

#### **Typical Application Circuits** 1.

Figure 1-1. Typical Application Circuit ATA6574

**Note:**1. The value of these capacitors depends on the external voltage regulators used.

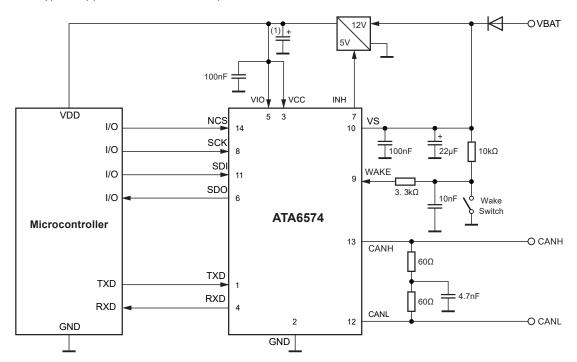

Figure 1-2. Typical Application Circuit 5V Only

Note:

1. The value of this capacitor depends on the external voltage regulator used.

## 2. Product Family

The device names, features, and package types of each device are listed in the following table. All devices integrate a high-speed CAN FD transceiver.

**Table 2-1.** ATA6574 Family Members

| Device            | Grade 0 | Grade 1 | Package |

|-------------------|---------|---------|---------|

| ATA6574-GNQW1-VAO |         | x       | SOIC14  |

| ATA6574-GNQW0-VAO | X       |         | SOIC14  |

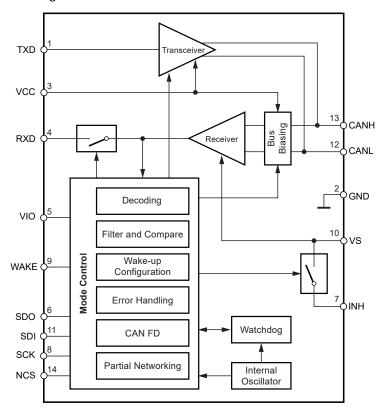

## 3. Block Diagram

Figure 3-1. Simplified Block Diagram

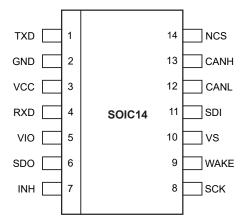

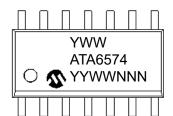

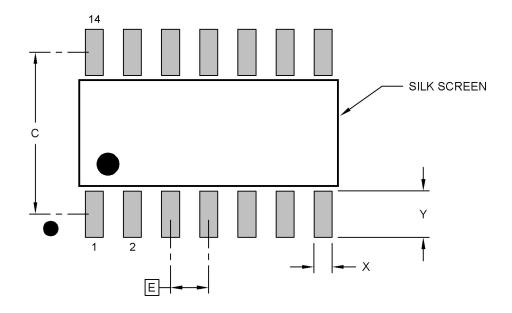

### 4. Pin Configuration

Figure 4-1. Pin Configuration

Table 4-1. Pin Description

| Pin    | Symbol | Function                                                   |

|--------|--------|------------------------------------------------------------|

| SOIC14 |        |                                                            |

| 1      | TXD    | Transmit Data Input                                        |

| 2      | GND    | Ground                                                     |

| 3      | VCC    | 5V CAN Transceiver Supply Voltage                          |

| 4      | RXD    | Receive Data Output, reads out data from the CAN bus       |

| 5      | VIO    | Supply Voltage for I/O Level Adapter                       |

| 6      | SDO    | SPI Serial Data Output                                     |

| 7      | INH    | High-Side Output for Switching External Voltage Regulators |

| 8      | SCK    | SPI Clock                                                  |

| 9      | WAKE   | High-Voltage Input for Local Wake-up                       |

| 10     | VS     | Battery Supply Voltage                                     |

| 11     | SDI    | SPI Serial Data Input                                      |

| 12     | CANL   | Low-Level CAN Bus Line                                     |

| 13     | CANH   | High-Level CAN Bus Line                                    |

| 14     | NCS    | SPI Chip Select Input                                      |

### 4.1 Supply Pin (VS)

The VS supply pin is the power supply pin for the ATA6574 device. In an application, this pin is usually connected to the battery via a serial diode for reverse battery protection. This pin withstands standard automotive conditions, such as 40V during a load dump.

An undervoltage detection circuit is implemented to avoid malfunctions or false bus messages. After switching on VS, the device starts in Standby mode and the INH output is switched on.

### 4.2 Ground Pin (GND)

The device does not affect the CAN bus in the event of GND disconnection.

### 4.3 Supply Pin (VCC)

This is the supply pin for the CANH and CANL bus drivers, the bus differential receiver and the bus biasing voltage circuitry. VCC is monitored for undervoltage conditions.

### 4.4 Supply Pin (VIO)

This is the supply pin for the digital input/output pins. VIO is monitored for undervoltage conditions. See Fail-Safe Features.

### 4.5 Bus Pins (CANH AND CANL)

These are the CAN bus terminals.

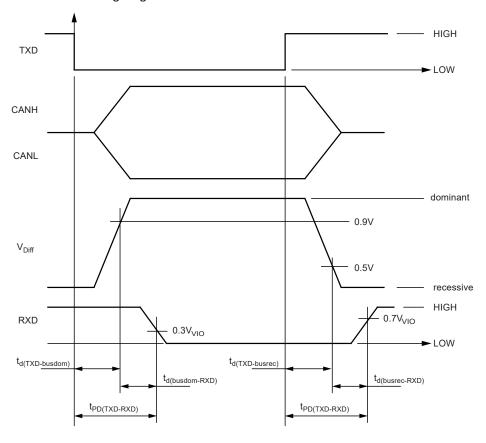

CANH is a high-side driver to VCC, and CANL is a low-side driver to GND. In Normal mode and with TXD high, the CANH and CANL drivers are off, and the voltage at CANH and CANL is approximately 2.5V, provided by the internal bus biasing circuitry. This state is called recessive.

When TXD is low, CANL is pulled to GND and CANH to VCC, creating a differential voltage on the CAN bus. This is called the dominant state.

In Standby mode, the CANH and CANL drivers are off. If the device is in Unpowered mode or Sleep mode, CANH and CANL are highly resistive with extremely low leakage current to GND, making the device ideally passive.

Pins CANH and CANL have integrated ESD protection and extremely high robustness against external disturbances, such as EMC and electrical transients. The CANH and CANL bus outputs are short-circuit protected, either against GND or a positive supply voltage, and are also protected against overtemperature.

### 4.6 Input Pin (TXD)

This is the device input pin that controls the CAN bus level. In the application, this pin is connected to the microcontroller transmit terminal. The TXD pin has an internal pull-up toward VIO to ensure a safely defined recessive driver state in case this pin is left floating.

In Normal mode, when TXD is high or floating, the CAN bus is driven to the recessive state.

TXD must be pulled to GND in order to activate the CANH and CANL drivers and set the bus to the dominant state. A TXD dominant time-out timer is started when the TXD pin is set to low. If the low state on the TXD pin persists for longer than  $t_{to(dom)}$  TXD, the transmitter is disabled, releasing the bus lines to the recessive state. This function prevents a hardware and/or software application failure from driving the bus lines to a permanent dominant state (blocking all network communications). The TXD dominant time-out timer is reset when the TXD pin is set to high.

If the TXD pin is held low (e.g., by a short circuit to GND), the transmitter is disabled and the device is switched into Normal mode and the bus lines are in the recessive state. The transceiver remains in this state until the TXD pin goes high.

### 4.7 Output Pin (RXD)

In Normal and Silent modes, this pin reports the state of the CAN bus to the microcontroller. In the application, this pin is connected to the microcontroller receive terminal. RXD is high when the bus is recessive. When the bus is dominant, RXD is low.

The output is a push-pull structure. The high side is connected to VIO and the low side to GND.

In Standby mode, the RXD output is switched to VIO. When a wake-up event is detected, RXD will be forced to low.

An RXD recessive clamping function (see section RXD Recessive Clamping) is implemented. This fail-safe feature prevents the controller from sending data on the bus if the RXD line is clamped to high (e.g., recessive).

### 4.8 Inhibit Output Pin (INH)

The inhibit output pin provides an internal switch towards VS and is used to control external voltage regulators. If the device is in Normal or Standby mode, the inhibit high-side switch is turned on. When the device is in Sleep mode, the inhibit switch is turned off, thus disabling the connected external voltage regulators or other connected external devices.

A wake-up event on the CAN bus or at the WAKE pin switches the INH pin to the VS level. After a system power-up (VS rises from zero), the INH pin switches to the VS level automatically.

The INH output pin has an additional function when the watchdog is enabled. At every Watchdog Reset, the INH pin will be switched off for a predefined time. This will trigger a Power-on Reset (POR) of the microcontroller if the supply of the microcontroller is controlled by the INH pin.

#### 4.9 Wake Input Pin (WAKE)

In the ATA6574, this pin is a high-voltage input used for waking up the device from Sleep mode. It is usually connected to an external switch to generate a local wake-up. If the WAKE pin is not needed, the local wake-up should be disabled and the WAKE pin should be connected to GND to ensure optimal EMI performance.

The WAKE pin has a special design structure and is triggered by a LOW-to-HIGH and/or a HIGH-to-LOW transition on the WAKE pin. This feature allows for maximum flexibility when designing a local wake-up circuit.

An internal filter is implemented to avoid a false wake-up event due to noise. A serial resistor should be inserted in order to limit the input current mainly during transient pulses and ESD. The recommended resistor value is  $10 \text{ k}\Omega$ . An external 10 nF capacitor is advised for better EMC and ESD performance (see Typical Application Circuits).

#### 4.10 SPI Serial Data In Pin (SDI)

Serial Data In input connected to an output of the microcontroller.

#### 4.11 SPI Serial data out Pin (SDO)

Serial Data Out output connected to an input of the microcontroller; this pin is in tri-state if NCS is high.

### 4.12 SPI Clock Pin (SCK)

Serial data clock; default level is low due to internal pull-down.

### 4.13 SPI Chip Select Pin (NCS)

Chip Select pin; active-low. If Chip Select is not active, no data are loaded from SDI on SCK edges or provided at SDO.

### 5. Functional Description

### 5.1 Device Operating Modes

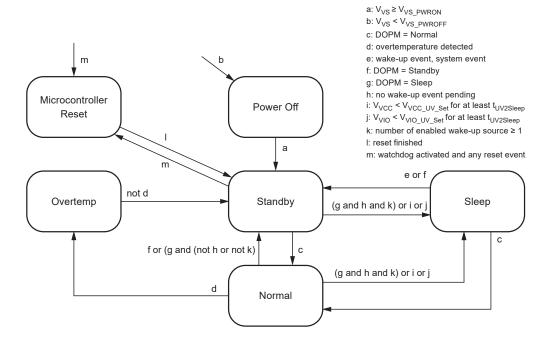

Figure 5-1. Overview to the Device Operating Modes

The mode control unit in the ATA6574 implements six different modes, as depicted in Figure 5-1. All of the modes are briefly described in this section.

Table 5-1. Operating Modes and Functions

| Block | Device Operating Mode |                                                             |                                                                                      |                                                             |                                                            |  |  |  |

|-------|-----------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------|--|--|--|

|       | Power Off             | Standby                                                     | Normal                                                                               | Sleep                                                       | Overtemp                                                   |  |  |  |

| SPI   | Disabled              | Active                                                      | Active                                                                               | Active if VIO<br>Supplied                                   | Disabled                                                   |  |  |  |

| INH   | High Ohmic            | VS Level                                                    | VS Level                                                                             | High Ohmic                                                  | VS Level                                                   |  |  |  |

| CAN   | TRX Off               | TRX Standby/TRX<br>Biased Standby                           | TRX Normal/TRX Standby/TRX<br>Biased Standby/TRX Silent<br>(determined by bits COPM) | TRX Standby/TRX<br>Biased Standby                           | TRX Off                                                    |  |  |  |

| RXD   | VIO Level             | VIO Level/Low if<br>Wake-up/<br>Interrupt Event<br>Detected | CAN Bit Stream if<br>COPM = 01/10/11; Otherwise,<br>same as Standby/Sleep            | VIO Level/Low<br>if Wake-up/<br>Interrupt Event<br>Detected | VIO Level/Low<br>if Wake-up/<br>Interrupt Event<br>Pending |  |  |  |

#### 5.1.1 Power-Off Mode

The device is in Power-Off mode when the supply voltage of the device ( $V_{VS}$ ) is lower than the defined device power-off detection voltage threshold ( $V_{VS\_PWROFF}$ ). This is the default mode when the battery is first connected. In this mode, the integrated CAN transceiver is in the TRX Off mode (see section TRX Off Mode). The watchdog is also in Off mode. The pins, CANH and CANL, are high ohmic, and the INH output is switched off. The device is not able to provide any functionality. As soon as  $V_{VS}$  rises above the power-on detection threshold ( $V_{VS\_PWRON}$ ), the device starts the transition to Standby mode. The whole device is reset and initialized. After  $t_{startup}$ , the device is in the Standby mode.

#### 5.1.2 Standby Mode

The Standby mode is the default mode after a Power-on Reset. In Standby mode, the integrated CAN transceiver is unable to transmit or receive data. The INH pin is at the VS level, and the external voltage regulator controlled by the pin is switched on.

The ATA6574 supports the autonomous bus biasing according to ISO 11898-2:2024 in Standby and Sleep modes (provided  $V_{VS} > V_{VS\_UV\_CAN\_Clear}$ ). The bus pins are biased to GND (via  $R_{CANH}$ ,  $R_{CANL}$ ) when the bus is inactive and at approximately 2.5V when a remote CAN bus wake-up request (Wake-Up Pattern, WUP, according to ISO 11898-2:2024) is detected.

In Standby mode, the ATA6574 supports both CAN bus remote wake-up via a standard WUP and via a selective Wake-up Frame (WUF). The CAN bus remote wake-up is only activated when the register bit CWUE is set to '1' (see section TRXECR). The low-power wake-up comparator in the receiver then monitors the bus activity and wakes up the device after detecting a valid wake-up event ( $V_{VS}$  must be above the VS CAN undervoltage release threshold; otherwise, the integrated transceiver is in TRX Off mode and no bus wake-up can be detected).

If CPNE = PNCFOK = 1, the selective wake-up is enabled. After a successful detection of a wake-up pattern, the bus pins are biased to 2.5V and the device is ready for decoding WUFs. Only after detecting a valid WUF, the wake-up event is registered and the wake-up process is finished. Decoding of CAN data and remote frames is supported during all mode transitions of the device. If the data frame is a valid WUF, the device will indicate a wake-up event.

If the selective wake-up is disabled and CAN remote wake-up is enabled, the standard wake-up via WUP is activated. The device biases its bus pin to 2.5V after successfully detecting a wake-up pattern, registers the wake-up event and completes the wake-up process.

The device also supports detecting system events (see section Wake-up and Interrupt Event Diagnosis via RXD Pin) and a local wake-up event via the WAKE pin in Standby mode. The internal wake-up flags, CWUS, LWURS and LWUFS (see sections TRXESR and WKESR), and the system event status registers are set to '1' by the device if the corresponding event is detected.

The device will not leave Standby mode after detecting a valid wake-up event. It will only set the corresponding internal Status register bits. A transition to the Normal mode will only happen when the register bits DOPM are set to '111' via SPI.

In Standby mode, the detection of a wake-up event or an interrupt event (see section Wake-up and Interrupt Event Diagnosis via RXD Pin) is denoted via the RXD pin, provided that the corresponding event interrupt is enabled (see section SECR to section WKECR). The RXD pin is usually at  $V_{VIO}$  level and will be forced to low if an enabled event is detected. The Status registers (see sections GESR through WKESR) allow the microcontroller to get further detailed information about the device via SPI

As shown in Figure 5-1, the device will enter Standby mode in the following cases:

- 1. From Power-Off mode: When the Power-on Reset disappears after  $V_{VS}$  rises above the power-on detection voltage threshold  $V_{VS\ PWRON}$ .

- 2. From Overtemp mode: After the chip temperature drops more than the thermal shutdown hysteresis T<sub>vlsd hvs</sub>.

- 3. From Sleep mode: After detecting enabled wake-up event or interrupt event.

- 4. From Sleep mode or Normal mode via SPI (DOPM = 0x4): If a valid interface voltage  $V_{VIO}$  is applied.

- 5. During a pending wake-up event: If Sleep mode is requested (DOPM = 0x1 is written) via SPI or all wake-up sources are disabled.

The watchdog can be activated (Window or Time-out mode) in Standby mode. To avoid unwanted configuration of the watchdog, configuration can only be done in Standby mode.

#### 5.1.3 Sleep Mode

Sleep mode is the most power-saving mode of the device. In this mode, the INH output is switched off. Therefore, the external voltage regulator(s) controlled by this pin is also switched off. This is the only difference between Sleep mode and Standby mode. If a valid Interface Supply Voltage (V<sub>VIO</sub>) is applied, registers of the device can still be accessed via the device's SPI interface.

As in Standby mode, the device can react to a variety of wake-up events (see section Wake-up). The device can be configured to be woken up in different ways. If a valid Interface Voltage  $V_{VIO}$  is applied, it is even possible to wake up the device from Sleep mode via an SPI command (DOPM = Standby/Normal).

The INH output switches on when either a CAN bus wake-up event, a host wake-up event (via SPI), a local wake-up, or an interrupt event (see section Interrupt Event/Wake-up Event Delay) is detected and the device switches into Standby mode. The INH output also switches on when a Watchdog Reset (Time-out mode) occurs and the device switches to microcontroller Reset mode.

As shown in Figure 5-1, the device enters Sleep mode in the following cases:

- 1. From the Normal mode or Standby mode via an SPI command, if no wake-up event is pending and at least one wake-up source (see section Wake-up) is enabled.

- 2. From the Normal mode or Standby mode, when detecting VCC or VIO undervoltage ( $V_{VIO} < V_{VIO\_UV\_Set}$  or  $V_{VCC\_UV\_Set}$  for  $t > t_{UV2Sleep}$ ). In this case, all pending wake-up events will be cleared. CAN bus wake-up (CWUE = 1; see section TRXECR) and local wake-up via the WAKE pin (LWUFE = 1 && LWURE = 1) are enabled. Selective wake-up is disabled (see section VCC/VIO Undervoltage Protection for details about VCC/VIO undervoltage protection).

The ATA6574 provides an SMTS bit (see DMSR) to denote whether or not the recent transition to Sleep mode is triggered by a VCC/VIO undervoltage event. The bit can be read by the microcontroller in Sleep mode (if a valid interface supply voltage is provided) or after waking up from Sleep mode.

#### 5.1.4 Normal Mode

In Normal mode, the transceiver can transmit and receive data through the bus lines CANH and CANL. This is the normal transmitting and receiving mode of the CAN Interface, in accordance with the CAN specification. The output driver stage is active and drives data from the TXD input to the CAN bus. The High-Speed Comparator (HSC) converts the differential signal on the bus lines into a digital signal, which is output to the RXD pin. The bus biasing is set to  $V_{VCC/2}$ . The slope of the output signals on the bus lines is controlled and optimized in a way that guarantees the lowest possible Electromagnetic Emission (EME).

The INH output is switched ON, so external loads controlled by the INH pin are also switched ON.

Wake-up flag CWUS and Interrupt Event Status registers will still be set to '1' by the device if the corresponding event is detected.

As shown in Figure 5-1, the device will enter Normal mode from Standby mode or Sleep mode via an SPI command.

#### 5.1.5 Overtemp Mode

The Overtemp mode is the operating mode which protects the device against damage due to overtemperature. The overtemperature protection is only active in Normal mode.

The device provides two levels of overtemperature protection. If the chip temperature rises above the overtemperature protection prewarning threshold (T >  $T_{OT\_Prew}$ ), the device first sets the status bit to OTPWS = 1. If the overtemperature prewarning interrupt is enabled (OTPWE = 1), an overtemperature prewarning interrupt will be generated (OTPW = 1, RXD signalization if COPM = 00 and DOPM = 111 (Normal mode)).

The device will enter Overtemp mode when the chip temperature rises above the overtemperature protection shutdown threshold ( $T_{lsd}$ ). In Overtemp mode, the integrated CAN transceiver is switched

to the TRX Off mode. The CAN bus pins are high ohmic. No further wake-up event will be detected, but the pending wake-up/interrupt event will still be signaled by a low level on pin RXD. As shown in Figure 5-1, the device will enter Overtemp mode from Normal mode when the chip temperature rises up the overtemperature protection shutdown threshold.

The device will exit Overtemp mode and enter Standby mode when the chip temperature drops by more than the thermal shutdown hysteresis ( $T_{vlsd\ hys}$ ) or when the device is powered off.

#### 5.1.6 Microcontroller Reset Mode

Transitions to Reset mode are only enabled when the watchdog is activated. In this mode, the INH output is switched off and the transceiver is disabled. The device transitions to Standby mode when the reset pulse width is reached.

#### 5.1.7 Related Registers

#### 5.1.7.1 Device Mode Control Register (Address 0x01)

Name: DMCR Offset: 0x01 Reset: 0x4

**Property:** Read/Write

The device operating mode is selected via bits DOPM in the device mode control register. The register is accessed via SPI at address 0x01. The register reflects the current mode when read.

| Bit    | 7 | 6 | 5             | 4         | 3 | 2   | 1   | 0   |

|--------|---|---|---------------|-----------|---|-----|-----|-----|

|        |   |   | Reserved[4:0] | DOPM[2:0] |   |     |     |     |

| Access | R | R | R             | R         | R | R/W | R/W | R/W |

| Reset  | 0 | 0 | 0             | 0         | 0 | 1   | 0   | 0   |

Bits 7:3 – Reserved[4:0] Reserved for future use

#### Bits 2:0 – DOPM[2:0] Select Device Operating Mode

| DOPM[2:0] | Device Operating Mode |

|-----------|-----------------------|

| 3'b001    | Sleep mode            |

| 3'b100    | Standby mode          |

| 3'b111    | Normal mode           |

#### 5.1.7.2 Device Mode Status Register (Address 0x03)

Name: DMSR Offset: 0x03 Reset: 0x20 Property: Read-only

The register provides device operating mode transition related information.

| Bit    | 7    | 6     | 5    | 4             | 3 | 2 | 1 | 0 |  |

|--------|------|-------|------|---------------|---|---|---|---|--|

|        | SMTS | OTPWS | NMTS | Reserved[4:0] |   |   |   |   |  |

| Access | R    | R     | R    | R             | R | R | R | R |  |

| Reset  | 0    | 0     | 1    | 0             | 0 | 0 | 0 | 0 |  |

#### Bit 7 - SMTS Sleep mode transition status

The device sets the bit to '0' if the recent transition to Sleep mode was triggered by an SPI command and sets the bit to '1' if the recent transition to Sleep mode was forced by a VCC/VIO undervoltage.

#### Bit 6 – OTPWS Overtemperature prewarning status

The device sets the bit to '1' if the device temperature is higher than the overtemperature prewarning threshold and to '0' if the device temperature is below the overtemperature prewarning threshold.

#### Bit 5 - NMTS Normal mode transition status

The device sets the bit to '0' when IC has entered Normal mode after power-up and set the bit to '1' when the IC has powered up but has not yet switched to Normal mode.

#### Bits 4:0 - Reserved[4:0] Reserved for future use

#### 5.2 Integrated CAN Transceiver Operating Modes

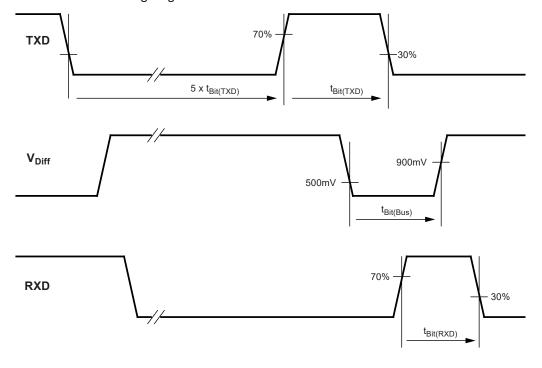

The integrated high-speed CAN transceiver in the ATA6574 is designed for classical CAN bit rates up to 1 Mbit/s and CAN Flexible Data-Rate (CAN FD) bit rates up to 5 Mbit/s. It provides differential transmit and receive capability to a CAN protocol controller. The transceiver is ISO 11898-2:2024 compliant.

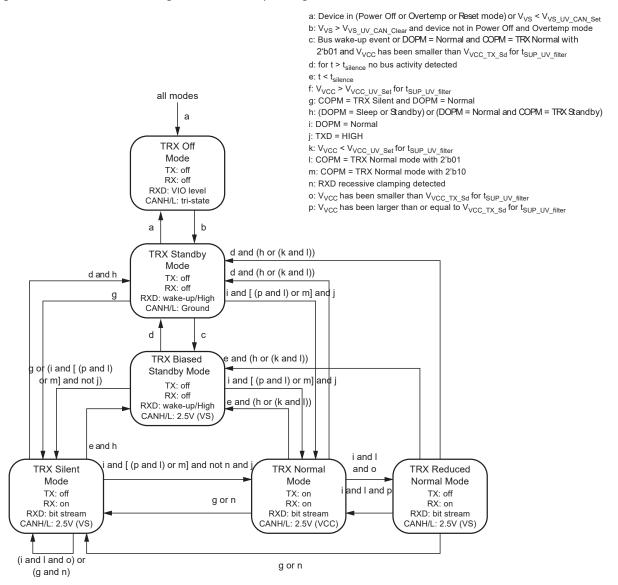

The integrated CAN transceiver supports the following operating modes: TRX Normal, TRX Reduced Normal, TRX Silent, TRX Standby and TRX Biased Standby (see Figure 5-2). The CAN transceiver operating mode depends on the device operating mode and on the setting of bits COPM in the CAN Mode Control register (see section TRXCR). When the device is in Normal mode, all four operating modes can be selected. The TRX Biased Standby mode cannot be selected via the COPM bits directly (see section TRX Biased Standby Mode). The operating modes of the integrated transceiver can be selected via bits COPM in the CAN Mode Control register (see section TRXCR). When the device is in Standby or Sleep mode, the transceiver is either in TRX Standby mode or in TRX Biased Standby mode.

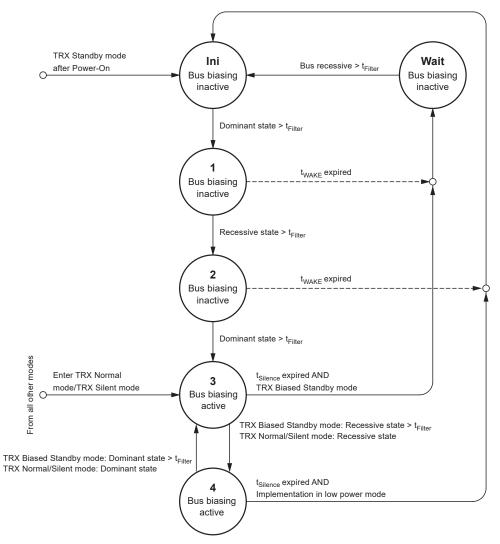

The CAN transceiver supports autonomous bus biasing in compliance with ISO 11898-2:2024. It is active in CAN TRX Standby mode. The bus is biased to 2.5V if there is activity on the bus (TRX Biased Standby mode). In TRX Biased Standby mode, the CAN bias voltage is derived directly from  $V_{VS}$ . If there is no activity on the bus for  $t > t_{Silence}$ , the bus is biased to GND (TRX Standby mode).

In TRX Normal and TRX Silent mode, the bus pins, CANH and CANL, are biased to 2.5V (see section TRXCR). The CAN bias voltage is derived from  $V_{VCC}$  in TRX Normal mode and derived from  $V_{VS}$  in TRX Silent mode. In TRX Off mode, the bus pins are highly resistive and the transceiver is disengaged from the bus.

Figure 5-2. Overview to the Integrated CAN TRX Operating Modes

#### 5.2.1 TRX Off Mode

The CAN transceiver is completely switched off in TRX Off mode. The CAN bus pins, CANH and CANL, are highly resistive and the RXD pin is at the VIO level.

As shown in Figure 5-2, the integrated CAN transceiver enters the TRX Off mode in the following cases:

- 1. The device switches to Power-Off mode.

- 2. The device switches to Overtemp mode.

- 3. V<sub>VS</sub> falls below the CAN undervoltage detection threshold, V<sub>VS UV CAN Set</sub>.

The integrated CAN transceiver will be switched on again and will enter CAN TRX Standby mode when  $V_{VS}$  rises above the CAN undervoltage release threshold and the device is no longer in Power-Off/Overtemp mode.

#### 5.2.2 TRX Standby Mode

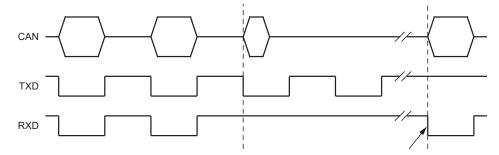

In TRX Standby mode, the transmitter and the receiver are switched off to reduce current consumption. The wake-up comparator monitors the bus lines for a valid remote bus Wake-up Pattern (WUP), provided that CAN bus wake-up detection is enabled (CWUE = 1). Two periods of dominant bus levels, separated by a period of recessive bus level, each of at least  $t_{Filter}$ , switch the RXD pin to low to signal a wake-up request to the microcontroller. Figure 5-3 describes the process and timing of the WUP detection. In the TRX Standby mode, the bus lines are biased to ground to reduce current consumption to a minimum.

CANH

CANL  $t_{dom} = t_{Filter}$   $t \le t_{Wake}$ Bus-wake-up is signaled

Figure 5-3. Timing of CAN Standard Wake-up via Wake-up Pattern (WUP)

As shown in Figure 5-2, the CAN transceiver enters TRX Standby mode in the following cases:

- 1. When the device leaves Power-Off mode or Overtemp mode and sufficient  $V_{VS}$  is applied.

- 2. Any of the conditions for CAN TRX Biased Standby mode are valid for longer than t<sub>Silence</sub> (see section TRX Biased Standby Mode).

#### 5.2.3 TRX Biased Standby Mode

The CAN transceiver behavior in the TRX Biased Standby mode is fundamentally the same as in the TRX Standby mode. The only difference is that in the TRX Biased Standby mode, the bus pins are biased to 2.5V. The integrated CAN transceiver will enter this mode when activity is detected on the CAN bus while the transceiver is in TRX Standby mode. The transceiver will return to TRX Standby mode if the CAN bus is silent for longer than t<sub>Silence</sub> (see Figure 5-4).

As shown in Figure 5-2, the CAN transceiver enters TRX Biased Standby mode in the following cases:

- 1. From TRX Silent/Normal/Reduced Normal mode, when  $t_{Silence}$  did not expire and the device is in Standby (DOPM = 100) or Sleep mode (DOPM = 001).

- 2. From TRX Silent/Normal/Reduced Normal mode, when  $t_{Silence}$  did not expire and the device is in Normal mode (DOPM = 111), and the COPM is set to TRX Standby mode (COPM = 00).

- 3. From TRX Normal/Reduced Normal mode (COPM = 01), when VCC <  $V_{VCC\_UV\_Set}$  is detected and  $t_{Silence}$  did not expire.

- 4. From TRX Standby mode when the device is in Normal mode (DOPM = 111), COPM is set to TRX Normal mode (COPM = 01) and VCC < V<sub>VCC TX Sd</sub> has been detected.

- 5. From TRX Standby mode when a wake-up event is detected on the CAN bus.

#### 5.2.4 TRX Silent Mode

The TRX Silent mode is a Receive-Only mode of the CAN transceiver. It can be used to test the connection of the bus medium or for the software-driven selective wake-up. In the TRX Silent mode, the device can still receive data from the bus, but the transmitter is disabled, and therefore, no data can be sent to the CAN bus. The bus pins are released to the recessive state. All other IC functions continue to operate as they do in the TRX Normal mode. CAN biasing remains active. Silent mode can be used to prevent a faulty CAN controller from disrupting all network communications. As shown in Figure 5-2, the CAN transceiver enters the TRX Silent mode in the following cases:

- 1. The device is in Normal mode (DOPM = Normal) and the CAN transceiver is in TRX Silent mode (COPM = TRX Silent).

- 2. The device is in Normal mode and the CAN transceiver is in TRX Normal mode, and a RXD recessive clamping failure is detected.

The CAN transceiver will remain in TRX Silent mode if a VCC undervoltage or an RXD recessive clamping failure is detected, even if CAN TRX Normal mode is selected in device Normal mode.

#### 5.2.5 TRX Normal Mode

In TRX Normal mode, the integrated transceiver is able to transmit and receive data via the CANH and CANL bus lines. The output driver stage is active and drives data from the TXD input to the CAN bus. The receiver converts the analog data on the bus lines into digital data, which are output to pin RXD. The bus biasing is set to  $V_{VCC}/2$  and the undervoltage monitoring of  $V_{VCC}$  is active.

The slope of the output signals on the bus lines is controlled and optimized in a way that ensures the lowest possible Electromagnetic Emission (EME).

As shown in Figure 5-2, the CAN transceiver enters TRX Normal mode in the following cases:

- 1. The device is in Normal mode (DOPM = Normal) **AND** the CAN transceiver has been enabled by setting bits COPM to '01' or '10' **AND** no VCC undervoltage is detected, **AND** no RXD recessive clamping is detected.

- 2. The transceiver is in the TRX Reduced Normal mode and  $V_{VCC} > V_{VCC}$  TX Sd for  $t > t_{SUP}$  UV filter.

If pin TXD is held low (e.g., by a short circuit to GND) when CAN TRX Normal mode is selected via bits COPM, the transceiver will not enter CAN TRX Normal mode but will switch to or remain in TRX Silent mode. It will remain in TRX Silent mode until pin TXD goes high in order to prevent a hardware and/or software failure from driving the bus lines to an unwanted dominant state.

The application can determine whether the CAN transceiver is ready to transmit data or is disabled by reading the CAN Transmitter Status bit (TXS) in the Transceiver Status Register (see section TRXSR).

#### 5.2.6 TRX Reduced Normal Mode

In the TRX Reduced Normal mode, the transmitter is switched off as VCC is lower than the  $V_{VCC\_TX\_Sd}$  threshold. All other features available in the TRX Normal mode are also provided in the TRX Reduced Normal mode.

As shown in Figure 5-2, the CAN transceiver enters the TRX Reduced Normal mode when the transceiver is in TRX Normal mode and  $V_{VCC} < V_{VCC}$  TX Sd for t > t<sub>SUP UV filter</sub>.

#### 5.2.7 Related Registers

#### 5.2.7.1 CAN Transceiver Control Register (Address 0x20)

Name: TRXCR Offset: 0x20 Reset: 0x41

**Property:** Read/Write

| Bit    | 7        | 6     | 5      | 4    | 3             | 2 | 1         | 0   |

|--------|----------|-------|--------|------|---------------|---|-----------|-----|

|        | Reserved | CFDPE | PNCFOK | CPNE | Reserved[1:0] |   | COPM[1:0] |     |

| Access | R        | R/W   | R/W    | R/W  | R             | R | R/W       | R/W |

| Reset  | 0        | 1     | 0      | 0    | 0             | 0 | 0         | 1   |

#### Bit 7 - Reserved Reserved for future use

#### Bit 6 - CFDPE

The host microcontroller should set the bit to '1' to enable the CAN FD passive feature when selective wake-up is activated, otherwise, it should be set to '0'. The bit is set to 1 by default after Power-on Reset. This setting has the effect that CAN FD frames are ignored when the device is waiting for a WUP. If set to '0', the error counter will increase if FD frames with a higher data bit rate are sent during that time.

#### Bit 5 - PNCFOK

The host microcontroller should set the bit to '1' after successfully configuring the partial networking registers, otherwise set to '0'. In addition, the device will reset the bit to 0 automatically after any write access to the partial networking configuration related registers.

#### Bit 4 - CPNE

The host microcontroller should set the bit to '1' to enable selective wake-up; otherwise, it should be set to '0'.

#### Bits 3:2 - Reserved[1:0] Reserved for future use

#### Bits 1:0 - COPM[1:0]

The TRXCR register is a control register. Therefore, the state of the transceiver will not be mirrored to this register. The COPM bit only defines the targeted state of the transceiver when the device is switched to Normal mode. The finite state machine in Figure 5-2 will not change the COPM bits.

| COPM[1:0]      | CAN TRX Operating Mode                                                                                                                                                                                                                                                           |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2'b00          | TRX Standby mode.                                                                                                                                                                                                                                                                |

| 2 <b>'</b> b01 | TRX Normal mode (when DOPM = Normal), VCC undervoltage detection active for the transceiver finite state machine. The transceiver switches to the TRX Biased Standby mode immediately after detecting the VCC undervoltage.                                                      |

| 2'b10          | TRX Normal mode (when DOPM = Normal), VCC undervoltage detection inactive for the transceiver finite state machine. The transceiver switches from TRX Normal/Reduced Normal mode to TRX Biased Standby mode when the device is forced to Sleep mode by a VCC undervoltage event. |

| 2'b11          | TRX Silent mode.                                                                                                                                                                                                                                                                 |

### 5.2.7.2 CAN Transceiver Status Register (Address 0x22)

Name: TRXSR

Offset: 0x22

Reset: 0x48

Property: Read-only

| Bit    | 7   | 6      | 5     | 4      | 3    | 2        | 1    | 0      |

|--------|-----|--------|-------|--------|------|----------|------|--------|

|        | TXS | PNERRS | PNCFS | PNOSCS | CBSS | Reserved | VCCS | TXDOUT |

| Access | R   | R      | R     | R      | R    | R        | R    | R      |

| Reset  | 0   | 1      | 0     | 0      | 1    | 0        | 0    | 0      |

#### Bit 7 - TXS

The device sets the bit to '1' if the transmitter is ready to transmit data and to '0' if the CAN transmitter is disabled.

#### Bit 6 - PNERRS

The device sets the bit to '0' if no CAN partial networking error is detected (PNEFD = 0 and PNCFOK = 1 and no oscillator hardware failure is detected (default)); it is set to '1' if  $PNEFD = 1 \mid PNCFOK = 0$ .

#### Bit 5 - PNCFS

The device sets the bit to '0' if a partial networking configuration error is detected (PNCFOK = 0); otherwise it is set to '1'.

#### Bit 4 - PNOSCS

The device sets the bit to '1' if the CAN partial networking oscillator is running at target frequency; otherwise it is set to '0'.

#### Bit 3 - CBSS

The device sets the bit to '1' if the CAN bus is inactive (for longer than t<sub>Silence</sub>); otherwise it is set to '0'.

### Bit 2 - Reserved Reserved for future use

#### Bit 1 - VCCS

The device sets the bit to '1' if  $V_{VCC}$  is below the undervoltage detection threshold; it is set to '0' if  $V_{VCC}$  is above the undervoltage detection threshold. This bit is only active in Device Standby and Normal mode.

#### Bit 0 - TXDOUT

The device sets the bit to '1' if the CAN transmitter is disabled due to a TXD dominant time-out event; it is set to '0' if no TXD dominant time-out event was detected.

#### 5.2.7.3 Bus Failure Indication Register (Address 0x33)

Name: BFIR Offset: 0x33 Reset: 0x00 Property: Read-only

| Bit    | 7             | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|--------|---------------|---|---|---|---|---|---|-----|

|        | Reserved[5:0] |   |   |   |   |   |   | BSC |

| Access | R             | R | R | R | R | R | R | R   |

| Reset  | 0             | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

Bits 7:2 - Reserved[5:0] Reserved for future use

#### Bit 1 - BOUT

The BOUT bit shows the current status of the bus dominant time-out detection. If the bit reads '1', the bus is currently in a dominant time-out state; otherwise, the bit reads '0'.

#### Bit 0 - BSC

The BSC bit shows the current status of the bus short-circuit event detection. If the bit reads '1', the bus is currently in a short-circuit state, otherwise the bit reads '0'.

#### 5.2.7.4 Transceiver Event Status Register 2 (Address 0x35)

Name: TRXESR2

Offset: 0x35

Reset: 0x00

Property: Read-only

| Bit    | 7             | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|---------------|---|---|---|---|---|---|---|

|        | Reserved[6:0] |   |   |   |   |   |   |   |

| Access | R             | R | R | R | R | R | R | R |

| Reset  | 0             | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Bits 7:1 - Reserved[6:0] Reserved for future use

#### Bit 0 - RXDRCS

The device sets the bit to '1' if the event is enabled in the TRXECR2 register and a RXD recessive clamping event is detected. The bit is reset to '0' by the device either when the device enters Sleep, Standby or Unpowered mode, or the RXD pin shows dominant again.

### 5.3 Wake-up

#### 5.3.1 Local Wake-up via WAKE Pin

The device provides the high-voltage WAKE input pin that can be used to wake-up the device. It is an edge-sensitive pin (LOW-to-HIGH or HIGH-to-LOW transition). Thus, even if the WAKE pin is at high or low voltage, it is possible to switch the IC into Sleep mode. The WAKE pin is usually connected to the ignition switch to generate a local wake-up when the ignition is switched on.

A glitch suppression circuit is integrated to avoid unexpected wake-up due to noise. The voltage on the pin is detected as stable only when the level remains stable for  $t_{local\_wu}$ . Therefore, a local wake-up request is detected when the logic level on the WAKE pin has already been stable for at least  $t_{local\_wu}$  and the new level remains stable for at least  $t_{local\_wu}$ .

Local wake-up via the WAKE pin can be enabled/disabled via the register bits, LWUFE and LWURE (see section WKECR), and the logic level at the WAKE pin can be read via the register PWKS (see section PWKS) if V<sub>VIO</sub> is within valid range.

To reduce the battery current during Low-Power mode, the WAKE pin has internal pull-up/pull-down current sources that are activated when a stable level at the WAKE pin has been detected:

- High level on pin is followed by an internal pull-up towards VS.

- Low level is followed by an internal pull-down toward GND.

Local wake-up can only be activated in Standby and Sleep mode. In Normal mode, the status of the voltage on the WAKE pin can always be read via bit PWKVS. Otherwise, PWKVS is only valid if local wake-up is enabled. In applications that do not make use of the local wake-up feature, local wake-up should be disabled and the WAKE pin should be connected to GND to ensure optimal EMI performance.

# 5.3.2 Remote Wake-up Pattern (WUP) According to ISO 11898-2:2024 (Partial Networking Disabled)

If the CAN transceiver is in TRX Standby mode and CAN bus wake-up is enabled (CWUE = 1), but CAN selective wake-up is disabled (CPNE = 0 or PNCFOK = 0), the device will monitor the bus for a wake-up pattern as specified in ISO 11898-2:2024.

This filtering helps avoid spurious wake-up events, which could be triggered, for example, by a dominant clamped bus or by dominant phases due to noise, spikes on the bus, transients or EMI.

The wake-up pattern consists of two dominant bus levels for a duration of at least  $t_{Filter}$ , each separated by a recessive bus level with a duration of at least  $t_{Filter}$ . Dominant or recessive bits in between the above mentioned phases that are shorter in duration than  $t_{Filter}$  are ignored.

The complete dominant-recessive-dominant pattern, as shown in Figure 5-3, must be received within  $t_{Wake}$  to be recognized as a valid wake-up pattern. Otherwise, the internal wake-up logic is reset. The complete wake-up pattern will then need to be retransmitted to trigger a wake-up event.

When a valid CAN WUP is detected on the bus, the wake-up bit CWUS in the Transceiver Event Status register is set (see section TRXESR), and the RXD pin driven low. If the device is in Sleep mode when the wake-up event is detected, it will switch the INH pin to VS to activate external voltage regulators (e.g., for supplying VCC and VIO) and enter Standby mode.

CAN wake-up via WUP can only be disabled via bit CWUE. If CWUE is set to '0', no remote wake-up via the CAN bus is possible. If CWUE is set to '1' and selective wake-up is disabled, the device will switch to Standby mode after detecting the Wake-up Pattern (WUP) coming from Sleep mode. If CWUE is set to '1' and the selective wake-up is enabled, the device will first switch on the bus biasing after detecting the WUP and will only switch to Standby mode afterward, when it detects a valid WUF (please refer to section CAN Selective Wake-up for WUF).

Figure 5-4 illustrates the control of the bus biasing and the WUP detection.

Figure 5-4. WUP Detection and Bias Control

### 5.3.3 Remote Wake-up Frame (WUF) According to ISO 11898-2:2024

#### 5.3.3.1 CAN Selective Wake-up

Partial networking makes it possible for a CAN node or a CAN sub-network to be woken up individually by means of dedicated and predefined frames, the so-called Wake-up Frames (WUF). When a particular node's tasks are not required, it is in selective Sleep mode.

The transceiver monitors the bus for dedicated CAN wake-up frames when both CAN wake-up (CWUE = 1) and CAN selective wake-up (CPNE = 1) are enabled, and the Partial Networking registers are configured correctly (PNCFOK = 1). An accurate oscillator and a low-power, high-speed comparator are activated to correctly detect wake-up frames.

According to ISO11898-2, a wake-up frame is a CAN frame consisting of an Identifier field (ID), a Data Length Code (DLC), a data field (optional) and a Cyclic Redundancy Check (CRC) code, including the CRC delimiter.

The wake-up CAN frame (ID and data) is fully configurable via the related registers for configuring CAN partial networking. A Standard (11-bit) or Extended (29-bit) Identifier for the wake-up frame format can be selected via the IDE bit in the Frame Control register, CFCR (see section CFCR).

The WUF ID is configured in the ID registers (see sections CIDR0 to CIDR3). ID bits can be masked using the ID mask (see sections CIDMR0 to CIDMR3), where a '1' means 'don't care'.

A single wake-up frame can wake up multiple groups of nodes by comparing the incoming data field with the data mask, as the data field indicates which nodes are to be woken up. Groups of nodes can be predefined and associated with bits in a data mask.

The number of data bytes expected in the data field of a CAN wake-up frame is set with the Data Length Code (bits DLC in the Frame Control register in section CFCR). If DLC  $\neq$  0000 (one or more data bytes expected), at least one bit in the data field of the received wake-up frame must be set to '1' and at least one corresponding bit in the associated Data Mask register in the transceiver (register for data mask to be defined) must also be set to '1' for a successful wake-up. Each matching pair of logic '1's indicates a group of nodes to be activated (since the data field is up to 8 bytes long, up to 64 groups of nodes can be defined).

If DLC = 0000, a node will wake-up if the WUF contains a valid identifier and the received data length code is '0000', regardless of the values stored in the data mask. If DLC  $\neq$  0000 and all data mask bits are set to '0', the device cannot be woken up via the CAN bus (note that all data mask bits are '1' by default). If a WUF contains a valid ID but the DLCs (in the Frame Control register and in the WUF) do not match, the data field is ignored and no nodes will be woken up. The Data Length Code and the data field can be excluded from the evaluation of the wake-up frame. If bit PNDM = 0 (see section CFCR), only the identifier field is evaluated to determine if the frame contains a valid wake-up frame. If PNDM = 1 (the default value), the data field is included as part of the wake-up filtering.

When PNDM = 0, a valid wake-up frame is detected and a wake-up event is captured (and CWUS is set to '1') when:

- The identifier field in the received wake-up frame matches the pattern in the ID registers after filtering AND

- The CRC field in the received frame (including a recessive CRC delimiter) was received without error.

When PNDM = 1, a valid wake-up frame is detected when:

- The identifier field in the received wake-up frame matches the pattern in the ID registers after filtering AND

- The frame is not a remote frame AND

- The Data Length Code in the received frame matches the configured Data Length Code (bits DLC)

AND

- If the Data Length Code is greater than 0, at least one bit in the data field of the received frame is set and the corresponding bit in the associated Data Mask register is also set **AND**

- The CRC field in the received frame (including a recessive CRC delimiter) was received without error.

The internal error counter will be incremented when an erroneous CAN frame (e.g., a stuffing error) is received prior to the ACK field. If a CAN frame is received without any errors preceding the ACK field, the counter will be decremented. Any data received after the CRC delimiter and before the next SOF will be ignored by the partial networking module. If the counter overflows (FEC > ERRCNT, see section EFCR), a frame detect error is captured (PNEFD = 1, see section TRXESR) and the device wakes up; the counter is reset to 0 when the bias is switched off.

After configuring the PN registers, the microcontroller must set the PNCFOK bit to '1'. The device will clear the PNCFOK bit after a write access to any of the CAN Partial Networking Configuration registers (see sections DRCR to CDMR0..7).

Any valid wake-up pattern (according to ISO 11898-2:2024) will trigger a wake-up event if selective wake-up is disabled (CPNE = 0), or partial networking is not configured correctly (PNCFOK = 0), and the CAN transceiver is in TXD Standby mode with wake-up enabled (CWUE = 1).

All wake-up patterns will be ignored if the CAN transceiver is in CAN Normal/Silent mode or CAN wake-up is disabled (CWUE = 0).

#### 5.3.3.2 CAN Selective Wake-up and CAN FD

CAN Flexible Data-Rate (CAN FD) is an improved CAN protocol with regard to bandwidth and payload. As specified in ISO 11898-1:2024, CAN FD is based on the CAN protocol and still uses the same arbitration method. However, after the arbitration phase, the data rate is increased and the data bits are transferred with a higher bit rate than in the arbitration phase. At the CRC delimiter, before the controllers transmit the Acknowledge bits, the bit rate is switched back to the same bit rate as used in the arbitration phase. Besides the increased bit speed, the new CAN FD allows data frames up to 64 bytes compared to the maximum of 8 bytes with classical CAN.

The ATA6574 can be configured to recognize CAN FD frames as valid frames. When CFDPE = 1, the error counter is decremented every time the control field of a CAN FD frame is received. The device remains in Sleep mode with partial networking enabled. CAN FD frames are never recognized as valid wake-up frames, even if PNDM = 0 and the frame contains a valid ID. After receiving the control field of a CAN FD frame, the device ignores further bus signals until Idle is detected again.

When CFDPE is set to '0', CAN FD frames are interpreted as frames with errors by the partial networking module. Therefore, the error counter is incremented when a CAN FD frame is received. The PNEFD bit is set to '1' and the device wakes up if the error counter overflows.

#### 5.3.4 Wake-up via SPI

In case of an SPI command while the system is in a low-power mode, but with the SPI interface enabled, the device will be woken up and will enter the operating mode issued together with the SPI command. An SPI command failure, such as an invalid length of an SPI command or write access to a read-only register, etc., will also trigger an interrupt event on the device (see Wake-Up Events).

### 5.3.5 Related Registers for Configuring the CAN Partial Networking

#### 5.3.5.1 Data Rate Configuration Register (Address 0x26)

Name: DRCR Offset: 0x26 Reset: 0x05

Property:

| Bit    | 7             | 6 | 5 | 4 | 3 | 2   | 1       | 0   |  |

|--------|---------------|---|---|---|---|-----|---------|-----|--|

|        | Reserved[4:0] |   |   |   |   |     | DR[2:0] |     |  |

| Access | R             | R | R | R | R | R/W | R/W     | R/W |  |

| Reset  | 0             | 0 | 0 | 0 | 0 | 1   | 0       | 1   |  |

Bits 7:3 - Reserved[4:0] Reserved for future use

Bits 2:0 - DR[2:0] Select CAN Data-Rate

| DR[2:0] | CAN Data Rate (Kbit/s)                                           |

|---------|------------------------------------------------------------------|

| 3'b000  | 50                                                               |

| 3'b001  | 100                                                              |

| 3'b010  | 125                                                              |

| 3'b011  | 250                                                              |

| 3'b100  | Reserved (intended for future use; currently selects 500 Kbit/s) |

| 3'b101  | 500                                                              |

| 3'b110  | Reserved (intended for future use; currently selects 500 Kbit/s) |

| 3'b111  | 1000                                                             |

#### 5.3.5.2 CAN ID Register 0 (Address 0x27)

Name: CIDR0 Offset: 0x27 Reset: 0x00

| Bit    | 7   | 6   | 5   | 4    | 3    | 2   | 1   | 0   |

|--------|-----|-----|-----|------|------|-----|-----|-----|

|        |     |     |     | ID0[ | 7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W  | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0    | 0   | 0   | 0   |

#### Bits 7:0 - ID0[7:0]

ID07 to ID00 Bits of the Extended Frame Format

#### 5.3.5.3 CAN ID Register 1 (Address 0x28)

Name: CIDR1 Offset: 0x28 Reset: 0x00

Property:

| Bit    | 7   | 6   | 5   | 4    | 3    | 2   | 1   | 0   |

|--------|-----|-----|-----|------|------|-----|-----|-----|

|        |     |     |     | ID1[ | 7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W  | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0    | 0   | 0   | 0   |

#### Bits 7:0 - ID1[7:0]

ID15 to ID08 Bits of the Extended Frame Format

#### 5.3.5.4 CAN ID Register 2 (Address 0x29)

Name: CIDR2 Offset: 0x29 Reset: 0x00

| Bit    | 7   | 6   | 5   | 4     | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-------|-----|-----|-----|-----|

|        |     |     | ID2 | [1:0] |     |     |     |     |

| Access | R/W | R/W | R/W | R/W   | R/W | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0     | 0   | 0   | 0   | 0   |

#### Bits 7:2 - ID2[7:2]

ID23 to ID18 Bits of the Extended Frame Format; ID05 to ID00 Bits of the Standard Frame Format

### Bits 1:0 - ID2[1:0]

ID17 to ID16 Bits of the Extended Frame Format

### 5.3.5.5 CAN ID Register 3 (Address 0x2A)

Name: CIDR3 Offset: 0x2A Reset: 0x00

Property:

| Bit    | 7             | 6 | 5 | 4        | 3   | 2   | 1   | 0   |  |

|--------|---------------|---|---|----------|-----|-----|-----|-----|--|

|        | Reserved[7:5] |   |   | ID3[4:0] |     |     |     |     |  |

| Access | R             | R | R | R/W      | R/W | R/W | R/W | R/W |  |

| Reset  | 0             | 0 | 0 | 0        | 0   | 0   | 0   | 0   |  |

Bits 7:5 - Reserved[7:5] Reserved for future use

#### Bits 4:0 - ID3[4:0]

ID28 to ID24 Bits of the Extended Frame Format, ID10 to ID06 Bits of the Standard Frame Format

#### 5.3.5.6 CAN ID Mask Register 0 (Address 0x2B)

Name: CIDMR0 Offset: 0x2B Reset: 0x00

| Bit    | 7         | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|--------|-----------|-----|-----|-----|-----|-----|-----|-----|--|

|        | IDM0[7:0] |     |     |     |     |     |     |     |  |

| Access | R/W       | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Reset  | 0         | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

#### Bits 7:0 - IDM0[7:0]

Mask Bits ID07 to ID00 of the Extended Frame Format. '1' means 'don't care'.

#### 5.3.5.7 CAN ID Mask Register 1 (Address 0x2C)

Name: CIDMR1 Offset: 0x2C Reset: 0x00

| Bit    | 7   | 6   | 5   | 4    | 3     | 2   | 1   | 0   |

|--------|-----|-----|-----|------|-------|-----|-----|-----|

|        |     |     |     | IDM1 | [7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W   | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0     | 0   | 0   | 0   |

#### Bits 7:0 - IDM1[7:0]

Mask Bits ID15 to ID08 of the Extended Frame Format. '1' means 'don't care'.

#### 5.3.5.8 CAN ID Mask Register 2 (Address 0x2D)

Name: CIDMR2 Offset: 0x2D Reset: 0x00

| Bit    | 7   | 6   | 5    | 4      | 3   | 2   | 1   | 0   |

|--------|-----|-----|------|--------|-----|-----|-----|-----|

|        |     |     | IDM2 | 2[1:0] |     |     |     |     |

| Access | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0    | 0      | 0   | 0   | 0   | 0   |

#### Bits 7:2 - IDM2[7:2]

Mask Bits ID23 to ID18 of the Extended Frame Format; ID05 to ID00 Bits of the Standard Frame Format. '1' means 'don't care'.

#### Bits 1:0 - IDM2[1:0]

Mask Bits ID17 to ID16 of the Extended Frame Format. '1' means 'don't care'.

#### 5.3.5.9 CAN ID Mask Register 3 (Address 0x2E)

Name: CIDMR3

Offset: 0x2E

Reset: 0x00

Property:

| Bit    | 7             | 6 | 5 | 4         | 3   | 2   | 1   | 0   |  |

|--------|---------------|---|---|-----------|-----|-----|-----|-----|--|

|        | Reserved[7:5] |   |   | IDM3[4:0] |     |     |     |     |  |

| Access | R             | R | R | R/W       | R/W | R/W | R/W | R/W |  |

| Reset  | 0             | 0 | 0 | 0         | 0   | 0   | 0   | 0   |  |

#### Bits 7:5 - Reserved[7:5] Reserved for future use

#### Bits 4:0 - IDM3[4:0]

Mask Bits ID28 to ID24 of the Extended Frame Format, ID10 to ID06 Bits of the Standard Frame Format. '1' means 'don't care'.

### 5.3.5.10 CAN Frame Configuration Register (Address 0x2F)

Name: CFCR Offset: 0x2F Reset: 0x40

Property:

| Bit    | 7   | 6    | 5       | 4       | 3   | 2   | 1     | 0   |

|--------|-----|------|---------|---------|-----|-----|-------|-----|

|        | IDE | PNDM | Reserve | ed[1:0] |     | DLC | [3:0] |     |

| Access | R/W | R/W  | R       | R       | R/W | R/W | R/W   | R/W |

| Reset  | 0   | 1    | 0       | 0       | 0   | 0   | 0     | 0   |

#### Bit 7 - IDE Identifier Format

The host microcontroller should set the bit to '1' if identifier is in extended frame format (29-bit), set to '0' if identifier is in standard frame format (11-bit).

#### Bit 6 – PNDM Partial Networking Data Mask

The host microcontroller should set the bit to '1' if Data Length Code and data field are evaluated at wake-up, set to '0' if Data Length Code and data field are 'don't care' at wake-up.

#### Bits 5:4 - Reserved[1:0] Reserved for future use

Bits 3:0 - DLC[3:0] Data Length Configuration Select number of data bytes expected in a CAN frame.

| DLC[3:0]           | Number of Data Bytes                                   |

|--------------------|--------------------------------------------------------|

| 4'b0000            | 0                                                      |

| 4'b0001            | 1                                                      |

| 4'b0010            | 2                                                      |

| 4'b0011            | 3                                                      |

| 4'b0100            | 4                                                      |

| 4'b0101            | 5                                                      |

| 4'b0110            | 6                                                      |

| 4'b0111            | 7                                                      |

| 4'b1000            | 8                                                      |

| 4'b1001 to 4'b1111 | Tolerated, 8 bytes expected; DM0 (Data Mask 0) ignored |

### 5.3.5.11 Error Frame Counter Threshold Register (Address 0x3A)

Name: EFCR Offset: 0x3A Reset: 0x1F

Property:

| Bit    | 7             | 6 | 5 | 4           | 3   | 2   | 1   | 0   |  |

|--------|---------------|---|---|-------------|-----|-----|-----|-----|--|

|        | Reserved[7:5] |   |   | EERCNT[4:0] |     |     |     |     |  |

| Access | R             | R | R | R/W         | R/W | R/W | R/W | R/W |  |

| Reset  | 0             | 0 | 0 | 1           | 1   | 1   | 1   | 1   |  |

Bits 7:5 - Reserved[7:5] Reserved for future use

#### Bits 4:0 - EERCNT[4:0]

Set the Error Frame Counter Overflow Threshold. If the counter overflows (counter > ERRCNT), a frame detect error is captured (PNEFD = 1) and the device wakes up.

#### 5.3.5.12 Failure Error Counter Register (Address 0x3B)

Name: FECR Offset: 0x3B Reset: 0x00 Property: Read-only

| Bit    | 7 | 6             | 5 | 4        | 3 | 2 | 1 | 0 |  |

|--------|---|---------------|---|----------|---|---|---|---|--|

|        |   | Reserved[7:5] |   | FEC[4:0] |   |   |   |   |  |

| Access | R | R             | R | R        | R | R | R | R |  |

| Reset  | 0 | 0             | 0 | 0        | 0 | 0 | 0 | 0 |  |

Bits 7:5 - Reserved[7:5] Reserved for future use

#### Bits 4:0 - FEC[4:0]

If the device receives a CAN frame containing errors (e.g., a stuffing error) that are received in advance of the ACK field, an internal error counter is incremented. If a CAN frame is received without any errors appearing in front of the ACK field, the counter is decremented. Data received after the CRC delimiter and before the next SOF is ignored by the partial networking module. If the counter overflows (FEC > ERRCNT, see section EFCR), a frame detect error is captured (PNEFD = 1, see section TRXESR) and the device wakes up; the counter is reset to zero when the bias is switched off and partial networking is re-enabled.

### 5.3.5.13 Glitch Filter Threshold Register (Address 0x67)

Name: GLFT Offset: 0x67 Reset: 0x02

| Bit    | 7 | 6 | 5             | 4        | 3 | 2   | 1   | 0   |

|--------|---|---|---------------|----------|---|-----|-----|-----|

|        |   |   | Reserved[4:0] | GLF[2:0] |   |     |     |     |

| Access | R | R | R             | R        | R | R/W | R/W | R/W |

| Reset  | 0 | 0 | 0             | 0        | 0 | 0   | 1   | 0   |

Bits 7:3 - Reserved[4:0] Reserved for future use

#### Bits 2:0 - GLF[2:0]

Set the glitch filter threshold from 5% to 55% of the arbitration bit rate.

| GLF[2:0] | #samples (≤ 500 Kbit/s) | #samples (1 Mbit/s) |

|----------|-------------------------|---------------------|

| 3'b000   | 1 [<2.42%/<5.17%]       | 1 [<4.83%/<10.35%]] |

| 3'b001   | 2 [<4.83%/<7.76%]       | 2 [<9.66%/<15.52%]  |

| 3'b010   | 3 [<7.25%/<10.35%]      | 3 [<14.49%/<20.7%]] |

| 3'b011   | 4 [<9.66%/<12.94%]      | 4 [<19.32%/<20.87%] |

| 3'b100   | 5 [<12.08%/<15.52%]     | 5 [<24.15%/<31.05%] |

| 3'b101   | 6 [<14.49%/<18.11%]     | 6 [<28.99%/<36.22%] |

| 3'b110   | 7 [<16.91%/<20.7%]      | 7 [<33.82%/<41.40%] |

| 3'b111   | 24 [<57.97%/<64.69%]    | 13 [<62.8%/<72.45%] |

Assumption: clock tolerance ±3%; transmitter ±0.5% tolerance.

### 5.3.5.14 CAN Data Mask Registers 0...7 (Address 0x68...0x6F)

Name: CDMR0..7 Offset: 0x68...0x6F Reset: 0xFF

Bit 7 6 5 3 2 0 1 DM0...7[7:0] Access R/W R/W R/W R/W R/W R/W R/W R/W Reset 1 1 1 1 1

### Bits 7:0 - DM0...7[7:0] data mask 0...7 configuration

Table 5-2. Data Mask and the CAN Data Filed

| Туре      | DLC     |     |        |        |        |        |        |        |        |        |     |

|-----------|---------|-----|--------|--------|--------|--------|--------|--------|--------|--------|-----|

| CAN Frame | DLC > 8 | DLC | Byte 0 | Byte 1 | Byte 2 | Byte 3 | Byte 4 | Byte 5 | Byte 6 | Byte 7 | CRC |

| Data Mask | _       | DLC | 00     | DM1    | DM2    | DM3    | DM4    | DM5    | DM6    | DM7    | CRC |

| CAN Frame | DLC = 8 | DLC | Byte 0 | Byte 1 | Byte 2 | Byte 3 | Byte 4 | Byte 5 | Byte 6 | Byte 7 | CRC |

| Data Mask | _       | DLC | DM0    | DM1    | DM2    | DM3    | DM4    | DM5    | DM6    | DM7    | CRC |

| CAN Frame | DLC = 7 | _   | DLC    | Byte 0 | Byte 1 | Byte 2 | Byte 3 | Byte 4 | Byte 5 | Byte 6 | CRC |

| Data Mask | _       |     | DLC    | DM1    | DM2    | DM3    | DM4    | DM5    | DM6    | DM7    | CRC |

| CAN Frame | DLC = 6 | _   |        | DLC    | Byte 0 | Byte 1 | Byte 2 | Byte 3 | Byte 4 | Byte 5 | CRC |

| Data Mask | _       |     |        | DLC    | DM2    | DM3    | DM4    | DM5    | DM6    | DM7    | CRC |

| CAN Frame | DLC = 5 | _   |        | _      | DLC    | Byte 0 | Byte 1 | Byte 2 | Byte 3 | Byte 4 | CRC |

| Data Mask |         | _   |        | _      | DLC    | DM3    | DM4    | DM5    | DM6    | DM7    | CRC |

| continued |         |   |   |   |   |     |        |        |        |        |     |

|-----------|---------|---|---|---|---|-----|--------|--------|--------|--------|-----|

| Туре      | DLC     |   |   |   |   |     |        |        |        |        |     |

| CAN Frame | DLC = 4 | _ | _ | _ | _ | DLC | Byte 0 | Byte 1 | Byte 2 | Byte 3 | CRC |

| Data Mask | _       |   |   |   | _ | DLC | DM4    | DM5    | DM6    | DM7    | CRC |

| CAN Frame | DLC = 3 |   |   | _ | _ | _   | DLC    | Byte 0 | Byte 1 | Byte 2 | CRC |

| Data Mask | _       |   |   |   | _ | _   | DLC    | DM5    | DM6    | DM7    | CRC |

| CAN Frame | DLC = 2 |   |   | _ | _ | _   |        | DLC    | Byte 0 | Byte 1 | CRC |

| Data Mask | _       |   |   |   | _ | _   |        | DLC    | DM6    | DM7    | CRC |

| CAN Frame | DLC = 1 |   |   | _ | _ | _   |        | _      | DLC    | Byte 0 | CRC |

| Data Mask | _       |   |   |   | _ | _   |        |        | DLC    | DM7    | CRC |

### 5.3.5.15 Bus Failure Event Capture Enable Register (Address 0x32)

Name: BFECR Offset: 0x32 Reset: 0x00

| Bit    | 7 | 6 | 5     | 4    | 3 | 2 | 1   | 0   |

|--------|---|---|-------|------|---|---|-----|-----|

|        |   |   | BOUTE | BSCE |   |   |     |     |

| Access | R | R | R     | R    | R | R | R/W | R/W |

| Reset  | 0 | 0 | 0     | 0    | 0 | 0 | 0   | 0   |

#### Bits 7:2 - Reserved[7:2] Reserved for future use

### **Bit 1 – BOUTE** Bus Dominant Time-out Event Capture Enable

The BOUTE bit must be set to '1' to enable the bus dominant time-out detection. Setting the bit to '0' disables the bus dominant time-out detection.

#### Bit 0 - BSCE Bus Short-Circuit Event Capture Enable

The BSCE bit must be set to '1' to enable the bus short-circuit event detection. Setting the bit to '0' disables the bus short-circuit event detection.

#### 5.3.5.16 Pin WAKE Status Register (Address 0x4B)

Name: PWKS

Offset: 0x4B

Reset: 0x00

Property: Read-only

| Bit    | 7 | 6 | 5     | 4        | 3 | 2 | 1 | 0 |

|--------|---|---|-------|----------|---|---|---|---|

|        |   |   | PWKVS | Reserved |   |   |   |   |

| Access | R | R | R     | R        | R | R | R | R |

| Reset  | 0 | 0 | 0     | 0        | 0 | 0 | 0 | 0 |

### Bits 7:2 - Reserved[7:2] Reserved for future use

#### Bit 1 – PWKVS Pin WAKE Voltage Status

The device sets the bit to '1' if WAKE is high, to '0' if WAKE is low. PWKVS is always '0' in Power-Down mode if local wake-up is disabled.

#### Bit 0 - Reserved Reserved for future use

### 5.3.5.17 Global Event Status Register (Address 0x60)

Name: GESR Offset: 0x60 Reset: 0x01 Property: Read-only

| Bit    | 7    | 6        | 5    | 4        | 3    | 2     | 1        | 0     |

|--------|------|----------|------|----------|------|-------|----------|-------|

|        | OSCS | Reserved | BFES | Reserved | WKES | TRXES | Reserved | SYSES |

| Access | R    | R        | R    | R        | R    | R     | R        | R     |

| Reset  | 0    | 0        | 0    | 0        | 0    | 0     | 0        | 1     |

#### Bit 7 – OSCS System Oscillator Status

The device sets the bit to '1' if a hardware failure of the system oscillator is detected and sets the bit to '0' when the system oscillator is disabled for power-saving purposes, the hardware failure is resolved, or the oscillator is enabled (for instance, in device Normal mode) and no hardware failure is present.

#### Bit 6 - Reserved Reserved for future use

#### Bit 5 - BFES Bus Failure Event Status

The device sets the bit to '1' if there is a bus failure event pending (any bit in the BFESR register is '1'). The bit reads '0' if all status bits in the BFESR register are cleared.

#### Bit 4 - Reserved Reserved for future use

#### Bit 3 - WKES WAKE Event Status

The device sets the bit to '1' if there is a WAKE pin event pending (any bit in the WKESR register is '1'). The bit reads '0' if all status bits in the WKESR register are cleared.

#### Bit 2 – TRXES Transceiver Event Status

The device sets the bit to '1' if there is a transceiver event pending (any bit in the TRXESR register is '1'). The bit reads '0' if all status bits in the TRXESR register are cleared.

#### Bit 1 - Reserved Reserved for future use

#### Bit 0 – SYSES SYSES System Event Status

The device sets the bit to '1' if there is a system event pending (any bit in the SESR register is '1'). The bit reads '0' if all status bits in the SESR register are cleared.

#### 5.3.5.18 System Event Status Register (Address 0x61)

Name: SESR Offset: 0x61 Reset: 0x10

Property:

| Bit    | 7 | 6             | 5 | 4      | 3        | 2    | 1     | 0        |  |

|--------|---|---------------|---|--------|----------|------|-------|----------|--|

|        |   | Reserved[2:0] |   | PWRONS | Reserved | OTPW | SPIFS | Reserved |  |

| Access | R | R             | R | R/W    | R        | R/W  | R/W   | R        |  |

| Reset  | 0 | 0             | 0 | 1      | 0        | 0    | 0     | 0        |  |

Bits 7:5 - Reserved[2:0] Reserved for future use

#### Bit 4 – PWRONS Power-on Status

The device sets the bit to '1' if the device has left Power-Off mode after power on. The bit can be reset to '0' by writing a '1' to the bit. PWRONS is also cleared when the device is forced into Sleep mode due to an undervoltage event. The information stored in PWRONS could be lost in this case. The NMTS bit in the Device Mode Status Register (DMSR) can be used in this case. The NMTS bit is set to '0' when the device switches to Normal mode after power on.

#### Bit 3 – Reserved Reserved for future use

#### Bit 2 - OTPW Overtemperature Prewarning Status

The device sets the bit to '1' if the event is enabled in the SECR register and the chip temperature has exceeded the overtemperature prewarning threshold. The bit can be reset to '0' by writing a '1' to the bit. OTPW is also cleared when the device is forced into Sleep mode due to an undervoltage event.

#### Bit 1 - SPIFS SPI Failure Status

The device sets the bit to '1' if the event is enabled in the SECR register and an SPI failure is detected. The bit can be reset to '0' by writing a '1' to the bit. SPIFS is also cleared when the device is forced into Sleep mode due to an undervoltage event.

#### Bit 0 - Reserved Reserved for future use

#### 5.3.5.19 Transceiver Event Status Register (Address 0x63)

Name: TRXESR Offset: 0x63 Reset: 0x00

| Bit    | 7             | 6 | 5     | 4   | 3       | 2       | 1    | 0    |

|--------|---------------|---|-------|-----|---------|---------|------|------|

|        | Reserved[7:6] |   | PNEFD | BS  | Reserve | ed[3:2] | TRXF | CWUS |

| Access | R             | R | R/W   | R/W | R       | R       | R/W  | R/W  |

| Reset  | 0             | 0 | 0     | 0   | 0       | 0       | 0    | 0    |

#### Bits 7:6 - Reserved[7:6] For future use

#### Bit 5 – PNEFD Partial Networking Frame Detection Status

The device sets the bit to '1' if a partial networking frame detection error is detected (error counter overflow). The bit can be reset to '0' by writing a '1' to the bit. PNEFD is also cleared when the device is forced into Sleep mode due to an undervoltage event.

#### Bit 4 - BS Bus Status

The device sets the bit to '1' if the event is enabled in the TRXECR register and no activity on the CAN bus is detected for  $t_{Silence}$ . The bit can be reset to '0' by writing a '1' to the bit. BS is also cleared when the device is forced into Sleep mode due to an undervoltage event.

#### Bits 3:2 - Reserved[3:2] For future use

#### Bit 1 – TRXF Transceiver Failure Status

The device sets the bit to '1' if the event is enabled in the TRXECR register and a CAN failure event is detected. The bit can be reset to '0' by writing a '1' to the bit. TRXF is also cleared when the device is forced into Sleep mode due to an undervoltage event. TRXF is triggered if:

TXD is clamped dominant and system is in TRX Normal mode.

- A VCC undervoltage is detected, COPM = 01 and system is in TRX Normal or TRX Reduced Normal mode.

- An RXD recessive clamping error is detected and system is in TRX Normal or TRX Silent mode. The RXD recessive clamping error detection must be individually enabled in the TRXECR2 register.

#### Bit 0 - CWUS CAN Wake-up Status

The device sets the bit to '1' if the event is enabled in the TRXECR register and a CAN wake-up event is detected. The bit can be reset to '0' by writing a '1' to the bit. CWUS is also cleared when the device is forced into Sleep mode due to an undervoltage event.

#### 5.3.5.20 WAKE Event Status Register (Address 0x64)

Name: WKESR Offset: 0x64 Reset: 0x00

| Bit    | 7 | 6     | 5     | 4 | 3 | 2 | 1   | 0   |

|--------|---|-------|-------|---|---|---|-----|-----|

|        |   | LWURS | LWUFS |   |   |   |     |     |

| Access | R | R     | R     | R | R | R | R/W | R/W |

| Reset  | 0 | 0     | 0     | 0 | 0 | 0 | 0   | 0   |

#### Bits 7:2 - Reserved[7:2] Reserved for future use

#### Bit 1 - LWURS Local Wake-up Rising Edge Status

The device sets the bit to '1' if the event detection is enabled in the WKECR register and a rising edge on the WAKE pin is detected. The bit can be reset to '0' by writing a '1' to the bit. LWURS is also cleared when the device is forced into Sleep mode due to an undervoltage event.

#### Bit 0 - LWUFS Local Wake-up Falling Edge Status

The device sets the bit to '1' if the event detection is enabled in the WKECR register and a falling edge on the WAKE pin is detected. The bit can be reset to '0' by writing a '1' to the bit. LWUFS is also cleared when the device is forced into Sleep mode due to an undervoltage event.

#### 5.3.5.21 Bus Failure Event Indication Status Register (Address 0x65)

Name: BFESR Offset: 0x65 Reset: 0x00

Property:

| Bit    | 7 | 6     | 5    | 4 | 3 | 2 | 1   | 0   |

|--------|---|-------|------|---|---|---|-----|-----|

|        |   | BOUTS | BSCS |   |   |   |     |     |