Dual Channel Differential Isolated Gate Driver HM3 CPM3 SiC Half-Bridge Module Companion Tool

## **Technical Features**

- Optimized for use with Wolfspeed's High-Performance HM3 Half Bridge Power Modules

- High-Frequency, Ultra-Fast Switching Operation

- On-Board 3 W Isolated Power Supplies

- Primary OVLO and UVLO with Hysteresis

- On-Board Overcurrent, Shoot-Through, and Reverse Polarity Protection

- Differential Inputs for Increased Noise Immunity

- Very Low Isolation Capacitance

- Single-Ended to Differential Daughter Board Available Upon Request (CGD12HB00D)

| V <sub>Drive</sub>     | +15/-4 V |

|------------------------|----------|

| l <sub>G</sub>         | ±14 A    |

| R <sub>g,ext-on</sub>  | 5 Ω      |

| R <sub>G,EXT-OFF</sub> | 2.5 Ω    |

| <b>™</b> G,EXT-OFF     | 2.5 11   |

## **Applications**

• DC Bus Voltages up to 1500 V

## **Maximum Ratings**

| Parameter                                                                              | Symbol             | Value       | Unit |  |  |

|----------------------------------------------------------------------------------------|--------------------|-------------|------|--|--|

| Supply Voltage                                                                         | V <sub>DC</sub>    | -0.5 to 18  |      |  |  |

| Logic Level Inputs                                                                     | V                  | -0.5 to 5.5 |      |  |  |

| Output Peak Current (T <sub>A</sub> = 25°C)                                            | I <sub>o</sub>     | ±14         | А    |  |  |

| Output Power per Channel (T <sub>A</sub> = 25°C)                                       | P <sub>Drive</sub> | 3           | W    |  |  |

| Maximum Switching Frequency (Module & MOSFET<br>Dependent, see Power Estimate Section) | fs                 | 94          | kHz  |  |  |

| Ambient Operating Temperature                                                          | T <sub>op</sub>    | -35 to 85   | °C   |  |  |

| Storage Temperature                                                                    | T <sub>stg</sub>   | -50 to 125  | °C   |  |  |

Rev. 1, January 2024

nloaded fro

# **Gate Driver Electrical Characterization**

| Parameter                                             | Symbol                   | Min. | Тур. | Max. | Unit  | Test Conditions                              |  |

|-------------------------------------------------------|--------------------------|------|------|------|-------|----------------------------------------------|--|

| Supply Voltage                                        | V <sub>DC</sub>          | 9    | 12   | 18   |       |                                              |  |

| Under Voltage Lockout                                 |                          | 13.8 | 14   | 14.3 |       | Turn On, Voltage Going High                  |  |

| UVLO Hysteresis                                       | - V <sub>UVLO</sub>      |      | 1.2  |      | l v   |                                              |  |

| High Level Logic Input Voltage                        | V <sub>IH</sub>          | 3.5  |      | 5.5  |       | Single-Ended Inputs                          |  |

| Low Level Logic Input Voltage                         | VIL                      | 0    |      | 1.5  |       |                                              |  |

| Differential Input Common Mode Range                  | VIDCM                    | -7   |      | +12  |       | Differential Inputs                          |  |

| Differential Input Threshold Voltage                  | V <sub>IDTH</sub>        | -200 | -125 | -50  | mV    | $V_{ID} = V_{Pos-Line} - V_{Neg-Line}$       |  |

| Differential Output Magnitude                         | V <sub>od</sub>          | 2    | 3.1  |      |       | R <sub>L</sub> =100 Ω                        |  |

| High Level Output Voltage                             | V <sub>GATE,HIGH</sub>   |      | +15  |      |       |                                              |  |

| Low Level Output Voltage                              | V <sub>GATE,LOW</sub>    |      | -4   |      | V     |                                              |  |

| Working Isolation Voltage                             | V <sub>IOWM</sub>        |      | 1500 |      |       | V <sub>RMS</sub>                             |  |

| Isolation Capacitance                                 | C <sub>ISO</sub>         |      | 17   |      | pF    | Per Channel                                  |  |

| Common Mode Transient Immunity                        | СМТІ                     | 100  |      |      | kV/μs | V <sub>CM</sub> = 1000 V                     |  |

| Output Resistance <sup>1</sup>                        | R <sub>GIC-ON</sub>      |      | 0.4  | 0.8  |       | Gate Drive Buffer                            |  |

| Output Resistance <sup>1</sup>                        | R <sub>GIC-OFF</sub>     |      | 0.3  | 0.6  |       | Tested at 1 A                                |  |

| External Turn-on Resistance <sup>2</sup>              | R <sub>G(ext)(on)</sub>  |      | 5.0  |      | Ω     | External SMD Resistor                        |  |

| External Turn-off Resistance <sup>2</sup>             | R <sub>G(ext)(off)</sub> |      | 2.5  |      |       | 2512 (6432 Metric)                           |  |

| Turn-Off Diode Forward Voltage                        | D <sub>VF-OFF</sub>      | 0.62 | 0.67 | 0.82 | V     |                                              |  |

| Output Rise Time                                      | t <sub>on</sub>          |      | 906  |      |       | $R_{G(ext)} = 1 \Omega$                      |  |

| Output Fall Time                                      | t <sub>off</sub>         |      | 527  |      | -     | C <sub>Load</sub> = 47 nF<br>From 10% to 90% |  |

| Propagation Delay (Turn Off)                          |                          |      | 95   |      | ns    | $R_{G(ext)} = 1 \Omega$                      |  |

| Propagation Delay (Turn On)                           | - t <sub>PHL</sub>       |      | 83   |      |       | C <sub>Load</sub> = 0 nF<br>From 50% to 50%  |  |

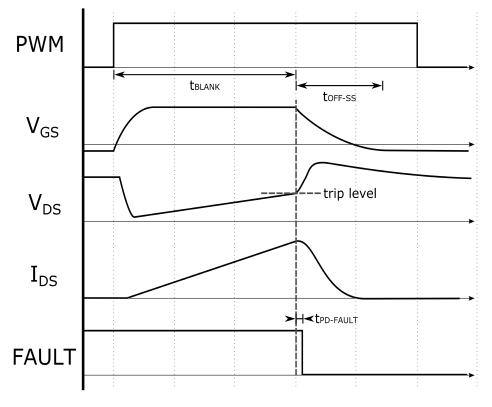

| Over-current Propagation Delay to FAULT<br>Signal Low | t <sub>PD-FAULT</sub>    |      | 40   |      | -     | Does Not Include Blanking                    |  |

| Soft-Shutdown Resistance <sup>3</sup>                 | R <sub>ss</sub>          |      | 5    |      | Ω     | Tested at 250 mA                             |  |

Notes:

<sup>1</sup>Output resistance of gate driver IC.

<sup>2</sup>Additional output resistance is added with SMD resistors. Separate resistors for turn-on and turn-off allowing tunable dynamic performance.

<sup>3</sup> Soft-Shutdown network will safely turn off the gate in the event an over-current is detected.

# **Input Connector Information**

| Pin Number | Parameter       | Description                                                                                                                                                                                                                              |  |  |  |

|------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1          | V <sub>DC</sub> | Power supply input pin (+12 V Nominal Input)                                                                                                                                                                                             |  |  |  |

| 2          | Common          | Common                                                                                                                                                                                                                                   |  |  |  |

| 3          | HS-P (*)        | ositive line of 5 V differential high-side PWM signal pair. Terminated Into 250 $\Omega$                                                                                                                                                 |  |  |  |

| 4          | HS-N (*)        | legative line of 5 V differential high-side PWM signal pair. Terminated into 250 $\Omega$                                                                                                                                                |  |  |  |

| 5          | LS-P (*)        | Positive line of 5 V differential low-side PWM signal pair. Terminated into 250 $\Omega$                                                                                                                                                 |  |  |  |

| 6          | LS-N (*)        | Negative line of 5 V differential low-side PWM signal pair. Terminated into 250 $\Omega$                                                                                                                                                 |  |  |  |

| 7          | FAULT- P(*)     | Positive line of 5 V differential fault condition signal pair<br>Drive strength 20 mA. A low state on FAULT indicates when a desaturation fault has occurred.<br>The presence of a fault precludes the gate drive output from going high |  |  |  |

| 8          | FAULT- N (*)    | Negative line of 5 V differential fault condition signal pair. Drive strength 20 mA                                                                                                                                                      |  |  |  |

| 9          | NTC-P (*)       | Positive line of 5 V temperature dependent resistor output<br>signal pair. Drive strength 20 mA. Temperature measurement is<br>encoded via PWM.                                                                                          |  |  |  |

| 10         | NTC-N (*)       | Negative line of 5 V temperature dependent resistor output<br>signal pair. Drive strength 20mA. Temperature measurement is<br>encoded via PWM.                                                                                           |  |  |  |

| 11         | PS-Dis          | Pull Down to Disable Power Supply. Pull up, or leave floating to enable. Gate and source are connected with 10 $k\Omega$ when disabled                                                                                                   |  |  |  |

| 12         | Common          | Common                                                                                                                                                                                                                                   |  |  |  |

| 13         | PWM-EN          | Pull down to disable PWM input logic. Pull up or leave floating to enable. Gate driver output will be held low through turn-off gate resistor if power supplies are enabled                                                              |  |  |  |

| 14         | Common          | Common                                                                                                                                                                                                                                   |  |  |  |

| 15         | Reset           | Pull down to clear over-current fault condition or disable overcurrent protection. Pull up (+5 V) or leave floating to enable.                                                                                                           |  |  |  |

| 16         | Common          | Common                                                                                                                                                                                                                                   |  |  |  |

Note:

(\*) Inputs 3 – 10 are differential pairs.

Rev. 1, January 2024

# **Signal Description**

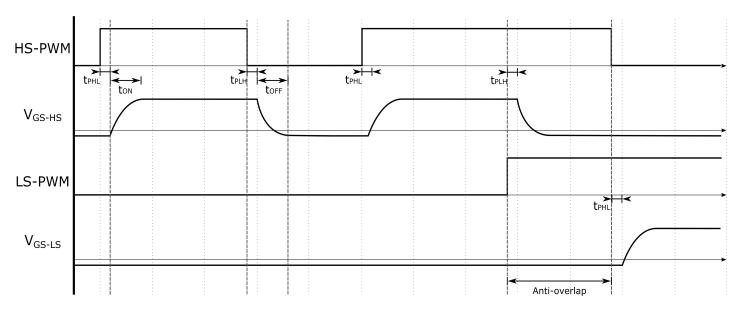

**PWM Signals:** High-side and low-side PWM are RS-422 compatible differential inputs. The termination impedance of the differential receiver is 120  $\Omega$ . Overlap protection is provided to prevent both the high-side and low-side gates from turning on simultaneously. The overlap protection should not be used as a dead time generator.

**Fault Signal:** The fault signal is a RS-422 compatible differential output with a maximum drive strength of 20mA. A high signal (positive line > negative line) means there are no fault conditions for either gate driver channel. This signal will be low if an over-current fault or UVLO fault condition is detected on either channel. A red LED will indicate a fault condition. The LED, DT3, indicates a high-side fault and DT6 indicates a low-side fault.

**UVLO Fault:** The UVLO circuit detects when the output rails of the isolated DC/DC converter fall below safe operating conditions for the gate driver. A UVLO fault indicates that the potential between the split output rails has fallen below the UVLO active level. The gate for the channel where the fault occurred will be pulled low through R<sub>G</sub> for the duration of the fault regardless of the PWM input signal. The fault will automatically clear once the potential has risen above the UVLO inactive level. There is hysteresis for this fault to ensure safe operating conditions. The UVLO faults for both channels are combined along with the over-current fault in the FAULT output signal. When there is no UVLO fault present, a green LED indicates a power good state. The LED, DT2, indicates a high-side power good status and DT5 indicates a low-side power good status.

**Over-Current Fault:** An over-current fault is an indication of an over-current event in the SiC power module. The over-current protection circuit measures the drain-source voltage, and the fault will indicate if this voltage has risen above a level corresponding to the safe current limit. When a fault has occurred the corresponding gate driver channel will be disabled, and the gate will be pulled down through a soft-shutdown resistor, R<sub>ss</sub>. The drain-source limit can be configured through on-board resistors. The over-current fault is latched upon detection and must be cleared by the user with a high pulse of at least 500 ns on the RESET signal.

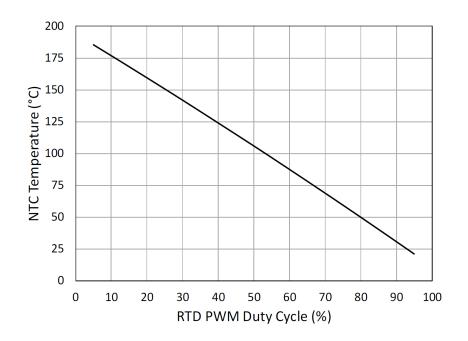

**NTC:** The NTC output is a differential signal that returns the resistance of the NTC temperature sensor integrated into HM3 modules. The signal is a 50 kHz PWM signal that encodes the resistance of the temperature sensor. The approximate temperature of the module can be determined from this resistance. See the section NTC Temperature Feedback for further details.

**PS-DIS:** The PS-DIS signal disables the output of the isolated DC/DC converters for the two channels. It is a singleended input that must be pulled low to turn off the power supplies. With the power supplies disabled the gate will be held low with a 10 k $\Omega$  resistor. This signal can be used for startup sequencing.

**PWM-EN:** This is a single-ended input that enables the PWM inputs for both channels. When this signal is pulled down the differential receivers for both channels are disabled and the gates will both be pulled low through  $R_{G(ext)(off)}$ . All protection circuitry and power supplies will continue to operate including FAULT and RTD outputs.

**Over-Voltage and Reverse Polarity Protection:** Power input on pin 1 of gate driver connector features a power management IC to protect the gate driver from damage by connecting a power source that exceeds the voltage rating of the gate driver or if the current limit is exceeded. There is also a diode and MOSFET in-line with the power input to protect against connecting a power source with positive and negative polarity reversed.

Rev. 1, January 2024

wnloaded from Arrow com

# **Truth Table**

| PWM | PWM-EN | PS-DIS | RESET | Overcurrent/<br>UVLO | FAULT | Output |

|-----|--------|--------|-------|----------------------|-------|--------|

| н   | H or Z | H or Z | L     | No                   | н     | Н      |

| L   | H or Z | H or Z | L     | No                   | Н     | L      |

| х   | L      | H or Z | L     | No                   | Н     | L      |

| х   | х      | L      | х     | No                   | L     | Z      |

| х   | H or Z | H or Z | L     | Yes                  | L     | L      |

| Х   | H or Z | H or Z | Н     | No                   | Н     | L      |

H = High | L = Low | X = Irrelevant | Z = High Impedance

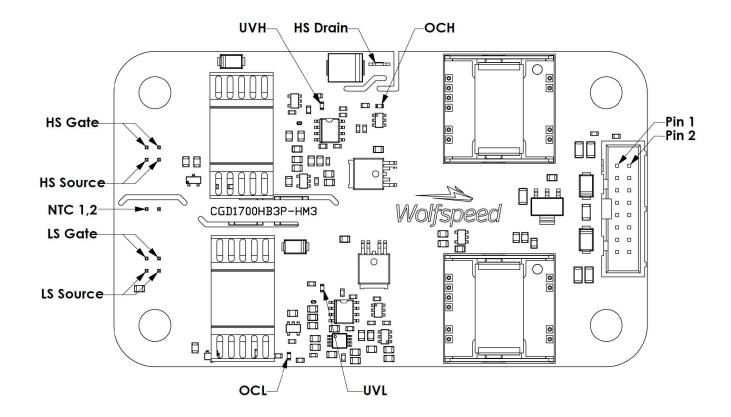

## **Gate Driver Interface**

Rev. 1, January 2024

rrow com

Downloaded from

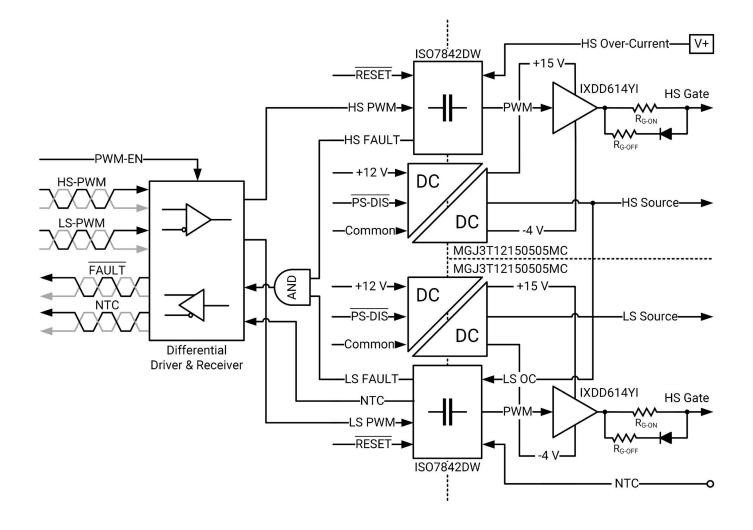

# **Function Block Diagram**

Rev. 1, January 2024

4600 Silicon Drive | Durham, NC 27703 | Tel: +1.919.313.5300 | wolfspeed.com/power

# **NTC Temperature Feedback**

The resistance measurement of the HM3 power module's NTC is available on the input connector of the gate driver as a differential pair on pins 9 and 10. The NTC resistance is converted to a pulse-width modulated (PWM) 50 kHz square wave. The temperature to duty cycle relationship is displayed in the figure below. The NTC measurement circuit is referenced to low-side gate drive channel, with the low-side digital isolator used to transmit the duty cycle-encoded signal back to the primary side of the driver. For this reason, the NTC signal does not need any additional isolation, and can be included in the same ribbon cable as the rest of the gate driver's signals. The temperature reported by the NTC differs largely from the junction temperature of the SiC MOSFETs and should not be used as an accurate junction temperature measurement.

Rev. 1, January <u>2024</u>

Downloaded from Arrow.com

4600 Silicon Drive | Durham, NC 27703 | Tel: +1.919.313.5300 | wolfspeed.com/power

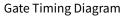

# **Timing Information**

Rev. 1, January 2024

## **Input Connector Information**

• 16 Positions Header, 0.100" (2.54mm) Pitch, Through Hole, Gold (SBH11-PBPC-D08-ST-BK)

## **Suggested Mating Parts**

- 16 Position Rectangular Header, IDC, Gold, 28 AWG (SFH210-PPPC-D08-ID-BK)

- 16 Position Header, 0.100" (2.54mm) Pitch, Through Hole, Gold (SFH11-PBPC-D08-RA-BK)

- 16 Position Header, 0.100" (2.54mm) Pitch, Through Hole, Right Angle, Gold (SFH11-PBPC-D08-RA-BK)

## **Output Connector Information**

• Quick Connect Female Connector, 0.110" (2.79mm), Non-Insulated (Keystone® 3534)

## **Power Estimates**

The gate driver power required is calculated using the formula below. The gate charge is dependent on the datasheets of the module being driven. Once the required gate driver power is calculated, the required input power can be calculated from the efficiency curves on the power supplies datasheet. This calculation is for one channel of the gate driver.

$$\boldsymbol{P}_{sw} = \boldsymbol{Q}_{G} * \boldsymbol{F}_{SW} * \boldsymbol{\Delta} \boldsymbol{V}_{PS}$$

P<sub>sw</sub>: gate driver power (per channel)

Q<sub>G</sub>: total gate charge (MOSFET gate charge × number of MOSFETs per switch position)

F<sub>sw</sub>: switching frequency

$\Delta V_{PS}$ : difference in isolated power supply voltage rails ( $V_{PS,HIGH} - V_{PS,LOW}$ )

Example:

Calculate the maximum switching frequency for CAS480M12HM3.

P<sub>sw</sub> 3 W (rated output power of isolated power supply on gate driver)

Q<sub>G</sub> 1589 nC (provided in CAS480M12HM3 datasheet)

V<sub>PS,HIGH</sub> 15 V (isolated power supply's positive output voltage)

V<sub>PS,LOW</sub> -5 V (isolated power supply's negative output voltage)

$\Delta V_{PS}$  20 V

## $3 W = 1589 nC * F_{SW-Max} * 20 V$

$F_{\text{SW-Max}}\approx 94$  kHz with margin

## **Supporting Links & Tools**

- CGD12HB00D: Differential Transceiver Board for CGD1200HB2P-BM3

- KIT-CRD-CIL12N-BM: Dynamic Performance Evaluation Board for 62mm Modules (CPWR-AN36)

- CPWR-AN34: Module Mounting Application Note

- CPWR-AN35: Thermal Interface Material Application Note

Rev. 1, January 2024

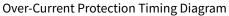

## Dimension

Rev. 1, January 2024

4600 Silicon Drive | Durham, NC 27703 | Tel: +1.919.313.5300 | wolfspeed.com/power

# **Important Notes**

This Wolfspeed-designed gate driver hardware for Wolfspeed components is meant to be used as an evaluation tool in a lab setting and to be handled and operated by highly qualified technicians or engineers. The hardware is not designed to meet any particular safety standards and the tool is not a production qualified assembly.

Each part that is used in this gate driver and is manufactured by an entity other than Wolfspeed or one of Wolfspeed's affiliates is provided "as is" without warranty of any kind, including but not limited to any warranty of non-infringement, merchantability, or fitness for a particular purpose, whether express or implied. There is no representation that the operation of each such part will be uninterrupted or error free.

This product has not been designed or tested for use in, and is not intended for use in, applications implanted into the human body nor in applications in which failure of the product could lead to death, personal injury or property damage, including but not limited to equipment used in the operation of nuclear facilities, life-support machines, cardiac defibrillators or similar emergency medical equipment, aircraft navigation or communication or control systems, or air traffic control systems.

The SiC MOSFET module switches at speeds beyond what is customarily associated with IGBT-based modules. Therefore, special precautions are required to realize optimal performance. The interconnection between the gate driver and module housing needs to be as short as possible. This will afford optimal switching time and avoid the potential for device oscillation. Also, great care is required to insure minimum inductance between the module and DC link capacitors to avoid excessive VDS overshoot.

© 2024 Wolfspeed, Inc. All rights reserved. Wolfspeed® and the Wolfstreak logo are registered trademarks and the Wolfspeed logo is a trademark of Wolfspeed, Inc.

#### **Contact info:**

4600 Silicon Drive Durham, NC 27703 USA Tel: +1.919.313.5300 www.wolfspeed.com/power

Rev. 1, January 2024

wnloaded from Arrow com

The information in this document is subject to change without notice.