# Sil3114 PCI to Serial ATA Controller

**Data Sheet**

Document # SiI-DS-0103-D

February 2007

### **Copyright Notice**

Copyright © 2007 Silicon Image, Inc. All rights reserved. These materials contain proprietary and confidential information (including trade secrets, copyright and other interests) of Silicon Image, Inc. You may not use these materials except only for your bona fide non-commercial evaluation of your potential purchase of products and/services from Silicon Image or its affiliates, and/or only in connection with your purchase of products and/or services from Silicon Image or its affiliates, and only in accordance with the terms and conditions herein. You have no right to copy, modify, transfer, sublicense, publicly display, create derivative works of or distribute these materials, or otherwise make these materials available, in whole or in part, to any third party.

### **Trademark Acknowledgment**

Silicon Image<sup>™</sup>, VastLane<sup>™</sup>, SteelVine<sup>™</sup>, PinnaClear<sup>™</sup>, Simplay<sup>™</sup>, Simplay HD<sup>™</sup>, Satalink<sup>™</sup>, and TMDS<sup>™</sup> are trademarks or registered trademarks of Silicon Image, Inc. in the United States and other countries. HDMI<sup>™</sup>, the HDMI logo and High-Definition Multimedia Interface<sup>™</sup> are trademarks or registered trademarks of, and are used under license from, HDMI Licensing, LLC.

#### **Further Information**

To request other materials, documentation, and information, contact your local Silicon Image, Inc. sales office or visit the Silicon Image, Inc. web site at www.siliconimage.com.

## **Revision History**

| Revision | Date     | Comment                                                                                                                                                                                   |

|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Α        | 09/08/03 | Derived from Preliminary datasheet Rev 0.65.                                                                                                                                              |

| A1       | 10/16/03 | Updated Table 2-6 SerDes Reference Clock Input Requirements; Updated Table 2-1 Absolute Maximum Ratings; Corrected inconsistent sentences (minor fixes including mistyping)               |

| A2       | 10/30/03 | Updated Section 8.2 Serial ATA Device Initialization                                                                                                                                      |

| A3       | 02/05/04 | Corrected part number on cover page to Sil3114CT176 from Sil3114CT144                                                                                                                     |

| A4       | 04/05/05 | Updated the part number on cover page to SiI3114 from SiI3114CT176; Added Part Ordering Number in section 4. Package Drawing; Updated Marking Specification in section 4. Package Drawing |

| В        | 07/21/06 | Corrected inconsistent sentences (minor fixes including mistyping); Updated Sil company logo                                                                                              |

| С        | 11/29/06 | This datasheet is no longer under NDA. Removed confidential markings                                                                                                                      |

| D        | 02/23/07 | New formatting applied throughout entire document.                                                                                                                                        |

© 2007 Silicon Image. Inc.

# **Table of Contents**

| Overview                                                 |    |

|----------------------------------------------------------|----|

| Key Benefits                                             |    |

| Features                                                 |    |

| Overall Features                                         |    |

| PCI Features Serial ATA Features                         |    |

| Other Features                                           |    |

| Applications                                             |    |

| References                                               |    |

| Functional Description                                   |    |

| PCI Interface                                            |    |

| PCI Initialization                                       |    |

| PCI Bus Operations                                       |    |

| PCI Configuration Space                                  |    |

| Deviations from the Specification                        |    |

| Electrical Characteristics                               |    |

|                                                          |    |

| Device Electrical Characteristics                        |    |

| SATA Interface Timing Specifications                     |    |

| SATA Interface Transmitter Output Jitter Characteristics |    |

| CLKI SerDes Reference Clock Input Requirements           |    |

| PCI 33 MHz Timing Specifications                         |    |

| PCI 66 MHz Timing Specifications                         |    |

| Flash Memory Timing Specifications                       |    |

| Pin Definitions                                          | 8  |

| SiI3114 Pin Listing                                      |    |

| SiI3114 Pin Diagram                                      | 13 |

| Sil3114 Pin Descriptions                                 |    |

| PCI 66MHz 32-bit                                         |    |

| Miscellaneous I/O<br>Serial ATA Signals                  |    |

| •                                                        |    |

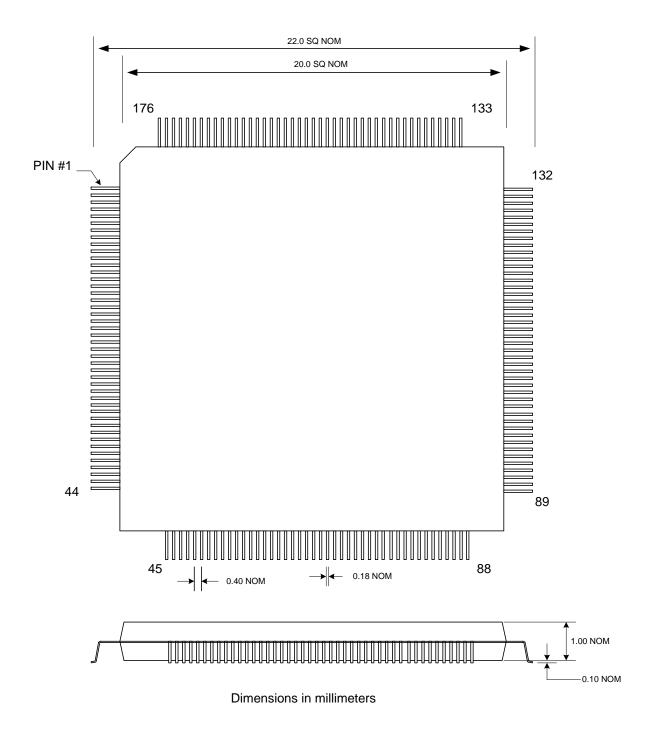

| Package Drawing                                          |    |

| Package Markings                                         | 20 |

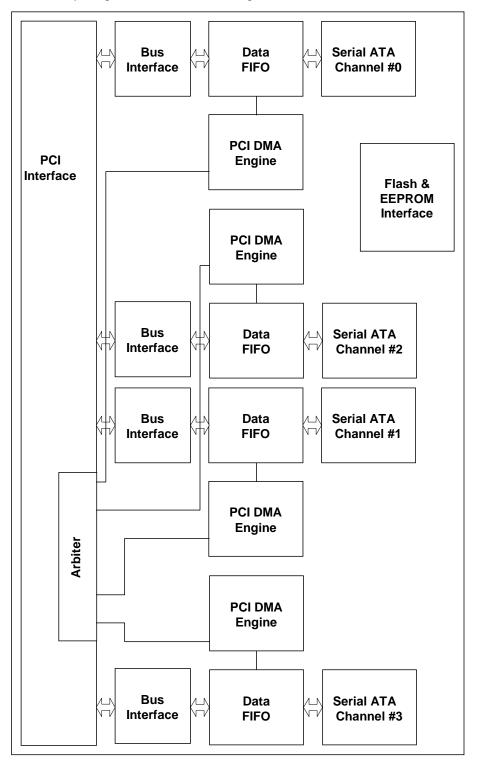

| Block Diagram                                            | 21 |

| Auto-Initialization                                      | 22 |

| Auto-Initialization from Flash                           | 22 |

| Auto-Initialization from EEPROM                          | 23 |

| Register Definitions                                     | 25 |

| PCI Configuration Space                                  |    |

| Device ID – Vendor ID                                    | 26 |

| PCI Status – PCI Command                                 |    |

| PCI Class Code – Revision ID                             | 28 |

| BIST – Header Type – Latency Timer – Cache Line Size     |    |

| Base Address Register 1                                  |    |

Downloaded from Arrow.com.

|                                                          | Silicon Image, Inc. |

|----------------------------------------------------------|---------------------|

| Base Address Register 2                                  | 29                  |

| Base Address Register 3                                  |                     |

| Base Address Register 4                                  |                     |

| Base Address Register 5                                  |                     |

| Subsystem ID – Subsystem Vendor ID                       |                     |

| Expansion ROM Base Address                               |                     |

| Capabilities Pointer                                     | 32                  |

| Max Latency – Min Grant – Interrupt Pin – Interrupt Line |                     |

| Configuration                                            |                     |

| Software Data Register                                   |                     |

| Power Management Control + Status                        |                     |

| PCI Bus Master – Channel 0/2                             |                     |

| PRD Table Address – Channel 0/2                          | 35                  |

| PCI Bus Master – Channel 1/3                             | 35                  |

| PRD Table Address – Channel 1/3                          | 35                  |

| Data Transfer Mode – Channel 0/2                         | 36                  |

| Data Transfer Mode – Channel 1/3                         |                     |

| System Configuration Status – Command                    |                     |

| System Software Data Register                            |                     |

| Flash Memory Address – Command + Status                  | 37                  |

| Flash Memory Data                                        |                     |

| EEPROM Memory Address – Command + Status                 | 38                  |

| EEPROM Memory Data                                       | 38                  |

| Channel 0/2 Task File Configuration + Status             | 38                  |

| Channel 1/3 Task File Configuration + Status             | 39                  |

| BA5 Indirect Address                                     | 39                  |

| BA5 Indirect Access                                      | 39                  |

| Internal Register Space – Base Address 0                 | 40                  |

| Channel 0/2 Task File Register 0                         | 40                  |

| Channel 0/2 Task File Register 1                         | 40                  |

| nternal Register Space – Base Address 1                  | 41                  |

| Channel 0/2 Task File Register 2                         |                     |

| nternal Register Space – Base Address 2                  |                     |

| Channel 1/3 Task File Register 0                         | 42                  |

| Channel 1/3 Task File Register 1                         | 42                  |

| nternal Register Space – Base Address 3                  | 43                  |

| Channel 1/3 Task File Register 2                         | 43                  |

| nternal Register Space – Base Address 4                  | 44                  |

| PCI Bus Master – Channel 0/2                             |                     |

| PRD Table Address – Channel 0/2                          |                     |

| PCI Bus Master – Channel 1/3                             |                     |

| PRD Table Address – Channel 1/3                          |                     |

| nternal Register Space – Base Address 5                  |                     |

| PCI Bus Master – Channel X                               | 53                  |

| PRD Table Address – Channel X                            |                     |

| PCI Bus Master2 – Channel X                              |                     |

| Summary Interrupt Status                                 |                     |

| PRD Address – Channel X                                  |                     |

| PCI Bus Master Byte Count – Channel X                    |                     |

| FIFO Valid Byte Count and Control – Channel X            |                     |

| System Configuration Status – Command                    |                     |

| System Software Data Register                            |                     |

| Flash Memory Address – Command + Status                  |                     |

| Flash Memory Data                                        |                     |

| EEPROM Memory Address – Command + Status                 |                     |

| EEPROM Memory Data                                       |                     |

Downloaded from Arrow.com.

|    | FIFO Port – Channel X                                      |    |

|----|------------------------------------------------------------|----|

|    | FIFO Pointers1- Channel X                                  |    |

|    | FIFO Pointers2– Channel X                                  |    |

|    | Channel X Task File Register 0                             |    |

|    | Channel X Task File Register 1                             |    |

|    | Channel X Task File Register 2                             |    |

|    | Channel X Task File Register 0 – Command Buffering         |    |

|    | Channel X Task File Register 1 – Command Buffering         |    |

|    | Channel X Extended Task File Register – Command Buffering  |    |

|    | Channel X Virtual DMA/PIO Read Ahead Byte Count            | 65 |

|    | Channel X Task File Configuration + Status                 |    |

|    | Data Transfer Mode – Channel X                             |    |

|    | Serial ATA SControl                                        |    |

|    | Serial ATA SStatusSerial ATA SError                        |    |

|    | Serial ATA Serior                                          |    |

|    | SMisc                                                      |    |

|    | Serial ATA PHY Configuration                               |    |

|    | SIEN                                                       |    |

|    | SFISCfg                                                    |    |

|    | RxFIS0-RxFIS6                                              | 73 |

| P  | rogramming Sequences                                       | 74 |

|    | Recommended Initialization Sequence for the SiI3114        |    |

|    | Serial ATA Device Initialization                           |    |

|    | Issue ATA Command                                          |    |

|    |                                                            |    |

|    | PIO Mode Read/Write Operation                              |    |

|    | Watchdog Timer Operation                                   |    |

|    | PIO Mode Read Ahead Operation                              |    |

|    | MDMA/UDMA Read/Write Operation                             |    |

|    | Virtual DMA Read/Write Operation                           |    |

|    | Using Virtual DMA with Non-DMA Capable Devices             |    |

|    | Using Virtual DMA with DMA Capable Devices                 |    |

|    | Second PCI Bus Master Registers Usage                      | 82 |

| Р  | ower Management                                            | 83 |

|    | Power Management Summary                                   | 83 |

|    | Partial Power Management Mode                              | 83 |

|    | Slumber Power Management Mode                              |    |

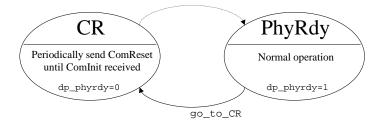

|    | Hot Plug Support                                           |    |

| _  | IS Support                                                 |    |

| r! | •••                                                        |    |

|    | FIS Summary                                                |    |

|    | FIS Transmission                                           |    |

|    | FIS Reception                                              |    |

|    | FIS Types Not Affiliated with Current ATA/ATAPI Operations |    |

|    | BIST SupportBIST Signals                                   |    |

|    |                                                            |    |

|    | DMA Setup                                                  |    |

| ATA Command Decoding                                                    | 90  |

|-------------------------------------------------------------------------|-----|

| Data Modes                                                              | 90  |

| ATA Commands                                                            | 90  |

| Obsolesced Commands                                                     |     |

| Read/Write Long                                                         |     |

| Vendor Specific Command Support                                         |     |

| Silicon Image's Vendor Specific Commands                                |     |

| Vendor Specific, Reserved, Retired and Obsolesced Commands  Definitions |     |

| Scheme                                                                  |     |

| Bridge Device Vendor Specific Commands                                  |     |

| Feature Set/Command Summary                                             |     |

| VS Lock                                                                 |     |

| VS Unlock Vendor Specific                                               |     |

| VS Unlock Reserved                                                      |     |

| VS Unlock IndividualVS Set General Protocol                             |     |

| VS Set Command Protocol                                                 |     |

| State Transitions                                                       |     |

| Protocols Summary                                                       |     |

| Reading and Writing of Task File and Device Control Registers           |     |

| 48-Bit LBA Addressing                                                   |     |

| Device Control Register and Soft Reset                                  |     |

| LED Support                                                             | 116 |

| Flash and EEPROM Programming Sequences                                  | 117 |

| Flash Memory Access                                                     | 117 |

| PCI Direct Access                                                       |     |

| Register Access                                                         | 117 |

| EEPROM Memory Access                                                    |     |

| EEPROM Write Operation                                                  |     |

| EEER LINARDOO LINDISTIAN                                                | 118 |

# **List of Figures**

| Figure 1. Address Lines During Configuration Cycle | 3  |

|----------------------------------------------------|----|

| Figure 2. Flash Memory Timing                      |    |

| Figure 3. Sil3114 Pin Diagram                      | 13 |

| Figure 4. Package Drawing – 176 TQFP               |    |

| Figure 5. Marking Specification – SiI3114CT176     | 20 |

| Figure 6. Marking Specification – SiI3114CTU       | 20 |

| Figure 7. Sil3114 Block Diagram                    | 21 |

| Figure 8. Auto-Initialization from Flash Timing    | 22 |

| Figure 9. Auto-Initialization from EEPROM Timing   | 23 |

| Figure 10. Hot Plug Logic State Diagram            |    |

|                                                    |    |

# **List of Tables**

| Table 1. Absolute Maximum Ratings                                    | 4    |

|----------------------------------------------------------------------|------|

| Table 2. DC Specifications                                           |      |

| Table 3. SATA Interface DC Specifications                            | 5    |

| Table 4. SATA Interface Timing Specifications                        | 5    |

| Table 5. SATA Interface Transmitter Output Jitter Characteristics    | 6    |

| Table 6. CLKI SerDes Reference Clock Input Requirements              | 6    |

| Table 7. PCI 33 MHz Timing Specifications                            |      |

| Table 8. PCI 66 MHz Timing Specifications                            | 7    |

| Table 9. SiI3114 Pin Listing                                         | 8    |

| Table 10. Pin Types                                                  | 12   |

| Table 11. Auto-Initialization from Flash Timing                      | 22   |

| Table 12. Flash Data Description                                     |      |

| Table 13. Auto-Initialization from EEPROM Timing                     | 23   |

| Table 14. Auto-Initialization from EEPROM Timing Symbols             | 23   |

| Table 15. EEPROM Data Description                                    |      |

| Table 16. SiI3114 PCI Configuration Space                            | 25   |

| Table 17. Sil3114 Internal Register Space – Base Address 0           | 40   |

| Table 18. Sil3114 Internal Register Space – Base Address 1           |      |

| Table 19. Sil3114 Internal Register Space – Base Address 2           |      |

| Table 20. Sil3114 Internal Register Space – Base Address 3           |      |

| Table 21. SiI3114 Internal Register Space – Base Address 4           |      |

| Table 22. Sil3114 Internal Register Space – Base Address 5           |      |

| Table 23. Software Data Byte, Base Address 5, Offset 00 <sub>H</sub> |      |

| Table 24. Software Data Byte, Base Address 5, Offset 10 <sub>H</sub> |      |

| Table 25. SError Register Bits (DIAG Field)                          |      |

| Table 26. SError Register Bits (ERR Field)                           |      |

| Table 27. Physical Region Descriptor (PRD) Format                    |      |

| Table 28. Power Management Register Bits                             |      |

| Table 29. FIS Summary                                                | 85   |

| Table 30. Configuration Bits for FIS Reception                       | 86   |

| Table 31. Default FIS Configurations                                 | 87   |

| Table 32. ATA Commands Supported                                     | 90   |

| Table 33. Data FIS                                                   |      |

| Table 34. Vendor Specific Command Summary                            |      |

| Table 35. 16-Entry Command Protocol Table                            |      |

| Table 36. Registers Used When Issuing VS Set Command                 |      |

| Table 37. Default State - VS_LOCKED                                  |      |

| Table 38. VS_VS                                                      |      |

| Table 39. VS_RSV                                                     | 110  |

| Table 40. VS_IND                                                     |      |

| Table 41. VS_VS_RSV                                                  |      |

| Table 42. VS_VS_IND                                                  |      |

| Table 43. VS_RSV_IND                                                 |      |

| Table 44. VS_VS_RSV_IND                                              |      |

| Table 45. Protocol Code Encoding Scheme                              |      |

| Table 46. Vendor Specific Protocol Code (in Alphabetical Order)      |      |

| Table 47. Vendor Specific Protocol Code (by Protocol Code)           |      |

| Table 46 - Venior Specific Projectic code un Albasherical Cimen      | 1115 |

#### Overview

The Silicon Image SiI3114 is a single-chip solution for a PCI to Serial ATA controller. It accepts host commands through the PCI bus, processes them, and transfers data between the host and Serial ATA devices. It can be used to control four independent Serial ATA channels. Each channel has its own Serial ATA bus and will support one Serial ATA device. The SiI3114 supports a 32-bit 66 MHz PCI bus and the Serial ATA Generation 1 transfer rate of 1.5 Gbit/s (150 MB/s).

## **Key Benefits**

The Silicon Image Sil3114 PCI to Serial ATA Controller is the perfect single-chip solution for designs that need to accommodate storage peripherals with the new Serial ATA interface. Any system with a PCI bus interface can simply add the Serial ATA interface by adding a card with the Sil3114 and loading the driver into the system.

The Sil3114 comes complete with drivers for Windows 98, Windows Millennium, Windows NT 4.0, Windows 2000, XP, Windows 2003, Netware 5.1, 6.0, 6.5, Red Hat Linux 8.0, 9.0, SuSE Linux 8.1, 8.2 and United Linux 1.0.

#### **Features**

## **Overall Features**

- Standalone PCI to Serial ATA host controller chip

- Compliant with PCI Specification, revision 2.3.

- Compliant with Programming Interface for Bus Master IDE Controller, revision 1.0.

- Driver support for Windows 98, Windows Millennium, Windows NT 4.0, Windows 2000, XP, Windows 2003, Netware 5.1, 6.0, 6.5, Red Hat Linux 8.0, 9.0, SuSE Linux 8.1, 8.2 and United Linux 1.0

- Supports up to 4Mbit external Flash or EPROM for BIOS expansion.

- Supports an external EEPROM, flash, or EPROM for programmable device ID, subsystem vendor ID, subsystem product ID, and PCI sub-class code.

- Supports the Silicon Image specific driver for special chip functions.

- Fabricated in a 0.18μ CMOS process with a 1.8 volt core and 3.3 volt I/Os.

- · Supports Plug and Play.

- Supports ATAPI device

- Supports Activity LEDs, one for each channel with 12mA open drain driving capability.

- Available in a 176-pin TQFP package.

#### **PCI** Features

- Supports 66 MHz PCI with 32-bit data.

- · Supports PCI PERR and SERR reporting.

- Supports PCI bus master operations: Memory Read, Memory Read Multiple, and Memory Write.

- Supports PCI bus target operations: Configuration Read, Configuration Write, I/O Read, I/O Write, Memory Read, Memory Write, Memory Read Line (Memory Read) and Memory Read Multiple (Memory Read)

- Supports byte alignment for odd-byte PCI address access.

- Supports jumper configurable PCI class code.

- Supports programmable and EEPROM, Flash and EPROM loadable PCI class code.

- Supports Base Address Register 5 in memory space.

### **Serial ATA Features**

- Integrated Serial ATA Link and PHY logic

- Compliant with Serial ATA 1.0 specifications

- Supports four independent Serial ATA channels.

- Supports Serial ATA Generation 1 transfer rate of 1.5Gbit/s.

- Supports Spread Spectrum in receiver

- Single PLL architecture, 1 PLL for all four ports

- Programmable drive strengths for Backplane applications

© 2007 Silicon Image, Inc. SiI-DS-0103-D

### **Other Features**

- Features independent 256-byte FIFOs (32-bit x 64 deep) per Serial ATA channel for host reads and writes.

- Supports legacy type operations (Master/Slave drive access) using I/O-mapped register space

- Supports 4 concurrent operations using memory-mapped register space

- Features Serial ATA to PCI interrupt masking.

- Features Watch Dog Timer for fault resiliency.

- Provides 8 bits of General Purpose I/O (GPIO)

## **Applications**

- PC motherboards

- · Serial ATA drive add on cards

- · Serial ATA RAID cards

### References

For more details about the Serial ATA technology, the reader is referred to the following industry specifications:

- Serial ATA / High Speed Serialized AT Attachment specification, Revision 1.0

- PCI Local Bus Specification Revision 2.3

- Advanced Power Management Specification Revision 1.0

- PCI IDE Controller Specification Revision 1.0

- Programming Interface for Bus Master IDE Controller, Revision 1.0

## **Functional Description**

The Sil3114 is a PCI-to-Serial ATA controller chip that transfers data between the PCI bus and storage media (e.g hard disk drive, etc). The Sil3114 consists of the following functional blocks:

- PCI Interface. Provides the interface to any system that has a PCI bus. Instructions and system clocks are based on this interface.

- Serial ATA Interface. Four separate channels to access storage media such as hard disk drive, floppy disk drive, CD-ROM.

### **PCI** Interface

The Sil3114 PCI interface is compliant with the PCI Local Bus Specification (Revision 2.3). The Sil3114 can act as a PCI master and a PCI slave, and contains the Sil3114 PCI configuration space and internal registers. When the Sil3114 needs to access shared memory, it becomes the bus master of the PCI bus and completes the memory cycle without external intervention. In the mode when it acts as a bridge between the PCI bus and the Serial ATA bus it will behave as a PCI slave.

### **PCI** Initialization

Generally, when a system initializes a module containing a PCI device, the configuration manager reads the configuration space of each PCI device on the PCI bus. Hardware signals select a specific PCI device based on a bus number, a slot number, and a function number. If a device that is addressed (via signal lines) responds to the configuration cycle by claiming the bus, then that function's configuration space is read out from the device during the cycle. Because any PCI device can be a multifunction device, every supported function's configuration space needs to be read from the device. Based on the information read, the configuration manager will assign system resources to each supported function within the device. Sometimes new information needs to be written into the function's configuration space. This is accomplished with a configuration write cycle.

## **PCI Bus Operations**

The Sil3114 behaves either as a PCI master or a PCI slave device at any time and switches between these modes as required during device operation. As a PCI slave, the Sil3114 responds to the following PCI bus operations:

- I/O Read

- I/O Write

- · Configuration Read

- Configuration Write

- · Memory Read

- · Memory Write

All other PCI cycles are ignored by the SiI3114.

As a PCI master, the SiI3114 generates the following PCI bus operations:

- · Memory Read Multiple

- · Memory Read

- Memory Write

## **PCI Configuration Space**

This section describes how the SiI3114 implements the required PCI configuration register space. The intent of PCI configuration space definition is to provide an appropriate set of configuration registers that satisfy the needs of current and anticipated system configuration mechanisms, without specifying those mechanisms or otherwise placing constraints on their use. These registers allow for:

- Full device relocation (including interrupt binding)

- Installation, configurations, and booting without user interventions

- System address map construction by device-independent software

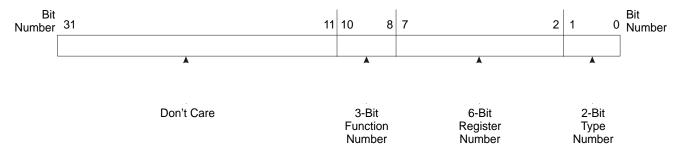

Figure 1 illustrates the address line assignments during the configuration cycle.

Figure 1. Address Lines During Configuration Cycle

The Sil3114 only responds to Type 0 configuration cycles. Type 1 cycles, which pass a configuration request on to another PCI bus, are ignored.

The address phase during a SiI3114 configuration cycle indicates the function number and register number being addressed which can be decoded by observing the status of the address lines AD[31:0].

The value of the signal lines AD[7:2] during the address phase of configuration cycles selects the register of the configuration space to access. Valid values are between 0 and 15, inclusive. Accessing registers outside this range results in an all-0s value being returned on reads, and no action being taken on writes.

The Class Code register contains the Class Code, Sub-Class Code, and Register-Level Programming Interface registers.

All writable bits in the configuration space except offset 44h, 8Ch are reset to their defaults by the hardware reset, PCI RESET (RST#) asserted. After reset, the SiI3114 is disabled and will only respond to PCI configuration write and PCI configuration read cycles.

# **Deviations from the Specification**

The Sil3114 product has been developed and tested to the specification listed in this document. As a result of testing and customer feedback, we may become aware of deviations to the specification that could affect the component's operation. To ensure awareness of these deviations by anyone considering the use of the Sil3114, we have included an Errata section at the end of this specification. Please ensure that the Errata section is

carefully reviewed. It is also important that you have the most current version of this specification. If there are any questions, please contact Silicon Image, Inc.

## **Electrical Characteristics**

## **Device Electrical Characteristics**

Specifications are for Commercial Temperature range, 0°C to +70°C, unless otherwise specified.

**Table 1. Absolute Maximum Ratings**

| Symbol                   | Parameter                                        | Ratings         | Unit |

|--------------------------|--------------------------------------------------|-----------------|------|

| VDDO                     | I/O Supply Voltage                               | 4.0             | V    |

| VDDI, VDDP<br>VDDA, VDDX | Digital, PLL, Analog and Oscillator Supply Power | 2.15            | V    |

| V <sub>PCI_IN</sub>      | Input Voltage for PCI signals                    | -0.3 ~ 6.0      | V    |

| V <sub>NONPCI_IN</sub>   | Input Voltage for Non-PCI signals                | -0.3 ~ VDDO+0.3 | V    |

| V <sub>CLKI_IN</sub>     | Input Voltage for CLKI                           | -0.3 ~ VDDX+0.3 | V    |

| I <sub>OUT</sub>         | DC Output Current                                | 16              | mA   |

| $\theta_{JA}$            | Thermal Resistance (Junction to Ambient)         | 32.6            | °C/W |

| T <sub>STG</sub>         | Storage Temperature                              | -65 ~ 150       | °C   |

**Table 2. DC Specifications**

| Symbol              | Parameter                      | Parameter Condition Type  |          | Limits   |                  |                  | Units |

|---------------------|--------------------------------|---------------------------|----------|----------|------------------|------------------|-------|

|                     |                                |                           |          | Min      | Тур              | Max              |       |

| VDDI                | Supply Voltage (Digital,       | -                         | -        | 1.71     | 1.8              | 1.89             | V     |

| VDDA                | Analog, PLL, Oscillator)       |                           |          |          |                  |                  |       |

| VDDP                |                                |                           |          |          |                  |                  |       |

| VDDX                |                                |                           |          |          |                  |                  |       |

| VDDO                | Supply Voltage(I/O)            | -                         | -        | 3.0      | 3.3              | 3.6              | V     |

| IDD <sub>1.8V</sub> | 1.8V Supply Current            | -                         | -        | -        | 325 <sup>1</sup> | 430 <sup>2</sup> | mA    |

| IDD <sub>3.3V</sub> | 3.3V Supply Current            | C <sub>LOAD</sub> = 20pF  | -        | -        | 12 <sup>1</sup>  | 40 <sup>2</sup>  | mA    |

| $V_{IH}$            | Input High Voltage             | -                         | 3.3V PCI | 0.5xVDDO | -                | -                | V     |

|                     |                                | -                         | Non-PCI  | 2.0      | -                | -                |       |

| V <sub>IL</sub>     | Input Low Voltage              | -                         | 3.3V PCI | -        | -                | 0.3xVDDO         | V     |

|                     |                                | -                         | Non-PCI  | -        | -                | 0.8              |       |

| V <sub>OH</sub>     | Output High Voltage            | $I_{OUT} = -500uA$        | 3.3V PCI | 0.9xVDDO | -                | -                | V     |

|                     |                                | -                         | Non-PCI  | 2.4      | -                | -                |       |

| V <sub>OL</sub>     | Output Low Voltage             | I <sub>OUT</sub> = 1500uA | 3.3V PCI | -        | -                | 0.1xVDDO         | V     |

|                     |                                | -                         | Non-PCI  | -        | -                | 0.4              |       |

| V+                  | Input High Voltage             | -                         | Schmitt  | -        | 1.8              | 2.3              | V     |

| V-                  | Input Low Voltage              | -                         | Schmitt  | 0.5      | 0.9              | -                | V     |

| $V_{H}$             | Hysteresis Voltage             | -                         | Schmitt  | 0.4      | -                | -                | V     |

| I <sub>IH</sub>     | Input High Current             | $V_{IN} = VDD$            | -        | -10      | -                | 10               | uA    |

| I <sub>IL</sub>     | Input Low Current              | V <sub>IN</sub> = VSS     | -        | -10      | -                | 10               | uA    |

| I <sub>ILOD</sub>   | Open Drain output sink current | -                         | -        | -        | -                | 12               | mA    |

| l <sub>oz</sub>     | 3-State Leakage Current        | -                         | -        | -10      | -                | 10               | uA    |

Notes: <sup>1</sup> Using the random data pattern (read/write operation) at 1.8V or 3.3V power supply, PCI interface = 33 MHz.

<sup>&</sup>lt;sup>2</sup> Using the maximum toggling data pattern (read/write operation) at 1.89V or 3.6V power supply, PCI interface = 66 MHz.

**Table 3. SATA Interface DC Specifications**

| Symbol               | Parameter                                            |                                                                                       | Unit |     |     |      |

|----------------------|------------------------------------------------------|---------------------------------------------------------------------------------------|------|-----|-----|------|

|                      |                                                      |                                                                                       | Min  | Тур | Max |      |

| V <sub>DOUT_00</sub> | TX+/TX- differential peak-to-peak voltage swing.     | Terminated by 50 Ohms. Tx Swing Value = 00                                            | 400  | 500 | 600 | mV   |

| $V_{DOUT\_01}$       | TX+/TX- differential peak-to-peak voltage swing.     | Terminated by 50 Ohms. Tx Swing Value = 01                                            | 500  | 600 | 700 | mV   |

| $V_{DOUT\_10}$       | TX+/TX- differential peak-to-peak voltage swing.     | Terminated by 50 Ohms. Tx Swing Value = 10                                            | 550  | 700 | 800 | mV   |

| V <sub>DOUT_11</sub> | TX+/TX- differential peak-to-peak voltage swing.     | Terminated by 50 Ohms. Tx Swing Value = 11                                            | 650  | 800 | 900 | mV   |

| $V_{DIN}$            | RX+/RX- differential peak-to-peak input sensitivity  | -                                                                                     | 325  | -   | -   | mV   |

| $V_{\text{DICM}}$    | RX+/RX- differential<br>Input common-mode<br>voltage | -                                                                                     | 200  | 300 | 450 | mV   |

| $V_{DOCM}$           | TX+/TX-differential<br>Output common-mode<br>voltage | -                                                                                     | 200  | 300 | 450 | mV   |

| $V_{SDT}$            | Squelch detector threshold                           | -                                                                                     | 100  | 50  | 200 | mV   |

| $Z_{DIN}$            | Differential input impedance                         | REXT = 1k 1% for 25MHz SerDes<br>Ref Clk REXT = 4.99k 1% for<br>100MHz SerDes Ref Clk | 85   | 100 | 115 | ohms |

| Z <sub>DOUT</sub>    | Differential output impedance                        | REXT = 1k 1% for 25MHz SerDes<br>Ref Clk REXT = 4.99k 1% for<br>100MHz SerDes Ref Clk | 85   | 100 | 115 | ohms |

# **SATA Interface Timing Specifications**

**Table 4. SATA Interface Timing Specifications**

| Symbol                    | Parameter                         | Condition                                                                                                                                          | Limits |     | Unit |     |

|---------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|------|-----|

|                           |                                   |                                                                                                                                                    | Min    | Тур | Max  |     |

| T <sub>TX_RISE_FALL</sub> | Rise and Fall time at transmitter | 20%-80%                                                                                                                                            | 133    | -   | 274  | ps  |

| T <sub>TX_SKEW</sub>      | Tx differential skew              | -                                                                                                                                                  | -      | -   | 20   | ps  |

| T <sub>TX_DC_FREQ</sub>   | Tx DC clock frequency skew        | -                                                                                                                                                  | -350   | -   | +350 | ppm |

| T <sub>TX_AC_FREQ</sub>   | Tx AC clock frequency skew        | SerDes Ref Clk = SSC AC modulation, subject to the "Downspread SSC" triangular modulation (30-33KHz) profile per 6.6.4.5 in SATA 1.0 specification | -5000  | -   | +0   | ppm |

## **SATA Interface Transmitter Output Jitter Characteristics**

**Table 5. SATA Interface Transmitter Output Jitter Characteristics**

| Symbol              | Parameter                           | Condition                                                                         |     | Limits | Limits |        |  |

|---------------------|-------------------------------------|-----------------------------------------------------------------------------------|-----|--------|--------|--------|--|

|                     |                                     |                                                                                   | Min | Тур    | Max    |        |  |

| RJ <sub>5UI</sub>   | 5UI later Random Jitter             | Measured at Tx output pins 1sigma deviation                                       | -   | 4.5    | -      | ps rms |  |

| RJ <sub>250UI</sub> | 250UI later Random<br>Jitter        | Measured at Tx output pins 1sigma deviation                                       | -   | 6.0    | -      | ps rms |  |

| DJ <sub>5UI</sub>   | 5UI later Deterministic<br>Jitter   | Measured at Tx output pins peak<br>to peak phase variation Random<br>data pattern | -   | 40     | -      | ps     |  |

| DJ <sub>250UI</sub> | 250UI later Deterministic<br>Jitter | Measured at Tx output pins peak to peak phase variation Random data pattern       | -   | 45     | -      | ps     |  |

# **CLKI SerDes Reference Clock Input Requirements**

Table 6. CLKI SerDes Reference Clock Input Requirements

| Symbol                      | Parameter                  | Condition                                                               |          | Unit      |          |     |

|-----------------------------|----------------------------|-------------------------------------------------------------------------|----------|-----------|----------|-----|

|                             |                            |                                                                         | Min      | Тур       | Max      |     |

| T <sub>CLKI_FREQ</sub>      | Nominal Frequency          | REXT = 1k 1%<br>REXT = 4.99k 1%                                         | -        | 25<br>100 | -        | MHz |

| V <sub>CLK_IH</sub>         | Input High Voltage         | -                                                                       | 0.7xVDDX | -         | -        | V   |

| V <sub>CLK_IL</sub>         | Input Low Voltage          | -                                                                       | -        | -         | 0.3xVDDX | V   |

| T <sub>CLKI_J</sub>         | CLKI frequency tolerance   | -                                                                       | -100     |           | +100     | ppm |

| T <sub>CLKI_RISE_FALL</sub> | Rise and Fall time at CLKI | 25MHz reference clock,<br>20%-80%<br>100MHz reference clock,<br>20%-80% | -        | -         | 4 2      | ns  |

| T <sub>CLKI_RC_DUTY</sub>   | CLKI duty cycle            | 20%-80%                                                                 | 40       | -         | 60       | %   |

Notes: CLKI must be 1.8V swing when external clock input to this pin

# **PCI 33 MHz Timing Specifications**

**Table 7. PCI 33 MHz Timing Specifications**

| Symbol                 | Parameter                            | Lin  | Unit |    |

|------------------------|--------------------------------------|------|------|----|

|                        |                                      | Min  | Max  |    |

| $T_{VAL}$              | CLK to Signal Valid – Bussed Signals | 2.0  | 11.0 | ns |

| T <sub>VAL (PTP)</sub> | CLK to Signal Valid – Point to Point | 2.0  | 11.0 | ns |

| T <sub>ON</sub>        | Float to Active Delay                | 2.0  | -    | ns |

| T <sub>OFF</sub>       | Active to Float Delay                | -    | 28.0 | ns |

| T <sub>SU</sub>        | Input Setup Time – Bussed Signals    | 7.0  | -    | ns |

| T <sub>SU (PTP)</sub>  | Input Setup Time – Point to Point    | 10.0 | -    | ns |

| T <sub>H</sub>         | Input Hold Time                      | 0.0  | -    | ns |

# **PCI 66 MHz Timing Specifications**

**Table 8. PCI 66 MHz Timing Specifications**

| Symbol                 | Parameter                            | Lin | Unit |    |

|------------------------|--------------------------------------|-----|------|----|

|                        |                                      | Min | Max  |    |

| T <sub>VAL</sub>       | CLK to Signal Valid – Bussed Signals | 2.0 | 6.0  | ns |

| T <sub>VAL (PTP)</sub> | CLK to Signal Valid – Point to Point | 2.0 | 6.0  | ns |

| T <sub>ON</sub>        | Float to Active Delay                | 2.0 | -    | ns |

| T <sub>OFF</sub>       | Active to Float Delay                | -   | 14.0 | ns |

| T <sub>SU</sub>        | Input Setup Time – Bussed Signals    | 3.0 | -    | ns |

| T <sub>SU (PTP)</sub>  | Input Setup Time – Point to Point    | 5.0 | -    | ns |

| T <sub>H</sub>         | Input Hold Time                      | 0.0 | -    | ns |

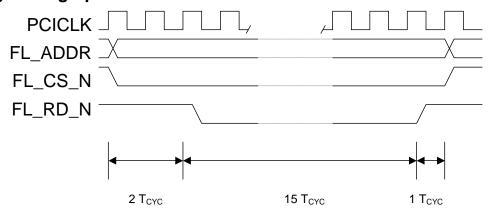

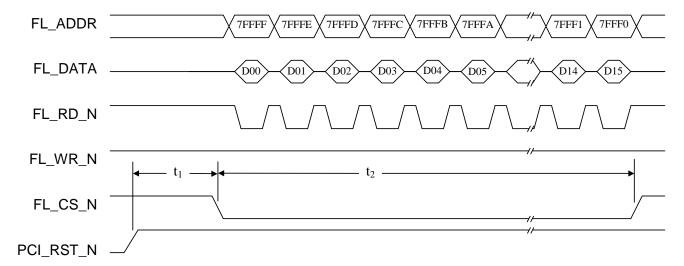

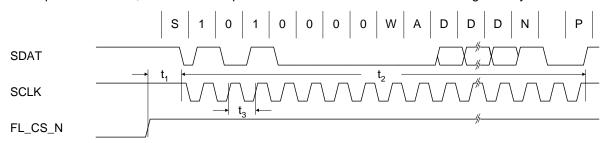

# **Flash Memory Timing Specifications**

# FLASH READ TIMING

# FLASH WRITE TIMING

Figure 2. Flash Memory Timing

## **Pin Definitions**

# Sil3114 Pin Listing

This section describes the pins of the SiI3114 PCI-to-Serial ATA host controller. Table 9 provides information on pin numbers, pin names, pin types, drive types where applicable, internal resistors where applicable, and descriptions. Table 10 shows the pin types used in the SiI3114.

Table 9. Sil 3114 Pin Listing

| Pin # | Pin Name   | Туре | Internal<br>Resistor | Description                                      |

|-------|------------|------|----------------------|--------------------------------------------------|

| 1     | N/C        | N/C  | -                    | No internal connection                           |

| 2     | GNDA       | GND  | -                    | Analog Ground                                    |

| 3     | TxP0       | 0    | ı                    | Channel 0 Differential Transmit +ve              |

| 4     | TxN0       | 0    | 1                    | Channel 0 Differential Transmit -ve              |

| 5     | GNDA       | GND  | 1                    | Analog Ground                                    |

| 6     | VDDA       | PWR  | ı                    | 1.8V SerDes Power                                |

| 7     | GNDA       | GND  | -                    | Analog Ground                                    |

| 8     | RxN0       | I    | -                    | Channel 0 Differential Receive -ve               |

| 9     | RxP0       | 1    | -                    | Channel 0 Differential Receive +ve               |

| 10    | VDDA       | PWR  | -                    | 1.8V SerDes Power                                |

| 11    | GNDA       | GND  | -                    | Analog Ground                                    |

| 12    | TxP1       | 0    | -                    | Channel 1 Differential Transmit +ve              |

| 13    | TxN1       | 0    | -                    | Channel 1 Differential Transmit -ve              |

| 14    | GNDA       | GND  | -                    | Analog Ground                                    |

| 15    | VDDA       | PWR  | -                    | 1.8V SerDes Power                                |

| 16    | GNDA       | GND  | -                    | Analog Ground                                    |

| 17    | RxN1       | I    | -                    | Channel 1 Differential Receive -ve               |

| 18    | RxP1       | -    | -                    | Channel 1 Differential Receive +ve               |

| 19    | VDDA       | PWR  | -                    | 1.8V SerDes Power                                |

| 20    | VDDX       | PWR  | -                    | 1.8V supply for Crystal Oscillator               |

| 21    | XTALO      | 0    | -                    | Crystal Oscillator Output                        |

| 22    | XTALI/CLKI | I    | -                    | Crystal Oscillator Input or external clock input |

| 23    | GNDA       | GND  | -                    | Analog Ground                                    |

| 24    | REXT       | I    | -                    | External Reference Resistor Input                |

| 25    | VDDP       | PWR  | -                    | 1.8V PLL Power                                   |

| 26    | GNDA       | GND  | -                    | Analog Ground                                    |

| 27    | TxP2       | 0    | -                    | Channel 2 Differential Transmit +ve              |

| 28    | TxN2       | 0    | -                    | Channel 2 Differential Transmit -ve              |

| 29    | GNDA       | GND  | -                    | Analog Ground                                    |

| 30    | VDDA       | PWR  | -                    | 1.8V SerDes Power                                |

| 31    | GNDA       | GND  | -                    | Analog Ground                                    |

| 32    | RxN2       | I    | -                    | Channel 2 Differential Receive -ve               |

| 33    | RxP2       | 1    | -                    | Channel 2 Differential Receive +ve               |

| 34    | VDDA       | PWR  | -                    | 1.8V SerDes Power                                |

| 35    | GNDA       | GND  | -                    | Analog Ground                                    |

| 36    | TxP3       | 0    | -                    | Channel 3 Differential Transmit +ve              |

| 37    | TxN3       | 0    | -                    | Channel 3 Differential Transmit -ve              |

| 38    | GNDA       | GND  | -                    | Analog Ground                                    |

| 39    | VDDA       | PWR  | -                    | 1.8V SerDes Power                                |

| 40    | GNDA       | GND  | -                    | Analog Ground                                    |

## Table 9. Sil3114 Pin Listing (continued)

| Pin # | Pin Name                   | Туре | Internal<br>Resistor | Description                                                 |

|-------|----------------------------|------|----------------------|-------------------------------------------------------------|

| 41    | RxN3                       | I    | -                    | Channel 3 Differential Receive -ve                          |

| 42    | RxP3                       | I    | -                    | Channel 3 Differential Receive +ve                          |

| 43    | VDDA                       | PWR  | •                    | 1.8V SerDes Power                                           |

| 44    | N/C                        | N/C  | -                    | No internal connection                                      |

| 45    | VDDO                       | PWR  | -                    | 3.3 Volt Power                                              |

| 46    | VSSO                       | GND  | -                    | Ground                                                      |

| 47    | EEPROM_SDAT                | I/O  | PU – 70k             | EEPROM Serial Data                                          |

| 48    | EEPROM_SCLK                | I/O  | PU – 70k             | EEPROM Serial Clock                                         |

| 49    | FL_ADDR[00] /<br>CLASS_SEL | I/O  | PU – 70k             | Flash Memory Address 0 / Mass Storage-RAID PCI Class Select |

| 50    | FL_ADDR[01] / BA5_EN       | I/O  | PU – 70k             | Flash Memory Address 1 / Base Address Register 5 Enable     |

| 51    | FL_ADDR[02]                | 0    | PU – 70k             | Flash Memory Address 2                                      |

| 52    | FL_RD_N                    | 0    | PU – 70k             | Flash Memory Read Strobe                                    |

| 53    | FL_WR_N                    | 0    | PU – 70k             | Flash Memory Write Strobe                                   |

| 54    | FL_ADDR[03]                | 0    | PU – 70k             | Flash Memory Address 3                                      |

| 55    | FL_ADDR[04]                | 0    | PU – 70k             | Flash Memory Address 4                                      |

| 56    | FL_ADDR[05]                | 0    | PU – 70k             | Flash Memory Address 5                                      |

| 57    | FL_ADDR[06]                | 0    | PU – 70k             | Flash Memory Address 6                                      |

| 58    | VDDO                       | PWR  | •                    | 3.3 Volt Power                                              |

| 59    | VSSO                       | GND  | ı                    | Ground                                                      |

| 60    | VDDI                       | PWR  | -                    | 1.8V Internal core Power                                    |

| 61    | VSSI                       | GND  | -                    | Ground                                                      |

| 62    | FL_ADDR[07]                | 0    | PU – 70k             | Flash Memory Address 7                                      |

| 63    | FL_ADDR[08]                | 0    | PU – 70k             | Flash Memory Address 8                                      |

| 64    | FL_ADDR[09]                | 0    | PU – 70k             | Flash Memory Address 9                                      |

| 65    | LED0                       | OD   | PU – 70k             | Channel 0 activity LED indicator                            |

| 66    | FL_ADDR[10]                | 0    | PU – 70k             | Flash Memory Address 10                                     |

| 67    | FL_ADDR[11]                | 0    | PU – 70k             | Flash Memory Address 11                                     |

| 68    | FL_ADDR[12]                | 0    | PU – 70k             | Flash Memory Address 12                                     |

| 69    | FL_ADDR[13]                | 0    | PU – 70k             | Flash Memory Address 13                                     |

| 70    | LED1                       | OD   | PU – 70k             | Channel 1 activity LED indicator                            |

| 71    | VDDI                       | PWR  | -                    | 1.8V Internal core Power                                    |

| 72    | VSSI                       | GND  | -                    | Ground                                                      |

| 73    | VDDO                       | PWR  | -                    | 3.3 Volt Power                                              |

| 74    | VSSO                       | GND  | -                    | Ground                                                      |

| 75    | FL_ADDR[14]                | 0    | PU – 70k             | Flash Memory Address 14                                     |

| 76    | FL_ADDR[15]                | 0    | PU – 70k             | Flash Memory Address 15                                     |

| 77    | FL_ADDR[16]                | 0    | PU – 70k             | Flash Memory Address 16                                     |

| 78    | LED2                       | OD   | PU – 70k             | Channel 2 activity LED indicator                            |

| 79    | FL_ADDR[17]                | 0    | PU – 70k             | Flash Memory Address 17                                     |

| 80    | FL_ADDR[18]                | 0    | PU – 70k             | Flash Memory Address 18                                     |

| 81    | FL_CS_N                    | 0    | PU – 70k             | Flash Memory Chip Select                                    |

| 82    | VDDI                       | PWR  | -                    | 1.8V Internal Core Power                                    |

| 83    | VSSI                       | GND  | -                    | Ground                                                      |

| 84    | LED3                       | OD   | PU – 70k             | Channel 3 activity LED indicator                            |

| 85    | FL_DATA[00]                | I/O  | PU – 70k             | Flash Memory Data 0                                         |

| 86    | FL_DATA[01]                | I/O  | PU – 70k             | Flash Memory Data 1                                         |

Table 9. Sil3114 Pin Listing (continued)

| Pin # Din Name Type Internal Description |             |           |                      |                          |  |  |

|------------------------------------------|-------------|-----------|----------------------|--------------------------|--|--|

| Pin #                                    | Pin Name    | Туре      | Internal<br>Resistor | Description              |  |  |

| 87                                       | FL_DATA[02] | I/O       | PU – 70k             | Flash Memory Data 2      |  |  |

| 88                                       | VDDO        | PWR       | -                    | 3.3 Volt Power           |  |  |

| 89                                       | VSSO        | GND       | -                    | Ground                   |  |  |

| 90                                       | FL_DATA[03] | I/O       | PU – 70k             | Flash Memory Data 3      |  |  |

| 91                                       | FL_DATA[04] | I/O       | PU – 70k             | Flash Memory Data 4      |  |  |

| 92                                       | FL_DATA[05] | I/O       | PU – 70k             | Flash Memory Data 5      |  |  |

| 93                                       | FL_DATA[06] | I/O       | PU – 70k             | Flash Memory Data 6      |  |  |

| 94                                       | FL_DATA[07] | I/O       | PU – 70k             | Flash Memory Data 7      |  |  |

| 95                                       | PCI_INTA_N  | OD        | -                    | PCI Interrupt            |  |  |

| 96                                       | PCI_RST_N   | I-Schmitt | -                    | PCI Reset                |  |  |

| 97                                       | PCI_CLK     | I         | -                    | PCI Clock                |  |  |

| 98                                       | PCI_GNT_N   | I         | -                    | PCI Bus Grant            |  |  |

| 99                                       | VDDO        | PWR       | -                    | 3.3 Volt Power           |  |  |

| 100                                      | VSSO        | GND       | -                    | Ground                   |  |  |

| 101                                      | VDDI        | PWR       | -                    | 1.8V Internal Core Power |  |  |

| 102                                      | VSSI        | GND       | -                    | Ground                   |  |  |

| 103                                      | PCI_REQ_N   | Т         | -                    | PCI Bus Request          |  |  |

| 104                                      | PCI_AD31    | I/O       | -                    | PCI Address/Data         |  |  |

| 105                                      | PCI_AD30    | I/O       | -                    | PCI Address/Data         |  |  |

| 106                                      | PCI_AD29    | I/O       | -                    | PCI Address/Data         |  |  |

| 107                                      | PCI_AD28    | I/O       | -                    | PCI Address/Data         |  |  |

| 108                                      | PCI_AD27    | I/O       | -                    | PCI Address/Data         |  |  |

| 109                                      | PCI_AD26    | I/O       | -                    | PCI Address/Data         |  |  |

| 110                                      | VDDO        | PWR       | -                    | 3.3 Volt Power           |  |  |

| 111                                      | VSSO        | GND       | -                    | Ground                   |  |  |

| 112                                      | PCI_AD25    | I/O       | -                    | PCI Address/Data         |  |  |

| 113                                      | PCI_AD24    | I/O       | -                    | PCI Address/Data         |  |  |

| 114                                      | PCI_CBE3    | I/O       | -                    | PCI Command/Byte Enable  |  |  |

| 115                                      | PCI_IDSEL   |           | -                    | PCI ID Select            |  |  |

| 116                                      | PCI_AD23    | I/O       | -                    | PCI Address/Data         |  |  |

| 117                                      | PCI_AD22    | I/O       | -                    | PCI Address/Data         |  |  |

| 118                                      | PCI_AD21    | I/O       | -                    | PCI Address/Data         |  |  |

| 119                                      | VDDI        | PWR       | -                    | 1.8V Internal Core Power |  |  |

| 120                                      | VSSI        | GND       | -                    | Ground                   |  |  |

| 121                                      | VDDO        | PWR       | -                    | 3.3 Volt Power           |  |  |

| 122                                      | VSSO        | GND       | -                    | Ground                   |  |  |

| 123                                      | PCI_AD20    | I/O       | -                    | PCI Address/Data         |  |  |

| 124                                      | PCI_AD19    | I/O       | -                    | PCI Address/Data         |  |  |

| 125                                      | PCI_AD18    | I/O       | -                    | PCI Address/Data         |  |  |

| 126                                      | PCI_AD17    | I/O       | -                    | PCI Address/Data         |  |  |

| 127                                      | PCI_AD16    | I/O       | -                    | PCI Address/Data         |  |  |

| 128                                      | PCI_CBE2    | I/O       | -                    | PCI Command/Byte Enable  |  |  |

| 129                                      | PCI_FRAME_N | I/O       | -                    | PCI Frame                |  |  |

| 130                                      | PCI_IRDY_N  | I/O       | -                    | PCI Initiator Ready      |  |  |

| 131                                      | PCI_PERR_N  | I/O       | -                    | PCI Parity Error         |  |  |

| 132                                      | VDDO        | PWR       | -                    | 3.3 Volt Power           |  |  |

Table 9. Sil3114 Pin Listing (continued)

| Pin# | Pin Name     | Туре | Internal<br>Resistor | Description              |

|------|--------------|------|----------------------|--------------------------|

| 133  | VSSO         | GND  | -                    | Ground                   |

| 134  | PCI_STOP_N   | I/O  | -                    | PCI Stop                 |

| 135  | PCI_DEVSEL_N | I/O  | -                    | PCI Device Select        |

| 136  | PCI_TRDY_N   | I/O  | -                    | PCI Target Ready         |

| 137  | PCI_SERR_N   | OD   | -                    | PCI System Error         |

| 138  | VDDI         | PWR  | -                    | 1.8V Internal Core Power |

| 139  | VSSI         | GND  | -                    | Ground                   |

| 140  | PCI_PAR      | I/O  | -                    | PCI Parity               |

| 141  | PCI_CBE1     | I/O  | -                    | PCI Command/Byte Enable  |

| 142  | PCI_AD15     | I/O  | -                    | PCI Address/Data         |

| 143  | PCI_AD14     | I/O  | -                    | PCI Address/Data         |

| 144  | VDDO         | PWR  | -                    | 3.3 Volt Power           |

| 145  | VSSO         | GND  | -                    | Ground                   |

| 146  | PCI_AD13     | I/O  | -                    | PCI Address/Data         |

| 147  | PCI_AD12     | I/O  | -                    | PCI Address/Data         |

| 148  | VDDI         | PWR  | -                    | 1.8 Volt Core Power      |

| 149  | VSSI         | GND  | -                    | Ground                   |

| 150  | PCI_AD11     | I/O  | -                    | PCI Address/Data         |

| 151  | PCI_AD10     | I/O  | -                    | PCI Address/Data         |

| 152  | PCI_M66EN    | 1    | -                    | PCI 66 MHz Enable        |

| 153  | PCI_AD09     | I/O  | -                    | PCI Address/Data         |

| 154  | PCI_AD08     | I/O  | ı                    | PCI Address/Data         |

| 155  | PCI_CBE0     | I/O  | -                    | PCI Command/Byte Enable  |

| 156  | VDDO         | PWR  | -                    | 3.3 Volt Power           |

| 157  | VSSO         | GND  | -                    | Ground                   |

| 158  | VDDI         | PWR  | -                    | 1.8 Volt Core Power      |

| 159  | VSSI         | GND  | -                    | Ground                   |

| 160  | PCI_AD07     | I/O  | -                    | PCI Address/Data         |

| 161  | PCI_AD06     | I/O  | -                    | PCI Address/Data         |

| 162  | PCI_AD05     | I/O  | -                    | PCI Address/Data         |

| 163  | PCI_AD04     | I/O  | -                    | PCI Address/Data         |

| 164  | PCI_AD03     | I/O  | -                    | PCI Address/Data         |

| 165  | PCI_AD02     | I/O  | -                    | PCI Address/Data         |

| 166  | PCI_AD01     | I/O  | -                    | PCI Address/Data         |

| 167  | PCI_AD00     | I/O  | -                    | PCI Address/Data         |

| 168  | VDDO         | PWR  | -                    | 3.3 Volt Power           |

| 169  | VSSO         | GND  | -                    | Ground                   |

| 170  | GPIOEN       | I    | PD -60k              | GPIO Enable              |

| 171  | TEST_MODE    | I    | PD -60k              | Test Mode Enable         |

| 172  | TMS          | I    | PU -70k              | JTAG Test Mode Select    |

| 173  | TCK          | I    | PU -70k              | JTAG Test Clock          |

| 174  | TDO          | 0    | -                    | JTAG Test Data Out       |

| 175  | TDI          | I    | PU -70k              | JTAG Test Data In        |

| 176  | TRSTN        | I    | PU -70k              | JTAG Test Reset          |

Table 10. Pin Types

| Pin Type  | Description                     |

|-----------|---------------------------------|

| I         | Input Pin with LVTTL Thresholds |

| I-Schmitt | Input Pin with Schmitt Trigger  |

| 0         | Output Pin                      |

| Т         | Tri-state Output Pin            |

| I/O       | Bi-directional Pin              |

| OD        | Open Drain Output Pin           |

Note: PCI pins are 5V tolerant.

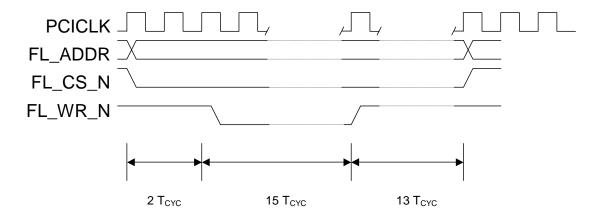

## Sil3114 Pin Diagram

Figure 3 shows the SiI3114 pinout. Note that most PCI signals are not labeled with the "PCI\_" prefix as used elsewhere.

Figure 3. SiI3114 Pin Diagram

## Sil3114 Pin Descriptions

### PCI 66MHz 32-bit

PCI Address and Data Pin Names: PCI\_AD[31..00]

Pin Numbers: 104-109, 112, 113, 116-118, 123-127, 142, 143, 146, 147, 150, 151, 153, 154, 160-167 Address and Data buses are multiplexed on the same PCI pins. A bus transaction consists of an address phase followed by one or more data phases. PCI supports both read and write bursts. The address phase is the first clock cycle in which PCI\_FRAME\_N signal is asserted. During the address phase, PCI\_AD[31:0] contain a physical address (32 bits). For I/O, this can be a byte address. For configuration and memory it is a dword address. During data phases, PCI AD[7:0] contain the least significant byte (LSB) and PCI AD[31:24] contain the most significant byte (MSB). Write data is stable and valid when PCI\_IRDY\_N is asserted; read data is stable and valid when PCI\_TRDY\_N is asserted. Data is transferred during those clocks where both PCI\_IRDY\_N and PCI TRDY N are asserted.

PCI Command and Byte Enables Pin Names: PCI CBE[3..0] Pin Numbers: 114, 128, 141, 155

Command and Byte Enables are multiplexed on the same PCI pins. During the address phase of a transaction, PCI CBE[3:0] N define the bus command. During the data phase, PCI CBE[3:0] N are used as Byte Enables. Byte Enables are valid for the entire data phase and determine which byte lanes carry meaningful data.

PCI ID Select

Pin Name: PCI IDSEL Pin Number: 115

This signal is used as a chip select during configuration read and write transactions.

PCI Frame Cycle

Pin Name: PCI FRAME N

Pin Number: 129

Cycle Frame is driven by the current master to indicate the beginning and duration of an access. PCI\_FRAME\_N is asserted to indicate that a bus transaction is beginning. While PCI\_FRAME\_N is asserted, data transfers continue. When PCI\_FRAME\_N is deasserted, the transaction is in the final data phase or has completed.

PCI Initiator Ready Pin Name: PCI IRDY N Pin Number: 130

Initiator Ready indicates the initializing agent's (bus master's) ability to complete the current data phase of the transaction. This signal is used with PCI\_TRDY\_N. A data phase is completed on any clock when both PCI IRDY N and PCI TRDY N are sampled as asserted. Wait cycles are inserted until both PCI IRDY N and PCI TRDY N are asserted together.

PCI Target Ready

Pin Name: PCI TRDY N

Pin Number: 136

Target Ready indicates the target agent's ability to complete the current data phase of the transaction. PCI\_TRDY\_N is used with PCI\_IRDY\_N. A data phase is completed on any clock when both PCI\_TRDY\_N and PCI\_IRDY\_N are sampled asserted. During a read, PCI\_TRDY\_N indicates that valid data is present on

PCI AD[31:0]. During a write, it indicates the target is prepared to accept data.

PCI Device Select

Pin Name: PCI DEVSEL N

Pin Number: 135

Device Select, when actively driven, indicates the driving device has decoded its address as the target of the current access. As an input, PCI DEVSEL N indicates to a master whether any device on the bus has been selected.

PCI Stop

Pin Name: PCI STOP N

Pin Number: 134

PCI STOP N indicates the current target is requesting that the master stop the current transaction.

PCI Parity Error

Pin Name: PCI PERR N

Pin Number: 131

PCI PERR N indicates a data parity error between the current master and target on PCI. On a write transaction, the target always signals data parity errors back to the master on PCI PERR N. On a read transaction, the master asserts PCI PERR N to indicate to the system that an error was detected.

PCI System Error

Pin Name: PCI SERR\_N

Pin Number: 137

System Error is for reporting address parity errors, data parity errors on Special Cycle Command, or any other system error where the result will be catastrophic. The PCI\_SERR\_N is a pure open drain and is actively driven for a single PCI clock by the agent reporting the error. The assertion of PCI\_SERR\_N is synchronous to the clock and meets the setup and hold times of all bused signals. However, the restoring of PCI SERR N to the deasserted state is accomplished by a weak pull-up. Note that if an agent does not want a non-maskable interrupt (NMI) to be generated, a different reporting mechanism is required.

PCI Parity

Pin Name: PCI PAR Pin Number: 140

PCI PAR is even parity across PCI AD[31:0] and PCI CBE[3:0] N. Parity generation is required by all PCI agents. PCI PAR is stable and valid one clock after the address phase. For data phases PCI PAR is stable and valid one clock after either PCI\_IRDY\_N is asserted on a write transaction or PCI\_TRDY\_N is asserted on a read transaction. Once PCI\_PAR is valid, it remains valid until one clock after the completion of the current data phase. (PCI\_PAR has the same timing as PCI\_AD[31:0] but delayed by one clock.)

PCI Request

Pin Name: PCI REQ N

Pin Number: 103

This signal indicates to the arbiter that this agent desires use of the PCI bus.

PCI Grant

Pin Name: PCI GNT N

Pin Number: 98

This signal indicates to the agent that access to the PCI bus has been granted. In response to a PCI request, this is a point-to-point signal. Every master has its own PCI GNT N, which must be ignored while PCI RST N is asserted.

PCI Interrupt A

Pin Name: PCI INTA N

Pin Number: 95

Interrupt A is used to request an interrupt on the PCI bus. PCI INTA N is open collector and is an open drain output.

PCI Clock Signal Pin Names: PCI CLK Pin Number: 97

Clock Signal provides timing for all transactions on PCI and is an input to every PCI device. All other PCI signals (except PCI\_RST\_N, and PCI\_INTA\_N) are sampled on the rising edge of PCI\_CLK. All other timing parameters are defined with respect to this edge.

PCI Reset

Pin Name: PCI\_RST\_N

Pin Number: 96

PCI\_RST\_N is an active low input that is used to set the internal registers to their initial state. PCI\_RST\_N is typically the system power-on reset signal as distributed on the PCI bus.

PCI M66EN

Pin Name: PCI\_M66EN Pin Number: 152

This pin configures the PCI bus operating frequency. When low, the PCI bus operates from 0 to 33 MHz. When

high, the PCI bus operates from 33MHz to 66MHz.

#### Miscellaneous I/O

Flash Signals

Pin Name: FL ADDR00 / CLASS SEL

Pin Number: 49

When PCI\_RST\_N is deasserted, this pin is an output and represents flash memory address bit 0. During reset, it is sampled to configure Mass Storage class or RAID mode in the PCI Class Code register. A high on this pin sets Mass Storage class, a low sets RAID mode. The configuration state is latched internally when PCI\_RST\_N is deasserted. This pad is internally pulled high to enable Mass Storage class if left unconnected.

Pin Name: FL\_ADDR01 / BA5\_EN

Pin Number: 50

When PCI\_RST\_N is deasserted, this pin is an output and represents flash memory address bit 1 During reset, it is sampled to configure Base address register 5. A high on this pin enables base address register 5, a low disables base address register 5. The configuration state is latched internally when PCI\_RST\_N is deasserted. This pin is internally pulled high to enable Base address register 5 when left unconnected.

Pin Name: FL ADDR[02-18]

Pin Numbers: 51, 54-57, 62-64, 66-69, 75-77, 79, 80

Flash Memory address bits; 19 total for 512K address space. Flash address pins 14 to 18 are used to select internal test modes in conjunction with the TEST\_MODE pin.

Pin Name: FL\_DATA[0-7] Pin Numbers: 85-87, 90-94

8-bit Flash memory data bus or GPIO pins

Pin Name: FL\_RD\_N Pin Number: 52

Flash read enable signal, active low

Pin Name: FL\_WR\_N Pin Number: 53

Flash write enable signal, active low

Pin Name: FL\_CS\_N Pin Number: 81

Flash chip select signal, active low

Serial EEPROM Interface Signals

Pin Name: EEPROM\_SDAT

Pin Number: 47

Serial Interface (I2C) data line

Pin Name: EEPROM\_SCLK

Pin Number: 48

Serial Interface (I2C) clock

LED Drivers